Copyright by Thomas Charles Lauzon 2009 The Thesis committee for Thomas Charles Lauzon certifies that this is the approved version of the following thesis:

# Suitability of FPGA-based Computing for Cyber-Physical Systems

APPROVED BY

SUPERVISING COMMITTEE:

Derek Chiou, Supervisor

Aloysius Mok, Supervisor

## Suitability of FPGA-based Computing for Cyber-Physical Systems

by

## Thomas Charles Lauzon

### THESIS

Presented to the Faculty of the Graduate School of The University of Texas at Austin in Partial Fulfillment of the Requirements for the Degree of

## MASTER OF SCIENCE IN ENGINEERING

THE UNIVERSITY OF TEXAS AT AUSTIN

December 2009

Dedicated to my parents, Véronique and Charles and my sister Catherine.

## Suitability of FPGA-based Computing for Cyber-Physical Systems

Thomas Charles Lauzon, M.S.E. The University of Texas at Austin, 2009

> Supervisors: Derek Chiou Aloysius Mok

Cyber-Physical Systems theory is a new concept that is about to revolutionize the way computers interact with the physical world by integrating physical knowledge into the computing systems and tailoring such computing systems in a way that is more compatible with the way processes happen in the physical world. In this master's thesis, Field Programmable Gate Arrays (FPGA) are studied as a potential technological asset that may contribute to the enablement of the Cyber-Physical paradigm. As an example application that may benefit from cyber-physical system support, the Electro-Slag Remelting process - a process for remelting metals into better alloys - has been chosen due to the maturity of its related physical models and controller designs. In particular, the Particle Filter that estimates the state of the process is studied as a candidate for FPGA-based computing enhancements. In comparison with CPUs, through the designs and experiments carried in relationship with this study, the FPGA reveals itself as a serious contender in the arsenal of computing means for Cyber-Physical Systems, due to its capacity to mimic the ubiquitous parallelism of physical processes.

Keywords: Cyber-Physical Systems, Particle Filter, Electro-Slag Remelting, FPGA, CPU, Sequential Monte-Carlo Methods, Pipelining, Bluespec.

# Table of Contents

| Abstra  | nct        |                     |                                                                  | v  |

|---------|------------|---------------------|------------------------------------------------------------------|----|

| List of | Table      | es                  |                                                                  | x  |

| List of | Figur      | es                  |                                                                  | xi |

| Chapte  | er 1.      | Introd              | uction                                                           | 1  |

| 1.1     | Resea      | rch Cont            | ext                                                              | 1  |

|         | 1.1.1      | Cyber-F             | Physical Systems                                                 | 1  |

|         | 1.1.2      | Plant M             | Iodel                                                            | 2  |

|         | 1.1.3      | Specific<br>Slag Re | Applications: Gas Metal Arc Welding and Electro-<br>melting      | 3  |

|         | 1.1.4      | State E             | stimation for the Electroslag Remelting Process .                | 4  |

|         | 1.1.5      | Particle            | Filtering Applied to Electroslag Remelting                       | 4  |

|         |            | 1.1.5.1             | Overview of Particle Filtering                                   | 5  |

|         |            | 1.1.5.2             | Theoretical Background                                           | 5  |

|         |            | 1.1.5.3             | Sampling Importance Resampling - Presentation                    | 7  |

|         |            | 1.1.5.4             | Sampling Importance Resampling - Algorithm .                     | 9  |

| 1.2     | Probl      | em to So            | lve                                                              | 10 |

| 1.3     |            |                     | udy: Influence of the Quantity of Particles on the<br>e Estimate | 10 |

|         | 1.3.1      | Experin             | nents, Analysis and Results                                      | 11 |

|         |            | 1.3.1.1             | Evaluation Means                                                 | 11 |

|         |            | 1.3.1.2             | Experimental Setup                                               | 11 |

|         |            | 1.3.1.3             | Results                                                          | 12 |

|         |            | 1.3.1.4             | Conclusion                                                       | 17 |

|         | 1.3.2      | Summa               | ry of the Problem to Solve                                       | 18 |

| 1.4     | Thesis     | s Statem            | ent                                                              | 18 |

| 1.5     | Objectives |                     | 19                                                               |    |

| 1.6     | Appro      | oach                |                                                                  | 19 |

| Chapter 2. |                               | Study of the Particle Filtering Algorithm as Applied<br>to Electro-slag Remelting            | $\frac{1}{21}$ |

|------------|-------------------------------|----------------------------------------------------------------------------------------------|----------------|

| 2.1        | Partic                        | cle Filter Algorithm for the Electro-slag Remelting Process                                  | 21             |

| 2.2        | 2.2 Parallelization Potential |                                                                                              |                |

|            | 2.2.1                         | Physical Model                                                                               | 26             |

|            | 2.2.2                         | Measurement Model                                                                            | 28             |

|            | 2.2.3                         | Likelihood Function                                                                          | 29             |

| Chapte     | er 3.                         | Implementation                                                                               | 30             |

| 3.1        | CPU                           | implementation in C $\ldots$                                                                 | 30             |

|            | 3.1.1                         | Code                                                                                         | 31             |

| 3.2        | FPGA                          | A Implementation                                                                             | 33             |

|            | 3.2.1                         | FPGA technology                                                                              | 33             |

|            | 3.2.2                         | ESL tool: Bluespec System Verilog                                                            | 34             |

|            | 3.2.3                         | FPGA Implementation Techniques                                                               | 35             |

|            | 3.2.4                         | Mixed control and data flow chart of the Algorithm                                           | 36             |

|            |                               | 3.2.4.1 Physical Model (F) $\ldots$ $\ldots$ $\ldots$ $\ldots$                               | 36             |

|            |                               | 3.2.4.2 Measurement Model (H) $\ldots$ $\ldots$ $\ldots$                                     | 39             |

|            |                               | 3.2.4.3 Whole Simulator $\ldots$                                                             | 40             |

|            | 3.2.5                         | Customized Operators                                                                         | 41             |

|            |                               | 3.2.5.1 Division                                                                             | 42             |

|            |                               | $3.2.5.2  \text{Inversion}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 46             |

|            |                               | 3.2.5.3 Inversion Farm                                                                       | 47             |

|            |                               | 3.2.5.4 Exponential $\ldots$                                                                 | 49             |

|            | 3.2.6                         | FPGA Implementation Toolchain                                                                | 51             |

|            |                               | 3.2.6.1 Software Versions                                                                    | 52             |

| Chapter 4. |                               | Implementation Results and Analysis                                                          | 53             |

| 4.1        | Imple                         | ementation Results                                                                           | 53             |

|            | 4.1.1                         | CPU Results                                                                                  | 53             |

|            | 4.1.2                         | FPGA Results                                                                                 | 53             |

| 4.2        | Analy                         | <i>r</i> sis                                                                                 | 56             |

|            | 4.2.1                         | Speed and Number of Devices                                                                  | 56             |

|        |        | 4.2.1.1 CPU Speed                                                   | 57  |

|--------|--------|---------------------------------------------------------------------|-----|

|        |        | 4.2.1.2 Number of CPUs Required for a Given Perfor-<br>mance Level  | 58  |

|        |        | 4.2.1.3 FPGA Speed                                                  | 58  |

|        |        | 4.2.1.4 Number of FPGAs Required for a Given Perfor-<br>mance Level | 60  |

|        | 4.2.2  | FPGA v. CPU performance outlook                                     | 60  |

|        |        | 4.2.2.1 Speeds                                                      | 60  |

|        |        | 4.2.2.2 Number of Devices                                           | 63  |

|        |        | 4.2.2.3 Performance Analysis                                        | 65  |

| Chapt  | er 5.  | Conclusion and Future Work                                          | 67  |

| 5.1    | Analy  | rsis of Results                                                     | 67  |

| 5.2    | Concl  | usion                                                               | 68  |

| 5.3    | Future | e Work                                                              | 69  |

| Appen  | dix    |                                                                     | 71  |

| Appen  | dix 1. | Bluespec Implementation Code                                        | 72  |

| 1.1    |        | iption                                                              | 72  |

| 1.2    |        | e Code                                                              | 72  |

|        | 1.2.1  | Types.bsv                                                           | 72  |

|        | 1.2.2  | Params.bsv                                                          | 75  |

|        | 1.2.3  | inverse.bsv                                                         | 78  |

|        | 1.2.4  | invFarm.bsv                                                         | 82  |

|        | 1.2.5  | ExponFix.bsv                                                        | 86  |

|        | 1.2.6  | HBRAM.bsv                                                           | 91  |

|        | 1.2.7  | Fpiped.bsv                                                          | 98  |

|        | 1.2.8  | FHpiped.bsv                                                         | 111 |

|        | 1.2.9  | FHpipedTb.bsv                                                       | 117 |

|        | 1.2.10 |                                                                     | 121 |

|        | 1.2.11 | MultipleFHTb.bsv                                                    | 123 |

| Biblio | graphy | 7                                                                   | 128 |

| Vita   |        | :                                                                   | 130 |

# List of Tables

| 4.1 | FPGA Specifications              | 54 |

|-----|----------------------------------|----|

| 4.2 | Xilinx ISE Project Configuration | 54 |

| 4.3 | FPGA Resource Utilization        | 55 |

# List of Figures

| 1.1 | Basic Form of a Manufacturing Process                                                                                                                  | 3  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | The Particle Filter: recursively improving the estimate of the posterior distribution by selecting the most important particles for the next iteration | 8  |

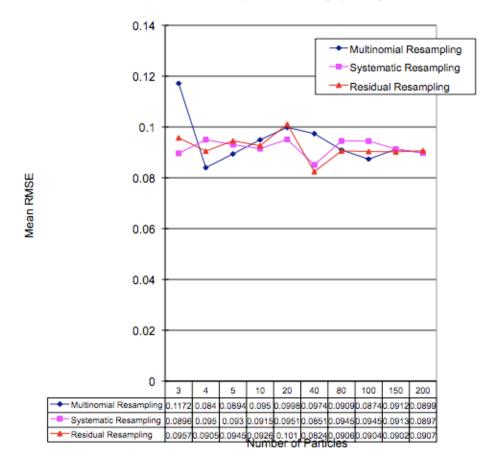

| 1.3 | RMSE $\Delta$                                                                                                                                          | 13 |

| 1.4 | RMSE $T_s$                                                                                                                                             | 14 |

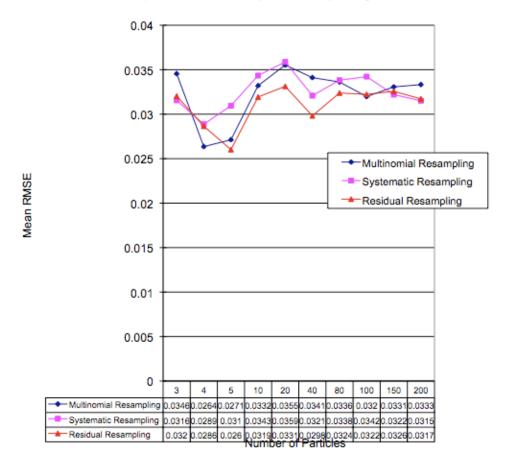

| 1.5 | RMSE $d$                                                                                                                                               | 15 |

| 1.6 | RMSE $X_{ram}$                                                                                                                                         | 16 |

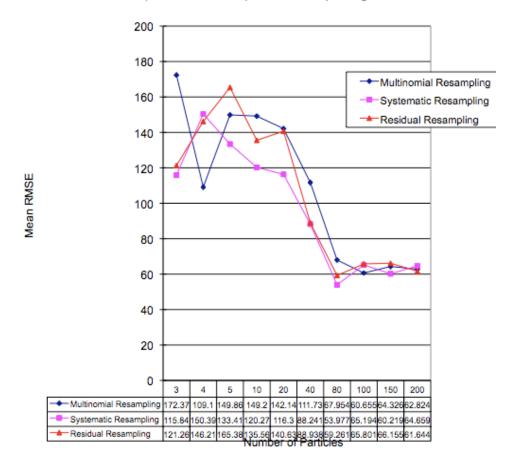

| 1.7 | RMSE $M_e$                                                                                                                                             | 17 |

| 2.1 | General Form of the Particle Filter Based Estimator                                                                                                    | 24 |

| 2.2 | Particle Filter with Multiple Sampling Stages in Parallel                                                                                              | 26 |

| 3.1 | Physical Model Flow Chart                                                                                                                              | 37 |

| 3.2 | Full Physical Model Flow Chart                                                                                                                         | 38 |

| 3.3 | Physical Model Flow Chart - Inversion Excluded                                                                                                         | 39 |

| 3.4 | Measurement Model Flow Chart                                                                                                                           | 40 |

| 3.5 | Whole System Flow Chart                                                                                                                                | 41 |

| 3.6 | Inversion Farm Module                                                                                                                                  | 49 |

| 3.7 | Computing the powers of x for the Taylor series expansion of the exponential function                                                                  | 51 |

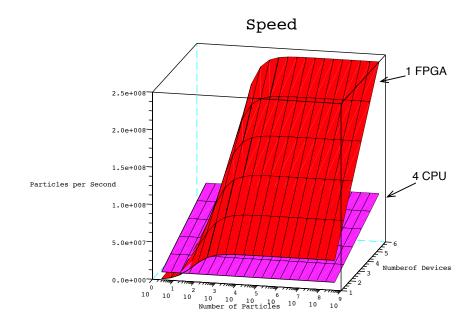

| 4.1 | Particle Computation Rates for 4 CPU Cores and 1 FPGA based simulator                                                                                  | 62 |

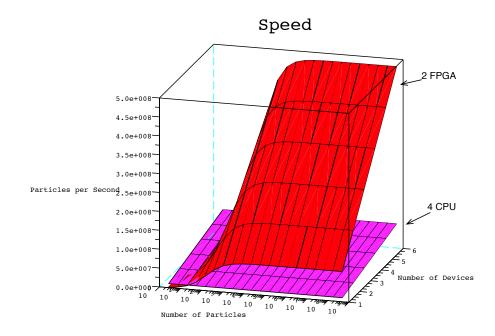

| 4.2 | Particle Computation Rates for 4 CPU Cores and 2 FPGA based simulator                                                                                  | 63 |

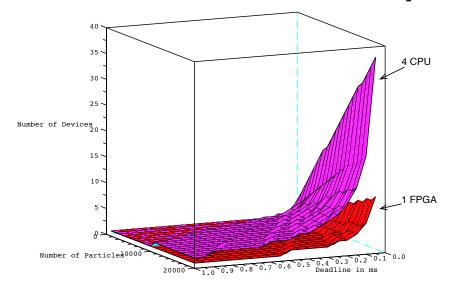

| 4.3 | Number of Devices Required; 4 Cores per CPU v. 1 Simulator<br>per FPGA                                                                                 | 64 |

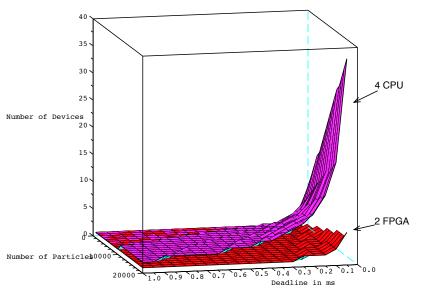

| 4.4 | Number of Devices Required; 4 Cores per CPU v. 2 Simulator<br>per FPGA                                                                                 | 65 |

## Chapter 1

## Introduction

## 1.1 Research Context

#### 1.1.1 Cyber-Physical Systems

The context of this research is the solution space exploration for the implementation of algorithms used in cyber-physical systems. Cyber-physical systems are the combination of control, information technology and communication. In such systems, timing is critical and processes evolve concurrently. Examples of systems that will benefit from this technology, some of which proposed by Lee [8], are:

#### Transportation

Automated shipyard management, advanced automotive systems, avionics, air traffic control;

### Medical

Robotic surgery, assisted living, patient monitoring systems;

#### Utilities and infrastructure

Electric power, environmental control, water resource management, communications;

#### Physical virtuality

Telepresence, telemedicine;

#### Manufacturing

Process control, resource management;

### **Civil Engineering**

Structure health monitoring, robotics assisted construction, smart structures.

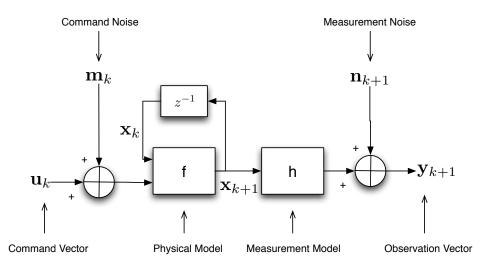

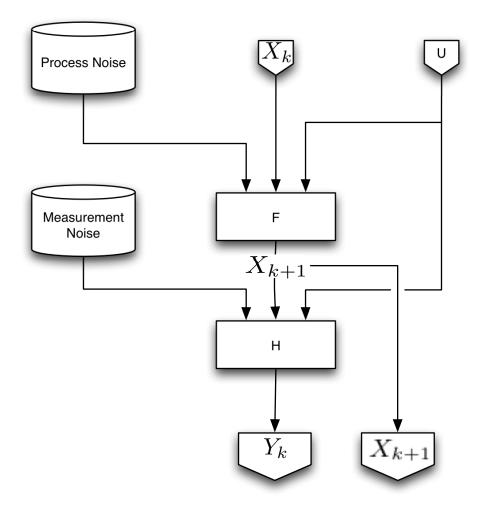

### 1.1.2 Plant Model

The physical elements in a cyber-physical system may be modeled in two parts: a physical model, f and a measurement model, h. The physical model is a set of equations that describe the dynamics of the system, whereas the measurement model is a set of equations that describe the link between the system's state and the sensor signals. In most complex (i.e. high-fidelity) models these equations are often non-linear.

The physical model outputs a new state based on the command signals and the current state. Usually, noise is present in the command signals. The measurement model outputs a new observation vector from the new state from the physical model. The observation vector also contains measurement noise.

The basic form of the plant model is demonstrated in Fig. 1.1.

Figure 1.1: Basic Form of a Manufacturing Process.

## 1.1.3 Specific Applications: Gas Metal Arc Welding and Electro-Slag Remelting

As an example of a process that can benefit from the Cyber-Physical Systems paradigm, our research group has selected the Gas Metal Arc Welding (GMAW) process. This process is similar to a previously studied process called Electroslag Remelting (ESR.) The study of the ESR was performed by Ahn for his Ph.D. [1]. Although the speed of the GMAW process is much faster than the ESR, it is assumed that the general forms of the control and observation algorithms are similar. This research is therefore a follow-up of Ahn's research.

#### 1.1.4 State Estimation for the Electroslag Remelting Process

One particular issue that arises in plants such as the ESR is the presence of noise on both the control signals and the observation signals. This is problematic for the purpose of controlling the process, since the state of the system may be quite different from the raw observations. If these raw observations were to be used directly, this would lead to improper process control. To resolve this problem, the state has to be inferred by a state estimator.

Due to the non-linear nature of the high-fidelity stochastic physical and measurement models of the ESR process, one estimation algorithm under investigation is the Particle Filter also known as Sequential Monte Carlo Methods (SMC.) Ahn's [1] study of estimation methods that inlcuded the Linear Kalman Filter, the Extended Kalman Filter and the Unscented Kalman Filter and the particle filter, has shown that although Kalman Filters provide good estimates in the Unscented Kalman Filter, the accuracy of these estimates doesn't match the accuracy of the Particle Filter for the ESR in terms of root mean squared error. This is due to the fact that if well designed and if the number of samples is large enough, the estimates tend toward the optimal Bayesian estimate.

#### 1.1.5 Particle Filtering Applied to Electroslag Remelting

Particle Filtering is also known as Sequential Monte Carlo Methods. A detailed explanation of Particle Filtering would be beyond the scope of this document.

#### 1.1.5.1 Overview of Particle Filtering

To understand the concept behind Particle Filtering, one may see each particle as a possible (or hypothetical) physical state of the plant. Additionally, each particle has a weight that represents how likely the plant may be in that state. The weights are normalized such that the sum of all the weights is equal to one. The particles with the heaviest weights are the ones that are most likely to be equal to the real plant state. After applying a certain command vector to the plant, simulations are done using the particles as initial states. These simulations provide new hypothetical states. The likelihood of each of these simulated states is obtained by further simulating their measurements and comparing their simulated measurements with the real measurements made on the real plant. The most likely states (i.e. the heaviest particles) are retained for the next round of simulations, hence the filtering. Ultimately, after a couple rounds, the particles should converge to the real state of the plant if the estimator is well designed.

#### 1.1.5.2 Theoretical Background

The basic objective of Sequential Monte Carlo Methods is to estimate recursively in time the posterior distribution of a random variable and the expectations for some function of interest.

In the case of cyber-physical systems, the random variable that needs its posterior to be estimated is the current state of the physical system. Knowing the current state is necessary to command the system to the next step on the trajectory that will lead the system into a desired final state. Typically, this signal is not directly available. It needs to be inferred from sensors, that may or may not directly sense the values that represent the state of the physical system. Furthermore, these sensed values often include significant noise.

Formally posed, the problem is stated as follows: [5]

The unobserved signal  $\{x_t; t \in \mathbb{N}\}, x_t \in \chi$ , is modeled as a *Markov Process* of prior distribution  $p(x_0)$  and transition  $p(x_t|x_{t-1})$ .  $\{y_t; t \in \mathbb{N}^*\}, y_t \in \Upsilon$  is a set of independent observations of the process with marginal distribution  $p(y_t|x_t)$ .

If we define  $x_{0:t} = \{x_0, \ldots, x_t\}$  and  $y_{1:t} = \{y_1, \ldots, y_t\}$  being all the signal values up to time t, *Bayes' theorem* gives at any time t:

$$p(x_{0:t}|y_{1:t}) = \frac{p(y_{1:t}|x_{0:t})p(x_{0:t})}{\int p(y_{1:t}|x_{0:t})p(x_{0:t})dx_{0:t}}$$

(1.1)

This equation can be written in recursive form:

$$p(x_{0:t+1}|y_{1:t+1}) = p(x_{0:t}|y_{1:t}) \frac{p(y_{t+1}|x_{t+1})p(x_{t+1}|x_t)}{p(y_{t+1}|y_{t+1})}$$

(1.2)

The marginal distribution, what we are looking for is obtained with these two steps:

Prediction:

$$p(x_t|y_{1:t-1}) = \int p(x_t|x_{t-1})p(x_{t-1}|y_{1:t-1})dx_{t-1}$$

(1.3)

Updating:

$$p(x_t|y_{1:t}) = \frac{p(y_t|x_t)p(x_t|y_{1:t-1})}{\int p(y_t|x_t)p(x_t|y_{1:t-1})\mathrm{d}x_t}$$

(1.4)

The probability density functions can be discretized.

For further details, the reader may refer to *Sequential Monte Carlo Methods in Practice* by Arnaud Doucet, Nando De Freitas, Neil James Gordon, Neil Gordon. [5] The following description comes from this source.

#### 1.1.5.3 Sampling Importance Resampling - Presentation

As stated in [2] the key idea behind Carlo Methods is to represent the posterior density function by a set of random samples with associated weights which can then be used to compute estimates. In [2], the observation vector  $\mathbf{y}$  is called  $\mathbf{z}$ . In the literature, we find both uses, although usually  $\mathbf{y}$  stands for the output, whereas  $\mathbf{z}$  is the observation, which are often the same, but not necessarily. For instance  $\mathbf{y}$  could be the raw data coming out of sensors, whereas  $\mathbf{z}$  could be the interpreted value.

$$p(\mathbf{x}_{0:k}|\mathbf{z}_{1:k}) \approx \sum_{i=1}^{N} w_k^i \delta\left(\mathbf{x}_{0:k} - \mathbf{x}_{0:k}^i\right)$$

(1.5)

where the weights  $w_k^i$  are defined recursively as:

$$w_k^i \propto w_{k-1}^i \frac{p\left(\mathbf{z}_k | \mathbf{x}_k^i\right) p\left(\mathbf{x}_k^i | \mathbf{x}_{k-1}^i\right)}{q\left(\mathbf{x}_k^i | \mathbf{x}_{k-1}^i, \mathbf{z}_k\right)}$$

(1.6)

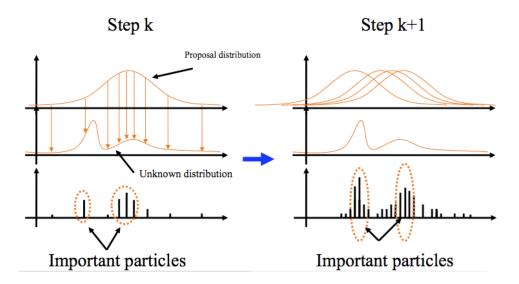

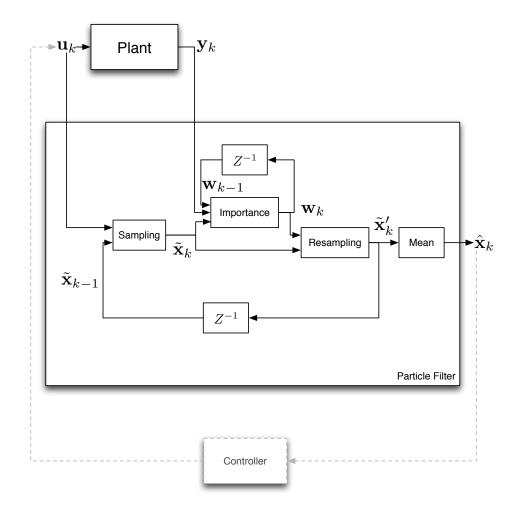

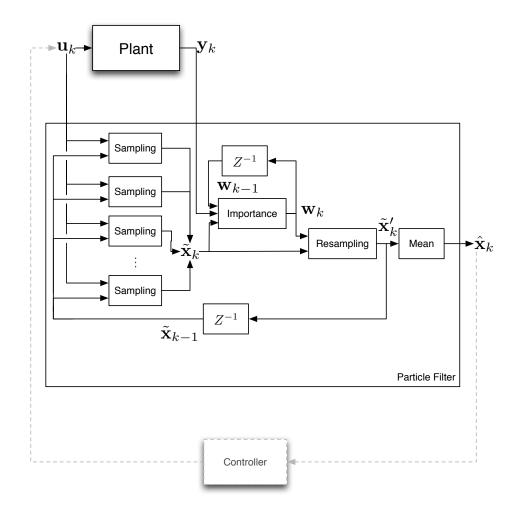

Figure 1.2: The Particle Filter: recursively improving the estimate of the posterior distribution by selecting the most important particles for the next iteration

The Sampling Importance Resampling (SIR) algorithm is the version that is used to for the Electroslag Remelting estimator. As the name suggest, it is composed of three steps:

**Sampling** This consist of drawing samples from the proposal distribution  $\tilde{\mathbf{x}}_{k}^{(i)} \sim q\left(\mathbf{x}_{k}^{(i)}|\mathbf{x}_{k-1}^{(i)}, \mathbf{z}_{k}\right)$

- **Importance** This is the computation of the samples weight using equation

(1.6)

- **Resampling** Which eliminates particles with small weights to concentrate on the most important one in order to reduce the *sample impoverishment* effect.

At each step, n simulations are done by adding noise to the physical and measurement models. The likelihood of each observation is then computed based on the real plant observation. The particles that generated the most likely observations are kept and replicated for the next round of simulations. The number of replicates depends on the importance (high likelihood) of the particle.

#### 1.1.5.4 Sampling Importance Resampling - Algorithm

As given in [2] and summarized in [1] the SIR particle filter algorithm is as follows:

$$\left\{ x_{k}^{(i)}, w_{k}^{(i)} \right\}_{i=1}^{N} = ParticleFilter \left[ \left\{ x_{k-1}^{(i)}, w_{k-1}^{(i)} \right\}_{i=1}^{N}, \mathbf{z}_{k} \right]$$

• For  $i = 1 : N$

- Draw  $\tilde{\mathbf{x}}_{k}^{(i)} \sim q \left( \mathbf{x}_{k}^{(i)} | \mathbf{x}_{k-1}^{(i)}, \mathbf{z}_{k} \right)$

- Evaluate  $w_{k}^{(i)} = p \left( \mathbf{z}_{k} | \mathbf{x}_{k-1}^{(i)} \right) w_{k-1}^{(i)}$

• For

$$i = 1 : N$$

– Normalize weights  $\bar{w}_k^{(i)} = \frac{w_k^{(i)}}{\sum j = 1^N w_k^{(j)}}$

• Calculate

$$N_e f f = \frac{1}{\sum_{k=1}^{N} \left( w_k^{(i)} \right)^2}$$

• If

$$N_{eff} < N_{thr}$$

-  $\left\{ \mathbf{x}_{k}^{(i)}, w_{k}^{(i)} \right\}_{i=1}^{N}$  = Resample  $\left[ \left\{ x_{k}^{(i)}, w_{k}^{(i)} \right\}_{i=1}^{N} \right]$

• Else

$$-\left\{\mathbf{x}_{k}^{(i)}, w_{k}^{(i)}\right\}_{i=1}^{N} = \left\{x_{k}^{(i)}, w_{k}^{(i)}\right\}_{i=1}^{N}$$

### 1.2 Problem to Solve

The initial problem we set ourselves to solve was the problem faced by Ahn. His implementation of the Particle Filter was unable to compute a sufficient amount of simulations under the process control deadline. Without studying the problem in detail, we opined that FPGA or ASIC would be a potential answer to this computation speed problem.

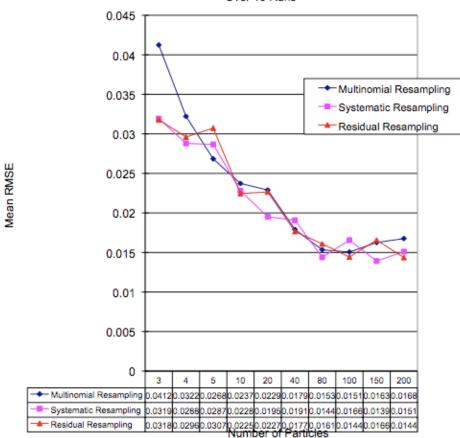

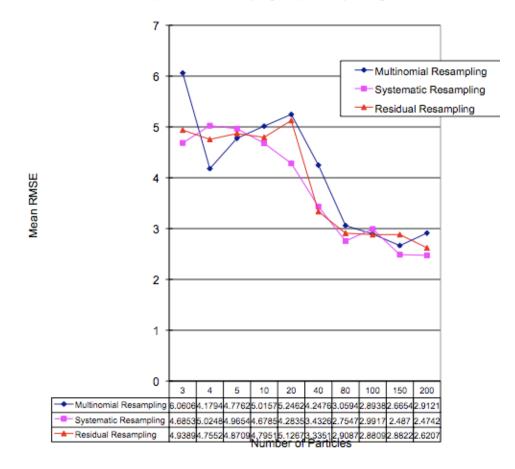

## 1.3 Preliminary Study: Influence of the Quantity of Particles on the Precision of the Estimate

An intuitive idea is that to improve the state estimates one only needs to increase the number of simulations. As a preliminary study, the influence of the number of particles on the precision of the estimates was studied in order to set a performance goal for the ESR estimator. The result of this study is that there is a limit to the maximum precision that can be achieved. In other words, that mean that there is a threshold after which increasing the number of particles has no effect on the precision of the estimates. Furthermore, a reassuring result is that increasing the number of particles (with the given models) always reduces the error of the estimate. While some state variable estimates are poorly sensitive to the number of particles others steadily improve up to 200 particles. After 200 particles, the improvements in precision are negligible (for this set of physical and measurement model.

## 1.3.1 Experiments, Analysis and Results

### 1.3.1.1 Evaluation Means

In order to evaluate the performance of the estimator, the root mean squared error (RMSE) between the true state of the plant (which is directly available from the plant model) and the estimated state is computed for each state variable. The objective is to have the smallest RMSE possible.

$$RMSE = \sqrt{\frac{\sum_{i=1}^{n} (\mathbf{x}_{true,i} - \mathbf{x}_{estimated,i})^2}{n}}$$

(1.7)

The estimator was tested in open loop configuration with no controller. The process and measurement noise were from a gaussian distribution with parameters that were measured by Ahn at the plant.

#### 1.3.1.2 Experimental Setup

These results were computed using the C implementation. Using the original implementation under Matlab would yield the same results.

Three types of resampling techniques were used.

- Systematic resampling

- Residual resampling

## • Multinomial resampling

This simulation was run over 1000 seconds divided in 7500 steps and repeated 10 times for statistical results.

The RMSE was computed for different numbers of particles for each state variable.

### 1.3.1.3 Results

The results are found in figure (1.3) to (1.7)

Root Mean Squared Error for Delta (Boundary Layer Thickness) Averaged Over 10 Runs

Figure 1.3: RMSE  $\Delta$

Root Mean Squared Error for Ts (Slag Temperature) Averaged Over 10 Runs

Figure 1.4: RMSE  $T_s$

Root Mean Squared Error for D (Penetration Length) Averaged Over 10 Runs

Figure 1.5: RMSE d

Root Mean Squared Error for Xram (Ram Position) Averaged Over 10 Runs

Figure 1.6: RMSE  $X_{ram}$

Root Mean Squared Error for Me (Electrode Mass) Averaged Over 10 Runs

Figure 1.7: RMSE  $M_e$

### 1.3.1.4 Conclusion

From these experiments it is concluded that 200 particles is the threshold after which the estimates have reached their maximum precision.

#### **1.3.2** Summary of the Problem to Solve

Based on the preliminary experimental results and the fact that the given sampling rate is 133 ms the goal to achieve is the computation of 200 particles under 133ms.

## 1.4 Thesis Statement

Based on the fact that the physical world is ubiquitously parallel, i.e. processes occur concurrently, it seems that parallel computing devices would be the best suited devices for real-time inline simulation of the physics of a cyber-physical system. Supporting this argument is the fact that modern estimation techniques, such as Particle Filtering, make use of independent probabilistic sampling. Since the sampling is independent, it can be done in parallel, bolstering the use of parallel devices, such as FPGAs. Although modern CPUs are now multicore and work at Gigahertz frequencies, FPGAs appear to be a better platform due to their intrinsic parallel architecture.

An FPGA based solution would take advantage of the fact that not only the physical simulations done in Particle Filtering are independent and can be done in parallel but also of the fact that the physical processes within the plant occur concurrently themselves. As a result, a significant amount of parallelization is possible, for which FPGAs are well suited.

### 1.5 Objectives

The objective is to figure out how to evaluate the performance of computing devices for the purpose of assisting the task of designing cyber systems that provides adequate computing power for controlling a specific physical process. We have identified and selected three types of computing devices that differ in nature and present potential applicability to the domain of cyberphysical systems. The first type is the Central Processing Unit (CPU) type, the second is the Graphical processing Unit (GPU) type (not discussed in this Master's Thesis) and the last one is the Field Programmable Gate Array (FPGA) type. These types may be characterized by the parallelism present in their computing architecture. CPUs present the lowest order of parallelism. Current CPUs on the market typically offer 4 or 8 fast cores that can be used in parallel. In contrast, GPUs provide a higher number of parallel processing units, in the order of the hundreds. On the other end of the spectrum, FPGAs are inherently parallel devices which can be tailored to concurrently process a large number of elementary operations.

### 1.6 Approach

Using a well known computer controlled manufacturing process, Electroslag Remelting (ESR), an application that is mature for experimentation, we designed an FPGA based solution and compared its performance with that of a reference CPU based implementation. From both implementation we derived computation speed models that give a macro level view of the performance attainable on both platforms.

## Chapter 2

# Study of the Particle Filtering Algorithm as Applied to Electro-slag Remelting

In this chapter, the algorithm is described in the special case of the Electroslag Remelting process. After this, the proposed method for accelerating the algorithm through the use of parallelization is presented, followed by a study of the data and data types and how this is a potential barrier to implementation and speedup potential

## 2.1 Particle Filter Algorithm for the Electro-slag Remelting Process

In the previous chapter, the general form of the particle filter has been introduced. However, this form is somewhat abstract. In fact, the question is "how do we draw particles?" As said earlier, the particles are drawn from a proposal distribution  $q(x_k|x_{k-1}, z_k)$ . Since this distribution is difficult to obtain, the transition prior  $q(\mathbf{x}_k|\mathbf{x}_{k-1})$  is chosen as a proposal distribution. This distribution is only dependent on the previous state  $\mathbf{x}$ . In many cases this is acceptable.

We would like to be able to sample from the transition prior by run-

ning a particle through the physical model and adding process noise to the new state. The problem is that it is difficult to know the parameters of the distribution of  $\mathbf{x}$  since we cannot measure it directly by experiment. Instead, particles are drawn by adding noise to the control vector,  $\mathbf{u}$ , running those noisy input values through the physical model and the measurement model, and then adding the measurement noise. The resulting values are the particles.

$$\mathbf{x}_{k}^{(i)} \sim q\left(\mathbf{x}_{k}^{(i)}|\mathbf{x}_{k-1}^{(i)}\right) \sim f\left(\mathbf{x}_{k-1}^{(i)}, \mathbf{u}_{k} + \mathbf{v}_{k}^{(i)}\right)$$

(2.1)

where:  $\mathbf{x}_{k}^{(i)}$  is the particle (i) at step k, f is the physical model,  $\mathbf{u}_{k}$  is the command vector at step k and  $\mathbf{m}_{k}$  is the generated process noise vector at step k for particle *i*. This noise may come from any distribution.

The next step is to evaluate the weights. This is done recursively by multiplying the previous weights by the likelihood of each observation. The likelihood function in the case of the ESR is a gaussian.

For each particle, the simulated observation is:

$$z_k = h\left(\mathbf{x}_k\right) + \mathbf{n}_k \tag{2.2}$$

where: h is the measurement model,  $\mathbf{x}_k$  is the drawn state and  $\mathbf{n}_k$  is the measurement noise vector. The noise vector is random and different for each particle. As can be seen from this equation, the observation is a direct function of the state and the noise. The likelihood is then:

$$p\left(z_k|x_k^{(i)}\right) \propto e^{\left(-\frac{1}{2}\left(z_k - z_k^{(i)}\right)^t R_r\left(z_k - z_k^{(i)}\right)\right)}$$

(2.3)

$R_r$  is the covariance matrix,  $z_k$  is the observation from the plant at step k,  $z_k^{(i)}$  is the simulated observation for particle *i*.

$$w_k^{(i)} = p\left(z_k | x_k^{(i)}\right) w_{k-i}^{(i)}$$

(2.4)

$w_k^{(i)}$  is the weight of particle *i* at step *k*,  $w_k^{(i)}$  is the weight of particle *i* at step *k*-1.

Once all the weights have been computed, they must be normalized so that the sum of the weights is equal to 1.

The last part is the resampling of the particles. This part is not covered in detail in this document in detail as it is not the target of this study. The basic mechanism is that the particles that are the most important (highest weights) are selected for the next step. The reader may consult [2] for further reference.

Figure 2.1: General Form of the Particle Filter Based Estimator.

## 2.2 Parallelization Potential

One specificity of the Particle Filter is that the sampling part can be parallelized since each particle is drawn independently from another. It is supposed that the sampling part may be accelerated through parallelization on an FPGA for example. Not only can the sampling of each particle be done in parallel, many of the internal computations, which are the physical and measurement models of the concurrent processes, can also be done in parallel. As seen in the estimator diagram, the likelihood function can also be computed in parallel. But the parallelization potential stops here, as the next step (normalization) requires all the weights from all the particles. Finally, the resampling may potentially benefit from internal parallelization, but this study has not been done yet and it is believed at this point that the speed improvement from this parallelization will not be as significant as the parallelization of the sampling stage, the mechanism of which remains the same independently of the physical and measurement models used. The equations for the models come from Ahn's Dissertation [1].

Figure 2.2: Particle Filter with Multiple Sampling Stages in Parallel

## 2.2.1 Physical Model

The physical model is a set of differential equations that describe the dynamics of the process. Here are the equations of the model for the Electroslag Remelting process.

$$\dot{\mathbf{x}} = \begin{bmatrix} \dot{\Delta} \\ \dot{T}_s \\ \dot{d} \\ \dot{X}_{ram} \\ \dot{M}_e \end{bmatrix} = f\left(\mathbf{x}, \mathbf{u}\right) = \begin{cases} \frac{C_{\Delta\Delta}\alpha_r}{\Delta} - \frac{C_{\Delta p}}{h_m} p_{m,r}(T_s) \\ \frac{1}{\rho_s \nu_s C_s} \left\{ p_{in,r}(T_s, d, I_c) - Q_m(T_s) - Q_s(T_s) \right\} \\ \frac{C_{s\Delta}\alpha_r}{\Delta} - \frac{C_{sp}}{h_m} p_{m,r}(T_s) + \frac{1}{a} \left( V_{ram,c} + V_{ram,b} \right) \\ V_{ram,c} + V_{ram,b} \\ -\rho A_e \dot{s}(\Delta, T_s) \end{cases}$$

(2.5)

where:

$$\begin{cases}

\dot{s}(\Delta, T_s) = -\frac{\alpha_r C_{s,\Delta}}{\Delta} + \frac{C_{sp} p_{m,r}(T_s)}{h_m} \\

p_{m,r}(T_s) = (1 + \mu_r) \frac{Q_m(T_s)}{A_e} \\

Q_m(T_s) = H_e A_e(T_s - T_m) \\

Q_s(T_s) = H_s 2\pi r_i h_{s0}(T_s - T_{ss}) \\

p_{in,r}(T_s, d, I_c) = Volt(T_s, d, I_c) I_c \\

Volt(T_s, d, I_c) = R(T_s, d) I_c \\

R(T_s, d) = R_d(d) e^{(} - A_{elect}(T_s - T_{s^*}) \\

R_d(d) = \begin{cases}

R_1 - m_0 d & d < d_inflection \\

R_1 - m_1 d & d \ge d_inflection

\end{cases}$$

While it is important for the the design of these models to know what all these names mean, for the problem of studying the computation what they stand for is insignificant. It is however important to realize that all the values that are not part of the state vector  $\mathbf{x}$  or the command vector  $\mathbf{u}$  are constants, i.e. the state vectors contain all the variables of these equations. All other values are parameters that can be pre-computed.

The discrete version is obtained by integrating  $f(\mathbf{x}, \mathbf{u})$  over the sampling period T.

$$\mathbf{x}_{k+1} = \mathbf{x}_k + f\left(\mathbf{x}_k, \mathbf{u}_k\right) . T$$

(2.6)

Finally, the command noise  $\mathbf{m}_k$  is added to the command vector, yielding:

$$\mathbf{x}_{k+1} = \mathbf{x}_k + f\left(\mathbf{x}_k, \mathbf{u}_k + \mathbf{m}_k\right) . T$$

(2.7)

#### 2.2.2 Measurement Model

In the case of the electroslag remelting model, the measurement equations are rather simple. The output vector  $\mathbf{y}$  contains the penetration depth d, the ram position  $X_{ram}$ , the current  $I_r$ , the weight read on the load cell LCand the voltage *Volt*

$$\mathbf{y} = h(\mathbf{x}) = \begin{cases} d \\ X_{ram} \\ I_c \\ LC \\ Volt \end{cases}$$

(2.8)

where:

$$\begin{cases} R = R_d e^{(-A_{elect}(T_s - T_{s^*}))} \\ R_d = \begin{cases} R_1 - m_0 d & d < 0 \\ R_1 - m_1 d & d > 0 \\ LC = \begin{cases} M_e - \rho_s A_e d & d > 0 \\ M_e & \text{otherwise} \\ Volt = RI_c \end{cases} \end{cases}$$

Finally, the measurement noise  $\mathbf{n}_k$  is added to the command vector, yielding:

$$\mathbf{y}_{k} = h\left(\mathbf{x}_{k}\right) + \mathbf{n}_{k} \tag{2.9}$$

#### 2.2.3 Likelihood Function

The weights are finally computed through the use of the likelihood function based on the simulated (drawn) observations. The likelihood function is the following:

$$l = e^{-\frac{1}{2} \left( \mathbf{y}_{\text{plant}} - \mathbf{y}_{\text{particle}} \right)^T \Sigma^{-1} \left( \mathbf{y}_{\text{plant}} - \mathbf{y}_{\text{particle}} \right)}$$

(2.10)

# Chapter 3

## Implementation

A working version of the estimator for the ESR process has been written under Matlab by Ahn. Both CPU and FPGA perform the same functions as this Matlab code. In fact the Matlab results were used to validate both implementations. The CPU implementation was done in C, whereas the FPGA implementation was done using Bluespec System Verilog.

## 3.1 CPU implementation in C

As discussed in the introduction of this chapter, the CPU implementation was done in C. The primary reason for this choice is the fact that many modern real-time control systems using CPUs use this language due to its simplicity and its robustness. Although C doesn't natively provide many types (e.g. no fixed-point type, which can be useful for speeding up some of the computation,) C natively supports double precision data types and comes with many mathematical functions such as the exponential function, which is required to compute the resistance values in the ESR's models. In order to verify that the C code performs the same tasks as the Matlab code, the Process and Measurement noise have been stored in text files that are both accessible by Matlab and C code. In the end it was verified that the C implementation provides the same results as the original Matlab code.

#### 3.1.1 Code

Only the physical model, f, and the measurement models are included, since we are only studying the sampling part.

```

void f

/*IN:*/

double x[SIZEOFX],

double u[SIZEOFU],

double noise [SIZEOFU],

double ts,

/*OUT:*/

double newX[SIZEOFX],

double * I

)

{

double tdelta, Rd, R, Volt, P, Qm, pm, Qs, Vram,

... Sdot, deltadot, Tsdot, ddot, Xramdot, Medot;

tdelta=ts;

if (X_D<dInflection)

Rd=R1-m0*X_D;

else

Rd=R1-m1*X_D;

R = Rd * exp(-Aelect * (X_TS-Tsstar));

*I=U_IC+Ib+noise[0];

Volt=R* *I+Voltb;

P=Volt * *I;

Qm = He * Ae * (X_TS - Tm);

pm=(1+mur)*Qm/Ae;

```

```

Qs=Hs*2*M_PI*ri*hs0*(X_TS-Tss);

Vram=U_VRAMC+Vramb+noise [1];

Sdot=-alphar*Csd0/X_DELTA+Csp*pm/hm;

//rate equations

deltadot = alphar *Cdd/X_DELTA-Cdp*pm/hm;

Tsdot = (P-Qm-Qs)/rhos/Vs/Cs0;

ddot = alphar * Csd0 / X_DELTA - Csp * pm / hm + Vram / a;

Xramdot = Vram;

Medot = -rhom *Ae * Sdot;

//Output

newX[0] = X_DELTA + deltadot*tdelta;

newX[1] = X_TS + Tsdot*tdelta;

newX[2] = X_D + ddot*tdelta;

newX[3] = X_XRAM + Xramdot*tdelta;

newX[4] = X_ME + Medot*tdelta;

}

void h

(

/*IN:*/

double x[SIZEOFX], double u[SIZEOFU],

... double noise [SIZEOFY],

/*OUT*/

double y [SIZEOFY]

)

{

double Rd, Ir, R, Volt, LC;

if (X_D < 0)

Rd = R1 - m0 * X_D;

else

Rd = R1 - m1 * X_D;

Ir = U_IC + Ib;

R = Rd * exp(-Aelect * (X_TS-Tsstar));

```

```

//estimated resistance

Volt = R*Ir + Voltb;

if (X_D>0)

LC = X_ME - rhos*Ae*X_D;

else

LC = X_ME;

y[0]=X_D+noise [0];

y[1]=X_XRAM+noise [1];

y[2]=Ir+noise [2];

y[3]=LC+noise [3];

y[4]=Volt+noise [4];

```

## 3.2 FPGA Implementation

## 3.2.1 FPGA technology

Field Programmable Gate Arrays (FPGA) are device that can be configured to perform sequential logical functions. FPGAs are the bigger type of logic devices in the programable device family. One of the advantages of FPGA is that the logic architecture can be designed specifically for a certain application, in particular, the architecture can be designed such that several computations are made in parallel, which can create a significant speedup in comparison with CPUs. One of the drawbacks is that an FPGA is more complicated to program compared to a CPU.

In our case, we hope to achieve a significant speedup through the parallelization of the sampling process. As discussed earlier, the sampling part of the algorithm can be done in parallel due to the fact that the samples are independent.

#### 3.2.2 ESL tool: Bluespec System Verilog

Electronic System Level design. ESL design is the creation of hardware from an algorithmic description. Bluespec has been identified as a tool that has a level of abstraction that is close to the algorithmic description, whilst at the same time being capable to give the designer control over the architecture of the hardware. Bluespec is capable of generating Verilog code that is directly usable in synthesis tools such as Xilinx ISE.

The first problem to consider when designing a system at the Electronic System Level is the set of operators that are available. At its most basic level, the FPGA is capable of performing logic operations on bits. On Xilinx FPGA this is done through the use of 6 bit Look-up tables (LUT). Xilinx FPGAs also feature DSP48 multipliers which are  $48 \times 48$  bit multipliers that return a 48 bit result. The Bluespec language provides additional operators, mostly for bits, or sets of bits such as integers.

The models, however, require rational numbers. Two options exist to represent rational numbers: fixed-point or floating point representation. Two points give fixed-point the advantage over floating-point. The first point is that fixed-point operations usually require less hardware, therefore are faster and require less physical resources. The second is that Bluespec already comes with a synthesizable fixed-point library whereas it currently provides no support for IEEE 754 floating point natively.

The Bluespec fixed point library [3] handles additions, subtractions and multiplications. It also provide function for bit field width extension or truncation and a multiplication function that returns data with the proper bit width. Unfortunately, the division and the exponential functions required for the algorithm are missing. They need to be implemented. On the upside, this allows for performance tradeoffs.

#### 3.2.3 FPGA Implementation Techniques

For the FPGA implementation, it is convenient to have a flow graph representation of the algorithm. The algorithm is separated in two parts: the computation of the physical model F and the measurement model H. Both models contain stages, which are separated by doted line in the diagrams. Operators within the same stage function in parallel. Furthermore, the design is made to operate in a pipelined fashion, therefore each stage is a stage of the pipeline. One final important detail that is absent in the figures for the sake of overcrowding the illustration are the memory queues between operators separated by multiple stages. The depth of these queues are naturally to be equal to the number of stages separating the operators minus one.

It is essential to note that the main operations natively provided are logic operations (AND, OR, NOT...) and 48 bit multiplications (on the Xilinx Virtex V FPGA). Any other operation needs to be provided by libraries or custom made. The first technique used is the pre-computation of parameters. Unlike C in which the compiler precomputes constant parameters (such as constant resistance values) automatically, parameters in the FPGA modules should be precomputed to avoid using operators unnecessarily. Furthermore, a nice feature of performing the pre-computation of parameters is that complicated operations such as divisions are avoided, saving many cycles and hardware resources.

The second technique is the use of non native operations in the form of modules. For the physical and measurement models of the ESR, two non native operations are required: divisions and exponentiations. These operations can be implemented in the form of modules. These modules may require several cycles to complete their functions. When this is the case, the length of the stage that contains such modules is equal to the length of the longest module - or longest chain of modules - in terms of number of cycles.

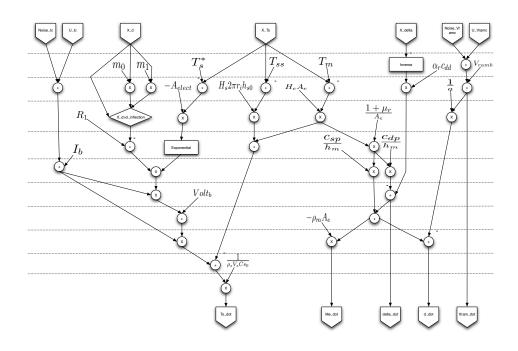

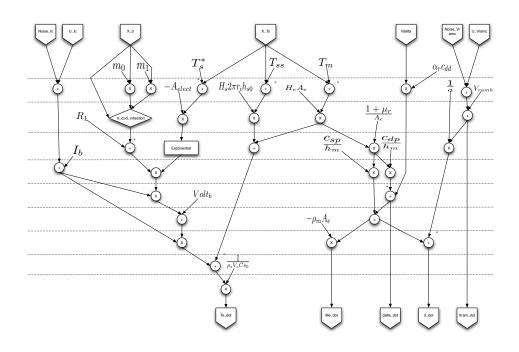

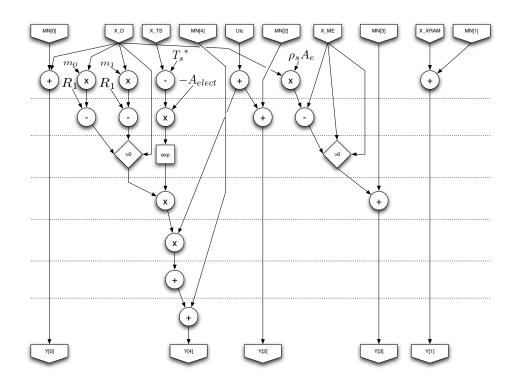

# 3.2.4 Mixed control and data flow chart of the Algorithm3.2.4.1 Physical Model (F)

The ESR's physical model has been divided in ten stages. While eight of these stages last only one cycle, two of them require multiple cycles due to the use of non-native operations. These non-native operations are presented later. The physical model computes the rates of variation of each state variable (i.e.  $\Delta$ ,  $T_s$ , d,  $X_{ram}$  and  $M_e$ ) based on the current state and the command vector. Additionally the command noise is added to the command vector within this modules, although this could have alternatively been done externally.

Figure 3.1: Physical Model Flow Chart

For the FPGA implementation it is interesting to decompose the physical model of the ESR plant into three parts: inversion, dynamics and integration. The reason for this separation from the rest of the physical equations is that it takes many more steps to compute the inversion and during this time, some of the computations can be done in parallel so that once the inversion is complete the rest of the computations can be completed in a fully-pipeline fashion, with a result at each cycle. In order to keep the pipeline full, the number of copies of parallel inverters need to be equal to the number of step it take to complete an inversion. For the sake of comprehension, we will call the physical model without the inversion the dynamics model, for lack of a better term.

Figure 3.2: Full Physical Model Flow Chart

The resulting dynamics model can be found in figure 3.3.

Figure 3.3: Physical Model Flow Chart - Inversion Excluded

## 3.2.4.2 Measurement Model (H)

The measurement model is rather straightforward compared to the physical model. The only non-native operation is an exponential used for the computation of the ESR's resistance. The observation vector is computed from a state. Noise is added to the measurement in the model.

Figure 3.4: Measurement Model Flow Chart

## 3.2.4.3 Whole Simulator

The whole simulator includes the physical and measurement models. Figure 3.5 shows how they are connected.

Figure 3.5: Whole System Flow Chart

## 3.2.5 Customized Operators

As discussed in the previous section, division and exponentiation are not natively supported by the Virtex 5 FPGA. Therefore, they have to be designed. This is a point on which performance may be gained (or lost if poorly executed).

#### 3.2.5.1 Division

According to [9] they are two categories of algorithms for division : recurrence and convergence. Recurrence approaches are slow as they produce one bit of the quotient per iteration, whereas convergence divisions produces several bits of the final quotient at each iteration through approximation, but require fast multipliers.

In this study, the recurrence approach has been chosen as a first approach, especially since only 1 division is present in the algorithm after factorizing. Were this approach too slow for other models, the convergence approach may be further studied and implemented.

The base version of the algorithm is the paper and pencil method that is common to most people. We are looking for  $Q = \frac{N}{D}$  through the use of the recurrence equation [9] :

$$P_{k+1} = rP_k - q_{n-k-1}D \text{ for } k = 1, 2, \dots, -1$$

(3.1)

where:

- ${\cal P}_k$  is the partial remainder after the selection of the  $k{\rm th}$  quotient digit

- $P_0 = N$  (subject to the constraint  $|P_0| < |D|$ )

r is the radix

$q_{n-k-1}$  is the kth quotient to the right of the binary point

D is the divisor.

During this research it was observed that a mix between the restoring and non restoring method could be implemented on an FPGA by making use of parallelization. At each step, the partial remainder is shifted to the left and the *n*-*k*th bit of the Numerator is concatenated to it. If the partial remainder is positive, then the Numerator is effectively removed from the partial remainder and the  $(n - k)^{th}$  bit of Q is set to one. If not, the partial remainder stays unchanged and the  $(n - k)^{th}$  bit of Q is set to 0.

```

package DivFix;

import FixedPoint :: * ;

interface Div_IFC#(numeric type ai, numeric type af,

numeric type bi, numeric type bf,

numeric type ci, numeric type cf);

method Action

start (

FixedPoint#(ai, af) a, FixedPoint#(bi, bf) b)

method FixedPoint\#(ci, cf)

result();

acknowledge();

method Action

endinterface

module mkDivFix(Div_IFC#(ai, af, bi, bf, ci, cf))

provisos (

Arith#(FixedPoint :: FixedPoint#(ci, cf)),

Bitwise#(FixedPoint :: FixedPoint#(ci, cf)),

\label{eq:Add} \ensuremath{\texttt{Add}}\ensuremath{\#}(\ensuremath{\texttt{TAdd}}\ensuremath{\#}(\ensuremath{\texttt{bi}}\ , \ \ensuremath{\texttt{bf}}\ ) \ , \ \ensuremath{\texttt{1}}\ \ensuremath{\texttt{TAdd}}\ensuremath{\#}(\ensuremath{\texttt{bi}}\ , \ \ensuremath{\texttt{bf}}\ ) \ , \ \ensuremath{\texttt{bf}}\ \ensuremath{\texttt{bi}}\ \ensuremath{\bi}\ \ensuremath{\texttt{bi}}\ \ensuremath{\bi}\ \ens

1))

\operatorname{Add}\#(1, a_{-}, \operatorname{TAdd}\#(\operatorname{ai}, \operatorname{af})),

```

```

\operatorname{Add} \#(1, b_{-}, \operatorname{TAdd} \#(bi, bf)),

Bits#(FixedPoint::FixedPoint#(ai, af), TAdd#(ai,

af))

);

Integer maxnum=valueOf(ai)+valueOf(af)+valueOf(

cf);

Integer maxa=valueOf(ai)+valueOf(af);

Integer maxb=valueOf(bi)+valueOf(bf);

Integer maxc=valueOf(ci)+valueOf(cf);

Integer shift=valueOf(af)-valueOf(bf);

Reg#(Bool)

<- \text{mkReg}(\text{True});

available

\operatorname{Reg}\#(\operatorname{Bit}\#(\operatorname{TAdd}\#(\operatorname{ai},\operatorname{af})))

<- \operatorname{mkReg}(0);

//Numerator

n

\operatorname{Reg}_{\#}(\operatorname{Bit}_{\#}(\operatorname{TAdd}_{\#}(\operatorname{TAdd}_{\#}(\operatorname{bi}, \operatorname{bf}), 1)))

<- \operatorname{mkReg}(1);

//Divisor

d

\operatorname{Reg}\#(\operatorname{Bit}\#(\operatorname{TAdd}\#(\operatorname{TAdd}\#(\operatorname{bi}, \operatorname{bf}), 1)))

<- \operatorname{mkReg}(0);

//remainder

r

\operatorname{Reg} #(\operatorname{Bit} #(\operatorname{TAdd} #(\operatorname{TAdd} #(\operatorname{ai}, \operatorname{bf}), \operatorname{cf})))

<- \operatorname{mkReg}(0);

q

Reg#(UInt#(TLog#(TAdd#(TAdd#(ai, af), ci))))

i

<- \text{mkReg}(0); //\text{cycle counter}

\operatorname{Reg}\#(\operatorname{Bit}\#(1))

<- \operatorname{mkReg}(?);

signs

rule cycle (i<fromInteger(maxnum) && (available

=False));

if(r \ge d)

action

q [from Integer(maxnum)-i] <=1;

if(i < fromInteger(maxa))r <= \{(r-d)\}

[\text{fromInteger}(\text{maxb}) - 2:0], n[

fromInteger (\max)-1-i;

else r <= (r-d) << 1;

```

```

endaction

else

action

q [from Integer (maxnum) - i] <= 0;

if (i<fromInteger (maxa))r<={r[

fromInteger (maxb) -2:0],n[

fromInteger (\max)-1-i };

else r \ll r \ll 1;

endaction

i \le i+1;

endrule: cycle

method Action start (FixedPoint\#(ai, af) a,

FixedPoint#(bi, bf) b) if (available);

n \ll pack(abs(a));

d <= signExtend(pack(abs(b)));

r \leq zeroExtend(n[fromInteger(maxa)-1]);

i <= 1;

q <= 0;

\operatorname{signs} \leq = (\operatorname{msb}(\operatorname{pack}(a)))^{(\operatorname{msb}(\operatorname{pack}(b)));

available \leq False;

endmethod

method FixedPoint\#(ci, cf) result() if (i >=

fromInteger(maxnum) );

FixedPoint#(ci, cf) res;

if ( shift < 0 )

res=(unpack(q[fromInteger(maxc)

-1:0])<<-shift);

else

res=(unpack(q[fromInteger(maxc)

-1:0)>>shift);

if(signs == 1)

return -res;

else

```

45

```

return res;

endmethod

method Action acknowledge() if ((i >=

fromInteger(maxnum)) && !available);

available <= True;

endmethod

endmodule : mkDivFix

endpackage : DivFix

```

The division delay using this method is equal to the number of bits of the numerator plus the number of bits in the fractional part of the result.

In the final version of the FPGA implementation, the division module has actually not been used although originally motivated by requirements of the ESR's physical. Instead, the code was reused to develop and inversion function, which is similar to a division, only with a numerator always equal to one. In the end, this division module is now available for applications that may require it.

#### 3.2.5.2 Inversion

The inversion module was created based on the division module. The motivation behind the creation and the use of this module is the fact that the inversion is a division that has a numerator equal to one. As a consequence, the number of steps required to complete an inversion is less than that of a division given the same data types. Because the fixed part of the numerator is just equal to one, there is no need to cycle over all the bit of the integer part, hence the sparing of a number of steps equal to the number of bits in the integer part of the fixed point data type. Therefore there are 2f steps instead of 2f + i, since only the fractional part has to be covered.

Naturally, divisions can be decomposed into an inversion and a multiplication:

$$\frac{N}{D} = N \times \frac{1}{D} \tag{3.2}$$

where N is the numerator and D is the denominator.

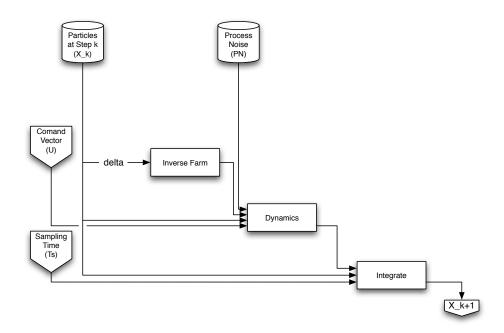

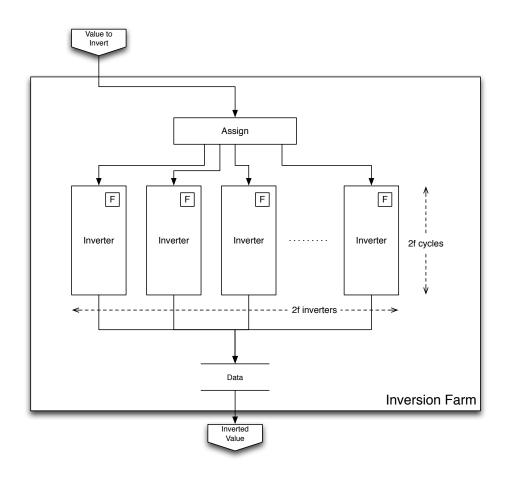

#### 3.2.5.3 Inversion Farm

When an inversion operation is requested, an inversion module takes 2f cycles to complete the inversion. If only one inversion module is present in the FPGA, a new inversion can only start once the previous inversion has been completed, that is after 2f cycles. This would create a serious bottleneck in the flow. Multiple instances of these modules can be created and grouped into a farm. This allows for handling several inversions (or other operations) at the same time. If there are as many modules in the farm as it takes cycles to complete one operation, the farm can handle a new request at each cycle. This technique was used in the FPGA implementation to achieve full pipelining. The inversion farm is illustrated in figure 3.6.

The following is a description of the farm and its behavior:

- The farm contains 2f inverters.

- Initially, all the inverters are available.

- When an inversion is requested, the inversion is assigned to the next available inverter.

- A flag associated with the inverter is set as busy.

- At the end of the inversion, the inversion result is queued and data in the inverter is released and the inverters flag is set to available.

Since the inversion algorithm used has a constant number of steps, the order of the results in the queue will naturally be in the same order as the request order. There is no need for order management. If fast division was used, order management will be required, since the number of cycles required to complete the division may not be constant.

Figure 3.6: Inversion Farm Module

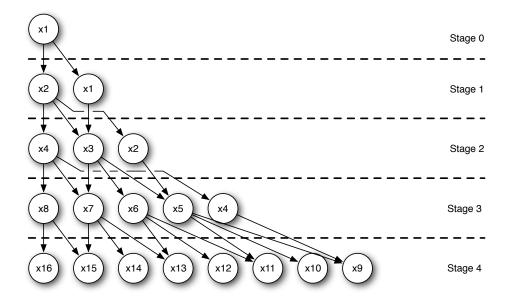

## 3.2.5.4 Exponential

A detailed architecture with performance results can be found in [4].

Two options have been identified concerning the exponential function. The first one is to store values that the exponential function would return in memory. The other option is to use the Taylor series expansion, which was selected.

$$e^{x} = \sum_{n=0}^{\inf} \frac{x^{n}}{n!} = 1 + x + \frac{x^{2}}{2!} + \frac{x^{3}}{3!} + \frac{x^{4}}{4!} + \dots$$

(3.3)

To compute the exponential with sufficient precision for the ESR estimator, the order should be 15 given the range of the input [-2.6686; 2.1834]. Whereas, the factorial numbers can be set as constants, the powers need to be computed. In order to do so in a pipelined fashion, the powers of x can be computed through successive multiplications. The computation of all the powers of x to the 16<sup>th</sup> power can be done in 4 stages as in figure (3.7).

To complete the exponential computation, the powers of x are multiplied by the inverse of the factorials at each stage. These inverse factorials are pre-computed during compile-time and stored as constants. Multiplying by the stored inverses avoids long divisions, and can be done in one cycle.

Figure 3.7: Computing the powers of x for the Taylor series expansion of the exponential function

#### 3.2.6 FPGA Implementation Toolchain

In the course of designing and implementing the FPGA based design, only two software suites are required. The first suite is Bluespec System Verilog which includes the tools for defining and testing the functional architecture of the design and the tools to generate hardware description language files, namely Verilog files. The second is Xilinx ISE which can synthesis and place and route the design for a specific FPGA target.

Bluespec include a compiler, bsc. BSC can generate simulations files that are executable within Linux and can display the value of registers or variables during runtime of the simulations, which behave in the same fashion as the printf() function is C. The same compiler can be used to generate Verilog files. The compiler provides the option of generating Verilog 95 compliant code, which excludes the display functions used for the simulation.

Xilinx ISE provides the rest of the tool chain to produce netlists and FPGA programation files. The first step consists in creating a project. The project has to be configured with the FPGA device number and the desired/required speed grade as well as design goal. The Verilog file that contains the top module is then imported into the project as well as optional additional Verilog files containing sub modules and the Bluespec provided libraries used in the design. From there, the design needs to be synthesized, placed and routed with optional constraint files.

#### 3.2.6.1 Software Versions

- Bluespec System Verilog v.2008.11.C

- Xilinx ISE v.10.1

# Chapter 4

# **Implementation Results and Analysis**

## 4.1 Implementation Results

In this section the speeds, in terms of particles per second, of the CPU and the FPGA implementation are compared. For the CPU implementation, the results are obtained by timing the computation of a given number of particles. For the FPGA implementation, the speed results are obtained by dividing the maximum FPGA frequency given by the design tools after place/route by the number of cycles that the computation of a given number of particles computation would require, obtained through functional simulation.

#### 4.1.1 CPU Results

For the given models, the approximate average speed of computation on the given CPU-based configuration was 2.67M particles per second. Since the CPU frequency is 2.6GHz, it can be deduced that each particle computation requires around 1000 cycles.

## 4.1.2 FPGA Results

The FPGA that was used to evaluate the performance of the implementation is XC5VSX240T Virtex 5 from Xilinx. The XC5VSX240T has the following specifications found in table 4.1:

| XC5VTXT240T                         |             |  |

|-------------------------------------|-------------|--|

| Resource                            | Amount      |  |

| Slices                              | 37,440      |  |

| Logic Cells                         | $239,\!616$ |  |

| CLB Flip-Flops                      | 149,760     |  |

| Maximum Distributed RAM (Kbits)     | 4,200       |  |

| Block RAM/FIFO w/ECC (36Kbits each) | 516         |  |

| Total Block RAM (Kbits)             | $18,\!576$  |  |

| DSP48E Slices                       | 1,056       |  |

#### Table 4.1: FPGA Specifications

Under the FPGA design tool, Xilinx ISE 10.1, the FPGA has been configured with the settings found in table 4.2.

| Project Configuration |             |  |

|-----------------------|-------------|--|

| Parameter             | Value       |  |

| Family                | Virtex 5    |  |

| Device                | XC5VTXT240T |  |

| Package               | FF1738      |  |

| Speed                 | -2          |  |

| Design Goal           | Balanced    |  |

Table 4.2: Xilinx ISE Project Configuration

The utilization results after synthesis and place and route are found in table 4.3.

| FPGA Resource Utilization              |       |           |             |  |

|----------------------------------------|-------|-----------|-------------|--|

| Slice Logic Utilization                | Used  | Available | Utilization |  |

| Number of Slice Registers              | 3,144 | 149,760   | 2%          |  |

| Number used as Flip Flops              | 3,144 |           |             |  |

| Number of Slice LUTs                   | 8,223 | 149,760   | 5%          |  |

| Number used as logic                   | 7,508 | 149,760   | 5%          |  |

| Number used as Memory                  | 689   | 67,200    | 1%          |  |

| Number used as Dual Port RAM           | 689   |           |             |  |

| Number used as exclusive route-thru    | 26    |           |             |  |

| Number of route-thrus                  | 316   | 299,520   | 1%          |  |

| Slice Logic Distribution               | Used  | Available | Utilization |  |

| Number of occupied Slices              | 2,626 | 37,440    | 7%          |  |

| Number of LUT Flip Flop pairs used     | 8,591 |           |             |  |

| Number with an unused Flip Flop        | 5,447 | 8,591     | 63%         |  |

| Number with an unused LUT              | 368   | 8,591     | 4%          |  |

| Number of fully used LUT-FF pairs      | 2,776 | 8,591     | 32%         |  |

| Number of unique control sets          | 176   |           |             |  |

| Number of slice register sites lost to | 282   | 149,760   | 1%          |  |

| control set restrictions               |       |           |             |  |

| Other                                  | Used  | Available | Utilization |  |

| Number of DSP48Es                      | 473   | 1,056     | 44%         |  |

Table 4.3: FPGA Resource Utilization

Minimum period achieved with speed grade -2: 24.529ns (Maximum Frequency: 40.767MHz.)

The maximum speed is achieved with a full pipeline, that is when a particle is produced at each clock cycle. Since the maximum frequency obtained under the given configuration is 40.767MHz, the achieved speed was  $40.767Mparticle.s^{-1}$ .

The 44% utilization of the DSP48Es (which provide for the fixed point multiplications) is the limiting factor as is it the resource that is the most utilized. The FPGA still has the potential to hold a second copy of the modules, which would double the simulation speed while using 88% of the DSP48E resources. Unfortunately, ISE runs out of memory while trying to place and route such a design, probably due to the complexity of finding a solution with so few resources left on the FPGA.

## 4.2 Analysis

#### 4.2.1 Speed and Number of Devices

Based on these results and the knowledge of the architectures it is possible to define models to figure out the speed of particle computation and the number of device required to achieved a certain performance level. This performance level is defined by a number of particles, P to compute within a certain deadline  $t_D$ .

#### 4.2.1.1 CPU Speed

For the purpose of real-time computing, that is to guaranty that all the tasks of the system are computed before a certain deadline (which is important when controlling a physical process), it is best to assume that the CPU will compute the code in a worst case scenario. In that scenario, the code doesn't benefit from CPU optimizations such as branch prediction and is executed in a constant worst time that is proportional to the CPU's frequency. A CPU may contain a set of cores, which are capable of computing one operation at a time. One operation may take several clock cycles depending on the architecture. The speed of computation therefore depends on the number of CPUs, the number of cores per CPU, the number of cycle to compute one particle and the CPU frequency with the following relationship:

$$R_{CPU} = N_{CPU} \times N_{cores} \times \frac{1}{N_{cycles}} \times F_{CPU}$$

(4.1)

where:

- $R_{CPU}$  is the particle computation rate on a CPU-based computation system;

- $N_{CPU}$  is the number of CPUs in the computation system;

- $N_{cores}$  is the number of cores per CPU;

- $N_{cycles}$  is the number of cycles per particle computation; and

•  $F_{CPU}$  is the frequency of the CPUs (assuming that the CPUs each run at the same frequency).

#### 4.2.1.2 Number of CPUs Required for a Given Performance Level

As mentioned in the introduction, there is a relationship between the number of particles, the required deadline to compute that number of particles and the minimum number of devices required to achieve this performance. In the case of CPUs this relationship is simple since the computing speed is independent from the number of particles. From the rate equation (4.1), the following device requirement equation is inferred:

$$N_{CPU} \ge \left\lceil \frac{P}{N_{cores} \times R_{CPU} \times t_d} \right\rceil$$

(4.2)

#### 4.2.1.3 FPGA Speed

Since the FPGA implementation uses pipelining, the FPGA speed depends both on the number of particles per FPGA, which determines the pipeline's usage, and the FPGA frequency. The speed is the time it takes to compute a number of particles. The number of cycles it takes to compute P particles is P + L, where P is the number of particles and L is the latency, that is the number of cycles it takes for the first particle computation to be output by the system. The speed of computation for one FPGA-based simulator is therefore equal to:

$$R_{simulator} = \frac{P}{L+P} \times F_{FPGA} \tag{4.3}$$

where:

- $R_{simulator}$  is the particles computation rate for one FPGA-based simulator in *particles*. $s^{-1}$ ;

- *P* is the number of particles;

- L is the latency in cycles; and

- $F_{FPGA}$  is the FPGA frequency in  $cycles.s^{-1}$ .

Further, an FPGA-based system can be comprised of multiple FPGA devices, each containing multiple simulators operating in parallel. This results in the following model:

$$R_{FPGA} = N_{FPGA} \times N_{simulators} \times \frac{P}{P+L} \times F_{FPGA}$$

(4.4)

where:

- $R_{FPGA}$  is the particles computation rate for one FPGA-based simulator in *particles*. $s^{-1}$ ;

- $N_{FPGA}$  is the number of FPGAs in the FPGA based system;

- $N_{simulators}$  is the number of simulators per FPGA;

- *P* is the number of particles;

- L is the latency in cycles; and

- $F_{FPGA}$  is the FPGA frequency in  $cycles.s^{-1}$ .

#### 4.2.1.4 Number of FPGAs Required for a Given Performance Level

As in the CPU case, a minimum number of FPGAs can be determined. Posing that for each FPGA device  $\left\lceil \frac{P}{N_{FPGA}} \right\rceil$  is the number of particles per device, we have:

$$\frac{L + \left\lceil \frac{P}{N_{FPGA}} \right\rceil}{F_{FPGA}} \le t_d \tag{4.5}$$

$$\implies L + \left\lceil \frac{\frac{P}{N_{FPGA}}}{N_{simulators}} \right\rceil \le t_d F \tag{4.6}$$

$$\implies \left\lceil \frac{P}{N_{simulators} N_{FPGA}} \right\rceil \le t_d F - L \tag{4.7}$$

$$\implies N_{FPGA} \ge \left\lceil \left\lceil \frac{P}{N_{simulators}} \right\rceil \frac{1}{t_d F - L} \right\rceil \tag{4.8}$$

#### 4.2.2 FPGA v. CPU performance outlook

Using the models presented in the previous sections, the performance of CPUs and FPGAs can be forecasted and compared. Currently, we were able to have only one simulator per FPGA and we only used one CPU core on one CPU. In the near future, we can hope to increase the FPGA frequency and hold multiple simulators per FPGA. On the CPU side, the use of 4 cores is currently feasible. To get an idea of what lies ahead, we can plot the performance levels given by the models.

#### 4.2.2.1 Speeds

The following plots show the speed performance for the CPU and FPGA implementations. The speed is measured in *particles.s*<sup>-1</sup>. For CPUs, the

speed remains constant for a given number of CPUs. The reason for this is that the CPU implementation is serial and therefore its speed is independent from the number of particles. In contrast, the FPGA computation speed depends on the number of particles. The speed increases as there are more particles to fill the pipeline. The maximum theoretical speed for one FPGA configuration is equal to the FPGA's clock frequency since the pipelining has been done in such a way that one particle computation result is produced on each cycle after the first result is obtained. The maximum speed is achieved when the input to output latency (i.e. the number of clock cycles it takes for the result to be obtained once the input has been applied) is negligible compared to the number of particles. In this implementation, this appears to happen around 15000 particles. From the performance plot it can be seen that the FPGA based simulations are substantially faster on FPGAs if the number of particles is greater than 10 in all cases. Since many applications are susceptible to require many more particles, FPGAs appear to be the solution of choice for future applications in terms of speed.

Figure 4.1: Particle Computation Rates for 4 CPU Cores and 1 FPGA based simulator

Figure 4.2: Particle Computation Rates for 4 CPU Cores and 2 FPGA based simulator

#### 4.2.2.2 Number of Devices

The following plots show the minimum numbers of CPUs or FPGAs that are or would be necessary to compute a certain number of particles under a given deadline. To better view the influence of deadline and particle the required minimum number of devices has been plotted in 3D. In these 3D plots it can be seen that the area where two CPUs are required is far away from the area of operation of the ESR estimator. However, for other applications such as the Gas Metal Arc Welding process which is a much quicker process, there may be a need for computing more particles under a shorter deadline. If this is the case, then it appears again that FPGAs will be the device of choice. The graphs show that many more CPUs will be needed as the number of particles increases and the deadline to compute this number of particles shortens compared to the number of FPGAs that will be necessary.

Minimum Number of Devices Required

Figure 4.3: Number of Devices Required; 4 Cores per CPU v. 1 Simulator per FPGA

Minimum Number of Devices Required

Figure 4.4: Number of Devices Required; 4 Cores per CPU v. 2 Simulator per FPGA

#### 4.2.2.3**Performance Analysis**

The major speed advantage that the FPGA implementation features is the use of pipelining. Pipelining the particle computation allows for intense parallelization, which leads to a substantial speed increase. In terms of speed and number of devices required, FPGAs provide the best performance at this point in time as well as in the years to come. Whereas the CPU implementation can only be improve through the use of multiple cores (the current working implementation uses only one single core), the FPGA implementation can still receive more enhancements. In the current implementation, many additions and multiplications are grouped together. Since the FPGA still has available resources, these steps of the pipeline can be cut into smaller substeps in which only one operation is performed. This will lead to two improvements: a shorter maximum delay (faster clock) and more parallelization. Currently, the FPGA implementation is limited by the number of DSP48 blocks used, which is 44%. The design could be modified to use fewer multipliers by adding some steps for instance.

# Chapter 5

# **Conclusion and Future Work**