Copyright by Bin Zhang 2009

# The Dissertation Committee for Bin Zhang certifies that this is the approved version of the following dissertation:

# IC Design for Reliability

**Committee:**

Michael Orshansky, Supervisor

Ari Arapostathis

Todd Arbogast

Jack Lee

David Pan

Nur Touba

# IC Design for Reliability

by

Bin Zhang, B.S.; M.S.

### Dissertation

Presented to the Faculty of the Graduate School of The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

## **Doctor of Philosophy**

The University of Texas at Austin May, 2009

# Dedication

To my family

### Acknowledgements

I am deeply grateful to my advisor, Prof. Michael Orshansky, for his guidance and support throughout these years. Prof. Orshansky is the one who introduced me into the world of CAD/VLSI. He has guided me, with great patience, through every step of conducting research, from formulating the problem to revising the research paper. This dissertation could not be in its current form without his assistance and encouragement. Thank you, Michael!

I would like to express my gratitude to the members of my dissertation committee, each of whom has given me guidance and important feedback. They are Prof. Ari Arapostathis, Prof. Todd Arbogast, Prof. Jack Lee, Prof. David Pan, Prof. Nur Touba. Their suggestions have made this dissertation better. Prof. Arapostathis has helped deriving the SRAM dynamic noise margin. Prof. Arbogast has spent a great amount of time with me on the differential equation solver for NBTI. Prof. Nur Touba has given his valuable comments on delay testing. Besides, I benefited from Prof. David Pan's optimization class and Prof. Nur Touba's dependable computing class. Prof. Jack Lee has made me aware of PBTI, an important failure mechanism. I am indebted to all of them.

There are several fellow students in the Robust IC Design Laboratory whom I would like to thank for their help. They are Wei-shen Wang, Murari Mani, Ashish Singh, Shayak Banerjee, and Ku He. I have benefited greatly from my discussions with them. I

would like to especially thank Wei-shen Wang for his great help with the many difficulties I have encountered in my research.

Finally, I am grateful to my family for their love and support. I am proud of all of them: my parents Dengyin Zhang and Youzhen Wen, sister Min Zhang, brother-in-law Yong Huang, and niece Yeshuang Huang.

## **IC Design for Reliability**

Publication No.\_\_\_\_\_

Bin Zhang, Ph.D. The University of Texas at Austin, 2009

#### Supervisor: Michael Orshansky

As the feature size of integrated circuits goes down to the nanometer scale, transient and permanent reliability issues are becoming a significant concern for circuit designers. Traditionally, the reliability issues were mostly handled at the device level as a device engineering problem. However, the increasing severity of reliability challenges and higher error rates due to transient upsets favor higher-level design for reliability (DFR). In this work, we develop several methods for DFR at the circuit level.

A major source of transient errors is the single event upset (SEU). SEUs are caused by high-energy particles present in the cosmic rays or emitted by radioactive contaminants in the chip packaging materials. When these particles hit a N+/P+ depletion region of an MOS transistor, they may generate a temporary logic fault. Depending on where the MOS transistor is located and what state the circuit is at, an SEU may result in a circuit-level error. We analyze SEUs both in combinational logic and memories (SRAM). For combinational logic circuit, we propose FASER, a Fast Analysis tool of Soft ERror susceptibility for cell-based designs. The efficiency of FASER is achieved through its static and vector-less nature. In order to evaluate the impact of SEU on

SRAM, a theory for estimating dynamic noise margins is developed analytically. The results allow predicting the transient error susceptibility of an SRAM cell using a closed-form expression.

Among the many permanent failure mechanisms that include time-dependent oxide breakdown (TDDB), electro-migration (EM), hot carrier effect (HCE), and negative bias temperature instability (NBTI), NBTI has recently become important. Therefore, the main focus of our work is NBTI. NBTI occurs when the gate of PMOS is negatively biased. The voltage stress across the gate generates interface traps, which degrade the threshold voltage of PMOS. The degraded PMOS may eventually fail to meet timing requirement and cause functional errors. NBTI becomes severe at elevated temperatures. In this dissertation, we propose a NBTI degradation model that takes into account the temperature variation on the chip and gives the accurate estimation of the degraded threshold voltage.

In order to account for the degradation of devices, traditional design methods add guard-bands to ensure that the circuit will function properly during its lifetime. However, the worst-case based guard-bands lead to significant penalty in performance. In this dissertation, we propose an effective macromodel-based reliability tracking and management framework, based on a hybrid network of on-chip sensors, consisting of temperature sensors and ring oscillators. The model is concerned specifically with NBTIinduced transistor aging. The key feature of our work, in contrast to the traditional tracking techniques that rely solely on direct measurement of the increase of threshold voltage or circuit delay, is an explicit macromodel which maps operating temperature to circuit degradation (the increase of circuit delay). The macromodel allows for costeffective tracking of reliability using temperature sensors and is also essential for enabling the control loop of the reliability management system. The developed methods improve the over-conservatism of the device-level, worstcase reliability estimation techniques. As the severity of reliability challenges continue to grow with technology scaling, it will become more important for circuit designers/CAD tools to be equipped with the developed methods.

# **Table of Contents**

| List of Tal | bles                                                         | xii   |

|-------------|--------------------------------------------------------------|-------|

| List of Fig | ures                                                         | xiii  |

| Chapter 1:  | Introduction                                                 | 1     |

| 1.1         | Physical Mechanisms of Transient and Permanent Faults        | 2     |

|             | 1.1.1 Transient faults                                       | 2     |

|             | 1.1.2 Permanent faults                                       | 3     |

| 1.2         | Analysis of Soft Error Susceptibility for Cell-based Designs | 4     |

| 1.2         | Analytical Modeling of SRAM dynamic Stability                | 7     |

| 1.4         | NBTI under Dynamic Temperature Variation                     | 10    |

| 1.5         | Online Circuit Reliability Monitoring                        | 13    |

| 1.6         | Dissertation Organization                                    | 14    |

| Chapter 2:  | FASER: Fast Analysis of Soft Error Susceptibility for Cell-E | Based |

| Desi        | gns                                                          | 15    |

| 2.1         | Cell Library Characterization                                | 16    |

| 2.2         | Static Analysis of Fault Events Propagation                  | 19    |

| 2.3         | Algorithm Flow and Latching Probability Computation          | 22    |

| 2.4         | Circuit Partitioning for Speed-Up                            | 24    |

| 2.5         | Experimental Results                                         |       |

| 2.6         | Summary                                                      |       |

| Chapter 3:  | Analytical Modeling of SRAM Dynamic Stability                |       |

| 3.1         | System Modeling Setup                                        |       |

| 3.2         | Dynamic State Space Analysis                                 |       |

| 3.3         | Transient Behavior of SRAM under Noise                       |       |

| 3.4         | Experimental Results                                         | 45    |

| 3.5         | Summary                                                      | 49    |

| Chap         | ter 4: | Modeling of NBTI-Induced PMOS Degradation under Arbitrary |    |

|--------------|--------|-----------------------------------------------------------|----|

|              | Dyna   | mic Temperature Variation                                 | 51 |

|              | 4.1    | Model of NBTI under Dynamic Temperature Variation and     |    |

|              |        | Constant Voltage Stress                                   | 52 |

|              | 4.2    | Joint Impact of Temperature Variation and Voltage Signal  |    |

|              |        | Transition                                                | 58 |

|              | 4.3    | Model Validation                                          | 60 |

|              | 4.4    | Summary                                                   | 64 |

|              |        | Appendix                                                  | 65 |

| Chap         | ter 5: | Online Circuit Reliability Monitoring                     | 67 |

|              | 5.1    | Circuit-Level Reliability Macromodel                      | 68 |

|              |        | 5.2.1 Device-level NBTI modeling                          | 68 |

|              |        | 5.2.2 Development of the reliability macromodel           | 70 |

|              | 5.4    | Online Model Calibration                                  | 73 |

|              | 5.5    | Experimental Results                                      | 75 |

|              | 5.6    | Summary                                                   | 79 |

| Chap         | ter 6: | Conclusions                                               | 80 |

| Bibliography |        |                                                           |    |

| Vita         |        |                                                           |    |

# List of Tables

| Table 2.1: Bit Error Rates for ISCAS' 85 benchmark circuits with different |  |  |

|----------------------------------------------------------------------------|--|--|

| partition sizes (Np)28                                                     |  |  |

| Table 2.2: Run-time and the maximum BDD size for the ISCAS' 85             |  |  |

| benchmark circuits                                                         |  |  |

# List of Figures

| Figure 1.1: Soft error analysis ignoring logic masking can              |

|-------------------------------------------------------------------------|

| overestimate soft error rates by up to 25X6                             |

| Figure 1.2: Lifetime of an inverter chain decreases by 2.2 X for        |

| every 10 °C increase in operating temperature due to                    |

| NBTI11                                                                  |

| Figure 1.3: Operating temperature exhibits significant dynamic          |

| variation11                                                             |

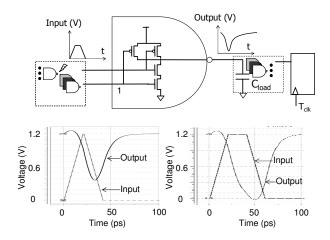

| Figure 2.1: Pulse generation is characterized by circuit simulation     |

| with SPICE17                                                            |

| Figure 2.2: Pulse propagation is characterized by circuit simulation    |

| with SPICE18                                                            |

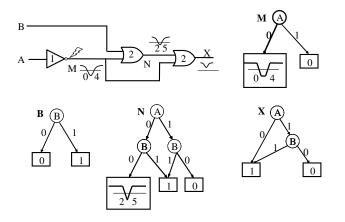

| Figure 2.3: Fault-encoding with event BDD for the biasing               |

| condition "10"19                                                        |

| Figure 2.4: Pulse propagation in a simple circuit. Numbers inside       |

| the gates are their propagation delays20                                |

| Figure 2.5: Pseudo-code of FASER flow24                                 |

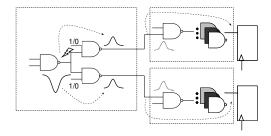

| Figure 2.6: Partitioning circuits for speed-up leads to the loss of     |

| correlations between pulses of different domains25                      |

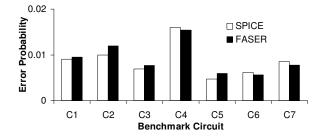

| Figure 2.7: Error probabilities by FASER and SPICE simulation.          |

| The average error is 12%                                                |

| Figure 2.8: Latching error probability due to each gate in circuit C128 |

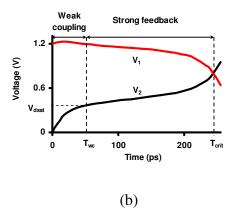

| Figure 3.1: A 6T SRAM cell with a transient current noise being         |

| injected (access transistors not shown)                                 |

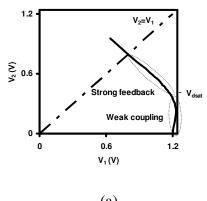

| Figure 3.2: State space and time-domain plots of SRAM nodal             |

| voltages with injected noise                                            |

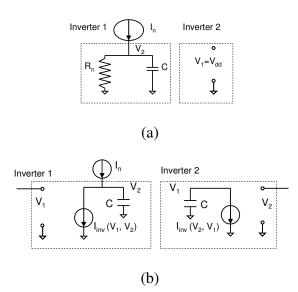

| Figure 3.3: Equi-current drive curves are used to capture I-V           |

| characteristics of an inverter                                          |

| Figure 3.4: To enable analytical solution a linear decoupled                                                                                                                                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOSFET model is used                                                                                                                                                                                                                                                                                                                 |

| Figure 3.5: Stability analysis is done using superposition of mirrored                                                                                                                                                                                                                                                               |

| transfer curves (drive curves)                                                                                                                                                                                                                                                                                                       |

| Figure 3.6: Without noise, the region of attraction for $\vec{V}_1(\vec{V}_0)$ is the                                                                                                                                                                                                                                                |

| entire region above (below) $V_2 = V_1$                                                                                                                                                                                                                                                                                              |

| Figure 3.7: For noise amplitudes higher than the SNM ( $I_n > I_{snm}$ ) only                                                                                                                                                                                                                                                        |

| one equilibrium state exists (above $V_2 = V_1$ )40                                                                                                                                                                                                                                                                                  |

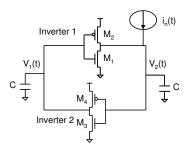

| Figure 3.8: Schematics of the SRAM cell with a transient current                                                                                                                                                                                                                                                                     |

| noise being injected41                                                                                                                                                                                                                                                                                                               |

| Figure 3.9: Using piece-wise linear gate model, SRAM operation is                                                                                                                                                                                                                                                                    |

| divided into regions of (a) weak coupling and (b) strong                                                                                                                                                                                                                                                                             |

| feedback43                                                                                                                                                                                                                                                                                                                           |

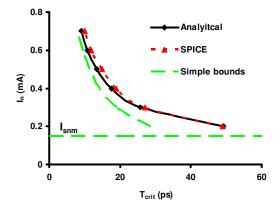

| Figure 3.10: Noise amplitude vs. pulse width: region below is safe45                                                                                                                                                                                                                                                                 |

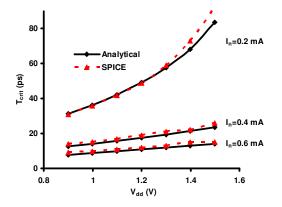

| Figure 3.11: The developed analytical model allows SRAM design                                                                                                                                                                                                                                                                       |

| space exploration, e.g., studying critical pulse $T_{crit}$ at                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                                                                      |

| different $V_{dd}$ and noise amplitudes                                                                                                                                                                                                                                                                                              |

| different $V_{dd}$ and noise amplitudes                                                                                                                                                                                                                                                                                              |

| -                                                                                                                                                                                                                                                                                                                                    |

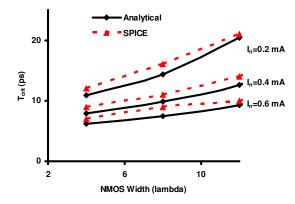

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different                                                                                                                                                                                                                                                                 |

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different transient noise amplitudes. PMOS size is $(W/L)_{pmos}=348$                                                                                                                                                                                                     |

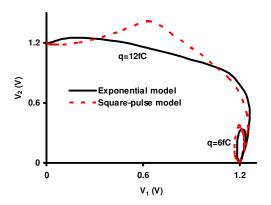

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}$ =348<br>Figure 3.13: A square pulse model approximates here exponential                                                                                                                              |

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}$ =348<br>Figure 3.13: A square pulse model approximates here exponential<br>current source by matching total charge                                                                                   |

| <ul> <li>Figure 3.12: Dependency of <i>T<sub>crit</sub></i> on the NMOS size for different transient noise amplitudes. PMOS size is (<i>W/L</i>)<sub>pmos</sub>=348</li> <li>Figure 3.13: A square pulse model approximates here exponential current source by matching total charge</li></ul>                                       |

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}=348$ Figure 3.13: A square pulse model approximates here exponential<br>current source by matching total charge                                                                                       |

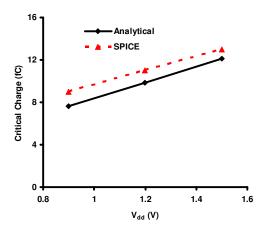

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}=348$ Figure 3.13: A square pulse model approximates here exponential<br>current source by matching total charge49Figure 3.14: Critical charge that will cause a state-flip by a single<br>event upset |

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}=348$ Figure 3.13: A square pulse model approximates here exponential<br>current source by matching total charge49Figure 3.14: Critical charge that will cause a state-flip by a single<br>event upset |

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}$ =348Figure 3.13: A square pulse model approximates here exponential<br>current source by matching total charge                                                                                       |

| Figure 3.12: Dependency of $T_{crit}$ on the NMOS size for different<br>transient noise amplitudes. PMOS size is $(W/L)_{pmos}=348$ Figure 3.13: A square pulse model approximates here exponential<br>current source by matching total charge                                                                                       |

| Figure 5.1: The proportionality function relating degradation models                        |

|---------------------------------------------------------------------------------------------|

| at AC and DC stress conditions69                                                            |

| Figure 5.2: Illustration of a portion of a path with switching                              |

| direction70                                                                                 |

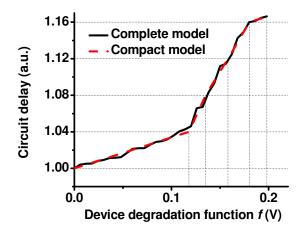

| Figure 5.3: Illustration that the compact model of the circuit delay                        |

| with respect to the device degradation function $f$ can be                                  |

| obtained by piece-wise linearizing the complete model72                                     |

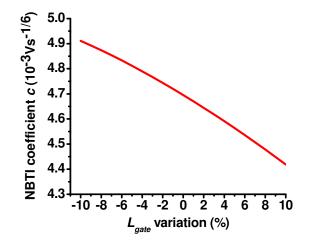

| Figure 5.4: NBTI model parameter $c$ is affected by $L_{gate}$ variation73                  |

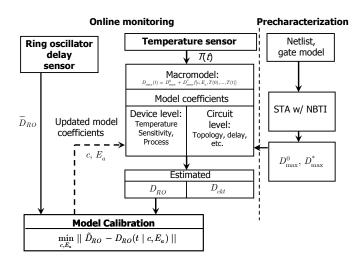

| Figure 5.5: The flowchart of the online reliability monitoring scheme.74                    |

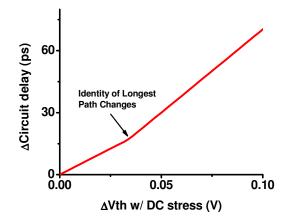

| Figure 5.6: $\Delta$ Circuit delay ( $\Delta D_{max}$ ) as a function of device degradation |

| function <i>f</i> for benchmark circuit c135575                                             |

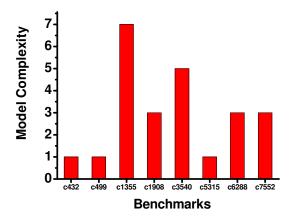

| Figure 5.7: The complexity of the macromodel in terms of the                                |

| number of coefficient sets required for ISCAS'85                                            |

| benchmark circuits76                                                                        |

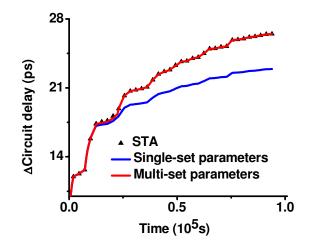

| Figure 5.8: The necessity of using multi-set of macromodel                                  |

| parameters76                                                                                |

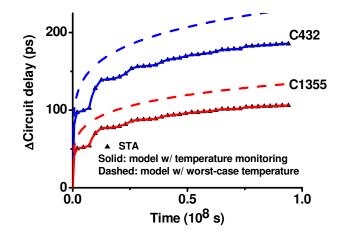

| Figure 5.9: The effect of temperature monitoring on estimation of                           |

| circuit delay degradation77                                                                 |

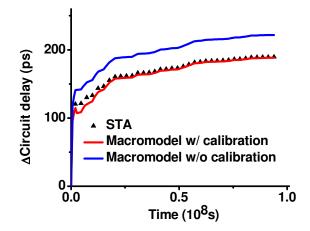

| Figure 5.10: Calibrating model coefficients to correct estimation                           |

| due to process variation77                                                                  |

| Figure 5.11: Model identification through online calibration of                             |

| model coefficients78                                                                        |

### **Chapter 1: Introduction**

The evolution of integrated circuits is driven by the trend of increasing operating frequency and greater functionality on a single chip. This is achieved through downscaling of the feature size of the devices on the chip. Downscaling increases process variation and leakage current, and makes the devices less reliable. In this dissertation, we are specifically interested in the device reliability issues. Downscaling threatens reliability through at least the following two ways. Firstly, smaller charge is stored on a scaled circuit node to represent a logic value which makes the circuit node more susceptible to noise [1]. Secondly, in practical scaling, the supply voltage does not scale as fast as the feature size because of the non-scaling of the subthreshold slope and the resulting leakage current [2], leading to higher device electrical fields which accelerate several failure mechanisms that we discuss below.

The impact of the above threats to reliability is the greater incidence of circuit faults. Based on whether a circuit can recover after the occurrence of a fault, we classify the faults as being transient or permanent. Faults may manifest themselves as functional errors of the circuits. Traditionally, the reliability issues were mostly addressed at the device level [3][4]. However, the increasing error rates due to downscaling favor higher-level deign for reliability (DFR). In this work, we focus on DFR at the circuit level. Specifically, we aim to develop analysis techniques that enable circuit designers to evaluate the error-susceptibility of a circuit and identify the problematic transistors, gates, or circuit blocks.

Error-susceptibility of a circuit is closely related to the physical nature of the faults. In the following, we give a brief introduction to the physics of the transient and permanent faults that we deal with in this work.

#### 1.1 PHYSICAL MECHANISMS OF TRANSIENT AND PERMANENT FAULTS

#### **1.1.1 Transient faults**

There are two types of transient faults. The first is due to on-chip noise, and the second, referred to as single event upset (SEU), is due to extrinsic high-energy particles, such as neutrons and alpha particles, which are present in cosmic rays or emitted by radioactive contaminants in the chip packaging materials [5][6].

On-chip noise sources include power and ground network noise, substrate injection noise and capacitive coupling noise [7][8][9]. They cause the node voltages to deviate from their noise-free values. On-chip noise can be minimized by proper design, such as adding de-coupling capacitors to the power/ground networks, so that the noise level at any point on the chip is kept under control [10].

An SEU occurs when a high-energy particle hits a N+/P+ depletion region of an MOS transistor, temporarily forming a low-impedance path between the depletion region and the ground or power supply. This leads to a current pulse flowing through the low-impedance path, which disrupts charge stored on the node, leading to a fluctuation of the node voltage [5][6][11]. If the deviation of the node voltage exceeds the threshold value, a logic fault occurs and may propagate to the output. Due to the wide energy spectrum of the high-energy particles [1], it is impractical to design circuits that can prevent logic fault due to every SEU at every point on the chip [12]. As a result, it is inevitable that certain transient logic faults will be generated, propagated (in a combinational logic

circuit) and latched by register, causing soft errors. The IBM design goal for soft errors is 1 SDC (silent data corruption) per 1000 years in its Power4 system [13].

#### **1.1.2** Permanent faults

Among important permanent faults are time-dependent oxide breakdown (TDDB), electro-migration (EM), hot carrier effect (HCE), negative bias temperature instability (NBTI). Their common feature is that permanent physical defects are gradually developed throughout the lifetime of the integrated circuit and that the emergence of these faults is accelerated by elevated temperature and voltage.

#### *Time-dependent oxide breakdown (TDDB)*

When the oxide layer of an MOS transistor is stressed by voltage across it, a high electrical field in the order of several MV/cm is created and can generate defects inside the oxide layer. When these defects form a low-impedance path across the oxide layer, an oxide breakdown is said to occur [14]. This breakdown is known as "hard breakdown". However, in recent years, it was found that for ultra-thin oxides, less than 1 out of 1015 oxide breakdowns is "hard", i.e., capable of destroying the transistor and even the entire chip, while the rest of the oxide breakdowns are "soft". Soft breakdowns lead to the increase of the leakage current through the oxide layer [15]. If an integrated circuit is fault-tolerant to at least two soft breakdowns, the lifetime of the circuit can be about 1000 times that predicted by the traditional way [16]. Therefore, it is now suspected that TDDB is not a fundamental obstacle for continued feature size scaling [16].

#### *Electro-migration (EM)*

Electro-migration refers to the mass transport of metal atoms in the interconnects. Electrical current flowing through the interconnect involves the collective motion of electrons. The movement of the electrons exerts force on the conductor metal atoms, causing them to be moved (depleted) from their original sites. As the sites of atom depletion pile up, the resistance of interconnect increases and may eventually result in an open circuit [17][18]. However, if the current can flow in both directions, the depleted sites can be partially re-filled with atoms when the current flows reversely [18].

#### Hot carrier effect (HCE)

When the drain-to-source voltage of an MOS transistor is biased in the saturation mode, the high electrical field near the drain accelerates the carriers (electrons or holes) in the channel, driving them to become energetic or "hot". The hot carrier effects can overcome the potential barrier at the Si-SiO<sub>2</sub> interface and penetrate into the oxide, generating localized traps near the drain, which degrade the current-voltage characteristics of the transistor. HCE only occurs when there is current flowing through the channel, which is only possible when the transistor is switching [19].

#### Negative bias temperature instability (NBTI)

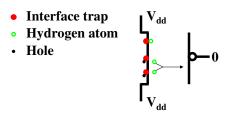

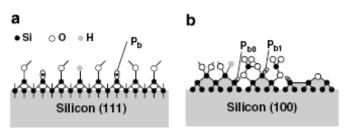

NBTI occurs only in PMOS transistors. When the gate of a PMOS transistor is under negative bias, holes are accumulated in the channel, which breaks the Si-H bonds at the Si-SiO<sub>2</sub> interface and generate interface traps. The accumulation of interface traps leads to increased threshold voltage for the PMOS transistor [53]. Removal of the voltage stress can partially anneal the interface traps, but can never make the PMOS return to its "fresh" state [20].

Our research focuses on transient faults due to SEU and permanent faults due to NBTI. However, some techniques we have developed are also extendable to faults due to other failure mechanisms.

#### 1.2 ANALYSIS OF SOFT ERROR SUSCEPTIBILITY FOR CELL-BASED DESIGNS

Reliability of commercial electronics with respect to the single event upsets (SEU) caused by extrinsic radiation is becoming a significant concern. Historically, the most significant impact of SEU was on memory units (latches, flip-flops, registers, and arrays). However, as the transistor feature size scales down, the error rate due to single event upsets in the combinational logic becomes substantial. It is predicted that by 2011, the soft error rate (SER) due to combinational logic may be comparable to that of the memory units [1]. Because of the increasing error rates in combinational circuitry, new tools and analysis methodologies are needed to ensure circuit reliability. System designers, micro-architects, and circuit designers need accurate prediction of error rates in the designed components. Having this capacity is a prerequisite for choosing the proper hardening strategy for the design.

A soft error may occur when a high-energy particle, typically, an alpha particle, or a neutron, hits the diffusion regions of an MOS transistor and produces charge that leads to a faulty transition. The pulse will cause an error only if it successfully propagates to the latching element and is latched at the clock arrival (sampling) time. There are several mechanisms that reduce the overall likelihood of the pulse producing an erroneous value at the memory units, making the actual SER substantially lower than the raw particle strike rate. In the literature [1][12][21][22][23][24], these mechanisms are referred to as electrical masking, logic masking, and latching-window masking.

In this work, we propose an efficient and accurate approach for SER analysis of cell-based designs. The efficiency is achieved by resorting to symbolic representation of the error pulses using binary decision diagrams (BDD). The accuracy is guaranteed by relying on the precise description of the non-linear gate transfer characteristics using the SPICE-based precharacterization of the cells in the library. In addition to the electrical properties of the cells, the logic structure of the circuit also has a significant impact on

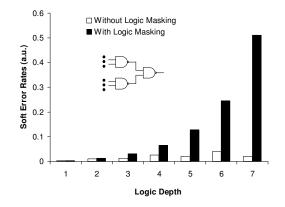

Figure 1.1: Soft error analysis ignoring logic masking can overestimate soft error rates by up to 25X.

the SER. Failing to account for logic masking may over-estimate SER by order of magnitude (25X for a tree-structured circuit with logic depth 7), as illustrated in Figure 1.1. It is evident that as the logic depth increases, logic masking plays a more important role. Accurately yet efficiently accounting for the reduction of error rate likelihood due to these masking mechanisms is the focus of this work.

Prior work in this area has concentrated on modeling and describing the particle interactions at the very low nuclear level [26], performing device-level simulations to predict the electrical response of individual transistors to a particle strike [27], and performing circuit-simulation of a small set of gates to model the propagation of pulses [1]. Several authors have addressed the problem of SER analysis for general combinational logic [12][21][22]. Accurately estimating the SER due to particle strikes on combinational logic gates represents a significant computational challenge. The primary reason is that SER de-ratings due to electrical, logic, and latching-window masking are all input vector dependent. Existing techniques approach this problem by explicitly enumerating all input vectors, or a set of randomly picked input vectors

[12][21][22]. However, the size of the input vector space is exponential in the number of primary inputs, and for circuits with a large number of primary inputs these techniques usually take hours, or even days, to achieve reasonable accuracy [22].

#### 1.2 ANALYTICAL MODELING OF SRAM DYNAMIC STABILITY

Verifying stability of SRAM-based memory arrays is an essential design task. For memory design in nanometer scale technologies, the traditionally-used static stability analysis may no longer be sufficient. The overriding reason is that the powerminimization driven supply voltage scaling dangerously reduces design options. This is especially so when static noise margins (SNM) [38] are used. Checking stability using dynamic noise margins requires complex time-dependent stability analysis but permits a more aggressive flexible design without jeopardizing reliability. Dynamic noise margins (DNM) take into account spectral and time-dependent properties of the specific noise patterns. These include the on-chip noise sources such as power and ground network noise, substrate injection noise, capacitive coupling, as well as the extrinsic transient noise such as those due to single event upsets (SEU) [11][7][8][9]. Single event upsets are becoming especially troublesome for memory arrays (much more than for combinational logic with its natural masking mechanisms) and dynamic stability analysis is essential for predicting bit error rates accurately. An additional factor for the growing importance of DNM analysis is the adoption of SOI devices for SRAM cells because the floating-body effect leads to a dynamic variation of transistor strengths during read and write operations [40].

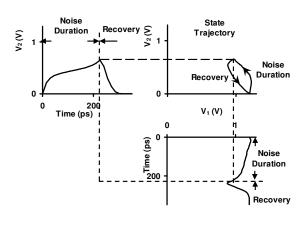

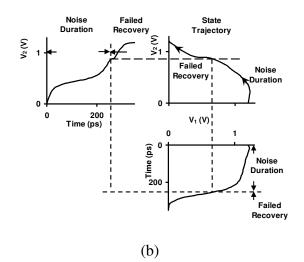

Stability analysis is concerned with identifying the maximum possible unintended violations that will not cause the stored state to be lost. Traditional static stability analysis finds the noise margins by identifying the maximum amplitude of a voltage deviation on an input node that can be tolerated. Static analysis ignores the fact that not all transient

noise affecting a sensitive node of an SRAM cell will cause the state to flip. There is a range of noise patterns that will cause only a temporary disturbance of the internal node voltage. Whether a transient noise signal is benign (will not cause a flip) or malignant (will cause a flip) depends not only on the amplitude of the signal but also on its duration (or pulse width). In addition, the outcome of the temporary disturbance is also determined by the electrical and geometric parameters of the cell. This work demonstrates how nonlinear study can be used to develop an analytical theory of the bi-stable cross-coupled inverter system affected by transient noise.

A well-developed and diverse theory exists for analysis of SRAM cell stability based on the notion of SNM [38]. SNM analysis ignores the transient aspect of noise and posits a constant noise signal is present at a node. Despite the wealth of methods, it has been shown the various criteria are equivalent [39], including coincidence of equilibrium states, the small signal closed-loop gain of the SRAM being unity, the setting of the Jacobian of the Kirchhoff equations of the SRAM to zero. The equivalency extends to the most "famous" criterion that is familiar to many SRAM circuit designers and is based on the graphical method of inscribing the maximum square between normal and mirrored voltage transfer characteristics [39].

While there exists rich theory for static stability analysis of SRAM cells, extending it to dynamic analysis has proven difficult. The importance of transient noise susceptibility of SRAM cells has been of course realized [11]. However, all of the prior works rely on simulation techniques at the device level [41], transistor level [27], or in a mixed mode of device and transistor levels [42]. Simulation techniques search for the minimum strength of a malignant transient noise (for instance, in the form of critical charge deposited by an SEU). Although accurate, the simulation results can only provide limited insight into the problem. A somewhat similar problem is encountered in the

characterization of combinational logic gates' susceptibility to transient errors [31][43][44]. Dynamic response of a gate is obtained by solving the simplified differential equations describing its dynamic behavior. However, because of the nonlinear cross-coupling between the nodal voltages of an SRAM cell, it is difficult to extend this literature to the problem at hand. Thus, a closed-form analytical formulation that reveals the relationship between the minimum strength of a malignant transient noise and the configuration parameters of the SRAM cell is sought. In addition to giving invaluable intuition about SRAM dynamic stability, it can be directly used for reliability, yield and optimization to avoid lengthy iterative SPICE simulations [45].

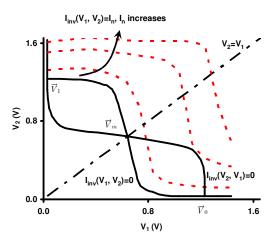

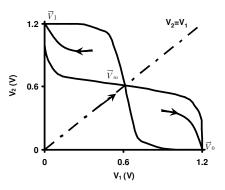

In this work, for the first time, a method for evaluating dynamic noise margins is developed analytically. The results allow predicting the transient error susceptibility of an SRAM cell using a closed-form expression. The key innovation involves using the methods of nonlinear system theory in developing this model. It is shown that when a transient noise of a given magnitude affects a sensitive node of a cell, the bi-stable, feedback-driven nature of the cell determine whether the noise will be suppressed or will evolve to eventually flip state. It is shown that for the flip to take place, the noise needs to exceed specific threshold amplitude, which is shown to be equal to the SNM, and be sustained longer than a minimum critical duration.

The inverters of the cross-coupled pair in an SRAM cell are described as operating in two modes: high gain and low gain, such that in each mode, the driving current of the inverter is a linear function of either the input voltage or the output voltage but not both [46]. This permits decoupling of the input and output voltage dependences. Using a piece-wise linear MOSFET model, rigorous analysis of the coupled nonlinear feedback system is performed. The specific formal and quantitative result is a closedform expression that can be used to predict whether a cell flip will occur for a noise signal with specific characteristics. For a given SRAM cell design, the expression evaluates the critical pulse width for various noise amplitudes.

#### 1.4 NBTI UNDER DYNAMIC TEMPERATURE VARIATION

In the nanometer regime, negative bias temperature instability (NBTI) is one of the dominant factors of transistor aging [50][51]. NBTI manifests itself as a gradual increase in the magnitude of PMOS threshold voltage. Over time, this leads to an increased circuit delay. At the end of the lifetime of the chip, a timing error may occur. The time until such a failure occurs is defined as the circuit lifetime. Industrial practice reveals that NBTI has been significant since the 90nm technology node and will get worse with further scaling [52].

NBTI occurs when the gate of the PMOS is negatively biased (i.e. the gate voltage is 0 *Volt* and the source voltage is  $V_{dd}$ ). The electrical field induced across the gate oxide generates a complex process of electro-chemical reaction that consists of several sub-processes and involves accumulation of interface traps and positive charge at the Si-SiO<sub>2</sub> interface leading to degradation of PMOS threshold voltage [53][54].

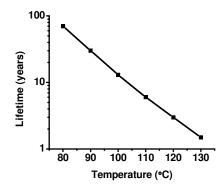

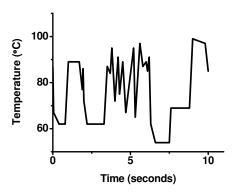

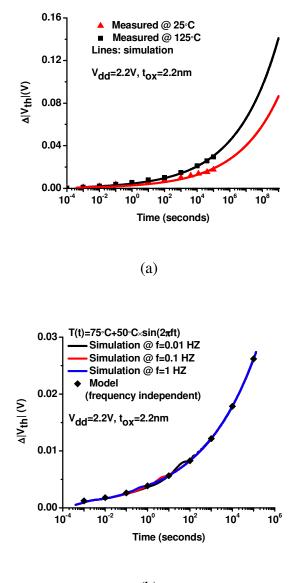

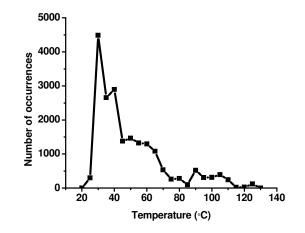

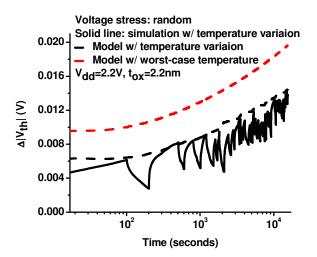

NBTI is highly sensitive to operating temperature. This is illustrated in Figure 1.2, where the NBTI-limited lifetime of an inverter chain is shown to decrease by 2.2X for every 10°C increase in operating temperature. On-chip temperature in modern ICs exhibits significant variation that depends on the operating conditions of the chip. The precise spatial and temporal characteristics of temperature behavior are complex. They depend on the thermal properties of the substrate, the local current densities, and the input switching patterns. Spatially, differences of temperature of up to 50°C are possible in high-end microprocessors [56]. Temporal temperature profile may change very rapidly. Figure 1.3 shows a trace of temperature in a circuit block [57] in which the temperature can vary by up to 50°C within 3 seconds. Because of the above reasons, to accurately

predict the amount of NBTI-induced circuit performance degradation it is indispensable to have a model capable of handling arbitrary temperature variation in which devices actually operate. In this work, we focus on the impact of temporal variation of temperature, i.e., dynamic temperature variation. Without ambiguity, we use the term "temperature variation" to mean the temporal variation of temperature in the rest of the work.

Figure 1.2: Lifetime of an inverter chain decreases by 2.2 X for every 10 °C increase in operating temperature due to NBTI. The temperature is held constant throughout the lifetime of the circuit. Degradation of PMOS threshold voltage is obtained from [51]. Circuit delay is obtained from SPICE simulation for 45nm technology node. Duty cycle of input signal is set to be 50%.

Figure 1.3: Operating temperature exhibits significant dynamic variation for workload C630 of the DRM block in a microprocessor design ([57]).

Several compact NBTI models suitable for circuit-level simulations have been proposed in the past. In [53][54][58][59], the models assume that both the temperature and the voltage stress are fixed at constant values. The impact of interrupting of voltage stress due to signal transition with a fixed temperature is studied in [51][60][61][62]. In [63], both the temperature and the voltage signal are assumed to change between only two levels. Moreover, the voltage signal at any time is assumed to be known. In the case of continuously-changing temperature that spans a large range, the assumption of such two-level temperature can result in significant error in the change of PMOS threshold voltage, if the rms value of the difference between the actual temperature and its two-level approximation is large.

In this work, a novel compact NBTI model that can handle arbitrary temperature variation is proposed. It takes into account the device-level characterization of the temperature dependence of the various sub-processes of NBTI [53][64][65][66] and is consistent with the general framework of reaction-diffusion (R-D) model [53][54]. When both temperature variation and signal transition are present, our model inherits the legacy of the existing models on the treatment of signal transition and also incorporates the impact of temperature variation at the same time.

The proposed model enables both optimal design of circuit for NBTI based on temperature-profiling and real-time adaptive control to mitigate the NBTI problem based on temperature-monitoring. For temperature-profiling, thermal simulators such as HotSpot [67] has been utilized at design-time to predict the spatial and temporal variation of temperature on the chip. Using the information of temperature variation can avoid over-design for NBTI mitigation. For real-time adaptive control, on-chip temperature sensors have been used to monitor the temperature variations during the usage of the chip. The monitored temperature values are fed into a controller for real-time thermal management [68]. This scheme can be easily adapted for real-time control of NBTI if the controller is equipped with an NBTI estimator based on the monitored temperature values.

#### 1.5 ONLINE CIRCUIT RELIABILITY MONITORING

In order to combat the degradation of devices, specifically NBTI, traditional design practice adds guard-band to the clock period to ensure that the circuit can properly function even if the circuit is stressed with the *worst-case* operating condition through its lifetime [52]. This pessimism inevitably incurs high cost in performance. To reduce the pessimism, online monitoring techniques have been employed to measure the actual degradation of the circuit [52][57][72]. The existing measurement-based techniques can be classified into three types. The first type measures the degradation of a simple structure (a PMOS transistor or a ring oscillator) and infers the degradation of a large circuit without considering the impact of its circuit topology [57]. The second type measures the delay degradation of the circuit directly, by sensors constantly monitoring part or all of the primary outputs of the circuit [52][72]. The major drawback of this technique is that the number of the sensors can be huge when there are a large number of primary outputs on the chip that need to be monitored. The third type involves occasional online full delay testing using test programs [73]. This approach requires expensive infrastructure for online delay testing and needs to interrupt the normal operation of the circuits.

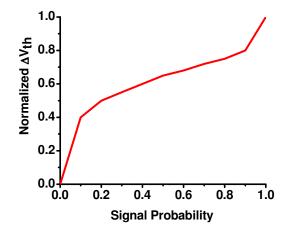

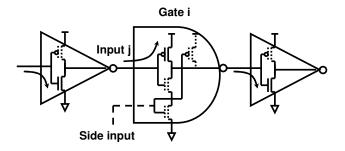

To overcome the above limitations, we develop an effective reliability tracking framework that uses a circuit reliability macromodel and a hybrid network of on-chip sensors that consist of temperature sensors and ring oscillators. The key feature of our work, in contrast to the traditional tracking techniques that rely solely on direct measurement [52][57][72][73], is an explicit reliability macromodel which takes realtime temperature measurements as input and maps them to the current circuit degradation (the increase of  $D_{max}$ ). We choose to monitor temperature because among environmental factors affecting NBTI that include signal probabilities, supply voltage ( $V_{dd}$ ,) and temperature, the latest has the dominant impact on the rate of device degradation. We found through simulation, by assuming typical variations of the environmental factors, that variations of signal probabilities,  $V_{dd}$  and temperature can lead up to 14%, 16% and 56% differences in circuit delay increase ( $\Delta D_{max}$ ) respectively, compared to the nominal  $\Delta D_{max}$  at the end of lifetime. In addition, cost-effective on-chip temperature sensors already exist and they have been used in commercial chips to monitor real-time chip temperature [74]. Another key aspect is the calibration scheme that allows model parameters refined via direct observation. This is necessary because of process variation and unknown physics [53][58][76].

#### **1.6 DISSERTATION ORGANIZATION**

The remainder of the dissertation is organized as follows. Chapter 2 presents a tool for fast analysis of soft error susceptibility for cell-based designs. Chapter 3 describes analytical modeling of SRAM dynamic stability. In Chapter 4, we present a model for NBTI under dynamic temperature variation. Chapter 5 describes a framework of online circuit reliability monitoring using a reliability macromodel and a network of sensors. Finally, Chapter 6 concludes this dissertation.

### Chapter 2: FASER: Fast Analysis of Soft Error Susceptibility for Cell-Based Designs

Soft errors have emerged to be a major reliability concern for combinational logic circuits as technology scales down [1]. Estimating the soft error rate is essential for choosing the proper hardening strategy for the design.

In Chapter 1, we have described that soft errors are the result of high-energy particle strikes at the sensitive areas of MOS transistors. However, due to several masking mechanisms [1][12][21][22][23][24], namely, electrical masking, logic masking, and latching-window masking, the actual soft error rate (SER) is substantially lower than the raw particle strike rate. The raw particle strike rate is readily available [11], hence the key is to estimate the reduction of error rate likelihood due to these masking mechanisms.

The soft error de-rating due to the masking mechanisms for a combinational logic circuit is dependent upon the circuit's input vector. Existing work on estimating soft error rate for combinational logic circuit uses simulation techniques to explicitly enumerate the input vectors [12][21][22]. However, the simulation approach suffers the problem of poor scalability since the number of input vectors grows exponentially with the number of primary inputs.

In this work, we propose FASER, which stands for Fast Analysis of Soft ERror susceptibility, for cell-based signs. The innovation is that we use binary decision diagrams (BDD) to avoid explicit enumeration of input vectors, and we use SPICE to precharacterize the cells for error generation and propagation to ensure the accuracy of the tool.

This chapter is organized as follows. Section 2.1 describes the cell characterization procedure. In Sections 2.2, 2.3 and 2.4, we discuss the static analysis of SER. Section 2.5 presents the experimental results, and we summarize this chapter Section 2.6.

#### 2.1 CELL LIBRARY CHARACTERIZATION

The proposed static SER analysis methodology FASER is targeted towards the use with the cell-based design methodology. Accurate library characterization is thus a key consideration. The two essential characterization steps are pulse generation and pulse attenuation (propagation).

A high-energy particle striking a node deposits charge which leads to a timevarying voltage pulse of a certain magnitude and shape. The characteristics of the pulse are dependent on the specific transistor network of each gate. Thus, the goal of the library characterization is to predict for every library gate the waveforms produced at the cell output for particle strikes at each vulnerable region. The current flow created by the charge deposited into the node is modeled as a single exponential for cosmic-ray related soft errors [1][22] (alternative models for alpha-particle related soft errors are also in existence [35][36][37]):

$$I(q,t) = \frac{2q}{\sqrt{\pi}T_s} \sqrt{\frac{t}{T_s}} e^{-\frac{t}{T_s}}$$

(2.1)

where q is the collected charge and  $T_s$  is the technology-dependent charge-collection time constant. Collected charge q depends on the particle energy, and follows an exponential distribution [1][22].

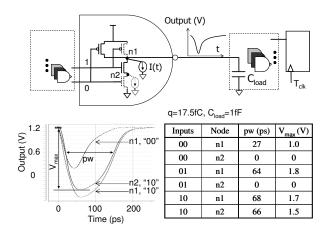

Figure 2.1: Pulse generation is characterized by circuit simulation with SPICE. The table shows the pulse produced at the output of NAND gate.

Figure 2.1 shows the SPICE simulation setup for characterization of pulse generation, where every vulnerable node is taken into account. The simulations are performed for a range of charge values (q) and load capacitances ( $C_{load}$ ). The voltage pulses produced at the cell output by a specific charge deposited on an intra-cell node strongly depends on the biasing condition determined by the input vector. In the example circuit of Figure 2.1, both n1 and n2 are sensitive if the input vector is "10" (the pulse generated at n2 is slightly attenuated by the transistor above it), while only n1 is sensitive if the input vector is "01" or "00". When the input vector is "00", the pull-up network has the smallest resistance, resulting in the smallest falling pulse generated.

Existing tools [1][12][21][22][23][24] either ignore the effects of biasing conditions, or assume the worst case biasing conditions for every gate in the circuit. Experiments show a difference of 1.5X - 4X between the SPICE simulation result and the analysis performed under the worst-case assumptions. Clearly, accurate soft error analysis tool needs to consider different biasing conditions of the gates.

Figure 2.2: Pulse propagation is characterized by circuit simulation with SPICE. The curves show the low-pass characteristic of NAND gate.

The voltage pulse produced at the cell output is approximated by a trapezoidal waveform, and are captured by two parameters, pulse width (pw) measured at  $0.5V_{DD}$  and maximum voltage value  $(V_{max})$ . The rise and fall times of the trapezoidal waveform are chosen to be typical values.

After a transient faulty pulse is generated, it propagates toward the primary outputs of the circuit. In the course of its propagation, the pulse's electrical properties, such as width and magnitude, evolve as a result of the low-pass characteristics of the gates it propagates through. Short pulses tend to be attenuated, while long pulses tend to maintain their original width and magnitude after passing through a combinational logic gate. Figure 2.2 shows the SPICE simulation setup for characterization of this dynamic transfer function, where pw and  $V_{max}$  of the output pulse is found as a function of the input pulse. While different input-pin to output paths may be characterized by somewhat different transfer characteristics, this is a secondary effect, which we have for now ignored.

Pulses may re-converge and overlap at a gate in a circuit if multiple paths exist between the particle-striking point (fault-site) and the gate. The interaction of two pulses arriving simultaneously can be modeled. Currently, characterization captures only the first-order effect of pulse-overlapping with the output produced by simple superposition, followed by low-pass filtering by the gate's dynamic transfer function. The error of estimation for circuit SER due to this approximation appears to be minor compared with SPICE simulation for the benchmark circuits we have tested.

#### 2.2 STATIC ANALYSIS OF FAULT EVENTS PROPAGATION

FASER is a static SER analysis methodology in that it relies on the implicit enumeration of the input vector space. The algorithm formally encodes and propagates the error pulses using binary decision diagrams. Binary decision diagrams are a powerful data structure proposed by Bryant [28] for efficient representation and manipulation of Boolean functions. By propagating the fault-encoding function to the primary outputs the algorithm can accurately predict output error probabilities. The error propagates only if the path from a fault-site to the output is sensitizable under the specific assignment of side inputs to the gates. The proposed BDD-based symbolic error manipulation algorithm succeeds in effectively capturing such logical masking [21][22]. However, the formation and propagation of the pulses symbolically is intrinsically linked in the algorithm with the accurate characterization of cell electrical properties, contained in the library. This guarantees accurate modeling of electrical masking [21].

Figure 2.3: Fault-encoding with event BDD for the biasing condition "10". The strength of the pulse depends on the biasing condition and the strike location within the gate.

Figure 2.4: Pulse propagation in a simple circuit. Numbers inside the gates are their propagation delays. Terminals of event BDDs contain pulse propagation delays and durations. Pulses encoded with event BDDs of N and M cancel each other, resulting in no pulse at X.

The BDD describing the Boolean function at a given node in an error-free environment is termed *static* BDD. It is constructed using the classic rules of [28]. A particle strike at a node creates a transient pulse that can be represented by modifying the static BDD. Such a data structure is referred to as *event BDD*. In the event BDD, the terminal vertices encode both the error pulses and the original static logic values. The event BDD encoding will contain the arrival time (*AT*), the maximum voltage ( $V_{max}$ ), and the width of the pulse (*pw*). Figure 2.3 shows fault-encoding with event BDD for biasing condition "10". If the pins of the gates are not primary inputs, the BDD describing the Boolean function of the biasing condition is found first, which is then modified to contain a pulse at one of its terminal vertex to become an event BDD.

Constructing the output event BDD for an operation on two input event BDDs is a recursive process similar to that of constructing the static BDD, which utilizes the standard BDD operations [28]. The operations are different only in how the terminal vertices are processed. Specifically, when the terminal vertex of one operand is reached, we check if the state of the output can be determined. If it can, a terminal vertex for the

output event BDD is generated. Otherwise, a non-terminal vertex for the output is generated, and the event BDD of the other operand is searched one level deeper. Determining the state of the output is through logic operation and table look-up from the library. Logic operation is performed, for example, if one operand has a controlling value and has no pulse, in which case, the output value is determined regardless of the state of another operand (logic masking). Table lookup is performed when the analog characteristics of the output pulse is to be determined (electrical masking).

As noted in the previous section, different biasing conditions may result in very distinct output pulse, sensitive area and hence latching error probability due to particle strikes at a given gate. In order to achieve near SPICE-level accuracy, this dependence needs to be taken into account during the analysis, which requires enumerating all gate biasing conditions and all intra-gate nodes. This clearly increases the computational burden on the algorithm since for each biasing condition and each intra-gate node an event BDD is now generated at the fault site and propagated to the latches. We have found that this is crucial for accuracy improvement and that the penalty is affordable in most cases. Indeed, assuming that the average cell fan-in is k, the increase in complexity due to this enumeration is  $O(k2^k)$ . Since k is typically between 1 and 3, the cost is manageable.

Propagating the fault events *statically* is equivalent to constructing the event BDDs for the circuit nodes in the fan-out cone of the fault-site where the particle-strike occurs. The event BDD of a circuit node is simply its static BDD if it is outside the fan-out-cone of the fault site, since no error-pulses will occur at the node.

To illustrate fully the working of the algorithm, consider a small circuit example of Figure 2.4. To simplify the discussion, the pulse magnitude is ignored and only the pulse width is taken into account. Given the collected charge, an event BDD is generated for each biasing condition and intra-gate node of the fault site (node M) is constructed. Due to electrical masking, the pulse width changes along the propagation. The error-pulse is logically-masked when B=1. The event BDD at node X is the same as its static BDD because the pulse at node X is too small due to re-convergence to reach the gate threshold voltage.

#### 2.3 ALGORITHM FLOW AND LATCHING PROBABILITY COMPUTATION

Ultimately, the static analysis of FASER is based on computing the probability of an error at the latch due to the totality of pulses propagating towards primary outputs. First, it is assumed that a particle can strike every node (diffusion region) in the circuit with the probability given by the ratio of the node area to total area. Second, the primary inputs remain stable. The validity of this assumption for SER analysis was demonstrated in [12]. Third, the equilibrium probabilities of the primary inputs are known and independent of each other. This last assumption has been successfully applied for power estimation and circuit reliability assessment [29]. Soft error estimation for circuits with strongly correlated primary inputs will be our future work.

The core of the algorithm is to find the conditional latching error probability P(q, bc, i, j, k), given the collected charge q, biasing condition bc of the victim gate (fault site), intra-gate node j of gate i, and latch k. Calculating P(q, bc, i, j, k) is discussed in the next paragraph. The contribution to the bit error rate (BER) of latch k by gate i is,

$$PL = \frac{pw - w}{T_{clk}} BER(i,k) = \sum_{j} \sum_{bc} \sum_{q} P(q,bc,i,j,k)(R(q,i,j)\Delta q)$$

(2.2)

where  $R(q, i, j)\Delta q$  is the strike rate for collected charge in the range of q and  $q + \Delta q$ , which is proportional to the area of node j of gate i. We use the average BER of all output latches by particle strikes on all gates as a merit of a circuit's soft error susceptibility. However, other criteria, such as the largest BER of the latches, can be used as well, depending on the application.

Propagating an event BDD to the primary output gives us a reliable measure of the occurrence probabilities and strengths of the pulses that will appear at the latch inputs. However, the latching error probability is linked to another masking mechanism, known as latching window masking. Latching window masking occurs due to the *temporal randomness* of the particle strike time [1][12][21][22], and the realization that the pulse arrival time at the latch has to be within the latching window for the error to occur. Assuming a uniform strike-time probability, the actual latching probability for a pulse is:

$$PL = \frac{pw - w}{T_{clk}}$$

(2.3)

where *PL* is the latching probability, *pw* is the width of the faulty pulse present at the input of the latch, *w* is latching-window size of the latch, and  $T_{clk}$  is the clock period. Given an event described by the set of parameters (*q*, *bc*, *i*, *j*, *k*), the event BDD at the primary output *k* is constructed first (Figure 2.5). With the assumption that the primary inputs are independent of each other, each edge of the event BDD is assigned a probability, based on the primary input the edge corresponds to. By recursively traversing the event BDD, the probability for an event contained in a terminal *v* to occur, *p*(*v*) can be calculated [10]. The conditional latching error probability *P*(*q*, *bc*, *i*, *j*, *k*), is then  $P(q, bc, i, j, k) = \sum_{v} p(v)PL(v) \qquad (2.4)$

where PL(v) is the latching error probability of the pulse contained in terminal v of the event BDD, determined by (2.3).

Generate static BDD for every circuit node; BER ← 0; for all combinations of (q, bc, i, j, k)

1. Retrieve the generated pulse shape for (q, bc, i, j, k), and generate an event BDD at the fault site i.

2. Propagate the event BDD in the fan-out cone of fault site i.

3. The event BDD at the primary output k (input of latch k) is traversed to find P(q, bc, i, j, k).

4. BER += P(q, bc, i, j, k)(R (q, i, j)∆q) end BER ← BER / num\_of\_latches;

Figure 2.5: Pseudo-code of FASER flow.

### 2.4 CIRCUIT PARTITIONING FOR SPEED-UP

It is well known that the worst-case complexity of the BDD encodings of logic functions is exponential in the number of variables [28]. To make manipulation of BDDs efficient, a partitioning heuristic is adopted. This is a common practice in CAD techniques that use BDDs [33][34]. The use of partitioning allows a significant speed-up without a noticeable loss of prediction accuracy.

The circuit is partitioned into smaller domains as shown in Figure 2.6. Some nodes are designated to be pseudo primary inputs, and serve as the boundary between the partitions. Signal correlations are only considered within the domains. To estimate the latching error probability due to a particle-strike on a particular gate, an event BDD is generated at the fault site and propagated to the boundary nodes, where the pulse occurrence probabilities are estimated by traversing the event BDDs. Next, these pulses are treated as being generated at the boundary nodes and assumed to be independent of each other. In principle, these secondary pulses can be independently propagated further to the latches. The latching error probability due to particle strike at the fault site is approximated by the sum of the latching probabilities of the secondary pulses weighted by their respective occurrence probabilities. In practice, if we process the fault sites backward starting from the gates closest to the latches, the latching probabilities of the secondary pulses can be directly estimated from the latching error probabilities due to particle-strike at the boundary nodes, without further propagation of the secondary pulses.

We define the partition size as the maximum number of primary/pseudo primary inputs of each domain. A larger partition size allows a more global account of signal correlations but at the cost of a rapidly growing run time and memory usage. The tradeoff between speed and accuracy is performed by adjusting the partition size. We believe that the most significant impact of signal correlation on pulse propagation occurs in the neighborhood of the fault site. Therefore, the improvement of accuracy beyond a certain partition size (typically, 15-20) is expected to be minimal, and this is confirmed by the experimental results.

Figure 2.6: Partitioning circuits for speed-up leads to the loss of correlations between pulses of different domains. The loss of accuracy is minimal for partition size beyond a certain point.

#### 2.5 EXPERIMENTAL RESULTS

The static SER analysis tool FASER was implemented in C++. The experiments investigated the accuracy of the static technique, the runtime of the algorithm, and the speed-accuracy trade-off using the partition heuristic. FASER takes a technology-mapped netlist, equilibrium probability of the primary inputs, clock period, and flux rate of the high-energy neutrons, and gives BER of the latches at the primary outputs. The widely utilized flux rates for New York City were used for analysis [11]. The SPICE technology files were based on the Berkeley Predictive Technology Model (BPTM) for the 100nm technology [30].

In order to verify the validity of the FASER, a Monte-Carlo experiment based on SPICE simulation was utilized. Since Monte-Carlo SPICE simulation is very timeconsuming, we were only able to perform the tests on small artificially constructed benchmark circuits, with the largest circuit containing 35 gates.

The Monte-Carlo simulation is designed to measure the latching error probability given a particle strike with a random data set of (collected charge q, strike time t, gate i, node j, input vector V). Collected charge q follows an exponential distribution [1][22]. Strike time t is uniformly distributed between 0 and  $T_{clk}$ . The probability for a strike to occur in node j of gate i is proportional to node j's area. We assume that all input vectors have equal probability

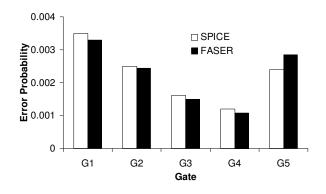

The experiments were conducted as follows. For a random data set of (q, t, i, j, V), a current pulse with magnitude corresponding to the collected charge q and polarity corresponding to node j's diffusion type is injected to node j of gate i at time t, with input vector V. Voltage samples are taken at the latch output at  $T_{clk}$  and  $2T_{clk}$ . If either value did not match the correct one, an error is declared. Under this set-up, the conditional latching error probability is equal to the number of errors divided by the total number of simulations. The run time of the Monte-Carlo tests ranges from 15 minutes to 45 minutes for the artificial benchmark circuits. FASER takes into account 5 different pulse strengths and its run-time for every test circuit is less than 0.01 seconds, giving a speed-up of over 90,000X. All experiments are conducted on a Dell GX260 workstation running Redhat Linux. The latching error probabilities of the benchmark circuits are compared in Figure 2.7. The average error between the two sets of data is 12% and can be well attributed to the simplified 2-parameter modeling of the error pulse in cell library characterization. Figure 2.8 shows the latching error probability due to each gate in circuit C1.

FASER with circuit partitioning heuristic is validated on the ISCAS'85 benchmark circuits. Partition size is expressed in terms of the maximum number of primary/pseudo primary inputs of the pulse propagation domains. Experimental results in Table 2.1 show that good accuracy can be achieved with relatively small partition size. The run-time varies between 22 seconds and 638 seconds for partition size 15 (Table 2.2). The runtime increases rapidly with partition size as shown in Table 2.1. However, improvement in accuracy is very small for partition sizes beyond 15. The estimated BER for 100nm CMOS technology is on the order of  $10^{-5}$  FIT, where 1 FIT is defined as 1 failure in  $10^9$  hours. It is to be noted that the partition size is not the sole factor that affects the run time. The circuit structure and the choice of pseudo primary inputs in partitioning also can greatly affect the BDD size, which is a well known property of BDD.

As a proxy of the memory usage, the maximum BDD size in terms of the number of vertices of the BDD is measured and shown Table 2.2. The general trend is that the BDD size increases drastically with partition size. The increase of BDD size with respect to the circuit size under the same partition size is due to the increased complexity of the nodal functions.

Figure 2.7: Error probabilities by FASER and SPICE simulation. The average error is 12%.

Figure 2.8: Latching error probability due to each gate in circuit C1.

| Table 2.1: Bit Error Rates for ISCA | S' 85 benchmark circuits with different partition sizes |

|-------------------------------------|---------------------------------------------------------|

| (Np)                                |                                                         |

| Circuits | Bit Error Rates (10 <sup>-5</sup> FIT) |       |       |  |

|----------|----------------------------------------|-------|-------|--|

|          | Np=15                                  | Np=20 | Np=30 |  |

| C432     | 3.0                                    | 3.2   | 3.1   |  |

| C499     | 2.0                                    | 2.0   | 2.0   |  |

| C1908    | 2.2                                    | 2.1   | 1.9   |  |

| C1355    | 2.0                                    | 2.0   | 2.0   |  |

| C3540    | 2.6                                    | 2.6   | 2.4   |  |

| C5315    | 1.1                                    | 1.1   | 1.1   |  |

| C7552    | 1.9                                    | 1.8   | 1.8   |  |

| Circuit | Run-time(s) |       |       | Max BDD Size |       |       |

|---------|-------------|-------|-------|--------------|-------|-------|

| eneur   | Np=15       | Np=20 | Np=30 | Np=15        | Np=20 | Np=30 |

| C432    | 22          | 76    | 465   | 99           | 1223  | 86083 |

| C499    | 39          | 63    | 129   | 101          | 145   | 404   |

| C1908   | 66          | 86    | 1050  | 169          | 187   | 26393 |

| C1355   | 40          | 62    | 119   | 101          | 145   | 406   |

| C3540   | 149         | 195   | 5400  | 1028         | 1353  | 17861 |

| C5315   | 278         | 546   | 1515  | 1372         | 6115  | 12100 |

| C7552   | 638         | 780   | 7200  | 1813         | 6702  | 11602 |

Table 2.2: Run-time and the maximum BDD size for the ISCAS' 85 benchmark circuits.

#### 2.6 SUMMARY

In this chapter, we proposed a fast static soft error analysis tool FASER. Accurate models are based on STA-like precharacterization methods, and logical masking is computed via binary decision diagrams with circuit partitioning. Experimental results indicate that the FASER achieves good accuracy compared to the SPICE-based simulation method. The average error across the benchmark circuits is 12% at over 90,000X speed up.

## **Chapter 3: Analytical Modeling of SRAM Dynamic Stability**

SRAM-based memory arrays are a major component of integrated circuits, and verifying the stability of SRAM cells is essential to ensure the quality of the integrated system. Evaluating the stability of an SRAM cell using static noise margin (SNM) static noise margin (SNM) [38] is straightforward, but it is at the cost of reduced design margins. On the other hand, checking stability using dynamic noise margins (DNM) requires complex time-dependent stability analysis but permits a more aggressive flexible design, without jeopardizing reliability. DNM take into account spectral and time-dependent properties of the specific noise patterns. In this work, we specifically study the DNM of an SRAM cell under the impact of single event upsets (SEU) [11][7][8][9].

Our contribution is this work is: 1) we propose a criterion for DNM of an SRAM cell; 2) we obtain an analytical form of DNM, under the approximation of piece-wise linearization. This chapter is organized as follows. In Section 3.1, we set up differential equations to describe the nonlinear dynamics of the SRAM cell. Based on the mathematical formulation of Section 3.1, we conduct the analytical study on the dynamic stability of the SRAM cell in Sections 3.2 and 3.3. We present the experimental results in Section 3.4. Finally we summarize this chapter in Section 3.5.

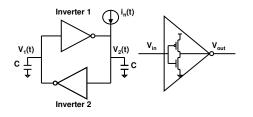

#### 3.1 SYSTEM MODELING SETUP

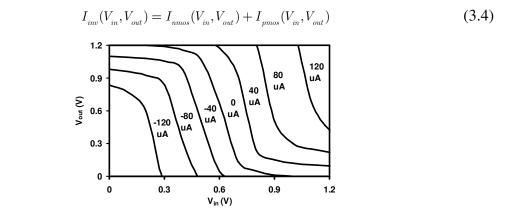

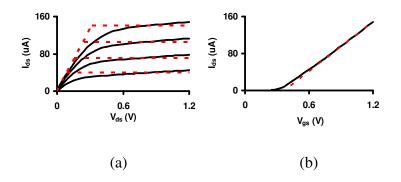

In this work, we focus on the stability of a 6T SRAM cell with respect to an SEU. An SEU is a rare and random event. At the moment when it occurs, the SRAM cell is most likely in the standby mode. Therefore, we will only evaluate the SRAM stability in the standby mode. For other noise sources, the most interested modes might be the read or write mode. However, the framework built in this work can be easily extended to those cases. A 6T SRAM cell consists of two identical cross-coupled inverters and two access transistors. For notational simplicity, the two access transistors are not included in the analysis. Without loss of generality, the noise source in this work is modeled as a current pulse injected into the internal node where the initial voltage is zero, Figure 3.1. If the noise source flows in the opposite direction, i.e. drawing positive charge from the internal node where the initial voltage is  $V_{dd}$ , the following discussion still applies, but with the roles of the NMOS and PMOS being switched. Capacitance, *C*, is the total lumped capacitance at the output node of each inverter. We describe the *state* of the cell by the *state vector*  $\vec{V} = (V_1, V_2)$ , where  $V_1$  and  $V_2$  are the two nodal voltages of the cell. For a given state vector value, the currents flowing through the four transistors can be determined. The set of  $\vec{V}$  of all possible values forms the *state space*. The transient noise current is modeled as a square pulse with amplitude,  $I_u$ , and pulse width, pw :

$$\dot{u}_{n}(t) = \begin{cases} I_{n} & (0 < t < pw) \\ 0 & (t \le 0 \text{ or } t \ge pw) \end{cases}$$

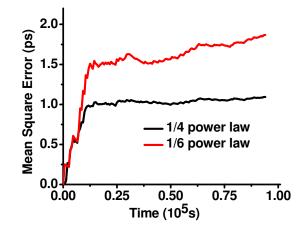

(3.1)