# Backward-compatible Enhancements to the 10 Mb/s Single-Pair Ethernet on Shared Media

by

HUSZÁK Gergely György

A dissertation submitted for the degree of Doctor of Philosophy in Engineering (Ph.D. Eng.)

University of Electro-Communications (UEC) Tokyo, Japan

$15^{\rm th}$  March 2022

## 共有メディア方式における 10 Mb/s シングルペアイーサネットの 後方互換性をもつ機能拡張に関する研究

フサーク ゲルゲイ ジォルジ

博士論文 (工学)

電気通信大学 (東京)

令和4年3月15日

## Dissertation Committee Members at the University of Electro-Communications

Professor YOSHINAGA Tsutomu Professor MATSUURA Motoharu Associate Professor OGAWA Tomohiro Associate Professor WU Celimuge Professor Emeritus MORITA Hiroyoshi Associate Professor OHZAHATA Satoshi

### Contents

| Chapte | er 1 Int                                         | troduction                              | 1             |  |  |  |  |

|--------|--------------------------------------------------|-----------------------------------------|---------------|--|--|--|--|

| 1.1    |                                                  | round                                   | $\frac{1}{3}$ |  |  |  |  |

| 1.2    | Objectives and contributions of the dissertation |                                         |               |  |  |  |  |

| 1.3    | Organ                                            | ization of the dissertation             | 5             |  |  |  |  |

| Chapte | er 2 Th                                          | ne evolution of technology and research | 6             |  |  |  |  |

| 2.1    |                                                  |                                         | 6             |  |  |  |  |

| 2.2    |                                                  |                                         | 6             |  |  |  |  |

| 2.3    |                                                  |                                         | 8             |  |  |  |  |

| -      | 2.3.1                                            |                                         | 9             |  |  |  |  |

|        | 2.3.2                                            |                                         | 11            |  |  |  |  |

|        | 2.3.3                                            |                                         | 15            |  |  |  |  |

|        | 2.3.4                                            | •                                       | 17            |  |  |  |  |

| 2.4    | The II                                           |                                         | 8             |  |  |  |  |

| 2.5    |                                                  |                                         | 9             |  |  |  |  |

|        | 2.5.1                                            |                                         | 9             |  |  |  |  |

|        | 2.5.2                                            | 8 8                                     | 9             |  |  |  |  |

| Chapte | er 3 Or                                          | the 10BASE-T1S preamble for multidrop 2 | <b>2</b>      |  |  |  |  |

| 3.1    |                                                  |                                         | 22            |  |  |  |  |

| 0.1    | 3.1.1                                            |                                         | 22            |  |  |  |  |

|        | 3.1.2                                            | -                                       | 23            |  |  |  |  |

| 3.2    |                                                  | •                                       | 25            |  |  |  |  |

| 0      | 3.2.1                                            | -                                       | 25            |  |  |  |  |

|        | 0                                                |                                         | 27            |  |  |  |  |

|        |                                                  |                                         | 28            |  |  |  |  |

|        | 3.2.2                                            |                                         | 28            |  |  |  |  |

|        |                                                  |                                         | 29            |  |  |  |  |

|        |                                                  |                                         | 29            |  |  |  |  |

| 3.3    | Evolut                                           |                                         | 29            |  |  |  |  |

|        | 3.3.1                                            |                                         | 29            |  |  |  |  |

|        | 3.3.2                                            |                                         | 80            |  |  |  |  |

|        | 3.3.3                                            |                                         | 80            |  |  |  |  |

|        |                                                  |                                         | 31            |  |  |  |  |

|        |                                                  |                                         | 33            |  |  |  |  |

| 3.4    | Presen                                           |                                         | 34            |  |  |  |  |

|        | 3.4.1                                            |                                         | 34            |  |  |  |  |

|        | 3.4.2                                            |                                         | 35            |  |  |  |  |

|        |                                                  |                                         | 37            |  |  |  |  |

|        |                                                  |                                         | 37            |  |  |  |  |

|        |                                                  | •                                       | 88            |  |  |  |  |

|        | 3.4.3                                            |                                         | 39            |  |  |  |  |

|        |                                                  | · · ·                                   | 41            |  |  |  |  |

|        |                                                  |                                         | 11            |  |  |  |  |

| 3.5    | Conclu                                           |                                         | 12            |  |  |  |  |

|        |                                                  |                                         |               |  |  |  |  |

| Chapt |                                                                                                                             | ackward-compatible Forward Error Correction of burst                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |  |  |  |  |  |

|-------|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|--|

|       |                                                                                                                             | rors and erasures for 10BASE-T1S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43 |  |  |  |  |  |

| 4.1   |                                                                                                                             | luction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |  |

|       | 4.1.1                                                                                                                       | Why FEC?                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |  |  |  |

|       | 4.1.2                                                                                                                       | The roots of problem being solved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |  |  |  |

|       | 4.1.3                                                                                                                       | Connection with the research on preamble                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |  |  |  |

| 1.0   | 4.1.4                                                                                                                       | Research and verification methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |  |  |  |

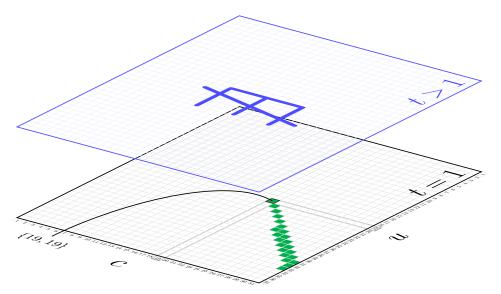

| 4.2   |                                                                                                                             | nel model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |  |  |  |  |  |

| 4.3   |                                                                                                                             | vard-compatibility                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |  |  |

|       | <ul><li>4.3.1 The reasons for requiring backward-compatibility</li><li>4.3.2 What backward-compatibility entails?</li></ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |

|       | 4.3.2                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |

|       |                                                                                                                             | 4.3.2.A General definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |

|       |                                                                                                                             | 4.3.2.B Requirements in technical terms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |  |  |  |  |  |

|       | 4 9 9                                                                                                                       | 4.3.2.C Additional preferences                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |  |  |  |  |  |

|       | 4.3.3                                                                                                                       | Details of backward-compatibility per sublayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |  |  |  |  |  |

|       |                                                                                                                             | 4.3.3.A Backward-compatibility at the PCS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |  |  |  |  |  |

|       |                                                                                                                             | 4.3.3.B Backward-compatibility with PLCA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |  |  |  |

|       | 494                                                                                                                         | 4.3.3.C Summary of backward-compatibility per sublayer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |  |  |  |  |  |

|       | 4.3.4                                                                                                                       | Forbidden Symbols                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |  |  |  |  |  |

| 4.4   | 4.3.5                                                                                                                       | Summary of all backward-compatibility requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |  |  |

| 4.4   |                                                                                                                             | features in conjunction with the FEC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    |  |  |  |  |  |

|       | $4.4.1 \\ 4.4.2$                                                                                                            | Multiplicative scrambling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |  |  |  |  |  |

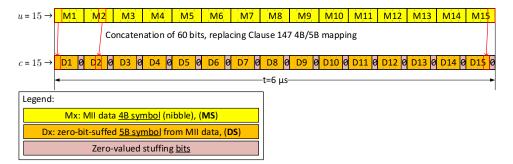

| 4 5   |                                                                                                                             | 4B/5B encoding and its timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |    |  |  |  |  |  |

| 4.5   |                                                                                                                             | Inderlying Error Correcting Code (ECC)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |  |  |  |  |  |

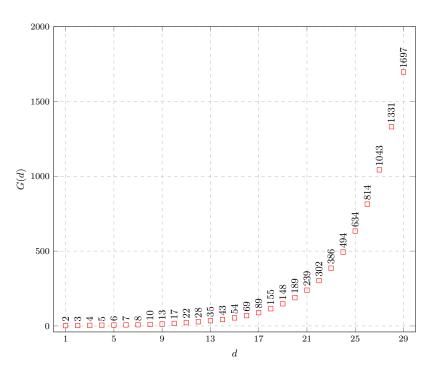

|       | 4.5.1                                                                                                                       | Reed-Solomon Error and Erasure Correcting Codes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |  |  |  |  |  |

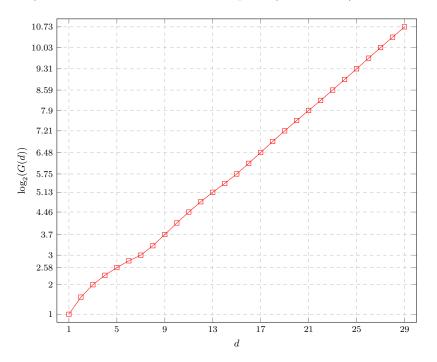

| 16    | 4.5.2                                                                                                                       | Field size vs. interleaving and other code parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |  |  |  |  |  |

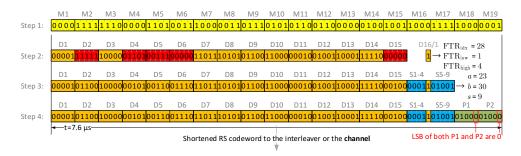

| 4.6   | -                                                                                                                           | proposed FEC scheme                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |  |  |  |  |  |

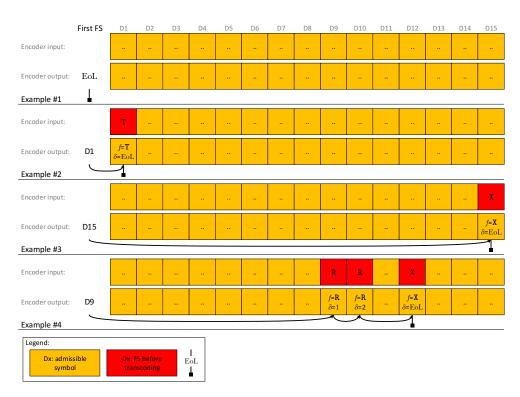

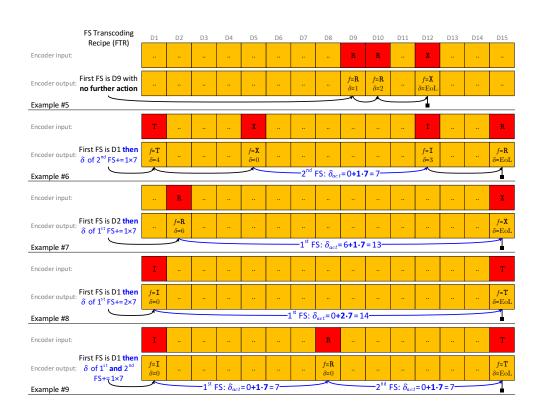

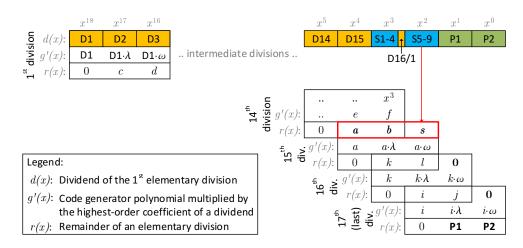

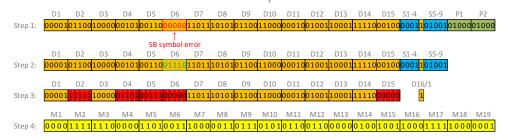

|       | $\begin{array}{c} 4.6.1 \\ 4.6.2 \end{array}$                                                                               | Encoding process without considering FSs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |  |  |  |  |  |

|       |                                                                                                                             | Avoiding Forbidden Symbols in the codeword                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |

|       | 4.6.3                                                                                                                       | 4.6.3.A Avoiding the appearance of an FS among <b>DS</b> s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |

|       |                                                                                                                             | 4.6.3.B Avoiding the appearance of an FS among <b>DS</b> s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |    |  |  |  |  |  |

|       |                                                                                                                             | 4.6.3.C Avoiding SBs forming an FS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |  |  |  |  |  |