Copyright

by

Xiaofeng Fan

2006

The Dissertation Committee for Xiaofeng Fan certifies that this is the approved version of the following dissertation:

# Quantum Corrected Full-band Semiclassical Monte Carlo Simulation Research of Charge Transport in Si, Stressed-Si, and SiGe MOSFETs

| Committee                          |

|------------------------------------|

|                                    |

| Sanjay K. Banerjee, Supervisor     |

|                                    |

| Leonard F. Register, Co-Supervisor |

|                                    |

| Ananth Dodabalapur                 |

|                                    |

| Joe C. Campbell                    |

|                                    |

| Graham F. Carey                    |

|                                    |

| Peter Zeitzoff                     |

|                                    |

# Quantum Corrected Full-band Semiclassical Monte Carlo Simulation Research of Charge Transport in Si, Stressed-Si, and SiGe MOSFETs

by

Xiaofeng Fan, B.S., M.S.E

#### **Dissertation**

Presented to the Faculty of the Graduate School of

the University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

December 2006

To my wife Yanjie and parents, Jianxin Ma and Jifu Fan

#### Acknowledgements

I would like to thank my supervisor, Dr. Sanjay K. Banerjee, for his encouragement, patience and stimulating guidance. In the past five years, I have been impressed by his wide knowledge, strong curiosity to acquire new knowledge and enthusiasm for research. He gave me great academic freedom in my research, which helped me gradually establish independent research ability. It is very important for my academic training as a graduate student.

I also like to thank my Co-Supervisor, Dr. Leonard F. Register. I am very impressed by his knowledge and experience in research, enthusiasm towards research and generous, friendly relationship with students. His supervision played an irreplaceable role in my work. I gained a lot of knowledge and experience from stimulating and fruitful discussions with him.

I would like to express my sincere appreciation to some special colleagues and mentors, Dr. Xin Wang, Dr. Brian A. Winstead, and Dr. Mark C. Foisy. The invaluable guidance and discussions in my graduate study finally leads to pleasing and fruitful collaboration.

Lots of colleagues and friends have given me help and shown me a good time during my time at the Microelectronics Research Center. My thanks go to Wanqiang Chen, Yang-yu Fan, Fei Li, Li Lin, Xin Zheng, Ken Liu, Yueran Liu, Joseph Donnelly, Bahniman Ghosh, Ning Kong, Mehedi, Ningyu Shi, and Matthew Gilbert.

My gratitude also goes to my doctoral committee. Finally, I am deeply indebted to my parents and wife. Their consideration, support and understanding are the most powerful motivations for my research.

Xiaofeng Fan

The University of Texas at Austin

October 2006

Quantum Corrected Full-band Semiclassical Monte Carlo

Simulation Research of Charge Transport in Si, Stressed-Si, and

SiGe MOSFETs

| Publication No. |  |

|-----------------|--|

|-----------------|--|

Xiaofeng Fan, Ph.D.

The University of Texas at Austin, 2006

Supervisor: Sanjay K. Banerjee

Co-Supervisor: Leonard F. Register

This Ph.D. research is centered around a full-band Monte Carlo device simulator ("Monte Carlo at the University of Texas", MCUT) with quantum corrections (based on one-dimensional Schrödinger equation solver). The code itself was based on a solid infrastructure of a Monte Carlo simulator, "MoCa" from the University of Illinois at Urbana-Champaign. To that there were added new methods and features during my Ph.D. program, including strained band structures, alternative (to conventional  $\langle 100 \rangle$ ) surface orientations, full-band scattering mechanisms, and valley-dependent quantum correction. These

features enable "MCUT" to be used to model various strained and/or alloyed silicon MOSFETs, as well as the MOSFETs composed of alternative materials such as Ge, in sub-100 nm regime. Monte Carlo simulation, itself, handles short channel effects and hot carriers in ultra small device well; full-band structure replaces the inaccurate and unknown (for new/strained materials) analytical formulae; and the quantum corrections approximate quantum-confinement effects on device performance. The goal is to understand and predict the device behavior of the so called "non-classical" CMOS — beyond bulk Si based CMOS — in the sub-100 nm regime.

# **Table of Contents**

| 1 | Resea | arch Background                                          | 1  |

|---|-------|----------------------------------------------------------|----|

|   | 1.1   | Full-band Semiclassical Monte Carlo Simulation           | 1  |

|   | 1.2   | Strained Materials for Semiconductor Devices             | 3  |

|   | 1.3   | Quantum Correction in Semiclassical Monte Carlo Method   | 5  |

|   | 1.4   | Monte Carlo at the University of Texas (MCUT)            | 6  |

| 2 | Tensi | ly Biaxially stressed Si nMOS                            | 7  |

|   | 2.1   | Motivation                                               | 7  |

|   | 2.2   | Strain Effects                                           | 9  |

|   | 2.3   | Valley-edge Quantum Corrections                          | 13 |

|   | 2.4   | Full-band Quantum Corrections via "Effective Strain"     | 18 |

|   | 2.5   | Transport within a Spatially-varying Band Structure      | 21 |

|   | 2.6   | Model Devices                                            | 22 |

|   | 2.7   | Mobility Calculations                                    | 24 |

|   | 2.8   | Illustrative High-field and Deeply Scaled Device Results | 29 |

|   | 2.9   | Scalability of TSSi nMOS on Technology Roadmap           | 32 |

|   | 2.10  | Conclusion                                               | 38 |

| 3 | Unia  | xially Stressed Si CMOS                                  | 39 |

|   | 3.1   | Motivation                                               | 39 |

|   | 3.2   | Band Structures                                          | 40 |

|   | 3.3   | Bulk Mobility                                            | 47 |

|   | 3.4   | Discussion                                               | 50 |

| 4 | PMO   | S Wafer Crystal Orientation                              | 52 |

|   | 4.1   | Motivation                                               | 52 |

|     | 4.2    | Band Structure Change under Confinement           | 54 |

|-----|--------|---------------------------------------------------|----|

|     | 4.3    | Confinement to Stress Mapping                     | 56 |

| 5   | Opti   | mum Combination of Stress and Crystal Orientation | 61 |

|     | 5.1    | Position Dependent Stress                         | 61 |

|     | 5.2    | Simulations with Position-Dependent Stress        | 63 |

|     | 5.3    | Combination of Stress and Quantum Confinement     | 65 |

| 6   | Dual   | Gate NMOS Simulation                              | 69 |

|     | 6.1    | Alternative quantum correction scheme             | 69 |

|     | 6.2    | MCUT simulations with dual gate Si nMOS           | 73 |

| 7   | Injec  | ction Efficiency with Bandgap Engineering         | 76 |

|     | 7.1    | Motivation                                        | 76 |

|     | 7.2    | Simulation Results                                | 77 |

| 8   | Conc   | clusions and recommendations                      | 79 |

|     | 8.1    | Conclusions                                       | 79 |

|     | 8.2    | Recommendations for future research               | 82 |

| Re  | ferenc | es                                                | 84 |

| Vit | a      |                                                   | 92 |

# **List of Figures**

| Figure 1-1: The lattice constant of SiGe is higher than that of Si. When Si is                                    |  |

|-------------------------------------------------------------------------------------------------------------------|--|

| grown epitaxially on SiGe, it stretches to conform to the atomic spacing                                          |  |

| of SiGe which puts it under biaxial tensile strain.                                                               |  |

| Figure 1-2: A cross-sectional electron micrograph of a strained Si transistor                                     |  |

| fabricated by UMC. The fabrication sequence used 130 nm node Si                                                   |  |

| technology, and the physical gate length for the transistor shown is 90                                           |  |

| nm. Credit: UMC. Image from www.compoundsemiconductor.net. 4                                                      |  |

| Figure 1-3: TEM micrograph of 45 nm p-type and n-type MOSFET.                                                     |  |

| Uniaxial stress is introduced in the channel, by either $Si_{1-\gamma}Ge_{\gamma}$                                |  |

| epitaxially grown source/drain or high stress overlayer film. Image                                               |  |

| from [Tho04]. 5                                                                                                   |  |

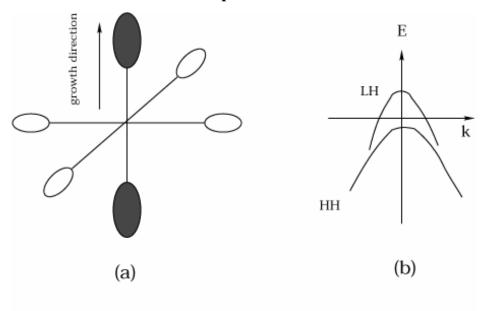

| Figure 2-1: (a) Schematic equi-energy surfaces of the six split valleys in the                                    |  |

| first conduction band in TS-Si. The minimum energies of the dark                                                  |  |

| valleys are lower than those of the open ellipsoids. (b) Schematic energy                                         |  |

| diagrams of heavy hole (HH) and light hole (LH) bands in TS-Si. 8                                                 |  |

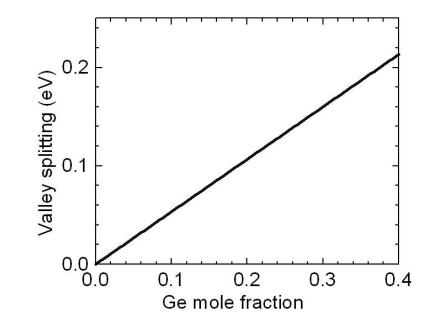

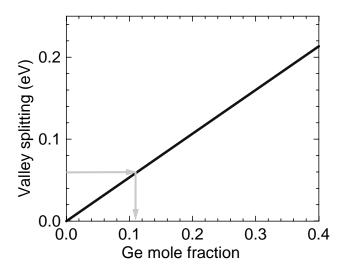

| Figure 2-2: $\Delta_2$ and $\Delta_4$ valley splitting vs. Ge mole fraction in $Si_{1-\gamma}Ge_{\gamma}$ buffer. |  |

| Note the essentially linear dependence. 9                                                                         |  |

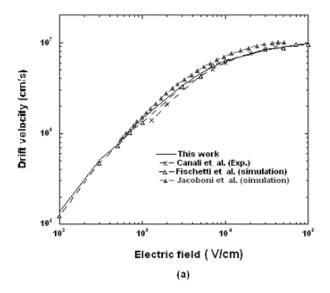

| Figure 2-3: Drift velocity of electrons in bulk Si as a function of electric field.                               |  |

| For comparison, the other measurements and simulation results are                                                 |  |

| also shown. [Jac83][Can75][Fis88] 11                                                                              |  |

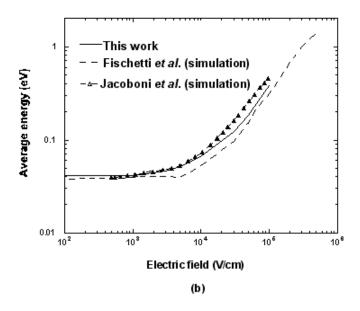

| Figure 2-4: Average energy of electrons in bulk Si as a function of electric                                      |  |

| field. For comparison, the other measurements and simulation results                                              |  |

| are also shown. [Jac83][Fis88]                                                                                    |  |

|                                                                                                                   |  |

| the saturation of mobility for increasing strain as the valley-splitting-                      |

|------------------------------------------------------------------------------------------------|

| induced transfer to the $\Delta_2$ valleys is completed for these low-energy                   |

| carriers. 12                                                                                   |

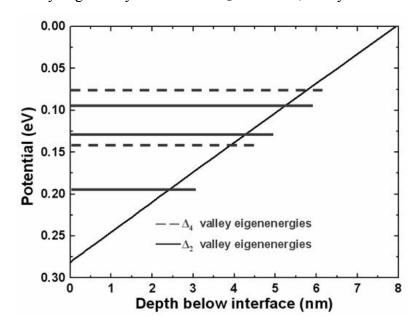

| Figure 2-6: Eigenvalues of the energy well for longitudinal and transverse                     |

| valleys 17                                                                                     |

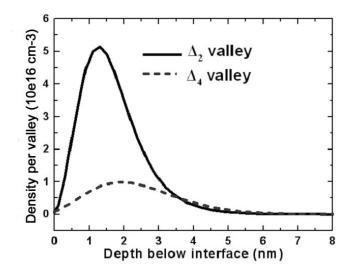

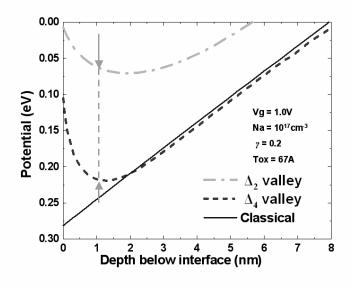

| Figure 2-7: Quantum mechanical electron distribution density per valley of                     |

| $\Delta_2$ and $\Delta_4$ valleys as a function of depth below interface. 18                   |

| Figure 2-8: Effects of quantum corrections alone on the $\Delta_2$ and $\Delta_4$ valley-      |

| minimum energies for unstrained Si exhibiting position dependent                               |

| additional valley splitting. 19                                                                |

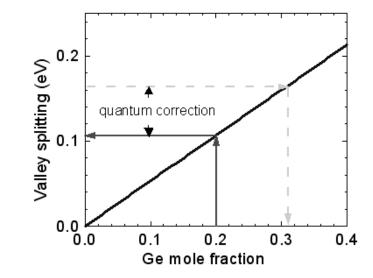

| Figure 2-9: An illustration of the calculation of the effective strain/mole                    |

| fraction $\gamma_{\it eff}$ (at one position) from the quantum-corrected valley-               |

| minimum splitting, using the strain vs. valley splitting results of Figure                     |

| 2-2.                                                                                           |

| Figure 2-10: Effects of both quantum correction and tensile strain on the $\Delta_2$           |

| and $\Delta_4$ valley-minimum energies for TSSi grown on $Si_{1-\gamma}Ge_{\gamma}$ buffer. 20 |

| Figure 2-11: An illustration of the calculation of the effective strain/mole                   |

| fraction $\gamma_{eff}$ (at one position) starting with the real strain-induced valley         |

| splitting and then adding quantum-correction induced valley splitting to                       |

| obtain a total valley splitting and corresponding new effective strain. 21                     |

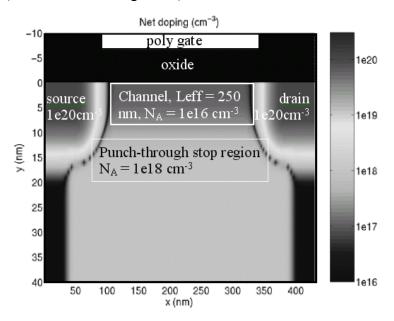

| Figure 2-12: 2D device doping profile. 23                                                      |

| Figure 2-13: Doping density along cross-section normal to gate at mid-                         |

| channel. 24                                                                                    |

|                                                                                                |

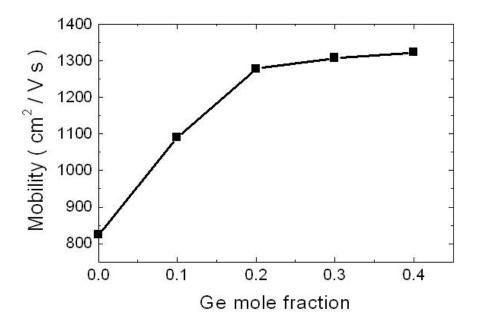

Figure 2-5: Low-field mobility vs. Ge mole fraction in  $Si_{1-x}Ge_x$  buffer. Note

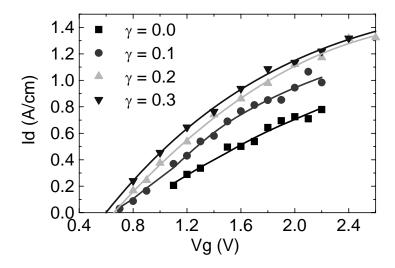

- Figure 2-14: Drain current vs. gate voltage vs. normal effective field in MOSFET with TSSi channel on relaxed  $Si_{I-\gamma}Ge_{\gamma}$  buffer.  $\gamma$  is the Ge mole fraction in the buffer layer such that  $\gamma=0$  denotes unstrained silicon.

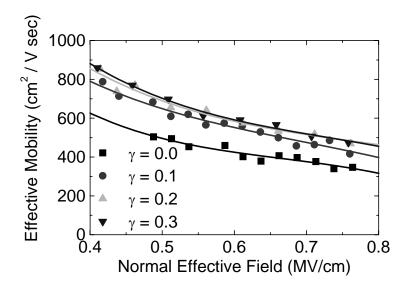

- Figure 2-15: Channel electron mobility vs. normal effective field in MOSFET with TSSi channel on relaxed  $Si_{1-\gamma}Ge_{\gamma}$  buffer.  $\gamma$  is the Ge mole fraction in the buffer layer such that  $\gamma=0$  denotes unstrained silicon. For TSSi with buffer of  $Si_{0.8}Ge_{0.2}$  and  $Si_{0.7}Ge_{0.3}$ , the mobility enhancements are very close as the carrier transfer to the  $\Delta_2$  valleys saturates.

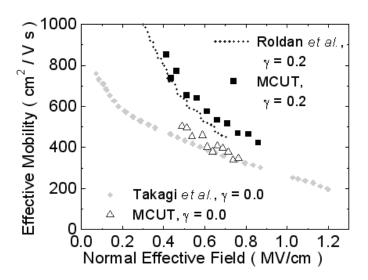

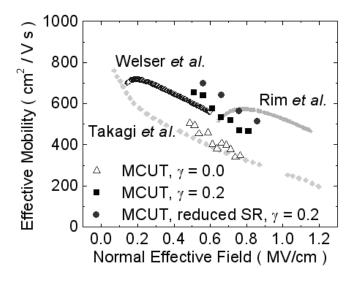

- Figure 2-16: Results of MCUT device simulation are compared with other simulation results [Rol96] and the universal mobility curve [Tag94].

Open triangles: MCUT MOSFET simulation on unstrained Si; solid squares: MCUT MOSFET simulation on TSSi.

- Figure 2-17: MCUT TSSi MOSFET (2D) simulations with and without a reduced rms amplitude of the Si/SiO<sub>2</sub> interface roughness are compared to experiment data [Wel94] [Rim00]. Unstrained Si universal mobility data [Tag94] are plotted as reference. Solid circle: MCUT TSSi MOSFET simulation with reduced surface roughness scattering rate; solid square: MCUT TSSi MOSFET simulation with fixed surface roughness scattering rate; open triangle: MCUT unstrained Si MOSFET simulation.

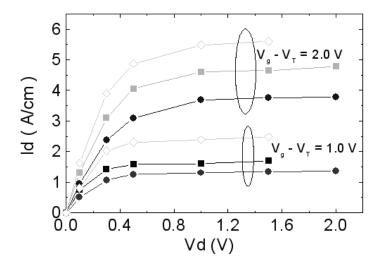

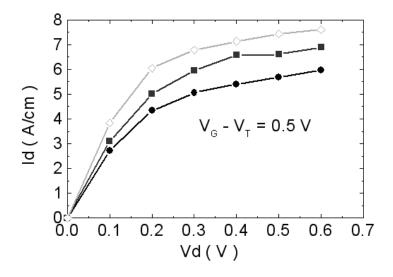

- Figure 2-18:  $I_d$ - $V_d$  curve. Drain currents as a function of drain voltage for nMOSFETs with TSSi ( $\gamma = 0.2$ ) channel and an unstrained Si ( $\gamma = 0.0$ ) channel. Closed circles: unstrained Si; closed squares: TSSi with

| fixed surface roughness parameters; open diamonds: TSSi with                      |

|-----------------------------------------------------------------------------------|

| reduced surface roughness scattering consistent with Figure 2-17. For             |

| the same $V_G - V_T$ , enhancement of the drive current is observed in the        |

| <i>TSSi.</i> 30                                                                   |

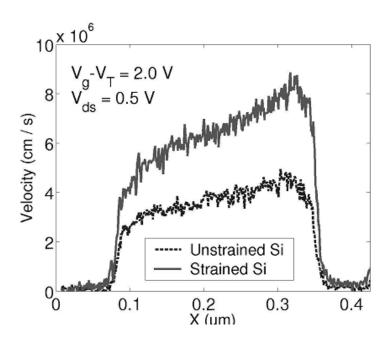

| Figure 2-19: Average carrier transport velocity along the channel for fixed       |

| $V_D$ and $V_G - V_T$ .                                                           |

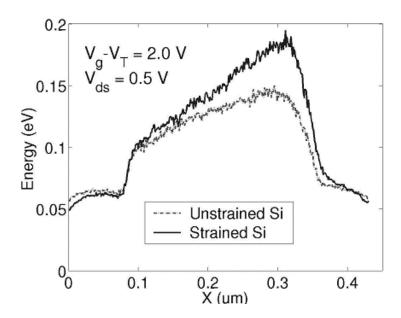

| Figure 2-20: Average carrier kinetic energy distribution along the channel        |

| for fixed $V_D$ and $V_G - V_T$ . Comparison is made between a TSSi               |

| channel with reduced surface roughness scattering and a relaxed Si                |

| channel. Increases are observed in both average energy and velocity               |

| within the channel for TSSi as compared to relaxed Si. 31                         |

| Figure 2-21: $I_d$ - $V_d$ curve for a 50 nm channel length well-tempered device  |

| after Ref. [Mit00]. Drain currents as a function of drain voltage for             |

| nMOSFETs with TSSi ( $\gamma=0.2$ ) channel and an unstrained Si ( $\gamma=0.0$ ) |

| channel. Closed circles: unstrained Si; closed squares: TSSi with                 |

| fixed surface roughness parameters; open diamonds: TSSi with                      |

| reduced surface roughness scattering consistent with Figure 2-17. For             |

| the same $V_G - V_T$ , ( $V_T$ 's are different in these three cases) enhancement |

| of the drive current is observed in the TSSi, although perhaps a bit less         |

| than the longer channel devices for this isolated example. 32                     |

| Figure 2-22: Channel surface doping in strained Si and bulk Si nMOSFETs.          |

| 35                                                                                |

| Figure 2-23: Average gate field in strained Si and bulk Si nMOSFETs. 35           |

| Figure 2-24: Energy splitting between A, and A, valleys in SSi and hulk Si        |

channels. 36

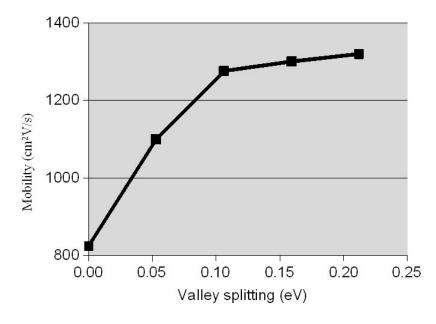

Figure 2-25: Low-field bulk mobility plotted as a function of energy splitting between  $\Delta_2$  and  $\Delta_4$  valleys.

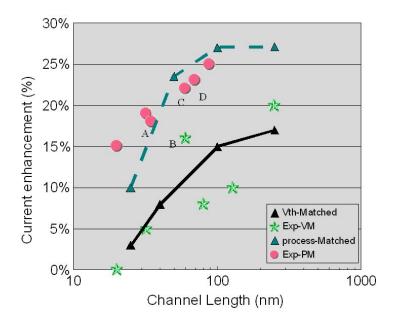

- Figure 2-26: Drain current comparison between Si and SSi nMOSFETs.

Lines represent MCUT simulations in "V<sub>T</sub>-matched" and "process-matched" conditions. Experimental results come from: a. Ref [Xia03], b. Ref [Rim02a], c. Ref [Lee02], d. Ref [Hwa03], the rest from Ref [Goo03].

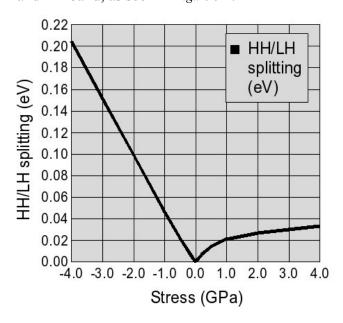

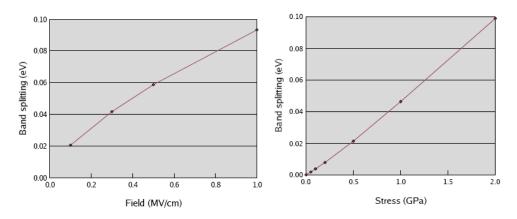

- Figure 3-1: Heavy hole and light hole band splitting in uniaxially-stressed Si.

Here and for subsequent figures the positive stress axis corresponds to tensile stress, and the negative stress axis to compressive stress.

41

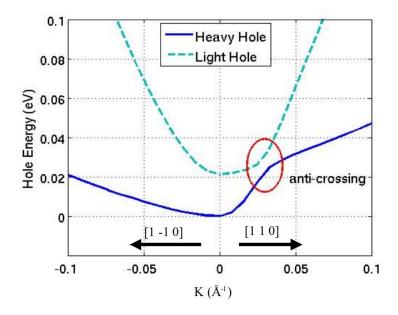

- Figure 3-2: Heavy-hole and light-hole energy-K dispersion in [110] and  $[1\overline{1}0]$  directions with compressive [110] uniaxial-stress of 500 MPa.43

- Figure 3-3: 2-D heavy-hole iso-energy contours (10 meV, 50 meV and 100 meV) for [110] uniaxially-stressed Si in the (001) plane with a compressive stress of 500 MPa in the [110] direction.

- Figure 3-4: Percentile change in the thermal average of the inverse effective mass in the [110] and [110] directions for [110] uniaxially-stressed Si as function of stress. The zero stress value is 2.79 times the reciprocal of the free space mass. For reference, the average inverse effective mass value in the [001] direction in unstrained Si is 2.80.

- Figure 3-5: Percentile change of the thermal velocity in the [110] and [110] directions for [110] uniaxially-stressed Si as function of stress. The

- unstrained Si thermal velocity is  $8.9 \times 10^6$  cm/s at room temperature. 46

Figure 3-6: Percentile change of the thermal average of inverse scattering rates (proportional to free flight time FFT) for [110] uniaxially-stressed Si as function of stress. The zero stress FFT (phonon scattering only) is ~0.15 ps at room temperature.

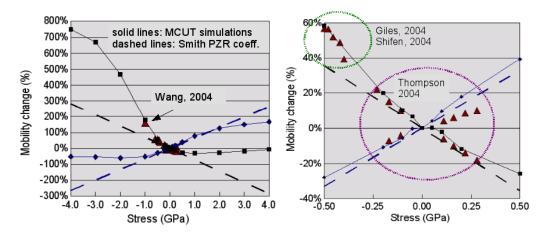

- Figure 3-7: Low field mobility of uniaxially-stressed Si vs. stress strength.

Dashed lines follow Smith's piezoresistance coefficient [Smi54].

Squares and diamonds plot MCUT bulk simulation results for transport parallel and perpendicular to stress directions, respectively.

Experimental results from [Gil04][Tho04][Shi04] and simulation results from [Wan04] are plotted as triangles for comparison. Results are shown on two scales with the lower stress region shown in detail in right hand side.

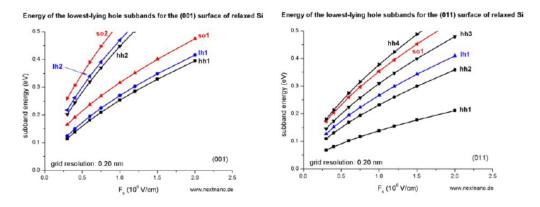

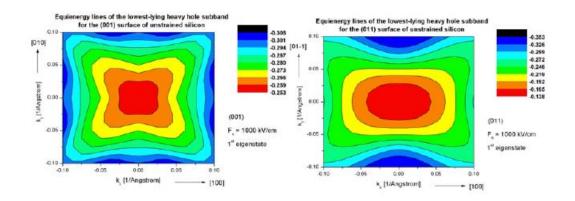

- Figure 4-1: The hole subband energy levels, as measured from the surface potential, formed in a triangular well in (left): (100) and (right): (110) surface orientations. The symbols are calculated value; the connecting lines only a guide to the eye.

- Figure 4-2: The first subband E-k dispersion in k<sub>//</sub> plane for (left): (100) and (right): (110) surface orientations separately.

- Figure 4-3: The first band E-k dispersion in  $k_{//}$  plane. (left) [100] uniaxial tensile stress, (100) plane; (right) [110] uniaxial tensile stress, (110) plane, spanned by [001] and  $\begin{bmatrix} 1 \ 1 \ 0 \end{bmatrix}$  axes.

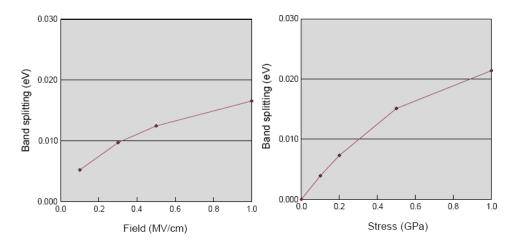

- Figure 4-4: Band splitting between the first and second hole bands induced by (left) [001] gate confinement field; and (right) [001] uniaxial stress.

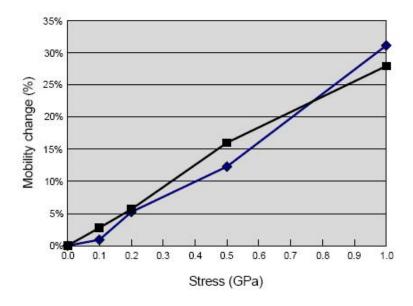

- Figure 4-5: [110] Hole transport mobility in [100] and [110] directions in (001) surface orientation. Curves show percentile change with [001] uniaxial tensile stress.

- Figure 4-6: Band splitting between the first and second hole bands induced by (left) [110] gate confinement field; and (right) [110] uniaxial stress.

60

- Figure 4-7: [110] transport mobility percentile change with [110] uniaxial stress.

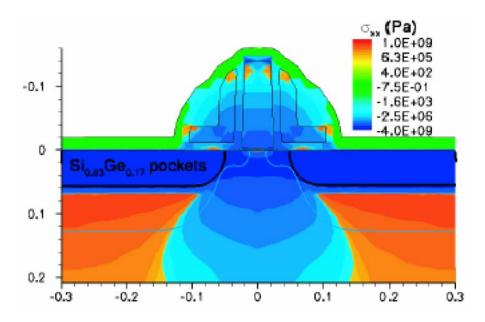

- Figure 5-1: Stress along the channel in a strained Si pMOS transistor, modeled by ISE04 [Ran05] 62

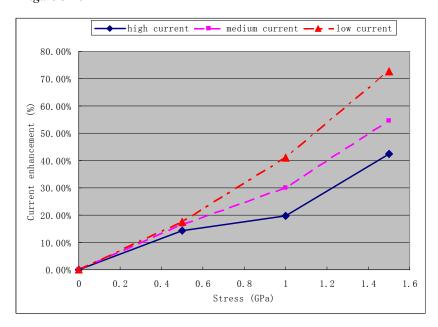

- Figure 5-2: Drain current enhancement as a function of channel maximum stress. "High current" simulation was achieved with gate bias -1.5 V and drain bias -0.5 V; "medium current" simulation was with gate bias -1.2 V and drain bias -0.2 V; and "low current" simulation was with gate bias of -1.2 V and drain bias -50 mV. Source and substrate were grounded.

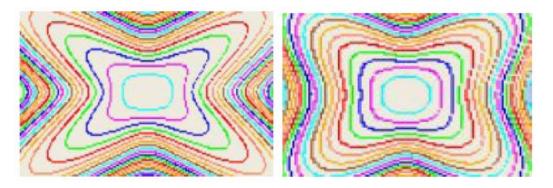

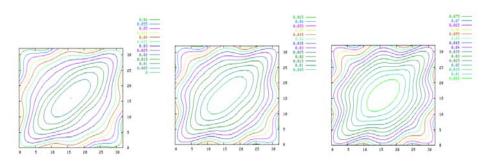

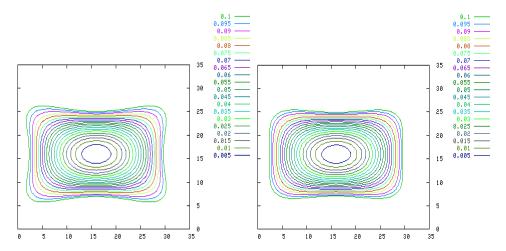

- Figure 5-3: 2-D energy contours of heavy-hole band (or in other term, first subband), for a [001] confinement field of 0.1 MV/cm, 0.5 MV/cm, and 1.0 MV/cm separately, from left to right, in energy separation of 5 meV, from band edge upto 100 meV. The range of k is from -0.1 Å<sup>-1</sup> to 0.1 Å<sup>-1</sup>. At different confinement field (0.1, 0.5 and 1.0 MV/cm), the band shape changes but a little.

- Figure 5-4: This plotting shows the above figure, the E-k dispersion, in

- [110] and [ $\overline{110}$ ] direction, with individual lines represent different [001] confinement fields of 0.1, 0.5 and 1.0 MV/cm. The range of k is from -0.1 Å<sup>-1</sup> to 0.1 Å<sup>-1</sup>, with energy unit in eV. The change is rather small, which implies that uniaxial stressed Si behaves similarly in strong confinement as in bulk.

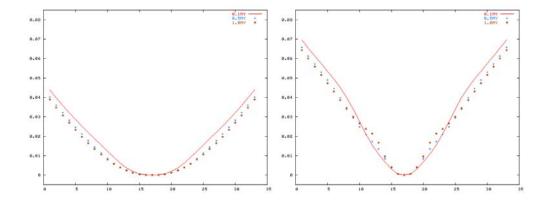

- Figure 5-5: Comparison between (110) orientation confinement effect and uniaxial stress effect. In the left hand side case, there is no stress; a field of 1.0 MV/cm is applied in gate (110) direction. In the right hand side, the confinement field is small 0.1 MV/cm, but a compressive uniaxial stress of 3.0 GPa is applied on transport direction. The contours show the first sub-band (heavy-hole) from band edge to 100 meV, in steps of 5 meV.

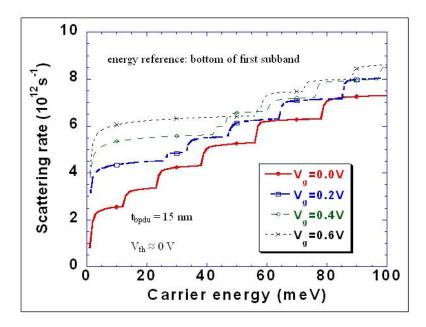

- Figure 6-1: Phonon scattering rates as function of carrier energy in confined channels. Scattering rates form steps with sub-band levels, while they increase with confinement.

- Figure 6-2: Replot scattering rates with energy reference fixed to bulk band edge at no confinement.

71

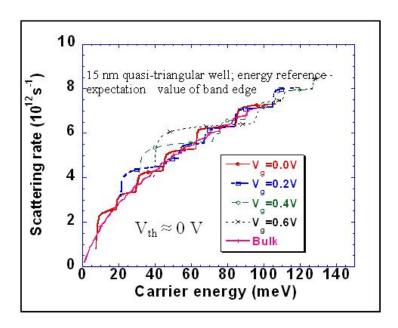

- Figure 6-3: With confinement, when valleys/bands become non-degenerate, intra- and inter-valley phonon scattering rates are function of "total energy", while some inter-valley scattering becomes energy-prohibited.

This effectively alternates valley/band concentration in simulations. 72

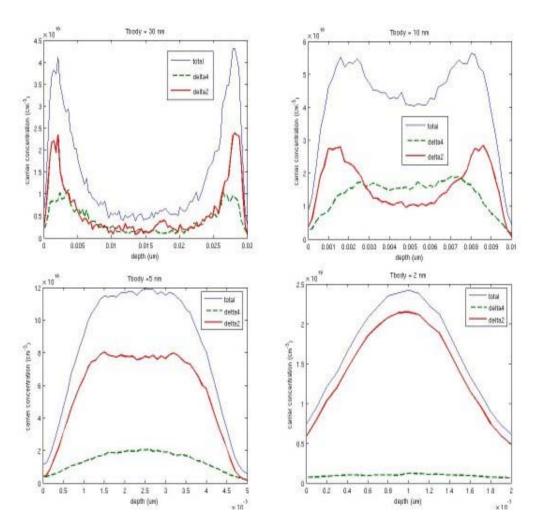

- Figure 6-4: Valley population in  $\Delta_2$  and  $\Delta_4$  valleys in Si dual gate MOSFET body.  $t_{body}$  shrinks from 30 nm down to 2 nm. The solid red lines represent  $\Delta_2$  valley concentration and the green dashed lines for  $\Delta_4$

| valleys. 74                                                                              |

|------------------------------------------------------------------------------------------|

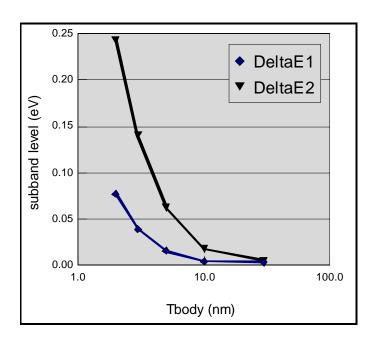

| Figure 6-5: $\Delta_2$ and $\Delta_4$ valley subband level in Si dual gate MOSFETs, with |

| the energy denoted by $\Delta E1$ and $\Delta E2$ . 75                                   |

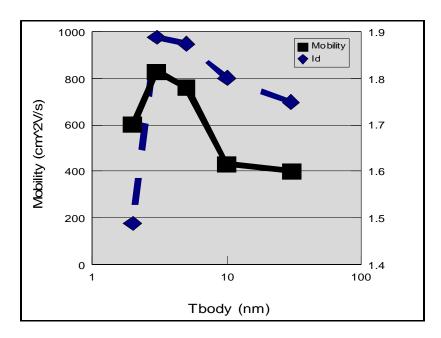

| Figure 6-6: Phonon-limited electron mobility in Si dual gate MOSFETs.                    |

| The confinement enhanced surface roughness scattering is not included                    |

| here. 75                                                                                 |

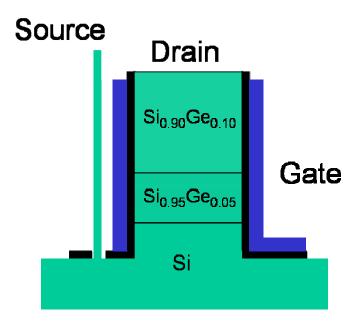

| Figure 7-1: Vertical pMOS structure with strained-SiGe grown on top of Si.               |

| Note the Ge mole fraction in SiGe forms steps from source to drain. 77                   |

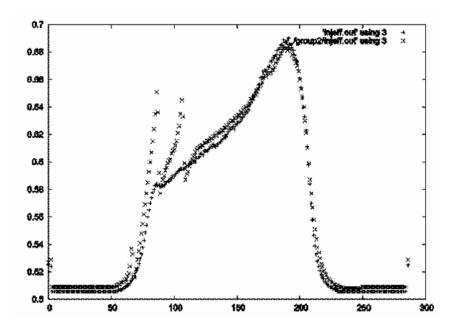

| Figure 7-2: Injection efficiency comparison between a device with Ge mole                |

| fraction steps and a control device. Note the peaks represent the Ge                     |

| mole fraction steps in channel. 78                                                       |

#### 1 Research Background

#### 1.1 Full-band Semiclassical Monte Carlo Simulation

The Monte Carlo method is a widely used stochastic approach for studying charge transport in semiconductors and semiconductor devices. It involves the simulation of the motion of charge carriers subject to a wide variety of scattering mechanisms and external forces. Although it requires appreciable computer resources, the simplicity of implementation and relatively complete description of semi-classical transport make the Monte Carlo method appealing for semiconductor simulation. It is the most accurate approach to treat transport at high fields and in short, non-classical devices. The Monte Carlo simulation consists of iterations of free flight, scattering-type selection and post-scattering momentum selection for an ensemble of particles. According to the band structure used in the Monte Carlo simulation of electron transport, there are three types of implementation. The most computationally efficient is a low-energy model using a single parabolic or non-parabolic band [Jac83] that is only applicable to those electrons with energy below 0.5 eV. The second class uses a hybrid model [Vog92] [Wan93] to reduce the computation time. The third class uses a full band structure [Fis88] [Fan04], which is the most time-consuming and has the least amount of parameter tuning. However, the high costs and risks of novel silicon technology development make it imperative to employ simulation [Jac83]. Among the existing classical device simulation methods, the full-band semiclassical Monte Carlo (below noted as "MC" for full-band semiclassical

Monte Carlo simulation) technique is more predictive and can provide a more complete understanding of carrier transport than drift-diffusion or hydrodynamic transport models [Jac83]. MC has the ability to accurately model the transport of high energy carriers and to consider non-local field effects such as ballistic transport and velocity overshoot that have become increasingly important as devices are scaled down below 0.1 µm channel lengths for production devices. MC also offers a combination of computational efficiency and ability for incorporation of diverse scattering processes not (yet at least) available in (full) quantum transport simulators. Semi-classical transport along the channel within sub-bands could be explicitly considered, as for the calculation of mobilities in [Fis02]. However, unlike for near-equilibrium channel mobility calculations, for far from equilibrium transport calculations the associated computational burden would be much greater still for re-calculating the transition rates among the quantum confined states defined by sub-band and interface parallel momentum for each position along the channel and each time step/iteration self consistently with the scattering-dependent charge distribution [Kri06]. Furthermore, again unlike for mobility calculations, device simulations must often be repeated for varying drain voltages. And the extension for hot-carrier transport would still be questionable. Therefore, the exploration of future MOSFET designs demands, or at least would greatly benefit from, a full-band semiclassical MC simulation tool capable of — in addition to the many capabilities of conventional full-band MC — considering multi-material systems and the *combined* effects of strain and quantum confinement on degeneracy breaking among energy valleys, spatial charge re-distribution and the associated effects on transport.

## 1.2 Strained Materials for Semiconductor Devices

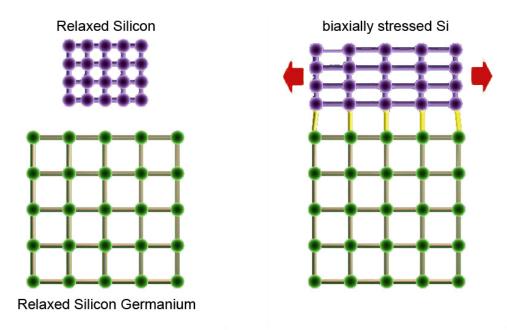

Strain and bandgap engineering of strained materials has emerged as an important technique for improving the device performance due to impediments to conventional scaling method. For example, Tensile-strained silicon (TSSi) on a relaxed SiGe buffer (*Figure 1-1*) has been studied extensively because of its enhanced electron and hole mobility which makes it a good candidate for n and p MOSFETs [Mii91] [Nel93] (*Figure 1-2*).

Figure 1-1: The lattice constant of SiGe is higher than that of Si. When Si is grown epitaxially on SiGe, it stretches to conform to the atomic spacing of SiGe which puts it under biaxial tensile strain.

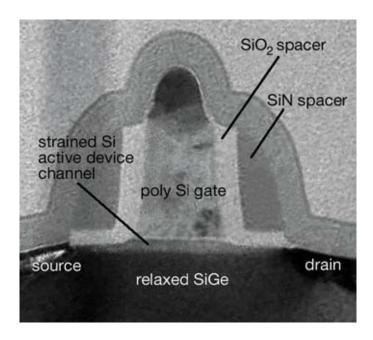

Figure 1-2: A cross-sectional electron micrograph of a strained Si transistor fabricated by UMC. The fabrication sequence used 130 nm node Si technology, and the physical gate length for the transistor shown is 90 nm. Credit: UMC. Image from www.compoundsemiconductor.net.

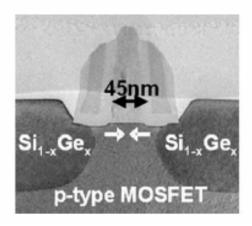

Recent experimental and theoretical work points to uniaxially-stressed Si as a possible channel material for next generation CMOS [Tho05] (*Figure 1-3*). Experimentally, uniaxial compressive stress has been applied to the channel area via source/drain hetero-epitaxial deposition of SiGe [Tho04, Gha03, Chia04], or by tensile/compressive capping layers on top of the gate [Arg04], while four-point or ring wafer bending is the main technique for quantitatively experimentally measuring piezoresistance [Bea92]. Greater than 50% stress-induced hole channel mobility improvement and 10% to 25% drain current enhancement has been demonstrated in strained Si devices for stress ranging from 100 to 500 MPa. Furthermore, although the hole mobility is often modeled as depending linearly on stress according to tabulated piezoresistance coefficients such as those of Ref. [Smi54], recent works have exhibited superlinear relationships between bulk

mobility and stress [Shi04, Wan04] suggesting even greater potential advantages in the high stress regime.

Figure 1-3: TEM micrograph of 45 nm p-type and n-type MOSFET. Uniaxial stress is introduced in the channel, by either  $Si_{1-\gamma}Ge_{\gamma}$  epitaxially grown source/drain or high stress overlayer film. Image from [Tho04].

### 1.3 Quantum Correction in Semiclassical Monte Carlo Method

The MC methods used in this PhD research is a full-band Monte Carlo plus gate-directional quantum correction. The quantum correction is based on one-dimensional effective mass Schrödinger equation solved in the gate direction in all positions through the device. The combined Poisson's equation and Schrödinger's equation provide (real and virtual) driving electrostatic forces. The quantum confinement in inversion layers of a MOSFET is of special importance. Based on this established method, new features were added for situations encountered in non-classical CMOS device simulations. Details of these quantum correction methods in this MC research will be discussed in following sections.

### 1.4 Monte Carlo at the University of Texas (MCUT)

The device simulation group led by Dr. Banerjee and Dr. Register in the Microelectronics Research Center of The University of Texas at Austin has developed a MC tool named "Monte Carlo at the University of Texas" (MCUT). This code borrows the robust framework of the University of Illinois Urbana-Champaign code MoCa [Win01] [Win03], and adds the vast and varied physics necessary to treat strain and valley-dependent quantum confinement to achieve the combined effects of quantum confinement and strain within a full-band structure treatment. The code provides simulation capability for both electrons and holes devices, and for both conventional devices and "non-classical" CMOS devices such as FinFETs. The following sections will focus on MUCT simulations on biaxially stressed Si nMOS, uniaxially stressed Si pMOS, and SiGe concept vertical pMOS. The enhanced features and capabilities of MCUT are covered in each section when they are applied to the simulations.

#### 2 Tensily Biaxially stressed Si nMOS

#### 2.1 Motivation

The advantages of biaxially tensile-stressed Si (TSSi), as achieved by growing strained Si on relaxed SiGe, have been briefly described in Section 1.2. It is argued that the electron mobility enhancement is due to the strain-induced splitting of the six-fold degeneracy of silicon conduction band minima; while the hole mobility enhancement is from the splitting of heavy-hole and light-hole energy bands [Obe98] (Figure 2-1). The strain-induced degeneracy breaking in the electron band structure of the TSSi that has been well characterized [Wan01] as shown in Figure 2-2. In particular, the six lowest,  $\Delta$  energy valleys in the conduction band separate into two groups: two valleys with the valley centers  $\mathbf{k}_l$ perpendicular to the plane of the silicon/oxide interface and to the direction of transport, (in other words,  $\mathbf{k}_l$  is parallel to the strained-Si growth direction)  $l=\Delta_2$ , and four higher energy in-plane valleys,  $l=\Delta_4$ . The strain-dependent energy difference  $E^{(\gamma)}(\mathbf{k}_{\Delta 4}) - E^{(\gamma)}(\mathbf{k}_{\Delta 2})$  leads to segregation of low energy carriers toward the  $\Delta_2$  valleys that have the lower Si "transverse" effective mass (of  $\sim 0.19 \ m_e$ ) in the direction of transport. This energy difference also reduces the densities of final states for low energy carriers, reducing the scattering rates accordingly [Wan93] [Wan01]. The mobility/drain current enhancement has been reported to be in the range of 50% to 110%, subject to different channel lengths, strain strength, and other device fabrication conditions [Wel94] [Rim98] [Rim02] [Hoy02]. Analyzing these experimental results, it should be noted that channel

length (thus short channel effect and hot carriers) and device structure played important roles, making the MC method preferable to mobility calculations based on effective mass or more accurate  $\mathbf{k} \cdot \mathbf{p}$  sub-band structure.

Figure 2-1: (a) Schematic equi-energy surfaces of the six split valleys in the first conduction band in TS-Si. The minimum energies of the dark valleys are lower than those of the open ellipsoids. (b) Schematic energy diagrams of heavy hole (HH) and light hole (LH) bands in TS-Si.

Figure 2-2:  $\Delta_2$  and  $\Delta_4$  valley splitting vs. Ge mole fraction in  $Si_{1-\gamma}Ge_{\gamma}$  buffer. Note the essentially linear dependence.

## 2.2 Strain Effects

The electron band structure of TSSi on a relaxed  $Si_{1-x}Ge_x$  substrate is calculated by the empirical pseudo-potential method (EPM) [Fri89] as a function of the substrate Ge mole fraction x. Acoustic and optical phonon scattering rate tables are calculated based on this full-band structure via Fermi's Golden Rule [Wan93]. *Figure 2-4* illustrates the agreement between our theoretical work, and the experimental and theoretical work of others for bulk unstrained Si [Jac83][Can75][Fis88]; *Figure 2-5*, the effects of strain on bulk mobility. In addition to phonon scattering in these device simulations, screened Coulomb scattering by impurities and surface roughness scattering are considered. The coupling potentials for the various phonon scattering processes were tuned by

matching the velocity and energy vs. driving electric field curve for unstrained bulk Si, and then the coupling parameters for surface roughness scattering [Rav00] were adjusted to match universal mobility data as a function of interface-normal effective field  $E_{eff}(x) = \int E_y(x, y) n(x, y) dy / \int n(x, y) dy$  for unstrained Si [Tag94]. As pointed out by Fischetti and Laux [Fis96], in strained silicon, inplane and out-of-plane valleys only differ by an energy shift approximately; the valley shape remains the same. We then follow the approximation that the same phonon coupling potentials can be used for strained silicon device simulation; this approximation is also used by Oberhuber et al. [Obe98] in treatment of the strained silicon valence band. The scattering rates, themselves, however change with the band structure and the availability of final states. We implement the surface roughness scattering mechanism following Goodnick's model [Goo85] with surface roughness rms value and correlation length tuned to fit universal mobility data. In strained silicon, both the case where the surface roughness parameters are held constant and, consistent with work of Ref. [Fis02], where surface roughness coupling parameters for strained Si are reduced are simulated. The band structure and the various band-structure dependent quantities are calculated with a resolution in the substrate germanium content  $\Delta x = 0.05$  (5%) over the range of 0.0 to 0.45. For intermediate values of mole fraction, a quadratic interpolation scheme is used.

Captured in these calculations is the strain-induced degeneracy breaking in the electron band structure of the TSSi that has been well characterized [Wan02] (Fig. 3). In particular, the six lowest  $\Delta$  energy valleys in the conduction band separate into two groups: two valleys with the valley centers  $\mathbf{k}_l$  perpendicular to the plane

of the silicon/oxide interface and to the direction of transport, (in other words,  $\mathbf{k}_l$  is parallel to the strained-Si growth direction)  $l=\Delta_2$ , and four higher energy inplane valleys,  $l=\Delta_4$ . The strain-dependent energy difference  $E^{(\gamma)}(\mathbf{k}_{\Delta 4}) - E^{(\gamma)}(\mathbf{k}_{\Delta 2})$  leads to segregation of low energy carriers toward the  $\Delta_2$  valleys that have the lower Si "transverse" effective mass (of ~0.19  $m_e$ ) in the direction of transport. This energy difference also reduces the densities of final states for low energy carriers, reducing the scattering rates accordingly [Wan93][Wan02].

Figure 2-3: Drift velocity of electrons in bulk Si as a function of electric field. For comparison, the other measurements and simulation results are also shown. [Jac83][Can75][Fis88]

Figure 2-4: Average energy of electrons in bulk Si as a function of electric field. For comparison, the other measurements and simulation results are also shown. [Jac83][Fis88]

Figure 2-5: Low-field mobility vs. Ge mole fraction in  $Si_{l-x}Ge_x$  buffer. Note the saturation of mobility for increasing strain as the valley-splitting-induced transfer to the  $\Delta_2$  valleys is completed for these low-energy carriers.

### 2.3 Valley-edge Quantum Corrections

In MOSFETs, perpendicular to the interface of silicon channel and gate oxide, size quantization in the inversion layer is important in at least two well known respects: decreased capacitive coupling of the channel to the gate and degeneracy breaking among the  $\Delta$  valleys. The inversion layer exists in a narrow energy well for carriers that results in the formation of sub-bands. A resulting shift of the charge probability density of these quantum-confined states away from the Si/oxide (SiO<sub>2</sub> or otherwise) interface leads to the decreased capacitive coupling of the channel to the gate. Due to the differences in interface-normal effective masses, the lower interface-perpendicular mass in-plane  $\Delta_4$  valleys have larger quantum confinement/sub-band energies breaking the degeneracy between the inplane  $\Delta_4$  valleys and the out-of-plane  $\Delta_2$  valleys even in the absence of strain. With tensile strain, lower energy electrons are partially segregated toward the  $\Delta_2$ valleys and inter-valley scattering for these low energy carriers is reduced. In MCUT a "quantum-corrected" position and strain-dependent band structure  $E^{(\gamma)}_{qc}(\mathbf{k},x,z)$  is used to approximate these two effects, and only these two effects, of quantum confinement within the channel within this otherwise semiclassical approach.

The procedure for calculating the *valley-edge* quantum corrections in MCUT is that of [Win03], with advantages and limitations described therein, except that the valleys are considered separately. Let  $E^{(\gamma)}(\mathbf{k},x,z)$  be the actual/uncorrected zero-field (flat-band neglecting material gradients) band structure as a function of position normal to the interface (z) including the band discontinuity at the

Si/oxide interface, and, potentially, in graded systems, position along the channel (x). Consider first the  $\Delta$  valley centers  $\mathbf{k}_l$ ,  $l = \Delta_2$ ,  $\Delta_4$ . At the beginning of each time step in the simulation, for each valley and for each position (grid point) along the channel (x-direction), the one-dimensional effective-mass Schrödinger's equation normal to the interface

$$-\frac{\hbar^{2}}{2}\frac{\partial}{\partial z}\left(\frac{1}{m_{z,l}(x,z)}\frac{\partial}{\partial z}\psi_{l,i}^{(\gamma)}(x,z)\right) + \left[E^{(\gamma)}(\mathbf{k}_{l},x,z) + \left(-e\right)V(x,z)\right]\psi_{l,i}^{(\gamma)}(x,z) = E_{l,i}^{(\gamma)}(x)\psi_{l,i}^{(\gamma)}(x,z)$$

(2-1)

is solved to obtain the quantum-confined eigenstates i,  $\psi^{(\gamma)}_{l,i}(x,z)$ , where V(x,z) is the electrostatic potential (in units of energy/charge), as per the example of *Figure 2-7*. Within a Boltzmann approximation, an equilibrium quantum mechanical electron density  $n_{qc,l}^{(eq,\gamma)}(x,z)$  is then calculated *independently for each valley* from the quantum confined states,

$$n_{qc,l}^{(eq,\gamma)}(x,z) = \sum_{i} \left| \psi_{l,i}^{(\gamma)}(x,z) \right|^{2} \int_{0}^{\infty} g_{2D}(E_{//}) \exp \left[ -\frac{E_{//} + E_{l,i}^{(\gamma)}(x) - E_{F}(x)}{k_{B}T} \right] dE_{//}$$

$$= \sum_{i} \left| \psi_{l,i}^{(\gamma)}(x,z) \right|^{2} \frac{m_{l,x}^{1/2} m_{l,y}^{1/2}}{\pi \hbar^{2}} k_{B}T \exp \left[ -\frac{E_{l,i}^{(\gamma)}(x) - E_{F}(x)}{k_{B}T} \right]$$

as per *Figure 2-8*. Boltzmann statistics are used for the calculation of the quantum corrections for reasons discussed in Ref. [Win03], and to be consistent with the Boltzmann statistics approached in the Monte Carlo simulation as a result of

(2-2)

scattering without consideration of final state occupancies and, thus, Pauli exclusion. (If the basic Monte Carlo method were improved to better reflect Pauli exclusion effects and the limit of Fermi statistics, then including Fermi statistics within the quantum correction should not then pose a prohibitive additional problem.) The "quantum-corrected" band structure  $E^{(\gamma)}_{qc}(\mathbf{k},x,z)$  is then *defined* to produce the same position-dependent *local* equilibrium electron densities

$$n_{qc,l}^{(eq,\gamma)}(x,z) \equiv N_l(x,z,T) \exp\left[-\frac{E_{qc}^{(\gamma)}(\mathbf{k}_l,x,z) - eV(x,z) - E_F(x)}{k_B T}\right]$$

(2-3)

where  $N_l$  is the effective density of states per valley (which is essentially valley independent except under large strain; here the l subscript is just a reminder that this is the per-valley effective density of states rather than that of the conduction band as a whole). Equation (2-3) can then be compared to the classical equilibrium electron concentration  $n_{cl,l}(x,z)$

$$n_{cl,l}^{(eq,\gamma)}(x,z) \equiv N_l(x,z,T) \exp \left[ -\frac{E^{(\gamma)}(\mathbf{k}_l,x,z) - eV(x,z) - E_F(x)}{k_B T} \right]$$

(2-4)

to obtain the valley and position-dependent quantum corrections

$$E_{qc}^{(\gamma)}(\mathbf{k}_{l},x,z) - E^{(\gamma)}(\mathbf{k}_{l},x,z) = k_{B}T \ln \left[ \frac{n_{cl,l}^{(eq,\gamma)}(x,z)}{n_{qc,l}^{(eq,\gamma)}(x,z)} \right]$$

(2-5)

where the choice of  $E_F$  for calculation of these equilibrium carrier concentrations is irrelevant. (In practice we simply choose  $E_F \equiv 0$  eV in our energy reference to obtain

$$E_{qc}^{(\gamma)}(\mathbf{k}_{l}, x, z) - eV(x, y) = k_{B}T \ln \left[ \frac{N_{l}(x, z)}{n_{qc, l}^{(eq, \gamma)}(x, z) \Big|_{E_{F}=0}} \right]$$

(2-6)

directly from Equation (2-4), avoiding the need to actually calculate  $n_{cl,l}^{(eq,\gamma)}(x,z)$ ; Equation (2-5) is for clarity of concept.) The *electrons within the Monte Carlo ensemble* with accompanying distribution function  $n_{MC}(x,z)$  are then moved subject to the quantum-corrected full-band structure  $E^{(\gamma)}_{qc}(\mathbf{k},x,z)$ —where the quantum-corrected *full*-band structure and the movement of carriers therein will be considered momentarily. At the beginning of the next time step a new electrostatic potential V(x,z) to be used in Equation (2-1) is calculated from the new ensemble Monte Carlo distribution  $n_{MC}(x,z)$ ,

$$\nabla \cdot [\varepsilon \nabla V(x,z)] = -e[-n_{MC}(x,z) + N_D^+(x,z) - N_A^-(x,z)], \quad (2-7)$$

so that the space and time-dependent quantum corrections are calculated self-consistently with the ensemble Monte Carlo distribution of carriers, as described in detail in the "flow chart" section to follow. The carrier temperature T in the above calculations could also be obtained approximately as a function of position from the Monte Carlo carrier ensemble as in Ref. [Win03], but this was not done for the examples in the illustrative work later. This procedure for calculating the band-edge quantum corrections is that of Ref. [Win03] except that the valleys are considered separately. This real-space and now valley-dependent quantum

correction addresses the reduced capacitive coupling of the channel to the gate as before, and now also the quantum-confinement-induced lifting of the energy valley degeneracy between the  $\Delta_2$  and the  $\Delta_4$  valleys.

Figure 2-6: Eigenvalues of the energy well for longitudinal and transverse valleys

Figure 2-7: Quantum mechanical electron distribution density per valley of  $\Delta_2$  and  $\Delta_4$  valleys as a function of depth below interface.

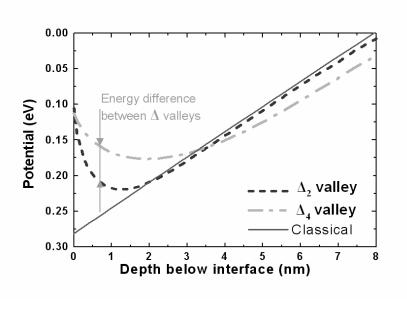

## 2.4 Full-band Quantum Corrections via "Effective Strain"

The above quantum corrections are, of course, only well defined and physically reasonable for near-valley center states. Near the drain, however, a significant fraction of carriers can be expected to occupy high-energy states. What the quantum corrections for such states far from the valley centers should be is not clear and certainly not available through an effective mass approximation. What they are also is likely of little physical consequence; for these latter energetic states the relative degree of and effects of quantum confinement are significantly reduced. Still, there must be some interpolation/extrapolation process for the quantum-corrected band structure from the valley centers to the rest of the Brillouin zone in order to run a full-band Monte Carlo. Furthermore, the scattering rates will vary, particularly for low-energy carriers, as a function of the quantum-confinement-induced valley splitting. In this work we take advantage of the similarity of the effect of strain and the quantum corrections on the band structure—noting that the strain has little effect on the effective masses [Fis96]—to address both of the above quantum-correction-related issues via the definition of an "effective strain" or as it is actually calculated, a positiondependent substrate Ge "effective mole fraction"  $\gamma_{eff}(x,z)$ . For example, if there is no actual strain, the substrate mole fraction  $\gamma(x,z)$  that would produce valleysplitting equal to  $E_{qc}(\mathbf{k}_{\Delta 4},x,z) - E_{qc}(\mathbf{k}_{\Delta 2},x,z)$  through strain is simply chosen as the effective mole fraction  $\gamma_{eff}(x,z)$ , as per Figure 2-9. If the channel material is actually strained ( $\gamma \neq 0$ ), the quantum-confinement-induced valley splitting is

simply added to the strain-induced valley splitting, and then this total splitting is translated back to the effective strain, as per *Figure 2-11*. In either case, the quantum corrected band-structure used in the Monte Carlo simulations becomes simply

$$E_{qc}^{(\gamma)}(\mathbf{k}, x, z) = E_{qc}^{(\gamma)}(\mathbf{k}_{\Delta_2}, x, z) + [E^{[\gamma_{eff}(x, z)]}(\mathbf{k}, x, z) - E^{[\gamma_{eff}(x, z)]}(\mathbf{k}_{\Delta_2}, x, z)]$$

(2-8)

that smoothly interpolates between the valley-centered quantum corrections calculated above. Furthermore, scattering rates and other simulation requirements, including some to follow, need only be calculated as a function of (effective) strain, not strain and degree of quantum confinement.

Figure 2-8: Effects of quantum corrections alone on the  $\Delta_2$  and  $\Delta_4$  valley-minimum energies for unstrained Si exhibiting position dependent additional valley splitting.

Figure 2-9: An illustration of the calculation of the effective strain/mole fraction  $\gamma_{\text{eff}}$  (at one position) from the quantum-corrected valley-minimum splitting, using the strain vs. valley splitting results of Figure 2-2.

Figure 2-10: Effects of both quantum correction and tensile strain on the  $\Delta_2$  and  $\Delta_4$  valley-minimum energies for TSSi grown on  $Si_{1-\gamma}Ge_{\gamma}$  buffer.

Figure 2-11: An illustration of the calculation of the effective strain/mole fraction  $\gamma_{eff}$  (at one position) starting with the real strain-induced valley splitting and then adding quantum-correction induced valley splitting to obtain a total valley splitting and corresponding new effective strain.

# 2.5 Transport within a Spatially-varying Band Structure

The particle motion in real space and **k**-space between scattering events are then calculated from, respectively,

$$\frac{d\vec{r}}{dt} = \frac{1}{\hbar} \left[ \nabla_{\mathbf{k}} E^{(\gamma)}(\mathbf{k}) \right]_{\gamma = \gamma_{eff}(x,z)}$$

(2-9)

and

$$\hbar \frac{d\mathbf{k}}{dt} = e \nabla_{\mathbf{r}} V(x, z) - \nabla_{\mathbf{r}} E_{qc}^{[\gamma_{eff}(x, z)]}(\mathbf{k}, x, z)$$

(2-10)

or, as the latter equation is actually calculated, from equation (2-8) and the chain rule of calculus,

$$\hbar \frac{d\mathbf{k}}{dt} = e \nabla_{\mathbf{r}} V(x, z) - \nabla_{\mathbf{r}} E_{qc}^{[\gamma_{eff}(x, z)]}(\mathbf{k}_{\Delta_{2}}, x, z)$$

$$- \nabla_{\mathbf{r}} \gamma_{eff}(x, z) \left\{ \frac{\partial}{\partial \gamma} [E^{(\gamma)}(\mathbf{k}) - E^{(\gamma)}(\mathbf{k}_{\Delta_{2}})] \right\}_{\gamma = \gamma_{eff}(x, z)}$$

(2-11)

The term in  $\nabla_{\bf k}$  on the right-hand-side of equation (2-9) and the position-independent term in  $\partial/\partial\gamma$  on the right-hand side of equation (2-11) are pretabulated as a function of  $\gamma$  and  ${\bf k}$  when the strained band structures are calculated. It should be noted that anytime the band structure changes with position, due to quantum corrections as here or simply due to variation in the material and/or strain, consideration of the  ${\bf k}$ -dependent gradient of the band structure with respect to position is necessary; it is the gradient with  ${\bf r}$  of the band structure at and only at the electrons location in  ${\bf k}$ -space, along with that of the external potential -eV(x,z), that produces the electron's crystal momentum change through energy conservation requirements, as per equation (2-10).

### 2.6 Model Devices

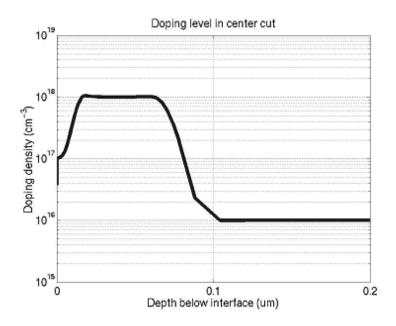

For the MOSFET simulations we consider two 0.25  $\mu$ m channel length nMOSFETs, one with a relaxed Si channel and the other with a TSSi channel corresponding to growth on a relaxed Si<sub>0.8</sub>Ge<sub>0.2</sub> buffer. These relatively long channel MOSFETs allow a good estimation of the channel electron mobility, which can be compared to the experiments of Rim *et al.*'s [Rim00]. As shown in *Figure 2-13*, the MOSFET has 67 Å oxide thickness, 130 Å thick p-type strained silicon channel with  $1\times10^{17}$  cm<sup>-3</sup> acceptor doping, and a 750 Å anti-punch-

through region underneath of  $1\times10^{18}$  cm<sup>-3</sup> acceptor doping. The n<sup>+</sup> source/drain is implanted in the strained silicon, and is chosen to be a Gaussian distribution with peak density of  $1\times10^{20}$  cm<sup>-3</sup>. However, the simulator is capable of handling experimental or simulated doping profiles. The polysilicon gate length is 0.25  $\mu$ m and doping is  $3\times10^{20}$  cm<sup>-3</sup> (*Figure 2-13*). In the strained device, because the inversion layer is within the TSSi, we neglect the Si<sub>0.8</sub>Ge<sub>0.2</sub> buffer in transport simulation (but not the resulting strain).

Figure 2-12: 2D device doping profile.

Figure 2-13: Doping density along cross-section normal to gate at mid-channel.

## 2.7 Mobility Calculations

To obtain low field electron mobility, a small drain-to-source voltage (0.1 V) was applied and gate voltage varied from 0.5 V to 2.4 V to vary the normal effective field. The channel mobility for the simulated devices is calculated as follows: At any point in the channel, neglecting small diffusive contributions, drive current is the product of channel mobility  $\mu$ , sheet charge density Q and driving field.

$$I = \mu \cdot Q(x) \cdot \left(-\frac{dV}{dx}\right). \tag{2-12}$$

Equation (2-12) can be rewritten as

$$\frac{-I}{O(x)}dx = \mu dV, \qquad (2-13)$$

and, assuming constant channel mobility, integrated from source to drain to obtain

$$\mu = \frac{(-I) \cdot \int \frac{1}{Q(x)} dx}{V_{DS}}.$$

(2-14)

Though mobility in the source/drain area is not equal to channel mobility, since carrier density Q(x) is much higher in source/drain region than in the channel, the channel region dominates the calculation of mobility and provides a reasonable estimate of average channel mobility.

Figure 2-14 and Figure 2-15 show the simulated drain current and associated calculated mobility as a function of gate voltage and corresponding effective field normal to the interface. Note that the mobility saturates as expected as a function of strain once the transfer of these, for mobility measurements, inherently low energy carriers to the  $\Delta_2$  valleys is essentially complete. Figure 2-16 and Figure 2-17 show calculated mobilities as a function of oxide-normal effective field for no strain ( $\gamma = 0$ ) and  $\gamma = 0.2$ , as well as relevant experimental results for comparison [Tag94][Rim00][Wel94]. Note that the MC simulations for fixed surface roughness scattering parameters apparently underestimate the actual increase in the channel mobility. Fischetti et al. [Fis02] have performed more rigorous calculations of channel mobility (calculation of which is a boundary condition of MCUT, not a goal) and indicate that the strain- and quantum-induced symmetry-breaking and the resulting reduction in conductivity effective mass and scattering rates alone is not sufficient to explain the experimentally obtained increase in mobilities in TSSi channels; they suggest a fortuitous decrease in the surface roughness scattering. Accordingly, to achieve better agreement with the experimental results we have reduced that of the surface

roughness coupling potential (rms roughness value) by 44% in this work to achieve better agreement as also shown in *Figure 2-17*.

Figure 2-14: Drain current vs. gate voltage vs. normal effective field in MOSFET with TSSi channel on relaxed  $Si_{1-\gamma}Ge_{\gamma}$  buffer.  $\gamma$  is the Ge mole fraction in the buffer layer such that  $\gamma=0$  denotes unstrained silicon.

Figure 2-15: Channel electron mobility vs. normal effective field in MOSFET with TSSi channel on relaxed  $Si_{1-\gamma}Ge_{\gamma}$  buffer.  $\gamma$  is the Ge mole fraction in the buffer layer such that  $\gamma=0$  denotes unstrained silicon. For TSSi with buffer of  $Si_{0.8}Ge_{0.2}$  and  $Si_{0.7}Ge_{0.3}$ , the mobility enhancements are very close as the carrier transfer to the  $\Delta_2$  valleys saturates.

Figure 2-16: Results of MCUT device simulation are compared with other simulation results [Rol96] and the universal mobility curve [Tag94]. Open triangles: MCUT MOSFET simulation on unstrained Si; solid squares: MCUT MOSFET simulation on TSSi.

Figure 2-17: MCUT TSSi MOSFET (2D) simulations with and without a reduced rms amplitude of the Si/SiO<sub>2</sub> interface roughness are compared to experiment data [Wel94][Rim00]. Unstrained Si universal mobility data [Tag94] are plotted as reference. Solid circle: MCUT TSSi MOSFET simulation with reduced surface roughness scattering rate; solid square: MCUT TSSi MOSFET simulation with fixed surface roughness scattering rate; open triangle: MCUT unstrained Si MOSFET simulation.

## 2.8 Illustrative High-field and Deeply Scaled Device Results

Figure 2-18 shows  $I_D$  vs.  $V_D$  curves for  $V_G - V_T = 1.0$  V and  $V_G - V_T = 2.0$  V showing the enhancement in drive current due to strain and, additionally, due to the apparent reduction in surface roughness discussed above for relatively large devices. Figure 2-19 and Figure 2-20 shows the carrier velocity and energy distribution along the channel for  $V_G - V_T = 2.0$  V and  $V_D = 0.5$  V. The results of Figure 2-18 suggest the possibility for significantly increased drive current, approximately a factor of 2 increase in the drive current for  $V_G - V_T = 1.0$  V. Figure 2-21 illustrates the simulation of devices with channel lengths of only a few

tens of nanometers (device after Ref. [Mit00]). Simulations such as this last one are the end goal of developing MCUT, and in the future such simulations will be performed using MCUT to analyze how and to what degree mobility enhancement and such drive current enhancement will translate to conventional and non-classical CMOS with channel lengths of a few tens of nanometers.

Figure 2-18:  $I_{d}$ - $V_{d}$  curve. Drain currents as a function of drain voltage for nMOSFETs with TSSi  $(\gamma = 0.2)$  channel and an unstrained Si  $(\gamma = 0.0)$  channel. Closed circles: unstrained Si; closed squares: TSSi with fixed surface roughness parameters; open diamonds: TSSi with reduced surface roughness scattering consistent with Figure 2-17. For the same  $V_{G} - V_{T}$ , enhancement of the drive current is observed in the TSSi.

Figure 2-19: Average carrier transport velocity along the channel for fixed  $V_D$  and  $V_G - V_T$ .

Figure 2-20: Average carrier kinetic energy distribution along the channel for fixed  $V_D$  and  $V_G - V_T$ . Comparison is made between a TSSi channel with reduced surface roughness scattering and a relaxed Si channel. Increases are observed in both average energy and velocity within the channel for TSSi as compared to relaxed Si.

Figure 2-21:  $I_d$ - $V_d$  curve for a 50 nm channel length well-tempered device after Ref. [Mit00]. Drain currents as a function of drain voltage for nMOSFETs with TSSi ( $\gamma = 0.2$ ) channel and an unstrained Si ( $\gamma = 0.0$ ) channel. Closed circles: unstrained Si; closed squares: TSSi with fixed surface roughness parameters; open diamonds: TSSi with reduced surface roughness scattering consistent with Figure 2-17. For the same  $V_G - V_T$ , ( $V_T$ 's are different in these three cases) enhancement of the drive current is observed in the TSSi, although perhaps a bit less than the longer channel devices for this isolated example.

# 2.9 Scalability of TSSi nMOS on Technology Roadmap

From the above discussion and simulation results, we have realized that the underlying physical principle of TSSi is the strain-induced degeneracy breaking between the interface-normal- and interface-parallel-oriented conduction band  $\Delta$  valleys which leads to a lower conductivity effective mass and reduced intervalley scattering and, thus, enhanced mobility [Fis96][Fan04]. However, size quantization in strong inversion also breaks the degeneracy among the  $\Delta$  valleys in much the same way, so that both systems have substantial degeneracy breaking;

strained Si simply has more. Therefore the actual advantage of SSi over Si may be less than otherwise expected, especially in high gate field regime [Fis02].

Because of the smaller bandgap, SSi nMOS has a smaller threshold voltage ( $V_{th}$ ) than its unstrained Si counterpart, if all processing steps are kept the same. Ideally the same threshold voltage is required for SSi devices in order to keep the same  $I_{on}/I_{off}$  ratio at  $V_{dd}$ . So SSi devices need to have  $V_{th}$  increased, either by using a gate material with a higher work function, or by increasing the channel doping level. While gate work function engineering is very difficult, increasing channel doping concentration seems to be a practical solution. However, higher doping results in increased effective field and impurity scattering rate in the channel, thus reducing channel mobility. Combining these effects: more valley splitting, higher channel doping, and possibly smoother interface, can we foresee SSi nMOS scalability? For the next generation nMOS, is SSi a better choice than Si? More device simulations with decreasing channel lengths were performed with MCUT to address this question.

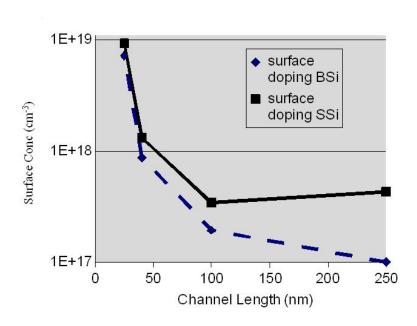

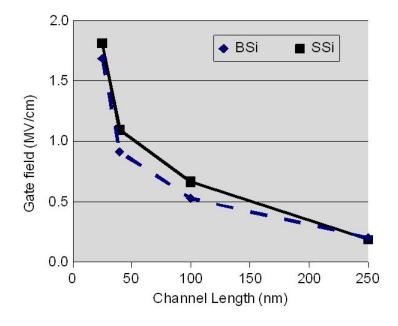

We choose physical channel lengths of 240 nm, 100 nm, 40 nm and 25 nm, with the gate length being 250 nm, 171 nm, 86 nm, and 50 nm, respectively. These lengths represent the scaling trend from 2002 to 2007. With channel length scaling,  $V_{dd}$  will decrease from 2.5 V to 1.1 V, while  $V_T$  changes from 0.7 V to 0.4 V. In our simulation, we took device doping profiles simplified from experiments [Rim00] and "well-tempered" bulk-Si nMOS devices [Mit00]. All the devices use anti-punchthrough implants by (super) halo doping. The surface channel p-type doping levels are plotted in *Figure 2-22*. Similar device profiles are used in SSi nMOS, except that more intensive halo implant are applied to

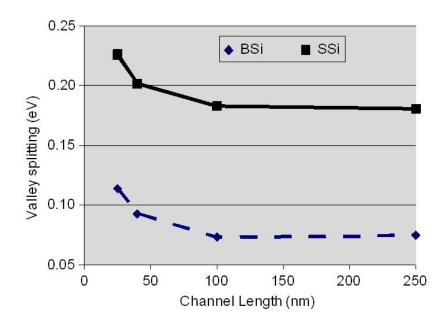

compensate for the effect of bandgap reduction of SSi. In our simulations, the halo doping levels in SSi nMOS were tuned to achieve the same  $V_T$  as for bulk-Si by examining  $I_D - V_G$  curves. Compared with Si nMOS, the channel surface doping in SSi is 76% ~ 30% higher, with the factor decreasing with channel length. Because of the increased channel doping, the transverse gate field in short channel devices is higher, as shown in Figure 2-23. As pointed out in section 2, higher gate field causes more degeneracy-breaking among  $\Delta$  valleys, as shown in Figure 2-24. The  $\Delta_2$  valleys with lower energy attract more carriers. For example, more than 75% of electrons reside in  $\Delta_2$  valleys, which happens when  $E(\Delta_2) - E(\Delta_2) \approx 100$  meV [Fis02]. The mobility enhancement due to valley splitting is plotted in Figure 2-25, for strained Si in the absence of a gate bias. It is clearly seen that mobility enhancement in strained Si reduces at valley splitting greater than 100 meV, which happens when nMOS  $L_{eff}$  shrinks from 40 nm to 25 For a 25 nm nMOS device, though SSi channels have more valley splitting energy than bulk Si does, the mobility enhancement diminishes. Since SSi nMOS devices have increased channel doping, it results in higher ionized impurity scattering rate. In ultra-short devices, both Si and SSi MOSFETs also undergo carrier heating and velocity overshoot. These are all captured by MCUT, and  $I_{on}$  enhancement as a function of channel length is shown in Figure 2-26, in the term of " $V_T$ -matched".

Figure 2-22: Channel surface doping in strained Si and bulk Si nMOSFETs.

Figure 2-23: Average gate field in strained Si and bulk Si nMOSFETs.

Figure 2-24: Energy splitting between  $\Delta_2$  and  $\Delta_4$  valleys in SSi and bulk Si channels.

Figure 2-25: Low-field bulk mobility plotted as a function of energy splitting between  $\Delta_2$  and  $\Delta_4$  valleys.

Figure 2-26: Drain current comparison between Si and SSi nMOSFETs. Lines represent MCUT simulations in " $V_T$ -matched" and "process-matched" conditions. Experimental results come from: a. Ref [Xia03], b. Ref [Rim02a], c. Ref [Lee02], d. Ref [Hwa03], the rest from Ref [Goo03].

In the most recent development on SSi devices, gate workfunction engineering has been applied to counter the  $V_T$  change [Xia03]. Though more complex gate process steps are required, the SSi device can be rid of increased channel dopants and thus keep the drain current advantage. In our work we assume ideal gate material for SSi device to counter the  $V_T$  change to get the so-called "process-matched"  $I_{on}$  comparison between bulk Si and SSi nMOS, and the results are shown in  $Figure\ 2-26$  too. In these simulations identical doping profiles were used in bulk Si and SSi nMOS, and gate biases were applied to maintain same overdrive ( $V_G - V_T$ ) in comparison.

Shown in *Figure 2-26*, MCUT simulation results in the " $V_T$ -matched" and "process-matched" categories are both consistent with experimental data (VT-matched: [Goo03][Rim02a]; process-matched: [Goo03] [Xia03] [Lee02] [Hwa03]). Both

our theoretical estimations and published experiments predict that SSi nMOS loses its performance advantage over unstrained Si at around 25 nm  $L_{ef}$ , in the threshold-voltage-matched case. Compared to other Monte Carlo simulation, this work takes quantum confinement induced valley splitting in both bulk Si and SSi into consideration, thus giving a better assessment of current enhancement of SSi nMOS over bulk devices.

#### 2.10 Conclusion

Biaxially tensile-stressed Si nMOS shows advantages over bulk Si MOSFETs in terms of low field channel mobility and electron velocity overshoot at submicron channel lengths. However, at ultra-short channel lengths, increased channel doping and gate quantization effects have brought diminishing returns to SSi over bulk Si. For nMOSFETs, our semiclassical Monte Carlo simulation comparison of bulk Si and SSi devices in the channel length range from 240 nm to 25 nm indicates that SSi will not be attractive as for nMOS channel material at the 25 nm channel lengths if  $V_T$ s are kept constants. Though oxide interface roughness remains an unsolved issue in these devices, other high mobility channel materials which do not exhibit bandgap lowering, such as uniaxial strained Si and III-V compound semiconductors, may be better choices.

### 3 Uniaxially Stressed Si CMOS

### 3.1 Motivation

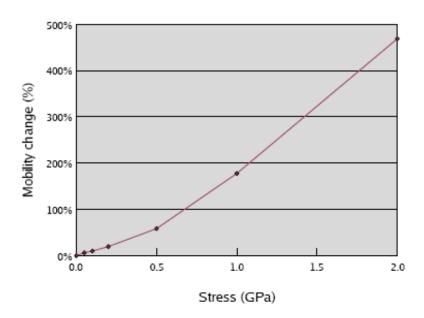

Recent experimental and theoretical works point to uniaxially-stressed Si as a possible channel material for next generation CMOS [Tho05]. As compared to tensile biaxially-stressed Si grown on relaxed SiGe substrates [Lei02] [Fis03] [Hoy02] uniaxial-stressed Si has the advantage that both theoretical estimations and experimental results indicate that the hole channel mobility improvement is maintained at high gate fields [Gil04] [Tho04]. Experimentally, uniaxial compressive stress has been applied to the channel area via source/drain heteroepitaxial deposition of SiGe [Tho04][Gha03][Chi04], or by compressive capping layers on top of the gate [Arg04], while four-point or ring wafer bending is the main technique for experimentally measuring piezoresistance [Bea92]. Greater than 50% stress-induced hole channel mobility improvement and 10% to 25% drain current enhancement has been demonstrated in strained Si devices for stress ranging from 100 to 500 MPa [Tho04][Gha03][Chi04][Arg04]. Furthermore, although the hole mobility is often modeled as depending linearly on stress according to tabulated piezoresistance coefficients such as those of Ref. [Smi54], recent studies have exhibited super-linear relationships between bulk mobility and stress [Shi04][Wan04] suggesting even greater potential advantages in the high stress regime.

For this work, the low-field bulk mobility of uniaxially-stressed Si is studied

theoretically but over a wider range of stress than considered previously. In addition, thermal velocities that, along with the low-field mobilities, are relevant for short channel devices [Lun97] are also calculated. This study focuses on transport in the [110] and [110] direction for [110] compressive and tensile uniaxially-stressed Si. Considered stress, both tensile and compressive, begins at 50 MPa within the realm of bulk piezoresistance measurements [Smi54], enters the GPa stress regime as now appears possible via process induced stress [Arg06], and continues up to 4 GPa in a search for limiting behavior. The valence band structures are calculated with a **k·p** Hamiltonian method. The thermal velocities, along with thermal average effective masses and phonon scattering rates (the latter being dependent on the stress-dependent densities-of-states) are obtained directly from the band structure. MCUT is then used operating in the bulk limit to accurately calculate the bulk mobility in the presence of the highly non-parabolic, anisotropic band structures and inelastic scattering.

### 3.2 Band Structures

For this work, the **k•p**-based bandstructure program Nextnano3 [Bir02] was used for uniaxially-stressed Si band structures, with the deformation potentials for stressed Si obtained from [Fis03]. And as in [Fis03], a 6x6 Hamiltonian was used in Nextnano3 to calculate the "heavy-hole" (HH), "light-hole" (LH) and "split-off" (SO) hole bands. Because it is a perturbation method, the reliability of the calculated band structure at high energies is limited. However, the approach should be reliable for the thermal velocity and low-field mobility calculations of this work.

Under increasing stress along the [110] direction, the warping of the Si HH band (here, in the presence of anti-crossings, defined as the lowest lying hole band/highest lying valence band) is gradually reduced with increasing splitting between the HH and LH band, as seen in *Figure 3-1*.

Figure 3-1: Heavy hole and light hole band splitting in uniaxially-stressed Si. Here and for subsequent figures the positive stress axis corresponds to tensile stress, and the negative stress axis to compressive stress.

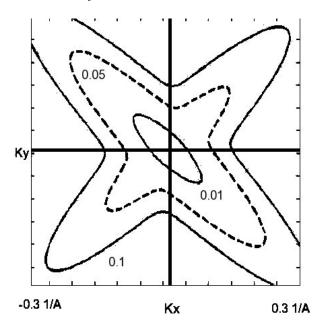

Note that with band occupation ratios of HH:LH:SO  $\approx 65:10:1$  for unstrained Si and with the ratios shifting further in favor of the HH band with increasing stress, hole transport is governed largely by the properties of the HH band. The anti-crossing between the HH and LH bands in the [110] direction makes the effective mass of the HH band in the [110] direction smaller near the  $\Gamma$  point and the isoenergy surfaces near ellipsoidal in the (001) plane at low energies, as shown in *Figure 3-2* and *Figure 3-3*, for a 500 MPa stress. In *Figure 3-3*, the 10 meV energy surface of the HH band resembles an ellipsoid with low  $m^*$  in the [110] direction,

the 50 meV surface—approximately the thermal average energy—is clearly becoming warped, and the 100 meV surface is quite similar in shape to the bulk Si energy contour with almost no advantage for transport in the [110] direction. The reduced warping at low energies can be understood as degeneracy breaking among the energy "wings" in the otherwise 12 equivalent <110> directions in bulk Si HH band. Under [110] compressive stress, the energy of the wings extending in  $[1\overline{1}0]$ ,  $[\overline{1}10]$ , [011],  $[0\overline{1}\overline{1}]$ , [101], and  $[\overline{1}0\overline{1}]$  are lowered relative to that of the remaining six wings. These relative shifts, together with the HH/LH band splitting, also cause a redistribution of carriers within the band structure. As the band splitting increases with stress, the region of the band structure below the anti-crossing where the band structure appears ellipsoidal increases, allowing more carriers within a thermal distribution to have a small effective mass in the [110] direction.

Figure 3-2: Heavy-hole and light-hole energy-K dispersion in [110] and  $[1\,\overline{1}\,0]$  directions with compressive [110] uniaxial-stress of 500 MPa.

Figure 3-3: 2-D heavy-hole iso-energy contours (10 meV, 50 meV and 100 meV) for [110] uniaxially-stressed Si in the (001) plane with a compressive stress of 500 MPa in the [110]

direction.

To better quantify the level of asymmetry in uniaxially-stressed Si hole bands as a function of stress magnitude, a thermal average of the reciprocal of the effective mass  $m_{\hat{\mathbf{n}}}$  in the chosen transport direction  $\hat{\mathbf{n}}$  is calculated from the full-band structure by averaging it over **k**-space and all hole bands  $\alpha$  using Boltzmann energy statistics at room temperature:

$$\frac{\hbar^2}{m_{\hat{\mathbf{n}}}} = \sum_{\alpha} \int \frac{\partial^2 E_{\alpha}(\mathbf{k})}{\partial k_{\hat{\mathbf{n}}}^2} \exp(-\frac{E_{\alpha}(\mathbf{k})}{k_B T}) d^3 \mathbf{k} / \sum_{\alpha} \int \exp(-\frac{E_{\alpha}(\mathbf{k})}{k_B T}) d^3 \mathbf{k} . \tag{3-1}$$

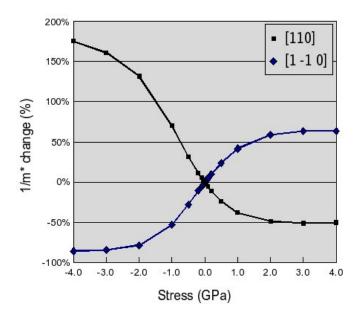

The mass reciprocal is used because of its nominally linear relationship to mobility. Results are shown in *Figure 3-4*. Note that in unstrained Si, consistent with essentially isotropic low field mobility in bulk Si [Ott75],  $m_{\hat{n}}$  is essentially isotropic despite the highly anisotropic multi-band band structure (a reminder that considering the directional dependence of the band curvature only at the  $\Gamma$  point can be highly misleading.) However, stress and the associated symmetry reduction in the band structure breaks the symmetry in the thermal average mass reciprocal, advantageously increasing it under appropriate combinations of stress and channel orientation.

Figure 3-4: Percentile change in the thermal average of the inverse effective mass in the [110] and  $[1\,\overline{1}\,0]$  directions for [110] uniaxially-stressed Si as function of stress. The zero stress value is 2.79 times the reciprocal of the free space mass. For reference, the average inverse effective mass value in the [001] direction in unstrained Si is 2.80.

Similarly, the Boltzmann distribution-weighted average of the thermal velocities in the transport direction,  $v_{th}$ , was obtained from

$$v_{th} = \sum_{\alpha} \int |\mathbf{v} \cdot \hat{\mathbf{n}}| \exp(-\frac{E_{\alpha}(\mathbf{k})}{k_B T}) d^3 \mathbf{k} / \sum_{\alpha} \int \exp(-\frac{E_{\alpha}(\mathbf{k})}{k_B T}) d^3 \mathbf{k} . \tag{3-2}$$

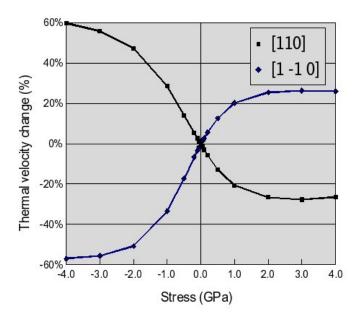

Results are shown in *Figure 3-5* where again significant and growing anisotropy is apparent under stress. (Note that for the highly isotropic HH band there can be both forward and backward moving carriers in a given half-**k**-space, and, thus, the integral over all **k**-space of the directed velocity magnitude was performed.)

Figure 3-5: Percentile change of the thermal velocity in the [110] and  $[1\,\overline{1}\,0]$  directions for [110] uniaxially-stressed Si as function of stress. The unstrained Si thermal velocity is  $8.9\times10^6$  cm/s at room temperature.

Another important feature of the impact of uniaxial stress on the band structure is the reduction of the DOS and the corresponding reduction in the phonon scattering rates. The phonon scattering processes included in bulk simulations were longitudinal acoustic, transverse acoustic and optical phonons. The scattering rates were calculated with Fermi's golden rule based on the band structures. Calibration on the scattering process has been done [Wan02] with unstrained Si with respect to drift velocity and carrier energy [Ott75][Jac77]. The shorter low-energy contours in *Figure 3-3* than in bulk Si are indicative of this reduced DOS. The reduced DOS in the HH band results in smaller intra-band phonon scattering rates. The HH/LH energy splitting also leads to fewer interband scattering events. Analogous to above, the thermal average of the

reciprocal of the scattering rate, the mean time between scattering events which is again nominally proportional to the mobility, were calculated as a function of stress from

$$\tau_{th} = \frac{1}{R_{th}} = \sum_{\alpha} \int \frac{1}{R_{\alpha}(\mathbf{k})} \exp(-\frac{E_{\alpha}(\mathbf{k})}{k_{B}T}) d^{3}\mathbf{k} / \sum_{\alpha} \int \exp(-\frac{E_{\alpha}(\mathbf{k})}{k_{B}T}) d^{3}\mathbf{k} . \tag{3-3}$$

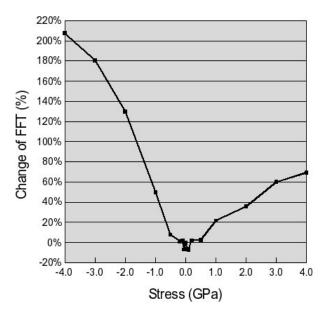

Results are shown in *Figure 3-6*. At low strains the change in the scattering rate is small, but at higher strain the increase in the mean time between scattering events clearly becomes significant.

Figure 3-6: Percentile change of the thermal average of inverse scattering rates (proportional to free flight time FFT) for [110] uniaxially-stressed Si as function of stress. The zero stress FFT (phonon scattering only) is  $\sim 0.15$  ps at room temperature.

## 3.3 Bulk Mobility

While the results obtained from Equations (3-1) and (3-3) are qualitatively