Copyright

by

Jung Woo Pyun

2007

# The Dissertation Committee for Jung Woo Pyun Certifies that this is the approved version of the following dissertation:

# Scaling and Process Effect on Electromigration Reliability for Cu/low k Interconnects

# Paul S. Ho, Supervisor Jang-Hi Im Jack C. Lee Llewellyn K. Rabenberg Ennis T. Ogawa

# Scaling and Process Effect on Electromigration Reliability for Cu/low k Interconnects

by

Jung Woo Pyun, B.S.; M.S.

## **Dissertation**

Presented to the Faculty of the Graduate School of

The University of Texas at Austin

in Partial Fulfillment

of the Requirements

for the Degree of

**Doctor of Philosophy**

The University of Texas at Austin

May 2007

# **Dedication**

To my family

## Acknowledgements

I would like to thank many people for helping me during last five years. I would especially like to thank my advisor, Dr. Paul S. Ho, for his continuous support and advice throughout my doctoral work. I am also very grateful for having an exceptional doctoral committee and wish to thank Dr. Im, Dr. Lee, Dr. Rabenberg, and Dr. Ogawa for their support and encouragement. I specially thank Dr. Im for proofreading my dissertation and valuable suggestions.

I want to take this opportunity to thank Samsung Electronics for giving me a great opportunity to pursue my Ph.D. study and the financial support. I am also very grateful to Dr. Larry Smith and Dr. Dean Denning at SEMATECH for providing the valuable test samples.

I extend many thanks to my colleagues and friends in the Laboratory for Interconnect and Packaging for their advices and discussions about my research. I am also thankful to Ms. Jo Ann Smith for her help. I would like to thank my Korean friends in J.J. Pickle research campus for their warm friendship.

Finally, I'd like to thank my family. I'm grateful to my parents and my sister for their continuous encouragement and patience. I am also thankful to parents in law for helping me accomplish this work. I'm especially grateful to my wife Insuk, my son Doyoung, and my daughter Gloria for their supports, dedications and endless loves.

# Scaling and Process Effect on Electromigration Reliability for Cu/low k Interconnects

| Publication No. | Publication | No. |  |  |

|-----------------|-------------|-----|--|--|

|-----------------|-------------|-----|--|--|

Jung Woo Pyun, Ph.D.

The University of Texas at Austin, 2007

Supervisor: Paul S. Ho

The microelectronics industry has been managing the *RC* delay problem arising from aggressive line scaling, by replacing aluminum (Al) by copper (Cu) and oxide dielectric by low-k dielectric. Electromigration (EM) turned out to be a serious reliability problem for Cu interconnects due to the implementation of mechanically weaker low-k dielectrics. In addition, line width and via size scaling resulted in the need of a novel diffusion barrier, which should be uniform and thin. The objective of this dissertation is to investigate the impacts of Ta barrier process, such as barrier-first and pre-clean first, and scaling of barrier and line/via on EM reliability of Cu/low-k interconnects. For this purpose, EM statistical test structures, having different number of line segments, line width, and via width, were designed. The EM test structures were fabricated by a dual-damascene process with two metal layers (M1/Via/M2), which were then packaged for EM tests. The package-level EM tests were performed in a specially designed vacuum chamber with pure nitrogen environment.

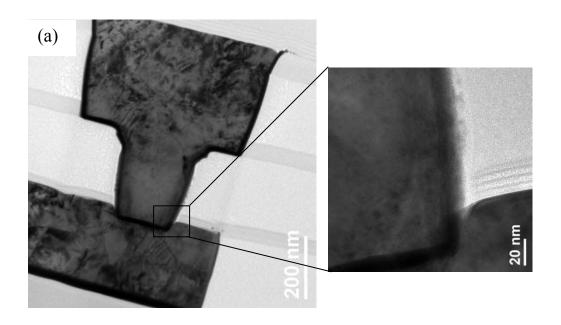

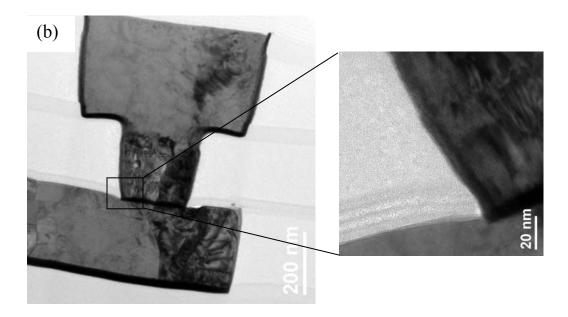

The novel barrier deposition process, called barrier-first, showed a higher  $(jL)_c$  product and prolonged EM lifetime, compared with the conventional Ta barrier deposition process, known as pre-clean first. This can be attributed to the improved uniformity and thickness of the Ta layer on the via and trench, as confirmed by TEM. As for the barrier thickness effect, the  $(jL)_c$  product decreased with decreasing thickness, due to reduced Cu confinement. A direct correlation between via size and EM reliability was found; namely, EM lifetime and statistics degraded with via size. This can be attributed to the fact that critical void length to cause open circuit is about the size of via width. To investigate further line scaling effect on EM reliability, SiON (siliconoxynitride) trenchfilling process was introduced to fabricate 60-nm lines, corresponding to 45-nm technology, using a conventional, wider line lithograph technology. The EM lifetime of 60-nm fine lines with SiON filling was longer than that of a standard damascene structure, which can be attributed to a distinct via/metal-1 configuration in reducing process-induced defects at the via/metal-1 interface.

## **Table of Contents**

| List of Tables                                                                              | X1  |

|---------------------------------------------------------------------------------------------|-----|

| List of Figures                                                                             | xii |

| Chapter 1: Introduction                                                                     | 1   |

| 1.1 Electromigration Fundamental                                                            | 2   |

| 1.2 Statistical Analysis of EM Using Multi-linked Structure                                 | 9   |

| 1.2.1 Statistical Measurement of EM Threshold in Cu Interconnect                            | s9  |

| 1.2.2 Statistical Measurement of Early Failure in Cu Interconnects                          | 11  |

| 1.3 EM Reliability Issues Related Scaling and Low-k Dielectrics                             | 14  |

| 1.4 Recent EM Studies                                                                       | 18  |

| 1.5 Proposed Work                                                                           | 20  |

| Chapter 2: Experimental Procedure                                                           | 23  |

| 2.1 EM Test Structure Design                                                                | 24  |

| 2.2 Wafer Fabrication and EM Test                                                           | 30  |

| 2.3 Measurement of (jL) <sub>c</sub> Product                                                | 33  |

| 2.4 Resistance Changes during EM Test                                                       | 37  |

| Chapter 3: Barrier Process Effect on Electromigration Reliability of Cu/low-k Interconnects |     |

| 3.1 Introduction                                                                            | 40  |

| 3.2 Experimental Details                                                                    | 43  |

| 3.3 Results and Discussion                                                                  | 44  |

| 3.3.1 Early Failure Behaviors for Different Barrier Processes                               | 44  |

| 3.3.2 Observation of Microstructure Using TEM                                               | 46  |

| 3.3.3 Barrier Process Effect on ( <i>jL</i> ) <sub>c</sub> Product                          | 49  |

| 3.4 Summary                                                                                 | 55  |

| Chapter 4: Barrier Thickness Effect on Electromigration Reliability of Cu/low Interconnects |     |

| 4.1 Introduction                                                                            | 58  |

| 4.2 Experimental Details                                                                | 59  |

|-----------------------------------------------------------------------------------------|-----|

| 4.3 Results and Discussion                                                              | 59  |

| 4.3.1 Barrier Thickness Effect on ( <i>jL</i> ) <sub>c</sub> Product                    | 59  |

| 4.3.2 Barrier Thickness Effect on Early Failure Statistics                              | 62  |

| 4.3.3 Physical Failure Analysis Using FIB and TEM                                       | 67  |

| 4.3.4 EM Activation Energies for Different Barrier Thicknesses                          | 69  |

| 4.3.5 EM Resistance Traces for Different Barrier Thicknesses                            | 72  |

| 4.4 Summary                                                                             | 76  |

| Chapter 5: Via Scaling Effect on Electromigration Reliability of Cu/low-k Interconnects | 77  |

| 5.1 Introduction                                                                        | 78  |

| 5.2 Experimental                                                                        | 78  |

| 5.3 Results and Discussion                                                              | 81  |

| 5.3.1 Via Scaling Effect on EM Reliability for Type I Structures                        | 81  |

| 5.3.2 Via Scaling Effect on EM Reliability for Type II Structures .                     | 85  |

| 5.3.3 Via Scaling Effect on EM Reliability for Type III Structures                      | 86  |

| 5.4 Summary                                                                             | 89  |

| Chapter 6: Electromigration Behavior for Ultra Fine Dual Damascene Cu<br>Interconnects  | 90  |

| 6.1 Introduction                                                                        | 90  |

| 6.2 Experimental Details                                                                | 91  |

| 6.3 Results and Discussion                                                              | 94  |

| 6.3.1 Effect of SiON Filling on EM Reliability                                          | 94  |

| 6.3.2 EM Failure Mechanism                                                              | 97  |

| 6.3.3 Line Width Effect on EM among SiON-filled Samples                                 | 99  |

| 6.3.4 Barrier Process and Thickness Effects on EM Reliability                           | 104 |

| 6.3.5 Early Failure Behavior                                                            | 105 |

| 6.3.6 Activation Energies and Current Density Exponents                                 | 107 |

| 6.4 Summary                                                                             | 110 |

| Chapter 7: Summary and Recommendations for Future Work                                  | 111 |

| 7.1 Summary                                                                             | 111 |

| 7.2 Recommendations for Future Work | 115 |

|-------------------------------------|-----|

| References                          | 117 |

| Vita                                | 128 |

# **List of Tables**

| Table 2.1 | Summary of EM testing structures including up-stream and down-stream  |  |

|-----------|-----------------------------------------------------------------------|--|

|           | electron flow conditions                                              |  |

| Table 3.1 | Summary of process flow for Ta barrier deposition using the pre-clean |  |

|           | first and the barrier-first scheme                                    |  |

# **List of Figures**

| Figure 1.1 | Schematic of the driving force of electromigration in metal wire. With                    |

|------------|-------------------------------------------------------------------------------------------|

|            | the electric field E, electrons collide with metal atoms in the electron                  |

|            | flow direction resulting in EM phenomenon                                                 |

| Figure 1.2 | Gate and interconnects delay as a function of generation. With                            |

|            | implementation of Cu and low-k dielectrics, the total delay was                           |

|            | significantly reduced, compared with Al/SiO <sub>2</sub> interconnects [6]5               |

| Figure 1.3 | Comparison of (a) conventional RIE process for Al interconnects with                      |

|            | (b) damascene process for Cu interconnects                                                |

| Figure 1.4 | (a) Mass transport in the Cu line encapsulated by the capping layer and                   |

|            | barrier layer. (b) Stress state for the Cu line under EM upon reaching                    |

|            | steady-state stress. 9                                                                    |

| Figure 1.5 | Cumulative failure distribution (CDF) plots of experimental and Monte                     |

|            | Carlo simulation results. The electromigration test was performed at 330                  |

|            | $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> . The weak-mode population |

|            | was about 0.3 %                                                                           |

| Figure 1.6 | Metal line and barrier thickness scaling for MPU and ASIC according to                    |

|            | the International Technology Roadmap for Semiconductors (ITRS) 2006                       |

|            | updated [2]                                                                               |

| Figure 1.7 | Maximum current density for MPU and ASIC at 105 $^{\circ}\mathrm{C}$ according to         |

|            | the International Technology Roadmap for Semiconductors (ITRS) 2006                       |

|            | updated [2]                                                                               |

| Figure 1.8 | Degradation of EM reliability in dual damascene Cu/low-k interconnects                    |

|            | due to line scaling and an implementation of low-k dielectrics18                          |

| Figure 2.1 | Summary of electromigration testing procedure24                                               |

|------------|-----------------------------------------------------------------------------------------------|

| Figure 2.2 | Schematics of EM test structure with (a) up-stream electron flow, and (b)                     |

|            | down-stream electron flow condition                                                           |

| Figure 2.3 | Schematics of (a) side view of early failure (EF) EM test structure, (b)                      |

|            | side view of critical length (LC) EM test structure, and (c) top view of                      |

|            | critical length (LC) EM test structure for up-current EM test condition.                      |

|            | 28                                                                                            |

| Figure 2.4 | EM testing module showing a guard ring, bonding pads, and EM test                             |

|            | patterns. An enlarged view shows EM test lines and wide dummy lines.                          |

|            | Blue, green, and black correspond to the color of M2 line, M1 line, and                       |

|            | via, respectively                                                                             |

| Figure 2.5 | Schematic of 16-pin side braze package with two EM samples and wire                           |

|            | bonding configuration for package-level EM test31                                             |

| Figure 2.6 | Package-level EM testing system                                                               |

| Figure 2.7 | Optical microscope image showing EM-induced voiding around cathode                            |

|            | end for a statistical multi-linked EM test structure. The stressing fine                      |

|            | lines are located between the wide extrusion monitoring lines. The EM                         |

|            | test was performed at 330 °C, with a current density of 1.0 MA/cm <sup>2</sup> .34            |

| Figure 2.8 | A plot of normalized number of fails as a function of line length for                         |

|            | Cu/low- k interconnects and the matching regression fitting on the                            |

|            | experimental results. The EM test was performed at 330 $^\circ\mathrm{C}$ at a current        |

|            | density of 1.0 MA/cm <sup>2</sup> . The probability of EM failure decreased with              |

|            | decreasing line length. The critical length was 20 $\mu$ m, and ( $jL$ ) <sub>c</sub> product |

|            | was approximately 2000 A/cm                                                                   |

| Figure 2.9 | Resistance traces for Cu interconnects including (a) typical gradual                          |

|------------|-----------------------------------------------------------------------------------------------|

|            | resistance increase, (b) abrupt resistance increase, and (c) step-like                        |

|            | resistance increase                                                                           |

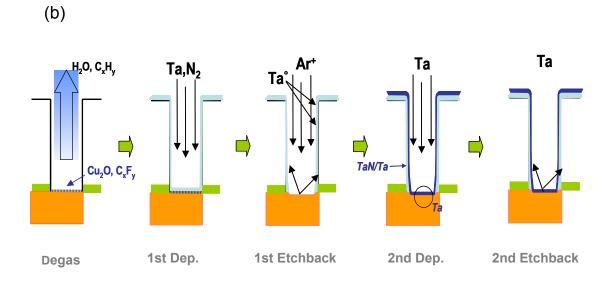

| Figure 3.1 | Schematics of (a) the conventional pre-clean first process, and (b) the                       |

|            | barrier-first process [64]                                                                    |

| Figure 3.2 | CDF plots of EM test results using Early Failure test structures with a                       |

|            | pre-clean first process (a) showing bi-modal failure distribution, and (b)                    |

|            | a barrier-first process showing the mono-modal failure distribution,                          |

|            | indicating the improvement in EM reliability45                                                |

| Figure 3.3 | Cross-sectional transmission electron microscopy (TEM) images                                 |

|            | showing Cu/low-k interconnects fabricated by dual damascene for                               |

|            | different barrier processes: (a) pre-clean first process, and (b) thin                        |

|            | barrier-first process                                                                         |

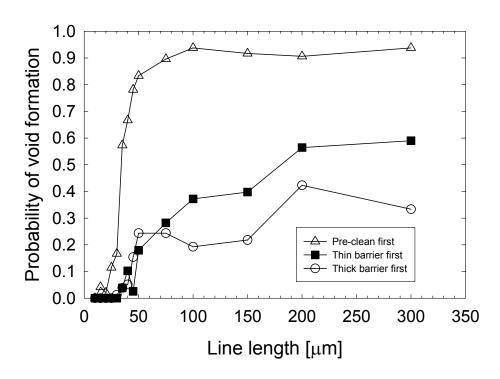

| Figure 3.4 | The probability of void formation as a function of M2 line length for the                     |

|            | different barrier processes. The probability of void formation was                            |

|            | calculated by dividing the number of lines with voids by the total                            |

|            | number of lines. The EM test was performed at 330 $^{\circ}\mathrm{C}$ , with a current       |

|            | density of 1.0 MA/cm <sup>2</sup>                                                             |

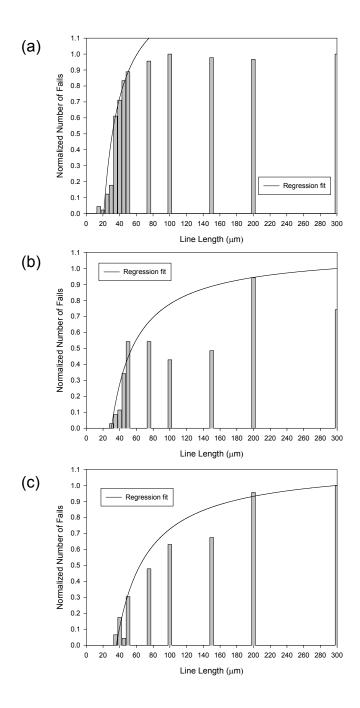

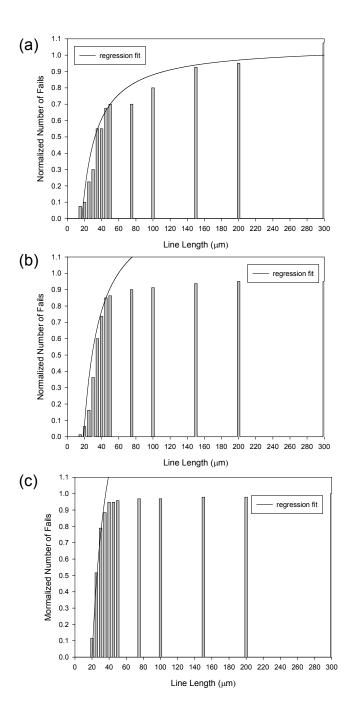

| Figure 3.5 | Plots of normalized number of fails as a function of line length for                          |

|            | Cu/low- k interconnects with (a) pre-clean first, (b) thin barrier-first, (c)                 |

|            | thick barrier first process. The EM test was performed at 330 $^\circ\!\!\mathbb{C}$ , with a |

|            | current density of 1.0 MA/cm <sup>2</sup>                                                     |

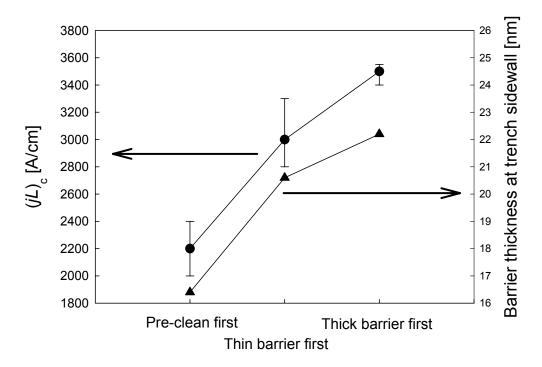

| Figure 3.6 | Plot of the statistically measured $(jL)_c$ product and the measured barrier                  |

|            | thickness using TEM for different barrier processes. The $(jL)_c$ product                     |

|            | shows good correlation with barrier thickness at the trench sidewall.53                       |

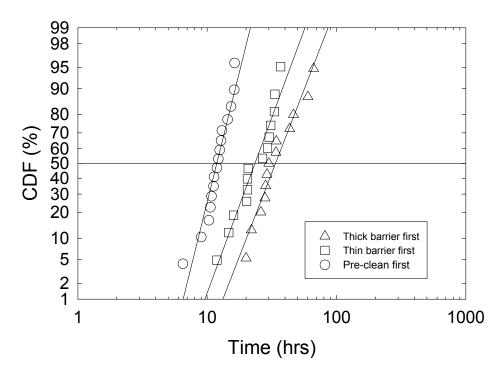

| Figure 3.7 | Cumulative failure distribution (CDF) plots of LC structures with                                                              |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

|            | different barrier processes for upstream electron flows. The EM test was                                                       |

|            | performed at 330 °C, with a current density of 1.0 MA/cm <sup>2</sup> 55                                                       |

| Figure 4.1 | Plots of normalized number of fails as a function of line length for                                                           |

|            | Cu/low- k interconnects with Ta barrier thickness of (a) 75, (b) 100, and                                                      |

|            | (c) 175 Å. The EM test was performed at 310 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|            | of 1.0 MA/cm <sup>2</sup> 60                                                                                                   |

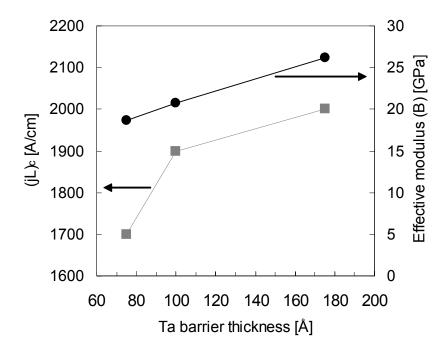

| Figure 4.2 | Plot of the statistically measured $(jL)_c$ product and the calculated                                                         |

|            | effective modulus (B) using FEM as a function of Ta barrier thickness.                                                         |

|            | The $(jL)_c$ product for the sample with 75 Å Ta barrier thickness showed                                                      |

|            | considerable decrease than that expected from FEM62                                                                            |

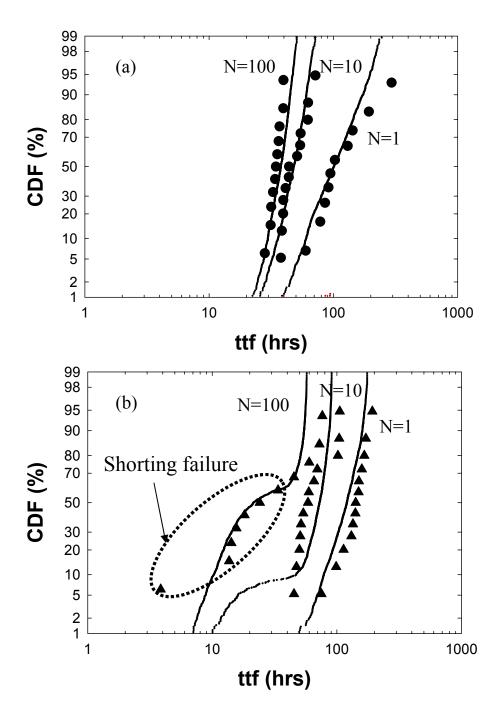

| Figure 4.3 | CDF Plots of EM test results using Early Failure test structures with Ta                                                       |

|            | barrier thickness of (a) 175 Å showing the mono-modal distribution, and                                                        |

|            | (b) 100 Å showing the bi-modal distribution due to the M2 line shorting                                                        |

|            | with the extrusion monitor line [65,66, 71]64                                                                                  |

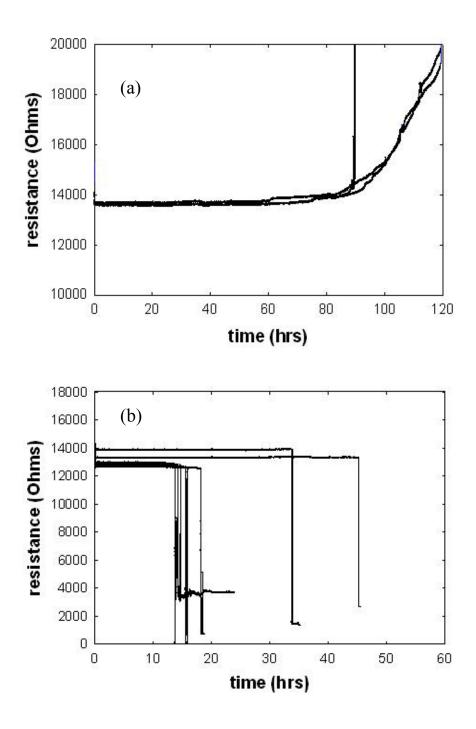

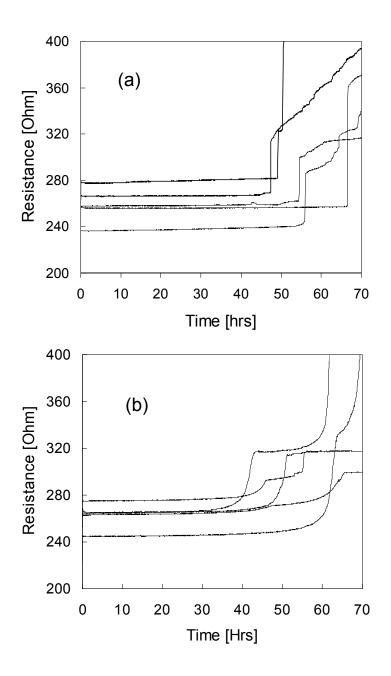

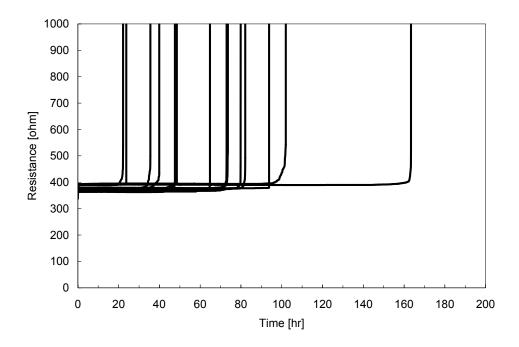

| Figure 4.4 | The resistance changes as a function of time of dual damascene Cu/low-                                                         |

|            | k interconnects with the Ta barrier thickness of (a) 175 Å, and (b) 100                                                        |

|            | Å. The EM test was performed at 330 $^{\circ}\mathrm{C}$ , with a current density of 1.0                                       |

|            | MA/cm <sup>2</sup> [71]66                                                                                                      |

| Figure 4.5 | A cross-sectional focused ion beam (FIB) micrograph of EM tested Cu                                                            |

|            | line and extrusion monitor lines from one of the shorting failed samples                                                       |

|            | shown in Figure 4.3(b). Thin Cu layer between the M2 metal line and                                                            |

|            | the extrusion monitor line is observed                                                                                         |

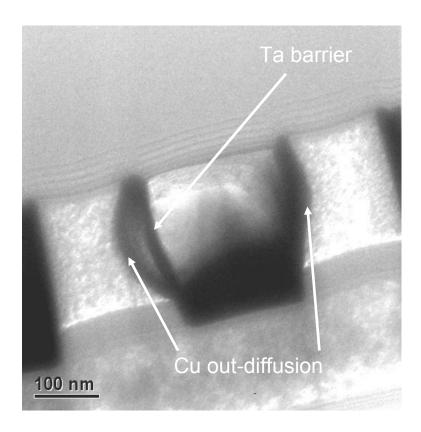

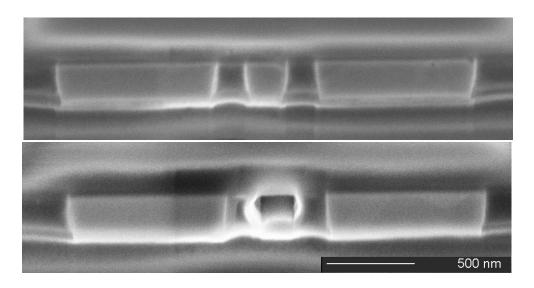

| Figure 4.6  | The cross-sectional transmission electron microscopy (TEM) image                                                                     |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------|

|             | showing the formation of a dark outer metal layer next to the EM                                                                     |

|             | stressed M2 line. The Ta barrier thickness was 100 Å, and the EM test                                                                |

|             | was performed at 330 $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> 68                                               |

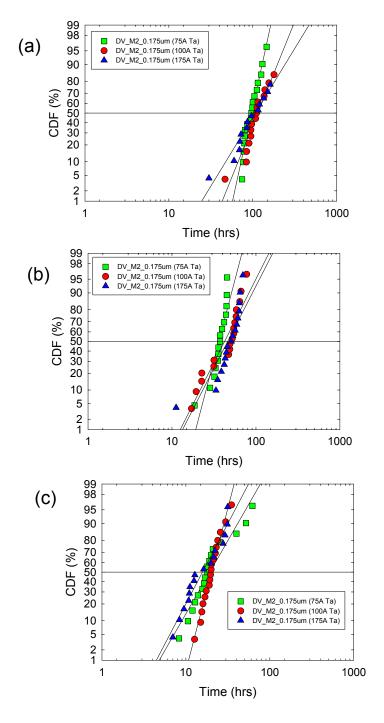

| Figure 4.7  | CDF plots of DV structures with different barrier thickness for up-stream                                                            |

|             | electron flow. EM tests were performed at (a) 300 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|             | (c) 360 $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> 70                                                            |

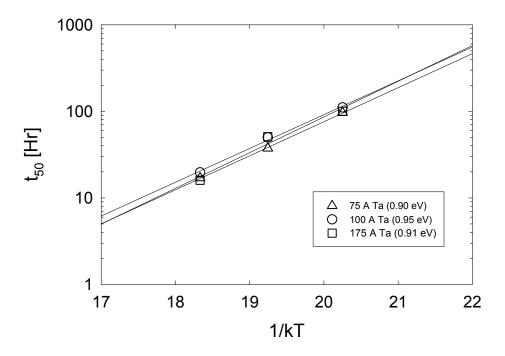

| Figure 4.8  | Electromigration lifetimes as a function of test temperature for the Cu                                                              |

|             | interconnects with different barrier thicknesses under the current density                                                           |

|             | of 1.0 MA/cm <sup>2</sup> . The activation energies demonstrate a similar interface                                                  |

|             | diffusion for different barrier thicknesses                                                                                          |

| Figure 4.9  | The resistance changes as a function of time of dual damascene Cu/low-                                                               |

|             | k interconnects with the Ta barrier thickness of (a) 175 Å, and (b) 100                                                              |

|             | Å. The electromigration test was performed at 330 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|             | density of 1.0 MA/cm <sup>2</sup>                                                                                                    |

| Figure 4.10 | The cross-sectional Focused Ion Beam (FIB) images of Cu/low-k                                                                        |

|             | interconnect with the Ta barrier thickness of (a) 175 Å, and (b) 75 Å                                                                |

|             | stressed at 330 $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> 75                                                    |

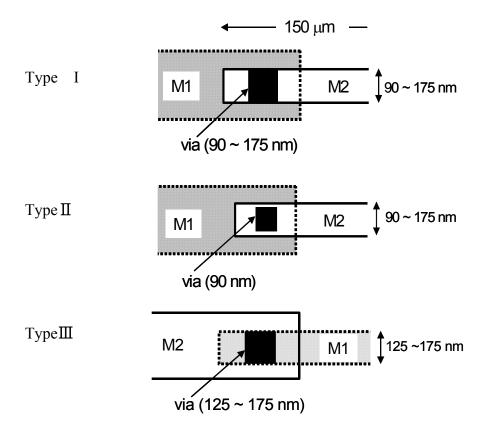

| Figure 5.1  | Schematics of two level (M1/via/M2) interconnect. The stressed line                                                                  |

|             | length was long (150 $\mu m)$ and narrow, while the connecting line was                                                              |

|             | short and wide to minimize the latter's EM damage. Up-current electron                                                               |

|             | flow was applied to Type I and II, and down-current electron flow to                                                                 |

|             | Type III80                                                                                                                           |

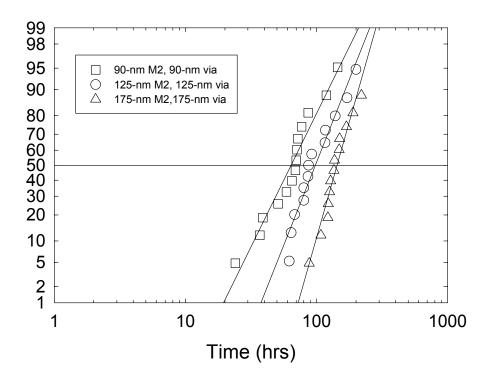

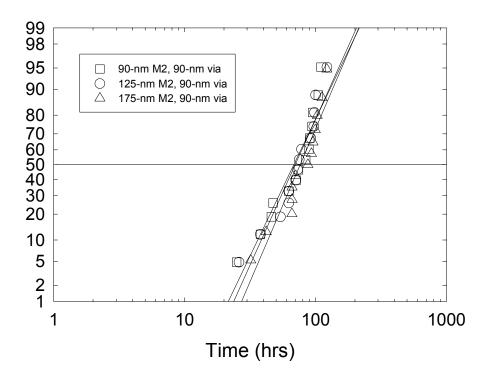

| Figure 5.2 | Cumulative failure distribution function (CDF) plots of type I structures               |

|------------|-----------------------------------------------------------------------------------------|

|            | with different M2 and via widths for up-stream electron flow. EM tests                  |

|            | were performed at 330 $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> 82 |

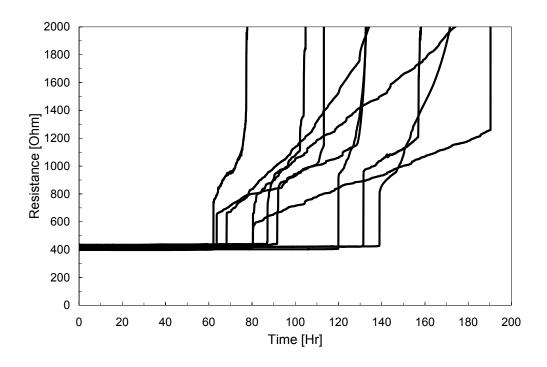

| Figure 5.3 | Resistance changes of 125-nm wide EM samples with type I structure.                     |

|            | 83                                                                                      |

| Figure 5.4 | Resistance changes of 90-nm wide EM samples with type I structure.84                    |

| Figure 5.5 | Focused Ion Beam (FIB) image showing a large cathode void in M2                         |

|            | trench for an EM failed 125-nm wide interconnect85                                      |

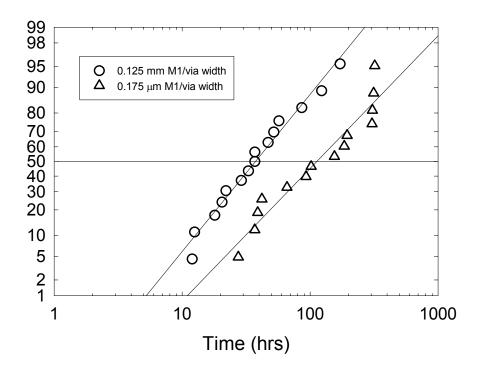

| Figure 5.6 | Cumulative failure distribution function (CDF) plots of type II structures              |

|            | with different M2 line widths for up-stream electron flow. EM tests were                |

|            | performed at 330 °C, with a current density of 1.0 MA/cm <sup>2</sup> 86                |

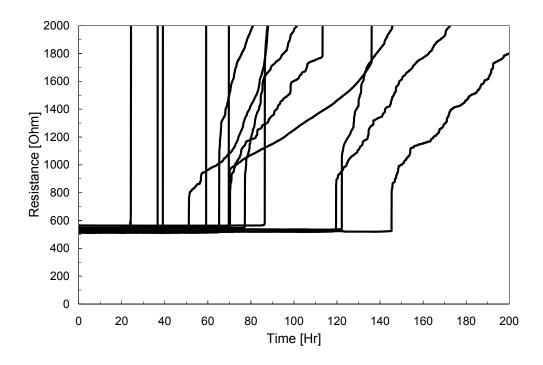

| Figure 5.7 | Cumulative failure distribution function (CDF) plots of type III                        |

|            | structures with different M1 line widths for down-stream electron flow.                 |

|            | EM tests were performed at 270 $^{\circ}$ C, with a current density of 1.0              |

|            | MA/cm <sup>2</sup> 87                                                                   |

| Figure 5.8 | Resistance changes of down-current electron flow EM samples with type                   |

|            | III structure                                                                           |

| Figure 5.9 | Focused Ion Beam (FIB) image showing a large cathode void in M1                         |

|            | trench for an EM failed interconnect                                                    |

| Figure 6.1 | Schematic diagram of a two level (M1/via/M2) EM test structure with                     |

|            | down current electron flow condition91                                                  |

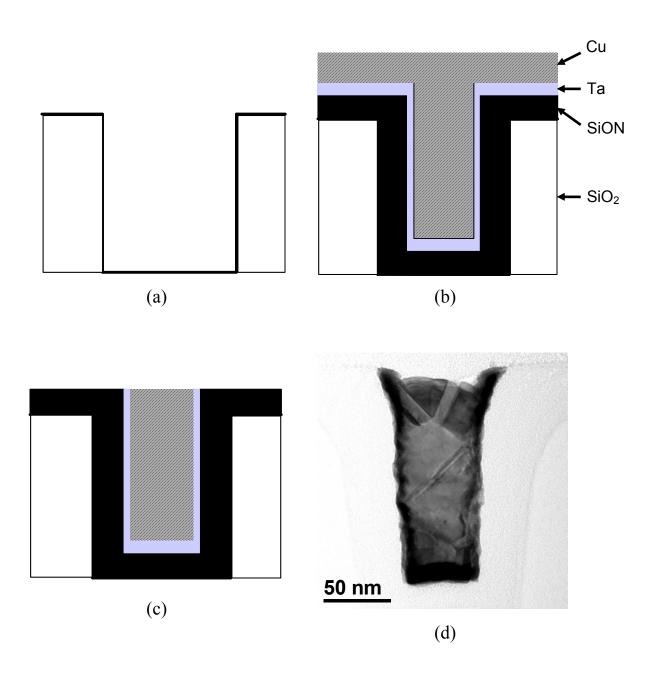

| Figure 6.2 | Schematics of SiON filling process scheme. (a) trench formation, (b)                    |

|            | SiON deposition + Ta barrier deposition + copper deposition, (d)                        |

|            | chemical mechanical polishing (CMP), (d) cross-sectional TEM image                      |

|            | showing 60-nm M1 trench with SiON filling93                                             |

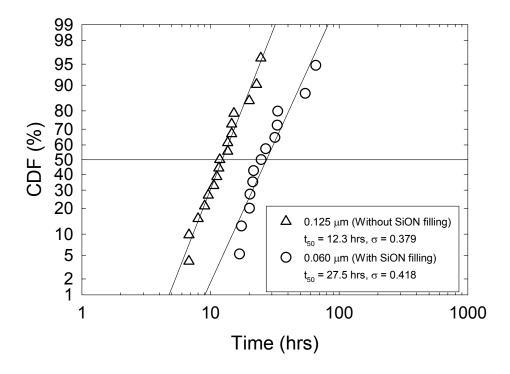

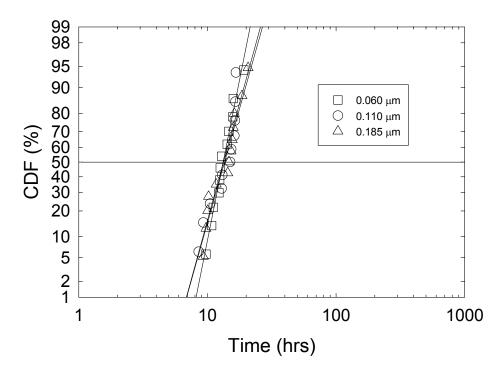

| Figure 6.3  | Cumulative failure distribution function (CDF) plots of down stream EM                       |

|-------------|----------------------------------------------------------------------------------------------|

|             | test structures with SiON filling layer (60 nm) and without SiON filling                     |

|             | layer (125 nm). EM test was performed at 270 $^{\circ}$ C, with a current                    |

|             | density of 1.0 MA/cm <sup>2</sup>                                                            |

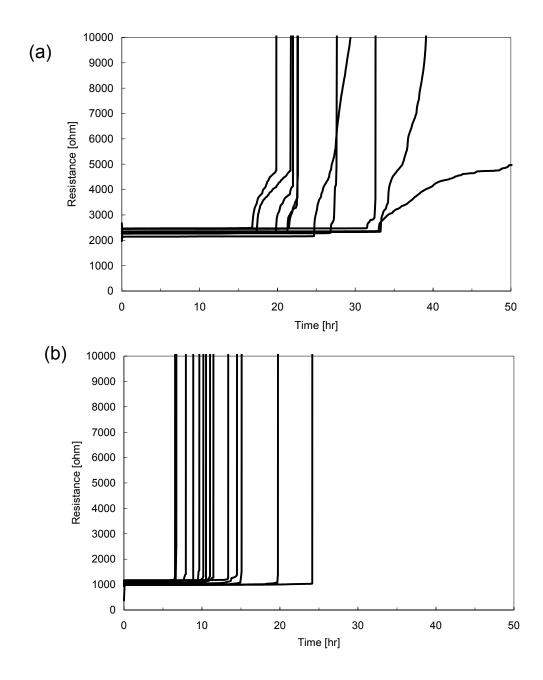

| Figure 6.4  | Resistance changes of down stream EM test structures (a) with SiON                           |

|             | filling layer (60 nm) and (b) without SiON filling layer (125 nm). EM                        |

|             | test was performed at 270 $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> .96 |

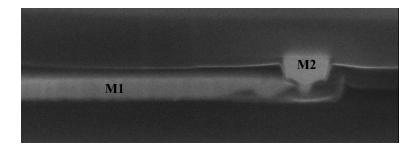

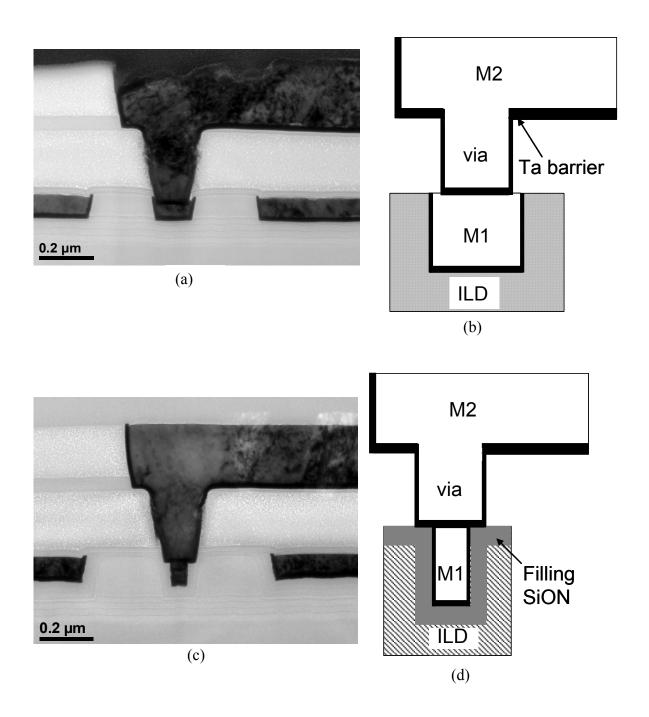

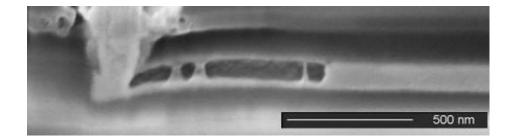

| Figure 6.5  | Transmission electron microscopy (TEM) images of dual-damascene Cu                           |

|             | interconnects. M1 trench width was reduced from 130 nm (a) to 60 nm                          |

|             | (c) using filling SiON layer, and the schematics, (b) and (d), are shown                     |

|             | on the right hand side of each TEM picture98                                                 |

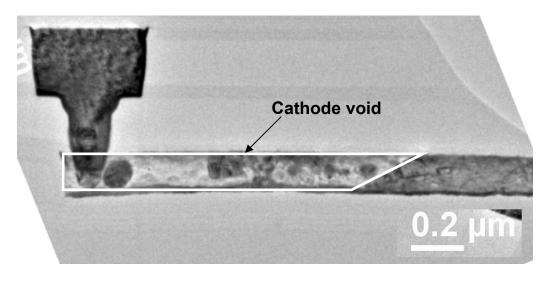

| Figure 6.6  | Transmission electron microscopy (TEM) image showing a large                                 |

|             | cathode void in M1 trench for an EM failed 60-nm wide interconnect.                          |

|             | 99                                                                                           |

| Figure 6.7  | Cumulative failure distribution function (CDF) plots with different line                     |

|             | widths for down stream electron flow. EM tests were performed at 300                         |

|             | $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> 100                           |

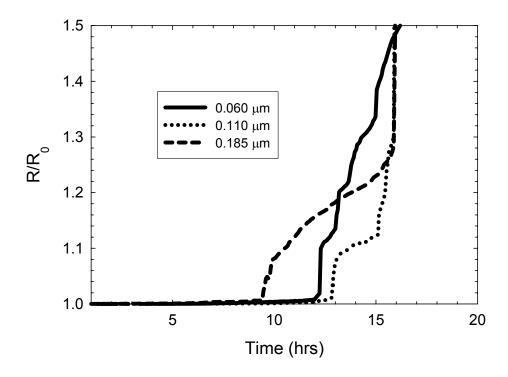

| Figure 6.8  | Normalized resistance changes of EM samples with different line widths.                      |

|             | EM tests were performed at 300 $^{\circ}$ C, with a current density of 1.0                   |

|             | MA/cm <sup>2</sup> 102                                                                       |

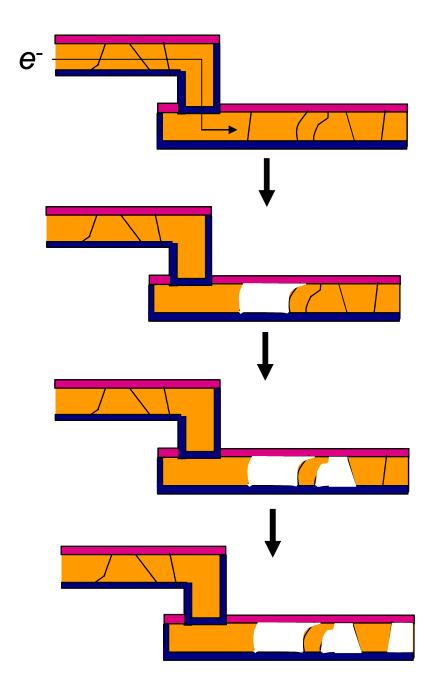

| Figure 6.9  | Schematics of void evolution in M1 trench for dual damascene Cu                              |

|             | interconnects with SiON filling layer                                                        |

| Figure 6.10 | Focused Ion Beam (FIB) microscope image showing EM-induced voids                             |

|             | near cathode in M1 trench for an 60-nm wide interconnect with SiON                           |

|             | filling layer                                                                                |

| Figure 6.11 Cumulative failure distribution function (CDF) plots with different |                                                                                                                      |

|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|

|                                                                                 | barrier processes and thicknesses for down stream electron flow for M1                                               |

|                                                                                 | width of 60 nm through SiON filling. EM tests were performed at 240                                                  |

|                                                                                 | $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup>                                                       |

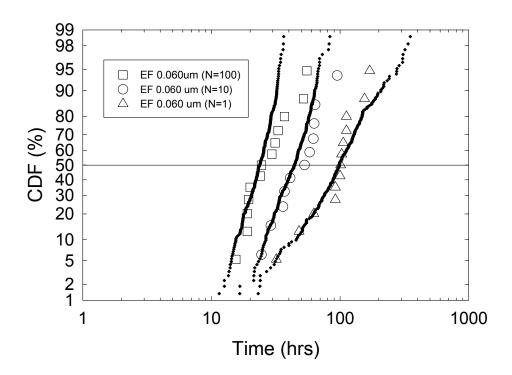

| Figure 6.12                                                                     | Cumulative failure distribution function (CDF) plots of multi-linked (EF)                                            |

|                                                                                 | structures with different number of line segments for down stream                                                    |

|                                                                                 | electron flow for M1 width of 60 nm through SiON filling. EM tests                                                   |

|                                                                                 | were performed at 240 $^{\circ}$ C, with a current density of 1.0 MA/cm <sup>2</sup> .106                            |

| Figure 6.13                                                                     | EM lifetimes as a function of test temperature for the Cu interconnects                                              |

|                                                                                 | with different line widths under the current density of 1.0 MA/cm <sup>2</sup> . The                                 |

|                                                                                 | activation energies were found to be 0.79 eV and 0.80 eV for the fine                                                |

|                                                                                 | lines and standard lines, respectively                                                                               |

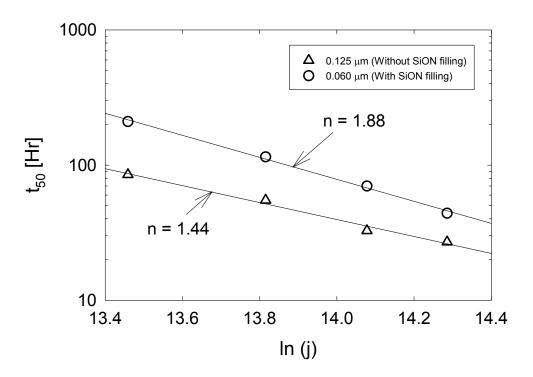

| Figure 6.14                                                                     | EM lifetimes as a function of current density for the Cu interconnects                                               |

|                                                                                 | with different line widths at 240 $^{\circ}\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!\!$ |

|                                                                                 | values (n) were found to be 1.88 and 1.44 for the fine lines and standard                                            |

|                                                                                 | lines, respectively                                                                                                  |

## **Chapter 1: Introduction**

RC delay problem accelerated the industry-wide move to replace aluminum (Al) interconnects with copper (Cu) interconnects for its superior electrical conductivity. However, compared with the natural passivating oxide that forms over Al free surfaces, Cu oxide layer cannot act as a self-protecting barrier layer to Cu due to its unstable and weak mechanical properties. Chemical Mechanical Polishing (CMP), which comprises one of the unit processes in the Cu damascene interconnect fabrication, generates significant amount of process defects on the upper surface of Cu lines. These two factors make the top interfaces of Cu to become the dominant diffusion path. To further improve the RC delay, conventional oxide dielectric was replaced by low-k dielectrics in the industry. With continued line scaling and the implementation of low-k dielectrics, the current density and interface area to volume ratio further increased. This increases the interfacial diffusion and decreases the electromigration (EM) lifetime. Therefore, it is important to investigate the scaling effect and the related process effect on EM reliability in Cu/low-k interconnects.

#### 1.1 ELECTROMIGRATION FUNDAMENTAL

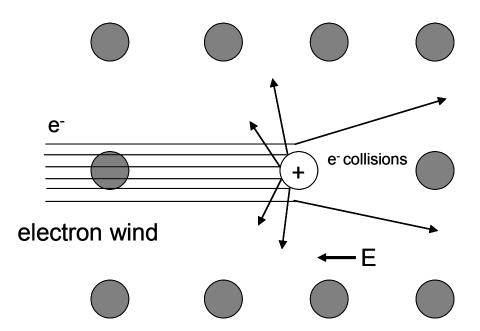

Electromigration (EM), known to be the most serious and persistent reliability issue, describes an atomic diffusion phenomenon in metal (such as Al, Cu) caused by an external direct current (DC) driving force [1]. Without the external driving force, metal atoms are in the state of random motion. With the electrical current flow through the metal wire, electrons collide with metal ions leading to an electron wind force as shown in Figure 1.1.

Figure 1.1 Schematic of the driving force of electromigration in metal wire. With the electric field E, electrons collide with metal atoms in the electron flow direction resulting in EM phenomenon.

The electron wind force causes the cathode of the metal line to become depleted.

The EM driving force can be expressed as

$$F_{\rm e} = Z^* e E = Z^* e \rho j \,,$$

(1.1)

where E is the electric field, e is the charge of an electron,  $Z^*$  is the effective charge number,  $\rho$  is the electrical resistivity, and j is the current density. The atomic flux  $(J_e)$  driven by the EM driving force  $(F_e)$  can be written as

$$J_{\rm e} = n v_{\rm d} \,, \tag{1.2}$$

where n is the atomic density, and  $v_d$  is the drift velocity. The drift velocity of moving metal ions can be expressed using the Nernst-Einstein relation:

$$v_d = \mu F_{eff} = \frac{D_{eff}}{kT} Z^* e E = \frac{D_{eff}}{kT} Z^* e \rho j,$$

(1.3)

where  $\mu$  is the atomic mobility,  $D_{eff}$  is the effective diffusivity of metal ion and k is the Boltzmann constant, and T is the absolute temperature. Two parameters in Equation 1.3 determine the drift velocity of metal atoms and in turn the EM lifetime. The first is current density j which will continue to increase with line scaling as outlined by the International Technology Roadmap for Semiconductors (ITRS) [2]. The second is the effective diffusivity  $D_{eff}$  of moving ions. Basically, EM phenomenon is a result of metal mass transport, therefore, mass-transport pathway is a major parameter to consider. EM can occur through a number of pathways such as surface, interface, grain boundary, and lattice. The effective diffusivity  $D_{eff}$  in Cu interconnects can be expressed by combining all these pathways as [3]

$$D_{eff} = n_B D_B^* + D_I^* \delta_I \frac{1}{h} + D_S^* \delta_S \left( \frac{2}{w} + \frac{1}{h} \right) + D_{GB}^* \left( \frac{\delta_{GB}}{d} \right) \left( 1 - \frac{d}{w} \right), \tag{1.4}$$

where the subscripts identify pathways of diffusion by B = bulk, I = Cu/Ta interface, S = un-coated Cu surface, GB=grain boundary.  $\delta_I$  is the width if the interface,  $\delta_s$  is the width of the surface, and  $\delta_{GB}$  is the width of grain boundary, d is the grain size, w is the line width, and h is the line thickness: and  $n_B$ ,  $\delta_I/h$ ,  $\delta_s(2/w+1/h)$ ,  $(\delta_{GB}/d)(1-d/w)$  are the fraction of atoms diffusing through the bulk, interface, surface, and grain boundary of the line, respectively.

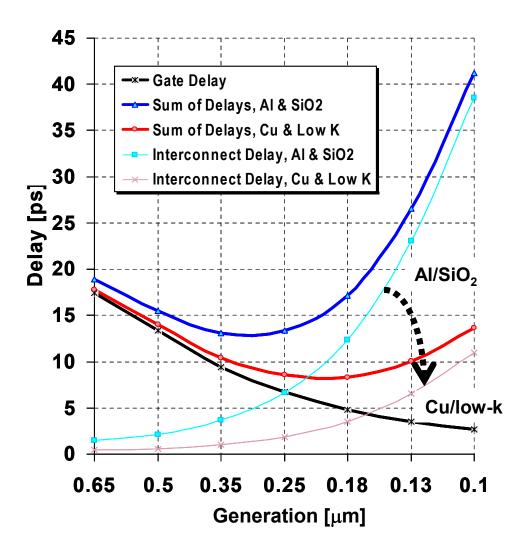

To reduce *RC* delay, new metals and dielectrics are needed to maintain the IC performance. Industry wide, copper (Cu) interconnects have replaced aluminum (Al) for their superior electric conductivity and thermal stability [1,4]. In addition, materials with low dielectric constant (low-k) were developed to replace the silicon oxide which has higher k [5]. Figure 1.2 shows a significant reduction of *RC* delay with incorporation of Cu and low-k dielectric compared with Al and silicon oxide [6,7].

Figure 1.2 Gate and interconnects delay as a function of generation. With implementation of Cu and low-k dielectrics, the total delay was significantly reduced, compared with Al/SiO<sub>2</sub> interconnects [6].

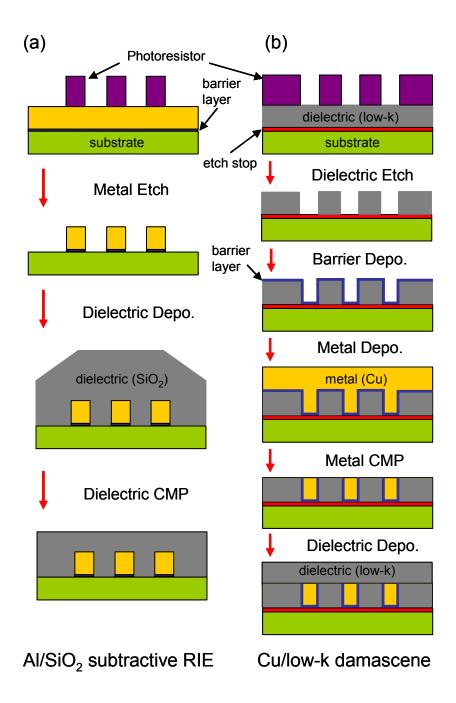

The traditional subtractive etching approach used to form Al metal lines can not be used to form the Cu interconnect structure due to the difficulty of RIE of Cu structures [4]. To build a Cu interconnect, a damascene process was developed by the industry. The comparison between conventional RIE process for Al interconnects and single damascene

process for Cu interconnects is shown in Figure 1.3. The advantage of the damascene process is that this process can be extended to deep submicron line dimensions with a high aspect ratio. However, the damascene process is a high-cost manufacturing process which requires accurate process control.

Figure 1.3 Comparison of (a) conventional RIE process for Al interconnects with (b) damascene process for Cu interconnects.

Several dual damascene integration schemes have been developed, which can generally be categorized as either "via first" or "trench first" depending on which pattern is initially delineated [4]. Via first approach has been widely adopted for small geometry devices. In the dual damascene process, the conductor (trench) and via are formed prior to deposition of the metal barrier/Cu seed/Cu fill. Therefore, only one metal fill and one metal CMP step are required for each level of interconnect, resulting in lower via resistance and improving reliability over that of the single damascene process. The disadvantages of the dual damascene approach include higher aspect ratios for etch/fill and more complicated integration schemes.

In addition to Cu metallization, implementation of low-k dielectric is one of the prominent aspects of the advanced interconnects. The implementation of low-k material to replace silicon oxide resulted in further reduction of the *RC* delay in a microelectronics device, and eventually reduced the number of metal levels for the same amount of device functionality. However, the low-k dielectric generated a number of problems including thermally or mechanically induced cracking or delamination [8], moisture absorption [9], current leakage and voltage breakdown reliability issues [10], poor mechanical strength, process complexity, and etch damage.

Compared with Al/oxide, Cu/low-k interconnects offered significant performance and reliability improvement but presented integration and reliability challenges. Since Cu atoms diffused into low-k dielectrics easily, Cu lines must be encapsulated with metallic (such as Ta, TaN) and dielectric (such as SiN, SiC) diffusion barriers to avoid corrosion and electric leakage between adjacent metal lines [11-15]. This requires optimization of fabrication processes such as dielectric etch, chemical mechanical polishing, copper/barrier metal deposition process and dielectric barrier deposition in order to produce chemically and mechanically stable interconnects.

#### 1.2 STATISTICAL ANALYSIS OF EM USING MULTI-LINKED STRUCTURE

#### 1.2.1 Statistical Measurement of EM Threshold in Cu Interconnects

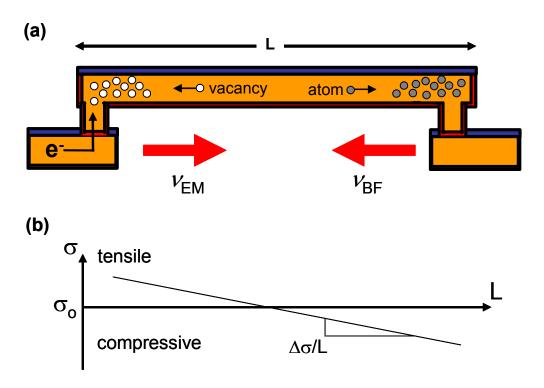

Under EM stress, the atomic flux driven by EM generates a back flow of metal atoms in the direction opposite to the EM flux. Suppose a Cu line is completely encapsulated by a capping layer on top and barrier layer at the sidewall and bottom as shown in Figure 1.4. During EM testing, the EM electron wind force pushes the Cu atoms toward the anode end while vacancies migrate toward the cathode end. Accordingly, the stress state becomes gradually compressive at the anode and tensile at the cathode compared with the initial stress ( $\sigma_0$ ) state [16].

Figure 1.4 (a) Mass transport in the Cu line encapsulated by the capping layer and barrier layer. (b) Stress state for the Cu line under EM upon reaching steady-state stress.

During EM, the drift velocity of moving ions,  $v_{EM}$ , can be expressed using the Nernst-Einstein relation:

$$v_{EM} = \frac{D_{eff}}{kT} Z * ej\rho, \qquad (1.5)$$

where  $D_{eff}$  is the effective diffusivity,  $Z^*$  is the effective charge, e is the electronic charge, f is the current density, f is the electrical resistivity of metal (Cu), f is Boltzmznn's constant, f is the ambient temperature. As shown in Figure 1.4, the back-flow stress generated by atoms with a drift velocity (f0 opposes the net EM drift velocity. Accordingly, the net atomic drift velocity (f0 under EM can be expressed by the Blech model as the following [45,46]:

$$v_{d} = v_{EM} + v_{BF} = \frac{D_{eff}}{kT} \left[ Z * ej\rho - \frac{\Omega \Delta \sigma}{L} \right], \tag{1.6}$$

where  $\Omega$  is the atomic volume,  $\Delta \sigma$  is the back-flow stress induced by EM, L is the metal line length.

As the metal line length decreases under a constant back-flow stress,  $\Delta \sigma$ , the steady-state stress gradient,  $\Delta \sigma/L$  increases. Once the back-flow stress gradient becomes large enough to compensate the EM flux, the net metal atomic flux will be zero [17-20]. The critical product  $(jL)_c$  defined for this condition can be deduced from Equation (1.6).

$$(jL)_{c} = \Omega \,\Delta \sigma / Z^{*}e\rho \,, \tag{1.7}$$

The  $(jL)_c$  product of Cu/low-k interconnects can be dominated by the confinement of the surrounding layers including the barrier and capping layers, while the mechanically weak low-k dielectric provides little confinement. Obviously, to improve EM lifetime, the net atomic drift velocity needs to be reduced. One way to reduce the net atomic drift velocity is to increase the stress gradient in the Cu line,  $\Delta \sigma / L$ . Thus, a conformal and reasonably thick barrier and capping layers will increase the effective modulus to improve the EM lifetime for Cu/low-k interconnects.

### 1.2.2 Statistical Measurement of Early Failure in Cu Interconnects

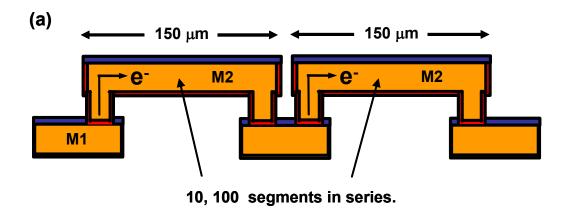

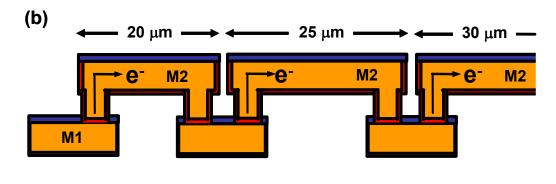

The early failure, so-called weak-mode failure, occurs at an earlier time than expected according to a mono-modal failure distribution [21-25]. Normally, the weak-mode failure shows about one order of magnitude shorter lifetime and smaller population than those of the strong-mode failure. Thus, the presence of weak-mode failures can seriously degrade EM reliability for Cu/low-k interconnects. The advantage of the multi-linked test structure is that an extremely small population of early failures can be detected. For example, using only single link (N=1) structures, it would take 1,000 samples to yield 3 early failures, on the average, to detect 0.3 % early failure. However, the same result can be reached by only 10 samples of N=100 multi-linked structure. Therefore, the testing time can be significantly reduced by multi-linked structures. In these test structures, long 150-µm M2 lines were connected to short 10-µm M1 lines and vias. Ten (N=10) and one-hundred (N=100) single component test structures were connected in series. EM tests using both single component and multi-linked test structures were performed to determine the statistics of the weak-mode failure and the strong-mode failure separately.

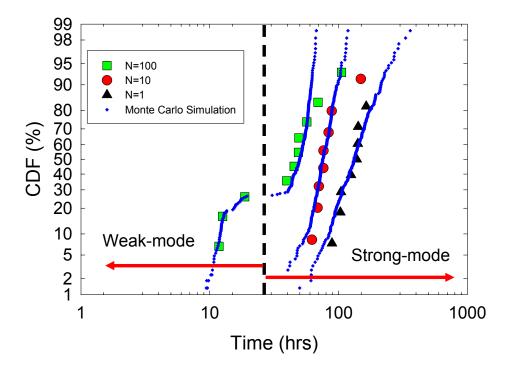

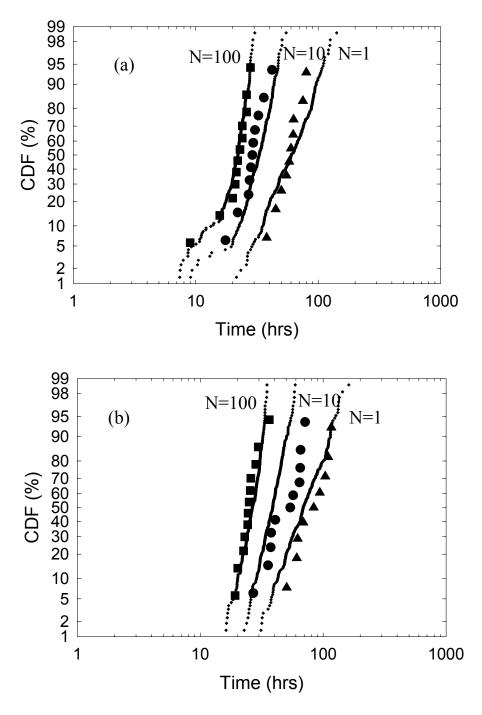

Figure 1.5 shows a Cumulative Failure Distribution (CDF) plot for 0.25-μm Cu/low-k interconnects. The EM test was performed at 330 °C, with a current density of 1.0 MA/cm². With increasing number of line segments, the probability of line failures increased, and the EM lifetime decreased. It was clearly seen that two different failure mechanisms were involved in the test samples. Monte Carlo simulation was used to derive the lifetime and failure statistics for the strong-mode and the weak-mode as a function of number of line segment, N [26-29]. Monte Carlo simulation generates random lifetimes for N line segments. Since the N line segments are connected in series, the first failed segment determines the lifetime for the whole structure. In such system, the random-failure time can be expressed as

$$\tau = \min \left[ \tau_1, \dots, \tau_N \right], \tag{1.8}$$

where  $\tau_i$  (=1, . . . , N) are the potential random failure times from a population of N interconnects. This idea comes from the so-called Weakest Link Approximation (WLA) so that the weakest link in the multi-linked structure determines the failure of the entire chain

$$F_N(t) = 1 - (1 - F_I(t))^N$$

, (1.9)

where N is the number of elements in the series and  $F_I(t)$  is the CDF for single elements. Thus, if the CDF for single elements is identified, CDFs with N elements in series can be generated using Equation (1.9).

Statistical parameters include strong-mode lifetime ( $t_{50}$ ), strong-mode standard deviation ( $\sigma$ ), weak-mode lifetime ( $t_{50}$ ), weak-mode standard deviation ( $\sigma$ ), and the

population of weak-mode. To derive the parameters, two failure modes need to be considered as independent to each other. As shown in Figure 1.5, Monte Carlo simulation can be performed successfully by fitting the experimental CDF plot. Using this method, the  $t_{50}$ 's from the simulation according to the experimental data was found to be 130 hrs and 13 hrs for strong-mode and weak-mode, respectively. In addition, the weak-mode failure for N=1 was found to be 0.3 % of the failure statistics.

Figure 1.5 Cumulative failure distribution (CDF) plots of experimental and Monte Carlo simulation results. The electromigration test was performed at 330  $\,^\circ\!\mathrm{C}$  , with a current density of 1.0 MA/cm². The weak-mode population was about 0.3 %.

#### 1.3 EM RELIABILITY ISSUES RELATED SCALING AND LOW-K DIELECTRICS

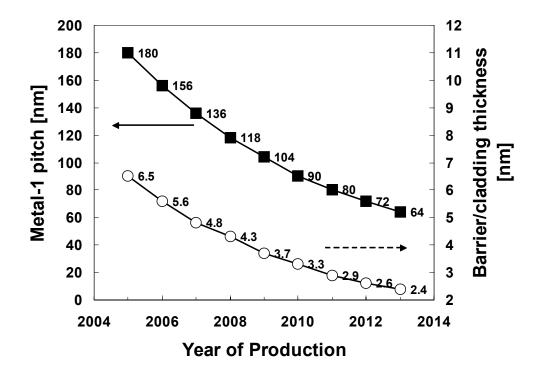

The dominant EM flux occurs along the Cu/capping layer interface [3, 30-33]. This makes EM reliability more serious for Cu interconnects with line scaling due to the increase in surface to volume ratio. Note that, in the case of Al interconnects, the EM performance can be improved with line width scaling due to a stronger "bamboo" like grain structure. This reduces grain boundary network along the metal line through which EM flux can occur. The EM flux in Cu interconnects can be further accelerated by defects caused by chemical mechanical polishing (CMP), which is a necessary step in the damascene process as shown in Figure 1.3(b). For this reason, most recent studies have focused on reducing surface diffusion by adding a capping layer such as CoWP, Pd, CoSnP, Cu<sub>3</sub>Sn etc., on top of the Cu layer after the CMP [34-38]. With surface diffusion so contained, efforts are now focused on a few other areas for controlling EM, such as barrier thickness and via processing. Among these areas, barrier thickness continues to scale according to the *International Technology Roadmap for Semiconductors* (ITRS) [2] shown in Figure 1.6.

Process-related issues on reliability have been observed, including a decrease in early failure lifetime and increase in reliability degradation for Cu/low-k interconnect with line scaling due to the difficulty in process control [39]. Therefore, with the continued scaling of line widths, significant efforts have been focused to develop novel barrier materials and barrier deposition processes [40-42]. Since Ta barrier thickness needs to be reduced to satisfy the projected interconnect performance, the development of a new barrier deposition process for thinner barrier and the evaluation of EM reliability for such process became equally important for the future interconnects [43]. Different Ta barrier deposition processes can lead to different profiles of via bottom, which is the most probable failure initiation site for process-induced early failures [44]. Since most of the

process defects occur at the thin diffusion barrier layer, a uniform and stable barrier is essential for improving EM reliability of Cu interconnects.

Figure 1.6 Metal line and barrier thickness scaling for MPU and ASIC according to the *International Technology Roadmap for Semiconductors* (ITRS) 2006 updated [2].

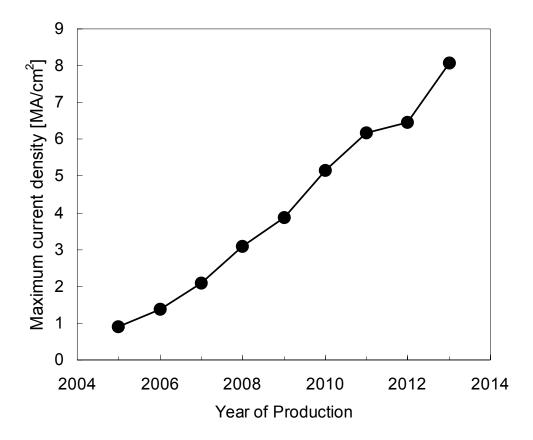

The metal line scaling will lead to increase in current density, which increases the reliability risk due to EM. As shown in Figure 1.7, the operating current density for the intermediate wire will be 3.08 MA/cm<sup>2</sup> with the 59 nm wide interconnects, which is about three times as large as a typical EM test condition for 90 nm node [2]. The trend of increasing current density will be continued for the future microelectronics devices. The

industry is very concerned on the EM reliability issues relating to line width scaling, barrier thickness scaling, and implementation of low-k dielectrics.

Figure 1.7 Maximum current density for MPU and ASIC at 105 °C according to the *International Technology Roadmap for Semiconductors* (ITRS) 2006 updated [2].

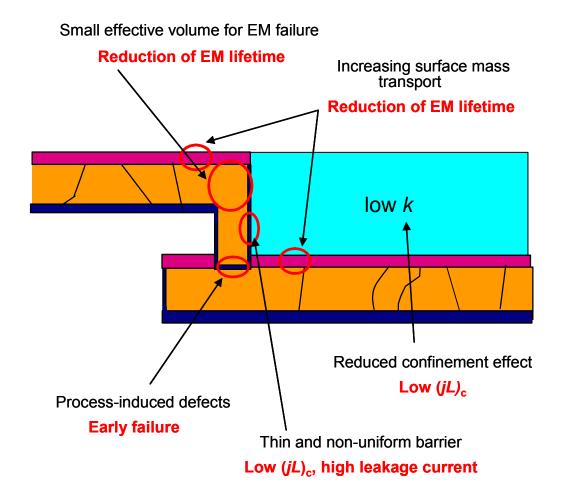

A schematic view of EM reliability issues, relating to line scaling and low-k dielectric, is shown in Figure 1.8. The critical length effect leading to the  $(jL)_c$  product was first advanced by I. A. Blech [45,46], and many studies of Cu/oxide and Cu/low-k interconnects followed [47-51]. They reported that the  $(jL)_c$  product of the Cu/low-k interconnects was lowered because the low-k dielectric was mechanically weaker than

oxide. In addition, as barrier thickness continues to scale down, the confinement of the Cu line will decrease and the  $(jL)_c$  product will be lowered.

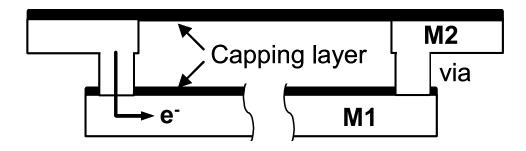

For Cu dual-damascene structure, the upper level trench (Metal-2) and via are formed simultaneously before Cu filling. Therefore, there is no flux divergence at the Metal-2/via interface. However, the dual-damascene process places the flux divergence at the Metal-1/via interface for up-current and down-current situations. This via-bottom flux divergence usually causes reliability problem because only a small amount of material depletion is needed for void formation to cause failure. As the via size shrinks further, via processing can exacerbate plasma damage and process-induced defects at the via bottom and uneven coverage of the barrier layer at the sidewall. These problems are manifested in EM early failures and stress migration failures [52]. It was reported that EM early failure was caused by local defects, which were related to processes such as liner deposition, pre-clean or trench etch [44].

Figure 1.8 Degradation of EM reliability in dual damascene Cu/low-k interconnects due to line scaling and an implementation of low-k dielectrics.

### 1.4 RECENT EM STUDIES

As discussed so far, with decreasing line dimension, the surface to volume ratio of Cu lines increases, and the effective void volume to cause line failure decreases. Therefore, the EM lifetime and the allowable current density will be reduced for future interconnects. Many studies have focused on reducing diffusion along the surface

between Cu and capping layer, such as SiN, known to be the most dominant mass transport path in Cu interconnect. C.-K Hu *et al.* [53] reported an EM lifetime improvement for the Cu lines capped with a 10-nm thick, electroless CoWP layer compared with the Cu lines capped with a 35-nm thick SiC<sub>x</sub>H<sub>y</sub> layer. The improvement of lifetime was about two orders of magnitude. The activation energy for EM with CoWP was 1.9 eV for bamboo-like grain structure, compared with 0.90 eV for SiC<sub>x</sub>H<sub>y</sub> capping [54].

Via width effect on EM reliability was reported, showing longer EM lifetime and tighter distribution of EM lifetime for a wider via [34]. This was attributed to the stable liner connection between via and underlying Cu line.

Using multi-linked EM test structure, observation of early failure was made [55,56]. An EM-induced voids causing weak-mode failure were frequently observed at the via bottom. The post-EM physical failure analysis showed that the less material is required for via voiding compared to that which is required for trench voiding. The activation energy for the weak-mode (early failure) was found to be  $1.00 \pm 0.05$  eV, which was consistent with interface dominant diffusion mechanism [26].

The EM lifetime of Cu/porous low-k interconnects is generally shorter than that of Cu/oxide interconnects under similar EM test conditions and identical test structure dimensions [27], which can be attributed a smaller back flow stress due to less thermomechanical confinement in Cu/low-k interconnects. The lower back-stress is consistent with a smaller effective modulus, which increases the net mass transport and in turn reduces EM lifetime. This led to a small value of  $(jL)_c$  product for Cu/low-k interconnects. The statistics of EM lifetimes and the origin of the lognormal standard deviation of Cu interconnects were reported [57, 58]. In this study, they investigated the effect on EM lifetime statistics due to the variations in void sizes, geometrical and

experimental factors of EM experiment, and differences in the interface diffusivity between lines. This report demonstrated that an optimum grain size and orientation distribution can improve the standard deviation of EM lifetime. Such an optimization is challenging for the deep submicron interconnects.

### 1.5 PROPOSED WORK

Electromigration (EM) is a serious reliability concern for Cu interconnects, particularly with continued scaling and the implementation of porous low-k dielectrics. The ratio of surface and interface area to volume of Cu interconnect will continue to increase with further line width and via scaling. The implementation of porous low-k dielectric weakens the interconnect structure, which further degrades EM performance of the Cu interconnects. The objective of this work is to investigate the effects of process and scaling on EM reliability for Cu/low-k interconnects. EM test structures and EM experimental procedure will be described in Chapter 2. The barrier process effect on EM will be discussed in Chapter 3, and then the effect of barrier thickness and line/via scaling on EM will be discussed in Chapter 4 and 5, respectively. EM reliability for 60 nm wide lines corresponding to 45-nm technology will be investigated for future devices in Chapter 6. Finally, summary and recommendation will be given to conclude this work in Chapter 7.

In Chapter 3, an important and recently introduced Ta barrier deposition process, the so-called barrier-first process, which was developed to produce a more uniform Ta barrier, will be evaluated. A systematic study of the barrier-first process effect on EM has not been previously reported. Since the Ta barrier thickness needs to be reduced in order to satisfy the projected interconnect performance, the development of a new barrier deposition process for thinner barrier and the evaluation of EM reliability for such

process will be equally important for the future development of Cu lines. Different Ta barrier deposition processes based on barrier-first and pre-clean-first will be used to study the barrier process effect on EM reliability. Different barrier processes can lead to different profiles of the via bottom, which is a suspect region for failure initiation in a process-induced early failure. Statistical multi-linked EM test structures will be used to determine the statistics of the weak-mode early failures and the strong-mode failures separately. In this way, the small population of the early failures can be detected. Statistical  $(jL)_c$  product will be determined for samples with different Ta barrier processes to understand how the barrier processes affect the confinement of Cu/low-k interconnects. The microstructures including Ta barrier morphology and EM-induced voids will be analyzed by transmission electron microscopy (TEM) and focused ion beam (FIB) microprobe.

In Chapter 4, the barrier thickness effect on EM reliability for Cu/low-k interconnects will be investigated using multi-linked test structures. The critical  $(jL)_c$  product for Cu/low-k interconnects with Ta barriers ranging from 75 Å to 175 Å in thickness will be measured. In addition, multi-linked early failure structures will be used to quantify the failure statistics for the intrinsic strong-mode failures as well as for the extrinsic weak-mode failures for the different barrier thicknesses. The weak-mode failures are particularly important since the overall lifetime of multi-linked interconnects is controlled by the weakest link, which in practice is dominated by extrinsic process-induced defects.

In Chapter 5, the effects due to via scaling and line scaling on EM reliability for Cu/low-k interconnects will be investigated. Three types of EM test structures varying in line width and via size will be designed for this study. Two types of up-stream electron flow condition and one type of down-stream electron flow condition will be included.

The M2 line width and the via size will be both scaled down from 175 nm to 90 nm for up-stream electron flow condition, while the M1 line width and the via size will be both scaled down from 175 nm to 125 nm for down-stream electron flow condition

In Chapter 6, the EM behavior of ultra fine lines, ~60 nm will be studied. With aggressive device size scaling, the metal-1 half pitch in the interconnects will be reduced to 59 nm in two years. However, EM reliability studies for the fine lines, ~60 nm has not been conducted widely due to the difficulty of processing. In this study, the EM test structure was fabricated by a novel process of pre-filling the trenches with SiON which can delineate 60-nm metal lines using a conventional, wider line lithograph technology. The new process provides a unique metal-1/via interface structure which can eliminate the most probable void formation site responsible for early failures. This projection will be put to test through statistical treatment of the failure data. To investigate the trenchfilling SiON effect on EM reliability, samples with and without SiON filling layer will be tested. Three different line widths; 60 nm, 110 nm, and 185 nm will be fabricated for this purpose. The activation energies for EM in Cu interconnects with different processes need to be determined in order to understand the dominant diffusion pathway. Also, the current density effect on EM reliability, particularly at high current density, will be investigated. This is because the current density continues to increase with the new design rules for microelectronics devices.

# **Chapter 2: Experimental Procedure**

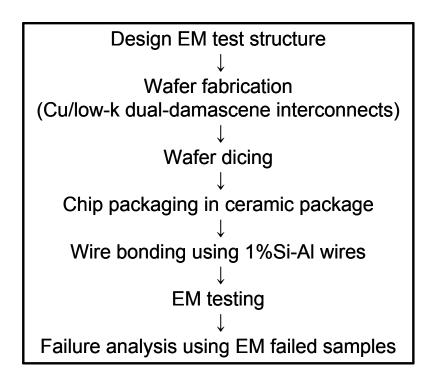

In this chapter, the details of EM experiments are described. The sequence of EM testing is illustrated in Figure 2.1. EM test structures were designed to investigate EM reliability of Cu interconnects. Based on the design, wafer fabrication for two-level interconnects (M1/via/M2) was done on 300 mm wafers using a dual-damascene process. The wafer was diced, the dies mounted on a ceramic package, and the connections between the die and the package were made by wire bonding. EM tests of the packaged samples were performed in a high vacuum chamber. The resistance traces were monitored to determine EM lifetime and study the EM failure mechanisms. From the lifetime data, Cumulative Failure Distribution (CDF) curves were constructed. Physical failure analysis was performed using transmission electron microscopy (TEM) and focused ion beam (FIB). In addition, statistical multi-linked EM test structures are discussed. Using these test structures, the critical line length and statistics of early failure were determined. Finally, the behavior of resistance traces during EM test was discussed.

Figure 2.1 Summary of electromigration testing procedure.

### 2.1 EM TEST STRUCTURE DESIGN

Two-level (M1, via, and M2) EM test structures were designed to investigate EM reliability for Cu interconnects. The EM test structures used are summarized in Table 2.1. Four to six EM patterns were included in a module. The minimum line/via width was 90 nm. Three line widths: 175, 125 and 90 nm were included corresponding to the 130, 90 and 65-nm nodes, respectively. Basic single line EM structures, denoted as DV, occupied six modules. Variations of line length, line width, and current direction were incorporated in the DV modules. To investigate the effect of via scaling on EM reliability, EM structures with different M2 line widths under identical via size were designed. These

structures were included in the VJ module. The details of the VJ structures will be described further in chapter 5.

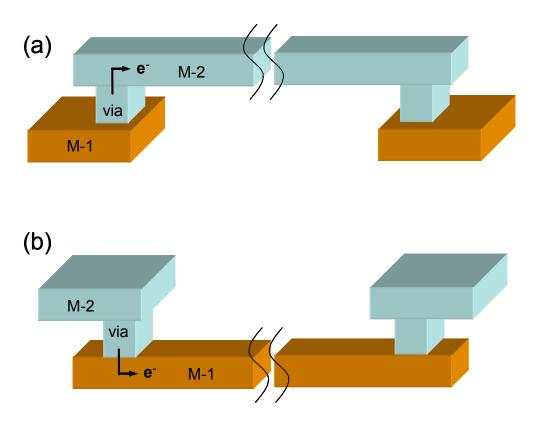

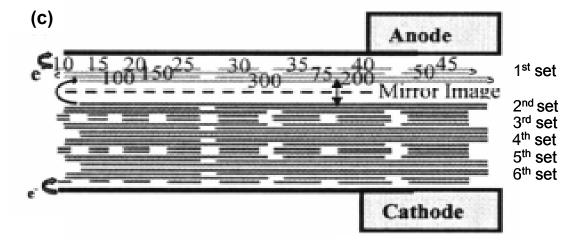

Up stream electron flow structure is shown in Figure 2.2 (a). In this structure, electrons flowed from a wide and short M1 line to a narrow and long M2 line. Thus EMinduced damage for M1 lines can be minimized. Using the up-stream electron flow structure, the void formation and line failure either in the M2 line or in the via can be observed. As shown in Figure 2.2 (b), the down stream electron flow structure was also designed to investigate the void formation and line failure in the M1 line. In this case, EM electrons flowed from the wide and short M2 level to the narrow and long M1 level. In addition to the single line structure which had one stressed line, two types of multilinked EM structures, denoted by EF and LC in the first column of Table 2.1, were included in the EM test modules to investigate critical line length effect and the statistics of early failure in Cu/low-k interconnects. The schematic side views of early failure (EF) and critical length (LC) are shown in Figure 2.3. The first multi-linked structure is an early failure (EF) structure, which contained different number of serial line segments comprising of one (N=1), ten (N=10) and one-hundred (N=100) test elements, respectively. The second multi-linked structure is a critical length (LC) structure, which comprises six repeating sets of multi-linked elements, where each set had the stressing metal 2 (M2) lengths varied from 10 µm to 300 µm, while the connecting metal 1 (M1) line length remained fixed at 5 µm in order to minimize EM damage in the M1 line. As shown in Figure 2.3 (c), 14 different line lengths are included in one set of interconnects with the line lengths of 10, 15, 20, 25, 30, 35, 40, 45, 50, 75, 100, 150, 200 and 300 μm. The schematics shown in Figure 2.2 are up-current electron flow test structures which are designed to investigate EM damage in the trench and/or via on the M2 level. In this structure, stressed M2 lines are narrow and long, while connecting M1 lines remains wide and short. In addition, down-current test structures are designed for EM tests on the M1 level with the pattern of line dimensions reversed to target failures at M1 rather than M2.

Table 2.1 Summary of EM testing structures including up-stream and down-stream electron flow conditions.

| Module            | Test Pattern |            |               |           |             |          |               |           |

|-------------------|--------------|------------|---------------|-----------|-------------|----------|---------------|-----------|

| 1 (DV_N1_M1_0090) | L=10 μm      | L=25 µm    |               | L=50 μm   | L=75 μm     | L=10     | 0 μm          | L=300 µm  |

| 2 (DV_N1_M2_0090) | L=10 µm      | L=25 µm    |               | L=50 µm   | L=75 μm     | L=100 µm |               | L=300 µm  |

| 3 (DV_N1_M1_0125) | L=10 µm      | L=25 µm    |               | L=50 µm   | L=75 µm     | L=100 µm |               | L=300 µm  |

| 4 (DV_N1_M2_0125) | L=10 µm      | L=25 µm    |               | L=50 µm   | L=75 μm     | L=100 µm |               | L=300 µm  |

| 5 (DV_N1_M1_0175) | L=10 µm      | L=2        | 5 μm          | L=50 µm   | L=75 μm     | L=100 µm |               | L=300 µm  |

| 6 (DV_N1_M2_0175) | L=10 µm      | L=2        | 25 μm L=50 μr |           | L=75 μm     | L=100 µm |               | L=300 µm  |

| 7 (VJ)            | M2=0.090     | μm         | M2=0.125 μm   |           | M2=0.175    | μm M2    |               | =0.250 µm |

| 8 (VJ_M2_0250)    | W=0.090      | μm W=      |               | =0.125 μm | W=0.175 μm  |          | W=0.250 μm    |           |

| 9 (VJ_via_0090)   | M2=0.090     | 0.090 μm M |               | =0.125 µm | M2=0.175 μm |          | M2=0.250 μm   |           |

| 10 (LC_M1)        | W=0.125      | W=0.125 μm |               | =0.175 μm | W=0.250 μm  |          | W=0.500 μm    |           |

| 11 (LC_M2)        | W=0.125 μm   |            | W=0.175 μm    |           | W=0.250 μm  |          | W=0.500 μm    |           |

| 12 (EF_M1_0090)   | N=1          |            | N=10          |           | N=100       |          | Temp. monitor |           |

| 13 (EF_M2_0090)   | N=1          |            | N=10          |           | N=100       |          | Temp. monitor |           |

| 14 (EF_M1_0125)   | N=1          |            | N=10          |           | N=100       |          | Temp. monitor |           |

| 15 (EF_M2_0125)   | N=1          |            | N=10          |           | N=100       |          | Temp. monitor |           |

| 16 (EF_M1_0175)   | N=1          |            | N=10          |           | N=100       |          | Temp. monitor |           |

| 17 (EF_M2_0175)   | N=1          |            | N=10          |           | N=100       |          | Temp. monitor |           |

Figure 2.2 Schematics of EM test structure with (a) up-stream electron flow, and (b) down-stream electron flow condition.

Figure 2.3 Schematics of (a) side view of early failure (EF) EM test structure, (b) side view of critical length (LC) EM test structure, and (c) top view of critical length (LC) EM test structure for up-current EM test condition.

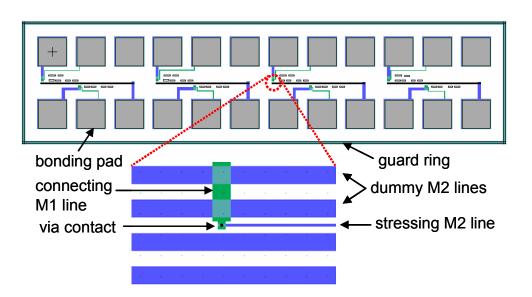

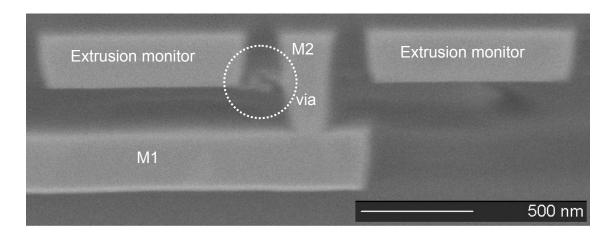

Figure 2.4 shows one of the EM testing modules with up-stream electron flow condition. The module is 2 mm long and 0.5 mm wide. For this particular module, 24 bonding pads (12 by 2) and 4 EM test patterns are arranged. Hence, a maximum of 6 bond pads can be assigned to each test pattern. Since the inter-layer dielectric (ILD) material is porous low-k, which is susceptible to water and oxygen, a guard ring was implemented along the outside of bonding pads. 0.85 µm wide dummy M2 lines, so called extrusion monitoring lines, were inserted on each side of the stressing M2 line for detecting extrusion failure at the anode. With the dummy lines, the uniformity of chemical mechanical polishing (CMP) can be improved by reducing the dishing issue usually observed on mechanically weak low-k dielectric.

Figure 2.4 EM testing module showing a guard ring, bonding pads, and EM test patterns. An enlarged view shows EM test lines and wide dummy lines. Blue, green, and black correspond to the color of M2 line, M1 line, and via, respectively.

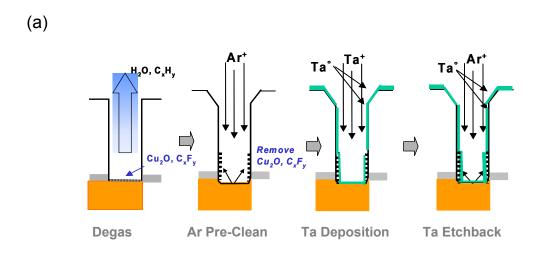

### 2.2 WAFER FABRICATION AND EM TEST

Based on the designs described so far, test samples were fabricated on 300-mm wafers using a dual-damascene process at SEMATECH. The inter-layer-dielectric (ILD) materials used for the study were porous MSQ low-k dielectric with  $k \sim 2.3$ , and silicon oxide with  $k \sim 3.9$ . The patterned wafers were diced to fit onto a ceramic package. The individual dies were attached on a ceramic package using silver paste, and then cured at 350 °C, for 30 minutes in a vacuum oven. A packaged test structure was electrically connected to a ceramic package by wire bonding. A wedge bonder with 25  $\mu$ m thin Al-1%Si wire was used for the wire bonding. The wire bonded packages were inserted in the lead frame sockets in the EM chamber.

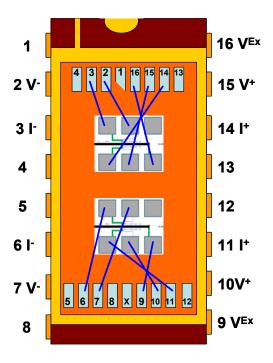

The schematic of the wire bonding connections is shown in Figure 2.5. The ceramic package used for this study is a 16-pin side braze package from the Kyocera Corporation. Normally two test patterns were attached to a package. The upper test structure was controlled by the upper five channels on the package, and the lower test structure was controlled by the lower five channels. Blue lines represent Al wires. Constant current was generated by a constant current controller sent through the EM test structure, and the current was monitored between the I- and I+ channel. Since constant current was applied to the EM structure regardless of the resistance of EM structure, the voltage between V- and V+ increased with increasing resistance due to EM-induced voiding. EM resistance change was deduced using the voltage changes and the constant current applied to the EM test pattern. In addition, voltage change between V- and V<sup>ex</sup> was monitored to detect EM sample failure by Cu extrusion at the anode.

Figure 2.5 Schematic of 16-pin side braze package with two EM samples and wire bonding configuration for package-level EM test.

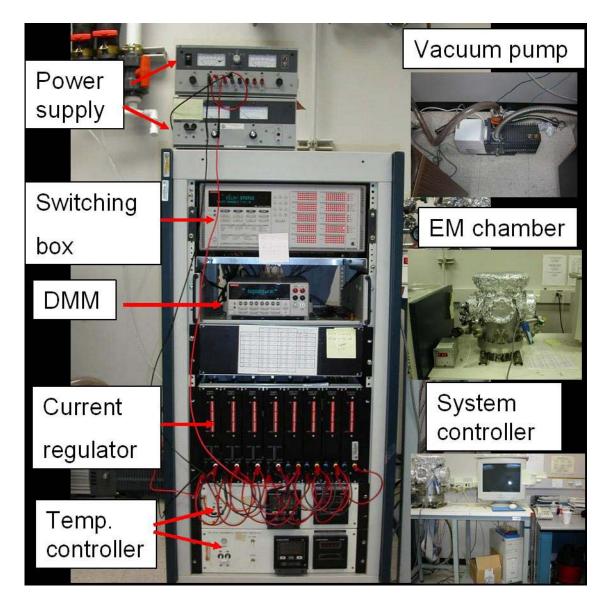

As shown in Figure 2.6, EM testing was performed in a vacuum chamber in a pure nitrogen environment at 20 torr. Up to 64 samples can be tested in the chamber at a time. Two heating coils were installed in the chamber. The primary heating coils located at the top and bottom plate are used to set the target test temperature. The secondary heating coils located at chamber sidewall are used to significantly reduce the temperature gradient in the chamber. The current regulator maintained the constant current density condition during the EM tests. A switching box (Keithley 7002 Switch System) selected the channel of the sample under test in sequence. A DMM (Keithley 2000 Multimeter) measured the voltage value of each channel. A PC system controller equipped with National Instruments LabView controlled data acquisition and data analysis.

Figure 2.6 Package-level EM testing system.

Most of EM tests were performed at a current density of  $1.0~\text{MA/cm}^2$ . The actual current value that passed through the samples was calculated by assuming uniform metal width and height. For example, the EM current for the finest lines in this study - 60 nm in width and 150 nm in height - was approximately 90  $\mu$ A. To do the accurate EM testing,

the current regulator was upgraded to improve on the stability and small current sources capabilities. The measured current stability of the upgraded current regulator was 90  $\pm$  0.001  $\mu A$  for the 60-nm wide lines.

The chamber temperature was ramped up at 3 °C/min to the target temperature. Resistance increase due to void formation was monitored to determine the EM lifetime. The time at the first appreciable line resistance increase (usually ~10 %) was taken as the EM lifetime. EM experiment was terminated after all samples failed. Some EM experiments were stopped right after EM resistance increase in order to observe EM voiding; otherwise, EM-induced void could not be found due to the severe joule heating. The observation of microstructure and EM-induced voids was performed by a transmission electron microscope (TEM) and a focused ion beam (FIB) microprobe.

## 2.3 MEASUREMENT OF (JL)<sub>C</sub> PRODUCT

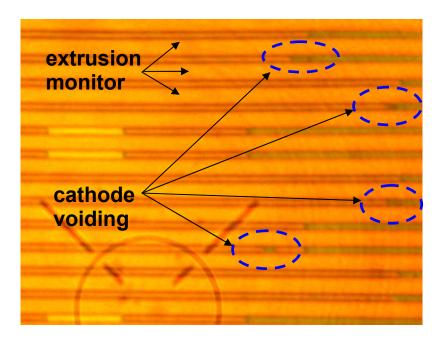

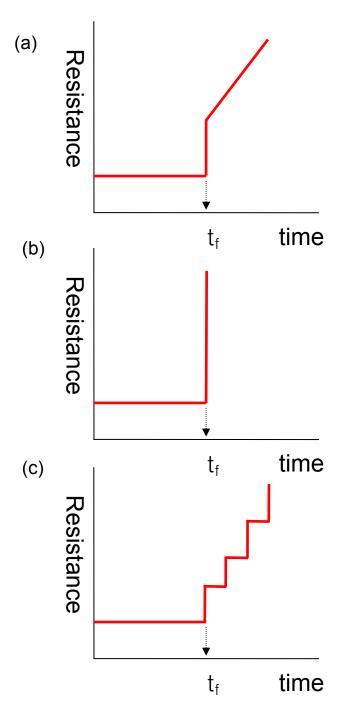

In order to obtain a  $(jL)_c$  product experimentally, the multi-linked statistical structures shown in Figure 2.3 (c) were tested under specific test conditions. After the test, EM-induced voids at the cathode end were monitored using an optical microscope. The observed image is shown in Figure 2.7 where the fine stressing lines were located between the wide extrusion monitoring lines. The cathode voids were found either at or nearby the cathode end. Since 6 repeating sets of multi-linked structures were included in a LC structure, 120 interconnects of each line length ranging from 10 to 300  $\mu$ m were tested at one time when 20 samples were loaded in the EM chamber. This arrangement provided enough data to determine the  $(jL)_c$  product.

Figure 2.7 Optical microscope image showing EM-induced voiding around cathode end for a statistical multi-linked EM test structure. The stressing fine lines are located between the wide extrusion monitoring lines. The EM test was performed at 330 °C, with a current density of 1.0 MA/cm<sup>2</sup>.

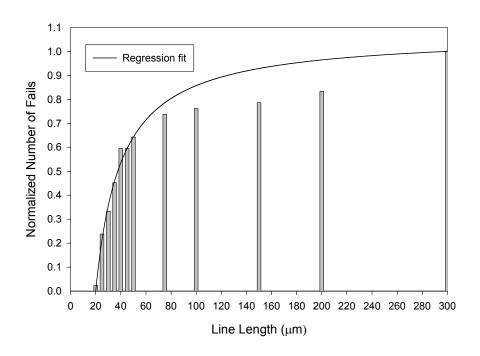

The entire set of EM tested lines were inspected, and the number of fails normalized by the total number of the given line lengths were plotted as shown in Figure 2.8. It was assumed that each metal line was failed by open circuit when a void was found at the cathode end. As expected, the probability of void formation decreased with the decreasing line length due to increasing back-flow stress gradient in the shorter lines. Eventually, no void was found for the lines shorter than 20 µm.

In order to determine the  $(jL)_c$  product value, statistical analysis was performed and the resulting regression curve was superimposed as shown in Figure 2.7. Assuming that the probability of interconnect failure under EM driving force for a given line length,  $L_i$ , and current density, j, is proportional to its average drift velocity, the failure probability,  $P(j,L_j)$  can be expressed as [26,50]

$$P(j, L_i) = C \left[ \frac{v_d(j, L_i)}{v_d(j, L_M)} \right] = C \left[ \frac{1 - L_c / L_i}{1 - L_c / L_M} \right], \quad \text{for } L_i \ge L_c,$$

(2.1)

where  $v_d$  is the average drift velocity for Cu ions at a given j and L under a steady-state back stress condition,  $L_M$  is the length of the longest interconnect in the test structure (i.e., 300 µm),  $L_c$  is the critical length, and C is a normalization constant.

The normalized number of fails can be deduced from Equation (2.1)

$$\frac{P(j, L_i)}{C} = \left[ \frac{1 - L_c / L_i}{1 - L_c / L_M} \right]. \tag{2.3}$$

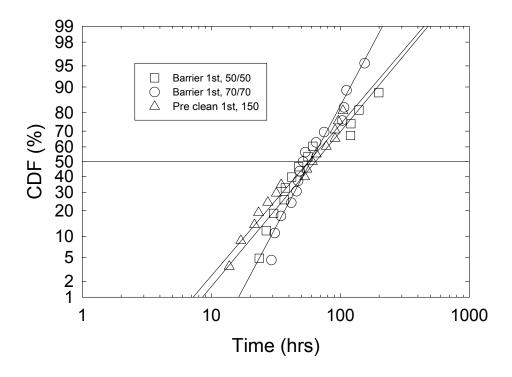

The regression fitting based on the Equation (2.3) shows that the critical length,  $L_c$  is approximately 20  $\mu$ m. With a current density of 1.0 MA/cm<sup>2</sup>, the statistical  $(jL)_c$  product for this sample was approximately 2000 A/cm.