Aalborg Universitet

## Binary-Quintuple Progression Based 12-Switch 25-Level Converter With Nearest Level Modulation Technique for Grid-Tied and Standalone Applications

Mishra, Nidhi; Yadav, Shivam Kumar; Singh, Bhim; Sanjeevikumar, Padmanaban; Blaabjerg, Frede

Published in: I E E E Transactions on Industry Applications

DOI (link to publication from Publisher): 10.1109/TIA.2020.3041563

Publication date: 2021

Document Version Accepted author manuscript, peer reviewed version

Link to publication from Aalborg University

Citation for published version (APA): Mishra, N., Yadav, S. K., Singh, B., Sanjeevikumar, P., & Blaabjerg, F. (2021). Binary-Quintuple Progression Based 12-Switch 25-Level Converter With Nearest Level Modulation Technique for Grid-Tied and Standalone Applications. *I E E Transactions on Industry Applications*, *57*(3), 3214 - 3223. [9275358]. https://doi.org/10.1109/TIA.2020.3041563

#### **General rights**

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal -

#### Take down policy

If you believe that this document breaches copyright please contact us at vbn@aub.aau.dk providing details, and we will remove access to the work immediately and investigate your claim.

# Binary-Quintuple Progression Based Twelve Switch Twenty-Five Level Converter with Nearest Level Modulation Technique for Grid-Tied and Standalone Applications

Nidhi Mishra, Member IEEE, Shivam Kumar Yadav, Student Member, IEEE, Bhim Singh, Fellow, IEEE, Sanjeevikumar Padmanaban, Senior Member, IEEE, and Frede Blaabjerg, Fellow, IEEE

Abstract—This paper introduces a cascaded packed U cell (CPUC) multilevel converter (MLC) to achieve a higher-level count in converter voltage with a minimum number of switches. Here, two five-level PUC topologies are connected in a cascaded manner to obtain twenty-five levels in its output converter voltage. The switch count in CPUC is reduced to 12, as compared to the number of semiconductor devices used for obtaining 25 levels in converter output. A binary-quintuple progression is used for selection of voltage ratios between DC voltage sources, and capacitors. CPUC is operated at low-frequency switching, using the nearest level modulation technique (NLMT). The fundamental switching frequency ensures reduced switching losses as compared to pulsewidth modulation (PWM) schemes. The converter performance is analyzed for grid-tied and standalone applications. The performance parameters such as total harmonic distortion (THD) of converter voltage and THD of grid/load current are examined. The CPUC configuration is modeled and simulated in MATLAB/Simulink, and test results are taken using OPAL-RT test bench. The acquired simulation and test results confirm viability, practicability, acceptability, and cost-effectiveness of CPUC-MLI converter over existing MLC topologies for efficient power conversion.

*Index Terms*— Cascaded Packed U cell, Nearest Level Modulation, Photovoltaic Array, Power Quality,

#### NOMENCLATURE

| $V_{dcl}$      | DC voltage source of converter I     |

|----------------|--------------------------------------|

| $V_{dc2}$      | DC voltage source of converter II    |

| $S_w$          | Switch function for ON and OFF state |

| $S_n$          | Switch $n^{th}$ in the converter     |

| $S_{nc}$       | Complementary of switch $S_n$        |

| $P_{1}-P_{12}$ | Twelve positive levels               |

| $N_1 - N_{12}$ | Twelve negative levels               |

| $i_g$          | Grid current                         |

| Vg             | Grid voltage                         |

| vL             | Load voltage                         |

| $i_{\rm L}$    | Load current                         |

|                |                                      |

This work was supported by Department of Science and Technology (DST) under FIST scheme with grant number: RP03195, in part by OPAL-RT: RP03253, Joint UK-India Clean Energy (JUICE) : RP03391, Indo-US Project: RP03443, SERI: RP03357 and J.C. Bose Fellowship : RP03128. (*Corresponding Author: Nidhi Mishra*)

N. Mishra, S. K. Yadav, and B. Singh are with the Department of Electrical Engineering, Indian Institute of Technology Delhi, New Delhi 110016, India

(e-mail:nidhimishra218@gmail.com;shivamyadaviitdelhi@gmail.com; bsingh@ee.iitd.ac.in).

S. Padmanaban is with the Center for Bioenergy and Green Engineering, Department of Energy Technology, Aalborg University, Esbjerg 6700, Denmark (e-mail: san@et.aau.dk).

F. Blaabjerg is with the Center of Reliable of Power Electronics, Department of Energy Technology, Aalborg University, Aalborg 9220, Denmark (e-mail: fbl@ et.aau.dk).

| igref          | Reference grid current                             |

|----------------|----------------------------------------------------|

| $I_{gdc}$      | Reference peak of the grid                         |

| $i_n$          | Current in <i>n</i> <sup>th</sup> switch           |

| $v_{ab}$       | The voltage across node ab                         |

| $v_{bc}$       | The voltage across node <i>bc</i>                  |

| $V_{cd}$       | The voltage across node <i>cd</i>                  |

| Vef            | The voltage across node <i>ef</i>                  |

| Vfg            | The voltage across node $fg$                       |

| Vgh            | The voltage across node gh                         |

| $T_L$          | Total number of levels                             |

| L              | Level obtained from each cell                      |

| Ν              | Number of PUC cells                                |

| $V_{mli}$      | Output Converter Voltage of CPUC                   |

| $C_{I}$        | The capacitor of converter I                       |

| $C_2$          | The capacitor of converter II                      |

| $V_{cl}$       | The voltage across capacitor I                     |

| $V_{c2}$       | The voltage across capacitor II                    |

| $i_{cl}$       | Current across capacitor I                         |

| $i_{c2}$       | Current across capacitor II                        |

| $R_p$          | Parasitic resistance                               |

| $L_f$          | Interfacing inductance                             |

| $I_{d1}$       | Compensating component for the balance of $V_{cl}$ |

| $I_{d2}$       | Compensating component for the balance of $V_{c2}$ |

| $I_{dT}$       | The resultant total peak of the grid current       |

| Vref           | Modulating Signal                                  |

| Ν              | Number of PUC Cells                                |

| Μ              | Number of positive or negative levels              |

| e <sub>r</sub> | The error between reference and actual signal      |

| $k_p$          | Proportional gain                                  |

| k <sub>i</sub> | Integral gain                                      |

#### I. INTRODUCTION

ultilevel converters (MLCs) have created a boom in the electrical sector due to a rise in demand for high power energy conversion [1]. These MLCs are introduced due to limitations of larger filter size and losses in a two-level converter. Furthermore, an extension to a higher power level is not possible without a series connection of semiconductor devices. These MLCs enhance level count in converter voltage and make it near to sinusoidal. In MLCs, switching stress becomes less, and the converter lifetime is increased. The wide known topologies of MLCs are cascaded H bridge (CHB), diode clamped MLC and capacitor clamped MLC [2]. CHB has become popular due to modular structure, but for higher levels isolated DC supply and switch count increase rapidly [3]. Moreover, for more isolated DC supplies, it requires phase-shifting transformers and an extra stage of rectification. The system becomes bulkier, which needs proper space and handling. The diode clamped MLC has a single DC source but possesses neutral point balancing issues [4]. Moreover, device count and additional capacitor balancing

remain a challenging issue. Similarly, capacitor clamped has balancing issues and flying capacitors (FCs) increase for higher-level MLCs [5]. The main objective is to optimize the converter configuration to reduce the number of devices. The maximum number of levels with minimum component count remains a potential research area in the field of MLCs. Apart from basic configurations, various new topologies have appeared in reduced device count. Packed U cell (PUC) topology is introduced for achieving reduced switch count. The modified PUC converter with the boost mode is proposed in [6]. The five-level and seven-level PUCs are analyzed using six switches, capacitor and DC source. The extension of PUC in terms of CPUC is required to achieve better MLC configurations [7]. The transformer-based multilevel converters with AC side isolation have a single DC source. The work on the configuration with minimum cost is required in gridconnected and standalone MLC systems. The asymmetric MLCs with the ternary sequence are implemented using unipolar PWM. MLCs have been used for single-phase, and three-phase photovoltaic (PV) fed grid-connected applications. The hybrid cascaded MLC with 1:7 asymmetries is discussed in [8]. A nine-level reduced device count active neutral point clamped (ANPC) is proposed in [9]. This configuration has balancing issues and higher device count and extra floating capacitor with higher levels. Nested multilevel topologies have also come but could not give promising solutions [10]. The novel K type multilevel converter is proposed in with selfbalancing approach [11]. The level doubling network with capacitor fed H bridge modules is implemented in the literature. Such configuration employs extra capacitors to achieve levels in the converter output voltage. A symmetric switched diode MLC topology with minimized switch count is proposed in [12]. The circuit employs six switches, two DC sources and a diode for obtaining seven level output voltage. A 25 level MLC itself requires 48 switches in CHB configuration. The same level generation with diode clamped MLC and flying capacitor MLC, is practically unfeasible due to a large number of switches, clamped diodes, and capacitors. Moreover, using transformer-based MLIs for 25 levels requires a transformer and measures to tackle saturation issues. The asymmetric MLCs use binary, ternary progressions in isolated DC voltages to obtain higher levels. The selection of ratio plays an important role in the level formation. Modular multilevel converters (MMCs) are also used, but these converters have circulating current issues, and each capacitor requires sorting based complex algorithms [13]. The MLC configurations are operated using several control techniques such as synchronous reference frame (SRF) control for grid-connected and standalone systems. A multifunctional control is implemented for CHB multilevel topology in [14]. The current reference control is implemented for standalone and grid-connected systems [15]. The active and reactive power (PQ) control is implemented for MLCs. Within control schemes, modulation techniques based on level shift and phase shift of carrier are employed. The optimization techniques are implemented for optimal switching angles for selective harmonic elimination (SHE) [16]. The fundamental frequency approach is implemented in MLCs for higher levels [17]. Moreover, hybrid carrier PWM techniques for improving power quality are being proposed. The PWM techniques are used in [18] for balanced power distribution in

MLCs. The PWM modulator, controller and optimized configuration are main parts of MLCs. In this paper, two PUCs are cascaded to attain 25 levels in output voltage using six switches in each PUC. The modes of operations and switching states are presented. The converter is tested in standalone and grid-connected mode with current reference unit template control for single-phase applications. The CPUC based MLC is presented with reduced switch count for twenty-five level MLC. This topology is compared with conventional MLCs and makes it a better contender for practical applications. The maximum 25 levels are attained at low switching frequency with a binary-quintuple based approach for selection of voltages. The cascaded converter is tested, and results are validated using OPAL-RT [19-20]. Moreover, a comparison with other topologies is presented with relevant parameters [21]-[27].

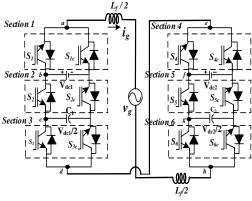

#### II. CASCADED PACKED U CELL CONVERTER

The CPUC converter consists of two five-level PUC cells connected in a cascaded manner, as shown in Fig. 1. Each cell contains six switches, one DC voltage source, and a capacitor. The converter switches states are formed with twelve positive levels, one zero level and negative levels are shown in Table I. CPUC forms twenty-five level in output voltage by the addition of converter I and converter II voltages. The sign convention of converter voltages depends on the direction of grid current, which is assumed going into the grid voltage source. CPUC is divided into six sections connected appropriately for level generating modes. Each section has two switches in an antiparallel configuration. The interfacing inductance is designed according to permissible harmonic current injection in the grid. The switches  $S_{1c}$ -  $S_{6c}$  are complementary for  $S_1$ -  $S_6$ .

Fig.1 System Configuration of CPUC

## A. Modes of Operation

The modes of operation are formed based on the combination of switches of Converter I and Converter II. The nine modes of operation out of 25 states are divided into three parts, as shown in Figs. 2-4. Fig. 2 (a) shows state zero voltage source and capacitor are not part of the circuit, and zero levels are attained. Fig. 2 (b) shows state N<sub>1</sub> where current flows through the capacitor and DC voltage source of first PUC converter with converter voltage of  $-V_{dc1}+V_{dc1/2}$ . Similarly, Fig. 2(c) discuses mode of operation for state N<sub>4</sub>, where S<sub>1c</sub>, S<sub>2</sub>, S<sub>3c</sub>, S<sub>4</sub>, S<sub>5c</sub>, and S<sub>6</sub> are turned ON.

<sup>0093-9994 (</sup>c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on December 08,2020 at 12:56:20 UTC from IEEE Xplore. Restrictions apply.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIA.2020.3041563, IEEE Transactions on Industry Applications

Fig.4 Operating Modes of CPUC Part III (a) State P4 Mode (b) State P6 Mode (c) State P12 Mode

Figs. 3 (a)-(b) show operating modes for middle negative state  $N_6$  and highest negative level  $N_{12}$ . Fig. 3 (c) shows the first positive level P<sub>1</sub> where the current forms path through capacitor  $C_1$  moving up through the first DC voltage source. The part III of operating mode discusses state  $P_4$ ,  $P_6$  and  $P_{12}$  as shown in Figs. 4 (a)-(c). The positive middle level is shown in Fig. 4(b) and the highest positive level is in state  $P_{12}$ . The modes of operation validate function and development of states.

The selection of CPUC voltage sources is such that the grid voltage of 325  $V_{p-p}$  is achieved. The interfacing inductor reduces the instantaneous error between each level of converter voltage and improves grid current harmonics.

#### B. Mathematical Model

The switching function of CPUC is defined as,

$$S_{w} = \begin{cases} 0, \text{ when } S_{n} \text{ is OFF} \\ 1, \text{ when } S_{n} \text{ is ON} \end{cases}$$

(1)

where n=12 for this converter. The complementary equation for each section switches in CPUC is given as,

$$S_n + S_{nc} = 1 \tag{2}$$

Each section works in complementary mode, and the current of each section contributes to the total current fed to load/grid. The load/grid current is related to each section current. The grid current having relation with non-complementary switches is given as,

$$i_g = \frac{i_n}{S_n} \tag{3}$$

The DC link voltages with switching functions are related as,

$$\begin{aligned} v_{ab} &= (S_1 - 1) / V_{dc1} \\ v_{bc} &= (1 - S_2) / (V_{dc1} - V_{dc1} / 2) \\ v_{cd} &= (1 - S_3)(V_{dc1} / 2) \\ v_{ef} &= (S_4 - 1)(V_{dc2}) \\ v_{fg} &= (1 - S_5) / (V_{dc2} - V_{dc2} / 2) \\ v_{gh} &= (1 - S_6)(V_{dc2} / 2) \end{aligned}$$

The total output voltage of the converter becomes,

$$V_{mli} = v_{ab} + v_{bc} + v_{cd} + v_{ef} + v_{fg} + v_{gh}$$

(5)

<sup>0093-9994 (</sup>c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on December 08,2020 at 12:56:20 UTC from IEEE Xplore. Restrictions apply.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIA.2020.3041563, IEEE Transactions on Industry Applications

|                       | I                              | MODES OF OPERATION                                              |                                      |

|-----------------------|--------------------------------|-----------------------------------------------------------------|--------------------------------------|

| Levels                | $S_1, S_2, S_3, S_4, S_5, S_6$ | Converter I                                                     | Converter II                         |

| P <sub>12</sub>       | 011011                         | V <sub>dc1</sub>                                                | V <sub>dc2</sub>                     |

| $P_{11}$              | 010011                         | $V_{dcl}$ - $V_{dcl}/2$                                         | $V_{dc2}$<br>$V_{dc2}$               |

| $P_{10}$              | 111011                         | $\mathbf{v}_{dcl} - \mathbf{v}_{dcl}/2$                         |                                      |

| г <sub>10</sub><br>Р9 | 101011                         | $-V_{dcl}+V_{dcl}/2$                                            | V <sub>dc2</sub><br>V <sub>dc2</sub> |

| r9<br>P8              | 100011                         | $-\mathbf{v}_{dcl} + \mathbf{v}_{dcl}/2$<br>$-\mathbf{V}_{dcl}$ | $V_{dc2}$<br>$V_{dc2}$               |

| -                     |                                |                                                                 |                                      |

| P <sub>7</sub>        | 011010                         | V <sub>dc1</sub>                                                | $V_{dc2}-V_{dc2}/2$                  |

| P <sub>6</sub>        | 010010                         | $V_{dcl} - V_{dcl}/2$                                           | $V_{dc2} - V_{dc2}/2$                |

| P <sub>5</sub>        | 111010                         | 0                                                               | $V_{dc2} - V_{dc2}/2$                |

| P <sub>4</sub>        | 101010                         | $-V_{dcl}+V_{dcl}/2$                                            | $V_{dc2} - V_{dc2}/2$                |

| P <sub>3</sub>        | 100010                         | -V <sub>dc1</sub>                                               | $V_{dc2}-V_{dc2}/2$                  |

| P <sub>2</sub>        | 100111                         | V <sub>dc1</sub>                                                | 0                                    |

| P1                    | 010111                         | $V_{dc1}-V_{dc1}/2$                                             | 0                                    |

| Ζ                     | 111111                         | 0                                                               | 0                                    |

| N <sub>1</sub>        | 101111                         | $-V_{dcl}+V_{dcl}/2$                                            | 0                                    |

| $N_2$                 | 100111                         | -V <sub>dc1</sub>                                               | 0                                    |

| N <sub>3</sub>        | 011101                         | V <sub>dc1</sub>                                                | $-V_{dc2}+V_{dc2}/2$                 |

| $N_4$                 | 010101                         | $V_{dc1}-V_{dc1}/2$                                             | $-V_{dc2}+V_{dc2}/2$                 |

| N <sub>5</sub>        | 111101                         | 0                                                               | $-V_{dc2}+V_{dc2}/2$                 |

| $N_6$                 | 101101                         | $-V_{dcl}+V_{dcl}/2$                                            | $-V_{dc2}+V_{dc2}/2$                 |

| $N_7$                 | 100101                         | -V <sub>dc1</sub>                                               | $-V_{dc2}+V_{dc2}/2$                 |

| N <sub>8</sub>        | 011100                         | $V_{dc1}$                                                       | -V <sub>dc2</sub>                    |

| N9                    | 010100                         | $V_{dc1}$ - $V_{dc1}/2$                                         | -V <sub>dc2</sub>                    |

| N <sub>10</sub>       | 111100                         | 0                                                               | -V <sub>dc2</sub>                    |

| N <sub>11</sub>       | 101100                         | $-V_{dcl}+V_{dcl}/2$                                            | -V <sub>dc2</sub>                    |

| N <sub>12</sub>       | 100100                         | -V <sub>dc1</sub>                                               | -V <sub>dc2</sub>                    |

In this configuration, total output levels are the multiplication of level obtained from each cell. The generalized expression of the total number of levels is as,

$$T_L = L^N \tag{6}$$

In this configuration, L is taken as 5 and N is selected as 2 to generate twenty-five levels. For example, 125 levels are to be obtained using 5 level PUC cells. The value of N is 3 from (6), which shows that only 3 PUC cells are enough to attain 125 levels in the output voltage. It is possible due to the asymmetric selection of voltages within and among the cascaded cells. The voltage equations for capacitors are given as,

$$\begin{cases} V_{c1} = \frac{1}{C_1} \int [S_3 - S_2] i_g \\ V_{c2} = \frac{1}{C_2} \int [S_6 - S_5] i_g \end{cases}$$

(7)

From (7), capacitor currents are given as,

$$\begin{cases} i_{c1} = [S_3 - S_2]i_g \\ i_{c2} = [S_6 - S_5]i_g \end{cases}$$

(8)

Similarly, load current equations can be formulated in terms of switching function and capacitors. Kirchhoff's voltage law gives the equation for both grid-connected and standalone mode as,

$$-V_{mli} + \left\{ R_p i_g + \left(\frac{L_f}{2}\right) \frac{di_g}{dt} \right\} + v_g + \left\{ R_p i_g + \left(\frac{L_f}{2}\right) \frac{di_g}{dt} \right\} = 0$$

$$-V_{mli} + \left\{ R_p i_L + \left(\frac{L_f}{2}\right) \frac{di_L}{dt} \right\} + v_L + \left\{ R_p i_g + \left(\frac{L_f}{2}\right) \frac{di_L}{dt} \right\} = 0$$

(9)

Rearranging terms of (9) one has,

$$V_{mli} - v_g = \left\{ 2R_p i_g + \left(L_f\right) \frac{di_g}{dt} \right\}$$

$$V_{mli} - v_L = \left\{ 2R_p i_L + \left(L_f\right) \frac{di_L}{dt} \right\}$$

(10)

The parasitic resistance is neglected, and (10) is made simpler for further analysis.

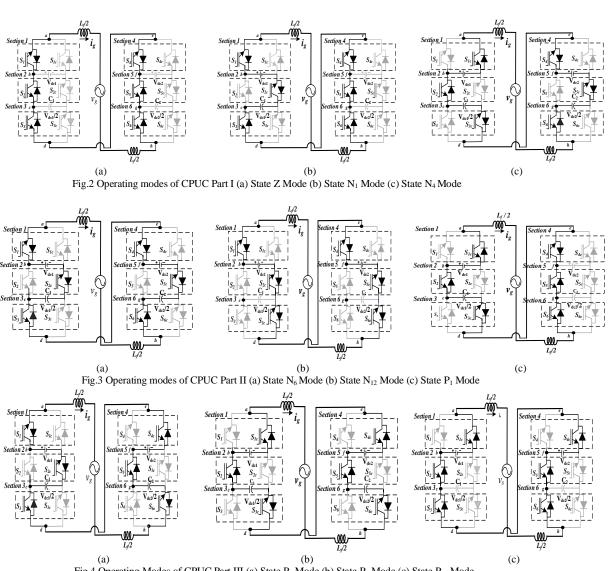

## C. Binary-Quintuple Progression Scheme

The level formation solely depends on the selection of voltage sources. The binary and quintuple progressions are integrated together in the proposed scheme to obtain 25 levels in output voltage, as shown in Fig. 5. The cell of CPUC has different ratios within the cell and between one another. The base 2 system is considered as binary and used to select the magnitude of voltage inside each cell of PUC. The ratio of binary is selected between DC voltage source, and capacitor voltage of first PUC cell. Similarly, DC voltage source is twice of capacitor voltage of the second PUC cell. Moreover, the base 5 system has been taken between the first and second PUC being cascaded. The base 5 system is termed as quintuple, where the DC voltage source of converter II is five times of Converter I. Furthermore, the ration between capacitor voltage of converter I and converter II are selected as 1:5. The appropriate selection of voltages has led to the generation of twenty-five level converter output voltage. PUC cell I and PUC cell 2 are converters that aids in level formation from cascaded topology.

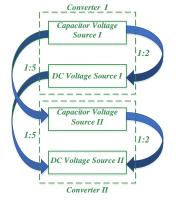

## III. CONTROL METHODOLOGY

The grid-connected current reference controller for CPUC is shown in Fig. 6. The same controller with modification is implemented for standalone operation. The controller is designed for feeding the desired current reference in the AC grid. The parameters for CPUC are shown in Table II, and comparative analysis of device count is given in Table III.

#### A. Standalone Operation

The standalone mode of operation is analyzed with the help of an R-L load. The DC source feeds R-L Load, and such a system has a vast potential in uninterrupted power supplies. The same controller is designated, but PLL is not sensed from the load voltage. A unit sine wave block is used for the generation of the unit template to avoid the effect of load disturbances on the controller. The load current is drawn from the DC side as per load demand.

#### B. Grid-Connected Operation

The grid-connected controller senses the grid voltage, and the signal is fed to PLL. The active and reactive power transfers are ensured with the help of the addition of phase delay in  $\theta$ . In the

Fig.5 Representation of Binary-Quintuple scheme

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIA.2020.3041563, IEEE Transactions on Industry Applications

| TABLE II<br>System Parameters            |                      |  |  |  |  |  |

|------------------------------------------|----------------------|--|--|--|--|--|

| Parameters                               | Values               |  |  |  |  |  |

| Grid Voltage (v <sub>s</sub> )           | 325 V <sub>p-p</sub> |  |  |  |  |  |

| Grid Frequency (f <sub>s</sub> )         | 50 Hz                |  |  |  |  |  |

| Grid Inductor (L <sub>f)</sub>           | 4 mH                 |  |  |  |  |  |

| DC Voltage Source I (V <sub>dc1</sub> )  | 54 V                 |  |  |  |  |  |

| Capacitor I Voltage (Vcl)                | 27 V                 |  |  |  |  |  |

| DC Voltage Source II (V <sub>dc2</sub> ) | 270 V                |  |  |  |  |  |

| Capacitor II Voltage (Vc2)               | 135 V                |  |  |  |  |  |

| R-L Load                                 | 60 Ω, 80 mH          |  |  |  |  |  |

absence of PV source, the reference DC component is injected in a grid-connected system. The first DC voltage source is halved and used as a reference signal for a capacitor of converter I. The voltage of the capacitor is sensed and balanced using proportional-integral (PI) controller. The balancing control for the converter I capacitor is given as,

$$I_{d1} = I_{d1}(g-1) + k_{p1}\{e_{r1}(g) - e_{r1}(g-1)\} + k_{i1}e_{r1}(g)$$

(11)

where,

$$e_{r1} = V_{c1}^* - V_{c1} \tag{12}$$

The PI controller minimizes the error  $e_{rl}$  between desired and sensed capacitor voltages. Similarly, the output of the PI controller for capacitor voltage balance of converter II is as,

$$I_{d2} = I_{d2}(g-1) + k_{p2}\{e_{r2}(g) - e_{r2}(g-1)\} + k_{i2}e_{r2}(g) \quad (13)$$

where,

$$e_{r2} = V_{c2}^* - V_{c2} \tag{14}$$

The modulating signal is generated, and control output for the same is given as,

$$v_{ref} = v_{ref}(g-1) + k_{p3}\{e_{ref}(g) - e_{ref}(g-1)\} + k_{i3}e_{ref}(g) \quad (15)$$

where,

$$e_{ref} = i_{gref} - i_g \tag{16}$$

Nearest level modulation technique (NLMT) is implemented, and its flow chart is shown in Fig. 7. This technique switches IGBTs at fundamental switching and is more efficient. CPUC operation depends on the switching of devices, and the modulation scheme decides the efficiency of the system on a large scale. Therefore, the approach taken is a fundamental switching frequency to avoid higher losses in high frequencybased switching. The switching losses are expressed as the sum of IGBTs turn ON and turn OFF losses. In this modulation strategy, the round function is used to find the nearest voltage level. A new convention is added that round "3.5" is taken as "4" to avoid ambiguity for half integers. The PUC cells are calculated by taking log on both sides of (6) as,

$$N = \log_L(T_L) \tag{17}$$

Moreover,

$$M = 0.5 * (T_L - 1) \tag{18}$$

The total number of positive levels are obtained using (18). The calculated value 12 is used to obtain the predefined level. The quotient k is calculated using the modulated signal and  $P_L$ . The  $L_n$  function is compared with integer values for switching the CPUC cells. The obtained gate pulses are given to switches of converters I and II.

## IV. OBSERVED RESULTS AND DISCUSSION

The CPUC is modeled in MATLAB/Simulink, and results are tested through OPAL-RT test bench. The test bench uses a plant and controller in OPAL-RT stacks. The rapid prototyping function of real-time simulators enables fast hardware synchronization. The OPAL-RT test bench with two stacks OP5700/OP5607 and host PCs are used. The digital and analog signals are processed in a loop using digital out (DO), digital in (DI), analog out (AO) and analog in (AI) ports.

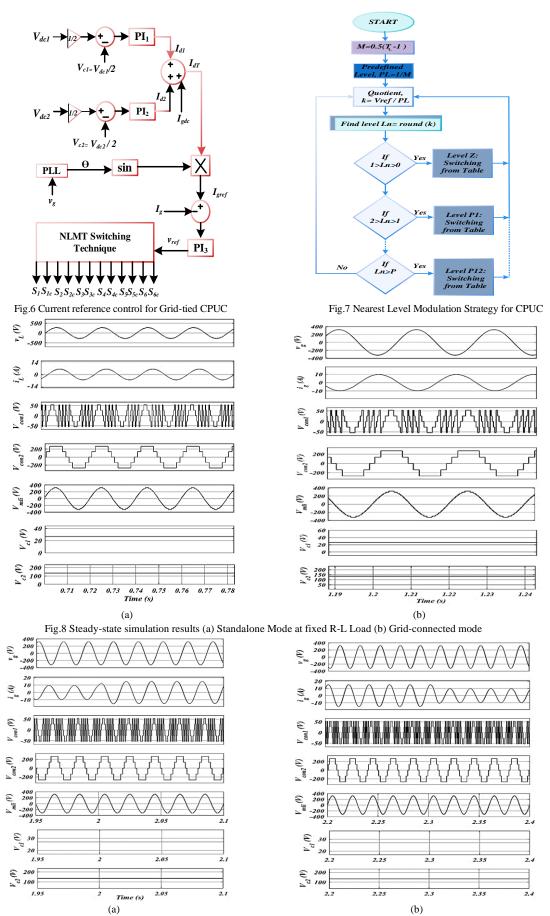

## A. Simulation Results

Fig. 8 (a) shows results of standalone mode when R-L Load is connected at converter output terminals. The load voltage and load current is in the same phase. A lagging nature is load current is observed due to load inductance. The converter voltage remains constant and has 25 levels. The cell voltages of converter I and II are shown. Both cell voltages of each PUC cells add up to form 25 level MLC. Fig. 8 (b) shows a gridconnected mode where the grid-current reference is injected in control to feed current into the grid. The DC voltage source acts as a battery feeding power to the grid. The grid current and grid voltage are in phase opposition, which signifies that power is fed into the grid. Moreover, the grid-current reference is changed from 10 A to 15 A for dynamic performance. The increase in grid current and a decrease in grid current reference, as shown in Figs. 9 (a)-(b). The capacitor voltages remain balanced at the dynamic state. The 25-level output voltage remains unaffected under sudden variation of grid current reference.

## B. Test Results

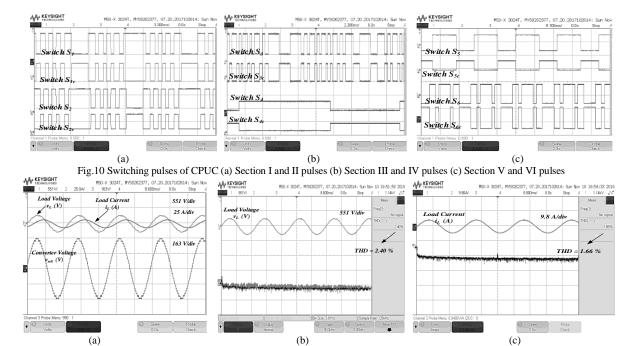

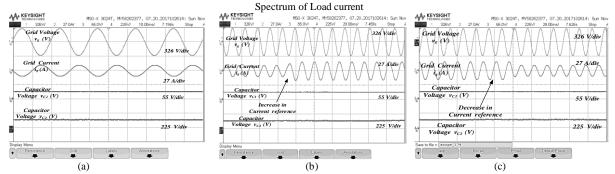

Figs. 10-14 show test results of CPUC for standalone and grid-connected operations. Fig. 10 shows are switching pulses, for the converter I and II. The switching pulses of switches in sections I and II of the first PUC cell are shown in Fig. 10 (a). Section III and Section IV pulses are shown in Fig. 10 (b). The pulses of Section V and VI are shown in Fig. 10 (c). The switching pulses in test results are complementary to its non-complementary switch. The standalone operation at a fixed R-L load is shown in Fig. 11(a). Moreover, the converter voltage having 25 levels is obtained at the steady-state condition. The load current lags behind the load voltage and capacitor voltages are also balanced for the standalone mode of operation. Figs. 11 (b)-(c) measure load voltage and load current THD, which is under 5% limit of the IEEE 519 standard.

Figs. 12 (a)-(c) depict performance in the grid-connected mode for steady-state and dynamic conditions. The capacitor voltages remain constant in steady-state. The grid voltage remains constant at the peak value of 325 V. Moreover, Fig. 12 (a) shows reference DC value as injected, which results in a constant grid current of 10 A. The grid current is in phase opposition, which ensures power is being fed into the grid. The unity power factor is maintained for both dynamic and steady-state conditions. In Figs. 12 (b-c) dynamic operation, the grid-current reference is increased from 10 A to 15 A. Furthermore, it is decreased to 10 A for the testing system at sudden changes in the grid-current reference. The controller tuning is as per minimum steady-state error between actual and reference modulating signals.

<sup>0093-9994 (</sup>c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on December 08,2020 at 12:56:20 UTC from IEEE Xplore. Restrictions apply.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIA.2020.3041563, IEEE Transactions on Industry Applications

Fig.9 Dynamic state simulation results (a) Increase in grid current reference (b) Decrease in grid current reference

6

0093-9994 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on December 08,2020 at 12:56:20 UTC from IEEE Xplore. Restrictions apply. This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIA.2020.3041563, IEEE Transactions on Industry Applications

| Parameters                    | [20]    | [21]    | [22]   | [23]    | [24]   | [25]      | [26]    | [27]  | [7]     | Proposed  |

|-------------------------------|---------|---------|--------|---------|--------|-----------|---------|-------|---------|-----------|

| Number of Levels              | 25      | 25      | 25     | 25      | 25     | 25        | 25      | 27    | 49      | 25        |

| Voltage Ratio                 | 1:5     | 1:5     | 1:5    | -       | -      | 1:1       | 1:2:3:6 | 1:3:9 | 1:7     | 1:5       |

| DC Sources                    | 2       | 2       | 2      | 1       | 22     | 6         | 3       | 3     | 2       | 2         |

| Switches                      | 10      | 10      | 16     | 41      | 15     | 26        | 12      | 12    | 12      | 12        |

| Diodes                        | 8       | 16      | 0      | 0       | 11     | 0         | 0       | 0     | 0       | 0         |

| Capacitors                    | 2       | 4       | 0      | 12      | 0      | 12        | 2       | 0     | 2       | 2         |

| Total Count                   | 22      | 32      | 18     | 54      | 48     | 44        | 17      | 15    | 16      | 16        |

| Modulation                    | PWM     | PWM     | PWM    | SHE     | SHE    | NLMT      | PWM     | PWM   | PWM     | NLMT      |

| Technique                     |         |         |        |         |        |           |         |       |         |           |

| Switching Losses              | Mediu   | High    | Medium | Low     | Low    | Low       | High    | High  | High    | Low       |

|                               | m       |         |        |         |        |           |         |       |         |           |

| Efficiency                    | Good    | Poor    | Good   | Good    | Good   | Good      | Good    | Good  | Good    | Very Good |

| Capacitor                     | Natural | Natural | -      | Natural | -      | Auxiliary | PWM     | -     | PI      | PI        |

| Balancing                     |         |         |        |         |        | Devices   |         |       | Control | Control   |

| Control Complexity            | Medium  | Medium  | Low    | Medium  | Medium | High      | Low     | Low   | Simple  | Simple    |

| Unequal Power                 | Medium  | Medium  | Medium | -       | -      | -         | High    | High  | High    | Medium    |

| Distribution                  | _       |         |        | _       | _      | _         |         |       |         | -         |

| Thermal Stress                | Low     | Medium  | Medium | Low     | Low    | Low       | High    | High  | High    | Low       |

| Harmonic                      | Good    | Good    | Good   | Good    | Good   | Good      | Good    | Good  | Very    | Good      |

| Performance                   |         |         |        |         |        |           |         |       | Good    |           |

| Thermal Design Cost           | Low     | Medium  | Medium | Low     | Low    | Low       | High    | High  | High    | Low       |

| Drivers and<br>Component Cost | Medium  | High    | Low    | High    | High   | High      | Low     | Low   | Low     | Low       |

TABLE III

COMPARATIVE ANALYSIS FOR THE PROPOSED WORK

Fig.12 Grid Connected Mode of Operation (a) Steady-state Operation at fixed grid current reference (b) Dynamic state with an increase in grid current reference (c) Dynamic state with the decrease in grid current reference.

0093-9994 (c) 2020 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information. Authorized licensed use limited to: Aalborg Universitetsbibliotek. Downloaded on December 08,2020 at 12:56:20 UTC from IEEE Xplore. Restrictions apply.

This article has been accepted for publication in a future issue of this journal, but has not been fully edited. Content may change prior to final publication. Citation information: DOI 10.1109/TIA.2020.3041563, IEEE Transactions on Industry Applications

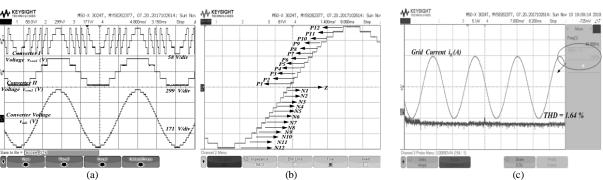

Fig.13 Converter cell voltages and Harmonic performance (a) Converter I, Converter II and MLI Voltage (b) Zoomed View of Converter Voltage, (c) Harmonic performance of grid current

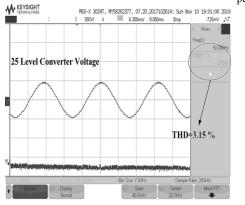

Fig.14 Harmonic performance of converter voltage

Fig. 13 (a) shows the stepped voltage waveform of each PUC cell. Both cell voltages add up to form a 25 level synthesized waveform. Figs. 13 (b)-(c) show a zoomed view of the converter voltage and harmonics analysis of the grid current THD, which is 1.64%. Fig. 14 shows the converter output AC voltage, which has a THD of 3.15% and it meets the IEEE 519 standard. Test results validate cascaded packed U cell-based multilevel converter for grid-tied and standalone applications.

#### V. CONCLUSIONS

A reduced switch count CPUC is implemented in this work for 25-levels output voltage. The binary quintuple progression scheme is used for the selection of voltages. The capacitor balancing is achieved under standalone as well as the gridconnected operation. The active power is fed into the grid seamlessly, and converter is switched at fundamental frequency using the NLM strategy. The comparative analysis shows that the proposed progression scheme provide a cost effective multilevel converter in terms of cost, reliability, power quality and system efficiency. The detailed comparison has shown the effectiveness of CPUC multilevel converter over other available topologies. The number of levels attained in CPUC is significantly increased. Furthermore, the power quality is improved as THD remains under permissible limits. OPAL-RT test results show the feasibility of this system for standalone and grid-connected applications.

#### References

[1] F. Zhao, G. Xiao, T. Zhu, T. Zhao, X. Zheng and Z. Wu, "Harmonic Analysis and Suppression Method of Output Current Distortion for Medium-Voltage Motor Drives with Modular Multilevel Converter", *IEEE Trans. Pow. Electron.*", vol. 35, no. 1, pp. 744-759, Jan. 2020.

- [2] H. Akagi, "Multilevel Converters: Fundamental Circuits and Systems, Proceedings of the IEEE", vol. 105, no. 11, pp. 2048-2065, Nov. 2017.

- [3] A. S. Gadalla, X. Yan, S. Y. Altahir and H. Hasabelrasul, "Evaluating the capacity of power and energy balance for cascaded H-bridge multilevel inverter using different PWM techniques," *The Journal of Engineering*, vol. 2017, no. 13, pp. 1713-1718, 2017.

- [4] R. Maheshwari, S. Busquets-Monge and J. Nicolas-Apruzzese, "A Novel Approach to Generate Effective Carrier-Based Pulse width Modulation Strategies for Diode-Clamped Multilevel DC–AC Converters," *IEEE Trans. Ind. Electron.*, vol. 63, no. 11, pp. 7243-7252, Nov. 2016.

- [5] L. He and C. Cheng, "A Flying-Capacitor-Clamped Five-Level Inverter Based on Bridge Modular Switched-Capacitor Topology," *IEEE Trans. Ind. Electron.*, vol. 63, no. 12, pp. 7814-7822, Dec. 2016.

- [6] N. Mishra and B. Singh, "Modified Reduced Switch Converter for Grid Interfaced Systems," 2018 IEEE Ind. App. Society Annual Meeting (IAS), Portland, OR, 2018, pp. 1-8.

- [7] M. Meraj, S. Rahman, A. Iqbal, M. Tariq, K. A. Lodi and L. Ben-Brahim, "A New Variable Frequency Control of 49-Level Cascaded Packed U-Cell Voltage Source Inverter," *IEEE Trans. Ind. App.*, vol. 55, no. 6, pp. 7537-7548, Nov.-Dec. 2019.

- [8] S. K. Chattopadhyay and C. Chakraborty, "Three-Phase Hybrid Cascaded Multilevel Inverter Using Topological Modules With 1:7 Ratio of Asymmetry," IEEE Journ. of Emerging and Selected Topics in Pow. Electron., vol. 6, no. 4, pp. 2302-2314, Dec. 2018.

- [9] N. Sandeep and U. R. Yaragatti, "Design and implementation of active neutral-point-clamped nine-level reduced device count inverter: an application to grid integrated renewable energy sources," *IET Pow. Electron.*, vol. 11, no. 1, pp. 82-91, 12 1 2018.

- [10] E. C. d. Santos, J. H. G. Muniz, E. R. C. da Silva and C. B. Jacobina, "Nested Multilevel Topologies," *IEEE Trans. Pow. Electron.*, vol. 30, no. 8, pp. 4058-4068, Aug. 2015.

- [11] E. Samadaei, M. Kaviani and K. Bertilsson, "A 13-Levels Module (K-Type) With Two DC Sources for Multilevel Inverters," *IEEE Trans. on Ind. Electron.*, vol. 66, no. 7, pp. 5186-5196, July 2019.

- [12] K. K. Rout and S. Mishra, "A Modified 7-Level Reduced Switch Symmetrical Inverter,"2018 National Power Engineering Conf. (NPEC), Madurai, 2018, pp. 1-5.

- [13] D. Samajdar, T. Bhattacharya and S. Dey, "A Reduced Switching Frequency Sorting Algorithm for Modular Multilevel Converter with Circulating Current Suppression Feature," *IEEE Trans. on Power Electron.*, vol. 34, no. 11, pp. 10480-10491, Nov. 2019.

- [14] A. Mortezaei, M. G. Simões, A. S. Bubshait, T. D. C. Busarello, F. P. Marafão and A. Al-Durra, "Multifunctional Control Strategy for Asymmetrical Cascaded H-Bridge Inverter in Microgrid Applications," *IEEE Trans. Ind. App.*, vol. 53, no. 2, pp. 1538-1551, March-April 2017.

- [15] H. Vahedi, P. Labbé and K. Al-Haddad, "Corrections to "Sensor-Less Five-Level Packed U-Cell (PUC5) Inverter Operating in Stand-Alone and Grid-Connected Modes" *IEEE Tran. Ind. Infom.*, vol. 12, no. 4, pp. 1298-1298, Aug. 2016.

- [16] K. Haghdar, "Optimal DC Source Influence on Selective Harmonic Elimination in Multilevel Inverters Using Teaching–Learning-Based Optimization," *IEEE Trans. Ind. Elect*, vol. 67, no. 2, pp. 942-949, Feb. 2020.

- [17] A. S. Gadalla, X. Yan, S. Y. Altahir and H. Hasabelrasul, "Evaluating the capacity of power and energy balance for cascaded H-bridge multilevel inverter using different PWM techniques," *The Journal of Engineering*, vol. 2017, no. 13, pp. 1713-1718, 2017.

- [18] S. Du, J. Liu and T. Liu, "Modulation and Closed-Loop-Based DC Capacitor Voltage Control for MMC With Fundamental Switching Frequency," *IEEE Trans. Pow. Elect*, vol. 30, no. 1, pp. 327-338, Jan. 2015.

- [19] G. Eshwar Gowd, P. C. Sekhar and D. Sreenivasarao, "Real-Time Validation of a Sliding Mode Controller for Closed-Loop Operation of Reduced Switch Count Multilevel Inverters," *IEEE Systems Journal*, vol. 13, no. 1, pp. 1042-1051, March 2019.

- [20] S. P. Gautam, "Novel H-Bridge-Based Topology of Multilevel Inverter with Reduced Number of Devices," *IEEE Journal of Emerging and Selected Topics in Pow. Electron.*, vol. 7, no. 4, pp. 2323-2332, Dec. 2019.

- [21] A. Taheri, A. Rasulkhani and H. Ren, "An Asymmetric Switched Capacitor Multilevel Inverter with Component Reduction," *IEEE Access*, vol. 7, pp. 127166-127176, 2019.

- [22] E. Babaei, M. F. Kangarlu and M. Sabahi, "Extended multilevel converters: an attempt to reduce the number of independent DC voltage sources in cascaded multilevel converters," *IET Pow. Electron.*, vol. 7, no. 1, pp. 157-166, January 2014.

- [23] M. Khenar, A. Taghvaie, J. Adabi and M. Rezanejad, "Multi-level inverter with combined T-type and cross-connected modules," *IET Power Electron.*, vol. 11, no. 8, pp. 1407-1415, 10 7 2018.

- [24] K. P. Panda, S. S. Lee and G. Panda, "Reduced Switch Cascaded Multilevel Inverter with New Selective Harmonic Elimination Control for Standalone Renewable Energy System," *IEEE Trans. Ind. App.*, vol. 55, no. 6, pp. 7561-7574, Nov.-Dec. 2019.

- [25] J. S. Mohamed Ali, R. Shalchi Alishah and V. Krishnasamy, "A New Generalized Multilevel Converter Topology with Reduced Voltage on Switches, Power losses, and Components," *IEEE Journal of Emerging* and Selected Topics in Pow. Electron., vol. 7, no. 2, pp. 1094-1106, June 2019.

- [26] J. Ebrahimi and H. Karshenas, "N-Tuple Flying Capacitor Multicell Converter—A Generalized Modular Hybrid Topology," in *IEEE Trans. Ind. Electron.*, vol. 66, no. 7, pp. 5004-5014, July 2019.

- [27] M. Rotella, G. Penailillo, J. Pereda and J. Dixon, "PWM Method to Eliminate Power Sources in a Nonredundant 27-Level Inverter for Machine Drive Applications," *IEEE Transactions Industrial Electronics*, vol. 56, no. 1, pp. 194-201, Jan. 2009.

Nidhi Mishra (Member, IEEE) had recieved her M.Tech from BIT Mesra, Ranchi, Jharkhand, in 2012. She was lecturer at NIT, Hamirpur for a year during 2013. She had completed her Ph.D. from IIT Delhi in September 2020. Presently she is working in Aligarh Muslim University for collaborated project of UNSW, Canberra, Australia. She also served as session chair in quite international conferences. Her areas of

interest includes multilevel converters, grid interaction of renewable energy systems and power quality improvement in grid-tied systems.

Shivam Kumar Yadav (Student Member, IEEE) received his M. Tech. Degree (Hons.) in Power Electronics and Drives from National Institute of Technology, Kurukshetra, India, in 2018. He is currently working towards Ph.D. degree in Power Electronics and Drives with the Department of Electrical Engineering, Indian Institute of Technology (IIT), Delhi, India. His

research interests are focused on multilevel converters for solar grid interface, soft computing techniques and their application in renewable energy.

**Bhim Singh** (SM"99, F"10) has received his M.Tech. (Power Apparatus & Systems) and Ph.D. from the Indian Institute of Technology Ph.D. in 1979 and 1983, respectively. In 1983, he joined the Department of Electrical Engineering, University of Roorkee, as a Lecturer. He became a Reader there in 1988. In December 1990, he joined the Department of Electrical Engineering, IIT Delhi, India, as an Assistant Professor, where he has become an Associate Professor in 1994 and a Professor in 1997. He has been ABB Chair Professor from September 2007 to September 2012. He has also been CEA Chair Professor from October 2012 to September 2017. He has been Head of the Department of Electrical Engineering at IIT Delhi from July 2014 to August 2016. He has been the Dean, Academics at IIT Delhi from August 2016 to August 2019. He is JC Bose Fellow of DST, Government of India since December 2015. He is CEA Chair Professor since January 2019. Professor Singh has guided 92 Ph.D. dissertations, and 168 M.E./M.Tech./M.S.(R) theses. He has been filed 62 patents. He has executed more than eighty five sponsored and consultancy projects. He has co-authored a text book on power quality: Power Quality Problems and Mitigation Techniques published by John Wiley & Sons Ltd. 2015. His areas of interest include solar PV grid interface systems, microgrids, power quality monitoring and mitigation, solar PV water pumping systems, EVs and improved power quality AC-DC converters.

Sanjeevikumar Padmanaban (Senior Member, IEEE) received Ph.D. degree in electrical engineering from the University of Bologna, Bologna, Italy, in 2012. He was an Associate Professor with VIT University, from 2012 to 2013. In 2013, he joined the National Institute of Technology, India, as a Faculty Member. In 2014, he was invited as a Visiting Researcher at the Department of Electrical

Engineering, Qatar University, Doha, Qatar, funded by the Qatar National Research Foundation (Government of Qatar). He continued his research activities with the DIT, Dublin, Ireland, in 2014. He was an Associate Professor with the Department of Electrical and Electronics Engineering, University of Johannesburg, South Africa, from 2016 to 2018. Since 2018, he has been a Faculty Member with the Department of Energy Technology, Aalborg University, Esbjerg, Denmark. He has authored over 300 scientific articles. He is a Fellow of the Institution of Engineers, IETE, India, and IET, U.K. He was a recipient of the Best Paper cum Most Excellence Research Paper Award IET-CEAT'16, IEEE-EECSI'19, IEEE-CENCON'19 and five Best Paper Awards from ETAEERE'16 sponsored Lecture Notes in Electrical Engineering, Springer book. He is an Editor/Associate Editor/ Editorial Board of refereed journals of IEEE and IET.

**Frede Blaabjerg** (Fellow, IEEE) was an Assistant Professor, in 1992, an Associate Professor, in 1996, and a Full Professor of power electronics and drives, in 1998 at Aalborg University. In 2017, he became aVillum Investigator. He is currently a Honoris Causa with Universitate Politehnica Timisoara, Romania, and Tallinn Technical University, Estonia. His current research

interests include power electronics and its applications, such as in wind turbines, PV systems, reliability, harmonics, and adjustable speed drives. He has published more than 600 journal articles. He had received 32 IEEE Prize Paper Awards, the IEEE PELS Distinguished Service Award, in 2009, the EPE-PEMC Council Award, in 2010, the IEEE William E. Newell Power Electronics Award, in 2014, the Villum Kann Rasmussen Research Award, in 2014, the Global Energy Prize, in 2019, and the 2020 IEEE Edison Medal. He was the Editor-in- Chief and has served as the President of the IEEE Power Electronics from 2006 to 2012. He is also the Vice-President of the Danish Academy of Technical Sciences. He is nominated in 2014-2019 by Thomson Reuters to be between the most 250 cited researchers in Engineering in the world. In 2017, he became Honoris Causa at University Politehnica Timisoara, Romania.