PROGRAMA DE DOCTORADO EN CIENCIA Y TECNOLOGÍA

**TESIS DOCTORAL**

#### ANÁLISIS DE PLANIFICABILIDAD Y OPTIMIZACIÓN DE SISTEMAS DISTRIBUIDOS DE TIEMPO REAL CON PARTICIONADO TEMPORAL

PhD THESIS

## SCHEDULABILITY ANALYSIS AND OPTIMIZATION OF TIME-PARTITIONED DISTRIBUTED REAL-TIME SYSTEMS

AUTOR ANDONI AMURRIO GONZÁLEZ DIRECTORES J. JAVIER GUTIÉRREZ GARCÍA MARIO ALDEA RIVAS

UNIVERSIDAD DE CANTABRIA

Escuela de Doctorado de la Universidad de Cantabria

Santander 2022

#### This PhD. Thesis has been funded by the program "Doctorados Industriales 2018" and it has been done in collaboration between:

Ikerlan Member of the Basque Research and Technology Alliance

&

University of Cantabria Software Engineering and Real-time group

| Author: An          | Author: Andoni Amurrio González |  |  |  |  |  |  |

|---------------------|---------------------------------|--|--|--|--|--|--|

| Ikerlan Supervisor: | Ekain Azketa Ferreras           |  |  |  |  |  |  |

| UC Supervisors:     | J. Javier Gutiérrez García      |  |  |  |  |  |  |

|                     | Mario Aldea Rivas               |  |  |  |  |  |  |

### Abstract

Nowadays, most of the computing systems found in industry, such as autonomous driving platforms, smart grids or industrial control systems, are usually real-time cyber-physical systems that have a strong coupling between the software components, in charge of controlling the whole system by means of specific algorithms, and the distributed hardware equipment, such as sensing and actuating devices. In addition to their functional requirements, this kind of systems must meet complex non functional requirements related to execution predictability or fault tolerance, in order to comply with safety and application-specific standards.

In this context, designing real-time systems faces several challenges. Real-time systems are characterized by their deterministic response to external events, executing a sequence of activities with precedence relationships called end-to-end flows, which may be linear or multipath. Their correctness does not only depend on their results being computed correctly, but also on the time at which these results are provided, which is usually achieved by imposing deadlines that must be met even in the worst-case scenario. The implementation of sophisticated software architectures, such as time partitioning techniques that allow isolation among components, and the hierarchical combination of cyclic scheduling and fixed priority (FP) scheduling found for example in the avionics and space domains, requires the development of new response time analysis, scheduling and allocation techniques. All this has led to an increasing complexity in their design, forcing researchers from academia and industry to combine their efforts to bridge theoretical developments and practical use-cases. The work developed in this thesis targets a real railway signalling application, which is a paradigmatic example that brings together all the features just described.

With regard to the response time analysis for event-driven real-time systems, new approaches or techniques have been proposed in the literature based on models with different complexity, from single processor to multiprocessor or distributed systems, and dealing with linear end-to-end flows or other complex multipath logics. The vast majority of the underlying models for these techniques were based on the authors' conception about a hypothetical target system. However, current applications in industry show that state-of-the-art approaches need to be extended in order to calculate their worst-case response times accurately. In this thesis, a new technique

that captures the complexity of current applications, that is, time partitioning plus fixed priority scheduling and multipath flows, has been developed.

In addition, it is also essential to optimize the utilization of resources of the real-time application while guaranteeing that its deadlines are met. In the last three decades, a large number of proposals have been developed for the optimization of the scheduling and deployment of distributed real-time systems under different algorithmic approaches, which provide acceptable solutions for this problem categorized as NP-hard in the strong sense. A survey of these works has been reported in this thesis, and their solutions have been characterized.

Based on the proposed schedulability analysis technique, two crucial aspects of the scheduling optimization are addressed. On the one hand, a collection of eight algorithms for the priority assignment of multipath end-to-end flows has been proposed, which can be applied both to hierarchically-scheduled systems like the motivating industrial use-case, and also to general FP systems. Moreover, the scheduling optimization of time partitions is also addressed by proposing an algorithm to perform the assignment of partition windows for a fixed available utilization in each partition and, on top of this, another algorithm is proposed to optimize partition utilization.

Finally, a first step has been taken to solve the problem of allocating real-time applications to heterogeneous multiprocessor architectures. The allocation problem, which has been widely addressed in the literature, is far from being optimally solved due to the novel computing platforms that are being used nowadays in trendy domains such as autonomous driving or robotics.

All techniques proposed in this thesis have been implemented in several prototype tools, which has been used to process the experimental evaluation in the industrial use-case as well as in synthetic use-cases that represent a more general set of systems. These tools can be integrated within a Model-Driven Engineering (MDE) methodology for the development of safety critical real-time systems.

#### Resumen

Hoy en día, la mayoría de los sistemas de computación hallados en la industria, tales como la automoción, las redes eléctricas inteligentes o los sistemas de control industrial, son típicamente sistemas ciberfísicos de tiempo real, en los que hay una gran interacción entre los componentes software, encargados del control del sistema mediante algoritmos específicos, y el equipamiento hardware distribuido, como son los dispositivos de sensorización y actuación. Además de sus propios requisitos funcionales, estos sistemas deben cumplir complejos requisitos no funcionales relacionados con la predictibilidad de su ejecución o la tolerancia a fallos, para así cumplir con los estándares de seguridad genéricos y sectoriales.

En este contexto, el diseño de sistemas de tiempo real afronta varios desafíos. Los sistemas de tiempo real se caracterizan por su respuesta determinista a eventos externos, ejecutando una serie de actividades con relaciones de precedencia llamados flujos de extremo a extremo, en inglés end-to-end (e2e) flows, que pueden ser lineales o multitrayecto (en inglés *multipath*). Su rendimiento adecuado no sólo depende de que el resultado del cómputo sea correcto, sino también de que este resultado haya sido obtenido en un lapso de tiempo determinado, lo que generalmente se obtiene imponiendo unos plazos que deben verificarse incluso en el peor de los casos. La implementación de sofisticadas arquitecturas en el software, como por ejemplo el particionado temporal que permite el aislamiento temporal entre componentes, y la combinación jerárquica de los ejecutivos cíclicos y las prioridades fijas que se encuentran por ejemplo en la industria aeronáutica, requieren del desarrollo de nuevas técnicas de análisis, despliegue y planificación. Todo esto ha llevado a que su diseño sea cada vez más complejo, obligando a la comunidad investigadora, desde la academia a la industria, a unir sus esfuerzos para aplicar los avances teóricos en casos de uso prácticos. El trabajo desarrollado en esta tesis se centra en una aplicacion real del sector ferroviario, dado que se trata de un caso paradigmático que reúne todas las características expuestas.

En cuanto al análisis de los tiempos de respuesta de sistemas gobernados por eventos, nuevos enfoques y técnicas han sido propuestos en la literatura, basados en modelos de mayor o menor complejidad, desde sistemas con un solo procesador hasta sistemas distribuidos o multiprocesador, y y que tratan flujos de extremo a extremo (en inglés *end-to-end* o simplemente *e2e*) lineales como por otras arquitecturas multitrayecto

de mayor complejidad. La gran mayoría de los modelos y técnicas propuestos están basados en sistemas hipotéticos, fruto de la concepción de quien los propone. Sin embargo, las aplicaciones que se encuentran en la industria hoy en día evidencian que los métodos existentes han de ser extendidos para que se puedan calcular sus tiempos de respuesta de forma precisa. En esta tesis, se ha desarrollado una nueva técnica de análisis que captura la complejidad de las aplicaciones industriales, es decir, el uso de particionado temporal combinado con la planificación basada en prioridades fijas y flujos e2e multitrayecto.

Asimismo, también es esencial la optimización del uso de los recursos de una aplicación de tiempo real a la vez que se garantiza que sus plazos se cumplen. En las tres últimas decadas, se ha llevado a cabo una gran cantidad de propuestas para la optimización del despliegue y la planificación de los sistemas de tiempo real distribuídos, mediante distintos enfoques algorítmicos, que producen soluciones aceptables para este problema categorizado como NP-difícil. En esta tesis se presenta una revisión de estos trabajos y sus soluciones se han caracterizado.

Teniendo como eje la técnica de análisis de planificabilidad desarrollada, se abordan dos aspectos cruciales de la planificación de los sistemas de tiempo real. Por un lado, se propone una colección de ocho algoritmos para la asignación de prioridades para flujos e2e multitrayecto, que pueden ser aplicados tanto a sistemas con planificación jerárquica como el del caso de uso industrial que ha motivado este trabajo, como a sistemas distribuidos generales basados en prioridades fijas. Por otro lado, también se aborda la planificación de particiones temporales mediante un algoritmo de asignación de ventanas temporales para una utilización fija de cada partición, y sobre éste se propone otro algoritmo para optimizar la utilización de las particiones.

Finalmente, se dan los primeros pasos para resolver el problema del despliegue de aplicaciones de tiempo real en arquitecturas multiprocesador heterogéneas. El problema del despliegue, que ha sido ampliamente abordado en la literatura, está lejos de ser resuelto de manera óptima debido a la complejidad de las novedosas plataformas de cómputo que se emplean hoy en día en ámbitos como la conducción autónoma o la robótica.

Todas las técnicas propuestas en esta tesis han sido implementadas en herramientas prototipo y han sido empleadas para llevar a cabo la experimentación, tanto sobre el caso de uso industrial, como sobre experimentos sintéticos que representan casuísticas más generales. Estas herramientas pueden integrarse como parte de la metodología denominada ingeniería basada en modelos, en inglés *Model-Driven Engineering (MDE)*, para el desarrollo de sistemas críticos de tiempo real.

## Acknowledgements

In these lines I would like to show my gratitude towards those that have supported me during this amazing journey.

One of the first days of work, I was told that the members of the ISTR group in the University of Cantabria were both lovely people and brilliant researchers. I can corroborate that at first hand, thank you so much for your kindness. I owe a huge debt of gratitude to my supervisors, Dr. J. Javier Gutiérrez and Dr. Mario Aldea, who have supported and guided me with wisdom, patience and perseverance.

To all members of the Dependable Embedded Systems group in Ikerlan, thank you very much for your guide and advice. I am deeply grateful to my supervisor Dr. Ekain Azketa, who is a reference for me and has worked really hard to carry out this thesis from the very first day.

I would also like to express my gratitude to Dr. Marko Bertogna, for accepting me at the University of Modena and Reggio Emilia. The incredible team at HiPeRT Lab made me feel at home, even during the hardest pandemic times, and I hope our paths will cross again. I must also thank Dr. Nacho Sañudo and Dr. Micaela Verucchi for their kind attention and advise during the stay, both in the office and beyond, and Carmelo Scribano for providing me with a safe and reliable means of transportation during my stay in Modena.

Euren maitasuna, beharbada merezi izan ez badut ere, egunero adierazi didatenak ekarri nahi ditut gogora, neurri handi batean lan hau haiena ere baita. Ehun mila esker familia eta kuadrilari, desberdintasunik balego bi hitz horien artean. Azkenik, bide luze honetan nire alboan uneoro sentitu zaituztedalako, aita, ama, Maddalen eta Ane, bihotz-bihotzez, eskerrik asko.

> Nekez uzten du bere sorterria sustraiak han dituenak. Nekez uzten du bere lurra zuhaitzak ez bada abaildu eta oholetan.

## Contents

| 1 | Intr | oduction                                                            | 1  |

|---|------|---------------------------------------------------------------------|----|

|   | 1.1  | Context and background                                              | 1  |

|   |      | 1.1.1 Real-time cyber-physical systems                              | 1  |

|   |      | 1.1.2 Real-time safety critical systems                             | 2  |

|   |      | 1.1.3 Model-driven engineering                                      | 3  |

|   |      | 1.1.4 Response-time analysis                                        | 4  |

|   | 1.2  | Industrial use-case                                                 | 7  |

|   | 1.3  | Objectives                                                          | 9  |

|   | 1.4  | Organization                                                        | 10 |

| 2 | Sch  | eduling and optimization in distributed real-time systems: a liter- |    |

|   | atur | re review                                                           | 13 |

|   | 2.1  | Introduction and methodology                                        | 13 |

|   | 2.2  | Genetic Algorithm (GA)                                              | 15 |

|   | 2.3  | Tabu Search (TS)                                                    | 18 |

|   | 2.4  | Simulated Annealing (SA)                                            | 19 |

|   | 2.5  | Mathematical Programming                                            | 21 |

|   | 2.6  | Branch and Bound (BB)                                               | 25 |

|   | 2.7  | Heuristics (HEU)                                                    | 26 |

|   | 2.8  | Classification of works and conclusions                             | 31 |

| 3 | Rea  | l-time system model                                                 | 35 |

|   | 3.1  | Logical architecture                                                | 35 |

|   | 3.2  | Physical architecture                                               | 37 |

|   | 3.3  | Hierarchical scheduling                                             | 38 |

|   | 3.4  | Sensitivity analysis                                                | 39 |

|   | 3.5  | Modeling the industrial use-case                                    | 42 |

| 4 | Res  | ponse-time analysis                                                 | 45 |

|   | 4.1  | Response-time analysis of linear e2e flows                          | 45 |

|   | 4.2  | Response-time analysis of multipath e2e flows                       | 46 |

|   |      | 4.2.1 Simple example                                                | 47 |

|   |      | 4.2.2 Implementation and tools                                     | 48  |

|---|------|--------------------------------------------------------------------|-----|

|   | 4.3  | Industrial use-case evaluation                                     | 49  |

|   | 4.4  | Response-time analysis performance                                 | 51  |

|   | 4.5  | Conclusions                                                        | 54  |

| 5 | Prio | rity assignment                                                    | 57  |

|   | 5.1  | Scheduling-parameter assignment overview                           | 57  |

|   | 5.2  |                                                                    | 60  |

|   |      | 5.2.1 Virtual Deadline assignment                                  | 60  |

|   |      | 5.2.2 Virtual Deadline transformation into priorities              | 68  |

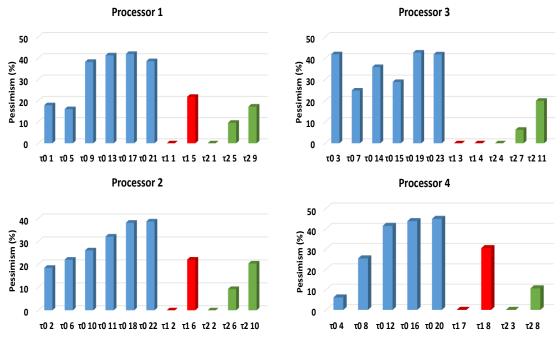

|   | 5.3  | Evaluation of the priority assignment algorithms                   | 70  |

|   |      | 5.3.1 Industrial use-case                                          | 70  |

|   |      | 5.3.2 Performance evaluation                                       | 73  |

|   | 5.4  | Conclusions                                                        | 80  |

| 6 |      | ition window assignment                                            | 81  |

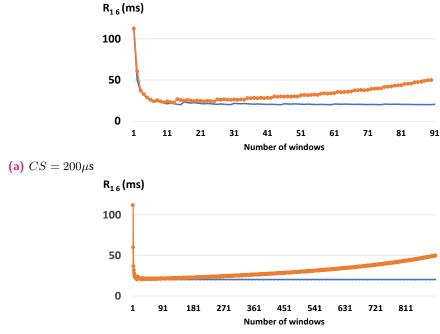

|   | 6.1  | Study of the influence of partition windows on schedulability      | 81  |

|   |      | 6.1.1 Available Utilization                                        | 82  |

|   |      | 6.1.2 Number of windows                                            | 82  |

|   |      | 6.1.3 Context switch overheads                                     | 83  |

|   |      | 5                                                                  | 85  |

|   | 6.2  |                                                                    | 86  |

|   |      |                                                                    | 86  |

|   |      | 6.2.2 Heuristic Optimized Partition Window Assignment (HOPWA)      | 89  |

|   | 6.3  | Performance evaluation                                             | 91  |

|   |      | 6.3.1 Design of the synthetic experiments                          | 92  |

|   |      | C                                                                  | 95  |

|   |      | 6.3.3 Evaluating HOPWA algorithm                                   | 99  |

|   |      | 6.3.4 Scheduling evaluation of the industrial use-case 1           |     |

|   | 6.4  | Conclusion                                                         | 107 |

| 7 | -    |                                                                    | 09  |

|   | 7.1  | 0                                                                  |     |

|   |      | 7.1.1 Multicore achitectures                                       |     |

|   |      | 7.1.2 Allocating real-time applications in heterogeneous systems 1 |     |

|   | 7.2  | Slack-Based Allocation (SBA) algorithm                             |     |

|   | 7.3  | Preliminary evaluation                                             |     |

|   | 7.4  | Conclusions                                                        | 117 |

| 8 | Con  | clusions 1                                                         | 21  |

| Bibliog | aphy 122             |

|---------|----------------------|

| 8.3     | Publications         |

| 8.2     | Future Work          |

| 8.1     | Thesis contributions |

## Introduction

# 1

In this chapter the context of this thesis is described, explaining the most relevant properties of real-time cyber-physical systems, real-time safety-critical systems, response time analysis and model-driven engineering, which are fundamental concepts in this work. Then, the motivational railway signalling application is presented as a paradigmatic industrial use-case of the schedulability analysis and optimization problems addressed here. Finally, the objectives of this thesis are listed, and the organization of this document is described.

#### 1.1 Context and background

#### 1.1.1 Real-time cyber-physical systems

In real-time systems, correct function depends not only on results being right, but also on them being produced in time, meeting the timing requirements imposed on the software, usually deadlines. Nowadays, many of these systems correspond to cyber-physical systems, which are information technology systems integrating computation, storage and communication capabilities along with sensorization and/or control of elements or devices in the physical world. This type of systems, as well as the technology developed around them, is particularly relevant in the conceptual framework of Industry 4.0 (or the fourth industrial revolution) on which both research entities and businesses are currently focusing their attention.

From the viewpoint of their physical architecture, these cyber-physical systems are in reality distributed real-time systems, with several processors that may be homogeneous or heterogeneous in terms of their core architecture and computation speed, connected by one or more communication networks. Such networks may be based on different standards, such as the IEEE 802.1 working group's Time Sensitive Networks (TSN) [TSN] or partitioned such as ARINC-664 [Aer09] from the avionics domain. Their logical architecture is composed of tasks and messages. Both are characterized by deadlines, which are timing requirements that must be met even in the worst scenario, and by worst-case execution/transmission times. Their

activation can be periodic or not. The task constitutes the minimal schedulable unit in a computer, which can only be executed if the required hardware and software resources are available. Their activation can undergo some variability, which is known as jitter. The messages, whose minimal schedulable units are the packets, enable the communication among tasks with precedence relationships, making up the so-called end-to-end flows (henceforth e2e flows). All tasks and messages are activated when certain stimuli are produced. Depending on the nature of the stimuli, two criteria for classification of the real-time systems are recognized in [Kop11]: those activated by time and called Time-Triggered (TT), and those activated by events and called Event-Triggered (ET).

Scheduling the execution order of concurrent tasks is determined by an algorithm implemented in a component called scheduler, which is in charge of determining when tasks are executed in a processor (and also when messages are sent through a network). Determining in which computers the tasks are executed and through which networks the messages are sent, often known as allocation, increases the problem's complexity, thus making it an NP-hard problem [TBW92]. Algorithms providing optimal solutions in polynomial time for this type of problems are not known yet, so typically generic search and optimization algorithms are used.

#### 1.1.2 Real-time safety critical systems

A critical system is one that has functions whose failure can bring about severe consequences for humans, materials and/or the environment. One of the main characteristics that a critical system must provide is dependability, bringing together the concepts of availability, reliability, integrity, maintainability and safety. Safety is quantified through the "Safety Integrity Level" (henceforth SIL), which is the relative level of risk reduction provided by a safety function, or an objective level for risk reduction [SS04]. The safety levels range from SIL1, the lowest, up to SIL4, the highest.

Complex systems such as automobiles, trains and airplanes combine non-safety functions with other different-level safety ones. In the past, these functions were deployed in independent physical systems to avoid interference of the non-safety ones with the safety ones. This paradigm usually requires a large amount of heterogeneous equipment, leading to increased costs of installation, start-up and maintenance.

With the aim of reducing costs and using resources efficiently, cyber-physical systems have evolved in recent years by incorporating multi-processor architectures and also

virtualization techniques, thus enabling the execution of distinct functionalities of the system in spatially and temporally protected environments, called partitions, on a single hardware platform. Each partition can have distinct non-functional requirements to guarantee response times, safety, confidentiality, etc., which make up the so-called mixed-criticality systems [Ves07]. In [BD17], a detailed review of the work done in the last decade on this type of systems is carried out, ranging from the most theoretical scheduling or design aspects, to the basic implementation mechanisms. In mixed-criticality systems it is necessary to have total independence among partitions with the aim that the processes of specification, design, implementation, certification (in those systems that require it) and execution are totally independent throughout the distinct system components [SO12] [BLS10] [Goo+13] [Cre+14]. In the European project MultiPARTES [Tru+14] for example, a set of tools was proposed for the development of mixed criticality systems based on partitioning, from hardware and software architectures to partition management tools.

In safety-critical systems, real-time operating systems are typically used to guarantee the deterministic execution of tasks, based on a specific scheduling policy or a combination of them, including cyclic executives, fixed priorities or deadline-based priorities [Liu00]. Cyclic executives were the most widely used until the advent of priority-based scheduling, which has had an enormous repercussion in most designs [PEP04a], and which is present in operating systems that follow the POSIX [IEE03] or AUTOSAR [AUT03] standards, in communications networks such as CAN [Bos91] and in programming languages such as the Ada standard [IS012]. Nowadays, partitioned systems enable the combination of characteristics of cyclic executives and fixed priorities in a hierarchical scheduling, with the partitions as the basic scheduling level and the use of priorities within each partition. This is the case of VxWorks [Win16] used in avionics, or Integrity [Gre] used in the railway domain, which are SIL3 certified.

#### 1.1.3 Model-driven engineering

The methodology consisting of creating abstractions, i.e. models, that allow developers to capture key information which is essential to the system-development process is called Model-Driven Engineering (MDE) [Sch06]. The abstraction of a system into a model allows developers to focus on relevant information independently from the platform where it is implemented. There are several aspects to address during the development of cyber-physical real-time systems, such as timing features, safety and security issues, logical and physical architectural designs, etc. All the information

contained in those aspects, represented by different models capturing different views of the same system, is formalized and then it can be processed through a series of model transformations, which greatly facilitates development.

The Object Management Group (OMG) defined several concepts for modeling realtime systems, gathered in the MARTE [Obj11] standard. In this context, the University of Cantabria developed the MAST model [Gon+01] to capture the time-related features of real-time systems, modeling the tasks and messages that compose the e2e flows in order to analyze them via response-time analysis techniques. Its first version, which allows both single-processor and distributed systems to be modeled, is used in all the analysis and optimization tools within the MAST tool suite. Its second version, MAST 2 [Har+13], changed a few element names in order to align them with MARTE's UML profile [Obj11] for real-time embedded systems, and also includes hierarchically scheduled systems, support for network switches and other novel scheduling approaches. MAST's implementation is open source under GPL license and it has been successfully integrated in other model-based development tools, such as TEMPO [Hen+15], as part of the MDE methodology.

#### 1.1.4 Response-time analysis

Guaranteeing the correct timing behavior of a system, even after building it, cannot be done generally by testing, as it is not possible to assure that the worst-case scenario has been considered by means of this methodology. Response-time analysis techniques are used to calculate the worst and best-case response times of tasks in a real-time system. This subsection contains a brief introduction to the most relevant approaches that have provided the basis for the new technique developed in this thesis.

Response time analysis for distributed real-time systems was first addressed in [TC94], where the authors propose the so called *Holistic* analysis for fixed priority systems. In this approach, each processor is analyzed independently, and it is assumed that all tasks are activated at the same time, thus not considering precedence relations that characterize e2e flows. That activation time is called the critical instant and leads to the busy period, which is the time when the processor is executing tasks with higher or equal priority to the task under analysis. This technique, rather than being exact, which would be intractable for complex systems, obtains upper bounds of worst-case response times. In that work, deadlines could be greater than the activation rates, and the activation *Jitter* that workload events may suffer was incorporated into the worst-case analysis.

With the aim of reducing the pessimism of Holistic analysis, offset-based analysis techniques were proposed [Tin94]. Offsets express the minimum instant at which a task is activated, which leads to a less pessimistic worst-case response time calculation. Later, this technique was extended to distributed systems by [PG98]. In [PG99] an improvement of the offset-based technique was introduced, which takes into account the precedence relationships of tasks to provide a tighter estimation of the response times. Another improvement of the offset-based technique was proposed in [MN08], which provides better results than [PG98] but it does not always improve the results of [PG99].

In [Pal+16] the authors propose an offset-based analysis technique for distributed real-time systems based on time-partitioning, based on the compositional approach of [Riv+11]. In order to analyze time-partitioned systems, each partition is analyzed independently. The rest of the partitions are modeled as a high priority e2e flow, called *Unavailability flow*, which is integrated in the offset-based analysis. This unavailability flow is inspired by the concept of *availability function* introduced in [AP04] to model the partition windows during which a given task may be scheduled; the authors used the inverse of this function for the analysis.

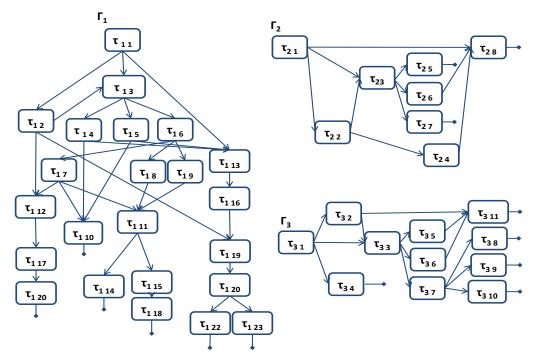

Modern real-time applications usually exhibit complex activation patterns, where a task may trigger more than one task, i.e. a fork pattern, and similarly, a task may be activated after the execution of one or more tasks is completed, i.e. join/merge patterns. This model is commonly known as a multipath model. In addition to the aforementioned MAST model, based on the MARTE standard 's e2e flows, the Directed Acyclic Graph (DAG hereafter) model is a system model that can also describe multipath architectures, which is widely used in the real-time community. It was first introduced by [LA10] to support the analysis of real-time tasks, and in [LA11] it was extended to distributed real-time systems.

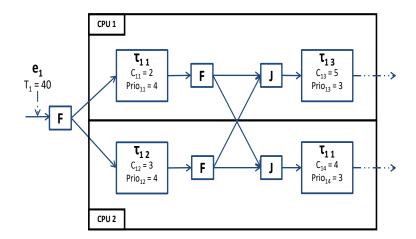

The schedulability analysis of multipath e2e flows was addressed in [GPH00], where the authors described the procedure to calculate the worst-case response times of tasks within multipath e2e flows. This technique is based on the holistic approach, which is known to be pessimistic. In [HE05] a compositional approach is proposed called Symta/S, where systems are modeled as networks of resources and workloads as tasks with precedence constraints. However, only fork patterns, and not join ones, are considered in this approach, which they name tree-shape dependecy model. In [Fon+16] a schedulability analysis method for DAG tasks is proposed, although it is not applicable in the context of this thesis due to some limitations that will be discussed later. To this day, there is no response-time analysis technique that includes the two fundamental features addressed in this thesis: time-partitioning and a multipath model.

There are other approaches that have addressed response time analysis considering similar system models. For instance, in [KHB16] a timing analysis approach for cyclic real-time stream processing applications is presented. The targeted architectures are multiprocessor systems. Another interesting contribution on the schedulability analysis of time-partitioned systems was proposed in [Mar+12], where a response time analysis method is proposed for mixed-criticallity applications. This technique is not applicable to this work since it does not allow tasks of the same e2e flow to be located in different partitions, which is a common feature in partitioned systems that make use of an Input/Output (I/O) partition to handle communications with other nodes of a distributed architecture.

A special mention should be made of Assertion Based Verification techniques, which include formal verification methods where designs are verified against certain assertions. In [Anw+20] a unified framework for executing static and dynamic verification [Anw+19] for embedded system design is presented. One common static verification method is Timed Automata Models [AD94] which enable the determination of whether or not timing requirements are met. A popular tool that is used in this context is UPPAAL [Hes+08], which can be used to assess whether a system will meet its timing constraints. A recent research work [HZZ20] shows how ARINC-compliant time-partitioned schedulers can be modeled following this method. However, the response time analysis techniques explored in this thesis have several advantages that may be important in some classes of systems. On the one hand, the result of the analysis, i.e., worst-case response times, are very intuitive numbers for engineers who want to assess how far or close the response times are to the deadlines. On the other hand, response time analysis can be used easily to analyze complex systems, which may have rather large timed automata models. Besides, for complex models response time analysis is considerably faster than applying model checking techniques. Readers are encouraged to read [Per+09], where the authors perform a deep study on how different abstractions affect the performance analysis of real-time systems, concluding that there is no abstraction that always outperforms the others.

These reasons motivate the extension of response time analysis to be applied in hierarchical time-partitioned systems to multipath flows.

#### 1.2 Industrial use-case

The use-case addressed in this thesis challenges the state-of-the-art schedulability analysis and scheduling optimization techniques developed so far, applied to safetycritical distributed real-time systems. It is based on a railway signalling application, part of the European Rail Traffic Management System (ERTMS) [ERT06]. ERTMS is a standard resulting from an important European industrial project which aims to create a common system for traffic signalling and management in railways. This standard has two main components: GSM-R (Global System for Mobile Communications - Railway), which is in charge of wireless communications, and ETCS (European Train Control System), which performs signalling and supervision duties for traffic management. On-board ETCS is the distributed and safety-critical equipment within the vehicles that performs computation tasks. It is connected to other on-board subsystems, such as switches, sensors or other processing units performing secondary functionalities, by point-to-point connections through interfaces specified in the standard.

Trains receive driving indications and restrictions from the railway infrastructure, such as balises and other interfaces, for instance radio connections with centralized control centers. The main duty of the on-board ETCS subsystem is to provide drivers with all the information needed for safe driving, as well as supervising that the train is travelling respecting the received instructions at all times.

To do so, different safety functionalities must be carried out within a bounded time. In this work, the signalling application performs three functionalities: (1) Applying the Emergency-Brake (EB functionality), (2) Radio Block Center communication session establishment (RBC-CS functionality) and (3) Parameter visualization in the Driver-Machine Interface (PV-DMI functionality). Each of these functionalities, as well as related software and hardware, need to be certified for a certain integrity level. Safety standards force all safety functionalities to be SIL4, while other noncritical functionalities might be lower, even though they share the execution platform with high-criticality ones. On the other hand, execution platform suppliers only guarantee SIL 2 hardware equipment, so another mechanism must be implemented in order to obtain SIL4 functionalities, even when software has been certified for SIL4. This mechanism is, in this case, a Dual Modular Redundancy (DMR) architecture, where results are voted for following a 1002 scheme [IEC10]. Event synchronization therefore becomes a major concern, since higher integrity levels can be reached with replicated software architecture rather than using a single instance of the execution platform.

7

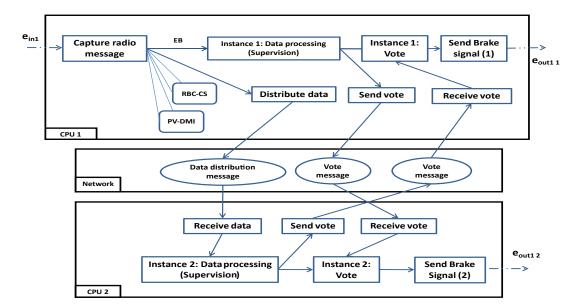

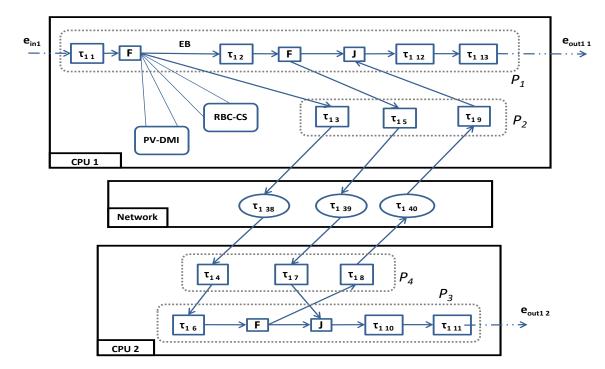

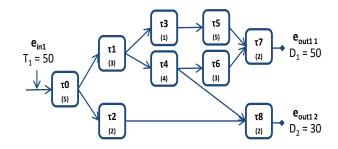

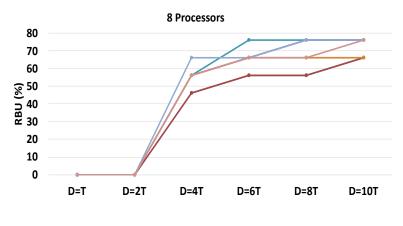

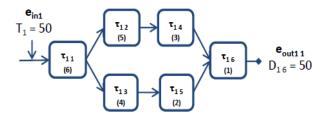

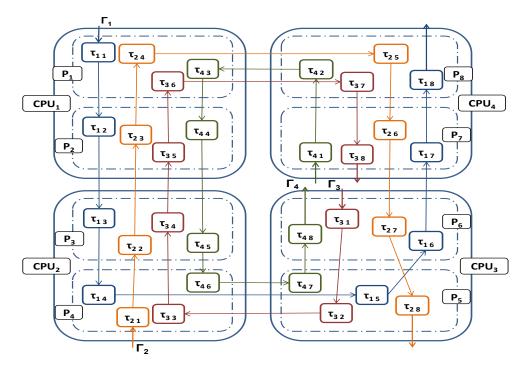

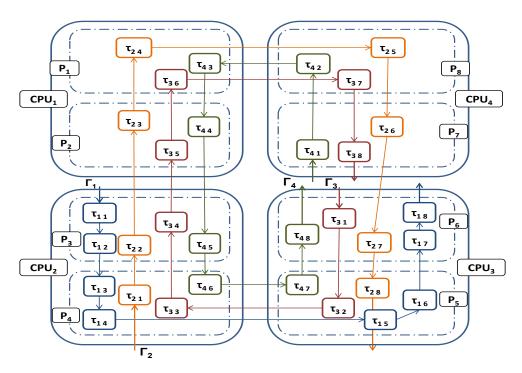

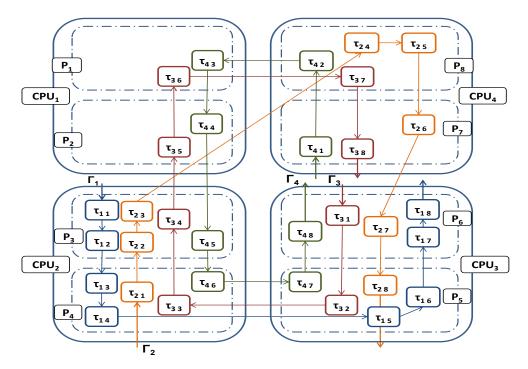

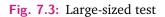

Fig. 1.1: Architecture of EB functionality

Figure 1.1 describes in detail the multipath architecture of the EB functionality for a SIL4 implementation. The other two functionalities (RBC-CS and PV-DMI) follow the same architecture. A workload event, which is triggered when the train runs through a balise or receives a radio message, activates a sequence of activities that are briefly explained as follows: (1) the message coming from any interface, considering that its integrity level is guaranteed by previous processing, is captured, (2) supervision is then performed at the first instance in CPU-1 by processing the captured data, and (3) concurrently, data is distributed to the second instance executing in CPU-2 for redundant processing, (4) results obtained from both supervision functions are interchanged, so that they are independently voted for each processor, and (5) the voting results are sent twice to the external subsystem in charge of commanding the brakes. Deadlines are imposed on the brake activation events ( $e_{out1 1}$  and  $e_{out1 2}$ ) referred to the signal reception ( $e_{in1}$ ). Missing these timing requirements would lead to a system failure and a train crash might happen.

Train manufacturers have already implemented such an application. However, its implementation is based on a simple cyclic executive where all functions composing functionalities are called periodically, even if they do not have useful work to do. This results in inefficient resource usage which has become a major concern for train companies: 100% of processing capacity is dedicated to the execution of the application. The current implementation does not support the addition of extra functionalities easily or the possibility of integration it with other applications while guaranteeing the system's integrity. Worst-case response times are estimated now by testing the sequential application code to ensure that deadlines are met, and

integrating this application with others would require more sophisticated response time analysis techniques than just testing. For these reasons, manufacturers seek a complete system re-design, making use of modern techniques such as those used in avionics or the automotion industry mentioned in the previous section. Timing behavior prediction of critical parts is essential. However, and to the best of our knowledge, there is no response-time analysis technique that could be directly applied to the redundant application based on partitioning addressed in the use-case, in order to check whether timing constraints are met. Therefore, in parallel to the system re-design, a new schedulability analysis technique will be developed, as well as an implementation in an analysis tool that will enable the validation of timing constraints of applications following the new architecture. Then, new optimization algorithms based on this approach will be proposed, including priority assignment, partition window assignment and allocation strategies.

#### 1.3 Objectives

The general purpose of this thesis is, based on the requirements that have been identified in the aforementioned use-case, to investigate optimized techniques for the schedulability analysis and optimization of partition-based distributed real-time systems with multipath flows. It is common that these systems are found in safety critical domains, such as automotive or avionics, where cyber-physical systems must adhere to strict safety requirements imposed by certification authorities. That is why the developed techniques, devoted to guaranteeing that timing requirements are met, are intended to be applicable to other systems with analogous requirements.

To do so, the following particular objectives will be addressed:

- Formalisation of the system model. It should be a realistic system model capable of capturing all the time-related features that describe the timing behavior of real-world cyber-physical systems used nowadays.

- Development of a schedulability analysis technique for partition-based distributed real-time systems with multipath flows, which enables the determination of whether the imposed deadlines are met under specific scheduling schemes. This technique will be implemented complying the system model previously mentioned, which will improve the precision of existing approaches.

- Development of algorithms that carry out the synthesis of the targeted systems, based on the proposed response-time analysis:

- Priority assignment algorithms: Based on the state-of-the-art algorithms, several non-iterative priority assignment algorithms will be proposed and adapted to the system model addressed in this work.

- Partition window assignment algorithm: An algorithm that produces a partition window assignment for each partition will be developed.

- As a secondary objective, an allocation algorithm will be developed in order to address the allocation problem in heterogeneous architectures.

Providing a complete solution to the industrial use-case is the priority of this thesis, where the allocation problem is not fully related to it.

- Validation of the proposed solutions. The aforementioned railway signalling application will be targeted, and general and representative systems will also be evaluated, in order to characterize the behavior of the proposed algorithms.

As a result of this thesis, it is expected that a methodology for developing distributed and partition-based real-time systems will be formalized. This methodology will include modeling, analysis, deployment and scheduling phases, and it will be composed of several tools that will be used in real-time safety-related industrial applications.

#### 1.4 Organization

This thesis is organized as follows. After this Introduction, where the most relevant concepts of this work are presented, an extensive literature review regarding the optimization of distributed real-time systems is detailed in Chapter 2.

Chapter 3 presents the system model that has been selected to describe the timerelated features of the applications addressed in this thesis.

In Chapter 4, the development of a new response time analysis technique is presented, together with its application and evaluation on the target industrial use-case and also to general distributed real-time systems scheduled by FP.

Chapter 5 describes the priority assignment algorithms proposed in this thesis, which can be applied to the railway use-case and also to general FP distributed systems. Some conclusions referred to their applicability are drawn in this chapter.

Chapter 6 contains the partition window assignment algorithm, which is used to derive the primary scheduler of the hierarchical schedulers addressed in this work.

In Chapter 7, the allocation problem is introduced and first steps are given, providing some solutions and opening the path towards more sophisticated ones for this open problem.

Finally, the most relevant conclusions of this thesis are drawn in Chapter 8, reviewing the objectives set at the beginning of the work. In addition, future research challenges to be addressed from now on are presented.

## Scheduling and optimization in distributed real-time systems: a literature review

This chapter compiles the work carried out on the task allocation and scheduling of distributed real-time systems. The works are classified according to their algorithmic approach and a brief outline of each one is provided.

#### 2.1 Introduction and methodology

The comprehensive literature review carried out in this chapter contributes to two main aspects. On the one hand, to complement the work [BD17] in which a detailed review was carried out of mixed criticality systems focused on the temporal analysis, both of single-processor and multiprocessor systems, and in which different system models and real industrial applications are also described. This work complements that review in relation to the optimization of the allocation and scheduling of distributed real-time systems, aspects that were dealt with in less depth and that are of great interest in the development of current systems. On the other hand, it also considers other works on allocation and scheduling optimization, which, although not focused on mixed-criticality systems, do address distributed real-time architectures that are of interest in the design of current industrial applications.

Thus, this chapter compiles works considering this problem, since it was approached for the first time in [TBW92] up to the first half of 2021, mostly ordered chronologically and classified according to the algorithmic focus employed. All the works are included in a table showing their most remarkable aspects, with the aim of providing a clear summary of the state-of-the-art and facilitating consultation for future work on the optimization of the allocation and scheduling of distributed real-time systems.

As mentioned in the previous chapter, due to the NP-hard nature of the problem of allocating and scheduling of distributed real-time systems, optimization algorithms

are used. These provide valid solutions that may be optimal or sub-optimal. This chapter focuses on works that use different algorithmic approaches, which will be briefly described:

- Genetic algorithms (GAs) [Hol75] are generic probabilistic metaheuristics that form part of the so-called evolutionary algorithms. These algorithms imitate biological mechanisms (adaptation to the environment, mutation, crossover, inheritance ...) that guide the evolution process in species, and which are used to look for solutions to diverse problems in wide search spaces.

- Tabu Search (TS) [Glo86] is a general-purpose metaheuristic procedure for search and optimization, which forms part of the local search techniques. Its main characteristic is the possibility to avoid sub-optimal local solutions within the solutions space of a specific problem.

- Simulated Annealing (SA) is a generic probabilistic metaheuristic technique to approximate the global optimization in an extensive search area. As can be seen in [Kir84], it is inspired by the annealing process in metallurgy.

- Mathematical programming [Min86] is a family of optimization techniques to maximize or minimize a function, systematically choosing input values among some permitted values and calculating the value of the function. This function can be subject to certain restrictions expressed in terms of equalities and/or inequalities. Depending on the type of functions and restrictions, as well as on the values assigned to them, there are different variants of mathematical programming.

The objectives of Linear Programming (LP) [Sch98], which forms part of mathematical programming, is to maximize or minimize a linear function subject to restrictions, which is formulated through simple linear equalities or inequalities. If all the variables are integer numbers, it is denominated Integer Linear Programming (ILP), while if only some are, it is denominated Mixed Integer Linear Programming (MILP). If all equalities and inequalities are non-linear, it is simply denominated Mixed Integer Programming (MIP). Geometric Programming (GP) [Boy+07] is the type of mathematical programming used to maximize or minimize polynomial functions with restrictions. These are formulated through monomial equalities equal to 1 and posynomial inequalities less than or equal to 1.

Constraint Satisfaction Programming (CSP) is a type of mathematical programming based on determining the value of the variables guaranteeing fulfillment of an objective function [Tsa14]. If the variables of the objective function and

14

the functions of restrictions are Boolean, it is called a Boolean Satisfaction Problem or simply SAT. Lastly techniques based on Satisfiability Modulo Theories (SMT) are also considered, which consist of formulas in first-order logic in which some function has additional interpretations, and it must be determined whether a formula can be satisfied [BT18].

- Branch and Bound (BB) [LD60] is a generic algorithm used in combinatorial and discrete optimization problems and mathematical optimization. The candidate solutions are numbered forming a tree and discards are made based on estimations above and below the factors that must be optimized.

- A heuristic (HEU) [Pea84] is a problem-solving method founded on rules built according to criteria linked to the problems themselves, generally based on previous experience. Although finding an optimal solution is not guaranteed, reasonably good solutions can be found in an acceptable time if they are well constructed.

The review of the works is done according to the following methodology. On the one hand, the problems addressed in each one are reported, from the viewpoint of allocation, type of scheduling and partitioning. These characteristics are fundamental in those real-time systems that implement functionalities with different levels of criticality. The review will also focus on the objectives of each work. They all share the aim of system schedulability, and we will also consider those aiming to minimize the following parameters: the number of computers, resource utilization and response times. Lastly, the restrictions presented in each work in terms of the use of memory and the relation between the deadlines and the periods (D/T) in the system model described are identified, where possible. All these characteristics are shown in tables as a summary, which constitutes a guide to finding in an easy way the solutions available for a specific problem of interest.

#### 2.2 Genetic Algorithm (GA)

In [MR93], [HAR94] and [MBD98] different variations of GAs are used to allocate tasks in processing elements. All of them are used to create cyclic schedulings with the aim of minimizing their response times. In [MR93] and [MBD98] e2e flows defined through their deadlines and periods are considered, and in [HAR94] a multiprocessor system is proposed.

In [DJ98] a multi-objective algorithm is developed to decide on the amount of hardware resources in a System On Chip (SoC), as well as to allocate the tasks in the processor nodes and to build cyclic executives. The combined use of GA and TS aims to minimize energy consumption and the price of the resultant system, while meeting all the temporal restrictions.

The work [FDB00] also proposes the allocation of periodic tasks and the creation of cyclic scheduling. However, the system model considers identical processors, connected through Time Division Multiple Access (TDMA hereafter) networks. To do so, turns are explicitly assigned.

In the works [OW04] and [Yoo09], GAs are used to allocate tasks in identical processors and to determine cyclic scheduling in distributed real-time systems. Both consider e2e flows and predefined deadlines, and their principal objective is to minimize the sum of all the differences between the worst-case response time and the deadline of all the flows. They also aim to minimize the number of processing elements. These works are differentiated by the convergence mechanisms of the GA towards a suitable solution.

In [Ham+06], a multi-objective GA is proposed to assign priorities to tasks, as well as to determine the timing slots for the messages transmitted through a TDMA network. A specific timing analysis technique is used, which enables the adjustment of the variables and objectives to be minimized.

In [SDJ07], a system model is considered, based on computers with memory resources and e2e flows whose period and deadline are predefined. Its main objective is to minimize price and energy consumption of the resultant system, in which the number of processors, communication elements and FPGAs are determined. Scheduling is carried out through a heuristic algorithm that uses Pareto optimization criteria to evaluate the candidate solutions [GH88], [FF98].

In [Sam+09], genetic algorithms are used to assign priorities to tasks and fixed priorities and frame identifiers to messages in a distributed real-time system connected through a FlexRay network. The main aim is to optimize the average response time of the system.

The work [Azk+11b] develops a permutational coding for a GA whose objective is the assignment of priorities to tasks and messages making up a distributed real-time system. The results obtained in this work show an improvement on those obtained by [GG95] using a heuristic called HOPA. Later, in [Azk+12], this same coding is used to schedule the tasks of that system, this time using HOPA to generate the first population of solutions that the algorithm will optimize. Finally, in [Azk+11a], a GA

16

is used to allocate and schedule tasks and messages in distributed real-time systems, minimizing parameters such as utilization of computers, memory resources and communications, response times and the number of computers used, while meeting all the real-time requirements.

In [Woz+13], a GA is used for the synthesis of distributed real-time systems, composed of heterogeneous processing elements. The synthesis process is made up of the following phases: allocation of software components (composed of sets of runnables) in processing elements and signals from the communications buses, decomposing the runnables into tasks and signals into messages, and assignment of fixed priorities. As well as meeting all the deadlines, it has the aim of optimizing some parameters: the response time of the e2e flows, the use of memory, the performance of the communications buses and the response time of the runnables.

The work [BO14] proposes a GA to minimize the response time of a real-time system with periodic and aperiodic tasks, while maintaining an equilibrated use of the processor elements. It considers flows with pseudo-periods and also the use of fixed and dynamic priorities. It uses a correcting technique in the solutions to guide the initialization of the algorithm and to maintain the precedence relations of the tasks. In [BO16], a stage based on quantum logic coding is added to the genetic algorithm.

In [Aya+16a], a genetic algorithm is used to allocate independent tasks in heterogeneous distributed real-time systems, to which fixed priorities are assigned following the Rate Monotonic scheme. The total execution time, the cost of communications among tasks and memory consumption are expressed in suitable fitness functions that must be minimized. In the next work [Aya+18], an advanced genetic algorithm (ImGA) is proposed that implements a crossover operator based on schedulability of tasks [Aya+16b], which improves the precision of the genetic algorithms previously used.

In [WME20], the authors develop a genetic algorithm to generate feasible schedules in hierarchically scheduled multicore systems, by means of novel chromosome coding and fitness functions.

After reviewing the works using genetic algorithms, it can be highlighted that this approach is used habitually as a multi-objective optimizer, given that they search for solutions in which more than one parameter has to be minimized (costs, number of computers, etc.). The reviewed works are collected in Table 2.1.

| Work      | Addressed Problems |              |            | Minimi    | Restrictions |          |       |        |

|-----------|--------------------|--------------|------------|-----------|--------------|----------|-------|--------|

| WOIK      | Allocation         | Scheduling   | Partitions | Computers | Utilization  | Timing   | D/T   | Memory |

| [MR93]    | Yes                | Cyclic       |            |           |              | Response |       |        |

| [HAR94]   | Yes                | Cyclic       |            |           |              | Response |       |        |

| [MBD98]   | Yes                | Cyclic       |            |           |              | Response | D = T |        |

| [DJ98]    | Yes                | Cyclic       |            | Cost      | Energy       |          | D < T |        |

| [FDB00]   | Yes                | Cyclic       |            |           |              |          | D = T |        |

| [OW04]    | Yes                | Cyclic       |            | Number    |              | Response |       |        |

| [Yoo09]   | Yes                | Cyclic       |            | Number    |              | Response |       |        |

| [Ham+06]  |                    | Priorities   |            |           |              |          | D < T |        |

| [SDJ07]   | Yes                | Cyclic       |            | Cost      | Energy       |          |       | Yes    |

| [Sam+09]  |                    | Priorities   |            |           |              | Response |       |        |

| [Azk+11a] | Yes                | Priorities   |            | Number    |              | Response |       |        |

| [Woz+13]  | Yes                | Priorities   |            |           |              | Response |       | Yes    |

| [BO14]    | Yes                | Priorities   |            |           |              | Response |       |        |

| [Aya+16a] | Yes                | Priorities   |            |           |              | Response |       | Yes    |

| [WME20]   | Yes                | Hierarchical | Yes        |           |              | Response | D = T |        |

Tab. 2.1: Reviewed Works - Genetic Algorithm

#### 2.3 Tabu Search (TS)

In [PKR00], the use of TS is proposed to allocate tasks with precedence relations in processors and create cyclic scheduling for real-time, heterogeneous multiprocessor systems, composed of identical processor except for one with higher processing power. The principal objective is to minimize the system's response time.

In [CL00], a hybrid algorithm is developed based on TS to solve the problem of allocating tasks with precedence relations in a multiprocessor architecture. The objective is to meet the real-time requirements of the system while satisfying the restrictions in maximal computation capacity of the computers, as well as to minimize the network traffic and the number of computers utilized.

The work [LKY00] proposes the values of the operators and configuration parameters of the TS and GA algorithms, with the objective of allocating real-time tasks and creating cyclic scheduling in multiprocessor architectures, whose processors are considered identical. The objective is to minimize the system's global response time.

In [TP11b], an optimization method is proposed for partitioned distributed realtime systems. Through an algorithm based on TS, it attempts to allocate tasks in processing elements and to define their temporal execution windows within the MAF. The algorithm is also in charge of assigning tasks to these temporal partitions and generating a cyclic executive. The objective is to meet the deadlines of all the tasks at the same time as maximizing the downtime of the temporal partitions. Later,

| Work    | Addressed Problems |              |            | Minim     | Restrictions |          |       |        |

|---------|--------------------|--------------|------------|-----------|--------------|----------|-------|--------|

|         | Allocation         | Scheduling   | Partitions | Computers | Utilization  | Timing   | D/T   | Memory |

| [PKR00] | Yes                | Cyclic       |            |           |              | Response |       |        |

| [CL00]  | Yes                | Priorities   |            | Number    | Net. & CPU   | Response |       |        |

| [LKY00] | Yes                | Cyclic       |            |           |              | Response |       |        |

| [JPJ17] |                    | Priorities   |            |           | Energy       | Response | D < T |        |

| [TP11b] | Yes                | Hierarchical | Yes        |           |              | Response | D < T |        |

| [TP15]  | Yes                | Hierarchical | Yes        |           | Cert. cost   | Response | D < T |        |

Tab. 2.2: Reviewed Works - Tabu Search

the work is extended in [TP15], where a series of techniques is proposed to enable the scheduling of the applications, for which the costs of certification are taken into account to host mixed criticality applications, which are minimized using different techniques.

In [JPJ17], a multiobjective algorithm based on TS is used to schedule tasks and messages in embedded distributed real-time systems. The objective is to develop an implementation that meets the system's real-time requirements, as well as the safety and dependability ones, while minimizing the energy consumption. Priorities are assigned to the tasks in descending order, and it is assumed they have been allocated in the processors previously.

Although there are not many works in which TS is used, it can be seen in Table 2.2 that varied problems and optimizations are tackled, including partition-based systems.

#### 2.4 Simulated Annealing (SA)

In [TBW92], SA is used to allocate tasks and to assign them fixed priorities in distributed real-time systems, in which a TDMA communications network is used. In this system model, memory resources of the computers are considered and the tasks have a series of candidate computers in which they can be allocated. Moreover, some tasks are replicas of others and cannot be allocated in the same processor. The deadline of the tasks is equal to their period, and the priorities are assigned following the Rate Monotonic criterion. The objective of this work is to minimize the network load while all the tasks meet their deadlines. Another restriction to be considered is the use of the memory of the computers, which must not be surpassed.

The work [Bur+93] proposes an algorithm based on SA to allocate tasks in processing elements and to assign them fixed priorities. It is considered that each task has a series of candidate computers in which it can be allocated. It also considers e2e flows with periods and deadlines. The objective is to minimize the worst-case response time of all the flows as well as the number of auxiliary tasks that route communications.

In [CP95], SA is used to generate cyclic schedules in distributed real-time systems. The objective is to minimize the jitter of the tasks while meeting the deadlines of the e2e flows.

In [DS95], SA is used to create a cyclic scheduling in distributed real-time systems based on flows made up of periodic tasks. The objective is to minimize the jitter of the tasks while the deadlines of the tasks and flows are met.

The work [VO05] presents a comparative study of Multi-start [Mar03], SA and TS algorithms used for scheduling distributed real-time systems, connected through a *Foundation Fieldbus* [VP08] communications network. The results show that SA is the most difficult algorithm to configure and that TS obtains more numerous and better results.

In [HGZ10], SA is used to allocate tasks in homogeneous computers, as well as to assign priorities and periods to the tasks and to configure access to the communications network based on Time-Triggered Protocol (TTP hereafter) [KG93b]. The deadlines of the tasks are equal to their periods, and the objective is to minimize the worst-case execution time of all the e2e flows. The proposal is based on two phases. The first uses SA for task allocation. Later, on top of this solution, GP is used to fix the deadlines of the tasks and to manage access to the communications network.

In [EB10], the use of SA is proposed for the allocation of tasks and messages and assignment of priorities with the aim of facilitating the extension or updating of scenarios, minimizing the impact of these changes in terms of the requirements of the original system.

In [TP11a], the use of SA is proposed to solve a problem of optimization of distributed real-time systems with partitions. The temporal partitioning is implemented through time slices in which the execution of tasks is divided within a processing element, and it is the algorithm that decides on the order and length of these portions within the processor. It is assumed that the tasks are previously allocated in the processors. The scheduling is cyclic for the critical tasks, while the non-critical ones are scheduled using preemptive fixed priorities. The objective is to optimize the sequence and length of the temporal windows and to obtain schedules that permit all the safety-critical applications to meet their deadlines.

20

| Work     | Addressed Problems |              |            | Minin     | Restrictions  |          |            |        |

|----------|--------------------|--------------|------------|-----------|---------------|----------|------------|--------|

|          | Allocation         | Scheduling   | Partitions | Computers | Utilization   | Timing   | D/T        | Memory |

| [TBW92]  | Yes                | Cyclic       |            |           | Network       | Response | T = D      | Yes    |

| [Bur+93] | Yes                | Cyclic       |            |           | Routing tasks | Response |            |        |

| [CP95]   | Yes                | Cyclic       |            |           |               | Response |            |        |

| [DS95]   |                    | Cyclic       |            |           |               | Jitter   |            |        |

| [VO05]   | Yes                | Cyclic       |            |           |               |          |            |        |

| [HGZ10]  | Yes                | Priorities   |            |           |               | Response | D = T      |        |

| [TP11a]  | Yes                | Hierarchical | Yes        |           |               | Response | $D \leq T$ |        |

| [PA15]   | Yes                | Priorities   |            |           |               | Response | D = T      |        |

| [McL+20] | Yes                | Priorities   |            |           |               | Response | $D \leq T$ |        |

Tab. 2.3: Reviewed Works - Simulated Annealing

In [PA15] a comparative study is also made, this time between SA and GA. The scheduling of tasks is evaluated in homogeneous multiprocessor architectures, with the objective of minimizing the response time of the system respecting the precedence relations of the tasks. The study demonstrates that after 9 case studies, SA obtains 6 acceptable solutions while GA obtains 5. Most of the works that made use of SA have approached the allocation problem as well as the scheduling one. The minimization of the jitter of the tasks is addressed for the first time.

In [McL+20], the authors use SA to address the allocation and scheduling of autonomous driving applications on multicore systems. They propose several strategies such as deadline and offset adjustments and random task re-allocations, and their results considerably improve previous works based on heuristics and GA.

Most of the works that use SA have addressed the task scheduling and allocation problems combined. As shown in Table 2.3, the minimization of tasks' jitter is addressed for the first time.

#### 2.5 Mathematical Programming

In [SK01], CSP is used to allocate tasks in processing elements and to create cyclic scheduling in distributed real-time architectures. These architectures are composed of heterogeneous networks that connect computers to memory resources and Application Specific Integrated Circuits (ASIC). The tasks are selected sequentially and allocated in the processor with the lowest cost. After the allocation, the BB technique is used to assign an execution time to each task. The objective is to minimize the time of all the scheduling without overusing the memory resources. In [SK03], a method is presented to facilitate the allocation problem and the scheduling one previously mentioned.

In [EJ01], CSP is used to allocate tasks in computers and to create cyclic scheduling in distributed real-time systems. The computers are heterogeneous and they are connected through a communications bus. The principal contribution of this work is the evaluation of several local search heuristics that decide which variables and what values are assigned in each iteration. There are 3 objectives: minimize the total time of the scheduling, minimize the communications through the bus and maintain an equilibrated use of the processor elements.

In [MH06], SAT is used to allocate and schedule tasks in distributed real-time systems composed of heterogeneous processor elements. For this, priorities are assigned to the tasks of each computer following the Deadline Monotonic scheme. Each task has a period, a deadline, memory requirements and a subset of candidate computers in which to be allocated, and some of them that cannot be allocated in the same computer are specified as another subset.

In [Dav+07], GP is used to optimize the periods of tasks and messages. In this case, they are already allocated and the priorities have also been previously assigned, so the objective is to minimize the sum of the worst-case execution times.

In [Zhe+07b], MILP is used to allocate tasks in computers, package signals into messages and assign fixed priorities to the tasks and messages in the distributed realtime systems based on CAN networks. This model considers e2e flows composed of tasks that exchange messages and which have deadlines and periods. The objective is to minimize the worst-case response time of the flows while their deadlines are met. Given that on industrial scale the techniques based on MILP are computationally very costly, the problem is divided into two sub-problems that can be solved separately.

Strictly periodic applications can have much longer response times than those activated by events. Therefore, when a deadline of a task or message is not met, it is possible to apply the ET paradigm so its response time decreases and the deadline can be met. In [Zhe+07a], MILP is used to adjust the activation model with the objective of meeting all the temporal restrictions.

In [Hla+08], CSP is used to allocate and schedule tasks in distributed real-time systems composed of homogeneous computers connected through a CAN network. It is assumed that the tasks and messages have deadlines equal to their periods, and that the priorities are assigned in a phase previous to this process. All the tasks have a subset of candidate computers in which they can be allocated, and they can be required to be allocated in the same or a different computer than other tasks. The objective is to obtain an allocation enabling all the deadlines to be met. To do so, two methods are proposed. The first is based on backtracking and it simultaneously

tackles the problems of allocation and scheduling. The second method is to divide these two sub-problems according to a Benders scheme [Sch98] to tackle them separately.

In [Zhu+09], MILP is used to allocate tasks in processors and signals in messages, as well as to assign fixed priorities to tasks and messages, in distributed real-time systems that assume a model based on e2e flows with fixed deadlines and harmonic periods. The objective is to maximize the extensibility: to prolong as much as possible the worst-case execution time without affecting the fulfillment of the temporal restrictions of the tasks while ensuring that all the deadlines are met. The method proposed assumes an initial assignment of priorities for messages and tasks.

In [ABH10], an algorithm based on MILP is proposed, used to allocate and schedule strictly periodic temporal partitions in distributed architectures based on Integrated Modular Avionics [Joh99]. A series of restrictions is defined mathematically (avoiding temporal overlapping, shared access to resources, communication costs, etc.) and solved through a commercial tool, obtaining nearly optimal results.

In [Zhu+12], MILP is used to allocate tasks on distributed architectures with heterogeneous processors interconnected through CAN networks, which are at the same time segmented through gateways. Priorities are also assigned to the tasks and messages, with the aim of meeting hard real-time requirements and minimizing the latency of the e2e flows.

In [CO14], CSP is proposed to allocate and schedule tasks and messages in distributed real-time systems. After building the logic restrictions that define the system, it uses two algorithms based on SMT. The first, called One-shot, tackles the scheduling of all types of tasks defined in the system model. The second method does not consider the scheduling of the independent tasks at a first approach, in such a way that no difficulty is added to the formulation of the SMT algorithm. After carrying out the scheduling based on the algorithm proposed in [COE14], the independent tasks are added. This work considers the scheduling of the processor elements and of the communications network, and in the following work [Cra+16], the schedulability analysis is applied to TSN networks.

In [Zha+14], MIP is used to schedule distributed real-time systems, at both computer and network level. It is assumed that the tasks are allocated in the computers with a single processor. The objective, represented through the objective function, is to minimize the response times of the applications that are executed while meeting all the deadlines of the tasks. The temporal restrictions are represented through equalities and inequalities, for which the maximum tolerable response time can be established.

In [Alt+12] and [Alt+14], an algorithm is presented based on ILP formulations that are used for allocating and scheduling of periodic tasks in distributed real-time systems. The architecture is based on multiple subsystems that are communicated through a global bus. The tasks are scheduled following the Deadline Monotonic scheme and they form e2e flows along with the messages they use to communicate.

In [Min+18], three approaches are proposed to schedule tasks and messages with jitter and precedence relations in real-time systems. It is assumed that the allocation of the tasks in the computers has already been done. First, an approach based on SMT is formulated, in which the solutions space is defined through five sets of restrictions. Later, an ILP model is described in a similar way, with the difference of the linear restrictions this method needs. Although the solutions obtained in these two approaches are optimal, a third heuristic based on three levels is proposed, which although not optimal, does obtain acceptable solutions in a reasonable time and with a much greater scalability of the problem.

In [Bli+18], an algorithm based on MILP is developed to schedule periodic tasks in distributed real-time systems based on IMA architecture. Through mathematical formulation of the real-time restrictions and requirements of the system, a cyclic executive is constructed whose period is the minimum common multiple of the periods of the tasks. It is assumed that the tasks have already been allocated. It uses partitions in the following way: the nodes forming this architecture implement different modules to provide the spatial partitioning, and through the cyclic executive resulting from the scheduling, temporal isolation is obtained. Within each temporal partition, the tasks are scheduled according to the RMS scheme.

Finally, [Gua+20] proposes an ILP formulation for scheduling real-time tasks in uniprocessor systems. The authors state that this approach can be applied to hierarchical schedulers, although they do not address distributed architectures.

As shown in Table 2.4, this method is one of the most widely used, but in general, several problems are not tackled at the same time, maybe due to the complexity of their mathematical formulation. When there is no specific minimization objective, these mathematical formulations are used to obtain a schedulable solution.

| Algorithm   | Work      | Add        | ressed Proble | ems        | Mi        | Restri              | ictions  |            |        |

|-------------|-----------|------------|---------------|------------|-----------|---------------------|----------|------------|--------|

| Aigoritiini | WOIK      | Allocation | Scheduling    | Partitions | Computers | Utilization         | Timing   | D/T        | Memory |

| CSP         | [SK01]    | Yes        | Cyclic        |            |           | Memory              | Response |            | Yes    |

| Cor         | [EJ01]    | Yes        | Cyclic        |            |           | Network / Processor | Response | D = T      |        |

| SAT         | [Hla+08]  | Yes        | Priorities    |            |           |                     |          | D = T      |        |

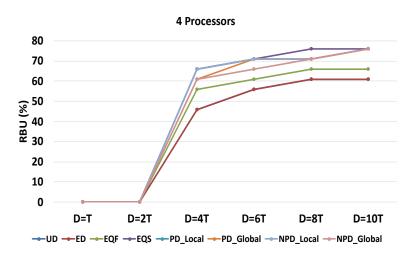

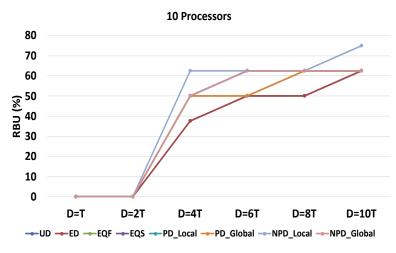

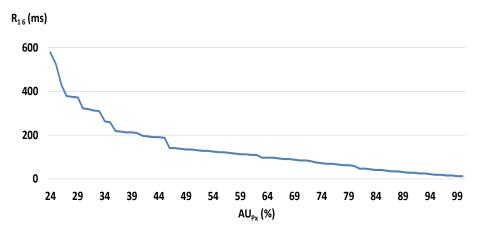

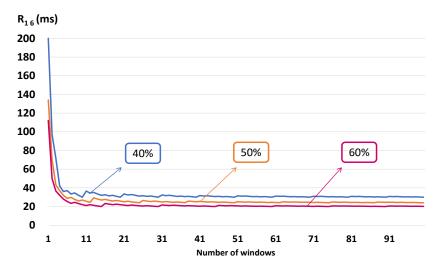

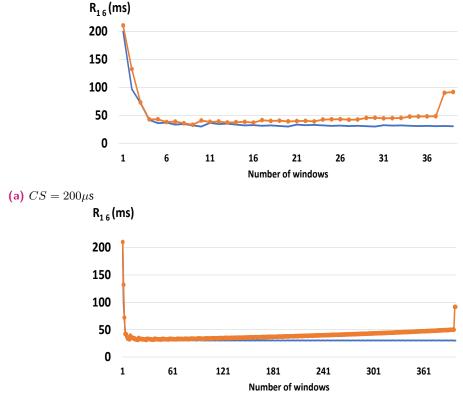

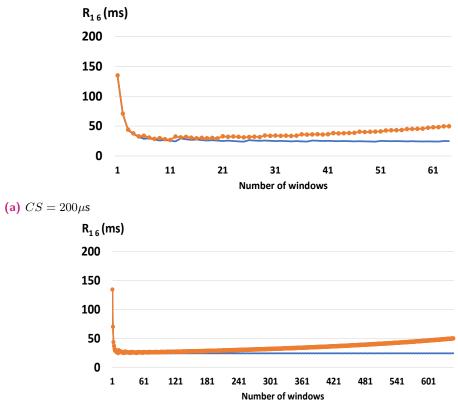

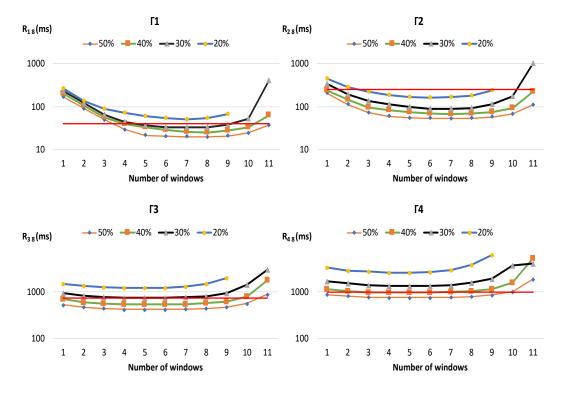

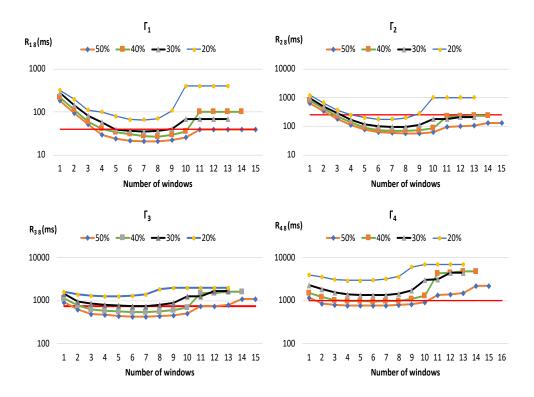

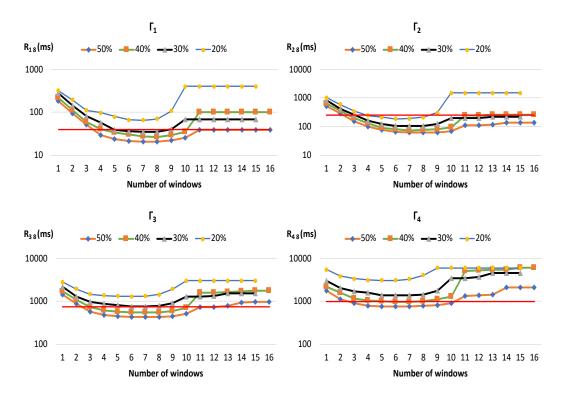

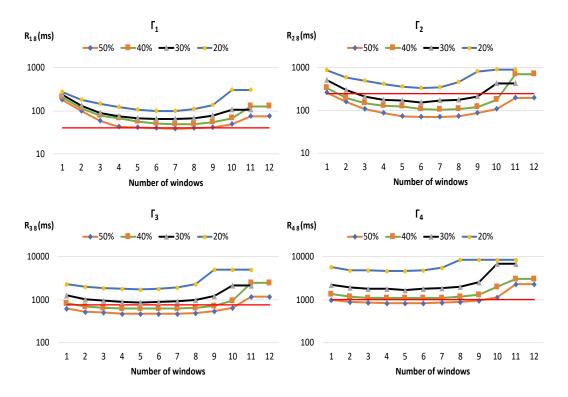

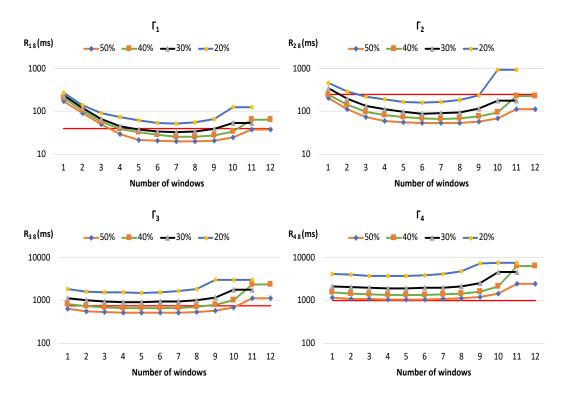

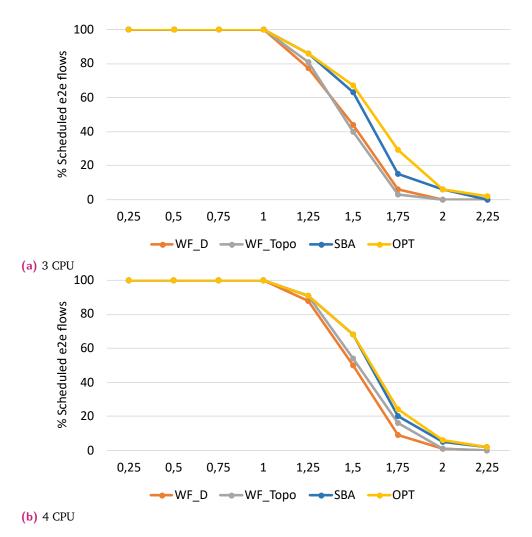

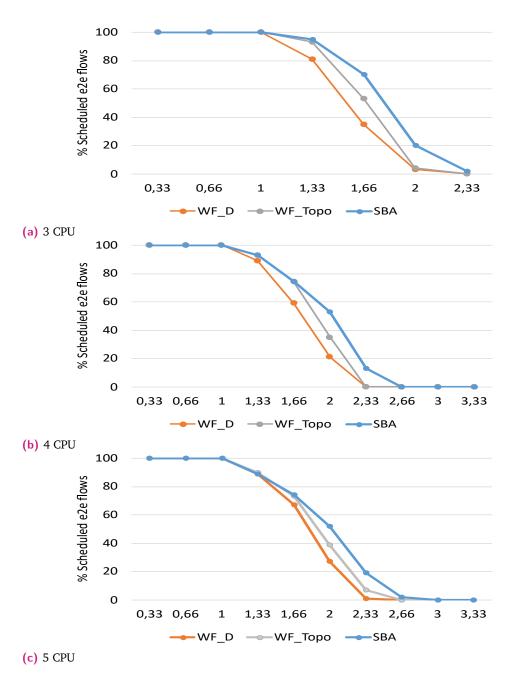

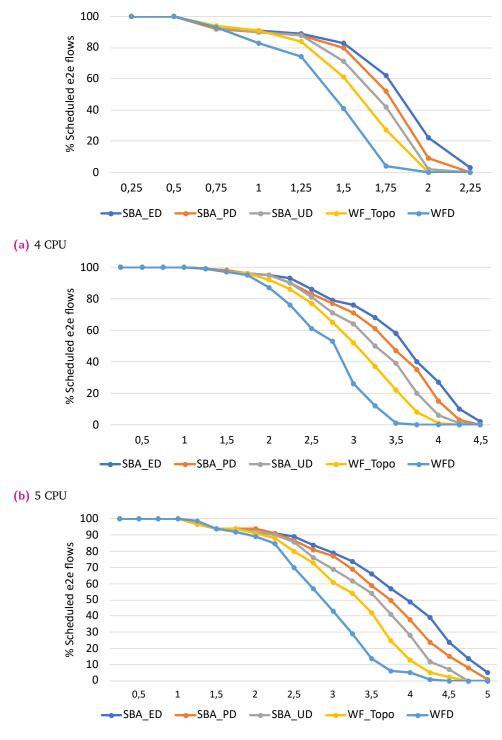

| SAI         | [MH06]    | Yes        | Priorities    |            |           |                     |          |            |        |