Manuscript accepted for publication in the IEEE Transactions on Electromagnetic Compatibility (TEMC-122-2021 final) This is the author's version of an article that has been published in this journal. Changes were made to this version by the publisher prior to publication. The final version is available at http://dx.doi.org/10.1109/TEMC.2021.3122348

# Fast Jitter Tolerance Testing for High-Speed Serial Links in Post-Silicon Validation

Andrés Viveros-Wacher, Ricardo Baca-Baylón, Francisco E. Rangel-Patiño, Johana L. Silva-Cortés, Edgar A. Vega-Ochoa, and José E. Rayas-Sánchez

Abstract— Post-silicon electrical validation of high-speed input/output (HSIO) links is a critical process for product qualification schedules of high-performance computer platforms under current aggressive time-to-market (TTM) commitments. Improvements in signaling methods, circuits, and process technologies have allowed HSIO data rates to scale well beyond 10 Gb/s. Noise and EM effects can create multiple signal integrity problems, which are aggravated by continuously faster bus technologies. The goal of post-silicon validation for HSIO links is to ensure design robustness of both receiver (Rx) and transmitter (Tx) circuitry in real system environments. One of the most common ways to evaluate the performance of a HSIO link is to characterize the Rx jitter tolerance (JTOL) performance by measuring the bit error rate (BER) of the link under worst stressing conditions. However, JTOL testing is extremely timeconsuming when executed at specification BER considering manufacturing process, voltage, and temperature (PVT) test coverage. In order to significantly accelerate this process, we propose a novel approach for JTOL testing based on an efficient direct search optimization methodology. Our approach exploits the fast execution of a modified golden section search with a high BER, while overcoming the lack of correlation between different BERs by performing a downward linear search at the actual target BER until no errors are found. Our proposed methodology is validated in a realistic industrial server post-silicon validation platform for three different computer HSIO links: SATA, USB3, and PCIe3.

*Index Terms*— bit error rate, golden section, HSIO link, ISI, jitter, jitter tolerance, PCIe, post-silicon validation, SATA, USB.

#### I. I. INTRODUCTION

Noise and undesired electromagnetic (EM) effects, such as jitter, inter-symbol interference (ISI), attenuation, reflection, crosstalk, and others, can create multiple signal integrity problems for high-speed input/output (HSIO) circuits in computer platforms. This is aggravated by the fact that channel speeds keep increasing from one generation bus technology to the next one. In general, the higher the signaling frequency, the more vulnerable the interconnect becomes to undesired EM effects. This is of particular concern for HSIO interfaces, such as Peripheral Component Interconnect Express (PCIe), Serial Advanced Technology Attachment (SATA), Universal Serial Bus (USB), and Ethernet interfaces.

1

Post-silicon electrical validation implies testing hundreds of silicon samples in realistic system application conditions, with the purpose of checking design robustness by measurements on both receiver (Rx) and transmitter (Tx) circuitry of the HSIO links. These measurements must comply with industrial standards, ensuring correct operation under worst case stressing conditions [1]. The combined effects of product complexity, performance requirements, and time-to-market (TTM) add tremendous pressure on industrial post-silicon validation. These challenges motivate the quest for novel strategies to make reliable validation faster and cheaper [1].

One of the most common ways to assess the performance of a HSIO link is by measuring the bit error rate (BER) of the link [2]. BER measurement is typically used to characterize the Rx jitter tolerance (JTOL) to determine compliance with industry standard specifications, such as XAUI [3], PCIe [4], USB [5], and SATA [6]. The goal of JTOL testing is to verify that the Rx under test is capable to operate at an acceptable BER under worst case signaling conditions. JTOL is usually measured with a BER tester (BERT) instrument by sweeping the injected periodic jitter ( $J_P$ ) amplitude across a range of frequencies until bit errors are detected. The test is passed when the measured error-free  $J_P$  amplitude is above the threshold defined by the protocol specification for each frequency point. A typical JTOL test can take several hours.

Fast and reliable JTOL testing methods are of great interest to industry. Most of the alternative methods use extrapolation to save testing time. However, extrapolation is only as good as the model used to describe the behavior of the device under test (DUT), which has prevented the wide adoption of these methods for compliance testing [7]. The extrapolated results may be useful in jitter problem solving, but uncertainty compared to a direct measurement persists. Therefore, there is currently a demand from the test instrumentation user community for faster measurement methods.

In this paper, we present a novel approach to dramatically accelerate JTOL testing based on a modified golden section direct search optimization algorithm. As demonstrated in Section V, our approach to accelerate JTOL testing follows a completely different strategy to those reported in the literature. Our proposed method exploits the fast convergence of the golden section algorithm, modified for a binary objective function, and applied with a high BER, with no need of gradients estimation. The lack of correlation between different BERs is solved by performing a downward linear search at the

A. Viveros-Wacher, R. Baca-Baylón, F. E. Rangel-Patiño J. L. Silva-Cortes, and E. A. Vega-Ochoa are with Intel Corp., Zapopan, 45109 Mexico (e-mail: andres.viveros.wacher@intel.com). J. E. Rayas-Sánchez and A. Viveros-Wacher are with the Department of Electronics, Systems, and Informatics, ITESO – The Jesuit University of Guadalajara, Tlaquepaque, Jalisco, 45604 Mexico. A. Viveros-Wacher was funded through a CONACYT scholarship (*Consejo Nacional de Ciencia y Tecnología*, Mexican Government).

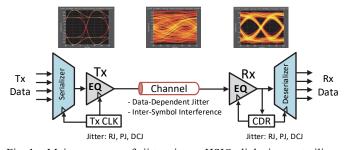

Fig. 1. Main sources of jitter in a HSIO link in post-silicon computer platforms' validation. Equalization (EQ) coefficients are tuned to cancel out the undesired effects.

actual target BER until no errors are seen, requiring just a few additional evaluations. Our proposed method is validated by applying it to three different computer HSIO links in a realistic industrial server platform: SATA, USB3, and PCIe3; demonstrating that JTOL testing can be extremely accelerated with respect to the current industrial practice.

This paper significantly expands our work in [8] by incorporating the following new aspects: a) several additional jitter measurement techniques are provided to complete the current industrial practice for which our proposed methodology is applicable; b) an updated and more complete review on existing approaches to speed-up JTOL testing is presented; c) more details are provided regarding the proposed modified golden section search strategy to deal with discrete (binary) objective functions; and d) further validation of our JTOL testing approach is achieved by two additional and more complex HSIO computer interfaces, USB and PCIe, whose bandwidth limitations, data rates, and more complex calibration procedures, render harder test cases to our methodology, confirming the robustness of the proposed methodology.

The rest of our paper is organized as follows. Section II provides a brief description of post-silicon validation. Section III describes JTOL testing. Section IV reviews existing techniques to speed-up JTOL testing. The proposed optimization technique to accelerate JTOL testing is presented in Section V. Finally, Sections VI and VII present the results obtained and our conclusions, respectively.

## **II. POST-SILICON ELECTRICAL VALIDATION**

In the context of modern computer platforms testing, silicon validation can be generally classified as pre-silicon and postsilicon. During the pre-silicon stage, testing is implemented in a virtual environment with complex simulation models, emulation and formal verification tools. Once the first silicon is available at the laboratory, post-silicon validation is done in a system environment looking for bugs that cannot be found in pre-silicon validation. In that stage, validation is performed at several levels, including functional validation (FV), bench design validation (BDV), and electrical validation (EV), among others. All of these validation levels are executed in parallel, with the objective of qualifying a product over different operation conditions, process corners, and usage models [9].

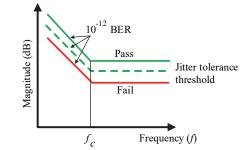

Fig. 2. Rx jitter tolerance threshold for testing [16].

EV focuses on testing electrical parameters and EM phenomena, as well as performance of microprocessor circuitry in a system environment. This includes validation of HSIO links, phase-locked loops (PLLs), analog/mixed-signal circuits, clock network, power delivery network, and physical layer (PHY) equalization settings tuning. The goal is to statistically validate the electrical/EM behavior in a real system environment across different process corners and operating conditions. Such a validation leads to a reasonable product release qualification (PRQ) decision.

A large portion of EV is devoted to the validation of HSIO links. Given that the data rate of HSIO interfaces is in the order of several gigabits per second (Gbps), the specifications associated to those interfaces regarding the timing budget is very stringent. This timing budget is reflected in several jitter specifications. On the Tx side, it is specified by the amount of timing deviation the Tx can generate to consume the total jitter budget. Whereas on the Rx side, it specifies how much timing deviation the Rx can tolerate before a false detection occurs.

# III. JITTER TOLERANCE TESTING IN POST-SILICON VALIDATION

Post-silicon electrical validation looks for Rx jitter tolerance performance in order to determine compliance with the industry standard specifications for all HSIO links, which implies using industry standard instruments and following standard protocols for jitter testing.

In a typical PHY serializer/de-serializer (SerDes), the clock data recovery (CDR) circuitry generates from the received serial data a clock to re-time the received data, which are restored to parallel format by the de-serializer. This SerDes mechanism needs encoding and decoding logic to manipulate the transmitted data transition density to ensure that the CDR works correctly. The CDR guarantees that the clock and data are in phase when the jitter frequency is in the bandwidth of the CDR. However, if there is high frequency jitter in the data stream, the CDR may not track the data, yielding bit errors. Limiting jitter to meet typical BER targets is critical when designing a robust Rx architecture [10], [11].

Typical jitter sources in HSIO links that contribute to the overall accumulated jitter at the Rx are illustrated in Fig. 1. Some level of jitter is already induced by the non-ideal clock synthesizer inside the Tx. Depending on the channel quality, ISI as well as reflections and crosstalk may degrade the signal

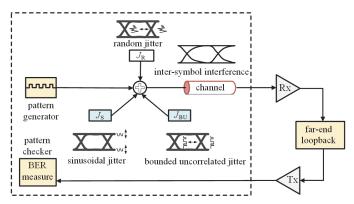

Fig. 3. A generic test setup for Rx jitter tolerance (JTOL) testing.

integrity through the transmission media. At the Rx side, a non-ideal equalizer and the PLL inherent phase noise of the CDR will additionally induce their own timing jitter [12]-[15].

JTOL testing consists of verifying that the measured Rx clock-recovery tolerance across frequencies is above the target threshold. If the measured JTOL curve is above the threshold curve, it indicates a passing result, thus the Rx can tolerate more jitter. On the other hand, if the measured curve is below the threshold curve, it indicates a failing result. Both scenarios are depicted in Fig. 2 [16].

HSIO links specifications require the measurement of various jitter components, which can be performed using different techniques, such as time interval error (TIE) measurement, jitter histograms, JTOL, and BER bathtub, among others. To perform a JTOL test, each protocol specification defines a calibration procedure prior to the JTOL execution. This procedure defines the specific random jitter ( $J_R$ ), bounded uncorrelated jitter ( $J_{BU}$ ), duty-cycle distortion (DCD), and ISI values injected to the test pattern, which remain constant throughout the JTOL test, while  $J_P$  is varied in both amplitude and frequency.

In the traditional way to run JTOL testing, at each frequency point, the value of  $J_P$  is initialized at a sufficiently low starting point to guarantee a PASS result from the BER tester (BERT). Then,  $J_P$  is increased by a certain amount, typically equivalent to the minimum value allowed by the BERT equipment for best accuracy. Then, a test is performed at the compliance BER. This is iteratively done until the BER tester yields a FAIL. The result reported at each frequency point is the last  $J_P$  value that yields a PASS.

Figure 3 shows a generic JTOL testing setup. It requires an instrument capable of generating a protocol-compliant test pattern and an error detector to measure the BER. Jitter measured with a BERT is the standard against which other methods are judged. Instead of quantifying the jitter of a system's own signals, a BERT provides a bit stream and compares the system's output to the known input.

The relationship between test time and BER confidence level is studied in [17] and [18], finding that the quantity N of data bits needed to guarantee a target BER is

$$N = \frac{1}{B} \left[ -\ln(1-a) + \ln\left(\sum_{k=0}^{E} \frac{(N \times B)^{k}}{k!}\right) \right]$$

(1)

where *B* is the desired BER level, *a* specifies the statistical probability or confidence level of a BER value being less than *B*, and *E* is the number of detected errors. When no bit errors occur (E = 0), then the second term of (1) is zero and the solution is simplified. Assuming a confidence level a = 95%, it is necessary to transmit  $N = 3 \times 10^{12}$  bits without errors in order to meet a BER =  $10^{-12}$ , as typically defined in HSIO standards with no forward error correction.

For instance, in SATA3 the time per testing frequency point per jitter amplitude step is N/speed =  $(3 \times 10^{12} \text{b})/(6 \times 10^{9} \text{bps})$  = 8.3 minutes. In order to build a chart as that one in Fig. 2, several frequency points specified in the corresponding protocol standard must be tested. In the case of SATA, 5 frequency points are needed. Following the conventional JTOL testing procedure, each frequency point is tested by increasing the jitter amplitude until a BER failure is found. Assuming a margin of 100 mUI per frequency point from the starting point until a BER test fails, and a test equipment configured to change the jitter amplitude in steps of 3 mUI, it would take 33 measurements per frequency point. In addition, each test is repeated 3 times in order to capture and analyze the measurement noise, yielding a test execution of around 68.5 hours. Such a long time for a single JTOL test is prohibitive in PHY tuning and high-volume production testing, especially when considering that many design parameters and DUT settings affect JTOL performance.

# IV. EXISTING ACCELERATION TECHNIQUES FOR JITTER TOLERANCE TESTING

Some alternatives for JTOL testing time reduction have been reported. In [19], a higher BER mask is presented as a means to approximate a pass/fail criterion at a BER of  $10^{-12}$ by slightly increasing the injected noise profile and executing the test at a BER of  $10^{-10}$ . Another common approach is to characterize the tolerated amplitude degradation between  $10^{-10}$ and  $10^{-12}$  tests. However, for both cases it is still needed to run a full test at the target BER to guarantee that the Rx passes the compliance test, mainly due to the lack of correlation between the  $10^{-10}$  and  $10^{-12}$  results.

An extrapolation algorithm for JTOL is proposed in [20] to predict JTOL at low BER based on high BER region data, with the objective to reduce the JTOL testing time. However, this algorithm failed when we applied it in a post-silicon validation compliance environment, as opposed to using it in high volume manufacturing testers. Under the high variation of measurements typically seen in system compliance tests, the linear regression of the Q factor [21] has a poor fit, which translates to poorly predicted values of  $J_P$  at low BER that do not correlate with real measurements. Moreover, the Q-factor regression is more suitable to extrapolate across  $J_R$  values which behave linearly in the Q scale, however,  $J_P$  does not have such a linear behavior, making extrapolation to typically fail in a system compliance environment.

Another set of innovative approaches have been proposed to accelerate jitter testing by using low-cost equipment on HSIO links. In [22], authors propose an algorithm for jitter testing by employing a method that requires only a single test with a high frequency input sine wave, and then a fast Fourier transform (FFT) is performed only once. Another solution for at-speed jitter performance testing on automated test equipment (ATE) is proposed in [23], focusing on jitter compliance test of a DUT Tx port but not considering full jitter tolerance test. In [24] a new data dependent jitter estimation approach is proposed by using stochastic analysis, where the authors create surrogate models of the HSIO link for jitter calculation by using polynomial chaos theory and linear regression. Two low-cost jitter generators for jitter tolerance testing are proposed in [25]; while these circuits work on bench, they cannot be used for compliance with the industry standard specifications.

While many solutions to reduce the testing cost and time of JTOL measurements have been investigated, most of them focused on cost-effective ways of generating data streams with the desired jitter, and then trying to eliminate the need for an external equipment [26]-[29]. However, these solutions imply additional design efforts (e.g. on-die instruments, CDR with adaptive JTOL circuits, etc.) beyond just designing the CDR, and then additional costs. Therefore, none of these methods has been adopted so far for JTOL industrial testing.

#### V. PROPOSED FAST JTOL TESTING APPROACH

Based on our description in Section III, a JTOL response  $R_J$  can be defined as

$$R_{\rm J} = u \big( J_{\rm P}, f \big) \tag{2}$$

where  $J_P$  is the periodic jitter amplitude injected by the BERT, and f is the frequency of the periodic jitter.

The evaluation of u in (2) implies sending a certain number of bits from the BERT, receiving the data stream at the Rx of the DUT, looping back the data to the Tx of the DUT, and receiving it once again at the BERT to check for bit errors. The equipment then computes the BER and returns a PASS if the number of errors is below the target BER, or a FAIL if there are more errors that those allowed to comply with the target BER. Therefore, u is a discrete function with continuous arguments; moreover,  $R_J$  is binary, since it can only have a PASS or a FAIL value. Given that there is usually a well-defined frontier between  $J_P$  values that yield a PASS and those that yield a FAIL, u can be treated as a unimodal function. Additionally, for a fixed value of f, the problem of finding the largest value of  $J_P$  that yields a PASS becomes a unidimensional optimization problem.

From the above perspective, we propose an optimization algorithm to accelerate JTOL testing time divided in two main stages: 1) execution of a direct search method based on a modified golden section strategy [30] at a high BER, typically  $10^{-11}$ , and 2) a downwards linear search at the compliance BER, i.e.  $10^{-12}$ , starting from the value obtained from the previous step. This technique clearly takes advantage of the fast execution of the golden section search strategy for a unimodal function in the interval of interest, as applied with a high BER, and overcomes the lack of correlation between different BERs by performing a downward linear search at the

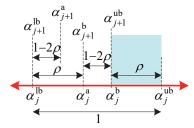

Fig. 4. Nature of the searching strategy of the golden section algorithm at the *j*-th iteration.

actual target BER until no errors are seen.

## A. Modified Golden Section Search

The golden section algorithm is one of the most effective and widely used unidimensional direct search optimization methods. It aims at finding in a given searching interval a minimizer of a scalar unidimensional objective function  $u(\alpha)$ :  $\Re \rightarrow \Re$ . If  $u(\alpha)$  is a unimodal function in the selected searching interval, the golden section method ensures finding the global minimum  $\alpha^*$  in the interval of interest.

The search strategy used by the golden section method is illustrated in Fig. 4. Assuming a unitary searching interval defined by lower  $\alpha_j^{lb}$  and upper  $\alpha_j^{ub}$  bounds at the *j*-th iteration, the two interior points  $\alpha_j^a$  and  $\alpha_j^b$  are selected at a distance  $\rho$  from the extremes. The interval reduction is then accomplished by comparing the function values at the interior points. If  $u(\alpha_j^a) < u(\alpha_j^b)$ , the minimum lies in the subinterval  $[\alpha_j^{lb}, \alpha_j^b]$ , as illustrated in Fig. 4, eliminating the shaded subinterval. However, if  $u(\alpha_j^a) > u(\alpha_j^b)$  then the minimum lies in the subinterval  $[\alpha_j^a, \alpha_j^{ub}]$ . At the next iteration, *j*+1, one of the prior interior points is re-used, and only one new interior point is generated at a distance  $\rho$  from the corresponding extreme. The relative reduction  $\rho$  at all iterations is kept fixed and given by the so-called golden ratio  $\rho = (3-\sqrt{5})/2$ .

The pseudo-code of our modified golden section direct search algorithm as applied to JTOL testing with a high BER is shown in Fig. 5. The initial searching interval is  $[\alpha^{lb}, \alpha^{ub}]$ . The same strategy for interval reduction is employed as described above, however, the objective function u is treated as a discrete function, for which we adjust the corresponding decision criteria to determine the next searching interval at each iteration. It is also worth noting that our algorithm modifies the manner in which an interval is eliminated, so that the final optimal point is the PASS/FAIL boundary of the test, instead of a maximum or minimum function value in the traditional algorithm. In other words, the modifications done to the algorithm allow to find the maximum  $J_P$  tolerated by the Rx before failing a BER test. The proposed algorithm is iterated, as depicted in Fig. 7, until the following stopping criterion is met:

$$\alpha_{i}^{\rm ub} - \alpha_{i}^{\rm lb} \le \varepsilon_{\rm step} \tag{3}$$

where  $\varepsilon_{\text{step}}$  is defined as either the minimum  $J_{\text{P}}$  increment allowed by the BERT or the known repeat measurement variability.

In JTOL testing, the evaluation of the objective function u in (2) returns a PASS or FAIL response from the BER test at a certain  $J_P$  and f. Our implementation of the golden section

begin

$$j = 0; \ \alpha_j^{lb} = \alpha^{lb}; \ \alpha_j^{ub} = \alpha^{ub}; \ \rho = (3 - \sqrt{5})/2$$

$$\alpha_j^a = \alpha_j^{lb} + \rho(\alpha_j^{ub} - \alpha_j^{lb}); \ \alpha_j^b = \alpha_j^{lb} + (1 - \rho)(\alpha_j^{ub} - \alpha_j^{lb})$$

$$u_j^a = u(\alpha_j^a); \ u_j^b = u(\alpha_j^b)$$

repeat until StoppingCriteria

if  $u_j^a = PASS \land u_j^b = FAIL$

$$\alpha_{j+1}^{lb} = \alpha_j^{lb}; \ \alpha_{j+1}^{ub} = \alpha_j^b$$

$$\alpha_{j+1}^b = \alpha_j^a; \ \alpha_{j+1}^a = \alpha_{j+1}^{lb} + \rho(\alpha_{j+1}^{ub} - \alpha_{j+1}^{lb})$$

$$u_{j+1}^a = u(\alpha_{j+1}^a); \ u_{j+1}^b = u_j^a$$

else if  $u_j^a = PASS \land u_j^b = PASS$

$$\alpha_{j+1}^{lb} = \alpha_j^a; \ \alpha_{j+1}^{ub} = \alpha_j^{ub}$$

$$\alpha_{j+1}^a = \alpha_j^b; \ \alpha_{j+1}^b = \alpha_j^{lb}$$

$$\alpha_{j+1}^a = u_j^b; \ u_{j+1}^b = u(\alpha_{j+1}^b)$$

end

$$j = j + 1$$

end

$$\alpha^* = (\alpha_j^{lb} + \alpha_j^{ub})/2$$

end

Fig. 5. Pseudo code implementation of the modified golden section algorithm as applied to the binary JTOL objective function.

algorithm differs from the classical one [30] since it is based on a discrete binary function response rather than a continuous one. Consequently, the decision of which search range to discard is based on the feasibility to approach on every iteration the actual boundary between the PASS and FAIL responses, which is our optimal point. The optimal value returned by the algorithm,  $\alpha^*$ , is the average between the upper and lower bounds at the last iteration, as seen in Fig. 7.

# B. Downwards Search

The second stage of the proposed algorithm performs a search starting from  $\alpha^*$  found in the previous stage, but now executing at the compliance BER. The search is performed in a downwards direction, meaning that the  $J_P$  is decremented in linear steps equivalent to  $\varepsilon_{step}$  (or a percentage of  $\varepsilon_{step}$  in accordance to precision used in the traditional method) until no errors are seen, or in other words, until the BER test passes. The range reduction achieved by the golden section search allows to decrease the number of evaluations in the downwards search. Typically, only one to three evaluations are needed at the compliance BER, thus the overall test time is dramatically reduced.

# VI. TEST CASES

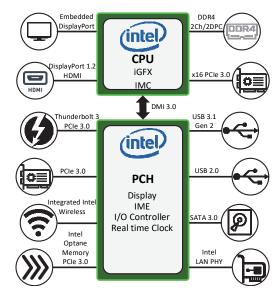

The proposed methodology described in Section VI was tested in three different computer HSIO links: SATA3, USB3, and PCIe3. These HSIO links are part of an Intel platform controller hub (PCH) that works in conjunction with the CPU through the direct media interface (DMI) on a server platform [31], as shown in Fig. 6.

The three HSIO links are tested under a specific set of

5

Fig. 6. Architecture of the system under test, including the platform controller hub (PCH) and CPU, as well as the USB, SATA, and PCIe HSIO links.

impairments and a compliance pattern, which are described by the specifications of each HSIO link. In order to guarantee that the JTOL test is compliant with the stress required by the specifications, a BERT calibration is required.

The starting point of the BERT calibration is the eye height (EH), of which the amplitude is defined in the standards and can be measured with an oscilloscope. After setting the amplitude, the Tx equalization presets including de-emphasis and pre-shoot are calibrated for each HSIO link. Once the calibrated BERT Tx can guarantee the delivery of compliant EH amplitude and presets equalization, the electrical impairments are calibrated and added to the transmitted signal.

The three HSIO links require the use of  $J_R$  and  $J_P$  as part of the impairments and are calibrated accordingly. Furthermore, the transmitted compliance pattern must interact with the discontinuities and losses present in the channel, therefore, the presence of  $J_{DD}$  is granted. High frequency components are attenuated due to channel losses, causing a stressed EH. In the case of PCIe, the EH is additionally stressed by adding the common mode interference (CMI) and the differential mode interference (DMI). The CMI and DMI must be calibrated, as these impairments emulate cross-talk aggressors.

Since the validation is executed in an industrial environment, 3 repetitions of each test are typically executed in order to capture and analyze the measurement noise. Our test time reported for each test case considers the overall duration of the 3 repetitions executed consecutively. For comparison purposes, we set the same initial value of  $J_P$  at each frequency point for both methods (traditional and proposed). A summary of the comparison between the traditional and the proposed methods for the three test cases is shown in Table I.

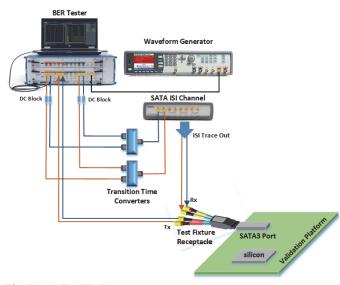

## A. Test Case 1: HSIO SATA3

The JTOL setup for SATA is comprised of a system platform that includes the DUT and a SATA connector, as well as a SATA3 Fixture, a SATA ISI Channel that emulates

Fig. 7. SATA JTOL test setup.

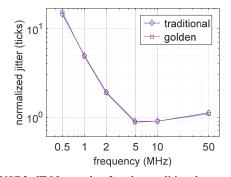

Fig. 8. SATA JTOL testing results for the traditional approach and the proposed golden section algorithm implementation.

the loss of a compliant 1-m cable, two transition time converters that allow to have specification-compliant slew rates, two power dividers which combine the signals from the two BERT channels in order to properly generate the out-ofbound signaling required for the interface initiation, and DC blocking capacitors, as shown in Fig. 7. During the Rx JTOL test, the BERT pattern generator sends a compliance test pattern with added jitter through the compliance channels connected with fixtures to the Rx. Prior to running the test, the port should transition to loopback state. Once in loopback, the data received from the DUT is compared to the data generated and errors are counted by the BERT.

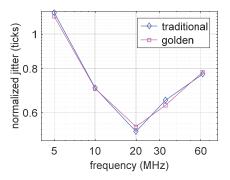

The JTOL execution following our proposal took 5.3 hours to complete 3 repetitions at five different frequency points, as compared to 72.6 hours that the traditional method required. Our proposal needs only 7.3% of the time required by the traditional approach to reach a comparable solution, as confirmed in Fig. 8.

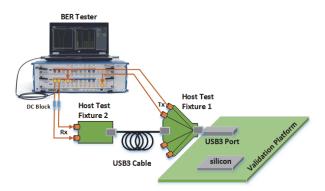

# B. Test Case 2: HSIO USB3

In the test case of USB3, the JTOL setup includes the system platform that contains the DUT and a USB3 connector where USB3 fixtures are inserted, one BERT and direct current (DC) blocking capacitors, as shown in Fig. 9, where we can see that, similarly to SATA3, the connection from the

Fig. 9. USB3 JTOL test setup.

Fig. 10. USB3 JTOL results for the traditional approach and the proposed golden section algorithm implementation.

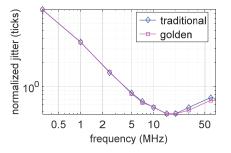

BERT to the Tx path is direct, whereas on the Rx path, the setup includes an actual USB3 cable, calibrated with the standard loss required for compliance tests. Validation time was significantly decreased using our JTOL algorithm as compared with the traditional methods, without sacrificing accuracy. In this test case, the JTOL results for the traditional approach and those with the proposed golden section algorithm were practically the same, as seen in Fig. 10, however, the validation time was reduced by up to 96.1% with respect to the traditional approach. Current methods require around 6 days for a complete execution, while the method proposed in this work can be completed in a few hours.

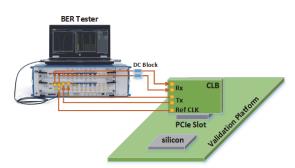

#### C. Test Case 3: HSIO PCIe3

Finally, for the PCIe test case, the JTOL setup consists of the BERT output connected with DC blocking capacitors to the compliance load board (CLB) fixture card, which is connected to the system platform that contains the DUT to reach its Rx, as shown in Fig. 11. Unlike SATA3 and USB3, this PCIe topology works on a common clock manner, where the host sends a clocking signal to the device to synchronize the incoming data. To emulate this in a compliance test, an additional reference clock connection is needed between the BERT and the CLB. To enable a common clock topology, the reference clock is taken from the system platform by the CLB fixture card and goes into the BERT. Additionally, the preset values for pre-cursor and post-cursor are set in the BERT, which sends the PCIe compliance sequence patterns to set loopback mode with the DUT.

With the traditional JTOL method, test lasted 263.6 hours to run 3 repetitions for twelve different frequencies points (about

Fig. 11. PCIe3 JTOL test setup.

Fig. 12. PCIe3 JTOL results for the traditional approach and the proposed golden section algorithm implementation.

TABLE I

TIME REQUIRED FOR JITTER TOLERANCE TESTING

| Interface | Traditional method (hours) | Proposed<br>method (hours) | Time reduction |

|-----------|----------------------------|----------------------------|----------------|

| SATA3     | 72.59                      | 5.29                       | 92.7%          |

| USB3      | 158.48                     | 6.2                        | 96.1%          |

| PCIe3     | 263.6                      | 10.02                      | 96.2%          |

11 days), whereas with the proposed algorithm the same 3 repetitions just took about 10 hours to be completed, reducing test time of the traditional approach by 96.2% and obtaining very similar results, as shown in Fig. 12.

## VII. CONCLUSION

We have described a novel approach to fast and reliable JTOL testing for HSIO links validation. The proposed approach has proven its effectiveness for reducing the jitter tolerance validation time as compared with the traditional method: it has been demonstrated that the JTOL testing time can be reduced by around 95% as compared to the traditional approach, without compromising measurement accuracy. The algorithm was tested on SATA, USB3 Gen1, and PCIe Gen3 CEM & BASE standards, with outstanding results. The proposed methodology can easily be ported to other standards based in the receiver JTOL test, such as XAUI, among others. The incorporation of the proposed algorithm to post silicon validation provides several potential benefits: a) a very significant reduction of TTM by reducing validation time; b) an increase in the product quality by making feasible more unit coverage; c) a more feasible incorporation of multiple frequency points to cover the ambiguity of the standards; and

d) a much lower execution cost of validation across PVT conditions.

#### ACKNOWLEDGMENT

Authors thank Carlos A. Galindo-Meza from Intel Corp., who greatly assisted this research.

# REFERENCES

- [1] F. E. Rangel-Patiño, A. Viveros-Wacher, J. E. Rayas-Sánchez, I. Durón-Rosales, E. A. Vega-Ochoa, N. Hakim, and E. López-Miralrio, "A holistic formulation for system margining and jitter tolerance optimization in industrial post-silicon validation," *IEEE Trans. Emerging Topics Computing*, vol. 8, no. 2, pp. 453-463, Apr.-Jun. 2020.

- [2] D. Hong and K.T. Cheng, "Bit-error rate estimation for bang-bang clock and data recovery circuit," in 26th IEEE VLSI Test Symp., San Diego, CA, Apr. 2008, pp. 17-22.

- [3] 10GEA Org. (2016), XAUI interface [Online]. Available: http://www.10gea.org/whitepapers/xaui-interface/

- [4] PCI SIG Org. (2016), Peripheral Component Interconnect Express 3.1 Specification [Online]. Available: https://pcisig.com/specifications

- [5] USB Org. (2016). Universal Serial Bus Revision 3.1 Specification [Online]. Available: http://www.usb.org/developers/doc

- [6] SATA Org. (2016), Serial Advanced Technology Attachment 3.2 Specification [Online]. Available: http://www.sata-io.org/

- [7] D. Derickson and M. Müller, Digital Communications Test and Measurement: High-Speed Physical Layer Characterization. Boston, MA: Pearson Education, 2007.

- [8] A. Viveros-Wacher, R. Baca-Baylón, F. E. Rangel-Patiño, M. A. Dávalos-Santana, E. A. Vega-Ochoa, and J. E. Rayas-Sánchez, "Jitter tolerance acceleration using the golden section optimization technique," in *IEEE Latin American Symp. Circuits and Systems Dig. (LASCAS 2018)*, Puerto Vallarta, Mexico, Feb. 2018, pp. 1-4.

- [9] C. Gu, "Challenges in post-silicon validation of high-speed I/O links," in 2012 IEEE/ACM Int. Conf. Computer-Aided Design (ICCAD), San Jose, CA, Nov. 2012, pp. 547-550.

- [10] B. Ham, "Methodologies for jitter and signal quality specification," *Tech. Report T11.2 / Project 1316-DT/ Rev 12.2*, INCITS, Washington, DC, Jan. 2004.

- [11] M. Perrott, M. Trott, and C. Sodini, "A modeling approach for Σ-Δ fractional-N frequency synthesizers allowing straightforward noise analysis," *IEEE J. Solid-State Circuits*, vol. 37, no. 8, pp. 1028–1038, Aug. 2002.

- [12] Agilent Tech. (2003), Jitter Analysis Techniques for High Data Rates [Online]. Available: www.agilent.com

- [13] B. Casper and F. O'Mahony, "Clocking analysis, implementation and measurement techniques for high-speed data links - a tutorial," *IEEE Trans. Circuits and Systems I*, vol. 56, no. 1, pp. 17–39, Jan. 2009.

- [14] M. P. Li, Jitter, Noise, and Signal Integrity at High-Speed. Boston, MA: Prentice Hall, 2007.

- [15] M. P. Li, "Jitter Challenges and reduction techniques at 10 Gb/s and beyond," *IEEE Trans. on Advanced Packaging*, vol. 32, no. 2, pp. 290– 297, May 2009.

- [16] L. T. Wang, C. E. Stroud, and N. A. Touba, System-on-Chip Test Architectures: Nanometer Design for Testability. Burlington, MA: Elsevier, 2008.

- [17] Agilent Tech (2005), Total Jitter Measurement at Low Probability Levels, Using Optimized BERT Scan Methods [Online]. Available: www.agilent.com

- [18] Maxim (2004), *Physical Layer Performance: Testing the Bit Error Ratio* (*BER*) [Online]. Available: www.maximintegrated.com

- [19] USB Org. (2016). USB3.0 Electrical Compliance Methodology White Paper [Online]. Available: http://www.usb.org/developers/doc

- [20] Y. Fan and Z. Zilic, "Accelerating jitter tolerance qualification for high speed serial interfaces," in *10th Int Symp on Quality Electronic Design*, San Jose, CA, Mar. 2009, pp. 360-365.

- [21] N. S. Bergano, F. W. Kerfoot, and C. R. Davidsion, "Margin measurements in optical amplifier system," *IEEE Photonics Technology Letters*, vol. 5, no. 3, pp. 304-306, Mar. 1993.

- [22] M. Wu, D. Chen, and J. Duan, "Fast & accurate algorithm for jitter test with a single frequency test signal," in *IEEE Int. Conf. Electro/Information Technology*, Mankato, MN, May 2011, pp. 1-5.

- [23] L. Ming, "Implementation of full jitter performance test in high-speed serial links with ATE," in *IEEE 2011 10th Int. Conf. Electronic Measurement & Instruments*, Chengdu, China, Aug. 2011, pp. 32-37.

- [24] M. A. Dolatsara, H. Yu, J. A. Hejase, W. D. Becker, and M. Swaminathan, "Polynomial chaos modeling for jitter estimation in high-speed links," in *IEEE Int. Test Conf. (ITC)*, Phoenix, AZ, USA, Oct.-Nov. 2018, pp. 1-10.

- [25] Y. Ozawa, T. Arafune, N. Tsukiji, H. Kobayashi, and R. Shiota, "Study of jitter generators for high-speed I/O interface jitter tolerance testing," in 2017 Int. Symp. Intelligent Signal Processing and Communication Systems (ISPACS), Xiamen, Nov. 2017, pp. 468-473.

- [26] Y. Cai, L. Fang, I. Chan, M. Olsen, and K. Richter, "12Gbps SerDes jitter tolerance BIST in production loopback testing with enhanced spread spectrum clock generation circuit," in *IEEE Int. Test Conf. (ITC* 2013), Anaheim, CA, Sep. 2013, pp. 1-8.

- [27] M. Park and J. Kim, "A built-in self-test circuit for jitter tolerance measurement in high-speed wireline receivers," in *Int. Test Conf. (ITC 2014)*, Seattle, WA, Oct. 2014, pp. 1-6.

- [28] T. D. Lyons, "Complete testing of receiver jitter tolerance," in *IEEE Int. Test Conf. (ITC 2010)*, Austin, TX, Nov. 2010, pp. 1-10.

- [29] H. -R. Kim, J. -Y. Lee, J. -S. Lee, D. -S. Kang and J. -H. Chun, "A 6.4– 11 Gb/s wide-range referenceless single-loop CDR with adaptive JTOL," *IEEE Solid-State Circuits Lett.*, vol. 3, pp. 470-473, Sep. 2020.

- [30] E. K. P. Chong and S. H. Zak, An Introduction to Optimization. New York, NY: Wiley-Interscience, 1996.

- [31] F. E. Rangel-Patiño, J. L. Chávez-Hurtado, A. Viveros-Wacher, J. E. Rayas-Sánchez, and N. Hakim, "System margining surrogate-based optimization in post-silicon validation," *IEEE Trans. Microwave Theory Techn.*, vol. 65, no. 9, pp. 3109-3115, Sep. 2017.

Andrés Viveros-Wacher was born in Mexico City, Mexico, in 1986. He received the B.Sc. in electronic engineering from the National Autonomous University of Mexico (UNAM), Mexico City, Mexico in 2010, the M.Sc. degree in microelectronics systems from the University of Bristol, Bristol, U.K. in 2011, and the Ph.D. degree in engineering sciences from ITESO – The Jesuit University of Guadalajara, Mexico, in 2020.

He joined Intel Corp in 2012 as an analog validation engineer, and currently manages a software tools team. His current research interests include optimization methods, machine learning-based surrogate modeling, automation, data analysis, and analog fault modeling and diagnosis methods.

**Ricardo Baca-Baylón** was born in Chihuahua, Chih. Mexico, in 1980. He received the B.Sc. in electronic engineering from the *Instituto Tecnológico de Chihuahua*, Chih. Mexico, in 2003, and the M.Sc. in electrical engineering from the University of Texas at El Paso, Texas, U.S.A., in 2011.

From 2011 to 2020, he was an analog validation engineer at Intel Corp. and since 2020 he is an analog engineer working in pathfinding and research of PCIe technologies.

**Francisco Elias Rangel-Patiño** received the B.Sc. degree in electronics engineering from the Universidad Veracruzana, Mexico, the M.Sc. degree in Electronics and Telecommunications Engineering from the CICESE Research Center, Mexico, the M.Sc. degree in Computer Sciences from the National Technological Institute of Mexico, Mexico, and the Ph.D. degree in engineering sciences from ITESO – The Jesuit University of Guadalajara, Mexico.

He joined Intel Corp. in 2010, where he is currently a Sr. Manager and responsible for the post-silicon electrical validation of high-speed I/O's for

server processors. His research interests include optimization methods, surrogate-based optimization, and neural network applications for post-silicon validation.

Dr. Rangel-Patiño was the recipient of the E. J. McCluskey Best Doctoral Thesis Award by the IEEE Test Technology Technical Council, and recipient of the Mexico National Innovation Award by ADIAT/CONACYT.

Johana L. Silva-Cortés was born in Guadalajara, Mexico, in 1998. She received the B.Sc. degree in biomedical electronics engineering from the Autonomous University of Guadalajara (UAG), in 2019.

She joined Intel Corp as an analog validation intern in 2018 and has been working as an engineer for the same area in high-speed interfaces since 2019. Her

current research interests include automation, data analysis, and optimization methods for high-speed I/O.

**Edgar A. Vega-Ochoa** received the bachelor's degree from the Technical Institute of Guzman City, Mexico, in 1997, and the master's degree from CINVESTAV Research Center, Guadalajara, Mexico, in 2000, both in electrical engineering.

He is an Analog Validation Engineer with Intel Corporation, Zapopan, Mexico, where he began his career as a Pre-Silicon Validation Engineer and spent three years on the validation of SONET/SDH framers and mappers. He then moved to the Electrical

Validation Group, where he has led the validation on multiple high-speed interfaces (parallel and serial) for different projects on client, server, and device market-segments.

José Ernesto Rayas-Sánchez (S'88–M'89–SM'95) received the B.Sc. degree in electronics engineering from ITESO, Guadalajara, Mexico, the M.Sc. degree in electrical engineering from Monterrey Tec, Monterrey, Mexico, and the Ph.D. degree in electrical engineering from McMaster University, Ontario, Canada.

He is *Profesor Numerario* (hons.) with ITESO-The Jesuit University of Guadalajara, where he leads

the Research Group on Computer-Aided Engineering of Circuits and Systems (CAECAS). He is a member of the Mexican National System of Researchers (SNI), Level II. His research focuses on computer-aided and knowledge-based modeling and design optimization of high-frequency circuits.

Dr. Rayas-Sánchez was Chair (2018-2019) and Vice-chair (2016-2017) of the Technical Committee on Computer Aided Design of the IEEE Microwave Theory and Techniques Society (MTT-S). He is member of the Technical Program Reviewers Committee of the IEEE MTT-S International Microwave Symposium (IMS). Since 2013, he is IEEE MTT-S Regional Coordinator for Latin America. He was the General Chair of the First IEEE MTT-S Int. Microwave Workshop Series in Region 9 (IMWS2009-R9) on Signal Integrity and High-Speed Interconnects (Guadalajara, Mexico, Feb. 2009), as well as the General Chair of the First IEEE MTT-S Latin America Microwave Conference (LAMC-2016, Puerto Vallarta, Mexico, Dec. 2016).