Machine Learning for AI-Augmented Design Space Exploration of Computer Systems

Jihye Kwon

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

© 2022

Jihye Kwon

All Rights Reserved

#### Abstract

Machine Learning for AI-Augmented Design Space Exploration of Computer Systems

Jihye Kwon

Advanced and emerging computer systems, ranging from supercomputers to embedded systems, feature high performance, energy efficiency, acceleration, and specialization. Design of such systems involves ever-increasing circuit complexity and architectural diversity. Commercial high-end processors, realized as very-large-scale integration circuits, have integrated exponentially increasing number of transistors on a chip over many decades. Along with the evolution of semiconductor manufacturing technology, another driving force behind the progress of processors has been the development of computer-aided design (CAD) software tools. Logic synthesis and physical design (LSPD) tool-chains allow designers to describe the computer system at the register-transfer level of abstraction and automatically convert the description into an integration circuit layout. The slowdown of technology scaling, on the other hand, has motivated the emergence of dark silicon and heterogeneous architectures with application-specific hardware accelerators. Design of various accelerators is facilitated by high-level synthesis (HLS) tools that translate a behavioral description of a computer system into a structural register-transfer level one. CAD approaches have evolved towards raising the level of design abstraction and providing more options to optimize the architecture.

For each system synthesized via advanced CAD tools, designers explore the design space in search of optimal configurations of the tool options and architectural choices, also called knobs. These knobs affect the execution of CAD algorithms and eventually impact the multi-dimensional quality-of-result (QoR) of the final implementation. During design-space

exploration (DSE), designers leverage their experience and expertise pertaining to determining the relationship between knobs and QoR. To further reduce the number of time and resource consuming CAD runs during DSE, a large number of heuristic and model-based approaches have been proposed. More recently, the rise of machine learning (ML) and artificial intelligence (AI) has prompted the possibility of AI-augmented DSE which exploits ML techniques to predict the knobs-QoR relationship. Yet, existing heuristic and ML-based approaches still require a sufficient number of CAD runs for each system because they do not accumulate and exploit experiential knowledge across the systems as designers would do.

To expand the potential of AI-augmented DSE and push the frontier forward, multiple challenges arise due to the characteristics of CAD flows. 1) Whereas many ML applications utilize data obtained from huge collections of users' input and public databases for a single problem, the QoR-prediction problem for each system suffers from limited availability of data obtained from expensive CAD runs. Especially, an industrial LSPD tool-chain specifies hundreds of separate knobs, resulting in an extreme curse of dimensionality. 2) Different systems exhibit different knobs-QoR relationship. Hence, learning from previously explored systems needs to be preceded by identifying distinct systems and relating them to one another. Often, it is difficult to obtain an efficient representation of a system. 3) Designers often apply different sets of knob configurations to different systems, which makes it harder to learn from previous DSE results. Especially in HLS, the heterogeneity of various systems leads to broad knob heterogeneity across them. To address these challenges and boost the ML performance, I propose to flexibly connect the elements of the many QoR-prediction problems with one another. My thesis is that the exploration of the design space of a computer system can be effectively augmented by artificial intelligence via learning from the experience with the design and optimization of other systems.

For LSPD of industrial high-performance processors, I propose a novel collaborative recommender system approach that learns hidden features from the interactions (CAD runs) of many *users* (systems) and *items* (knob configurations). To cope with the curse of dimensionality, the item features are decomposed into features of item attributes (knobs). The combined model predicts QoR for each user-item pair. For HLS of application-specific accelerators, I present a series of neural network models in the order of evolution towards the proposed mixed-sharing transfer learning model. Transfer learning aims at leveraging knowledge gained from previous problems; however, due to the system and knob heterogeneities, the model needs to distinguish which piece of that knowledge should be transferred. The proposed ML approaches aim to not only use experiential knowledge as designers do but also to ultimately assist designers by providing alternative insights and suggesting optimization possibilities for new systems. As an effort in this direction, I develop an AI-augmented DSE tool that exploits the aforementioned models and generates recommended knob configurations for new target systems. Through this research, I investigate the potential of next-level AI-augmented DSE with the goal of promoting secure collaborative engineering in the CAD community without the need of sharing confidential information and intellectual properties.

## Table of Contents

| Chapter | 1: Introduction                                                                           | 1  |

|---------|-------------------------------------------------------------------------------------------|----|

| 1.1     | Design of Computer Systems                                                                | 1  |

| 1.2     | Design Space Exploration of Computer Systems                                              | 5  |

| 1.3     | AI-Augmented Design Space Exploration of Computer Systems                                 | 7  |

| 1.4     | Machine Learning for AI-Augmented Design Space Exploration of Computer Systems            | 9  |

| 1.5     | Contributions and Outline                                                                 | 11 |

| Chapter | 2: Background                                                                             | 13 |

| 2.1     | Emergence of Integrated Circuits: A Historical Perspective                                | 13 |

| 2.2     | Computer-Aided Design for Modern Computer Systems                                         | 15 |

|         | 2.2.1 High-Level Synthesis                                                                | 16 |

|         | 2.2.2 Logic Synthesis                                                                     | 30 |

|         | 2.2.3 Physical Design                                                                     | 33 |

| Chapter | 3: A Recommender System Approach for Industrial Logic Synthesis and Physical Design Flows | 37 |

| 3.1     | Design of High-Performance Processors                                                     | 37 |

| 3.2     | Industrial LSPD Flows for High-Performance Processors                                     | 41 |

| 3.3     | Opportunities for Machine Learning: LSPD Results Archive                                  | 43 |

| 3.4     | Releva   | nt Machine Learning Approaches: Recommender Systems                | 45 |

|---------|----------|--------------------------------------------------------------------|----|

| 3.5     | -        | sed Approach: Collaborative Recommendation with Tensor Decompo-    | 46 |

|         | 3.5.1    | Offline Learning Module                                            | 47 |

|         | 3.5.2    | Online Recommendation Module                                       | 53 |

| 3.6     | Experi   | imental Results                                                    | 54 |

|         | 3.6.1    | QoR Prediction Model                                               | 54 |

|         | 3.6.2    | LSPD Parameter Recommendations                                     | 56 |

| 3.7     | Conclu   | iding Remarks                                                      | 58 |

| Chapter | · 4: A T | ransfer Learning Approach for High-Level Synthesis                 | 60 |

| 4.1     | Design   | of Hardware Accelerators: the HLS approach                         | 60 |

| 4.2     | Challe   | nges for Design-Space Exploration with HLS                         | 62 |

| 4.3     | Challe   | nges for Transfer Learning with HLS                                | 65 |

| 4.4     | Propos   | sed Approach: Towards Mixed-Sharing Multi-Domain Transfer Learning | 66 |

|         | 4.4.1    | System Model and Problem Description                               | 67 |

|         | 4.4.2    | Single-Task Learning                                               | 68 |

|         | 4.4.3    | Multi-Task Learning                                                | 69 |

|         | 4.4.4    | Cross-Domain Transfer Learning                                     | 72 |

|         | 4.4.5    | Multi-Domain Transfer Learning                                     | 73 |

|         | 4.4.6    | Mixed-Sharing Multi-Domain Transfer Learning                       | 75 |

| 4.5     | Experi   | imental Results                                                    | 78 |

| 4.6     | Concl    | ıding Remarks                                                      | 82 |

| Chapter  | 5: A Survey on Online and Offline Machine Learning for Design Space Exploration | 84  |

|----------|---------------------------------------------------------------------------------|-----|

| 5.1      | Classification categories                                                       | 84  |

| 5.2      | Approaches for High-Level Synthesis                                             | 86  |

| 5.3      | Approaches for Logic Synthesis                                                  | 89  |

| 5.4      | Approaches for Physical Design                                                  | 90  |

| 5.5      | Approaches for Logic Synthesis and Physical Design flows                        | 92  |

| 5.6      | Approaches for FPGA flows                                                       | 93  |

| 5.7      | Concluding Remarks                                                              | 95  |

| Chapter  | 6: Future Work and Concluding Remarks                                           | 96  |

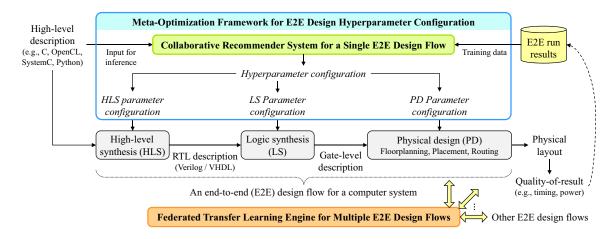

| 6.1      | AI-Augmented DSE with End-to-End CAD                                            | 96  |

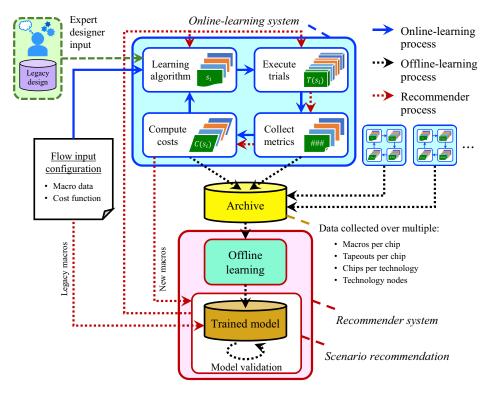

| 6.2      | Interplay of Online and Offline Machine Learning                                | 98  |

| 6.3      | Concluding Remarks                                                              | 99  |

| Referenc | ces                                                                             | 101 |

| T. 1.    |                                                                                 | 110 |

# List of Figures

| 1.1 | A typical computer-aided design (CAD) flow with high-level synthesis (HLS),                            |    |

|-----|--------------------------------------------------------------------------------------------------------|----|

|     | logic synthesis (LS), and physical design (PD). Each CAD tool or tool-chain                            |    |

|     | (a rounded and shaded box) transforms a higher-level specification into a                              |    |

|     | lower-level implementation.                                                                            | :  |

| 1.2 | An advanced CAD process with configurable CAD parameters                                               | 4  |

| 1.3 | Exploration of design spaces with multiple QoR metrics to minimize (or max-                            |    |

|     | $imize).  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  $                    |    |

| 2.1 | A typical design process with an HLS tool that translates a high-level speci-                          |    |

|     | fication into an RTL implementation as guided by the design parameters                                 | 18 |

| 2.2 | A control and data flow graph of the body of process_layer from Listing 2.2.                           | 22 |

| 2.3 | Effect of loop transformations in HLS                                                                  | 25 |

| 2.4 | An example of scheduling of the data flow graph from Fig. 2.2 (b). The dotted                          |    |

|     | lines represent discrete time steps. In this example, each operation is assumed                        |    |

|     | to take a single time step.                                                                            | 27 |

| 2.5 | An example of binding of the data flow graph scheduled in Fig. 2.4. The op-                            |    |

|     | erations are bound to functional units. Some variables are bound to registers,                         |    |

|     | shown as the oranges boxes                                                                             | 29 |

| 2.6 | A typical design process with an LS tool that translates an RTL specification                          |    |

|     | into a gate-level implementation as guided by the design parameters                                    | 31 |

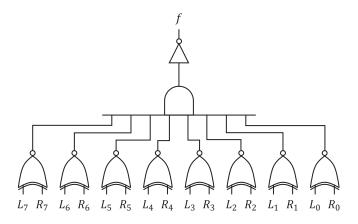

| 2.7 | A logic representation of the negated equality-comparator unit $\overline{\mathtt{COMP}}$ in Fig. 2.5. | 32 |

| 2.8 | An example of an optimized implementation of the logic network in Fig. 2.7.                |    |

|-----|--------------------------------------------------------------------------------------------|----|

|     | The green dotted boxes represent bound cells from the technology library                   | 33 |

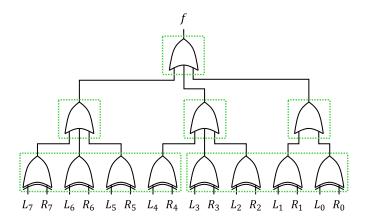

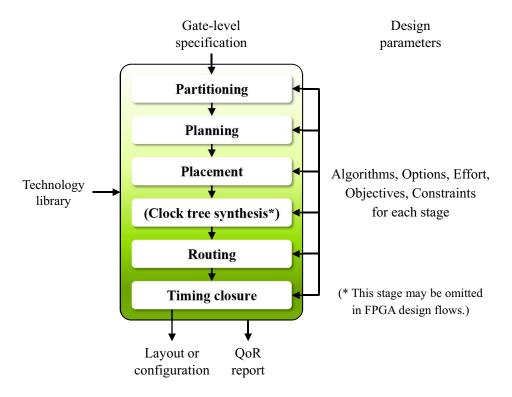

| 2.9 | A typical design process with a PD tool or tool-chain that translates a gate-              |    |

|     | level specification into a physical layout (for integrated circuits) or configu-           |    |

|     | ration bitstream (for FPGAs). Each stage may involve the solution of in-                   |    |

|     | tractable optimization problems and their execution can be guided by the                   |    |

|     | design parameters                                                                          | 34 |

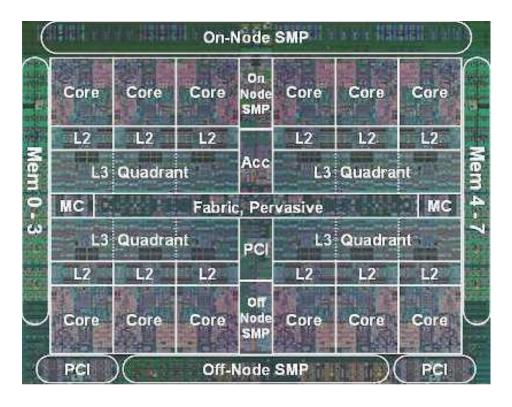

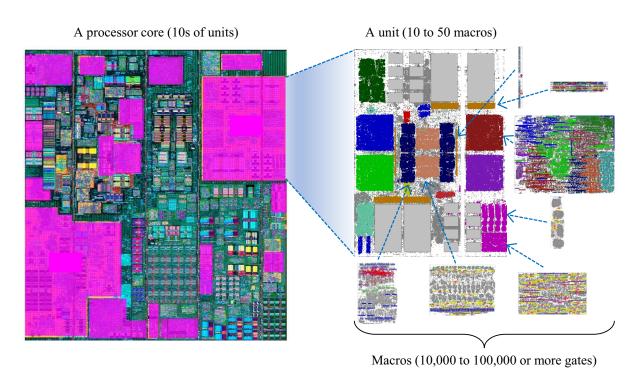

| 3.1 | A hierarchical overview of a high-performance server-class chip, processor core,           |    |

|     | unit, and macros [124]                                                                     | 38 |

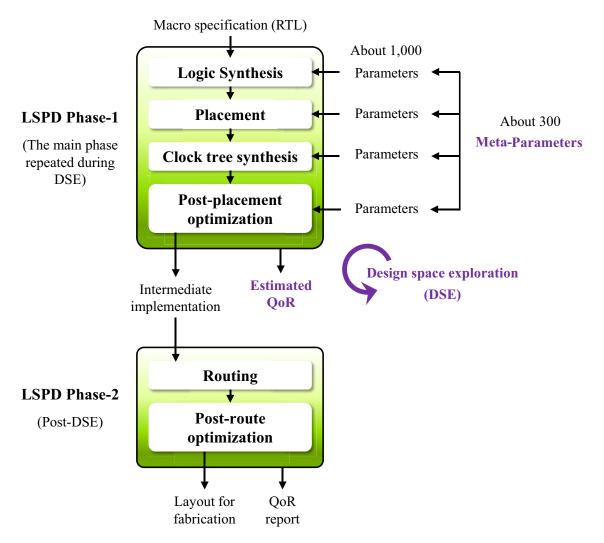

| 3.2 | An LSPD flow deployed in an industrial environment for designing server-class              |    |

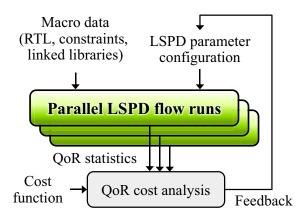

|     | high-performance processors                                                                | 42 |

| 3.3 | DSE with an iterative parameter tuning flow                                                | 43 |

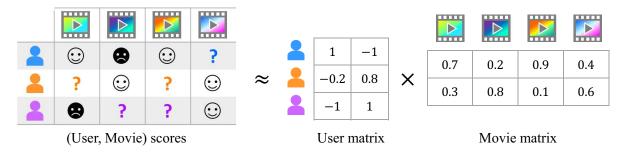

| 3.4 | An exemplary illustration of the LSPD results archive                                      | 44 |

| 3.5 | An example of a collaborative movie recommender system                                     | 45 |

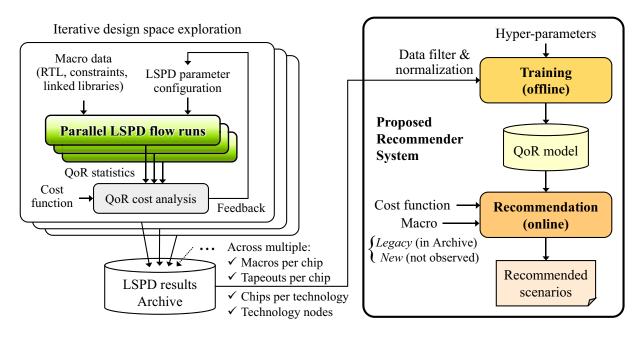

| 3.6 | Overview of the LSPD tuning process, data archive, and proposed recom-                     |    |

|     | mender system                                                                              | 46 |

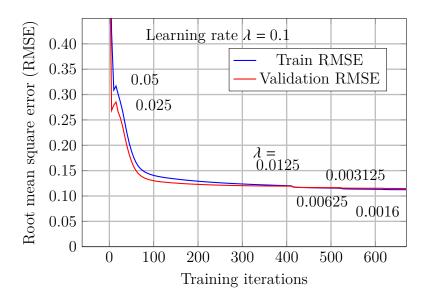

| 3.7 | Train and validation error of the QoR prediction model                                     | 55 |

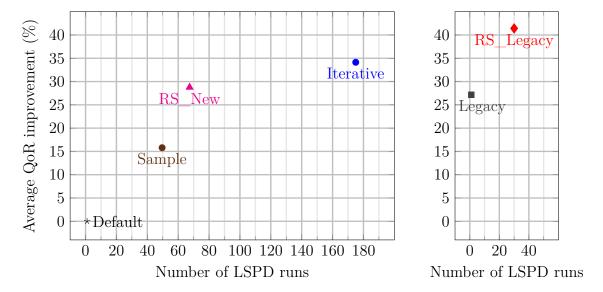

| 3.8 | The QoR improvement and the number of LSPD runs by the six methods,                        |    |

|     | averaged over the five macros in Table 3.2. The macros are considered as new               |    |

|     | macros for Default, Sample, Iterative, and RS_New methods (left), and as                   |    |

|     | legacy macros for Legacy and RS_Legacy methods (right)                                     | 58 |

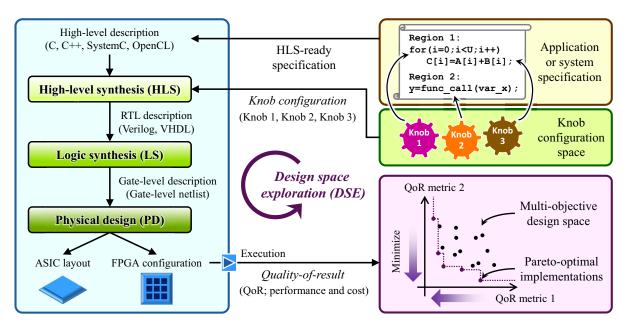

| 4.1 | An overview of design-space exploration with high-level synthesis                          | 61 |

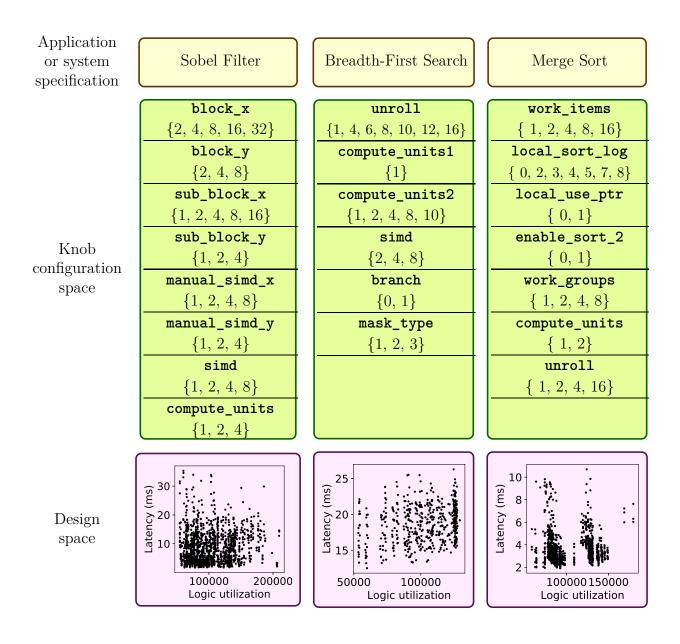

| 4.2 | Design space exploration results for three applications in the Spector bench-              |    |

|     | mark suite: Sobel Filter, Breadth-First Search, and Merge Sort [148]                       | 63 |

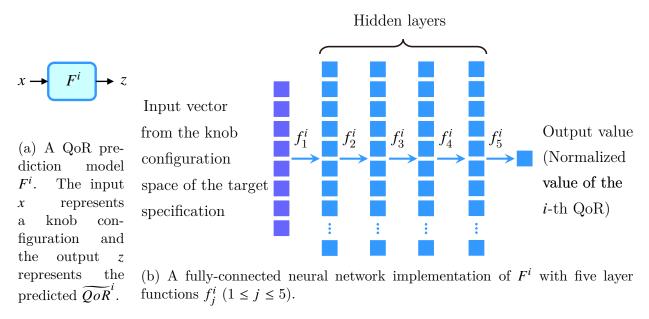

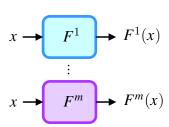

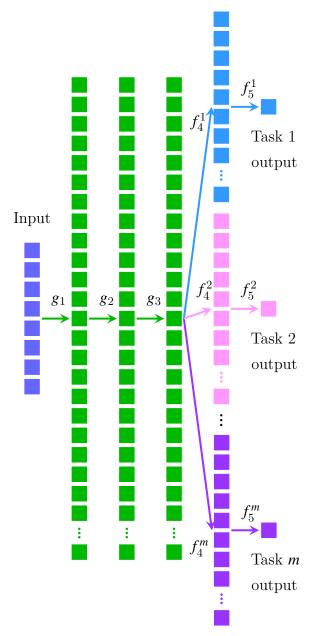

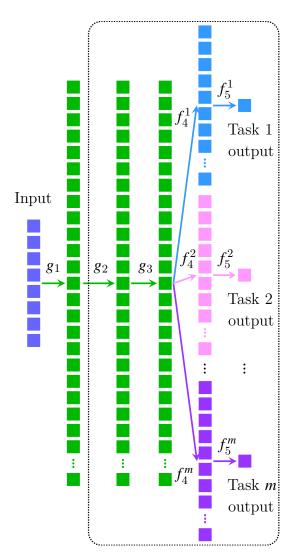

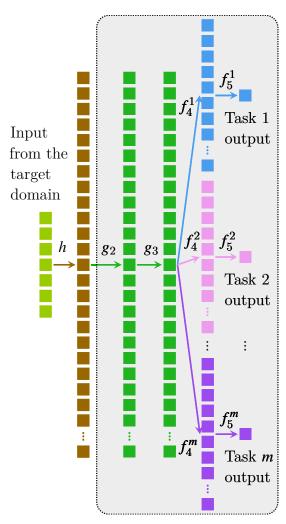

| 4.3 | A predictive model $F^i$ for $\widetilde{QoR}^i$ $(1 \le i \le m)$ in single-task learning | 68 |

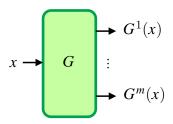

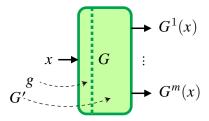

| 4.4 | A predictive model $G$ for $\widetilde{OoR}$ in multi-task learning                        | 70 |

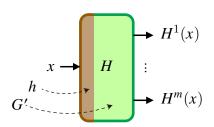

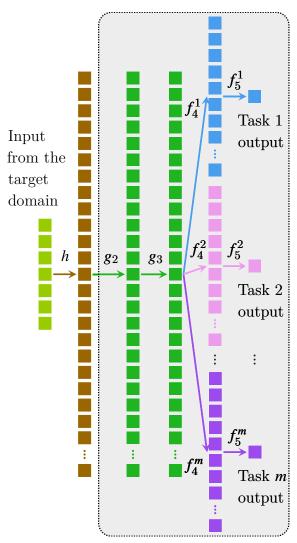

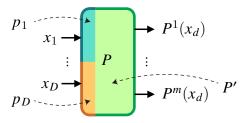

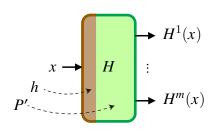

| 4.5  | A source model $G$ and a target model $H$ for cross-domain transfer learning                                     | 71 |

|------|------------------------------------------------------------------------------------------------------------------|----|

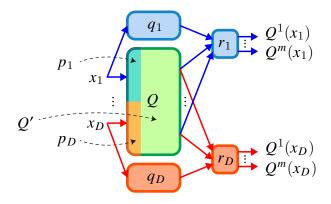

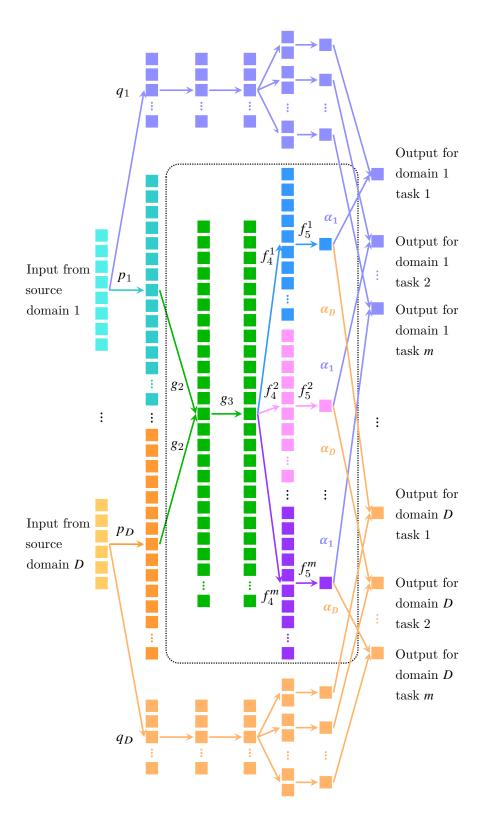

| 4.6  | A source model $P$ and a target model $H$ for multi-domain transfer learning                                     | 74 |

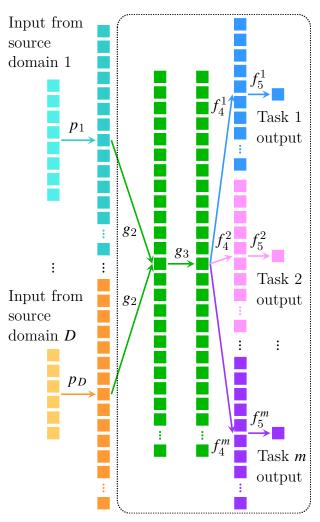

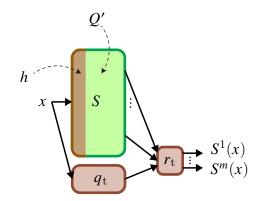

| 4.7  | A source model $\boldsymbol{P}$ and a target model $\boldsymbol{S}$ for mixed-sharing multi-domain trans-        |    |

|      | fer learning with both hard and soft parameter sharing                                                           | 76 |

| 4.8  | A neural network implementation of the mixed-sharing multi-domain model                                          |    |

|      | Q shown in Fig. 4.7 (a). The sub-network in the dotted box ( $Q'$ ) is transferred                               |    |

|      | to the target model                                                                                              | 77 |

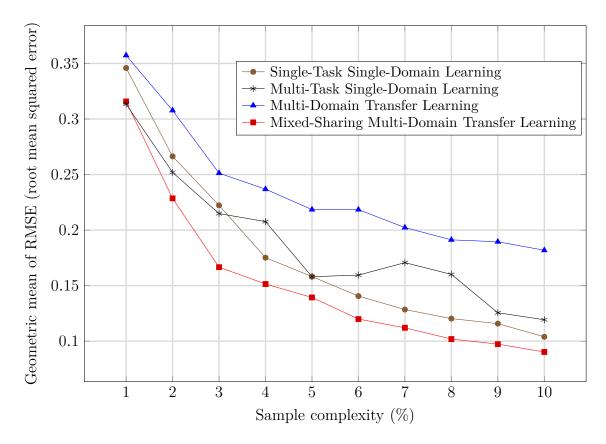

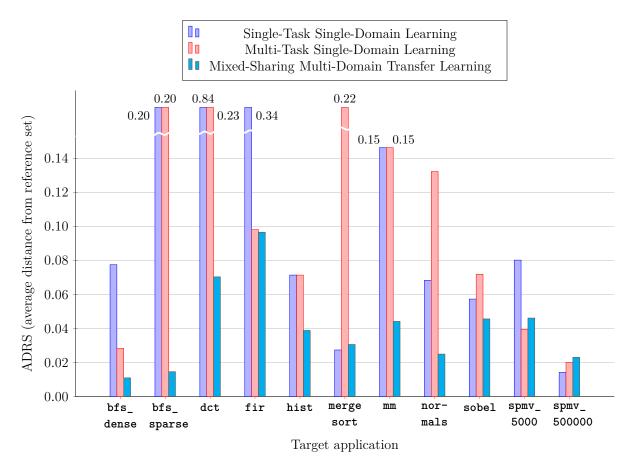

| 4.9  | Geometric mean of RMSE across the 11 sets of HLS QoR, achieved by each                                           |    |

|      | of the four predictive models                                                                                    | 81 |

| 4.10 | Simulated AI-augmented DSE results for the nine Spector applications with                                        |    |

|      | $3\%\text{-sample}$ and $3\%\text{-proposed}$ configurations. Each of $\mathtt{bfs}$ and $\mathtt{spmv}$ has two |    |

|      | versions of the input                                                                                            | 82 |

| 6.1  | An overview of the proposed AI-augmented DSE with end-to-end CAD flows.                                          | 97 |

| 6.2  | An overview of the proposed system with the interplay of online and offline                                      |    |

|      | machine learning [49]                                                                                            | 98 |

### List of Tables

| 3.1 | Examples of $LSPD$ parameters. These meta-parameters were activated as a result        |    |

|-----|----------------------------------------------------------------------------------------|----|

|     | of the DSE for an exemplary macro                                                      | 40 |

| 3.2 | A representative set of five macros from industrial 14nm high-performance              |    |

|     | processors                                                                             | 56 |

| 3.3 | Sum of QoR metrics over the five 14nm macros (top), and the metrics for a              |    |

|     | 7nm macro (bottom). Positive slacks, lower congestion and power are pre-               |    |

|     | ferred. 'a.u.' represents an arbitrary unit                                            | 59 |

| 4.1 | Design spaces of the nine applications in the Spector dataset. Each of bfs             |    |

|     | and spmv has two versions of the QoR results                                           | 80 |

| 4.2 | Geometric mean of ADRS from the simulated AI-augmented DSE using the                   |    |

|     | three predictive models, across the nine Spector applications with $3\%\mbox{-sample}$ |    |

|     | and $3\%$ proposed configurations                                                      | 83 |

| 5.1 | Categorization of approaches: (1) Machine learning (ML) inside CAD tools.              | 86 |

| 5.2 | Categorization of approaches: (2) Machine learning (ML) outside CAD tools.             | 86 |

| 5.3 | Categorization of approaches: (3) Machine learning (ML) outside CAD flows.             | 87 |

#### Acknowledgements

I am sincerely grateful to my advisor, Prof. Luca P. Carloni. When I had ambiguous thoughts, he inspired me to transform them into ambitious goals. I said, "They are too challenging to achieve," and he replied, "That is why they are *interesting* and *worthwhile*!" I learned the beauty of research and the importance of challenges. Whenever I faced difficulties, he offered endless support and guidance, which led me to complete this dissertation.

I am also deeply thankful to my dissertation committee for their insightful questions and discussions. Moreover, I was privileged to work with Prof. Keren Bergman on the mind-blowing topic of *optical* computers. Prof. Martha A. Kim provided invaluable tips on New York life and advice on how to *improve* my presentations. Prof. Rocco A. Servedio enabled me to establish my foundation for machine learning and *learnability*. Dr. Matthew M. Ziegler, my *mentor*, guided me through industrial research, shared his expertise, made stimulating suggestions, and gave constructive feedback. I am incredibly thankful to all of them for our discussions and interactions throughout my PhD program.

Special thanks to all members of the System-Level Design Group: Giuseppe (who sat next to me in the office for many years and answered all my beginner's questions), my dear TAs and mentors (Christian, Paolo, and YoungHoon), Emilio (who always responded to my confusing questions with 100% accuracy), Young-Jin (who gave me the mechanical keyboard, books, and more valuable tips), Hung-Yi (who mentored me for my first small project), Tuca, Kuan-Lin, Guy, Joseph, Maico, Gabriele, Biruk, and all. Thank you so much for all your support, mentorship, and friendship! I am truly blessed to have known Davide Giri as a friend and colleague. He will continue to live in our minds and in our good memories of him.

I want to extend my gratitude to members of the Fish Bowl (David Williams-King, Andrea Lottarini, Martha Barker, and all), who brightened up my ordinary days, and to the former board members of Womxn in Computer Science, with whom I shared very precious experiences. I am immensely thankful to all in the Department of Computer Science.

From the bottom of my heart, I am grateful to my family for their love and support.

#### Chapter 1: Introduction

Machine learning has achieved remarkable performance over the past decades in detecting objects, recognizing patterns, extracting relations, and predicting results. These tasks comprise the computational core of artificial intelligence (AI) applications and AI-augmented systems in diverse areas including computer vision, natural language processing, autonomous robots, and health care. Computer engineering, and especially, design of computer systems are relatively new application areas of AI. Prior to the recent rise of AI, the design process has been aided by computers that automatically transform an abstract description of a system into a specific hardware description. Yet, it has been left to the design experts to explore the enormous design space by leveraging their knowledge and experience. This chapter introduces the concept of AI-augmented design space exploration of computer systems and the challenges of machine learning for such applications.

#### 1.1 Design of Computer Systems

Computers perform computations. Machines operate automatically. Advances in computing machinery has enabled humans to accomplish progressively more complex tasks in such a way that humans make higher-level decisions while offloading repeated subtasks to the specialized machines: the modern computer systems. Ranging from mighty supercomputers to ubiquitous embedded systems, computers have had and are having a tremendous impact on human life and society. In order to take advantage of those machines, humans first design and then build them.

'Design' can both refer to the product, as a noun, and to the process, as a verb [1]. Since this dissertation specifically addresses the design of computer systems, I will use the

term 'design' to refer to the process, while referring to the product as a 'computer system', or briefly as a 'system'. Matchett defines 'design' (from an engineer's perspective) as the process of 'achieving the optimum solution to the sum of the true needs of a particular set of circumstances' [2]. To achieve the optimum solution, designers often engage in systematic and chaotic thinking, employing both mechanical calculation and imaginative thought [1]. In the *computer-aided* design (CAD) methodology, designers may offload the systematic thinking and mechanical calculation to computers. This way, designers can cope with the excessively increasing complexity of the product and the design process, as well as exercising their creativity to solve problems at a higher level.

Modern electronic computer systems execute software instructions with hardware circuits such as central processing units (CPUs), graphical processing units (GPUs), tensor processing units (TPUs), application-specific integrated circuits (ASICs), field-programmable gate arrays (FPGAs), and other types of specialized processors or accelerators. The complexity of integrated circuits has continued to increase at an exponential pace, actualizing the phenomenon known as Moore's law [3, 4]. The very large-scale integration (VLSI) circuits of the 1970s integrated tens of thousands of transistors; today's system-on-chip (SoC) circuits host multiple billions of transistors [5, 6, 7, 8]. This outstanding growth of computational capabilities has been sustained in part by the progress in development of CAD software tools for computer systems. The designer abstractly describes the target computer system in the form of a specification of the system. Then, a CAD tool or a CAD flow (a chain of sequentially executed CAD tools) performs refinement steps from the higher level down to the detailed level of description to automatically generate an implementation of the input specification. Hence, the CAD flow facilitates the design of extremely complex systems; moreover, it does so by providing separation of concerns between the specification and the implementation.

Both in academia and in industry, CAD approaches (also frequently called 'electronic design automation (EDA)' approaches in industry) have evolved towards raising the level of abstraction. Advanced CAD flows typically include the steps of high-level synthesis (HLS),

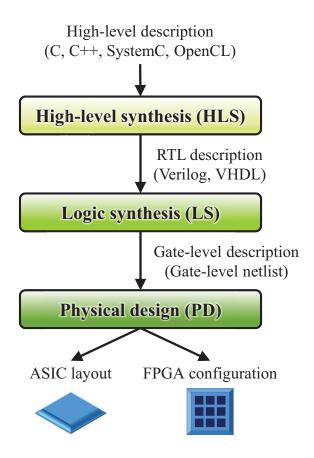

Figure 1.1: A typical computer-aided design (CAD) flow with high-level synthesis (HLS), logic synthesis (LS), and physical design (PD). Each CAD tool or tool-chain (a rounded and shaded box) transforms a higher-level specification into a lower-level implementation.

logic synthesis (LS), and physical design (PD), as shown in Fig. 1.1. An HLS tool transforms a behavioral specification (in high-level languages such as C, C++, SystemC [9], and OpenCL [10]) into a structural implementation, which describes the structures and operations of the specified system at register-transfer level (RTL) [11]. An LS tool translates an RTL specification (in hardware description languages such as Verilog [12] and VHDL [13]) into a gate-level implementation, which is a network of logic gates implementing the specified logic and functionality [14]. Given a gate-level specification (in a gate-level netlist), a PD tool or tool-chain performs placement and routing to generate a final implementation. Placement determines the location of the logic gates, and routing interconnects those gates with wires [15]. The final implementation will be a physical layout for an integrated circuit

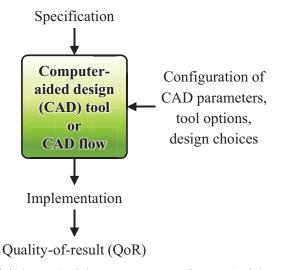

(a) A single CAD run with configurable CAD parameters. Their configuration guides the execution of CAD algorithms, which in turn affects the quality-of-result (QoR).

Optimal implementation(s)

(b) Repeated CAD runs for a specification and design objectives in the search of optimal implementations. This process is called design space exploration (DSE).

Figure 1.2: An advanced CAD process with configurable CAD parameters.

system, and it will be a configuration bitstream for an FPGA-based system.

Most stages in CAD require the solution of many intractable (NP-hard) problems at a very large scale [16]. A single run of a CAD flow may take many hours to days, depending on the complexity of the designed system. However, a designer's task does not complete with a single run. Let us recall the aforementioned definition of design: achieving the 'optimum solution to the sum of the true needs of a particular set of circumstances'. For CAD of a particular modern electronic computer system (whose behavior is well specified), the needs are to maximize the system performance while minimizing various types of cost associated with the production and operation of the system. The principal performance (e.g., latency, throughput, accuracy) and cost (e.g., area occupation, power dissipation, wire congestion) metrics are often inversely affected by design choices [17, 18]. For instance, improving the performance by reducing the latency usually comes at the expensive cost of larger occupation of silicon area or FPGA resources. Thus, it is infeasible for CAD tools to automatically generate a final implementation that presents optimal values for all metrics of interest. Instead, advanced CAD tools and flows provide a variety of CAD parameters that

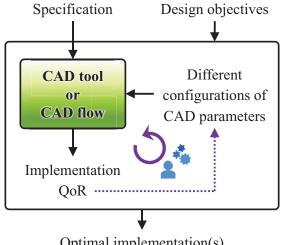

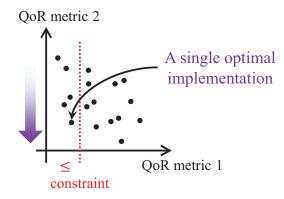

- (a) Multi-objective DSE to find many Pareto optimal implementations.

- (b) DSE with constraints to find a single optimal implementation.

Figure 1.3: Exploration of design spaces with multiple QoR metrics to minimize (or maximize).

affect the execution of the algorithms within the tools and, eventually, drastically impact the resulting performance and cost, also called quality-of-result (QoR), as shown in Fig. 1.2 (a). Hence, it is an essential role of designers to configure the CAD parameters in order to obtain implementations with acceptable, desirable, or optimal QoR, as shown in Fig. 1.2 (b).

#### 1.2 Design Space Exploration of Computer Systems

The process of searching for the optimal CAD parameter configurations for a computer system is called design space exploration (DSE). Effects of CAD parameters on QoR vary depending on the particular system being designed. Moreover, different metrics of QoR require a careful balancing of the delicate trade-offs. Therefore, designers usually test numerous configurations of different parameter values by repeatedly running the CAD tools with each configuration in order to navigate the multi-objective design space where each objective corresponds to maximizing or minimizing one QoR metric of interest. This process of DSE forms an integral part of optimizing each system, and it consumes a considerable amount of time along with computing and human resources, even with today's state-of-the-art industrial CAD flows.

Multi-objective DSE aims at minimizing or maximizing multiple, often conflicting, QoR

metrics of an implementation. Fig. 1.3 (a) illustrates a design space of a specification with two QoR metrics to minimize. The black points represent distinct implementations of the same specification. For simplicity, when the objective is to minimize all metrics, one implementation is said to *Pareto dominate* another implementation if (1) the formal has QoR values less than or equal to those of the latter in all metrics, and (2) the formal has a strictly smaller QoR value than the latter for at least one metric. Among all implementations (in consideration) of a specification, an implementation that is not Pareto-dominated by any other is called *Pareto optimal* [19]. In Fig. 1.3 (a), the black points connected by the purple dotted lines correspond to the Pareto optimal implementations. A goal of the DSE process is to identify all CAD parameter configurations that lead the CAD tools to generate the Pareto optimal implementations. This is mainly for reusing the specification in various circumstances.

The intellectual property (IP) reuse methodology has become one of the keys for the productivity improvement of modern computer system design [20]. A final implementation that exhibits predetermined QoR is classified as hard IP, whereas a higher-level specification that can be synthesized to have various QoR is soft IP. A library of reusable IP blocks with various timing, area, and power configurations allows a new system integrator to reuse the IP blocks with the best configurations to meet the target system's requirements [21]. Thus, it is often the goal of DSE with HLS tools, especially for designing reusable hardware accelerators, to find many, if not all, of the CAD parameter configurations that are mapped to the Pareto optimal implementations, or to the implementations of close QoR values to those of some Pareto optimal ones [22].

LS and PD tools, on the other hand, generate highly optimized hard IP for a target system (which could be reused as well). Many stages of optimization in PD (e.g., placement, routing, post-routing optimization) are order of magnitude more computationally expensive than those in HLS. Such high complexity of the CAD problems makes it infeasible to find all Pareto optimal implementations during the DSE, especially for complex VLSI systems

with stringent time-to-market requirements. Moreover, such exploration has a lower payoff when done with LS and PD than with HLS [23]. Therefore, another goal of DSE – also called parameter tuning or CAD flow tuning with respect to this goal – is to find a single optimal implementation that minimizes (or maximizes) an objective function subject to a set of constraints, as shown in Fig. 1.3 (b). The objective function is usually defined as a single QoR metric, or as a scalarization (e.g., a weighted sum) of multiple QoR metrics [24]. The constraints describe a valid range of values for certain QoR metrics. For instance, the goal with an LS process is to find an implementation 'with a minimum area while meeting the delay constraint' [25]. The ultimate goal with another LS and PD process is 'to reach timing closure at the lowest achievable power' [26].

Strategies for DSE include exhaustively evaluating every possible configuration; randomly sampling the design space; leveraging the designer's knowledge, experience, and expertise; developing analytical models for QoR estimation; and applying heuristics or meta-heuristics, such as genetic algorithms and simulated annealing [27, 22]. Since an exhaustive search is impracticable, it is crucial to discover the optimal, or near optimal, configurations after running the CAD tools or flows as few times as possible. Recently, the proliferation of AI and machine learning in a wide variety of application areas has motivated the advent of AI-augmented DSE of computer systems [22, 28].

#### 1.3 AI-Augmented Design Space Exploration of Computer Systems

AI is 'the science and engineering of making intelligent machines' which have 'computational ... ability to achieve goals in the world' [29]. Since Turing proposed in 1950 to consider the question 'Can machines think?' [30], researchers have attempted to 'find how to make machines use language, form abstractions and concepts, solve kinds of problems now [or, then] reserved for humans, and improve themselves' [31]. While the rate of progress in AI thereafter has been 'unpredictable', twenty-first century AI has seen extraordinary advances fueled by 'the maturing of machine learning' [32]. Such maturation has been supported

by the availability of large-scale data (also called 'Big Data'), and the capabilities of modern high-performance computer systems [32, 33, 34]. Consequently, AI has been deployed or integrated in a variety of AI-assisted, AI-based, AI-centric, AI-driven, AI-enabled, and AI-powered applications in diverse domains [35, 36, 37, 38, 39, 40].

Design of optimal computer systems is another goal that could be targeted by AI, but not solely by AI – as of today and in the near future. A more thorough definition of 'design' is derived in a survey by Evbuomwan et al. (from mechanical engineers' perspective):

[Design is] The process of establishing requirements based on human needs, transforming them into performance specification and functions, which are then mapped and converted (subject to constraints) into design solutions (using creativity, scientific principles and technical knowledge) that can be economically manufactured and produced [41].

Design of computer systems involves (1) establishing requirements, (2) transforming them into a specification, and (3) converting them into implementations that are optimal or feasible. The first two steps are led by humans. 'The current state of AI technology is still far short of the field's founding aspiration of recreating full human-like intelligence in machines,' states the 2021 Study Panel of the long-term investigation of AI, One Hundred Year Study on AI [42]. It is not only the limited capabilities of the current AI, but more importantly, the impact and responsibility of the decisions made in the first two steps that require those decisions to be made or confirmed by humans. The third step, which is the main focus of this dissertation, has been led by humans, aided by computers. AI may assist them.

Initially, human designers manually produced the physical layout. Development and sophistication of the CAD tools enabled designers to put more effort into producing the specification and performing DSE while offloading to CAD tools the repeated subtask of converting the specification into implementations. These activities, by both the designers and CAD tools, demand *intelligence*, namely creativity, scientific principles, and technical knowledge (as noted by Evbuomwan et al.). The goal of AI-augmented design or DSE

is to develop an AI system with such *intelligence* to boost both design productivity and quality. Many approaches have been proposed over the past decade targeting various stages of CAD [28]. More recently, Google and Nvidia have released that their next-generation computer systems are designed by AI-driven systems, while Synopsys and Cadence have announced AI-based optimization platforms targeting their CAD tool products [43]. At the core of all those AI applications for computer system design is machine learning<sup>1</sup>.

# 1.4 Machine Learning for AI-Augmented Design Space Exploration of Computer Systems

Machine learning is 'a subfield of AI' that addresses the question of 'how to build computers that improve automatically through experience' [34, 44]. A subcategory of machine learning that has been extensively studied is supervised learning, where machines use a labeled set of data, i.e., tuples of (input data; output label), in order to predict the output label from the unseen input data. For classification problems, the labels are classes or categories. For instance, in the problem of handwritten digit recognition, the goal is to learn a model that takes in an image consisting of pixel values and outputs the corresponding digit:  $0, 1, \dots, 9$  [45]. This model is trained using a labeled set of (input: image; output: digit) data. For regression problems, the labels are continuous values, such as the temperature, house prices, or the amount of carbon dioxide emissions. During DSE of a computer system, designers run CAD tools a large number of times with various CAD parameter or flow configurations to learn the corresponding QoR. This DSE problem can be translated into a regression problem with (input: specification, CAD configuration; output: QoR).

Multiple challenges arise in this problem due to the characteristics of CAD problems.

Many machine learning applications utilize data obtained from huge collections of users' input and public databases for a single problem. The QoR-prediction problem for each system suffers from limited availability of data obtained from expensive CAD runs.

<sup>&</sup>lt;sup>1</sup>Not all, although a majority, of AI applications involve machine learning.

Especially, an industrial CAD flow specifies hundreds of separate CAD parameters, resulting in an extreme curse of dimensionality. Hence, I propose to learn from the experience (labeled datasets) not only with the target computer system, but also with other systems.

- 2. Different systems exhibit different configuration-QoR relationship. As a result, a model learned from a few previously explored systems cannot be directly exploited to predict the QoR for new target systems. Hence, I propose to learn from the experience with many other systems. Then, in order to successfully learn from many other heterogeneous systems, it is required to identify each system's characteristics and its relationship with other systems.

- 3. Designers apply unique sets of CAD configurations during the DSE of each individual system. This makes it harder to learn from previous DSE results. Especially in HLS, the specification heterogeneity leads to broad CAD configuration heterogeneity across specifications. Hence, I propose to collaborate with designers, augmenting their performance with AI, and to transfer common knowledge across the design tasks.

To address the above challenges and improve the performance of AI-augmented DSE, I propose to flexibly connect the elements of the many QoR-prediction problems with one another. My thesis is that The exploration of the design space of a computer system can be effectively augmented by artificial intelligence via learning from the experience with the design and optimization of other systems.

For the design of industrial high-performance processors, I propose a novel collaborative recommender system approach that learns hidden features from the interactions (CAD runs) of many users (computer systems) and items (configuration of design parameters). To cope with the curse of dimensionality, the item features are decomposed into features of item attributes (individual parameters). The combined model predicts QoR for each user-item pair.

For the design of application-specific accelerators, I present a series of neural network models in the order of evolution towards the proposed mixed-sharing transfer learning model. Transfer learning aims at leveraging knowledge gained from previous problems; however, due to the target computer system and design parameter heterogeneities, the model needs to distinguish which piece of that knowledge should be transferred.

The proposed machine learning approaches aim to not only use experiential knowledge as designers do but also to ultimately assist designers by providing alternative insights and suggesting optimization possibilities for new systems. As an effort in this direction, I develop an AI-augmented DSE tool that exploits the aforementioned models and *generates* recommended CAD configurations for new target systems.

#### 1.5 Contributions and Outline

My research contributions span across HLS, LS, and PD stages of CAD (shown in Fig. 1.1) and address DSE problems of both searching for Pareto-optimal implementations (Fig. 1.3(a)) and searching for a single optimal implementation (Fig. 1.3(b)). The contributions are summarized as follows:

- A recommender system approach for industrial LS and PD flows [46, 47]

- A transfer learning approach for HLS flows [48] (Best Paper Award)

- A classification of machine-learning-based approaches for design optimization ([49], a book chapter under submission, and a survey paper in preparation)

- AI-augmented DSE by learning from the experience with other computer systems, configuration spaces, technology, and CAD tools (All of the above work, and a journal article in preparation)

The rest of this dissertation is organized as follows. Chapter 2 presents a typical design process of a modern computer system, as a background for the research problems addressed

in this dissertation. Chapter 3 proposes a collaborative recommender system approach for AI-augmented DSE with LS and PD flows for industrial high-performance processors. Chapter 4 proposes a transfer learning approach for AI-augmented DSE with HLS flows for specialized accelerators. Chapter 5 reviews and categorizes machine-learning-based approaches for DSE with CAD of computer systems. Chapter 6 presents the future work and concluding remarks.

#### Chapter 2: Background

A monolithic integrated circuit, also called an integrated circuit, a microelectronic circuit, a microchip, or a chip, is a complete circuit or set of circuits manufactured on a single piece of semiconductor material [50]. Its miniaturizability and scalability have brought about the impressive success of the microelectronic industry since the 1960s. Today, it serves as the essential component of most of the contemporary computers, ranging from supercomputers and cloud servers to embedded systems and IoT (Internet-of-things) devices. Design of such computer systems has been facilitated and expedited by CAD methodology, which has evolved in the direction of raising the level of abstraction. The first PD tools date back to the 1960s, LS tools to the 1980s, and HLS tools to the 1990s [15, 51]. This chapter first provides a brief historical perspective on the emergence of integrated circuits. Then, it introduces the major stages of modern CAD flows in the reverse order of their development, following the order of their execution in today's CAD flows.

#### 2.1 Emergence of Integrated Circuits: A Historical Perspective

Going back in history, Turing proposed in 1936 a mathematical model of computing machines that laid the foundation of modern computers [52]. The first electronic calculating machine was built by Atanasoff and Berry in 1939, using a vacuum tube (which controls the flow of electrons in a vacuum) as a switch or amplifier to control the flow of electric current [53, 54]. ENIAC (Electronic Numerical Integrator and Computer), the first general-purpose electronic computing machine was built during the Second World War and presented to the public in 1946 [55]. It was the fastest and large-scale at the time, while being equipped with about 17,000 vacuum tubes, weighing 26 tons, occupying 440 cubic meters, and consuming

174 kilowatts of electricity – not a scalable technology [54].

Smaller and less power-consuming switches to control electronic signals, called transistors, were created by the Bell Labs scientists, Shockley, Bardeen, and Brattain in 1947 [56]. Transistors are made from semiconductor materials, such as silicon and germanium. Semiconductors have electrical properties that are between conductors and insulators, and their conductivity can be controlled by doping, i.e., adding impurities. The first transistors were made from germanium; later, silicon has become the dominant material, as it offers advantages of higher operating temperatures, breakdown voltage, and power-handling ability [54]. The race for miniaturization of electronic circuits intensified until 1958, when Kilby at Texas Instruments invented and demonstrated the first (hybrid) integrated circuits, with on-chip components connected by external wires [57, 58]. After a half year, Noyce at Fairchild Semiconductor independently invented the first monolithic integrated circuits, with all wires and components on a single chip [59, 60]. The inventions of transistors and integrated circuits have revolutionized the electronics industry and were recognized by the Nobel Prize in Physics in 1956 and 2000, respectively [61, 62].

Integrated circuits consist of different components, such as transistors, resistors, capacitors, and diodes, that are all made from the same materials (usually silicon) for integration [58, 54]. Those circuit components can be analogous to the parts of speech, such as nouns, verbs, adjectives, and adverb, as noted by Reid [63]. Each component has its own function, and by connecting them in different ways, we can obtain the sentences or circuits that perform in different ways [54]. It is the designers' task to connect those components to build a circuit that performs as desired. At first, designers produced by hand a geometric description of circuits, called a layout, on papers and films (for fabricating integrated circuits on semiconductor substrates by photolithography) [64].

Technology continued to advance to allow integrated circuits to incorporate thousands of transistors on a single chip by the late 1960s. The computers built with those integrated circuits were harnessed to speed the development process and eliminate errors in the design of the next generation of integrated circuits [65]. IBM and Fairchild developed in-house graphical CAD tools for circuit layout design and simulation [66, 67, 68, 69]. Their work, along with the academic project SPICE (Simulation Program with Integrated Circuit Emphasis) laid the foundation for CAD of integrated circuits [67, 70, 71].

#### 2.2 Computer-Aided Design for Modern Computer Systems

Design methodology for integrated circuits has advanced to achieve increasing levels of automation and abstraction. The automation of computation has allowed designers to offload the fixed computational subtasks to computers, while solving problems that require higher degree of creativity. The abstraction level refers to the level at which designers specify circuits. By raising this level, CAD tools provide separation of concerns between the higher-level structure, behavior, or functionality, and the lower-level implementation details [72]. Such advances in CAD have supported the development of the state-of-the-art computer systems that offer high performance, energy efficiency, acceleration, and specialization.

Modern computer systems contain computational subsystems that range from general-purpose to specialized systems. Since their invention, transistors have reduced in size exponentially, resulting in an exponential increase of transistor density on a chip (Moore's law), yet still capable of maintaining constant power density (Dennard scaling) [3, 4, 73]. Thanks to the VLSI technology and advanced CAD, today's high-performance processors and systems-on-chip include multiple billions of transistors on a single chip [5, 6, 7, 8]. Most of them include general-purpose processors that can run an extensive variety of applications. The technology scaling, however, has slowed down due to the physical limitations and the end of Dennard scaling around 2005 [74]. In order to improve the performance while maintaining the power dissipation and heat generation below thresholds, multi-core and heterogeneous architectures have emerged. State-of-the-art SoC architectures may include multiple and heterogeneous subsystems such as general-purpose processors, special-purpose processors (e.g., GPUs, TPUs, digital signal processors, and neural processors), and application-specific

hardware accelerators [75]. The specialized processors or accelerators execute the specific instructions or applications that they are designed for. Programmable logic devices (e.g., FPGAs) and coarse-grain reconfigurable devices (e.g., coarse-grain reconfigurable arrays) can be configured after fabrication to execute (a group of) specific functionalities. They can be configured to implement specialized processors or accelerators, and reconfigured for different applications [76, 77, 78, 79].

A computer system in this dissertation refers to a computational subsystem, be it general-purpose, specialized, or reconfigurable, that is often designed (or configured) independently from one another. By extension, the term also refers to a full computer system that includes those subsystems. Ch. 3 addresses the design of high-performance general-purpose processors, and Ch. 4 focuses on the design of various specialized accelerators. The following subsections depict an exemplary CAD flow for modern, electronic, digital<sup>1</sup>, and synchronous<sup>2</sup> computer systems, which belong to the dominant type of modern computer systems.

#### 2.2.1 High-Level Synthesis

A typical CAD flow for a computer system today includes HLS, LS, and PD. To take a closer look at the design process, let us recall the definition of 'design' by Evbuomwan et al. from the previous chapter. Design is the process of

- (i) establishing requirements based on human needs,

- (ii) transforming them into performance specification and functions,

- (iii) mapping and converting them (subject to constraints) into design solutions (using creativity, scientific principles and technical knowledge) that can be economically manufactured and produced [41].

<sup>&</sup>lt;sup>1</sup>Digital circuits deal with discrete levels of signals: e.g., a high voltage representing '1' and a low voltage representing '0' in binary systems. Analog circuits, on the contrary, deal with continuous signal values.

<sup>&</sup>lt;sup>2</sup>In a synchronous digital circuit, an oscillating clock signal determines when the state of memory elements is changed (values written or read): e.g., on the rising clock edge. Asynchronous circuits do not have global clock.

Let us assume that (i) a designer, Danny, was asked to design a low-power real-time accelerator for a specific artificial neural network (ANN) application (human needs). Danny determines the algorithm, function, or behavior of the ANN application, and confirms system requirements such as power and latency (requirements). Then, (ii) Danny generates a specification from the requirements determined in the previous step. The algorithm, function, or behavior of the application is transformed into a high-level specification written in a high-level language, e.g., C, C++, SystemC [9], or OpenCL [10] (function specification). The system requirements are quantified, e.g., target or maximum values of the power and latency are set (performance specification). Those values are sometimes given by the customer or determined from a larger design project. After generating the specification, (iii) Danny runs an HLS tool to convert it into RTL implementations (map and convert into design solutions). The HLS tool uses the synthesis algorithms (scientific principles) and an RTL component library (technical knowledge). Aided by the HLS tool, Danny performs DSE to minimize the power, latency (performance specification), and resource utilization (economically manufactured and produced).

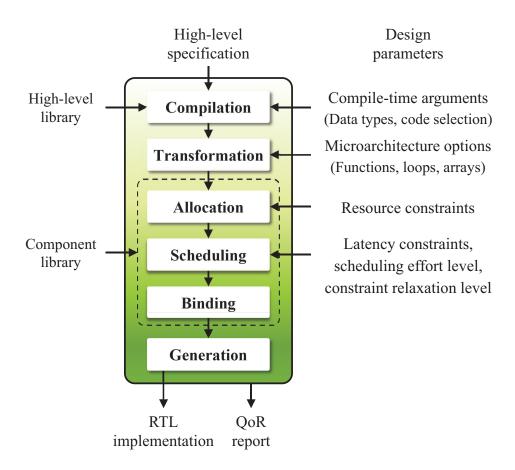

Fig. 2.1 illustrates an overview of a typical HLS process. The HLS tool takes in a high-level specification and generates an RTL implementation of it [11]. The tool may refer to high-level libraries (which the designer used in the specification) for front-end compilation. The RTL component library provides information required in the generation of RTL implementations that consist of those components. The designer can constrain, guide, and control the HLS process with design parameters as shown on the right in Fig. 2.1.

#### Compilation

First, the high-level specification is compiled into a formal model of computation. A model of a system is a representation that shows relevant features without associated details, and formal models have a well-defined syntax and semantics for interpretation and transformation [14]. A formal model in HLS generally exhibits the data and control depen-

Figure 2.1: A typical design process with an HLS tool that translates a high-level specification into an RTL implementation as guided by the design parameters.

dencies between the operations without language-dependent details.

Let us take our designer Danny's ANN accelerator as an example. ANNs usually consist of interconnected layers of nodes, where each node contains a value and each layer can be represented as a vector (or a tensor of a higher dimension). Starting from a given input layer, the next layer is often computed by performing matrix multiplications to the previous layer, adding a bias, and applying a non-linear activation function. This part can be expressed as follows:

$$y = f(A \cdot x + b), \tag{2.1}$$

where x and y represent the previous and the next layer, respectively; and A is the weight matrix, b is the bias vector, and f is the activation function (e.g., tanh, sigmoid, a rectified linear unit, or softmax) for computing the next layer.

```

1

void add_bias(dType b[n_next], dType y[n_next]) {

2

int i;

3

for (i = 0; i < n_next; i++)

y[i] = y[i] + b[i];

4

}

5

6

7

void apply_tanh(dType y[n_next]) {

8

int i;

9

for (i = 0; i < n_next; i++)

y[i] = \tanh(y[i]);

10

}

11

12

void process_layer(dType x[n_pre], dType A[n_next][n_pre],

13

dType b[n_next], dType y[n_next]) {

14

int i, j;

15

dType temp;

16

for (i = 0; i < n \text{ next}; i++)

temp = (dType) 0.0;

17

for(j = 0; j < n_pre; j++)

18

temp = temp + A[i][j] * x[j];

19

y[i] = temp;

20

}

21

add_bias(b, y);

22

23

apply_tanh(y);

24

}

```

Listing 2.1: A high-level specification in C. The top function (to become the top level of the implementation) is process\_layer which computes Eq. 2.1.

```

// i = 0

1

r0 = 0

2

3

Block 1:

// j = 0

r1 = 0

4

// \text{ sum} = 0

5

r5 = 0

6

r9 = r3 + r0 * n_pre // address of A[i]

7

8

Block 2:

9

r6 = load(r9 + r1) // load A[i][j]

r7 = load(r2 + r1) // load x[j]

10

11

r8 = r6 * r7

// \text{ temp} = A[i][j] * x[j]

12

r5 = r5 + r8 // sum = sum + temp

13

r1 = r1 + 1

// j++

eval r1 != n_pre // ctrl = (j != n_pre)

14

15

cjump Block_2 // jump to Block_2 if ctrl is True

16

17

Block 3:

18

store(r4 + r0, r5) // store y[i]

19

r0 = r0 + 1

// i++

eval r0 != n_next // ctrl2 = (i != n_next)

20

21

cjump Block_1 // jump to Block_1 if ctrl2 is True

22

23

Block 4:

call add_bias, r10, r4 // subfunction add_bias

24

25

call apply_tanh, r4 // subfunction apply_tanh

```

Listing 2.2: An intermediate representation of the body of process\_layer from Listing 2.1.

Given the above requirements, Danny produces a specification in C as shown in Listing 2.1. Function  $process_layer$  computes Eq. 2.1, where  $n_pre$  denotes the number of nodes in the previous layer x, and  $n_next$  is for the next layer y. dType is a user defined data type whose definition is in a header file or in a high-level library. Danny defines it as a native C type, such as float, for the software version, and selects a fixed-point data type for HLS. Function tanh shown in line 10 is also provided by a high-level library.

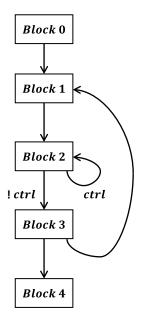

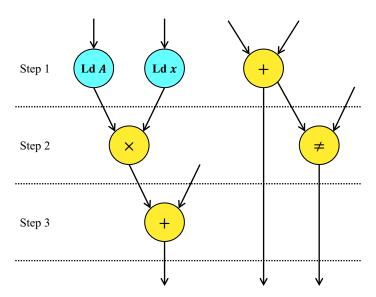

The compilation process involves preprocessing, lexical analysis, parsing, and semantic analysis. After compilation, a formal model of the specification, called *intermediate repre*sentation, can be obtained as shown in Listing 2.2<sup>3</sup>. This can be further translated into a control and data flow graph, which is another formal model of the specification as follows. The intermediate representation is partitioned into basic blocks, which allow only sequential execution of instructions except the entry and exit points. A control flow graph is a directed graph whose nodes represent the basic blocks and directed edges represent the control flow between the blocks. Fig. 2.2(a) shows a control flow graph of the body of process layer from Listing 2.2. The computation in each node (block) of the control flow graph can be represented by a data flow graph. A data flow graph is a directed graph whose nodes represent the operations (e.g., Ld (load),  $\times$ , +, and  $\neq$ ) and directed edges represent the data dependency. Fig. 2.2 (b) illustrates a data flow graph of *Block* 2 in process layer. The left subgraph corresponds to lines 10 – 13 of the intermediate representation in Listing 2.2, which compute the sum of products of elements from the weight matrix A and from the previous layer vector x. The right subgraph represents lines 14-15, which update the index j and compute a control signal ctrl as a result of eval in line 15. This signal ctrl is used to control the flow that goes out of Block 2, as shown in Fig. 2.2(a). A combination of a control flow graph and a data flow graph for each block in the control flow graph is called a control and data flow graph. Since the basic blocks allow only sequential execution, the data flow graph for each block is acyclic by construction. Some HLS tools enforce that all data

<sup>&</sup>lt;sup>3</sup>An *intermediate representation* is a representation of a software program between the source code and the machine code. A software compiler usually produces this as an internal representation.

- (a) A control flow graph of process\_layer. *Block* 2's computation is presented in (b).

- (b) A data flow graph of *Block* 2 in process\_layer. The left and right subgraphs correspond to lines 10 13 and lines 14 15 of the intermediate representation in Listing 2.2, respectively.

Figure 2.2: A control and data flow graph of the body of process\_layer from Listing 2.2.

flow graphs remain acyclic throughout the synthesis process.

Design parameters for the compilation process include compile-time arguments such as data type definitions (e.g., dType), code selection (e.g., an alternative version of the same functionality), library selection, parallelism options (e.g., number of parallel threads), and compiler optimizations (e.g., -O0 or -O3).

#### Transformation

In addition to the front-end compiler optimizations, the formal model (e.g., an intermediate representation or a control and data flow graph) may undergo a set of semantic-preserving transformations. In some cases, those transformations are automated; in others, they are guided by the designer [14]. Design parameters applied during this process determine microarchitectural details of the implementation. The major transformation parameters are listed below in three categories. State-of-the-art commercial HLS tools support most (but

not necessarily all) of them, possibly with different names [80, 81, 82]. Some parameters become effective when certain conditions related to the target transformation are satisfied.

• Function transformations: function\_inline, function\_instantiate, convert\_to \_lookup.

Danny's top function process\_layer contains two subfunction calls, add\_bias and apply\_tanh. If those function calls are *inlined*, they dissolve into the calling function, process\_layer, and may share components in the RTL implementation. Otherwise, the callee functions are *instantiated*; they remain as separate hierarchy blocks in the RTL, and do not share components with the upper level blocks.

A possible benefit of function\_inline is that the scope of application of some optimization techniques is enlarged [14]. However, if the same function is called multiple times, inlining them every time may result in the increased area or resource utilization. In that case, function\_instantiate will instead have a single block of implementation used multiple times, as long as the function calls are at the same level of hierarchy. convert\_to\_lookup converts a combinational function call into a table lookup. Inputs to the function drive the address of the table (array) element, and the values read out of the table drive the outputs of the function. This conversion may be useful for combinational functions with long latency, as it can improve the timing [81].

Loop transformations: loop\_break, loop\_unroll, loop\_pipeline, loop\_flatten, loop\_merge.

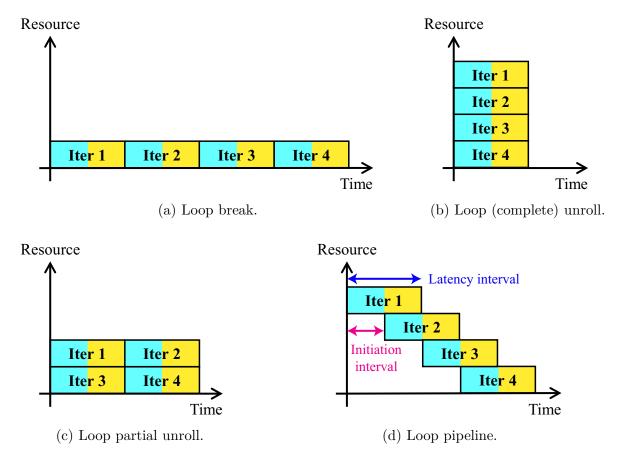

Fig. 2.3 illustrates the effect of four loop transformations on time and resource. loop\_break inserts states so that each iteration of the loop takes at least one clock cycle, and the iterations are executed in a sequence [81] (Fig. 2.3 (a)). loop\_unroll replaces the loop by as many instances of its body as the number of loop iterations, allowing some or all of the iterations to occur in parallel (if data dependencies and resources allow) [14, 80] (Fig. 2.3 (b)). Complete unrolling can be applied only when the loop

has a data-independent exit conditions [14]. For this, Danny has to explicitly assign or define values to n pre and n next. When those values are not determined at design time, Danny can use upper bound values to state the loop exit conditions, and execute the loop body only when the iteration counter value is less than n pre or n next at runtime. Partial unrolling creates as many copies of the loop body as the given unrolling factor. For instance, Fig. 2.3(c) shows the partial unrolling of the loop in Fig. 2.3(a) by a factor of 2. loop pipeline allows the overlapped execution of loop bodies, as shown in Fig. 2.3 (d). When pipelining loops, the designer may specify the initiation interval, the minimum latency interval, and the maximum latency interval. The initiation interval (denoted by the pink arrow in the figure) is the number of clock cycles between two consecutive executions of the loop body. Due to loop-carried dependencies, the problem of finding the minimum initiation interval of a given loop is known to be NP-complete [83]. Thus, commercial HLS tools often require the designer to specify this interval when applying loop pipelining [84, 81, 80]. The latency interval (the blue arrow) refers to the number of clock cycles to complete the execution of a single loop body instance. As shown in Fig. 2.3, loop break may be used to minimize the area, loop unroll to reduce the latency and increase the throughput, and loop pipeline to optimize altogether the throughput, resource utilization, and the number of concurrent memory accesses.

loop\_flatten removes the loop hierarchy by flattening the innermost loop into a single outer loop, when only the innermost loop contains loop-body contents. In the RTL implementation, it requires one clock cycle to move from an outer loop to an inner loop, and from an inner loop to an outer loop; hence, flattening nested loops may save clock cycles and allow them to be optimized as a single loop [80]. loop\_merge combines consecutive loops at the same level of hierarchy into a single loop. The loop bounds of all merged loops must be a constant or a variable of the same value. This transformation may reduce the overall latency (in RTL for transitioning between

Figure 2.3: Effect of loop transformations in HLS.

merged loops), increase sharing of components among the loops, and improve logic optimization [80].

Array transformations: array\_flatten, allocate\_memory, array\_merge, array\_split, array\_restructure.

Some arrays in the specification are built into memories, either as a set of flat registers, with a built-in memory, with a prototype memory (as a placeholder), or with a vendor memory from the component library. array\_flatten transforms the array into a set of registers, replacing all read and write operations to the array with equivalent reading and writing of the variables that each represent an element of the array [81]. This transformation may reduce the area and latency when the flattened arrays are small and heavily used. allocate\_memory creates the specified type and implementation of

memory (e.g., built-in memory, random access memory (RAM), block RAM (BRAM), ultra RAM (URAM), or read-only memory (ROM)) and binds it to the array. The numbers of read, write, and read/write ports of the memory indicate how many read and write operations can be performed in parallel at the same clock cycle.

array\_merge combines multiple arrays into a single array, which may be smaller than multiple individual arrays. array\_split, on the other hand, splits a single array into multiple smaller arrays. The split method can be specified among cyclic, block, and complete [80]. This transformation may improve the memory access parallelism at the cost of an increased area. array\_restructure changes the number of elements (words) in an array. The array can be scaled up (increased number of words with decreased data width) or scaled down (decreased number of words with increased data width) in multiples of powers of 2 [81].

# Allocation

From the formal model after the transformations, the data dependency part (also represented as a data flow graphs) is translated into a datapath, while the control dependency part (also represented as a control flow graph) becomes a finite state machine that controls the datapath. The datapath is generated through the steps of allocation, scheduling, and binding, which may occur concurrently or in various orders.

Allocation determines the type and quantity of hardware resources (e.g., functional units, storage units, and interconnection units) to be used in the implementation [85, 86]. The functional units (e.g., arithmetic logic units, multipliers, shifters, and other custom units) implement operations. The storage units (e.g., registers, register files, and memories) implement variables and arrays. The interconnection units (e.g., multiplexers and buses) connect the storage and functional components to transfer the signals [86]. Some resources may be added during scheduling or binding. Most hardware components are selected from the RTL component library, which also provides the characteristics, such as area, timing, and power,

Figure 2.4: An example of scheduling of the data flow graph from Fig. 2.2(b). The dotted lines represent discrete time steps. In this example, each operation is assumed to take a single time step.

of each component.

Resource constraints specify the maximum number of hardware resources, operations, functions, or IP cores. This may reduce the utilization of the specified resources, possibly reducing the area and increasing the latency.

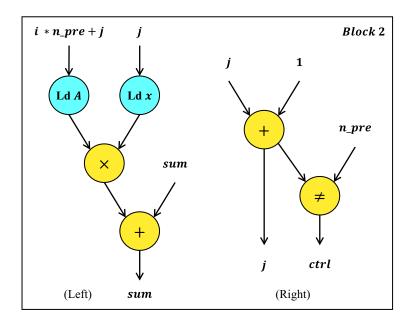

# Scheduling

Scheduling maps a set of operations in the formal model onto a set of discrete time steps (i.e., clock cycles) such that all data dependency constraints specified in the model are satisfied [23]. Fig. 2.4 shows an example of scheduling for the data flow graph in Fig. 2.2 (b). It is assumed that each operation in this example takes a single time step, but some functional units that implement certain operations may have longer latency. Additional constraints such as resource constraints, *latency constraints*, and the *length of a clock period* are also taken into account.

The main objectives of scheduling are to minimize the total number of time steps (i.e., overall latency), and to minimize the area or resource utilization. Area is a critical QoR for integrated circuits (such as ASICs), and resource utilization is important for reconfigurable

devices such as FPGAs. The scheduler exploits the component library (and the allocation results) to obtain the latency and area information of the components.

Two fundamental categories of scheduling approaches are time-constrained scheduling (to minimize the number of components) and resource-constrained scheduling (to minimize the overall latency) [85]. Since most HLS scheduling problems are NP-hard, schedulers often employ heuristic methods. Resource-constrained approaches include list-based scheduling [87] and static list scheduling, such as ASAP (as soon as possible) and ALAP (as late as possible) [88]. Time-constrained scheduling approaches include force-directed scheduling [89] and iterative refinement methods [90]. Other heuristic methods such as simulated annealing [91] and path-based scheduling [92] have been applied as well. Linear programming and integer linear programming methods formally formulate the scheduling problem [93], such as using a system of difference constraints [94]. For complex industrial scale designs, the solution space is too large and, therefore, a slack-based scheduling approach computes the sequential slack of each operation from the data flow graph and applies heuristic scheduling and binding by slack budgeting [95].

Design parameters applied during scheduling (and allocation) include resource constraints, latency constraints, the scheduling effort level, and the constraint relaxation levels. When the scheduler cannot find a feasible solution after the initial exploration (e.g., in a time limit), the scheduler employs a more time-consuming and compute-intensive method with a high scheduling effort, and relax some designer-specified constraints when constraint relaxation is allowed. Otherwise, it may notify the designer a schedule failure [81].

# **Binding**

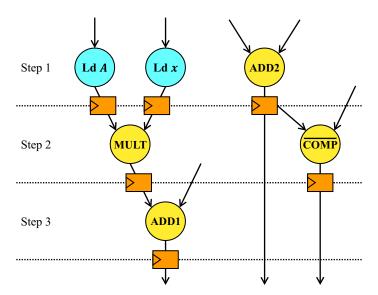

Binding maps each operation, variable, and interconnection in the scheduled model to a functional unit, storage unit, and interconnection unit, respectively, while maximizing resource sharing [86]. Fig. 2.5 illustrates an example of binding of the data flow graph scheduled in Fig. 2.4. The operation × is bound to a functional unit MULT. The two +

Figure 2.5: An example of binding of the data flow graph scheduled in Fig. 2.4. The operations are bound to functional units. Some variables are bound to registers, shown as the oranges boxes.

operations are bound to ADD1 (for fixed-point addition) and ADD2 (for integer addition), respectively. The operation ≠ is bound to a negated equality-comparator unit COMP. Multiple operations of the same type can be bound to a common functional unit if those operations are scheduled at different time steps. Each variable that carries values across the time steps is bound to a storage unit, such as a register. In Fig. 2.5, the orange boxes on the edges crossing a time step line represent the registers. Registers can also be shared among multiple variables with mutually exclusive lifetimes. Each transfer from component to component is bound to a interconnection unit, such as a bus or a multiplexer [86]. Due to the tight relationship among the problems, binding may occur concurrently or interleaved with scheduling and allocation [14, 86, 96, 97, 98].

# Generation

After allocation, scheduling, and binding, the decisions made in those steps are applied to generate an RTL description of the model written in a hardware description language (HDL) such as Verilog [12] or VHDL [13]. The RTL implementation contains the synthesized data path (consisting of the bound functional, storage, and interconnection components) and the

associated controller. The controller implements the control finite state machine, by typically using registers to store the current state and combinational logic to compute the next state based on the current state and the conditions coming from the data path [99]. Some parts of the data path may be left unbound after HLS; in this case, they are bound and optimized in the LS and PD stages, using more accurate and practical timing estimates [86].

After the HLS tool generates an RTL implementation, or many implementations using different configurations of the design parameters, one last subtask remains before the designer moves onto the LS stage: validation. Although the implementations generated by HLS tools should be functionally equivalent to the input specification by construction, it is important to perform validation to ensure that the implementation will function correctly and to eliminate any possible design errors [14]. This is especially critical in industrial design processes, where a large volume of expensive chips are manufactured from a single implementation. Validation can be performed by simulation and verification methods [100]. Since it is not the main focus of this dissertation, let us assume that Danny completes validation and starts the LS process.

# 2.2.2 Logic Synthesis

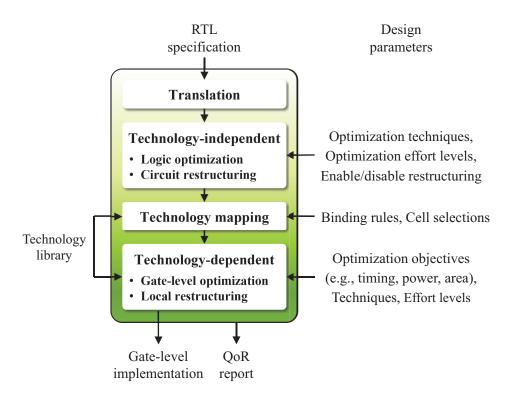

Fig. 2.6 illustrates a typical design process with LS. An LS tool takes in an RTL specification, either auto-generated from an HLS tool or provided by the designer, and transforms it into a gate-level implementation.

• Translation: The RTL specification (in a hardware description language such as Verilog or VHLD) is first translated into a technology-independent logic representation, such as finite state machines (for sequential components), Boolean functions (for combinational components), or logic networks (for mixed sequential and combinational components) [14].

For example, the negated equality-comparator unit  $\overline{\texttt{COMP}}$  in Fig. 2.5 takes in two inputs, namely L and R, and outputs f = 0 if L = R, and f = 1 if  $L \neq R$ . Assuming that each of U and V represents an unsigned binary number of 8 bits, the component  $\overline{\texttt{COMP}}$  can

Figure 2.6: A typical design process with an LS tool that translates an RTL specification into a gate-level implementation as guided by the design parameters.

be translated into a logic network that computes f as shown in Fig 2.7.  $L_n$  and  $R_n$  denote the bit value at index n ( $0 \le n \le 7$ ) of L and R, respectively. The XNOR gates at the first level determine whether a pair of bits at the same index of L and R are the same. The AND gate at the second level outputs 1 if all pairs match, and 0 otherwise. The NOT gate at the third level negates the output from the AND gate. Hence, the full network represents  $\overline{\text{COMP}}$ .

• Technology-independent optimization: The abstract logic representation is optimized with an objective of minimizing the complexity, e.g., in terms of the number of Karnaugh map implicants, logic gates, levels in logic networks, or states in finite state machines. The optimization methods have been investigated heavily over multiple decades for two-level combinational logic [101, 102, 103, 104], multi-level combinational logic [105, 106, 107], and sequential logic components [108, 109, 110, 111, 14]. As many of them are heuristic and iterative methods, advanced LS tools allow the

Figure 2.7: A logic representation of the negated equality-comparator unit  $\overline{\texttt{COMP}}$  in Fig. 2.5.