High Performance Silicon Photonic Interconnected Systems

Ziyi Zhu

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

2022

© 2022

Ziyi Zhu

All Rights Reserved

## Abstract

High Performance Silicon Photonic Interconnected Systems

#### Ziyi Zhu

Advances in data-driven applications, particularly artificial intelligence and deep learning, are driving the explosive growth of computation and communication in today's data centers and high-performance computing (HPC) systems. Increasingly, system performance is not constrained by the compute speed at individual nodes, but by the data movement between them. This calls for innovative architectures, smart connectivity, and extreme bandwidth densities in interconnect designs. Silicon photonics technology leverages mature complementary metal–oxide–semiconductor (CMOS) manufacturing infrastructure and is promising for low cost, high-bandwidth, and reconfigurable interconnects. Flexible and high-performance photonic switched architectures are capable of improving the system performance. The work in this dissertation explores various photonic interconnected systems and the associated optical switching functionalities, hardware platforms, and novel architectures. It demonstrates the capabilities of silicon photonics to enable efficient deep learning training.

We first present field programmable gate array (FPGA) based open-loop and closed-loop control for optical spectral-and-spatial switching of silicon photonic cascaded micro-ring resonator (MRR) switches. Our control achieves wavelength locking at the user-defined resonance of the MRR for optical unicast, multicast, and multiwavelength-select functionalities. Digital-to-analog converters (DACs) and analog-to-digital converters (ADCs) are necessary for the control of the switch. We experimentally demonstrate the optical switching functionalities using an FPGA-based switch controller through both traditional multi-bit DAC/ADC and novel single-wired DAC/ADC circuits. For system-level integration, interfaces to the switch controller in a network control plane are developed. The successful control and the switching functionalities achieved are essential for system-level architectural innovations as presented in the following sections.

Next, this thesis presents two novel photonic switched architectures using the MRR-based switches. First, a photonic switched memory system architecture was designed to address memory challenges in deep learning. The reconfigurable photonic interconnects provide scalable solutions and enable efficient use of disaggregated memory resources for deep learning training. An experimental testbed was built with a processing system and two remote memory nodes using silicon photonic switch fabrics and system performance improvements were demonstrated. The collective results and existing high-bandwidth optical I/Os show the potential of integrating the photonic switched memory to state-of-the-art processing systems. Second, the scaling trends of deep learning models and distributed training workloads are challenging network capacities in today's data centers and HPCs. A system architecture that leverages SiP switch-enabled server regrouping is proposed to tackle the challenges and accelerate distributed deep learning training. An experimental testbed with a SiP switch-enabled reconfigurable fat tree topology was built to evaluate the network performance of distributed ring all-reduce and parameter server workloads. We also present system-scale simulations. Server regrouping and bandwidth steering were performed on a large-scale tapered fat tree with 1024 compute nodes to show the benefits of using photonic switched architectures in systems at scale.

Finally, this dissertation explores high-bandwidth photonic interconnect designs for disaggregated systems. We first introduce and discuss two disaggregated architectures leveraging extreme high bandwidth interconnects with optically interconnected computing resources. We present the concept of rack-scale graphics processing unit (GPU) disaggregation with optical circuit switches and electrical aggregator switches. The architecture can leverage the flexibility of high bandwidth optical switches to increase hardware utilization and reduce application runtimes. A testbed was built to demonstrate resource disaggregation and defragmentation. In addition, we also present an extreme high-bandwidth optical interconnect accelerated low-latency communication architecture for deep learning training. The disaggregated architecture utilizes comb laser sources and MRR-based cross-bar switching fabrics to enable an all-to-all high bandwidth communication with a constant latency cost for distributed deep learning training. We discuss emerging technologies in the silicon photonics platform, including light source, transceivers, and switch architectures, to accommodate extreme high bandwidth requirements in HPC and data center environments. A prototype hardware innovation - Optical Network Interface Cards (comprised of FPGA, photonic integrated circuits (PIC), electronic integrated circuits (EIC), interposer, and high-speed printed circuit board (PCB)) is presented to show the path toward fast lanes for expedited execution at 10 terabits.

Taken together, the work in this dissertation demonstrates the capabilities of high-bandwidth silicon photonic interconnects and innovative architectural designs to accelerate deep learning training in optically connected data center and HPC systems.

## **Table of Contents**

| Acknow   | ledgme  | nts                                                                                | cii |

|----------|---------|------------------------------------------------------------------------------------|-----|

| Dedicati | ion     | x                                                                                  | iii |

| Chapter  | 1: Intr | oduction and Background                                                            | 1   |

| 1.1      | Deep I  | Learning Trends and Challenges                                                     | 1   |

| 1.2      | Silicor | Photonic Circuit Switching                                                         | 7   |

| 1.3      | Silicor | Photonic High Bandwidth Transceivers                                               | 10  |

| 1.4      | Scope   | of Dissertation                                                                    | 15  |

| Chapter  | 2: FP0  | GA-controlled Silicon Photonic Interconnects                                       | 17  |

| 2.1      | Introdu | $\mathbf{action}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 17  |

| 2.2      | Optica  | l Switching in Cascaded-MRR Switch                                                 | 18  |

| 2.3      | FPGA    | -Based Open Loop Control                                                           | 20  |

|          | 2.3.1   | System Architecture                                                                | 20  |

|          | 2.3.2   | Experimental Demonstration for Unicast and Multicast                               | 22  |

|          | 2.3.3   | Experimental Demonstration for Multiwavelength-select                              | 24  |

| 2.4      | FPGA    | Based Closed Loop Control                                                          | 26  |

|          | 2.4.1   | Closed-loop Single-wire DAC and ADC Architecture                                   | 27  |

|          | 2.4.2   | Experimental Setup                                                                 | 29  |

|         | 2.4.3 Results                                                    | 30 |

|---------|------------------------------------------------------------------|----|

| 2.5     | Chapter Summary                                                  | 33 |

| Chapter | 3: Optically Connected Memory for Deep Learning                  | 34 |

| 3.1     | Introduction                                                     | 34 |

| 3.2     | System Architecture                                              | 36 |

|         | 3.2.1 (de)Serialization of Memory Transfers                      | 38 |

|         | 3.2.2 Map to Local System Address Space                          | 39 |

|         | 3.2.3 SiP Switch Control                                         | 39 |

|         | 3.2.4 Accelerator Design                                         | 41 |

| 3.3     | Testbed                                                          | 42 |

| 3.4     | Experiment and Results                                           | 45 |

|         | 3.4.1 Optical Spectra                                            | 45 |

|         | 3.4.2 Eye Diagrams                                               | 47 |

|         | 3.4.3 Switching Time                                             | 48 |

|         | 3.4.4 End-to-end Reconfiguration Time                            | 49 |

|         | 3.4.5 Application and Execution Time                             | 50 |

| 3.5     | Discussion                                                       | 54 |

| 3.6     | Chapter Summary                                                  | 57 |

|         |                                                                  | -  |

| Chapter | 4: Photonic Switched Architectures for Distributed Deep Learning | 58 |

| 4.1     | Introduction                                                     | 58 |

| 4.2     | System Architecture and SiP Switch Control                       | 60 |

|         | 4.2.1 System Architecture                                        | 60 |

|         | 4.2.2  | SiP Switches and Control                        | 61 |

|---------|--------|-------------------------------------------------|----|

| 4.3     | Testbe | d                                               | 63 |

| 4.4     | Experi | ments and Results                               | 66 |

| 4.5     | System | n-scale Evaluation                              | 69 |

|         | 4.5.1  | Simulation Setup                                | 70 |

|         | 4.5.2  | Server Regrouping and Bandwidth Steering        | 71 |

|         | 4.5.3  | Results                                         | 72 |

| 4.6     | Chapte | er Summary                                      | 76 |

| Chapter | 5: Dis | aggregated Architectures for Deep Learning      | 77 |

| 5.1     |        | le Optically Interconnected Computing Resources |    |

|         | 5.1.1  | Introduction                                    |    |

|         |        |                                                 |    |

|         | 5.1.2  | System Architecture                             | /8 |

|         | 5.1.3  | Experimental Setup and Results                  | 80 |

|         | 5.1.4  | Conclusion                                      | 83 |

| 5.2     | SiPAC  | : Silicon Photonic Accelerated Compute Cluster  | 83 |

|         | 5.2.1  | Introduction                                    | 83 |

|         | 5.2.2  | Topology Design                                 | 85 |

|         | 5.2.3  | Wavelength Routing/Selection                    | 86 |

|         | 5.2.4  | Testbed Experiment                              | 88 |

|         | 5.2.5  | System-scale Simulation                         | 91 |

|         | 5.2.6  | Conclusion                                      | 93 |

| 5.3     | Chapte | er Summary                                      | 94 |

|           | 5.3.1    | Future V | Work      |         |      |      | • •  |      | •  |     | •    |    | • |     | • |     | • |     |     | • | • |    | • | 94  |

|-----------|----------|----------|-----------|---------|------|------|------|------|----|-----|------|----|---|-----|---|-----|---|-----|-----|---|---|----|---|-----|

| Chapter   | 6: Fast  | Lanes fo | or Exped  | ited E  | xec  | utio | n at | : 10 | Te | rat | oits | •  | • | ••  | • | ••  | • | • • | •   | • | • | •• | • | 96  |

| 6.1       | Introdu  | ction .  |           |         |      |      |      |      | •  |     | •    |    |   |     |   |     |   |     |     |   | • |    |   | 96  |

| 6.2       | ONIC N   | Module ( | Overview  | ·       |      |      |      |      |    |     |      |    | • |     |   |     |   |     | ••• |   | • |    | • | 97  |

|           | 6.2.1    | Overall  | Packagin  | ng Pla  | n.   |      |      |      |    |     |      |    | • |     |   |     |   |     | ••• |   | • |    | • | 97  |

|           | 6.2.2    | Link An  | alysis .  |         |      |      |      |      | •  | • • |      |    | • |     |   |     | • |     |     |   | • |    | • | 99  |

| 6.3       | Silicon  | Photonic | e Transce | eiver ( | Chip | ).   |      |      | •  |     |      |    | • |     | • |     | • |     |     |   | • |    | • | 100 |

| 6.4       | Develop  | pment of | O-NIC     | PCB     |      |      | •••  |      | •  |     | •    |    | • | • • |   |     |   |     |     |   | • |    | • | 103 |

| 6.5       | Test Pac | ckages   |           |         |      |      | •••  |      | •  |     | •    |    | • | • • |   |     |   |     |     |   | • |    | • | 104 |

|           | 6.5.1    | RX Test  | Package   |         |      |      | • •  |      | •  |     |      |    |   |     |   |     |   |     |     |   | • |    |   | 105 |

|           | 6.5.2    | TX Test  | Package   |         |      |      |      |      |    |     |      |    |   |     |   |     |   |     |     |   | • |    | • | 110 |

| 6.6       | PCIe In  | terface  |           |         |      |      |      |      | •  |     |      |    | • | ••• |   |     |   |     |     |   | • |    |   | 110 |

| 6.7       | Chapter  | r Summa  | ıry       |         |      |      |      |      | •  |     |      |    | • |     | • |     |   |     | ••• |   | • |    |   | 113 |

| Conclus   | ion      | ••••     |           | •••     | ••   | ••   | •••  | •••  | •  | ••  | •    | •• | • | ••  | • | ••  | • | • • | ••  | • | • |    | • | 114 |

| Reference | ces      |          |           | •••     |      | ••   | ••   |      | •  | ••  | •    | •• | • | ••  | • | ••• | • | • • | ••  | • | • | •• | • | 117 |

# List of Figures

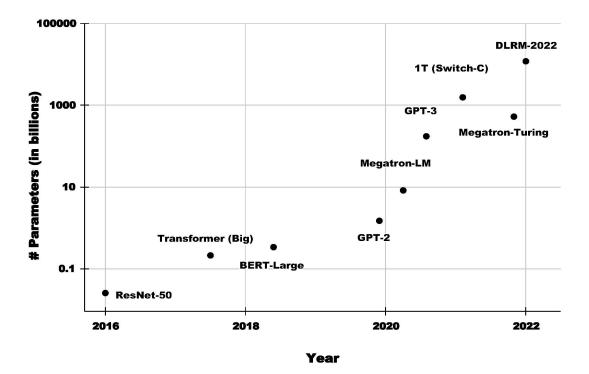

| 1.1  | Model Trend from 2016 to 2022                                                                                                                                                                                                                                                                                                                                                                   | 2  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

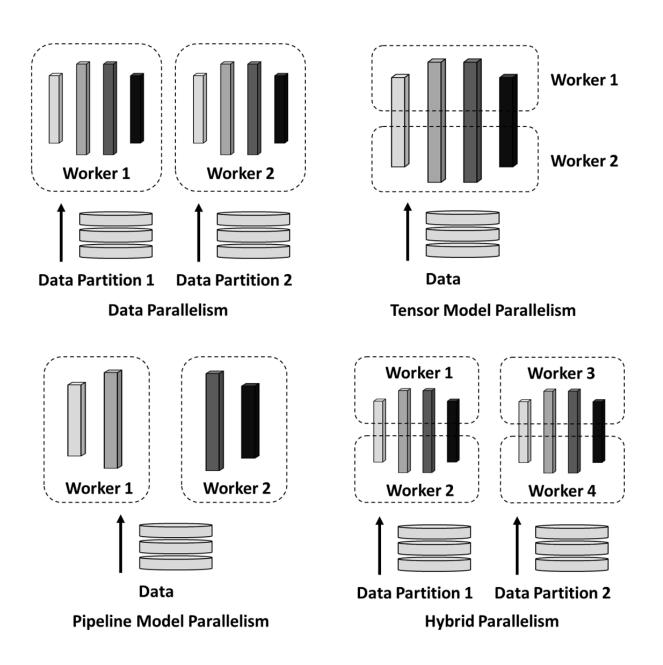

| 1.2  | Data parallelism, tensor model parallelism, pipeline model parallelism, and hybrid parallelism.                                                                                                                                                                                                                                                                                                 | 3  |

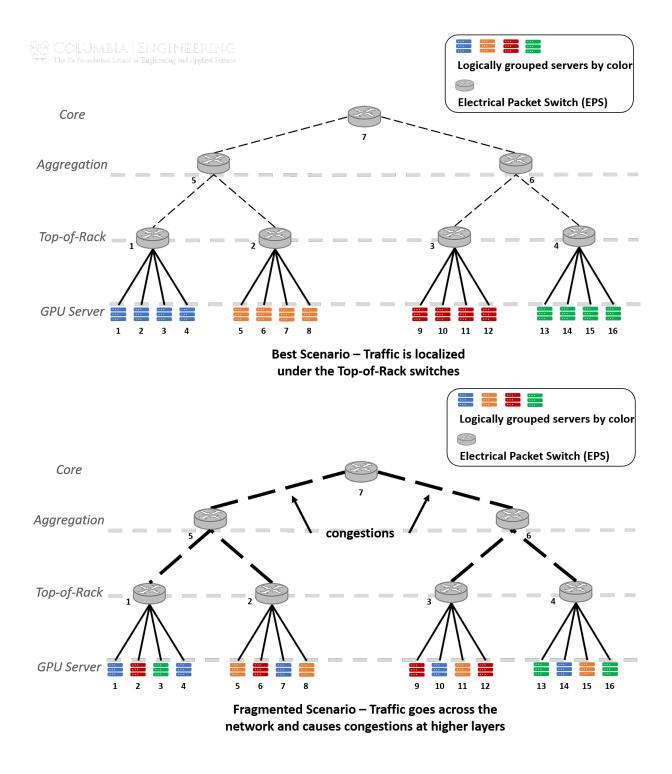

| 1.3  | Illustrations of localized nodes and fragmented nodes                                                                                                                                                                                                                                                                                                                                           | 5  |

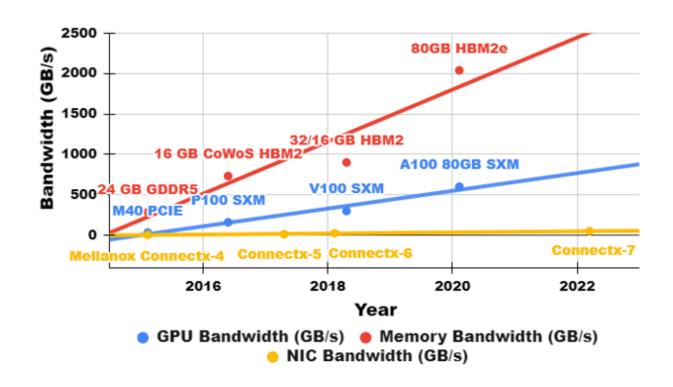

| 1.4  | Hardware bandwidth trend from 2015 to 2022                                                                                                                                                                                                                                                                                                                                                      | 6  |

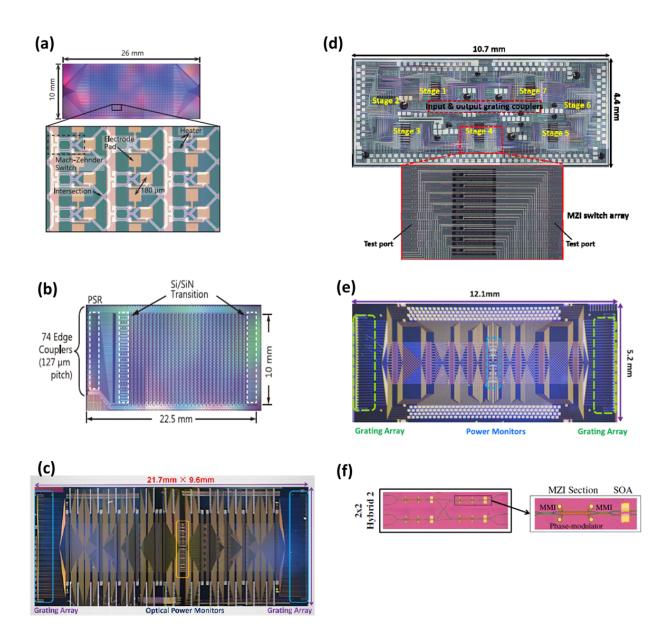

| 1.5  | (a) Low insertion loss $32 \times 32$ MZI switch, reprinted from [47]. (b) Polarization-<br>diversity $32 \times 32$ MZI switch, reprinted from [48]. (c) $64 \times 64$ T-O MZI switch,<br>reprinted from [49]. (d) $16 \times 16$ E-O MZI switch, reprinted from [50]. (e) $32 \times 32$ E-O MZI switch, reprinted from [51]. (f) Hybrid $2 \times 2$ MZI-SOA module,<br>reprinted from [52] | 8  |

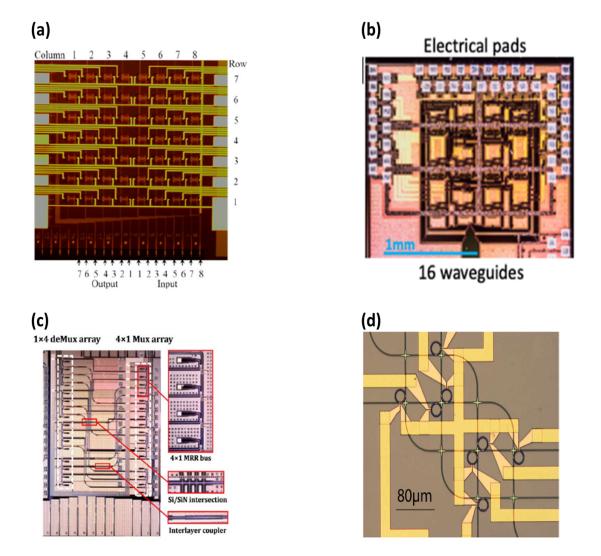

| 1.6  | (a) $8 \times 7$ cross-bar switch, reprinted from [53]. (b) $8 \times 8$ Omega switch, reprinted from [54]. (c) $4 \times 4$ switch-and-select switch, reprinted from [55]. (d) $4 \times 4$ hitless switch, reprinted from [56]                                                                                                                                                                | 9  |

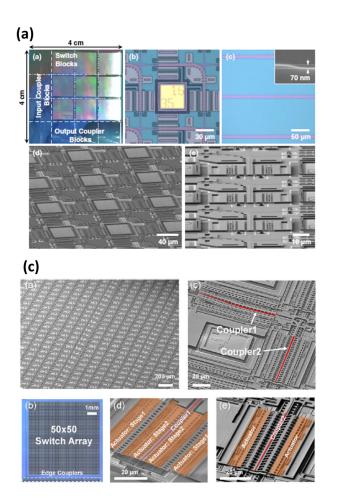

| 1.7  | (a) $240 \times 240$ MEMS cross-bar switch, reprinted from [60]. (b) Polarization-<br>Insensitive MEMS switch, reprinted from [61]. (c) $32 \times 32$ MEMS switch fab-<br>ricated in a commercial foundry, reprinted from [62].                                                                                                                                                                | 11 |

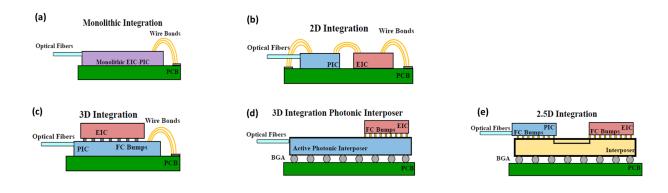

| 1.8  | The various integration approaches to integrate PICs with EICs. (a) Monolithic integration. (b) 2D integration. (c) 3D integration. (d) 3D integration with active photonic interposer. (e) 2.5D integration. Reprinted from [63].                                                                                                                                                              | 11 |

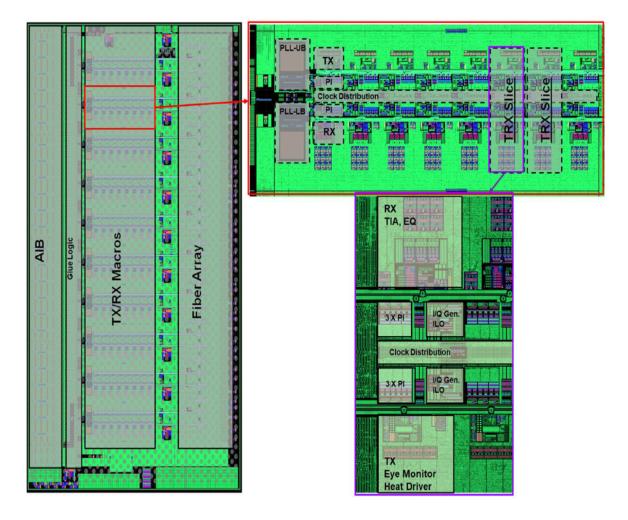

| 1.9  | TeraPHY chiplet showing optical Tx/Rx macros, fiber array, and Tx/Rx circuits.<br>Reprinted from [68].                                                                                                                                                                                                                                                                                          | 13 |

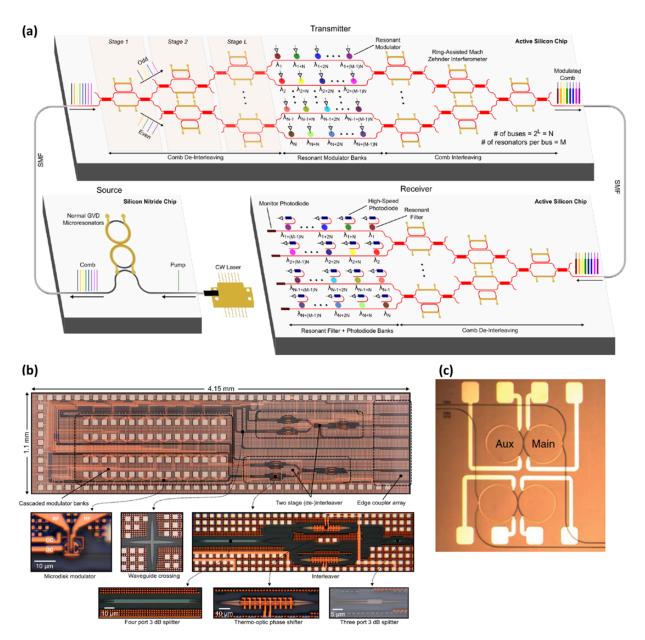

| 1.10 | (a) Schematic of the comb-driven transceiver architecture, reprinted from [69]. (b) Micrograph of the full die, reprinted from [69]. (c) Image of the Kerr comb device, reprinted from [70].                                                                                                                                                                                                    | 14 |

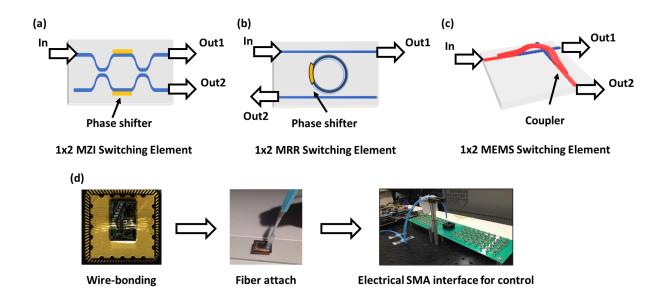

| 2.1  | (a) $1 \times 2$ MZI cell. (b) $1 \times 2$ MRR cell. (c) $1 \times 2$ MEMS-actuated coupler cell. (d) Packaging with wirebonding and fiber attachment                                                                                                              | 18 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

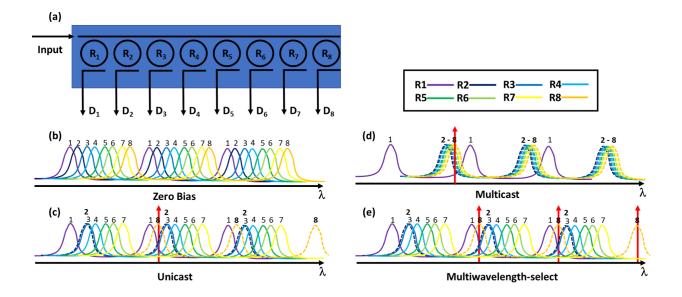

| 2.2  | (a) Switch architecture with 8 Cascaded MRRs. (b) Zero bias scenario. (c) Unicast scenario. (d) Multicast scenario. (e) Multiwavelength-select scenario                                                                                                             | 19 |

| 2.3  | Open-loop control scheme.                                                                                                                                                                                                                                           | 21 |

| 2.4  | <ul><li>(a) Tunable laser. (b) Schematic of the unicast and multicast experimental setup.</li><li>(c) FPGA-based switch controller and the packaged MRR switch on a PCB</li></ul>                                                                                   | 22 |

| 2.5  | Experimental results of 8 different cases including unicast, multicast, and broadcast.                                                                                                                                                                              | 23 |

| 2.6  | Schematic of the multiwavelength-select experimental setup                                                                                                                                                                                                          | 24 |

| 2.7  | Experimental results for multiwavelength-select operations                                                                                                                                                                                                          | 25 |

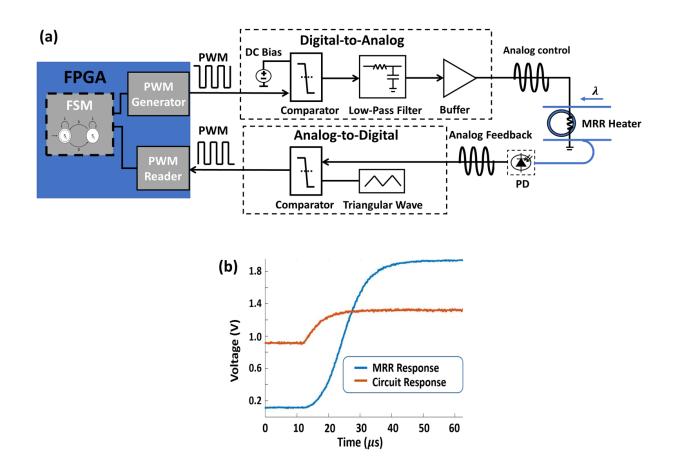

| 2.8  | (a) Schematic of digital-to-analog and analog-to-digital control and feedback (b)<br>Transient of digital-to-analog circuit response and MRR response due to a changed<br>duty cycle of the PWM control signal.                                                     | 27 |

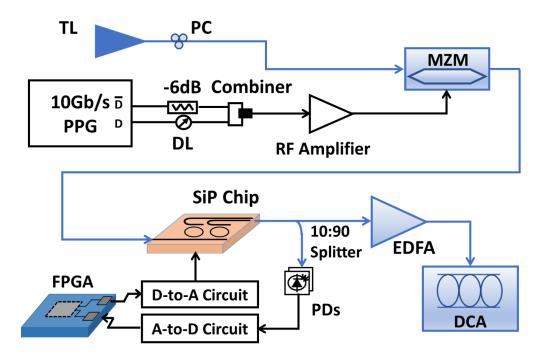

| 2.9  | Experimental setup demonstrating the single-wire ADC and DAC silicon photonic circuits evaluated with PAM-4 signal.                                                                                                                                                 | 29 |

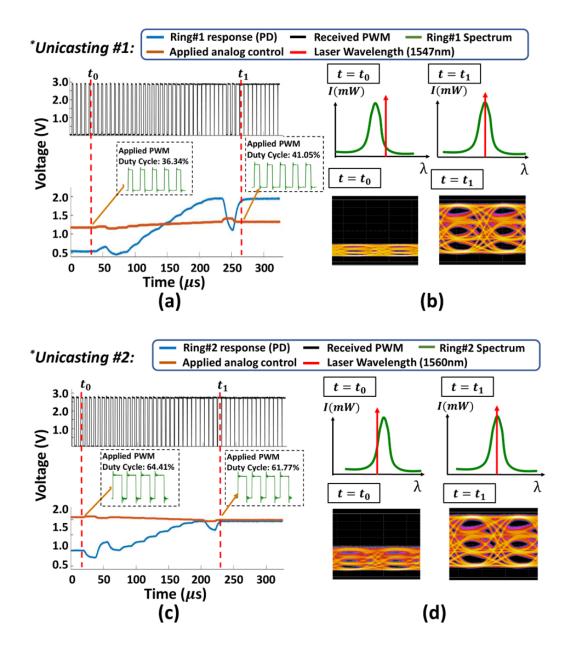

| 2.10 | (a) Transient responses for unicasting of MRR #1. (b) Corresponding spectrums and eye diagrams of MRR #1 before and after tuning. (c) Transient responses for unicasting of MRR #2. (d) Corresponding spectrums and eye diagrams of MRR #2 before and after tuning. | 30 |

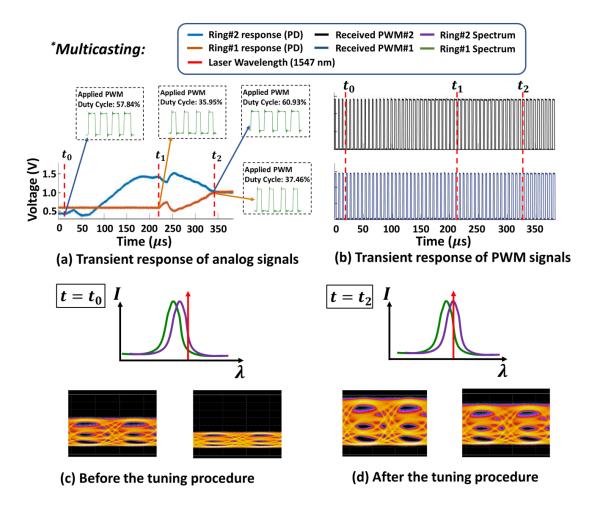

| 2.11 | (a) Optical transient before and after the feedback tuning procedure for multicast-<br>ing. (b) Received PWM transient. (c) Corresponding spectrum and eye diagrams<br>before the tuning procedure. (d) Corresponding spectrum and eye diagrams after<br>tuning     | 32 |

|      |                                                                                                                                                                                                                                                                     |    |

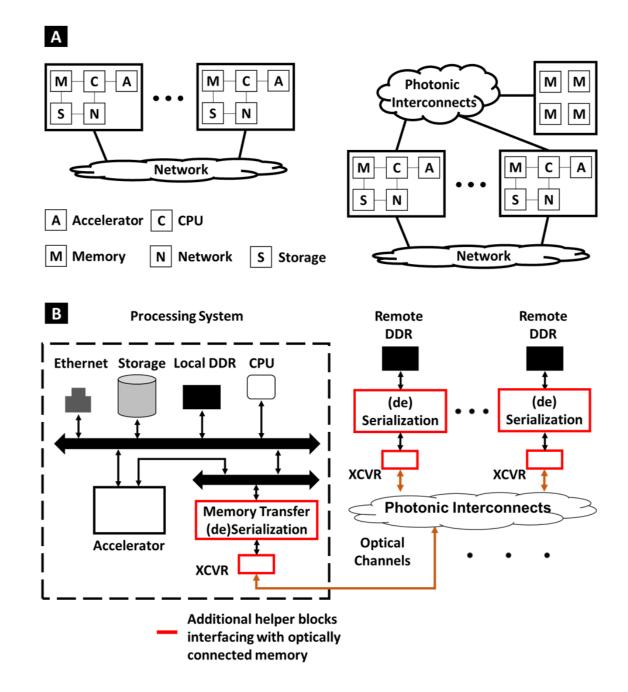

| 3.1 | (A) On the left, the traditional system architecture with each processing system composed of preconfigured and fixed CPU, memory, storage, accelerator and network resources. In our proposed system architecture, on the right, each processing system using optical I/Os is also connected to a remote memory pool through photonic interconnects. (B) Detailed implementation of photonic switched system architecture with optically connected memory. The processing system includes additional (de)serialization and transceiver (XCVR) helper blocks for (de)serializing memory mapped transactions being transmitted through optical links. On the right, remote double date rate synchronous dynamic random-access memory (DDR) nodes, are also equipped with the (de)serialization and XCVR helper blocks, and the photonic interconnects physically connect remote memory nodes to the processing system. | 37 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

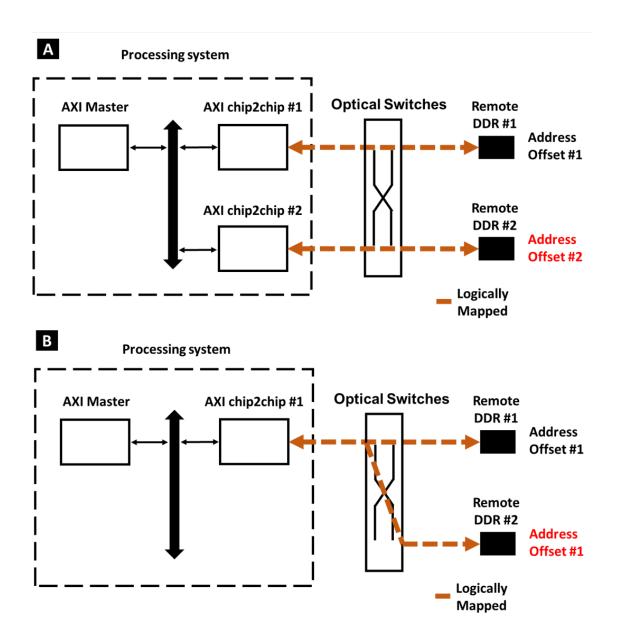

| 3.2 | (A) An example of case 1, two remote memory resources mapped to two AXI chip2chip cores in the local processing system for the unswitched case after the resources are assigned. Each chip2chip core is assigned with a unique memory address offset (B) An example of case 2, the switching case. Both remote DDR #1 and remote DDR #2 are mapped to the AXI chip2chip #1 in the processing system. They share the same memory address offset                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 40 |

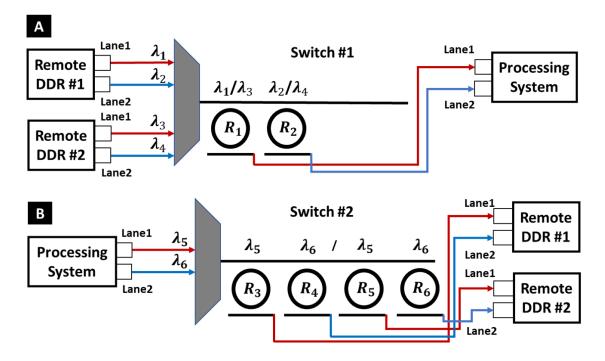

| 3.3 | SiP switches' configurations for the dynamic access to remote DDRs. (A) Remote memory resources to the processing system direction. (B) The processing system to remote memory resources direction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 42 |

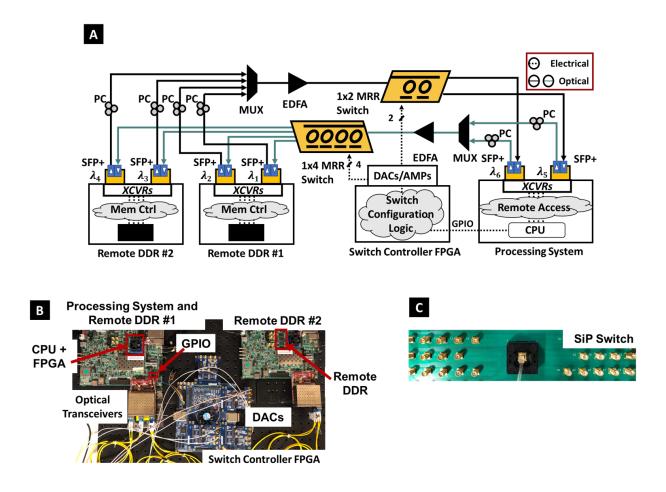

| 3.4 | (A) Experimental setup demonstrating a case of photonic switched optically con-<br>nected memory system with dynamic allocation of remote DDR resources to the<br>processing system. (B) Key hardware components. One Xilinx ZCU106 board<br>containing the processing system and the remote DDR #1 nodes, another ZCU106<br>board containing only the remote DDR #2 node, and the TR4 switch controller<br>FPGA board. (C) A packaged SiP MRR based switch with electrical SMA interface.                                                                                                                                                                                                                                                                                                                                                                                                                           | 44 |

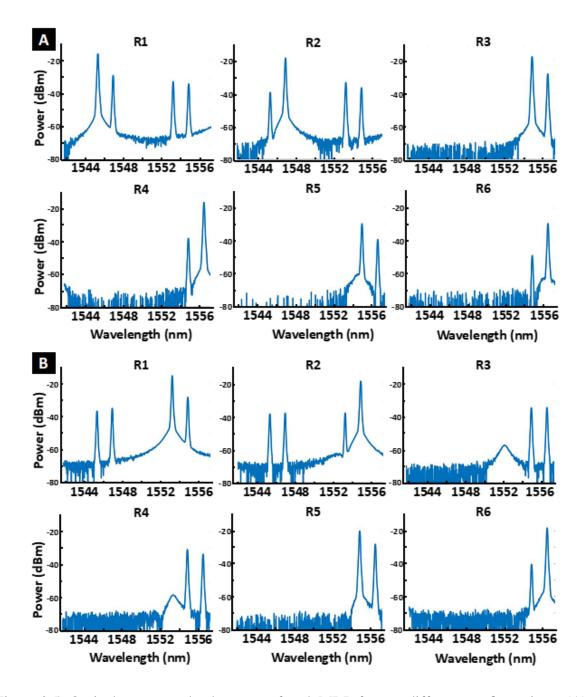

| 3.5 | Optical spectra at the drop port of each MRR for two different configurations. (A) Two SiP switches configured as the processing system connecting to the remote DDR #1 node. (B) Two SiP switches configured as the processing system connecting to the remote DDR #2 node. (In this figure, the MRR numbers are consistent with the MRR numbers shown in Fig. 3.3.).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46 |

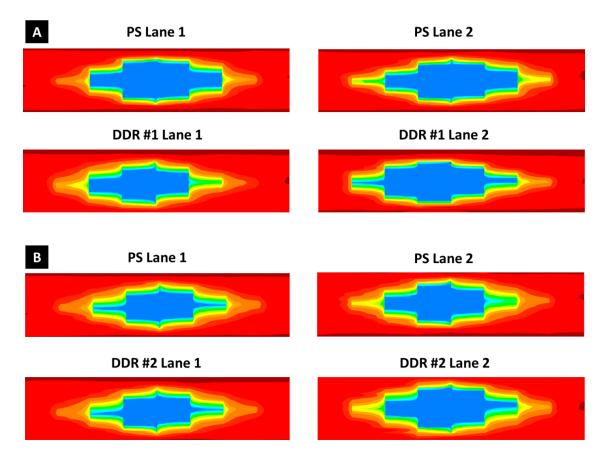

| 3.6 | Screen shots of open eye diagrams of connected receiver ports at 10 Gb/s PRBS-<br>31. (A) Two SiP switches configured as the processing system (PS) connecting<br>to the remote DDR #1 node. (B) Two SiP switches configured as the processing<br>system connecting to the remote DDR #2 node                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47 |

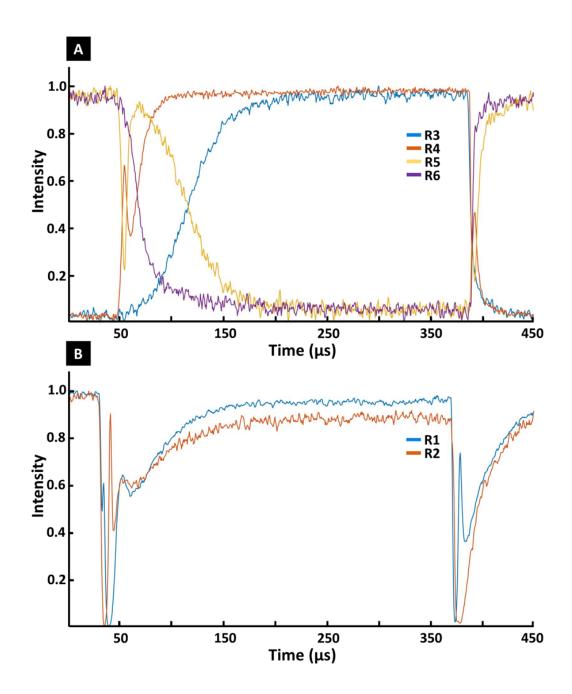

| 3.7  | Screen shots of open eye diagrams of connected receiver ports at 10 Gb/s PRBS-<br>31. (A) Two SiP switches configured as the processing system (PS) connecting<br>to the remote DDR #1 node. (B) Two SiP switches configured as the processing<br>system connecting to the remote DDR #2 node                                     | 48 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

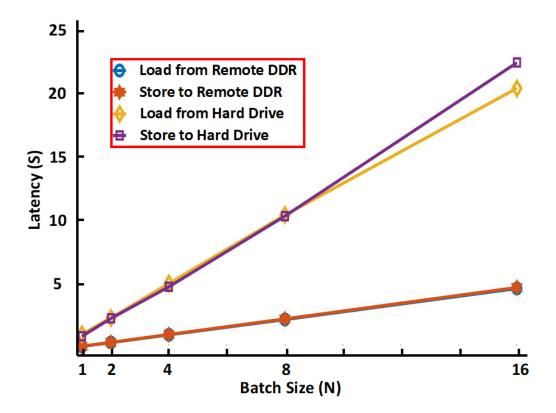

| 3.8  | Loading/storing latencies using hard drive and remote DDR memory of different batch sizes.                                                                                                                                                                                                                                        | 51 |

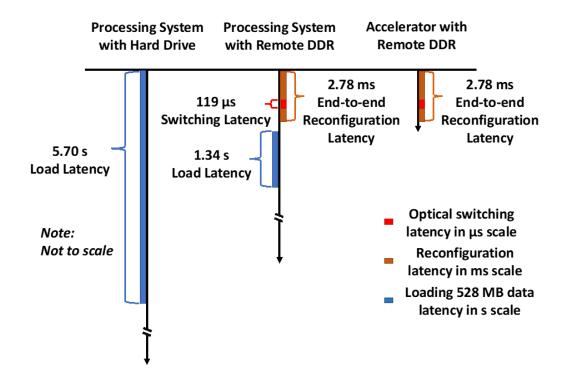

| 3.9  | Timelines comparing system latencies in different scenarios for switching case #2                                                                                                                                                                                                                                                 | 54 |

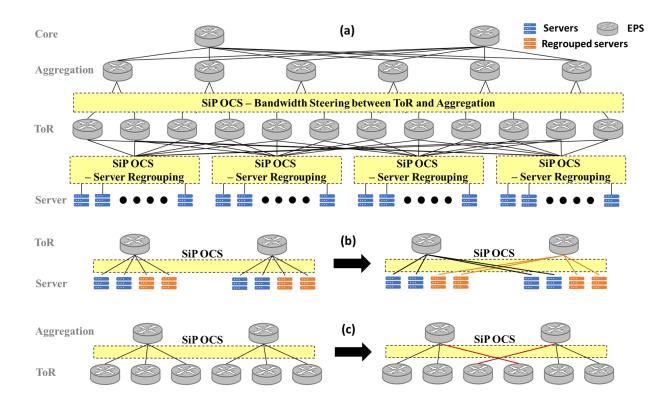

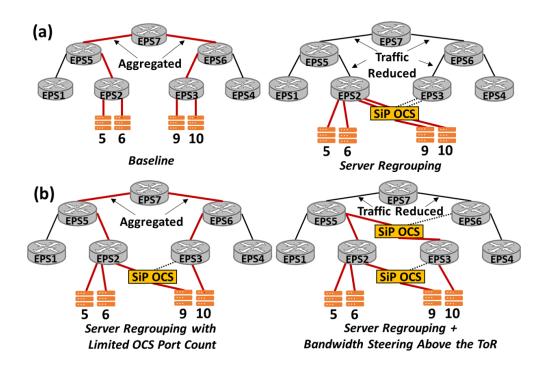

| 4.1  | (a) System architecture demonstration with server nodes arranged in the fat tree topology to show SiP switch-based server regrouping and higher-layer bandwidth steering. (b) An example of before (left) and after (right) server regrouping. (c) An example of before (left) and after (right) bandwidth steering above the ToR | 60 |

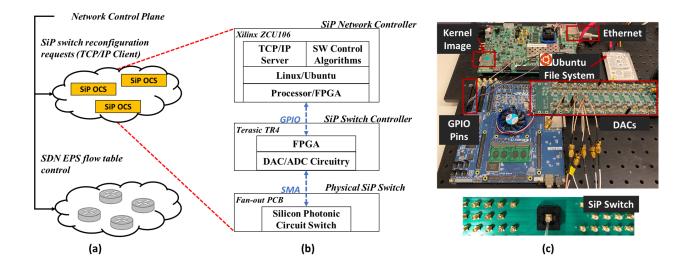

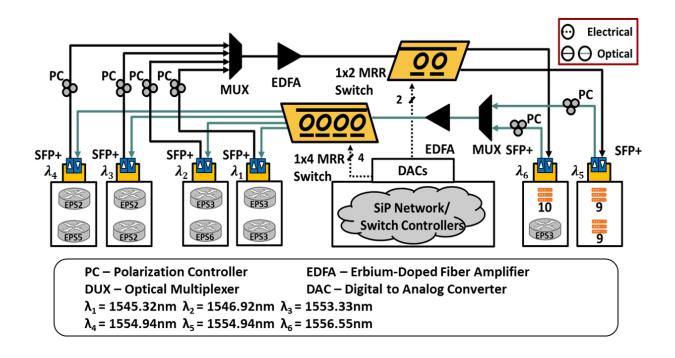

| 4.2  | (a) Overall network control plane. (b) SiP OCS subsystem including the SiP network controller, SiP switch controller, and SiP switches. (c) The SiP network controller board (ZCU106), SiP switch controller board (TR4), and PCB holding a packaged SiP switch.                                                                  | 61 |

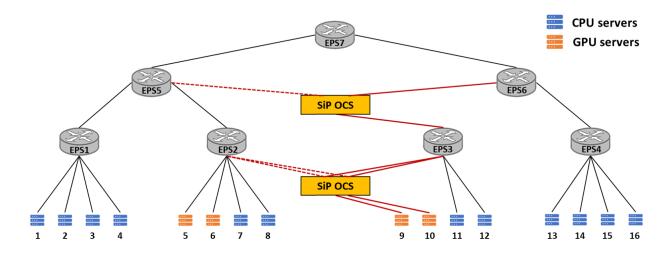

| 4.3  | A 16-node experimental testbed with SiP OCSs and EPSs in a reconfigurable fat tree topology.                                                                                                                                                                                                                                      | 62 |

| 4.4  | Experimental setup demonstrating the cases of server regrouping and bandwidth steering above the ToR.                                                                                                                                                                                                                             | 63 |

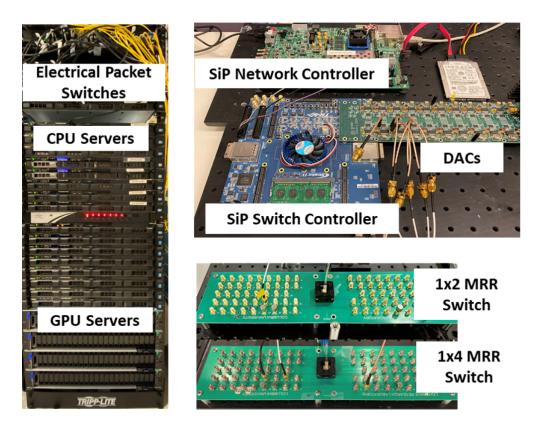

| 4.5  | A photograph of EPSs, CPU servers, GPU servers, SiP switches, SiP network con-<br>troller, and SiP switch controller.                                                                                                                                                                                                             | 64 |

| 4.6  | A photograph of EPSs, CPU servers, GPU servers, SiP switches, SiP network con-<br>troller, and SiP switch controller.                                                                                                                                                                                                             | 65 |

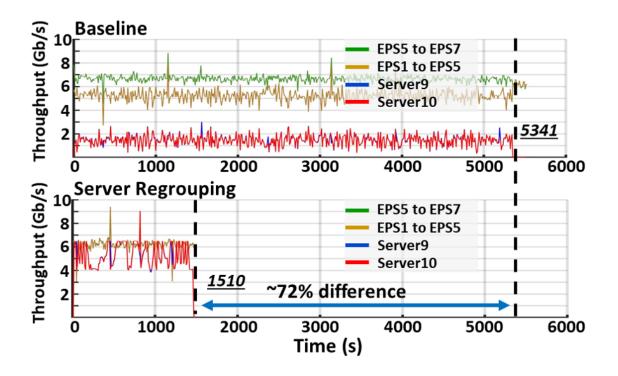

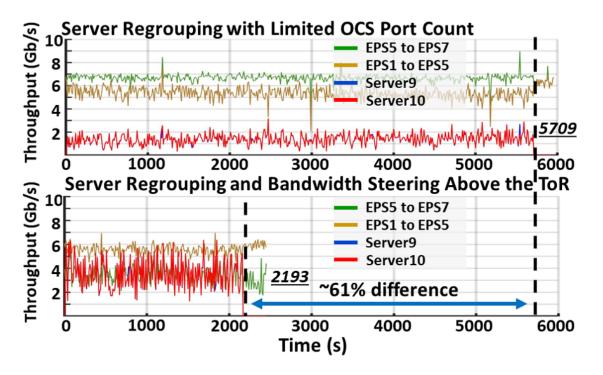

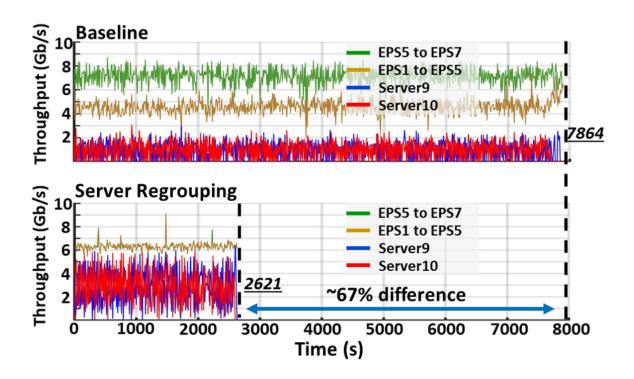

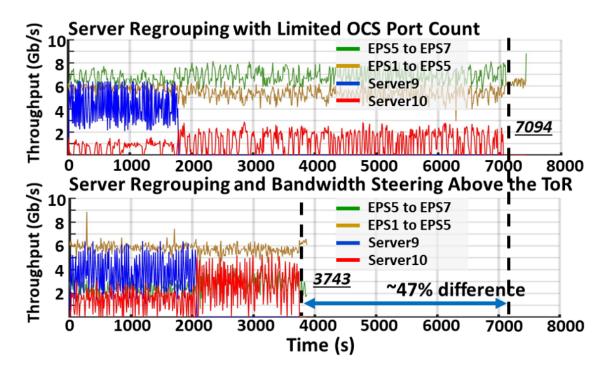

| 4.7  | Throughput of the links to server #9 and #10, from EPS #1 to EPS #5, and from EPS #5 to EPS #7 for test case #1 in the synchronized training of the VGG neural network.                                                                                                                                                           | 67 |

| 4.8  | Throughput of the links for the test case #2 in the synchronized training                                                                                                                                                                                                                                                         | 67 |

| 4.9  | Throughput of the links for the test case #1 in the asynchronized training                                                                                                                                                                                                                                                        | 68 |

| 4.10 | Throughput of the links for the test case #2 in the asynchronized training                                                                                                                                                                                                                                                        | 68 |

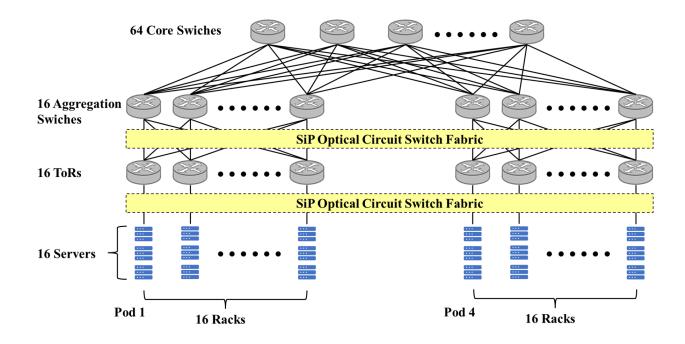

| 4.11 | A 1024-node untapered fat tree topology with SiP OCSs in between the server-ToR and ToR-aggregation layers.                                                                                                                                                                                                                       | 70 |

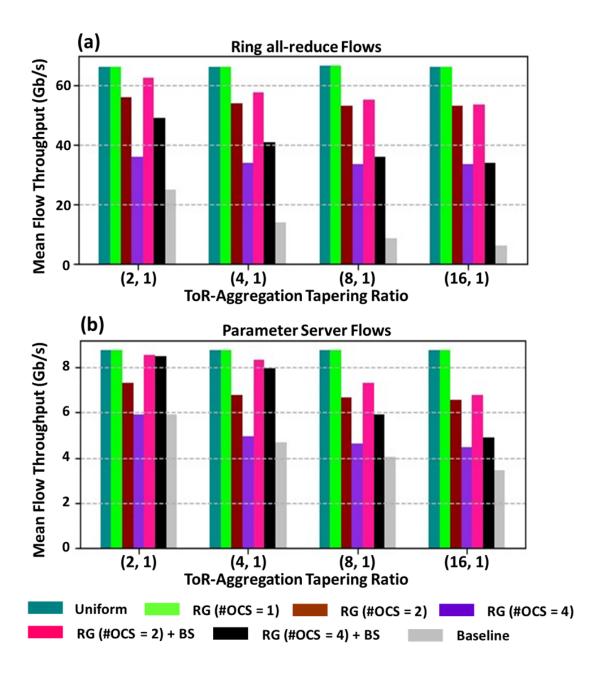

| 4.12 | Average flow throughput of all the flows as a function of the tapering ratio for all the traffic and job mapping scenarios. RG denotes regrouping and BS denotes higher-layer bandwidth steering. With the exception of Uniform (uniform job-mapping), all other cases assume an adversarial interpod job mapping as described in the Simulation Setup Section. (a) Results for ring all-reduce flows. (b) Results for parameter server flows. | 74 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

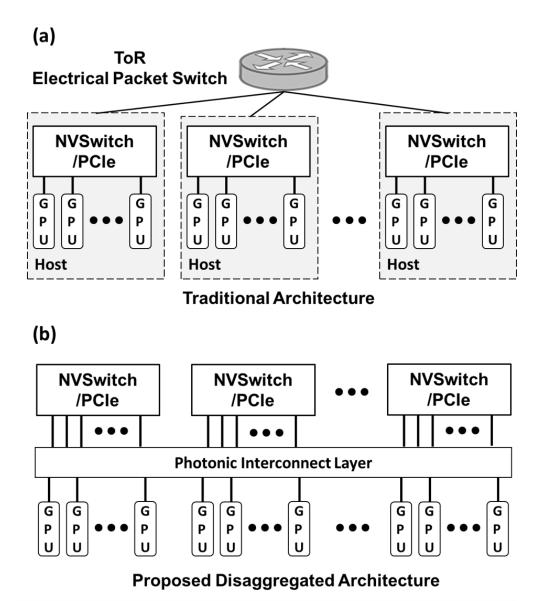

| 5.1  | (a) Traditional architecture for GPU clusters. (b) Proposed system architecture for disaggregated GPU resources.                                                                                                                                                                                                                                                                                                                               | 78 |

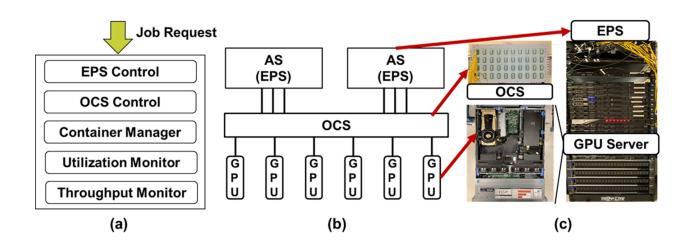

| 5.2  | (a) Network control plane. (b) Testbed architecture. (c) Hardware implementations using Calient MEMS switch, server rack with ToR switch and rack server                                                                                                                                                                                                                                                                                       | 79 |

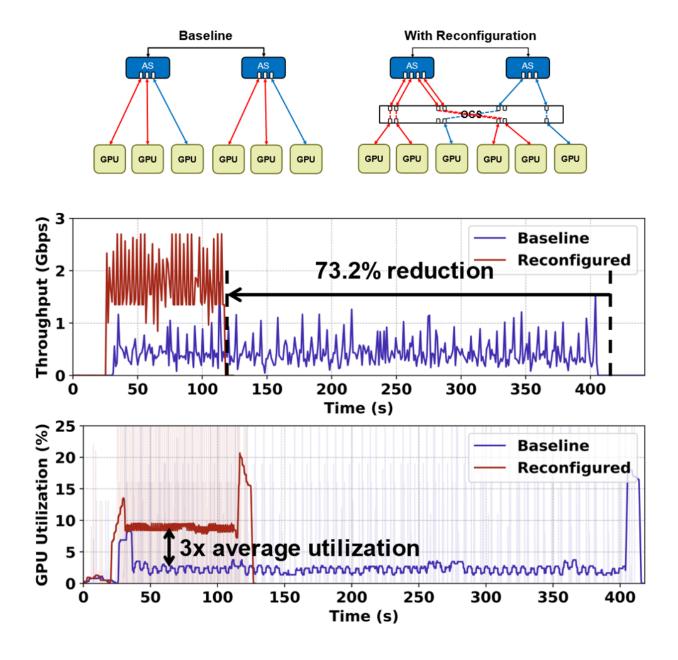

| 5.3  | Testbed topology for two synchronous ML workload using 4 GPUs and 2 GPUs for training. Experimental results that show network performance and utilization improvements.                                                                                                                                                                                                                                                                        | 81 |

| 5.4  | Testbed topology for two synchronous ML workload using 3 GPUs and 3 GPUs for training. Experimental results that show network performance and utilization improvements.                                                                                                                                                                                                                                                                        | 82 |

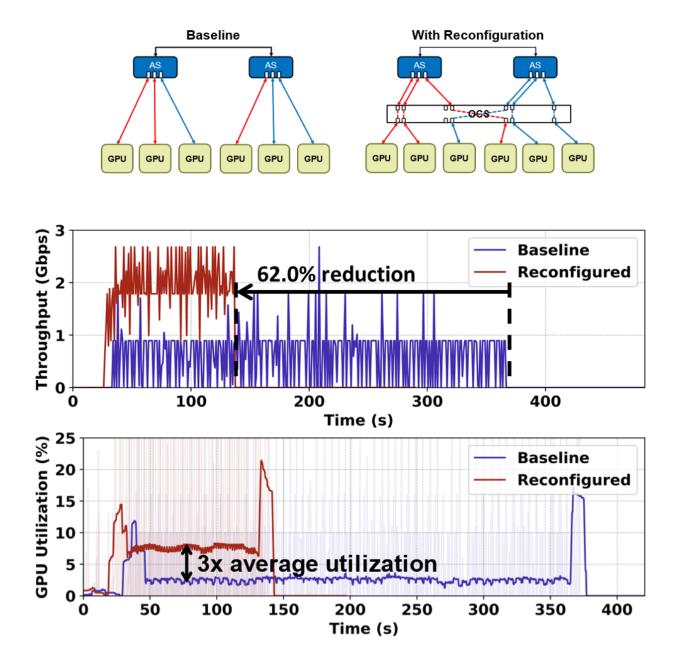

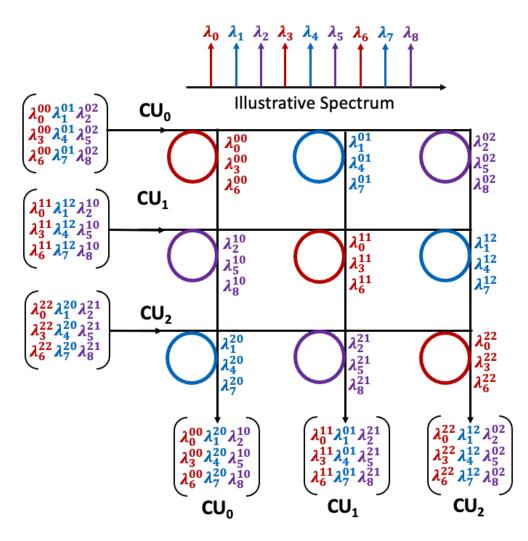

| 5.5  | a) SiPAC architecture based on the recursive BCube topology with $L = l + 1$ levels.<br>The <i>l</i> th level is constructed from $r^l$ <i>r</i> -port switches and $r$ ( $l - 1$ )th level units. b)<br>The base unit of the SiPAC topology where <i>r</i> CUs are connected to a WSS                                                                                                                                                         | 85 |

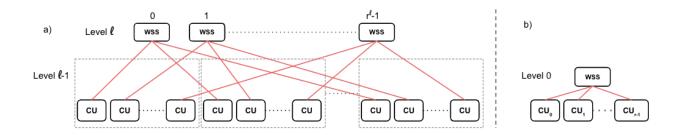

| 5.6  | Example of wavelength multiplexing for a $3 \times 3$ multi-WSS and 8 wavelengths per transmitter ( $w = 8$ ).                                                                                                                                                                                                                                                                                                                                 | 87 |

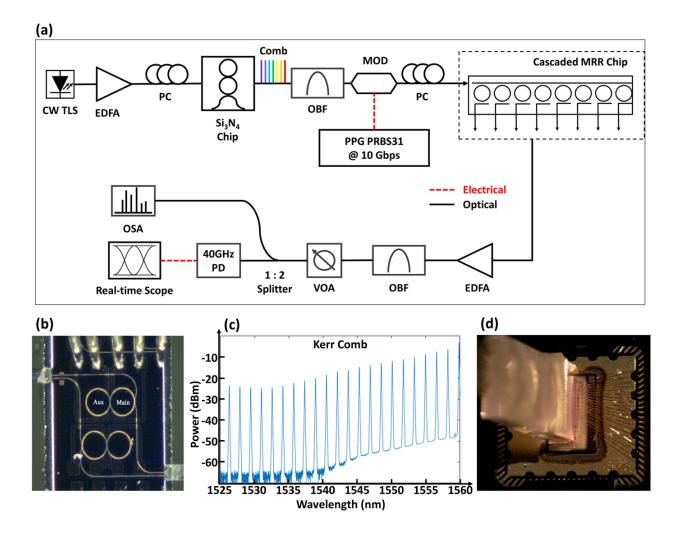

| 5.7  | <ul> <li>(a) Experimental setup for the comb laser. (b) Micrograph of Kerr comb source.</li> <li>(c) Output of Kerr Comb source. (d) Micrograph of packaged 1 × 8 microring resonantor switch.</li> </ul>                                                                                                                                                                                                                                      | 88 |

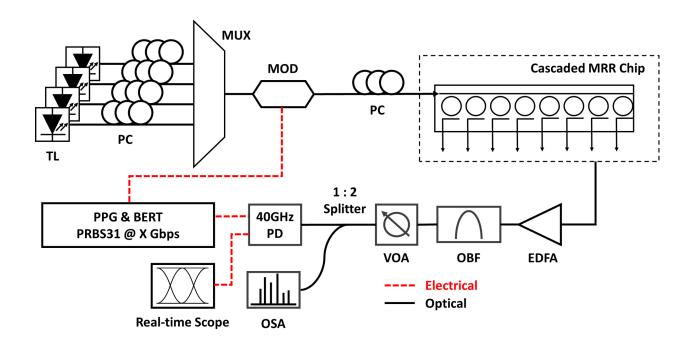

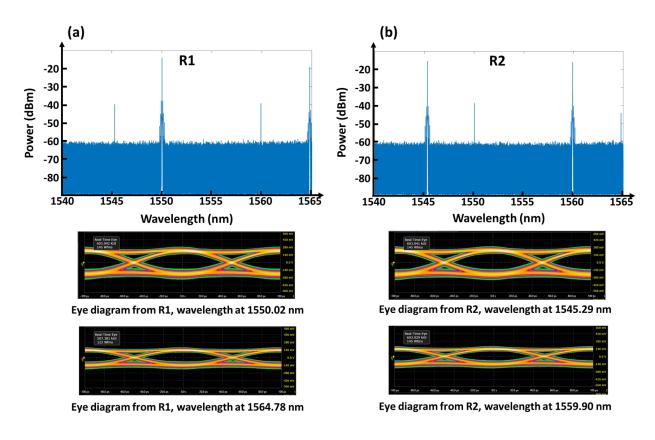

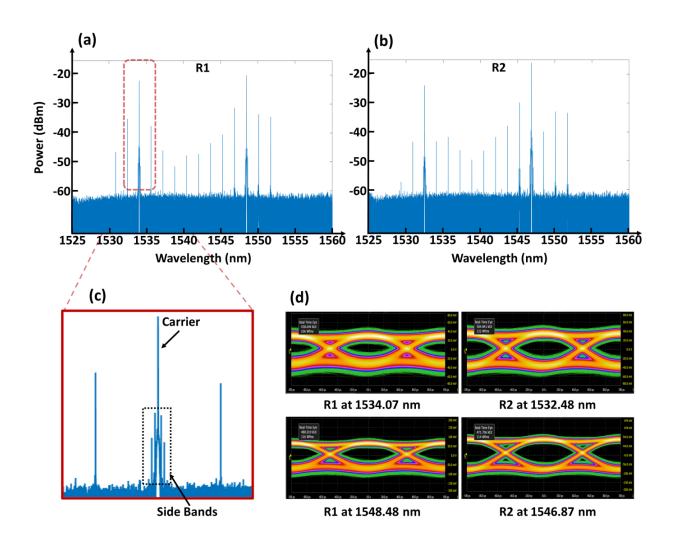

| 5.8  | (a) Output spectrum of Ring 1. (b) Output spectrum of Ring 2. (c) Inset of (a), illus-<br>trating the sidebands surrounding the modulated carrier. (d) Output eye-diagrams<br>of dropped signals.                                                                                                                                                                                                                                              | 90 |

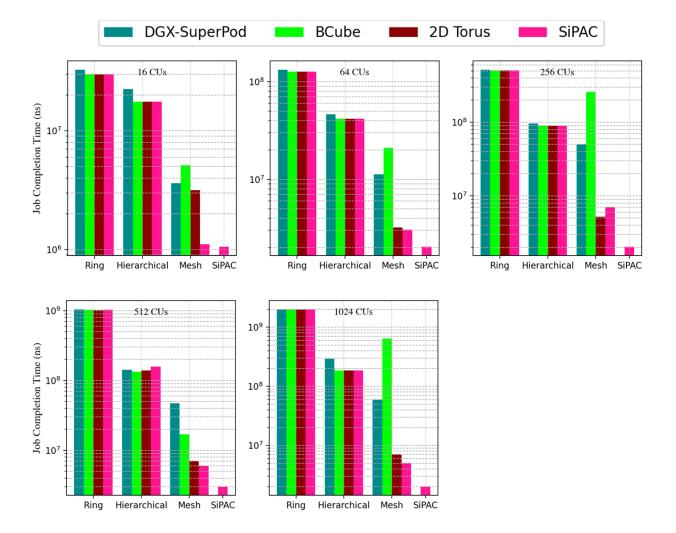

| 5.9  | Job completion time of different topology-collective combinations for varying net-<br>work sizes. The message size is set to be 1MB.                                                                                                                                                                                                                                                                                                           | 92 |

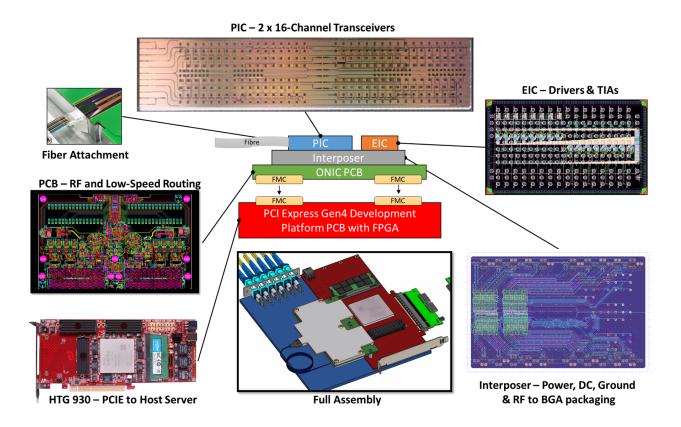

| 6.1  | FLEET hardware overview, reprinted from [141].                                                                                                                                                                                                                                                                                                                                                                                                 | 97 |

| 6.2  | FLEET O-NIC packaging plan.                                                                                                                                                                                                                                                                                                                                                                                                                    | 98 |

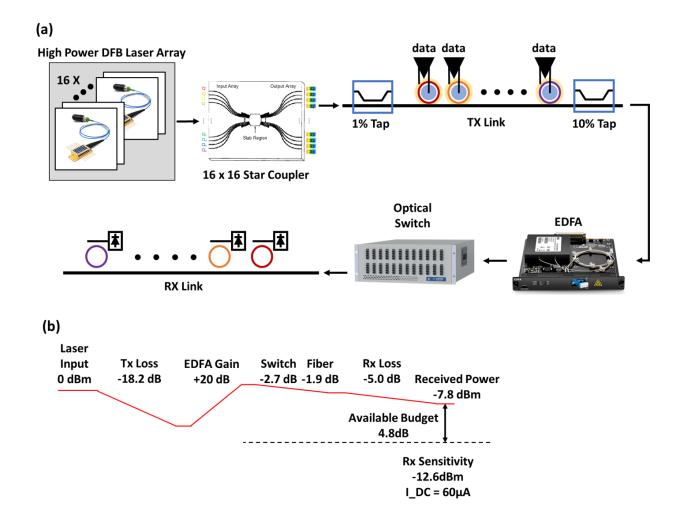

| 6.3  | FLEET O-NIC link and power budget                                                                                                                                   |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

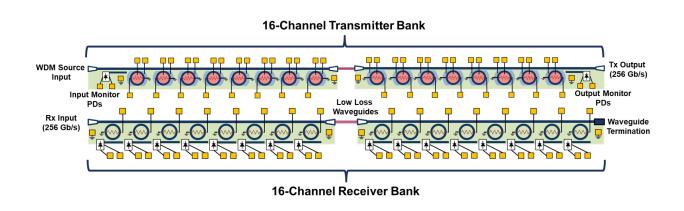

| 6.4  | FLEET PIC transmitter and receiver banks                                                                                                                            |

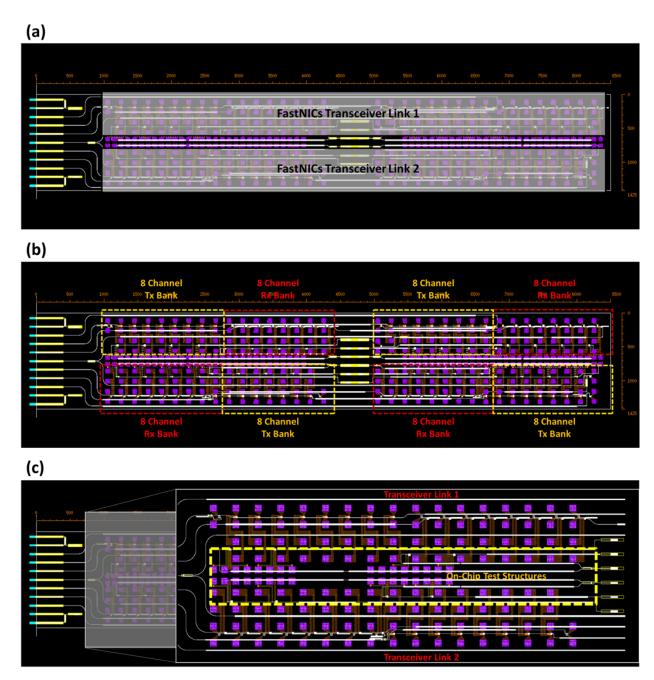

| 6.5  | FLEET PIC floor plan. (a) The two 16-channel transceiver links. (b) The transmitter and receiver banks. (c) Two 8-channel transceiver banks and test structures 101 |

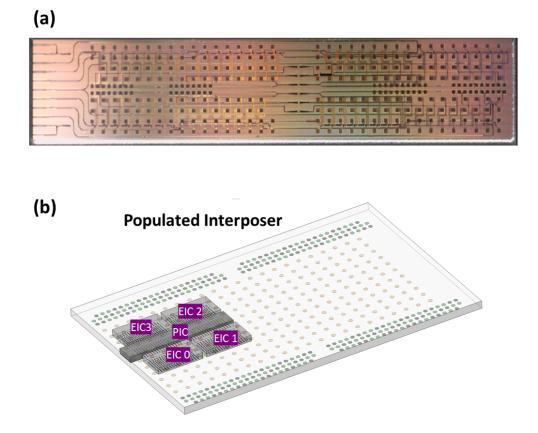

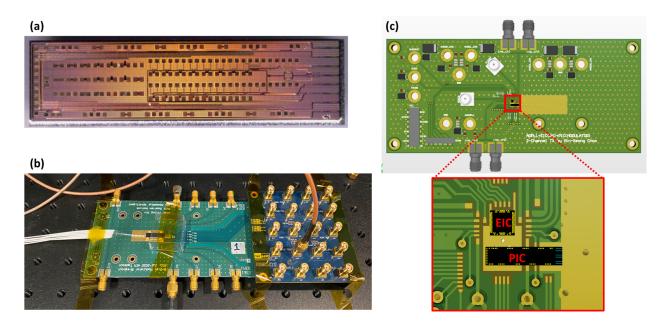

| 6.6  | (a) FLEET PIC chip.(b) Illustration of a populated interposer                                                                                                       |

| 6.7  | (a) FLEET PIC chip.(b) Illustration of a populated interposer                                                                                                       |

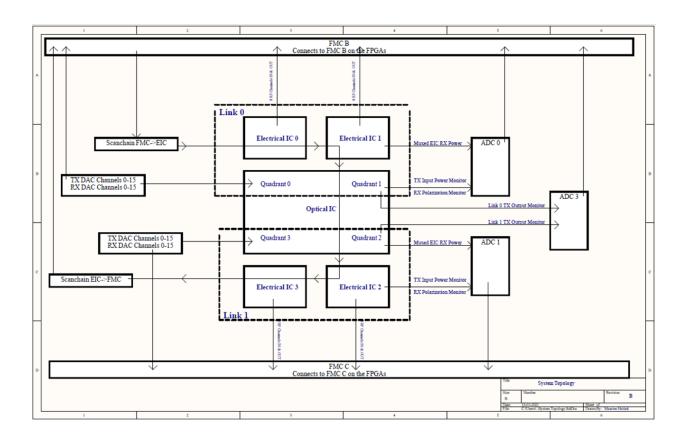

| 6.8  | FLEET O-NIC PCB layout                                                                                                                                              |

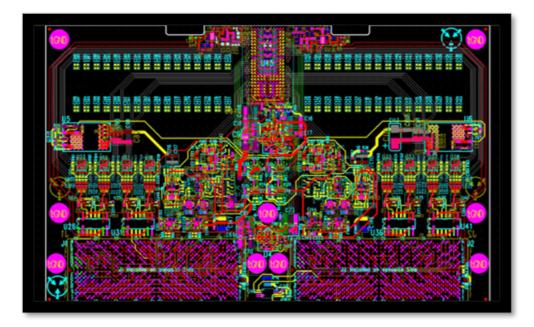

| 6.9  | FLEET RX test PIC chip and packaging plan                                                                                                                           |

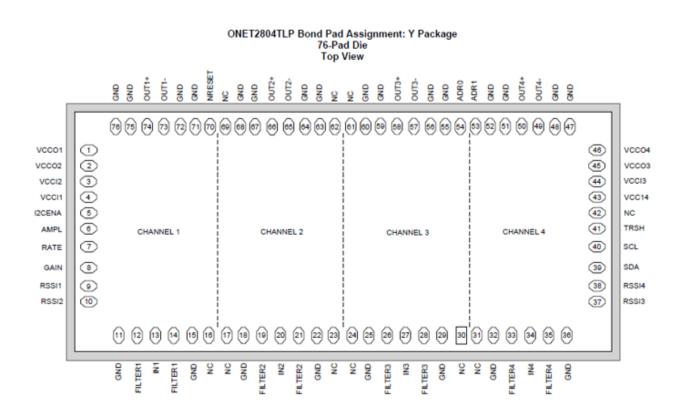

| 6.10 | TIA bond pad assignment                                                                                                                                             |

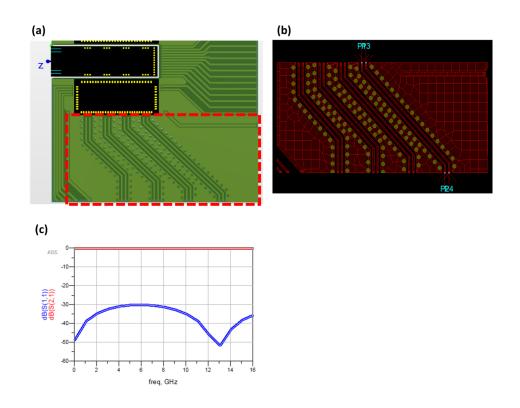

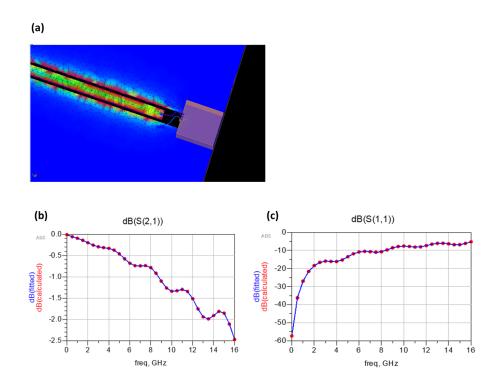

| 6.11 | (a) Interposer differential traces. (b) ADS layout model. (c) $S_{21}$ and $S_{11}$ results. $\ . \ . 107$                                                          |

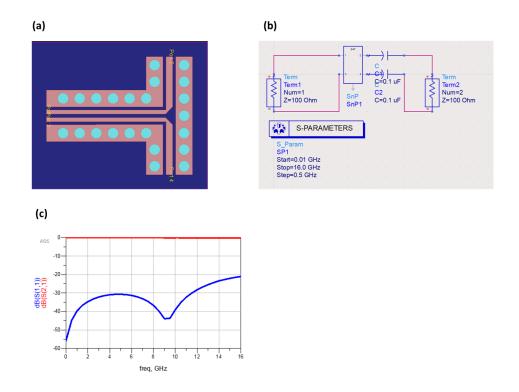

| 6.12 | (a) ADS layout model for PCB differential to single ended traces. (b) ADS circuit model. (c) $S_{21}$ and $S_{11}$ results                                          |

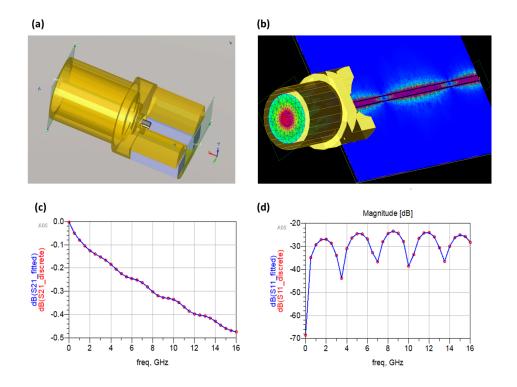

| 6.13 | <ul> <li>(a) ADS EMPro edge sma model. (b) 3D model with landing trace. (c) S<sub>21</sub> result.</li> <li>(d) S<sub>11</sub> result</li></ul>                     |

| 6.14 | (a) ADS 3D wirebonds model. (b) $S_{21}$ result. (c) $S_{11}$ result                                                                                                |

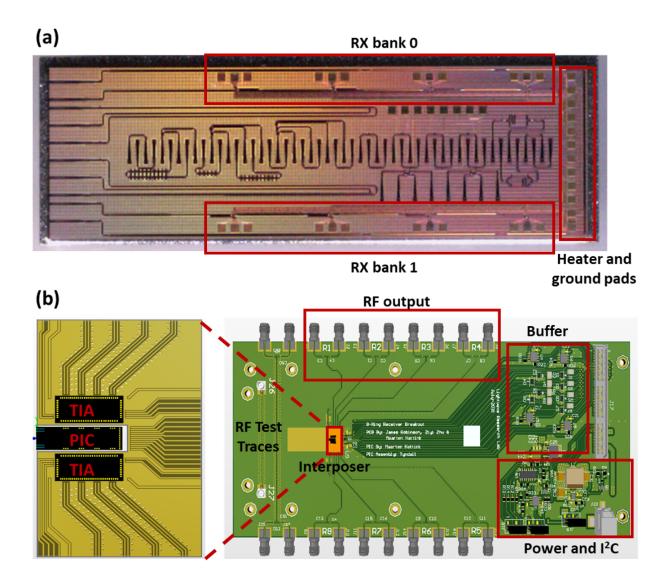

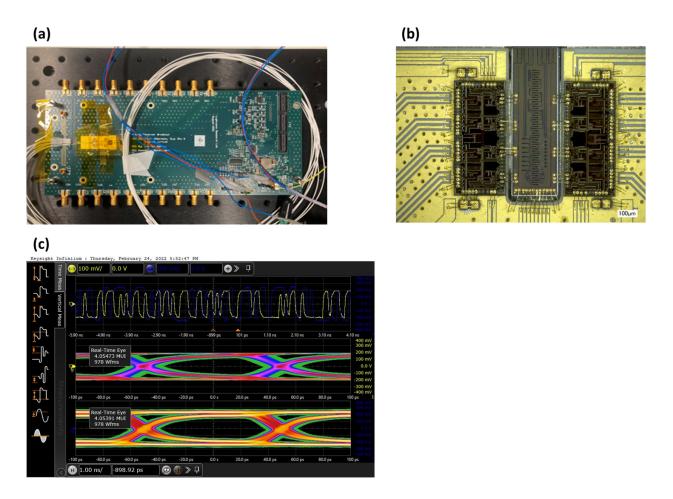

| 6.15 | (a) RX test package full assembly. (b) Wire-bonding picture. (c) Eye diagrams 109                                                                                   |

| 6.16 | (a) TX test PIC chip. (b) TX test board. (c) Packaging plan with a driving EIC 110                                                                                  |

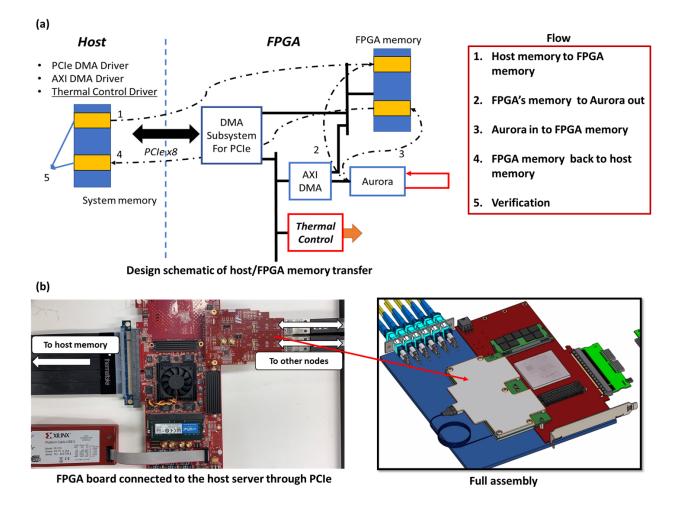

| 6.17 | (a) Schematic of the system for the host and FPGA memory transfers. (b) Physical hardware                                                                           |

| 6.18 | PCIe subsystem block diagram                                                                                                                                        |

## List of Tables

| 3.1 | System Performance Measurements                    | 53 |

|-----|----------------------------------------------------|----|

| 4.1 | Experiment and Simulation Performance Measurements | 75 |

### Acknowledgements

First and foremost, I would like to thank my advisor, Professor Keren Bergman, for giving me the opportunity to join the Lightwave Research Laboratory at Columbia University. Her guidance and support throughout my graduate studies helped me not only build my knowledge and skills, but also shape my viewpoint of conducting research.

I want to thank my colleagues at the Lightwave Research Laboratory, especially Dr. Madeleine Glick, Dr. Qixiang Cheng, and Dr. Alexander Gazman for their mentorship and advise during my doctoral study. I am also grateful to other members in the group including Dr. Yiwen Shen, Dr. Min Yee Teh, Maarten Hattink, Richard Dai, Brian Wu, Kristoff Yan, and many others for their discussions, collaborations, and contributions to my research projects. Additionally, I would like to thank Constance Zhou for keeping me optimistic and happy during my Ph.D.

Also, I want to thank my mentors who provided the opportunities for my internships. In particular, Dr. Noriaki Kaneda at Nokia Bell Labs and Dr. Urs Muller at Nvidia. During my internships, I learned valuable skill sets, which assist my research explorations.

Further, I would like to acknowledge the support of my research projects from the Advanced Research Projects Agency Energy (ARPA-E) under the ENLITENED Project, the U.S. Department of Energy (DOE) SBIR/STTR Program under the P-SSIO Project, and the U.S. Defense Advanced Research Projects Agency (DARPA) under the FastNICs Project.

Finally, I would also like to thank my thesis committee members, Professor Keren Bergman, Professor Luca Carloni, Professor Zoran Kostić, Professor Christine Hendon, and Professor Mingoo Seok for their valuable time and their evaluation of my thesis.

xii

## Dedication

This dissertation is dedicated to my parents, Nanyuan Ke and Zhenwu Zhu.

## **Chapter 1: Introduction and Background**

#### **1.1 Deep Learning Trends and Challenges**

Deep learning (DL) is a branch of machine learning that has drastically improved the state-ofthe-art in many applications that enhance our daily lives and impact various aspects of our society. The computational models used in deep learning, called deep neural networks (DNNs), have been successfully applied to various fields including activity recognition [1], image classification [2], and natural language processing [3]. The DNNs consist of many processing layers whose computation is mainly defined by weights and biases. These weights and biases, called parameters of the DNNs, are learned during the training, and used for the inference. Accelerators, such as graphics processing units (GPUs) and field programmable gate arrays (FPGAs), are used for accelerating these training and inference processes [4, 5]. As researchers make continuous studies to improve these DL models, it is found that larger model sizes and larger dataset usually result in better model accuracy [6, 7]. Increased model size is at the center of these advancements [8, 9, 10], and multiple studies have shown that this trend will continue in natural language processing particularly [11, 12]. As a result, there has been significant investment in training huge models. As Fig.1.1 shows, the model sizes have increased over 100,000 times over the past five years to more than 1 trillion parameters.

Researchers have adopted distributed deep learning training [14, 18, 19], where the DL models or the training datasets are partitioned and distributed onto GPUs, to train such large models. There are three major parallelism strategies: data parallelism (DP), model parallelism (MP), and hybrid parallelism (HP). For a model that fits in the device memory for training, DP is used to scale training to multiple devices. DP keeps a full copy of the entire training model on each worker node while distributing the partitioned input dataset to different working nodes. Each worker executes

Figure 1.1: Model Trend from 2016 to 2022. [2, 3, 8, 13, 9, 14, 15, 16, 17]

the forward and backward propagation on a different subset of data samples. For synchronized training, workers need to synchronize their averaged gradients with each other and update the model locally at each integration through all-reduce collective operation. For asynchronized training, each worker sends the averaged gradients to parameter servers [20] and retrieves the updated model parameters for each iteration without waiting for others. When a model does not fit in the device memory, tensor model parallelism (TP) [14, 21] and pipeline model parallelism (PP) [18, 22] can be performed. In TP, the training model is split vertically across layers, so each tensor layer is placed on multiple nodes. The results on each node are then synchronized across the DP workers. In PP, the training model is split horizontally across layers, placing one or more layers on each working node. This requires computing nodes to receive activations/gradients from previous layers before they can proceed onto computing the next layer. Hybrid Parallelism (HP) combines both DP and MP to partition both the models and the dataset. Computing nodes are divided into DP groups of MP nodes. At each iteration, each group of MP nodes synchronize among themselves

using MP-transfers and then synchronize across the DP groups. Figure 1.2 illustrates DP, TP, PP and HP using DP and TP, respectively.

Figure 1.2: Data parallelism, tensor model parallelism, pipeline model parallelism, and hybrid parallelism.

Despite the distributed deep learning training and parallelism techniques, there are three major

challenges.While the maximum memory requirement keeps growing, the real-time memory usage is application dependent and often requires on-demand solutions. First, different deep learning applications show varying memory requirements based on their architectures for example convolutional neural networks (CNNs), recurrent neural networks (RNNs), transformers, and etc.) Second, the memory capacity requirement for various batch sizes [23] and optimization strategies [24] can change within a large range, but the method requiring a larger memory size does not always guarantee a better system performance [25]. Lastly, the size of embeddings that are used in recommendation applications is dependent on the entry size and number of models [26]. Having a fixed and preconfigured amount of memory in the local system for the maximum memory capacity requirement is inefficient and will become more so. A scalable and dynamic solution is required to address the memory challenges for future deep learning applications.

Besides, DL workloads are taking a large proportion of the computation in today's HPC operations, and observation has shown that the demand is dramatically growing in datacenters [27]. Distributed deep learning workloads can require many server nodes and show strong communication patterns between these nodes. These trends have shifted the performance bottleneck from the compute to the network interconnect due to system fragmentation (applications often receive an allocation on a set of distant and non-contiguous nodes) [28]. An example of system fragmentation in a tapered 16-node fat tree topology is shown in Fig. 1.3. Under the top-of-rack (ToR) switch the full bandwidth can be utilized under the best scenario, no traffic goes beyond the ToR switches. However, for the fragmented case, nodes for running the same job can distribute across the network and constrained bandwidth is experienced. Due to the constrained links at higher layers, training workloads can be slowed down substantially. This places a tremendous challenge on interconnect designs to provide high bandwidth and low latency networking to sustain the continual growth of these hardware-driven deep learning applications. These challenges present a unique opportunity for flexible photonic switched networks that have the capabilities to perform topology reconfiguration and have motivated much research to explore reconfigurable network architectures based on optical circuit switches (OCSs).

Figure 1.3: Illustrations of localized nodes and fragmented nodes

Lastly, researchers have also demonstrated the GPU clusters that have increased to more than

Figure 1.4: Hardware bandwidth trend from 2015 to 2022. [30, 31, 32, 33, 34, 35, 36, 37]

3000 GPUs [29] for training extremely large models with hybrid parallelism. However, current hardware solutions can only provide high-bandwidth network for a limited group of computing units (e.g. Nvidia DGX Station connects 8-16 GPUs using high speed NVSwitches and NVLinks for up to 600 GB/s bidirectional bandwidth [30]). To scale the training to sizes larger than the group size would require inter-group communication that relies on 200 Gb/s InfiniBand links which are much slower than the intra-group fabric. And this bandwidth discrepancy has severely limited the communication efficiency during the training process. As Fig.1.4 shows, the increase in network bandwidth is not able to catch up with the exponential rate at which the model sizes are increasing. And the on-board memory/GPU bandwidth (red and blue lines in Fig.1.4 have been growing at a much faster rate than the inter-board bandwidth (yellow line).

To this end, novel reconfigurable architectures and high-bandwidth inter-node interconnects are required to address these challenges and to meet the requirement of scaling trends of deep learning training.

#### 1.2 Silicon Photonic Circuit Switching

Optical circuit switching offers a promising approach to reconfigure the interconnect in order to address the challenges mentioned above. In particular, optical switches can (1) regroup a set of distant and non-contiguous nodes and (2) steer bandwidth at network layers for efficiency. Depending upon underlying traffic patterns of the nodes at different times, optimized topology connections can be dynamically formed on demand.

Commercially available technologies, such as microelectromechanical systems (MEMS) [38], beam-steering [39], and liquid crystal on silicon (LCOS) [40], can be used to implement the reconfigurable network. However, there are still challenges to achieve commercial adoption. The rigorous calibration and the installation of discrete components introduce significant complexity and result in high cost per port. Similarly, arrayed waveguide grating routers (AWGRs) [41] based interconnects usually require higher cost tunable wavelength transceivers that add complexity and additional power consumption in broadcast and select type architectures. For low-cost datacenter/HPC adoption, lithography-based photonic integration technologies hold great promise for large-scale optical integrated switch fabrics with smaller device footprint, and reduced assembly and calibration overheads.

The silicon photonics (SiP) platform, in particular, leverages the mature and widespread CMOS manufacturing infrastructure, and SiP switches are promising for the dynamic topology reconfiguration with better power efficiency, lower cost-per-port, smaller footprint, and the potential for nanosecond range dynamic switching [42, 43, 44, 45, 46]. However, there are several technical challenges to address in this platform, specifically loss through the switch, polarization dependency, thermal stability, and switch radix scalability. Research works have been reported to address these challenges, and the primary switching cells that are being explored are Mach-Zehnder interferometers (MZIs), microring resonators (MRRs), and MEMS-actuated couplers.

Figure 1.5: (a) Low insertion loss  $32 \times 32$  MZI switch, reprinted from [47]. (b) Polarizationdiversity  $32 \times 32$  MZI switch, reprinted from [48]. (c)  $64 \times 64$  T-O MZI switch, reprinted from [49]. (d)  $16 \times 16$  E-O MZI switch, reprinted from [50]. (e)  $32 \times 32$  E-O MZI switch, reprinted from [51]. (f) Hybrid  $2 \times 2$  MZI-SOA module, reprinted from [52].

MZI switching circuits of  $32 \times 32$  connectivity have been realized using thermo-optic (T-O) phase shifters with 6.1 dB on-chip loss [47]. To overcome the polarization dependency, a polarization-diversity SiP MZI switch was further developed [48]. The current record for the T-O MZI switch is a  $64 \times 64$  implementation in Bene topology [49]. For fast electro-optic (E-O) switching, carrier-injection based PIN junctions are employed.  $16 \times 16$  and  $32 \times 32$  E-O MZIbased switches were proposed in Refs. [50, 51]. Performance, however, can be limited due to the high insertion loss. Gain-integrated switches with semiconductor optical amplifiers (SOAs) for lossless operation can be applied to overcome this challenge [52]. Figure. 1.5 depicts the MZI based switches.

Figure 1.6: (a)  $8 \times 7$  cross-bar switch, reprinted from [53]. (b)  $8 \times 8$  Omega switch, reprinted from [54]. (c)  $4 \times 4$  switch-and-select switch, reprinted from [55]. (d)  $4 \times 4$  hitless switch, reprinted from [56].

MRR based devices show ultra-compact and energy-efficient potentials for optical switching. Recent work has demonstrated 8 x 7 cross-bar [53], 8 x 8 Omega [54], 4 x 4 switch-and-select [55], and 4 x 4 hitless [56] architectures. Add-drop filters assembled in a 1-D bus structure can act as spatial (de)multiplexers [57]. Thermal stabilization [58, 59] is necessary for MRR based switches to address wavelength drifts due to the thermal dependencies to the varying ambient temperature. Figure. 1.6 depicts the MRR based switches.

The largest-scale SiP switch fabric reported to date is the MEMS-actuated cross-bar switch with  $240 \times 240$  connectivity, which consists of a  $3 \times 3$  array of identical  $80 \times 80$  switch blocks [60]. Maximum on-chip loss of 9.8 dB was reported. Multilayer bus waveguides can be used for eliminating waveguide crossings to reduce insertion loss and for addressing polarization sensitivity [61]. Recent work has shown successful fabrication of SiP MEMS using a commercial foundry with reduced driving voltage down to 9.45V [62].

More detailed discussions on the photonic switching technologies in datacenter/HPC systems can be found in the reviews [42, 43, 44]. We note that SiP switches are promising for optical switching in datacenter/HPC rack-to-rack applications; however, the loss should be further reduced before being deployed in practice. Approaches, such as (1) integration with SOAs, (2) improvement of coupling loss, and (3) progress on individual component to have a better loss performance, are being taken to further reduce the loss of silicon photonic switched architectures.

#### **1.3** Silicon Photonic High Bandwidth Transceivers

The increasing mismatch between on-board and off-board bandwidth, as indicated in Fig. 1.4, calls for new interconnect design to overcome the network bottleneck and speed up applications such as the distributed training of extreme large models. Co-packaged silicon photonics with unprecedented bandwidth density, efficiency, and reach lends itself to the applications that require Tb/s data links. Direct silicon photonic connectivity for central processing units (CPUs), GPUs, FPGAs, domain-specific accelerators, and memory will impact a host of future deep learning applications.

Figure 1.7: (a)  $240 \times 240$  MEMS cross-bar switch, reprinted from [60]. (b) Polarization-Insensitive MEMS switch, reprinted from [61]. (c)  $32 \times 32$  MEMS switch fabricated in a commercial foundry, reprinted from [62].

(b)

din in

Figure 1.8: The various integration approaches to integrate PICs with EICs. (a) Monolithic integration. (b) 2D integration. (c) 3D integration. (d) 3D integration with active photonic interposer. (e) 2.5D integration. Reprinted from [63].

Figure 1.8 shows different methods of SiP co-packaging integration. In monolithic integration, both photonic integrated circuits (PICs) and electronic integrated circuits (EICs) components are fabricated in within the same die. It achieves minimum parasitics and simplified packaging with wire bonds for the connectivity to the PCB. However, it lags in cutting edge electronic performance and suffers from high waveguide loss, low photodiode responsivity, and low photodiode bandwidth. Figure 1.8(a) shows the monolithic integration approach. In 2D integration, the PIC and the EIC chips are placed side by side on a PCB, and wire bonds are used to connect the chips as well as to interface to the PCB. 2D integration allows most advanced technologies in photonics and electronics, but it shows limited I/O density, and introduces parasitic inductance. Figure 1.8(b) shows 2D integration approach. Another approach is 3D integration, where EIC chip is flip chip (FC) bonded to the PIC chip. 3D integration increases the connectivity throughout the twodimensional solder bumps, and reduces the parasitics between the EIC and PIC chips compared to 2D approach. However, PIC active components may be sensitive to the heat dissipated by the EIC chip. A promising approach is incorporate PIC components into an interposer. This is ideal for a dense, high performance I/O packaging; however, it is a relatively new technology and requires more development efforts. Figure 1.8 (c) and (d) shows the 3D integration and 3D active interposer integration approaches. A compromised solution is 2.5D integration, where PIC and EIC chips are flip chipped bonded to an interposer. The interposer supports EIC-to-PIC connections and fanouts necessary signals to PCB through a ball grid array (BGA). This approach also allows for high I/O bandwidth and density, and has fewer thermal concerns compared to the traditional 3D integration. Figure 1.8(e) shows the 2.5D integration approach. More detailed discussions can be found in Ref. [63].

The SiP transceiver architecture is the key enabler for high bandwidth interconnects. Coherent technology with advanced modulation format is widely used to provide high-capacity links in long-distance networks and metropolitan area networks. However, coherent systems are expensive for short-reach applications. They require narrow-linewidth lasers, power-consuming digital signal processing (DSP), and digital-to-analog and analog-to-digital (DA/AD) converters. Many schemes

have been proposed to reduce the power consumption, transceiver cost, and DSP complexity [64, 65, 66, 67].

Figure 1.9: TeraPHY chiplet showing optical Tx/Rx macros, fiber array, and Tx/Rx circuits. Reprinted from [68].

Another approach is to still use simpler intensity-modulated direct-detection (IM-DD) links as preferred in today's DC applications. IM-DD links with on-off-keying (OOK) or pulse amplitude modulation 4-level (PAM 4) modulation formats can be reconstructed directly without forward error correction (FEC) for error-free operations. An example is TeraPHY [68] that supports up to 2Tbps bandwidth per chiplet. It uses a bus of 8 MRR based modulators running at 25Gbps each and a bus of 8 MRR based detectors form a transceiver macro. Each transceiver macro transmits and receives 8 different wavelengths of light. The chiplet then contains 10 macros to achieve the

aggregated bandwidth. Figure 1.9 shows the TeraPHY chip. It projects 100 Tbps and beyond for future generations on the roadmap. One drawback is its scalability. Each macro requires a pair of fibers for the input and output, such that the number of fibers linearly grows with the number of macros in the chiplet.

Figure 1.10: (a) Schematic of the comb-driven transceiver architecture, reprinted from [69]. (b) Micrograph of the full die, reprinted from [69]. (c) Image of the Kerr comb device, reprinted from [70].

Dense wavelength division multiplexing (DWDM) can be used to solve this issue and scale up high-bandwidth per fiber. The key challenges are the DWDM light source with hundreds of lines and a scalable transceiver architecture that is able to modulate and detect each of the wavelengths. Recently, a promising Kerr frequency comb-driven silicon photonic transceiver architecture [69] has been reported to achieve this goal. It leverages a frequency comb [70] that generates the DWDM light source. A de-interleaver is used to split the comb spectrum into subgroups. Each wavelength subgroup gets modulated by a bus of cascaded microdisk modulators, and then all the subgroups are recombined using an identical interleaver and coupled off the chip into a single fiber. At the receiver, the modulated comb lines are de-interleaved similarly and are incident on buses with cascaded MRR based detectors. Figure 1.10(a) shows the transceiver architecture and Fig.1.10(b) shows the transmitter chip. The Si3N4 dual-micro-resonator system for the comb generation is shown in Fig. 1.10(c).

Novel SiP transceiver technologies and proper packaging schemes have the potential to enable efficient muti-Tbps chip-to-chip communications and to meet the inter-chip bandwidth requirement posed by the scaling deep learning models.

### **1.4 Scope of Dissertation**

The work in this dissertation addresses system level challenges posed by deep learning training, focuses on innovative architectural designs leveraging high performance silicon photonic interconnects, and demonstrates prototype systems to show the potential of integrating silicon photonic interconnects in future datacenters and HPCs. The chapters in this dissertation are comprised of the author's works in published peer reviewed journals and research conference proceedings.

In Chapter 2, we explore various optical spectral and spatial switching of SiP MRR based switches, such as unicast, multicast, and multiwavelength-select functionalities. We demonstrate our FPGA-based open-loop and closed-loop control over the switches. The successful control and the switching functionalities are essential for new architectural explorations in the following chapters.

In Chapter 3, we propose a photonic switched optically connected memory architecture for addressing memory constraints in deep learning. A "lite" (de)serialization scheme is used to reduce the communication overhead for memory transfers in optics. We evaluate the system performance on an experimental testbed with processing system, remote memory nodes, and SiP switches. The collective results show the potential of using optically connected memory for deep learning.

In Chapter 4, we demonstrate a silicon photonic switched architecture for deep learning in datacenter and HPC networks. The proposed architecture leverages reconfigurable optical switching fabrics to tackle the network challenges and accelerate distributed deep learning training. Experimental and simulation results suggest integrating SiP switches into datacenter and HPC systems can improve system performance and accelerate distributed deep learning training at scale.

In Chpater 5, we present two silicon photonic-enabled disaggregated system architectures for deep learning. The first architecture shows the concept of rack-scale disaggregation. The flexible optical switches enable resource disaggregation and defragmentation. The second architecture leverages comb laser sources and multi-wavelength selective MRR-based cross-bar switches to enable the all-to-all high bandwidth communication. We observe improved system performance of our proposed architecture compared to other existing topologies.

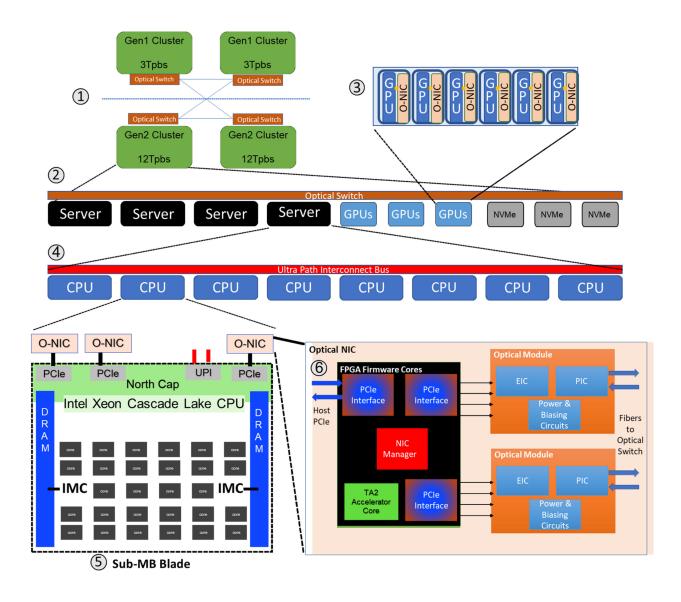

Lastly, in Chapter 6, we report our progress on the development of optical network interface cards for the FLEET project. We show the design and packaging flow to expand PCIe communication into optical domain. Test packages for system development and verification are presented. This chapter shows integrating of silicon photonic technologies into high performance systems.

### **Chapter 2: FPGA-controlled Silicon Photonic Interconnects**

#### 2.1 Introduction

Reconfigurable networks and optical circuit switches (OCSs) based architectures have been proposed to be deployed in datacenter and HPC systems. These architectures including Helios [71], Mordia [72], ProjecToR [73], Flexfly [74], and many others, can establish high-bandwidth connections to optimize network performance for frequently-communicating nodes. Commercially available technologies [38, 39, 40] suffer from high cost per port due to their rigorous calibration and installation of discrete components. For low-cost adoption, lithography-based photonic integration technologies hold great promise for large-scale optical integrated switch fabrics by reducing the device footprint and also the overhead in terms of assembly and calibration. Planar integrated optical switches have been developed on several material platforms, such as indium phosphide, lithium niobate, silica, and silicon [52, 75, 76, 55].

Silicon photonics, fabricated in high volume CMOS compatible foundries, is promising for low-cost, power-efficient interconnects. The primary switching cells that are being explored are MZIs [47], MRRs [54], and MEMS-actuated couplers [60]. A basic  $1 \times 2$  MZI switching cell is shown in Fig. 2.1(a). The phase delays in the two arms can be changed by their corresponding phase shifters through electronic bias input to thermo-optic heaters or electro-optic drivers for carrier injection/depletion. The resultant phase differences between the MZI arms can direct the input light to output port #1 (bar state) or output port #2 (cross state), respectively. Same bias control mechanism can be applied to MRRs. A fundamental  $1 \times 2$  MRR switching cell is shown in Fig. 2.1(b). The input light can be directed to output port #1 (through state) or output port #2 (drop state), respectively. The difference is that MZI switches are broadband switches, while MRR switches are narrowband devices and only periodic wavelengths with a certain free-spectrum-range

Figure 2.1: (a)  $1 \times 2$  MZI cell. (b)  $1 \times 2$  MRR cell. (c)  $1 \times 2$  MEMS-actuated coupler cell. (d) Packaging with wirebonding and fiber attachment

(FSR) can be dropped. Figure 2.1(c) the fundamental  $1 \times 2$  MEMS switch. By biasing the electrodes of MEMS, the input light can be forwarded to output port #1 (off state) or redirected through the adiabatic couplers to output port #2 (on state), respectively. In general, all three switching cells can be tuned by electrical bias voltages. Figure 2.1(d) shows a generic packaging scheme for the interface to a large radix switch chip that consists of many of those basic switching cells. Since the tuning scheme is similar, only the MRR-based switches are mainly discussed in the rest of this chapter.

#### 2.2 Optical Switching in Cascaded-MRR Switch

Figure 2.2(a) shows an array of eight cascaded SiP MRRs. This cascaded MRR switch can achieve various optical functionalities such as unicast, multicast, and multiwavelength-select. Figure 2.2(b) illustrates the responses of the MRRs in the chip when no bias voltage is applied. By design, the responses of the rings are separated by 1.27 nm (160 GHz) with an FSR of 13 nm and 3 dB bandwidth of 0.7 nm.

Figure 2.2(c) shows a unicast operation where the input data on the wavelength denoted by a red

Figure 2.2: (a) Switch architecture with 8 Cascaded MRRs. (b) Zero bias scenario. (c) Unicast scenario. (d) Multicast scenario. (e) Multiwavelength-select scenario.

vertical arrow is routed to output port 8 (dashed black curve). To obtain this mode of operation, i) the resonance of ring R2 must be detuned to prevent dropping at port 2 because R2 has the precedence over R8 in the MRR array, and ii) the resonance of ring R8 must be tuned to the red wavelength. Detuning is required for ring R2 to achieve error free operation for ring R8. As the bias voltage over R2 is increased gradually, its resonance is shifted to allow the signal to propagate to R8. The bit-error-rate (BER) is needed to verify the amount of detuning necessary in order to reach the error free transmission (BER = 10e-12) with negligible crosstalk effects [77]. At a bias of 0.85 V the signal is fully routed to the output port 8. We estimated that this amount of detuning is about 1.08 nm which corresponds to a channel suppression of 10 dB between the desired output port (R8) and the detuned MRR (R2). This amount of detuning is chosen for power efficiency; any further detuning will cost more energy-per-bit while introducing negligible improvement on the BER of the routed signals.

Figure 2.2(d) illustrates a one-to-seven multicasting operation. This operation is possible by aligning the Lorentzian response of each MRR so that the power of the optical signal is divided equally among the desired output ports; i.e. tuning the rings to the appropriate resonances, starting

from the last MRR participating in the multicast operation. The last MRR, R8 in this example, is tuned so that its resonance aligns exactly with the input wavelength, allowing maximal transmission over its drop path. R7 is then tuned to its 3dB bandwidth point, allowing a drop of 50% of the optical power. Continuing with this approach R6, R5, R4, R3 and R2 are tuned to the following drop power ratios: 33.33%, 25%, 20%, 16.67% and 14.28%, respectively, i.e. following a harmonic series (1, 1/2, 1/3, 1/4 . . . ). When the process is complete, each of these seven rings will equally drop 14.28% of input optical power coupled into the SiP chip. Realizing multicast exhibits the fine tuning levels, and demonstrates the potential of SiP for error-free multicast operation of one stream of data over a single wavelength.

Figure 2.2(e) shows a three-to-one multiwavelength-select operation. This operation leverages the ring's FSR. Each ring is capable of dropping a train of input signals as long as their input wavelengths are separated from each other with a distance as the ring's FSR. Similar to the unicast case, the resonance of ring R8 is tuned to each of the input red wavelengths, and ring R2's resonance is detuned to prevent dropping them at port 2. This operation allows to aggregate more bandwidth with multiple wavelengths at drop port of each ring, and potentially enables a shuffling operation in a cross-bar ring-based switch fabric. More discussions on the cross-bar switch design and its usage can be found in chapter 7.

#### 2.3 FPGA-Based Open Loop Control

#### 2.3.1 System Architecture

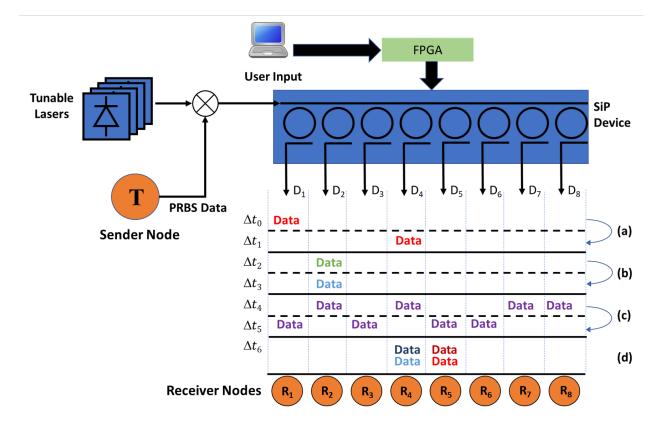

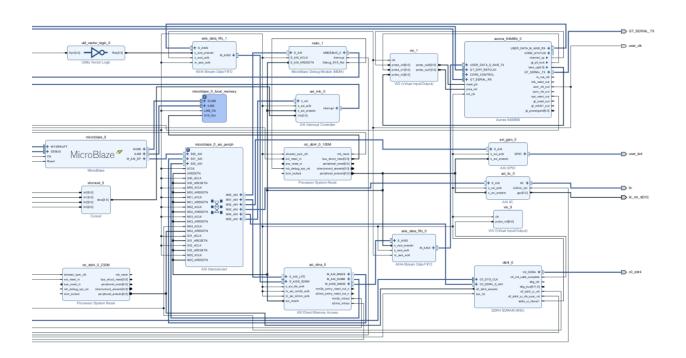

Figure 1 shows a block diagram of our proposed system architecture. The main components are fast tunable lasers (TL), a SiP chip, a field programmable gate arrays (FPGA) and a computer that provides an interface to the user. Depending on the desired configuration, the computer sends operation messages to the FPGA via a serial data transfer interface. The TLs can adjust its output optical power and the wavelength of operation over the C-band. The FPGA controls the array of eight cascaded MRRs and sets their resonances. As shown in Fig. 1, an external modulator is used to encode data onto the laser outputs. Altogether, the system is capable routing of optical data to

any of the eight output ports, splitting the incoming data to a number of output ports, as well as selecting/forwarding multiple wavelengths to a single MRR.

Figure 2.3: Open-loop control scheme.

The time-slot diagram in Fig. 2.3 illustrates four possible operations of the system. In this example, the different colors of the data in the figure correspond to different wavelengths. During slot  $\Delta t_0$  the data stream is routed to output R1. During  $\Delta t_1$  slot the data stream is switched to output R4 (Fig. 1(a)) without changing the operating wavelength (red color). In the second case, shown in Fig. 1 (b), wavelength routing is performed. During time slot  $\Delta t_2$  the data is transmitted to output R2 on a carrying wavelength  $\lambda_1$  (green color) while in slot  $\Delta t_3$  the output port stays the same but the wavelength changes to  $\lambda_2$  (blue color). Multicast (one to many) operations are also performed. During  $\Delta t_4$ , an incoming data stream modulated on the wavelength (purple color) is split among four output ports: R2, R4, R7, and R8. In the following time slot  $\Delta t_5$ , the configuration is modified to R1, R3, R5, and R6. Finally, during time slot  $\Delta t_6$ , R2 and R3 are used to perform

multiwavelength-select operations. Wavelengths in blue and dark blue separated a FSR are dropped by R4. Similarly, the adjacent R5 drops wavelengths in red and dark red. The minimum transition time between the time slots is determined by the reconfiguration time of the SiP device from the moment the FPGA apply the bias voltages for new configurations.

The operation of the system is not limited to the particular sequential illustration presented in Fig. 2.3. The SiP device can perform unicast (one to one), multicast (one to many), and broadcast (one to all), multiwavelength-select (many to one) operations, numerous deterministic combinations are possible without any constraints.

#### 2.3.2 Experimental Demonstration for Unicast and Multicast

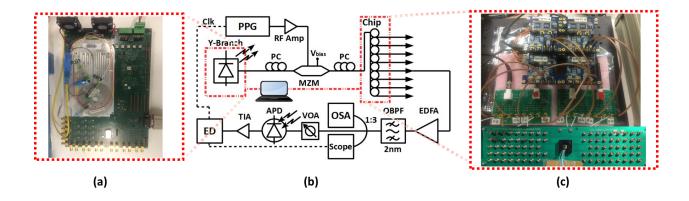

Figure 2.4: (a) Tunable laser. (b) Schematic of the unicast and multicast experimental setup. (c) FPGA-based switch controller and the packaged MRR switch on a PCB.

The schematic of the experimental setup is shown in Fig. 2.4. A tunable Y-branch laser [78] (Fig. 2.4(a)) was used to output light at various frequencies across the ITU 100 GHz C-band grid. The packaged SiP device along with its control plane is shown in Fig. 2.4(c). The control plane is based on an Stratix III EP3SL150 FPGA capable of hosting and controlling eight parallel digital-to-analog converters (65 MHz DAC) with 14 bits of resolution. The output voltage from the DACs (0 – 1V) is amplified by 5 in the gain stage to achieve a full FSR swing for each MRR. The amplified control signals are connected to a break-out printed-circuit-board (PCB) which hosts the SiP chip. After fabrication, the chip was attached to, and wire-bonded on, a standard electrical IC

|                | Drop<br>port 1 | Drop<br>port 2 | Drop<br>port 3 | Drop port<br>4 | Drop<br>port 5 | Drop<br>port 6 | Drop<br>port 7 | Drop<br>port 8 |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Unicast        |                | $\bigotimes$   |                |                |                |                |                |                |

| Multicast of 2 |                | XX             |                |                |                |                | XX             |                |

| Multicast of 3 | $\bigcirc$     | 00             | $\propto$      |                |                |                |                |                |

| Multicast of 4 | 00             | XX             | $\bigcirc$     |                |                |                |                | $\infty$       |

| Multicast of 5 | XX             | 9              | $\sim$         |                |                |                | $\bigcirc$     | 00             |

| Multicast of 6 | 00             | $\odot$        | 8              | $\bigotimes$   |                |                | 00             | 8              |

| Multicast of 7 | $\infty$       | $\infty$       | $\infty$       | XX             | XX             |                | XX             | XX             |

| Broadcast      | $\infty$       | $\infty$       | 00             | 00             | $\infty$       | XX             | $\infty$       | $\infty$       |

Figure 2.5: Experimental results of 8 different cases including unicast, multicast, and broadcast.