# $\begin{tabular}{l} \textbf{In-situ} and \begin{tabular}{l} \textbf{In-field} temperature and transistor BTI sensing techniques with \\ microprocessor-level implementation \\ \end{tabular}$

Teng Yang

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy under the Executive Committee of the Graduate School of Arts and Sciences

COLUMBIA UNIVERSITY

2022

©2022

Teng Yang

All Rights Reserved

#### ABSTRACT

In-situ and In-field temperature and transistor BTI sensing techniques with microprocessor-level implementation

#### Teng Yang

In modern deep-scaled CMOS technologies, various silicon-related pitfalls present challenges to the long-term performance of microprocessors. Such challenges include (1) local hot spots, which breach the thermal limitations of a microprocessor, and (2) transistor aging, especially NBTI, which degrades transistor threshold voltage, ultimately threatening the reliability of the entire memory block. In previous systems, the dummy circuit was placed next to the subject, where the dummy was frequently analyzed, and the readout was used to infer the condition of the target. Due to rapidly changing ambient conditions (e.g., temperature and voltage) and the potential scale of the target dimensions, such metrics may not accurately represent the condition of the target. Moreover, such temperature sensors and canary circuits occupy significant area.

Therefore, it would be highly preferable to monitor the target circuit in-situ, i.e., to sense the precise transistor at operation. It is also important to achieve an accurate sensing metric. When the temperature is analyzed, the readout should account for voltage and process variations. While sensing the aging degradation, the readout should account for voltage and temperature fluctuations. This would allow testing during in-field operation, while the circuits achieve area-efficiency.

This research had two stages. One result of the first stage was a silicon test chip that was a compact temperature sensor. It involved a family of PTAT+CTAT sensor front-ends that unitized only 6 to 8 conventional CMOS logic devices, yielding a smaller sized chip.

The sensor demonstrates accuracy within the target and achieves a 14.3x smaller foot print than preceding published designs. The second product of the first stage was a PMOS aging sensor used in 6T SRAM circuits. The test chip has a real SRAM array, integrated with the proposed PMOS NBTI sensor. It can sense real PMOS NBTI effects in any bit cell (in-situ) and provide robust readings of temperature and voltage (in-field). Intensive aging tests validated the proposed sensing technique.

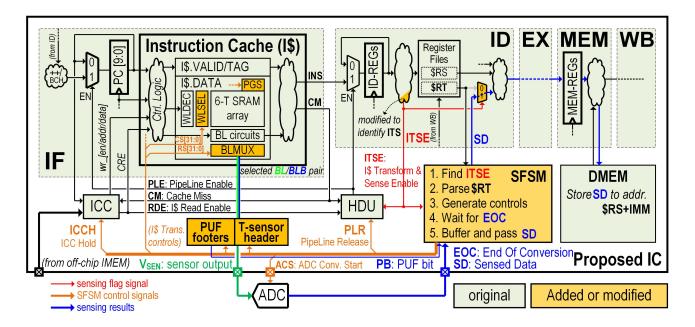

The second stage was focused on implementing the in-situ and in-field sensing techniques in a real processor. The MIPS microprocessor had a modified instruction cache (I\$) and instruction set architecture. With the addition of new instruction aging sensing and minor modification of the circuits, the processor can execute aging sensing opportunistically to evaluate the aging level of its instruction cache. A software framework was developed and verified to estimate the retention voltage of the instruction cache over the lifetime of the chip.

An area-efficient SoC was developed that could transform the instruction cache to an ambient temperature sensor. It had a physically unclonable function (PUF), and it was built with an area-saving technique similar to the earlier work.

This thesis has four chapters. They are presented in the chronological and they are aligned with the research described above.

# Table of Contents

| 1 | Intr                                                                            | ntroduction                                                                 |    |  |  |  |  |

|---|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------|----|--|--|--|--|

|   | 1.1                                                                             | Background                                                                  | 1  |  |  |  |  |

|   | 1.2                                                                             | Compact Voltage-scalable on-chip temperature sensor                         | 2  |  |  |  |  |

|   | 1.3                                                                             | In-situ and In-field BTI sensors for register file                          | 4  |  |  |  |  |

|   | 1.4 Circuit, architecture and run-time framework for memory reliability manage- |                                                                             |    |  |  |  |  |

|   |                                                                                 | ment in a microprocessor                                                    | 7  |  |  |  |  |

|   | 1.5                                                                             | An area-efficient SoC with instruction cache transformable to a temperature |    |  |  |  |  |

|   |                                                                                 | sensor and a PUF                                                            | 9  |  |  |  |  |

| 2 | Con                                                                             | npact, Voltage-scalable on-chip Temperature Sensor                          | 13 |  |  |  |  |

|   | 2.1                                                                             | Motivation                                                                  | 13 |  |  |  |  |

|   | 2.2                                                                             | Operation Principle                                                         | 15 |  |  |  |  |

|   | 2.3                                                                             | Accuracy Improvements                                                       | 19 |  |  |  |  |

|   |                                                                                 | 2.3.1 Output Range Tuning                                                   | 19 |  |  |  |  |

|   |                                                                                 | 2.3.2 Differential Read-out                                                 | 21 |  |  |  |  |

|   |                                                                                 | 2.3.3 Supply-voltage Scalability                                            | 24 |  |  |  |  |

|   |                                                                                 | 2.3.4 Noise                                                                 | 25 |  |  |  |  |

|   | 2.4                                                                             | Read-out conditioning circuit design                                        | 26 |  |  |  |  |

|   | 2.5   | Silicon Implementation                                  | 30 |

|---|-------|---------------------------------------------------------|----|

|   | 2.6   | Measurements                                            | 30 |

|   |       | 2.6.1 Sensor Accuracy                                   | 30 |

|   |       | 2.6.2 VDD Scalability                                   | 34 |

|   | 2.7   | Conclusion                                              | 35 |

| 3 | In-si | tu and In-field NBTI sensor for Register Files          | 39 |

|   | 3.1   | Motivation                                              | 39 |

|   | 3.2   | Register File Architecture                              | 43 |

|   | 3.3   | In-situ PMOS $V_{TH}$ Sensor                            | 46 |

|   |       | 3.3.1 Sensor Circuits                                   | 46 |

|   |       | 3.3.2 Sensor Operation Principle                        | 47 |

|   |       | 3.3.3 Differential Reading                              | 50 |

|   |       | 3.3.4 Sensor Gain ( $V_{TH}$ Sensitivity)               | 51 |

|   |       | 3.3.5 Leakage Reduction                                 | 52 |

|   |       | 3.3.6 Noise                                             | 54 |

|   | 3.4   | Silicon Prototyping                                     | 55 |

|   | 3.5   | Measurements                                            | 56 |

|   |       | 3.5.1 Monitoring NBTI Degradation                       | 56 |

|   |       | 3.5.2 Robustness in Monitoring                          | 58 |

|   | 3.6   | Aging Deceleration Experiment                           | 60 |

|   |       | 3.6.1 Monitoring the Polarity of Data Retention Voltage | 61 |

|   |       | 3.6.2 Recovery Vector                                   | 62 |

|    | 3.7    | Comparison and Conclusion                                                | 68  |

|----|--------|--------------------------------------------------------------------------|-----|

| 4  | Circ   | uits, Architecture and Run-Time Framework for Memory Reliability Manage- |     |

|    | men    | t in a Microprocesosr in the Field                                       | 71  |

|    | 4.1    | Motivation                                                               | 71  |

|    | 4.2    | Circuits and Micro-architecture Design                                   | 73  |

|    | 4.3    | Testchip and Measurements                                                | 77  |

|    | 4.4    | DRV Estimation Framework                                                 | 78  |

|    | 4.5    | Conclusion                                                               | 83  |

| 5  | An     | Area-Efficient SoC with an Instruction-Cache Transformable to an Ambient |     |

|    | Tem    | aperature Sensor and a Physically Unclonable Function                    | 87  |

|    | 5.1    | Motivation                                                               | 87  |

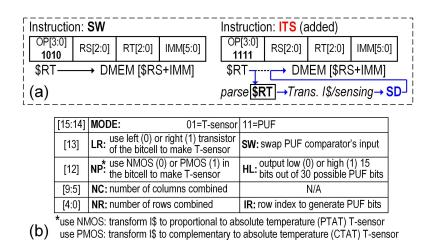

|    | 5.2    | Circuit Design and Transformation                                        | 90  |

|    |        | 5.2.1 T-sensor Transformation                                            | 90  |

|    |        | 5.2.2 PUF Transformation                                                 | 93  |

|    | 5.3    | Micro-architecture Design                                                | 98  |

|    | 5.4    | Testchip and Measurement                                                 | 102 |

|    | 5.5    | Conclusions                                                              | 110 |

| Сс | onclus | sion                                                                     | 113 |

| Ri | hliom  | ranhy                                                                    | 115 |

# List of Figures

| 1.1 | Structures of proposed sensor front end                                      | 3  |

|-----|------------------------------------------------------------------------------|----|

| 1.2 | Layouts of proposed sensor front end                                         | 3  |

| 1.3 | Demonstration of $V_{TH}$ sensing capability and robustness                  | 6  |

| 1.4 | Microprocessor architecture of proposed DRM technique                        | 7  |

| 1.5 | (a) Sensing task assignment (b) Framework to estimate current DRV            | 8  |

| 1.6 | (a) Low duty cycle operation such as ambient temperature sensing and PUF.    |    |

|     | (b) Dedicate hardware implementation of those functions compared with con-   |    |

|     | ventional design. (c) Proposed transformation approach can save area. $$     | 10 |

| 1.7 | The proposed $\mu p$ -SoC microarchitecture. The modified and added portions |    |

|     | are highlighted in yellow                                                    | 11 |

| 2.1 | Trends in numbers of on-chip temperature sensors in $\mu Ps$ and SoCs        | 14 |

| 2.2 | Structures of proposed sensor front end                                      | 15 |

| 2.3 | Layout snapshots of three proposed sensor front ends                         | 16 |

| 2.4 | Simulation setups for the I-V characterizations                              | 17 |

| 2.5 | The zoomed-in temperature characteristics of the CTAT and PTAT generator     | 18 |

| 2.6 | The output range and slope of PTAT and CTAT generator                        | 20 |

| 2.7 | Differential read improves linearity                                         | 23 |

| 2.8  | Differential reading achieves smaller error across the VDD scaling $\dots \dots$     | 25 |

|------|--------------------------------------------------------------------------------------|----|

| 2.9  | Noise simulation                                                                     | 26 |

| 2.10 | Test-chip block diagram                                                              | 26 |

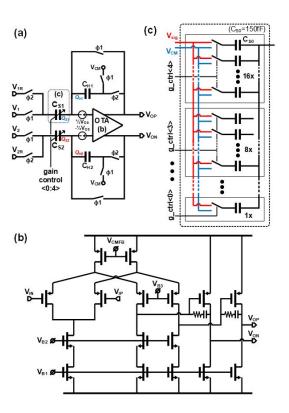

| 2.11 | DSCDA schematics                                                                     | 27 |

| 2.12 | Four modes of DSCDA                                                                  | 28 |

| 2.13 | The available amplification rooms of the ER and the SR mode                          | 29 |

| 2.14 | Test chip die photo                                                                  | 30 |

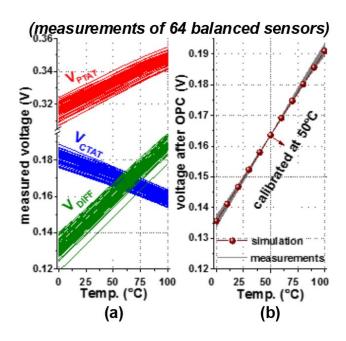

| 2.15 | The measurements PTAT, CTAT, PTAT-CTAT and after OPC                                 | 31 |

| 2.16 | The errors of 64 balanced front-end circuits after OPC                               | 31 |

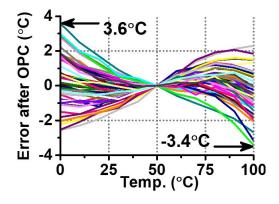

| 2.17 | The summary of the error performance of three front-end designs after OPC            | 32 |

| 2.18 | The relative error from measurements                                                 | 33 |

| 2.19 | VCC scalability measurements                                                         | 34 |

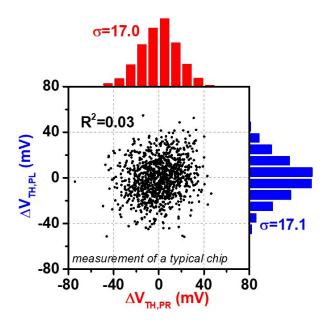

| 3.1  | Measured $V_{TH}$ s between left and right PMOS in the bit<br>cells from 1Kb RF $$ . | 41 |

| 3.2  | RF configured to sensing mode supports in-situ monitor PMOS $V_{TH}$                 | 43 |

| 3.3  | Demonstration of $V_{TH}$ sensing capability and robustness                          | 47 |

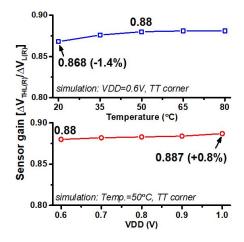

| 3.4  | The gain of the $V_{TH}$ sensor across temperature and supply voltage variations     | 51 |

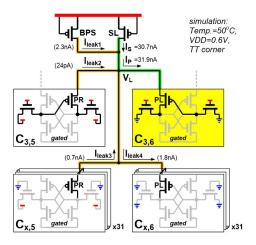

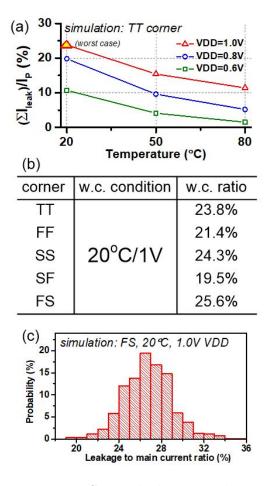

| 3.5  | Sensor leakage snapshots                                                             | 53 |

| 3.6  | Sensor leakage simulation                                                            | 54 |

| 3.7  | Chip microphotograph and the layout of a register file with the proposed             |    |

|      | technique                                                                            | 55 |

| 3.8  | Area overhead of the proposed technique                                              | 56 |

| 3.9  | Measurements of NBTI-related $V_{TH}$ degradation/recovery                           | 57 |

| 3.10 | Robustness measurements against temperature variations                              | 59 |

|------|-------------------------------------------------------------------------------------|----|

| 3.11 | Robustness measurements against supply voltage variations                           | 60 |

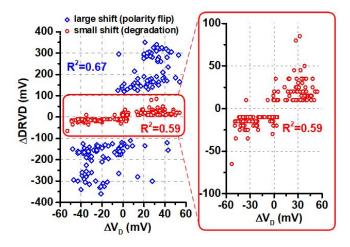

| 3.12 | Measured $\Delta V_D$ as a function of $\Delta$ DRVD after AAT                      | 62 |

| 3.13 | The sequence of recovery vector experiment                                          | 64 |

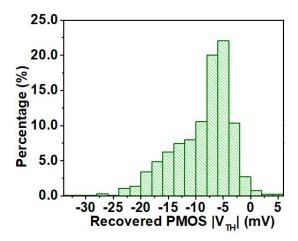

| 3.14 | PMOS $V_{TH}$ is recovered through $RV_{SRV}$                                       | 65 |

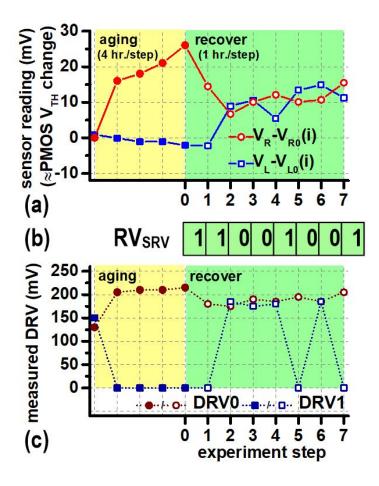

| 3.15 | Measurements during aging deceleration experiment                                   | 66 |

| 3.16 | PMOS aging skews of bitcells before and after experiment                            | 67 |

| 3.17 | Measured DRVs during deceleration experiments of a typical array and mul-           |    |

|      | tiple arrays                                                                        | 68 |

| 4.1  | Peripherals that converting a bitcell PMOS $in\text{-}situ$ into a $V_t$ sensor     | 74 |

| 4.2  | Configurations to enable converting 6 transistors into $V_t$ sensors                | 75 |

| 4.3  | Formats comparison between existing instruction $\mathbf{ST}$ and added instruction |    |

|      | AS                                                                                  | 76 |

| 4.4  | Microprocessor architecture of proposed DRM technique                               | 77 |

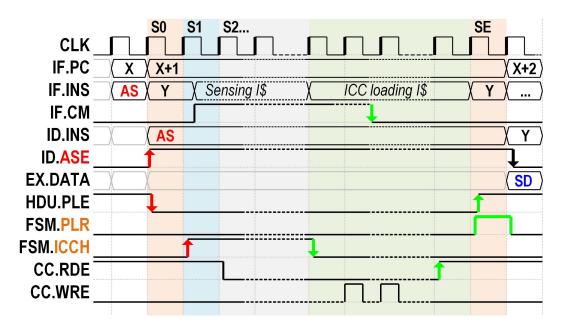

| 4.5  | Timing diagram when executing instruction $\mathbf{AS}$                             | 78 |

| 4.6  | ASFSM state transfer graph                                                          | 79 |

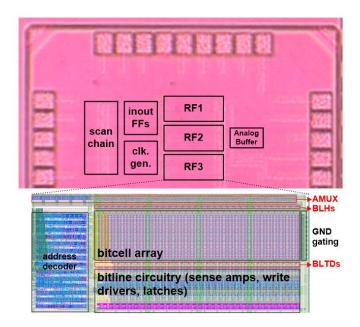

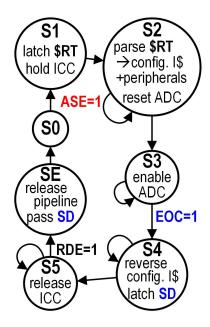

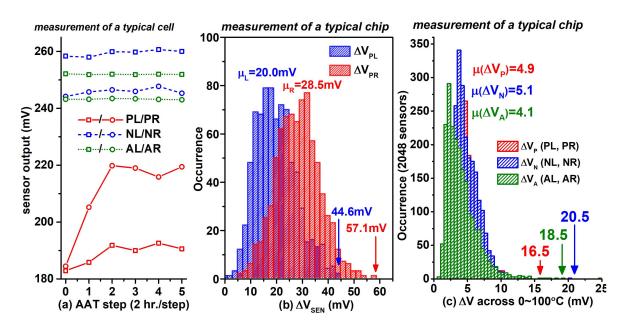

| 4.7  | Area breakdown and chip die photo                                                   | 80 |

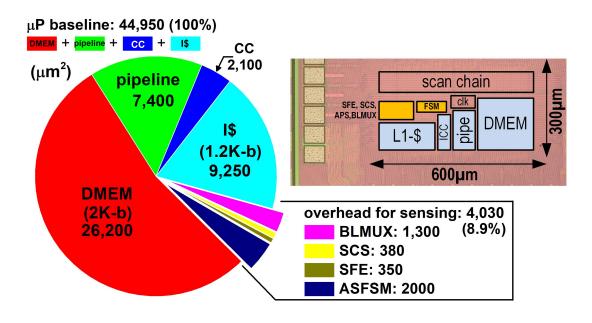

| 4.8  | Sensor measurement (a) a cell case (b) a chip case (c) sensitivity to temperature   | 81 |

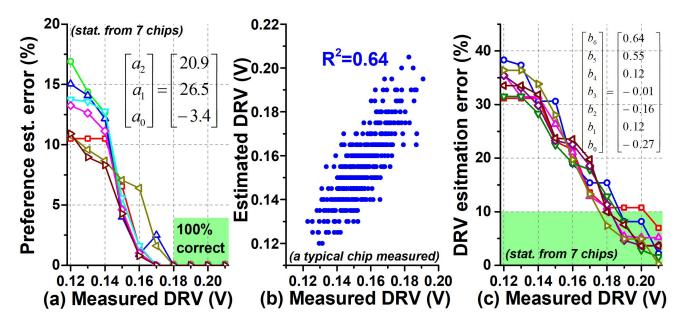

| 4.9  | Framework modules to estimate (a) retention preference (b) DRV (c) DRV              |    |

|      | degradation                                                                         | 82 |

| 4.10 | (a) RPE: coefficient A and accuracy (b) Estimated and measured original             |    |

|      | DRV (c) DE: coefficient B and accuracy                                              | 83 |

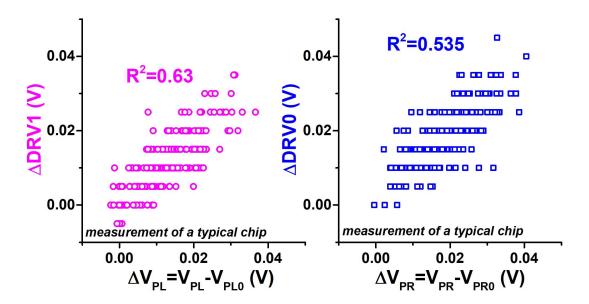

| 4.11 | $\Delta$ DRV and PMOS $V_t$ sensor output correlation                           | 84 |

|------|---------------------------------------------------------------------------------|----|

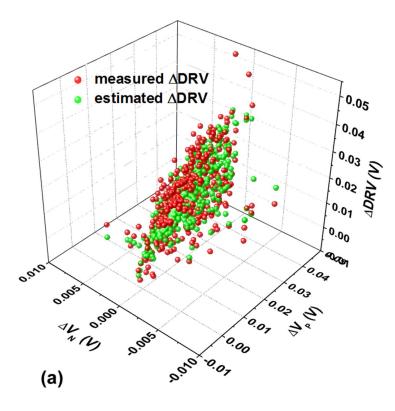

| 4.12 | Estimated and measured $\Delta$ DRV correlation                                 | 85 |

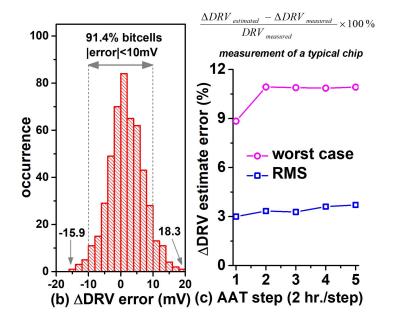

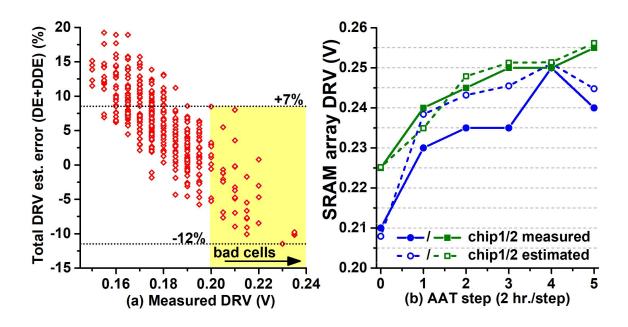

| 4.13 | (b) error statistics (c) errors across AAT                                      | 85 |

| 4.14 | (a) Sensing task assignment (b) Framework to estimate current DRV               | 86 |

| 4.15 | DRV estimation error for (a) bitcells, (b) L1 Cache                             | 86 |

| 5.1  | (a) Low duty cycle operation such as ambient temperature sensing and PUF.       |    |

|      | (b) Dedicate hardware implementation of those functions compared with con-      |    |

|      | ventional design. (c) Proposed transformation approach can save area            | 88 |

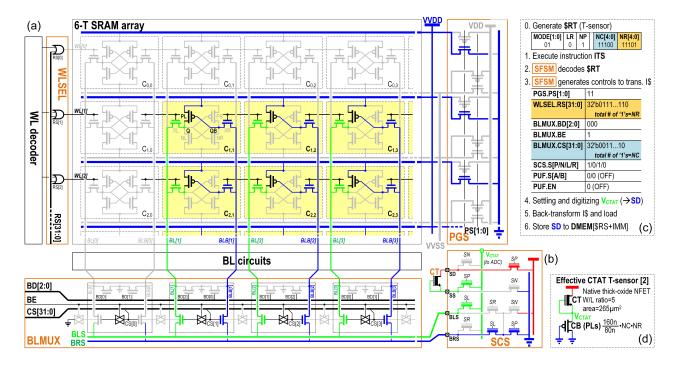

| 5.2  | (a) The SRAM with the added peripherals showing the configuration for T-        |    |

|      | sensor transformation. (b) The schematics of SCS and CT. (c) \$RT and           |    |

|      | control signal values. (d) The effective circuits of the transformed T-sensor   | 91 |

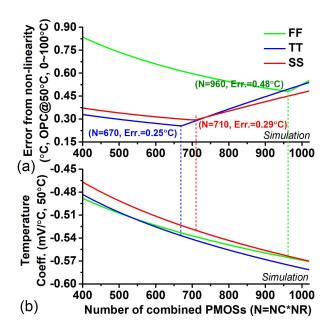

| 5.3  | (a) Accuracy-optimal NC and NR combinations across process corners and          |    |

|      | (b) the corresponding temperature coefficient                                   | 93 |

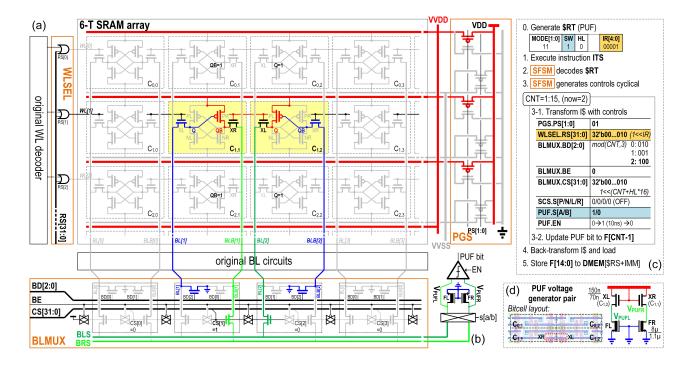

| 5.4  | (a) Circuits configurations for PUF transformation. (b) The schematics of       |    |

|      | the PUF peripherals that contains PUF footers, a comparator and an input        |    |

|      | swapper. (c) \$RT and control signals. (d) The effective circuits of the trans- |    |

|      | formed PUF bitcell                                                              | 94 |

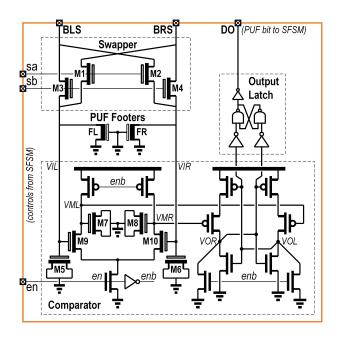

| 5.5  | Schematics of the PUF peripherals                                               | 95 |

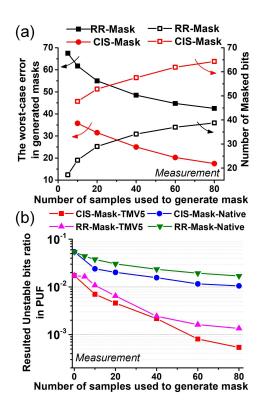

| 5.6  | (a) The accuracies of masks generated by the proposed CIS and the conven-       |    |

|      | tional RR techniques. (b) The unstable bit ratios post mask applications        | 98 |

| 5.7  | (a) ITS and (b) \$RT formats for transformations                                | 96 |

| 5.8  | The proposed µp-SoC microarchitecture. The modified and added portions       |     |

|------|------------------------------------------------------------------------------|-----|

|      | are highlighted in yellow                                                    | 100 |

| 5.9  | The sequences of the $\mu$ P-SoC of executing one ITS instruction            | 101 |

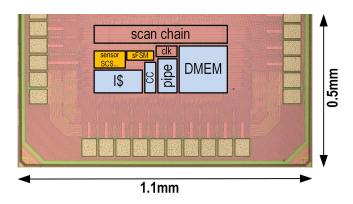

| 5.10 | The die photo of the prototyped $\mu$ P-SoC                                  | 102 |

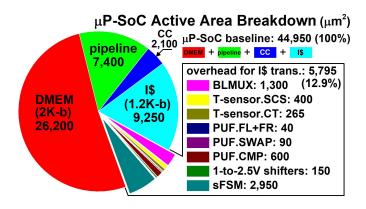

| 5.11 | Detailed area breakdown                                                      | 102 |

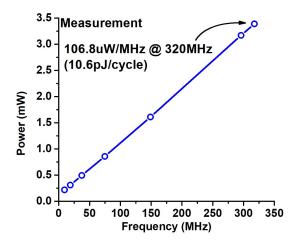

| 5.12 | Clock frequency and power dissipation of the $mu$ P-SoC                      | 103 |

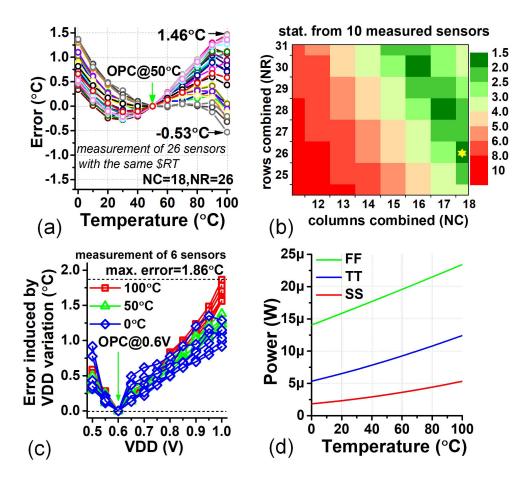

| 5.13 | T-sensor measurement results: (a) Post-OPC accuracy. (b) The post-OPC        |     |

|      | worst-case error across NC and NR combinations. (c) Post-OPC accuracy        |     |

|      | across VDDs. (d) The power dissipation across corners and temperatures       | 104 |

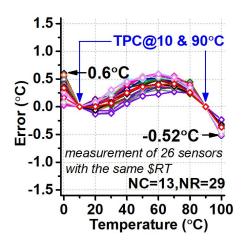

| 5.14 | T-sensor measurement results: The error of the transformed T-sensors after   |     |

|      | TPC                                                                          | 105 |

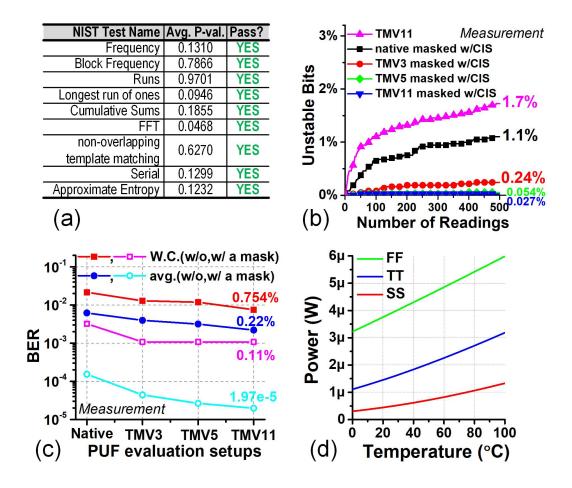

| 5.15 | PUF measurement results: (a) Applicable NIST test results on the 3712-bit    |     |

|      | PUF output. (b) the unstable bit ratios of the PUF with the TMV and CIS.     |     |

|      | (c) The BER with the TMV and CIS. (d) The power dissipation across corners   |     |

|      | and temperatures                                                             | 106 |

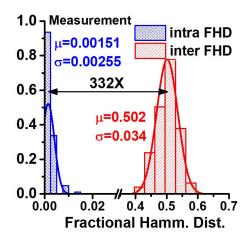

| 5.16 | PUF measurement: Distributions of the inter-PUF and intra-PUF FHDs $$        | 107 |

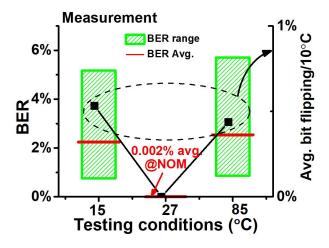

| 5.17 | PUF measurement: BER across temperature variations                           | 107 |

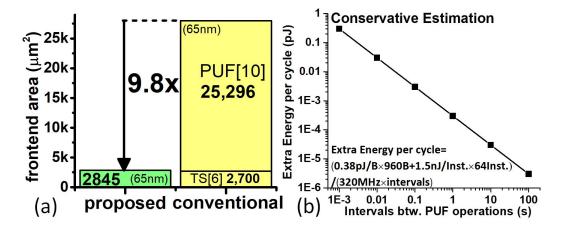

| 5.18 | (a) The area overhead comparisons. (b) Extra energy per cycle conservatively |     |

|      | estimated with PUF operation                                                 | 109 |

# List of Tables

| 2.1 | Summary table of three sensors               | 36  |

|-----|----------------------------------------------|-----|

| 2.2 | Comparison table to the state-of-the-art     | 36  |

| 3.1 | Different PU-SD combinations                 | 48  |

| 3.2 | Sensor gain across different process corners | 52  |

| 3.3 | Comparisons to existing sensing techniques   | 69  |

| 4.1 | Comparison table                             | 82  |

| 5.1 | Comparison table for T-sensor                | 108 |

| 5.2 | Comparison table for PUF                     | 108 |

## Acknowledgments

As I recall seven years of life at Columbia University in New York City, a few vivid memories come to mind. To me, they are important, wonderful, and will never be forgotten.

After completing a bachelor's degree at BUPT, I came to Columbia University to pursue an EE master's degree in 2010. In this fantastic city, I found my true passion and future career path. The process was arduous and not straightforward. Unlike others, I chose to study a variety of fields in the first semester; I took courses in the fields of EE, BME, and CS, and then I changed to neuroscience. I started a research project with Prof. A.A. Lazar and studied related courses.

However, I ultimately realized that I was not sufficiently motivated, as the project required a greater understanding of mathematics and theory. I am more excited about practical and experimental subjects, such as VLSI design. I had some basic knowledge and skills accumulated in the VLSI field, but I hesitated as it was late for a master's student to switch the panel during the last semester. I talked to my father about my thoughts, and he said that he would support my decision unconditionally, even if I were to re-apply for another EE degree program in the VLSI track. My roommate and schoolmate, Jianxun Zhu, who studies radiofrequency circuit design, introduced me to his research field and encouraged me to talk to Prof. Kinget about my dilemma. Prof. Kinget nicely provided his suggestions for my next steps, approved my request to extend my master's degree study, and received me as a research student. Fortunately, with my determination and assistance from my mentor, Karthik Tripurary, and Prof. Kinget, I joined Prof. Mingoo Seok's group as a Ph.D. candidate to start the next page of my study.

No words can describe my sincere gratitude to Prof. Kinget, Jianxun Zhu, my father, and Karthik Tripurary for your kind help, which lights my future path.

During the 3rd year of my Ph.D. research, we enhanced the previous NBTI sensor to a general aging sensor and investigated a more delicate circuit to embed into real SRAM. On the technical side, it went smoother than the previous year, as I accumulated knowledge and skills. With the improved structure and the promising measurement results, I expected another fruitful year; however, my papers were all rejected. Because of the readers' critical feedback, I felt distraught, and I doubted whether the research topic I was pursuing followed industry trends and met specific requirements. That was the darkest period during my Ph.D. Imagine a person who had an encouraging start with ISSCC and JSSC publications, only to lose motivation in the third year. Mingoo detected my frustration and offered help in many ways. On the research side, we went through readers' comments carefully, modified the flows of the experiment accordingly, and demonstrated results systematically. Further, he advised me to investigate the implementation of the technique at the block or system level. On the personal side, he continued to encourage me to persist with my research goal. He also brought me opportunities to interact with peers and referred me to IBM Research for a summer internship. There, I was able to learn about industry trends and talk to experts. Gradually, life became better. We revised our papers, and they were accepted. In the following year, we build a real pipeline processor with aging sensors integrated. Eventually, we proudly demonstrated our novel processor in the CICC. I am highly confident and satisfied with my latest silicon chip from both the technical and spiritual perspectives.

I have received a great deal of support and assistance throughout my Ph.D. study. Without you, I would not have become an independent researcher and understood the power of critical reasoning.

First, I would like to express my sincere gratitude to Professor Mingoo Seok, the principal advisor throughout my Ph.D. study. You offered valuable technical guidance for the research, and you provided considerable spiritual mentoring. I would not have been motivated to finish the degree without your help and encouragement. Your rich knowledge and charming personality inspired me, and it will continue to affect the rest of my life. I also want to extend my thanks to Professor Peter Kinget, my co-advisor. You kindly accepted me as your research student and brought me into the world of VLSI. You also generously provided technical and life advice in the past few years.

Second, I would like to thank other committee members, Professor Martha Kim, Professor Harish Krishnaswamy, and Professor Ioannis Kymissis. Thank you all for your commitment and valuable time to help me toward graduating.

Third, I am grateful to my group colleagues, Seongjiong Kim, Doyun Kim, Jiangyi Li, and Joao Pedro Cerqueira. Thank you all for assisting with my research, especially during the busy tape-out season. I am grateful to CISL peers from neighbor research groups, Jianxun Zhu, Yang Xu, and Ning Guo, for their generous help with CAD tools and chip integration.

Finally, I express my profound thanks to my family for their continuous love and support. I am grateful to my parents for always listening to me, relieving my pressure, and providing emotional and financial support. I am also grateful to my grandma, with whom I spent most of my childhood, for your unconditional trust and timely encouragement.

## Chapter 1

#### Introduction

#### 1.1 Background

In modern deep-scaled CMOS technologies, various silicon-related pitfalls present longterm challenges to microprocessor performance. Such challenges include but are not limited to: (1) local hot spots, which breach the thermal limitations of a microprocessor, and (2) transistor aging, especially NBTI that degrades transistor threshold voltage, ultimately threatening the reliability of the entire memory block. In previous systems, the dummy circuit was placed next to the subject, where the dummy was frequently analyzed and the readout was used to infer the condition of the target. Due to rapidly changing ambient conditions (e.g., temperature and voltage), and the potential scale of the target dimensions, such metrics may not accurately represent the condition of the target; additionally, such temperature sensors and canary circuits occupy a significant amount of area.

Therefore, it would be highly preferable to monitor the target circuit in-situ, i.e., to sense the exact transistor at operation. It is also important to achieve an accurate sensing metric: when the temperature is analyzed, the readout should account for voltage and process variations; while sense the aging degradation, the readout should account for voltage

and temperature fluctuations. Such a feature is called in-field operation. Additionally, the circuits should achieve area-efficiency.

During my Ph.D. research period, I built 4 test chips (one in collaboration with Jiangyi Li) to achieve my research goals.

#### 1.2 Compact Voltage-scalable on-chip temperature sensor

Compact temperature sensors are critical to implement dynamic thermal management (DTM) techniques in high-performance microprocessors ( $\mu$ Ps) and systems on chips (SoC). Those sensors are embedded at multiple locations on a die, and provide fine-grained temperature information to DTM engine, which to maintain the  $\mu$ Ps operate efficiently within thermal budget.

There are three requirements for those temperature sensors. First, sensor front-ends need to be very area efficient. So we opt-out BJT structure. Second, sensor readings need to have a low calibration cost while achieving target accuracy (e.g. absolute <8°C and a relative <3°C). So we avoid to use expensive 2-temperature-point calibration. Third, the sensors should be able to operate at a low supply voltage and robust to VDD fluctuations. This also eliminates the possibility of any BJT-based structures.

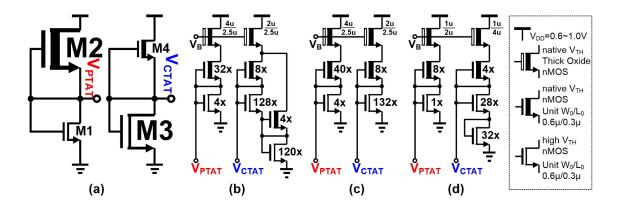

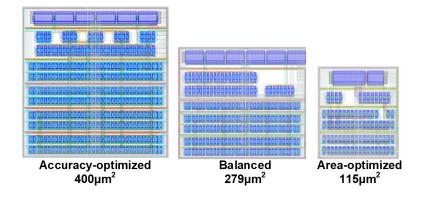

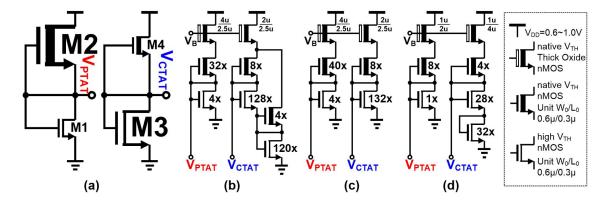

Based on three requirements, we designed a new type of temperature sensors, as shown in fig. 1.1 and fig. 1.2. To achieve small area cost, the sensor only costs 6 or 8 NMOS normal-sized transistors. To achieve low voltage operation, we set the sensors to operate at the sub-threshold region. To achieve good accuracy at the low-cost one temperature point calibration (OPC), we differentiate the readouts of VDD-compensated proportional-to-absolute-temperature (PTAT) and complementary-to-absolute-temperature (CTAT) volt-

Figure 1.1: Structures of proposed sensor front end

Figure 1.2: Layouts of proposed sensor front end

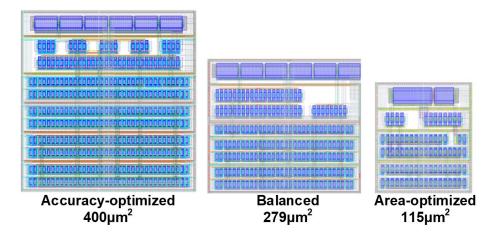

age generators [23]. We implemented three sensor frontend designs on the 65nm CMOS. Three sensor front-ends are presented with different sizes and accuracies to meet different performance-area requirements (area-optimized, balanced, and accuracy-optimized).

The balanced front end achieves a  $14.3 \times$  smaller footprint than the 22nm design in [13], while it exhibits a worst error of less than  $7.0^{\circ}$ C (-3.4°C < error < 3.6°C), after calibration, across 64 sensors in 8 chips. The worst-case measured error among 8 sensors in a chip across 8 chips is  $5.2^{\circ}$ C. Our sensor can operate at VDDs from 0.6 to 1V, whereas none of the other designs in the comparison can operate below 1V. The average error incurred by the voltage scaling is  $0.3^{\circ}$ C. The area-optimized front end has a footprint of  $115\mu m^2$ , and a worst-case error of  $8.8^{\circ}$ C (-2.0 < error <  $6.8^{\circ}$ C) across 64 sensors in 8 chips after calibration. The

accuracy-optimized front end exhibits the per-front-end area of  $400\mu m^2$  which is still 10x smaller than [13] and a worst-case error of 5.4°C (-0.7 < error < 4.7°C).

The compact footprint and the large voltage-scalability of the designs enable the integration of order-of-magnitude more sensor front ends on a chip at a small additional overhead, enabling dense thermal monitoring in modern VLSI systems.

#### 1.3 In-situ and In-field BTI sensors for register file

In modern deeply-scaled CMOS technologies, transistor aging effects such as bias temperature instability (BTI), hot carrier injection (HCI), and time-dependent dielectric breakdown (TDDB) have been one of the major challenges for maintaining long-term reliability of computing systems [26]. In particular, negative bias temperature instability (NBTI) is one of the most critical aging mechanisms, which can increase PMOS threshold voltage ( $V_{TH}$ ) at high temperature when PMOS is negatively biased [27,29,57]. Such  $V_{TH}$  degradation causes digital circuit delay to increase, compromising the maximum clock frequency over chip's lifetime. Recent studies also show that NBTI can be worse for technology scaling [59], confirming its importance in future microelectronics.

NBTI can also degrade robustness of embedded memory circuits [30, 59]. Particularly an 6-transistor (6T) register file (RF) is one of the most vulnerable blocks since it often experiences high temperature due to high switching activities and the heat generated by other digital gates around it. Furthermore, the 6T bitcell typically used in an RF has one of its PMOSs negatively biased (i.e., stressed) during an RF is powered on. Last but not the least, if a bitcell is not written frequently, one of the PMOSs in the bitcell can receive DC stress, which is more detrimental than the AC one [31]. The degradation of  $V_{TH}$  of PMOSs

in bitcells can hurt robustness and performance of an RF. It can reduce the static noise margin (SNM), thus worsening data retention voltage (DRV), read  $V_{MIN}$  and read access time. Note that the bitcell that undergoes the worst degradation determines the robustness and performance of the entire RF it belongs to.

Conventional approaches to mitigate NBTI impacts is to set design margins based on a coarsed block-level estimation. Those margins including (1) Upsizing device size to reduce random variations and (2) Operate RF block at a certain amount of higher VDD voltage than pre-silicon block  $V_{MIN}$ , a.k.a, a voltage margin. The coarse estimation leads to conservative margin that degrades the area effeciency as well as increase power consumptions. Such margin is pessimistic and unnecessary because the only one or tow worst-case bitcells limit the perofrmance of the entire RF block [32].

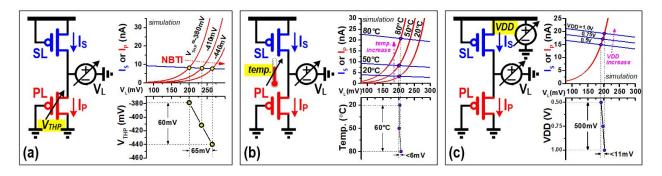

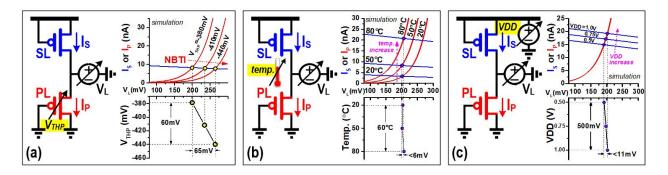

To tackle this challenge, we propose techniques to dynamically monitor and decelerate NBTI degradation in an RF with a focus to enable/enhance three critical abilities, namely in-situ monitoring, in-field monitoring, and post-deployment NBTI management [55]. First, we devised an in-situ monitoring technique, i.e., directly sensing  $V_{TH}$  of a target PMOS in a bitcell instead of using of replica/canary circuits [33,35]. Second, we have pursued to enhance robustness in monitoring so as to enable in-field monitoring (post-deployment). Robustness against temperature and power supply voltage (VDD) variations is paramount since it is non-trivial to control such parameters in field as shown in fig. 1.3.

Finally, we developed a software framework for dynamic reliability management (DRM). During chip's lifetime, we can execute the framework routinely (e.g., every several months) in the maintenance mode, which monitors  $V_{TH}$  degradation, evaluates the degree and the progressing rate of NBTI degradation, and analyzes the skew of  $V_{TH}$  degradations between

Figure 1.3: Demonstration of  $V_{TH}$  sensing capability and robustness

two PMOSs in a bitcell. In addition to those monitoring, the framework can also create recover vectors (RV) using the skew information of bitcells. Written into bitcells opportunistically, RVs can partially recover the more-aged one of two PMOSs in each bitcell and thereby decelerating SNM and DRV degradation.

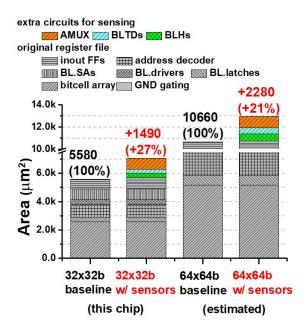

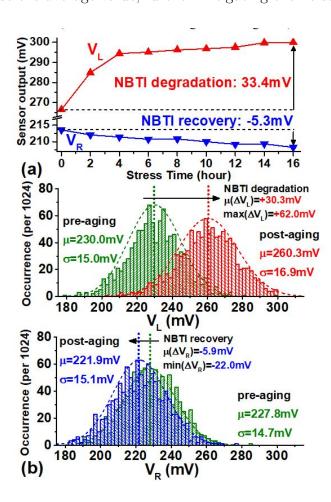

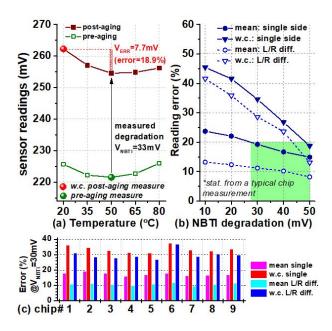

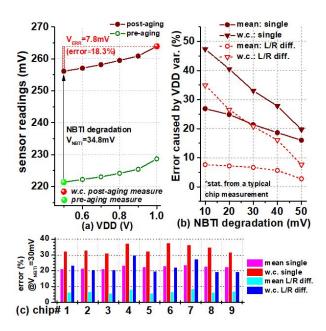

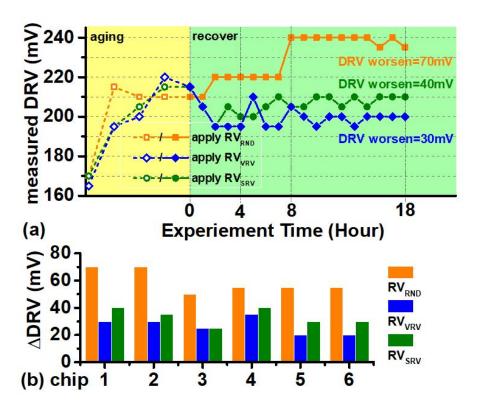

We prototype test chips, each of which includes a 1-Kb RF with the proposed techniques, in a 65nm CMOS. The measurement results confirm the in-situ and in-field capability with the average error of 19% against temperature variation (20-80C) and that of 21.8% against VDD variations (0.5-1V) in monitoring an NBTI-induced  $V_{TH}$  degradation larger than 30mV. Those errors are respectively 4.4X and 3.4X smaller than the estimation of previous work [39]. We also confirm that RVs created based on our monitoring technique can successfully slow down DRV degradation: in our 16-hour accelerated aging experiments, the RFs that store the RVs from the proposed technique exhibit 30mV to 70mV less DRV degradation in average than RFs storing random fixed values. The area overhead of the proposed technique is 27% for a 1-kb RF and 21% for a 4-kb RF.

# 1.4 Circuit, architecture and run-time framework for memory reliability management in a microprocessor

In deeply scaled VLSI systems, device aging effects, such as bias temperature instability (BTI) have been identified as a key reliability challenge. Especially, embedded caches (\$) and register-files (RF) are highly vulnerable to NBTI since they use intrinsically sensitive circuits and become hot as nearby logic circuits are actively switching and dissipating heat. What's worse is that the single worst-case bitcell can determine the reliability of the entire memory block. It is paramount to manage the reliability of the embedded memory over the chip's lifetime.

To manage reliability it is cost-prohibitive to disassemble working  $\mu$ P and send the chip to a laboratory. Thus, a key requirement is to perform the reliability management without disassembly, i.e., post-deployment and in-field. In this work, we propose such a solution, including circuits, a microarchitecture and a runtime software framework to implement a post-deployment in-field memory reliability management.

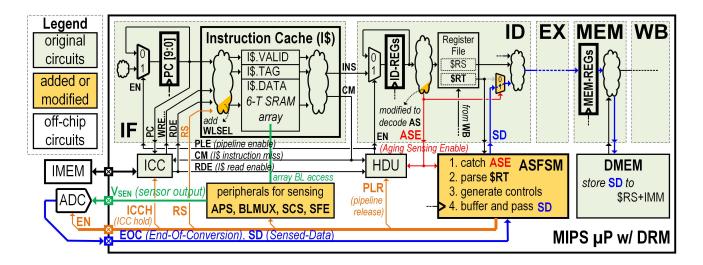

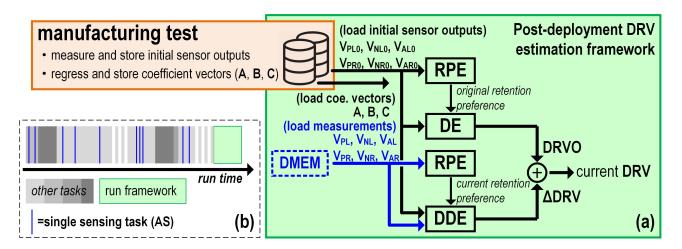

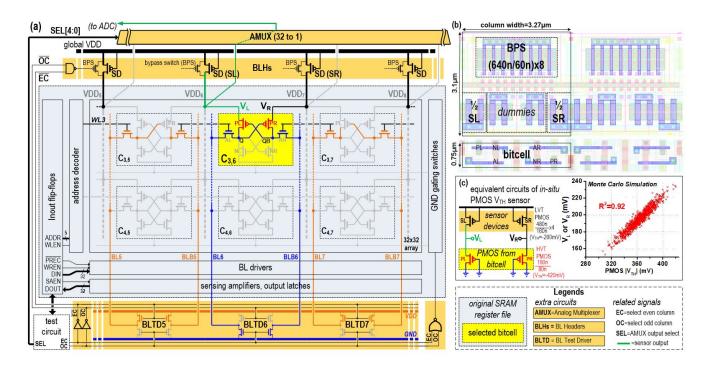

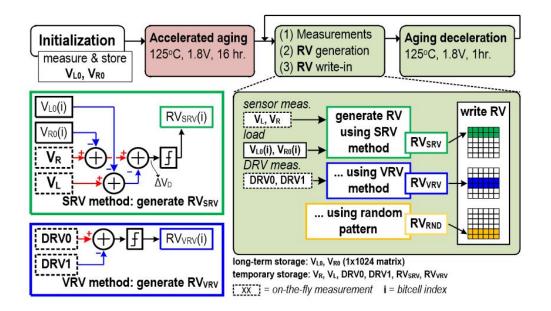

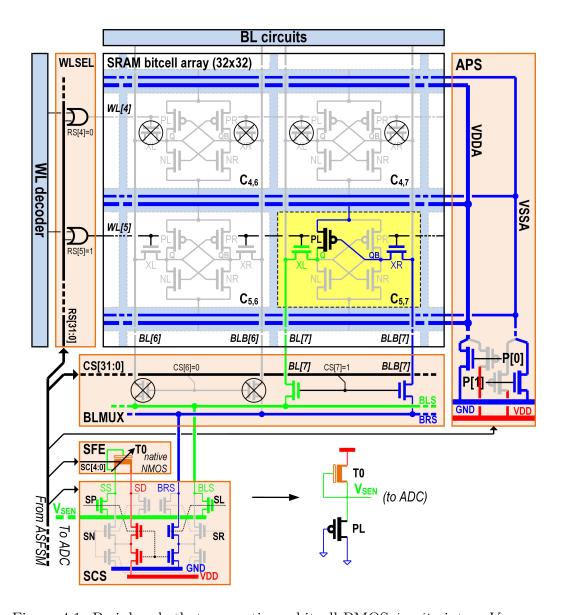

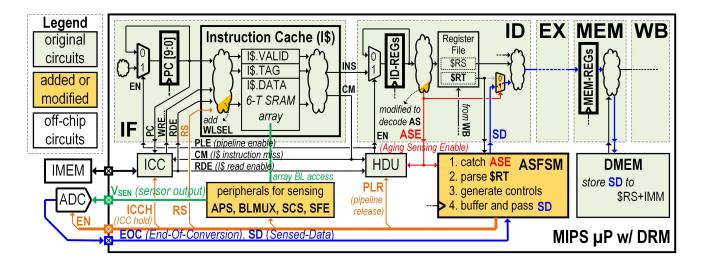

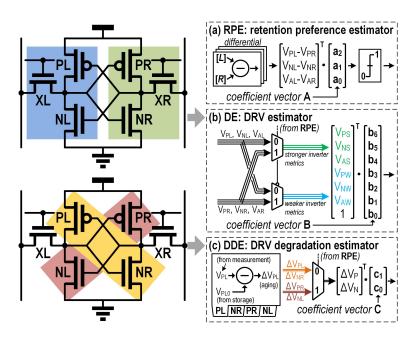

Figure 1.4: Microprocessor architecture of proposed DRM technique

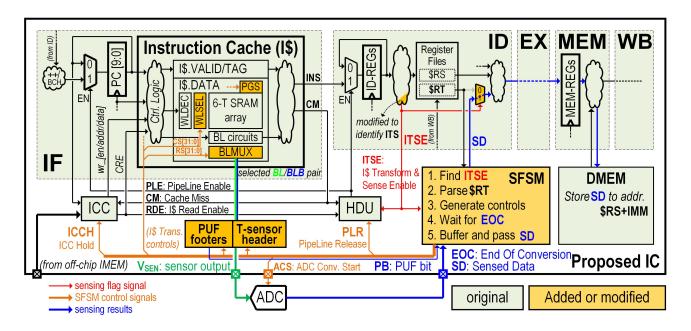

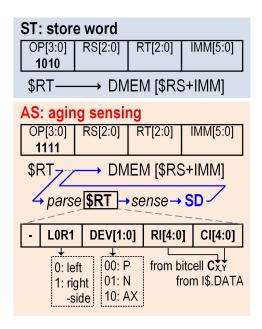

We prototyped a test chip with the implementation of previous developed NBTI sensing circuits into the circuit of instruction cache (I\$) of a standard 5-stage MIPS  $\mu$ P (fig. 1.4). we devised a RISC microarchitecture having a new instruction (called AS) to trigger the reliability management. The  $\mu$ P can execute the AS instruction opportunistically during its regular operation to sense the  $V_t$ s of its bitcells, thereby evaluate its aging effects. The sensor is able to *in-situ* sense the  $V_t$  of any one of six transistors in any bitcell. The sensing readout is robust against temperature variations and thus very suitable to the on-the-fly sensing, which it is impractical to regulate temperature rapidly.

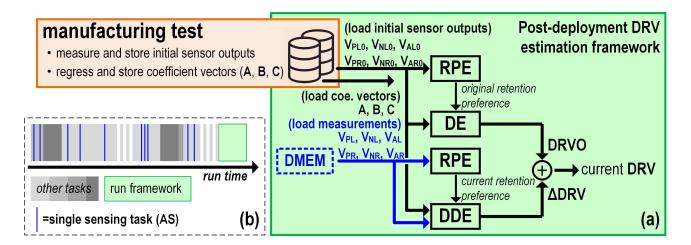

Figure 1.5: (a) Sensing task assignment (b) Framework to estimate current DRV

We also proposed a runtime software framework (fig. 1.5) to convert the low-level  $V_t$  measurements to circuit-/architecture-level metrics, i.e., the data retention voltage (DRV). The framework is composed of basic operations  $(+, \times)$  and can be accomplished by original instructions of the  $\mu$ P ISA. Such extraction is critical for operating systems and firmware as they need high-level metrics to run dynamic reliability managements (DRM), such as to decelerate aging in bitcells [65], to reduce the guard band in dynamic voltage scaling of memory during the standby mode, and to balance aging degradations among memory

## 1.5 An area-efficient SoC with instruction cache transformable to a temperature sensor and a PUF

Heading towards the era of Internet of Things (IoT), it is critical for integrated-circuit research and development to deliver compact, low-cost, and dependable edge devices with various capabilities, e.g., sensing, computing, communication, and security [67]. This challenge has motivated to integrate an increasing number of components and function blocks into a Microprocessor-based System-on-Chip ( $\mu$ P-SoC) to shrink system footprint and associated cost [82, 88, 89]. However, such integration often incurs silicon area increase since most of analog, mixed-signal, and digital circuits require substantial amounts of silicon area to implement fast, accurate, and robust functions.

An ambient temperature sensor (T-sensor) and a Physically Unclonable Function (PUF) are two widely used components in IoT devices. The former is a critical building block for environmental monitoring; the latter is a notable security macro used for secret key generation for cryptography and chip-ID generation for authentication. However, implementing dedicated circuits for those functions requires non-negligible silicon area, especially when they are designed for high accuracy and robustness [68–77,79,84,86–89].

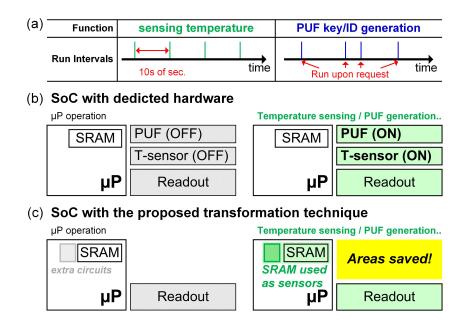

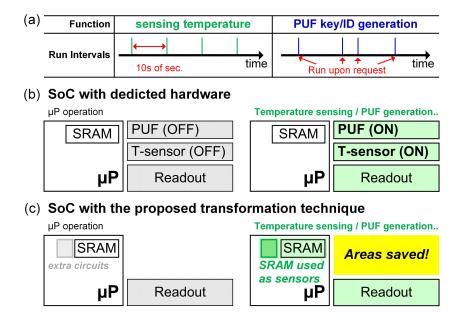

It is noteworthy that in many applications, T-sensors and PUFs exhibit low duty cycle, making the approach of dedicated hardware further inefficient in area. As shown in fig. 5.1(a), for example, a T-sensor can be only active every several seconds (or even longer) since ambient temperature changes rather slowly [82,88]. A PUF also needs to be active only upon a request for e.g., encrypting and decrypting messages, and chip authentication processes

[85,86]. Therefore, the dedicated hardware can be idle for most of the time.

Figure 1.6: (a) Low duty cycle operation such as ambient temperature sensing and PUF. (b) Dedicate hardware implementation of those functions compared with conventional design. (c) Proposed transformation approach can save area.

Therefore, we aim to address such area inefficiency, and propose a novel technique to transform the existing SRAM in the instruction cache (I\$) of a  $\mu$ P into a T-sensor or a PUF (fig. 1.6(c)). This hardware recycling approach can reduce silicon footprint while integrating more features on a chip. To enable such transformation, we made a minimal amount of change in the SRAM circuits, Instruction Set Architecture (ISA), and pipeline control logic. The outputs of the transformed T-sensor and PUF operations are stored in the data memory of the  $\mu$ P for post digital processing.

We prototyped a  $\mu$ P-based SoC with the proposed technique in a 65nm general-purpose CMOS, fig. 5.1. The  $\mu$ P can operate at 320MHz at 1V supply voltage  $(V_{DD})$  and consumes 10.6 pJ/cycle. The transformed T-sensor achieves an error of -0.5/+1.5°C after One-temperature-Point Calibration (OPC) across 26 instances. It achieves low  $V_{DD}$  sensitivity,

Figure 1.7: The proposed µp-SoC microarchitecture. The modified and added portions are highlighted in yellow.

exhibiting only 0.46°C error for 100mV  $V_{DD}$  variation from 1V to 0.5V. The transformed PUF also achieves a desirable randomness: the analog differential output shows a normal distribution with  $\mu$ =-1.3mV and  $\sigma$ =31.2mV; the digitized bitstream passes all the applicable NIST tests and achieves 0.502 inter-PUF Fractional Hamming Distance (FHD). It also achieves robustness comparable to the state of art: 0.027% unstable bit ratio and 1.97 × 10<sup>-5</sup> Bit Error Ratio (BER) after Temporal Majority Voting (TMV11) and Comparator Input Swapping (CIS) based masking.

The proposed transformation capability increases the area of the baseline  $\mu$ P by 12.9% (9.2% only for the T-sensor and 9.1% only for the PUF). The first 6.3% is for the update in the SRAM circuits and the next 6.6% is for the microarchitecture modification. The standalone T-sensor [73] and PUF [76] circuits achieving the similar accuracy and robustness would consume more silicon area, that would be 62.9% of the baseline  $\mu$ P area.

### Chapter 2

## Compact, Voltage-scalable on-chip Temperature Sensor

#### 2.1 Motivation

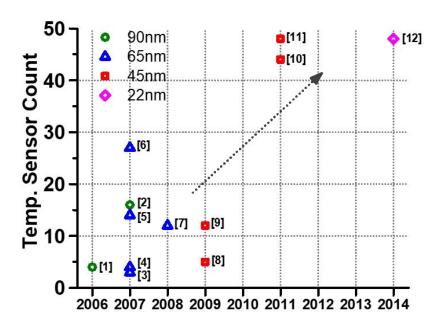

Compact temperature sensors are critical to implement dynamic thermal management (DTM) techniques in high-performance microprocessors ( $\mu$ Ps) and systems on chips (SoC). Those sensors are embedded at multiple locations on a die, and the temperature information sensed is used to maintain the chip operation within thermal constraints. While existing sensor designs [13–18] achieve small area and high accuracy, emerging technology trends such as multi-core architectures, 3D-integration, fin-fet devices, and low-voltage operation require the development of sensors of better performance that meet stricter requirements.

There are three requirements for those emerging applications.

First, sensors need to be very area efficient. Recently, the number of sensors embedded on a digital VLSI system has rapidly increased (fig. 2.1). Meanwhile, the continuing increasing the level of integration (3D integration, SiP, etc.) and consequently the number of thermal hot spots, future digital VLSI systems will have more locations that require thermal monitoring. In order to reduce the overhead while monitoring all of those locations, the sensor footprint needs to be minimized. Additionally, a compact footprint ensures design flexibility

Figure 2.1: Trends in numbers of on-chip temperature sensors in  $\mu$ Ps and SoCs

as sensor's location is often determined at the later stages of the design process [13].

Second, sensors need to have a low calibration cost while achieving target accuracy (e.g. absolute <8°C and a relative <3°C).

Third, the sensors need to be able to operate at a low supply voltage. Sub-1V operation for digital VLSI systems is being extensively explored, as part of the ongoing request to reduce power consumption. The conventional sensors hardly operate below 1V, thereby requiring additional power distribution or local power regulation. The ability to operate below 1V eliminates those overheads.

Existing published temperature sensor designs [13–18] hardly meet above requirements simultaneously. BJT-based sensors [13, 14] achieve good accuracies but cost large area and require above 1V VDD. A lateral CMOS diode based sensor [15] and CMOS  $V_t$ -based design [17] achieve small foot print but require expensive two temperature point calibration (TPC) to satisfy accuracy target.

Therefore, we are motivated to propose a new type of temperature sensor design. To achieve small area cost, the sensor only costs 6 or 8 NMOS normal-sized transistors. To achieve low voltage operation, we set the sensors to operate at the sub-threshold region. To achieve good accuracy at the low-cost one temperature point calibration (OPC), we differentiate the readouts of VDD-compensated proportional-to-absolute-temperature (PTAT) and complementary-to-absolute-temperature (CTAT) voltage generators [23]. To meet different performance-area requirements, we implemented three sensor frontend designs on the 65nm CMOS. Three sensor front ends with different sizes and accuracies, namely area-optimized, balanced, and accuracy-optimized.

#### 2.2 Operation Principle

Figure 2.2: Structures of proposed sensor front end

fig. 2.2(a) shows the basic structure of the proposed sensor front-end, which contains a PTAT and a CTAT voltage generator with outputs  $V_{PTAT}$  and  $V_{CTAT}$ . Transistor M2, M4 are native- $V_t$  NMOS and transistor M1, M3 are thin-oxide, high- $V_t$  NMOS at diode-connection. To generate PTAT voltage, M2 is sized larger than M1; similarly, M4 is sized smaller than M3 to generate CTAT voltage. The  $V_{PTAT}$  and  $V_{CTAT}$  are sensed, differentiated and digitized

at the back-end read-out circuits. The read-out circuits are shared across all sensor front ends. fig. 2.2(b), (c) and (d) show the actual implementations of the three sensor front ends. Several supplementary devices are added to the basic structure to improve various metrics. fig. 2.2(b) shows the design for optimal accuracy at the larger footprint (referred to as accuracy-optimized design); fig. 2.2(c) shows the design for balancing area and accuracy (balanced design); and fig. 2.2(d) shows the design for minimizing area (area-optimized design). fig. 2.3 shows the layouts of the front ends. The areas of the three sensor front ends are  $400\mu m^2$ ,  $279\mu m^2$  and  $115\mu m^2$ .

Figure 2.3: Layout snapshots of three proposed sensor front ends

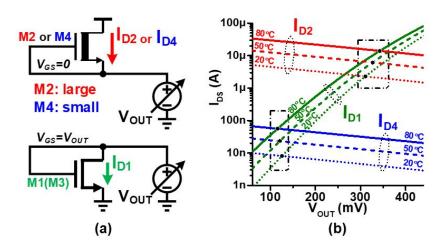

The operation of the PTAT or CTAT generator can be explained through the device current-voltage (I-V) characteristics between the top and bottom transistors. fig. 2.4(a) shows the model that we used: either PTAT or CTAT generator contains a top transistor (M2 or M4) with gate-source shorted (a.k.a. a single-transistor current source with zero  $V_{gs}$ ) and a bottom transistor (M1 or M3) configured as diode. Then we split the structure into top and bottom parts from the output node of the sensor. Each breaking node is connected to an ideal voltage source and force the voltage to  $V_{OUT}$ . To demonstrate different mechanisms

Figure 2.4: Simulation setups for the I-V characterizations

between PTAT and CTAT, we chose two sizes for top transistor (M2 is bigger than M4). To ensure same reference, we use only one size for bottom transistor (M1). Then we swept  $V_{OUT}$  from 50 to 450mV at three different temperatures. The channel currents (Id) of transistors are measured and plotted in fig. 2.4(b). Green lines represent Id of bottom transistor, increasing with  $V_{OUT}$  and temperature. Blue lines represent Id of the smaller top transistor (M4), decreasing with  $V_{OUT}$  but increasing with temperature. Red lines represent Id of the bigger top transistor (M2) with similar trend, however, the absolute current value is nearly three magnitude bigger than that of M4.

The intersect points between blue and green curves are the output of CTAT generator (M4 with M1). The intersect points between red and green curves are the output of PTAT generator (M2 with M1). Both intersections are at deep sub-threshold region. fig. 2.5(a) shows the zoom-in of Id intersection between M4 (smaller top) and M1, the  $V_{OUT}$  is CTAT. fig. 2.5(b) shows the zoom-in of Id intersection between M2 (bigger top) and M1, the  $V_{OUT}$  is PTAT.

The analytical equation for  $V_{PTAT}$  and  $V_{CTAT}$  can be derived similarly as for the compact

Figure 2.5: The zoomed-in temperature characteristics of the CTAT and PTAT generator

2-transistor voltage reference circuits [19]. Here, we focus only on  $V_{PTAT}$  since the equations for  $V_{CTAT}$  are the same except for the different transistor notations. The sub-threshold current is Equation (1)

$$I_D = \mu C'_{ox} \frac{W}{L} (n-1) \phi_t^2 e^{\frac{V_{gs} - V_t}{n\phi_t}} (1 - e^{-\frac{V_{ds}}{\phi_t}})$$

(1)

where  $\mu$  is the carrier mobility,  $C'_{ox}$  is sheet oxide-capacitance density, W, L are the width and length of the transistor,  $V_t$  is threshold voltage, n is subthreshold slope,  $V_{GS}$  is gate-source voltage,  $V_{DS}$  is drain-source voltage, and  $\phi_t$  is the thermal voltage. Based on Equation (1), the current equations for M1 and M2 can be derived as Equation (2)

$$\begin{cases}

I_{D1} = \mu_1 C'_{ox1} \frac{W_1}{L_1} (n_1 - 1) \phi_t^2 e^{\frac{V_{PTAT} - V_{t1}}{n_1 \phi_t}} \\

I_{D2} = \mu_2 C'_{ox2} \frac{W_2}{L_2} (n_2 - 1) \phi_t^2 e^{-\frac{V_{t2}}{n_2 \phi_t}}

\end{cases}$$

(2)

Since M1 and M2 are connected in series,  $I_{D1}$  and  $I_{D2}$  in Equation (2) are identical so that we can solve the  $V_{PTAT}$  as Equation (3)

$$V_{PTAT} = \underbrace{n_2 \ln \left( \frac{\mu_1}{\mu_2} \cdot \frac{C'_{ox1}}{C'_{ox2}} \cdot \frac{W_1 L_1}{W_2 L_2} \cdot \frac{n_1 - 1}{n_2 - 1} \right) \frac{k}{q} \cdot T + \underbrace{V_{t2} - \frac{n_2}{n_1} V_{t1}}_{\text{offset}}$$

(3)

where k is the Boltzmann constant and q is the electron charge. The temperature sensitivity (slope of  $V_{PTAT}$ ) is, to the first order, determined by the size ratio between M1 and M2. The offset of  $V_{PTAT}$  is a function of process parameters  $V_t$  and n.

#### 2.3 Accuracy Improvements

#### 2.3.1 Output Range Tuning

We optimized the sensor front end to ensure that all transistors to operate in subthreshold and in saturation (i.e.,  $V_{DS}$  is several times larger than  $\phi_t$ ) across temperature and process variations. This is critical because a high  $V_{DS}$  ensures that the last term in Equation (1) to be negligible, thereby reducing the  $V_{DD}$  dependency and improving the linearity of  $V_{PTAT}$  and  $V_{CTAT}$  over temperatures.

In order to ensure sufficiently high  $V_{DS}$ s for transistors, we connect the gates of the top transistors to the outputs, as shown in fig. 2.2(a). This is a modification of the original topology in [19], and raises the level of  $V_{PTAT}$  by approximately  $1/2(V_{t2} - V_{t1})$  and that of  $V_{CTAT}$  by approximately  $1/2(V_{t4} - V_{t3})$ , contributing to sufficiently higher  $V_{DS}$ s for the bottom transistors (M1, M3). In addition, we carefully chose the device types to give  $V_{PTAT}$  and  $V_{CTAT}$  optimal offsets in their output voltage, i.e. the second term in Equation (3). The optimal offset is 1/2VDD since it ensures largest  $V_{DS}$ s for both top and bottom transistors

of the PTAT or CTAT generators. However, as the offset is roughly the difference of Vts of the top and the bottom transistors, it tends to be less than 1/2VDD.

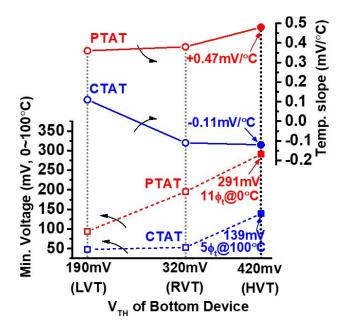

Figure 2.6: The output range and slope of PTAT and CTAT generator

Therefore, we explored the use of three different types of devices and found the lowest values of the  $V_{PTAT}$  (at 0°C) and  $V_{CTAT}$  (at 100°C). As shown in fig. 2.6, using high- $V_t$  NMOSs for the bottom devices provides higher offsets ( $V_{PTAT,MIN} = 291 \text{mV} = 11 \phi_t$  at 0°C and  $V_{CTAT,MIN} = 139 \text{mV} = 5 \phi_t$  at 100°C). This device choice further enables a sufficient temperature sensitivity of 0.47 mV/°C for  $V_{PTAT}$ , and -0.11 mV/°C for  $V_{CTAT}$ .

For the accuracy-optimized and area-optimized front ends, we added a diode and a temperature- and voltage-compensated voltage reference circuit [19], respectively, as a footer. The footers can increase the offset of  $V_{CTAT}$  which is typically smaller than  $V_{PTAT}$  and limits the accuracy of sensor front ends.

#### 2.3.2 Differential Read-out

In order to improve linearity over temperature even in the presence of process variations, we propose a differential read-out scheme where the difference between  $V_{PTAT}$  and  $V_{CTAT}$  is used to measure temperature. Good linearity over temperature is critical to reduce errors after OPC. Using either  $V_{PTAT}$  or  $V_{CTAT}$  alone causes poor linearity since some of the parameters determining the temperature-slope of  $V_{PTAT}$  and  $V_{CTAT}$ , namely n,  $\mu$ , and  $V_t$ , are temperature dependent [20, 21]. Moreover, those parameters vary with process, further degrading linearity.

The differential reading scheme mitigates the impact of those nonlinear parameters on the temperature-slope of  $V_{PTAT}$  or  $V_{CTAT}$ . Now the temperature-slope is mainly determined by transistor sizing ratios after canceling process-dependent parameters. Both  $V_{PTAT}$  and  $V_{CTAT}$  have form of Equation (3), we can find the expression for  $V_{DIFF} = V_{PTAT} - V_{CTAT}$ as Equation (4)

$$V_{DIFF} \approx \underbrace{n_1 \ln\left(\frac{W_1 W_4 L_2 L_3}{W_2 W_3 L_1 L_4}\right) \frac{k}{q}}_{\text{slope}} \cdot T - \Delta V_{t1,3} + \frac{n_1}{n_2} \Delta V_{t2,4}$$

$$\tag{4}$$

where  $\Delta V_{ti,j}$  is  $V_{ti} - V_{tj}$ . Since transistors {M1,M3} and {M2,M4} are the same type, it is reasonable to assume that the  $T_{NOM}$  values and temperature-dependencies of the pairs {n1,n3}, {n2,n4}, { $\mu_1,\mu_3$ }, { $\mu_2,\mu_4$ }, { $V_{t1},V_{t3}$ }, { $V_{t2},V_{t4}$ }, { $C'_{ox1},C'_{ox3}$ } and { $C'_{ox2},C'_{ox4}$ } are tracking each other across temperatures and process variations. Equation (4) clearly shows that the sources of nonlinearity, i.e. n,  $\mu$ , and  $V_t$ , are mostly canceled out.

In addition to reduce nonlinearity, the proposed differential reading scheme can mitigate

the impact of systematic process variations. Systematic variations modulate the parameters of the same transistor type in similar directions. As shown in Equation (4), the use of  $V_{DIFF}$  cancels out most of the dependencies of systematic process variations, comparing with the single  $V_{PTAT}$  (Equation (3)) or  $V_{CTAT}$ .

Although removing most of the temperature and process-dependent parameters  $(\mu, n)$  in the slope term, the slope of  $V_{DIFF}$  still suffers from local mismatches, which hurt the accuracy. The expression of  $V_{DIFF}$  can be expanded further to investigate the impacts from local mismatches. The temperature dependency of threshold voltage  $(V_t)$  is given by Equation (5)

$$V_t = V_{t0} + (K_1 + K_2 V_{BS}) \left(\frac{T}{T_{NOM}} - 1\right)$$

(5)

where  $K_1$  and  $K_2$  are temperature coefficients of  $V_t$ ,  $T_{NOM}$  is the reference temperature. By plugging this into Equation (5), we can derive the explicit expression of  $V_{DIFF}$ , as shown in Equation (6)

$$V_{DIFF} \approx \underbrace{\left[n_{1} \ln \left(\frac{W_{1}W_{4}L_{2}L_{3}}{W_{2}W_{3}L_{1}L_{4}}\right) \frac{k}{q} - \frac{\Delta K_{1,3}}{T_{NOM}} + \frac{n_{1}}{n_{2}} \frac{\Delta K_{2,4}}{T_{NOM}}\right] \cdot T}_{\text{slope}} + \underbrace{\frac{n_{1}}{n_{2}} (\Delta V_{t0-2,4} - \Delta K_{2,4}) - (\Delta V_{t0-1,3} - \Delta K_{1,3})}_{\text{offset}}$$

(6)

where  $\Delta K_{1,3}$  is the mismatch of  $K_1$  between transistor {M1,M3};  $\Delta K_{2,4}$  is the mismatch of  $K_1$  between transistor {M2,M4}. Body effect coefficients  $K_2$  is ignored since the value is much smaller than  $K_1$ .

As shown in Equation (6), the offset term, which is insensitive to temperature, can be removed after OPC. The slope term contains more parameters than Equation (4) after expansion. The slope variation of  $V_{DIFF}$  is caused by (1) process variation of n1, (2) mismatches between four transistors' dimension, (3) mismatch of  $K_1$  across four transistors, (4) mismatch of n between transistor {M1,M2}. The straight forward approach to reduce slope variation is to upsize W and L, which reduces the variability of such parameters as W, L, n and  $\Delta K_1$ . This is pursued in this paper. Another way to further improve the variability might be to use the common-centroid layout technique between PTAT and CTAT generators. This can mitigate the parameter mismatches due to gradient variation.

Figure 2.7: Differential read improves linearity

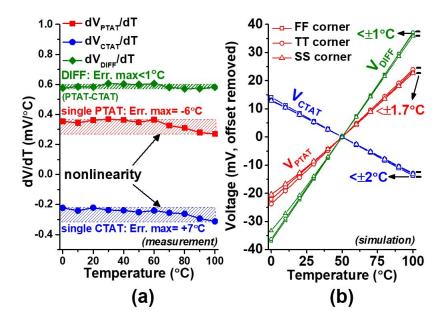

Measurement results confirm the reduced impact of the temperature dependency of those parameters on the linearity of  $V_{DIFF}$ . As shown in fig. 2.7(a), when using either  $V_{PTAT}$  or  $V_{CTAT}$  only, the poor linearity over the temperature range of 0 to 100°C can cause -6°C or +7°C error after OPC, respectively. The use of  $V_{DIFF}$  achieves drastically better linearity,

resulting in an error less than 1°C after OPC. This is also confirmed by the process-corner simulations. As shown in fig. 2.7(b), the use of  $V_{DIFF}$  has errors of only  $\pm 1$ °C across FF, TT, and SS process corners, while the use of either  $V_{PTAT}$  or  $V_{CTAT}$  can cause 1.7 to 2X larger errors.

# 2.3.3 Supply-voltage Scalability

Dynamic voltage scaling (DVS) is a popular technique in today's digital VLSI systems to reduce power consumption. The VDD is dynamically modulated to less than 1V when lower performance demands allow to opportunistically save energy. Temperature sensors that can work below 1V can share power grids with the digital circuits. The existing sensors, however, cannot operate at sub-1V supplies; they need additional power distribution and local regulation, causing a significant area overhead. In order to make the sensors to use digital power rails, it is further critical to achieve a good power-supply reject ratio (PSRR). In the proposed design the low-frequency PSRR (LF-PSRR) is particularly important since the low-pass-filter like VDD-to-output behavior of PTAT and CTAT generators has a good high-frequency PSRR [19].

The proposed differential reading can improve LF-PSRR, by canceling the error caused by the common-mode change in  $V_{PTAT}$  and  $V_{CTAT}$  due to VDD scaling. The total output change in  $V_{PTAT}$  and  $V_{CTAT}$  over VDD-scaling can be decomposed into a differential mode error  $(DME = \Delta V_{PTAT} - \Delta V_{PTAT})$  and a common mode error  $(CME = (\Delta V_{PTAT} + \Delta V_{PTAT})/2)$ , where  $\Delta V_{PTAT}$  and  $\Delta V_{CTAT}$  are the change of  $V_{PTAT}$  and  $V_{CTAT}$  for a given VDD change.

In order to remove the remaining DME, as shown in fig. 2.2(b)(c) and (d), we added cascode devices on the top and biased them at VB. Thick-oxide native-Vt NMOSs were chosen

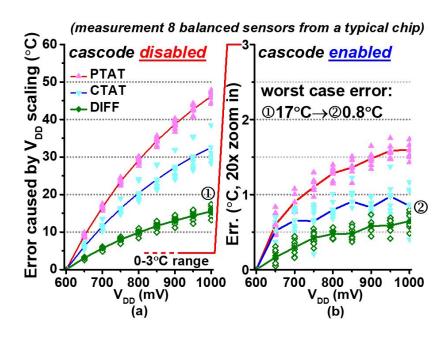

for the cascode devices for two reasons. First, these devices have only a small amount of gate-leakage. Second, their Vt is close to zero, allowing a bias voltage (VB) lower than VDD which can be generated by an on-chip low-voltage low-power voltage reference circuit like in [19]. fig. 2.8(a) and (b) show the error-reduction achieved by using the differential-reading scheme and employing the cascode devices, respectively. The former achieves approximately 10dB improvement, and the latter can achieve additional 26dB in LF-PSRR. The resultant measured error is 0.8°C for a VDD scaling from 1V down to 0.6V in a typical chip. Besides using cascode devices, increasing transistor length could be another way to improve LF-PSRR, but this would cause an area penalty.

Figure 2.8: Differential reading achieves smaller error across the VDD scaling

#### 2.3.4 Noise

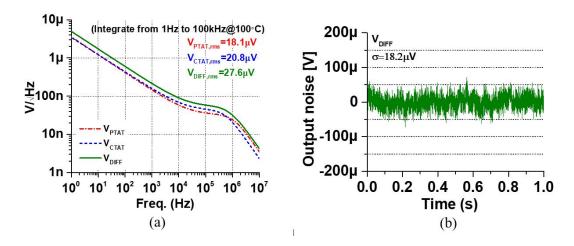

The noise performance of the sensor front ends have been investigated with simulations. fig. 2.9(a) shows the output noise spectrum of the balanced front end design at 100°C.

Figure 2.9: Noise simulation

Flicker noise with a corner frequency of about 10 kHz dominates. The differential reading scheme slightly increases the noise output compared to reading either  $V_{PTAT}$  or  $V_{CTAT}$ . The integration of the  $V_{DIFF}$  noise spectrum from 1Hz to 100kHz is 27.6 $\mu$ VRMS, which is only 14.5ppm of the nominal  $V_{DIFF}$  value of 190 mV at 100°C. As shown in fig. 2.9(b), we also performed transient noise simulations. The root-mean-square (rms) value of the noise output of  $V_{DIFF}$  is found to be 18.2 $\mu$ VRMS. This corresponds to a worst-case  $\pm 3\sigma$  error of 0.19°C.

#### 2.4 Read-out conditioning circuit design

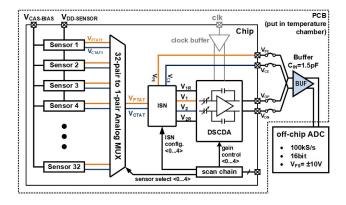

Figure 2.10: Test-chip block diagram

As shown in fig. 2.10, we designed a test chip that has 32 sensor front ends with a

shared back end. The back end comprises of a 32-to-1 two-channel analog multiplexer, an input switch network (ISN), and an on-chip differential switched-capacitor difference amplifier (DSCDA). The analog multiplexer takes 32 output pairs (the  $V_{PTAT}$  and  $V_{CTAT}$  of 32 sensor front ends) and passes one such pair to the ISN. The ISN then convey the inputs to the DSCDA. The analog voltage from the amplifier ( $V_{OP}$ ,  $V_{ON}$ ) is digitized by an off-chip analog-to-digital converter (ADC). Alternatively, the on-chip amplifier can be bypassed via the ISN. The ISN the produces  $V_{PE}$  and  $V_{CE}$  which are the outputs of the selected sensor front end.  $V_{PE}$  and  $V_{CE}$  can be sensed with an off-chip buffer and then digitized by the ADC. Both the analog multiplexer and the ISN use thick-oxide devices in order to eliminate gate-leakage. Since the  $V_{PTAT}$  and  $V_{CTAT}$  are less than 0.4V across 0 to 100°C, NMOS-only switches can be used instead of transmission gates, which is more area efficient.

Figure 2.11: DSCDA schematics

fig. 2.11(a) shows the schematic of the DSCDA, which consists of a classical 2-stage folded-cascode fully differential amplifier (fig. 2.11(b)) and two symmetric programmable switched-capacitor banks (CS1 and CS2). In order to minimize the impact of input-offset  $(V_{OS})$  and low-frequency noise, auto-zero double-sampling [21] is used in the amplifier. As shown in fig. 2.11(c),  $C_{S1}$  and  $C_{S2}$  can be configured from  $1 \cdot C_{S0}$  to  $(16+8+4+2+1) \cdot C_{S0}$ , where  $C_{S0}$  is 150 fF. The holding-capacitors  $(C_{H1}, C_{H2})$  are 150 fF each. MIM capacitors are used to implement these capacitors.

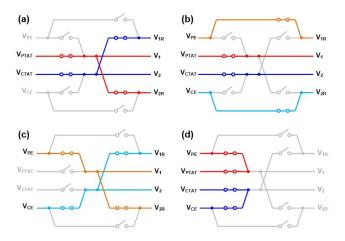

Figure 2.12: Four modes of DSCDA

The ISN and the DSCDA can support four different modes to produce four analog outputs, namely  $V_{OP}$ ,  $V_{ON}$ ,  $V_{PE}$ , and  $V_{CE}$ . In the self-reference (SR) mode, shown in fig. 2.12(a), the  $V_{PTAT}$  and  $V_{CTAT}$  not only act as the two input signals, but also serve as each other's reference voltage for the DSCDA. The second mode is the external-reference (ER) mode, where  $V_{PTAT}$  and  $V_{CTAT}$  become signal inputs and two off-chip signals ( $V_{PE}$  and  $V_{CE}$ ) are used for reference inputs for the DSCDA (fig. 2.12(b)). The third mode is the amplifier calibration mode, where two off-chip signals from  $V_{PE}$  and  $V_{CE}$ , respectively, are connected to both the signal ( $V_1$ ,  $V_2$ ) and the reference ( $V_{1R}$ ,  $V_{2R}$ ) nodes of the amplifier (fig. 2.12(c)). The fourth

operation mode is the off-chip readout mode, where the  $V_{PTAT}$  and  $V_{CTAT}$  of a sensor front end are fed to the off-chip buffer via the  $V_{PE}$  and  $V_{CE}$  nodes (fig. 2.12(d)). In this work we mainly used the SR mode since it supports the differential reading scheme without external reference voltages and it can also provide higher robustness to the mismatch between  $C_{SS}$ and  $C_{HS}$  than the ER mode. The output function of SR and ER modes is Equation (7)

$$ER : V_{OD} = \frac{C_S}{C_H} [(V_{PTAT} - V_{PE}) - (V_{CTAT} - V_{CE})]$$

$$SR : V_{OD} = 2\frac{C_S}{C_H} (V_{PTAT} - V_{CTAT})$$

(7)

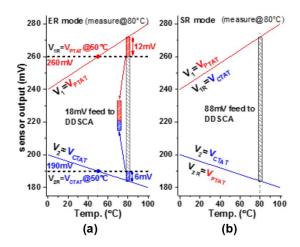

Figure 2.13: The available amplification rooms of the ER and the SR mode

While we mainly use the SR mode, it is noteworthy that the ER mode can provide higher voltage gain which may relax the precision requirement of the ADC. In fig. 2.13(a), at 50°C,  $V_{2R}$  can be set as  $V_{PTAT}$  (the middle point of the temperature range) and likewise,  $V_{1R}$  as  $V_{CTAT}$ . The full difference between  $V_{PTAT}$  and  $V_{CTAT}$  (e.g., 18mV at 80°C) can now be amplified at a higher (e.g., 30X) gain. For the same case, the SR mode limits the maximum gain to 9X, since the input voltage,  $V_{PTAT} - V_{CTAT}$ , contains a large temperature-independent

offset (e.g., 70mV at 80°C as seen in fig. 2.13(b)).

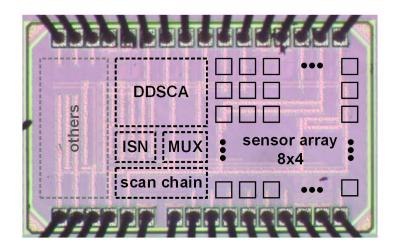

## 2.5 Silicon Implementation

Figure 2.14: Test chip die photo

The test chips for the proposed temperature sensors have been fabricated in a 65nm General-Purpose CMOS process. fig. 2.14 shows the die photo of the test chip. The three types of sensor front ends are configured in a 4-by-8 array. The area of the chip, including I/O pads, is  $0.9 \times 0.72 mm^2$ .

# 2.6 Measurements

### 2.6.1 Sensor Accuracy

We measured multiple sensor front ends with two scenarios (off-chip amplifier with off-chip ADC; on-chip DSCDA with off-chip ADC). Then the worst case errors are reported based on statistics of the data.

First, we measured the performance of sensor front ends using an off-chip amplifier and ADC. The off-chip ADC has a 16-bit resolution for an input range of  $\pm 10$ V, a sampling

Figure 2.15: The measurements PTAT, CTAT, PTAT-CTAT and after OPC

Figure 2.16: The errors of 64 balanced front-end circuits after OPC

rate of up-to 100 kS/s, and an input common-mode voltage of 1.25V. We operated the ADC at 20 kS/s. We swept the temperature from 0 to 100°C with a step-size of 10°C, while measuring the  $V_{PTAT}$  and  $V_{CTAT}$  of the 64 balanced-sensor front-end designs across 8 chips. fig. 2.15(a) shows the  $V_{PTAT}$ ,  $V_{CTAT}$ , and  $V_{DIFF}$ , with the  $V_{DIFF}$  being calculated only after we digitized and subtracted the  $V_{PTAT}$  and  $V_{CTAT}$ . Then, as shown in fig. 2.15(b), we perform OPC, where the slope of  $V_{DIFF}$  across temperature is extracted from the SPICE simulations. The OPC-ed  $V_{DIFF}$  are then converted to temperatures, and now the accuracy

of the sensor front end, shown in fig. 2.16, can be found. The sensor front ends exhibit an acceptable worst-case error of  $7^{\circ}$ C (+3.6°C < error < -3.4°C). Worst-case errors of the accuracy-optimized and area-optimized front end designs also are measured and found to be  $5.4^{\circ}$ C (-0.7 < error < +4.7°C) and  $8.8^{\circ}$ C (-2.0 < error < +6.8°C), respectively.

Figure 2.17: The summary of the error performance of three front-end designs after OPC

The sensor front ends are also measured with the on-chip DSCDA and the off-chip ADC. The ISN is configured for the SR mode without external reference voltages. For the different sensor front-end designs we use the different gains in the amplifier - 10x, 12x, and 16x for the accuracy-optimized, balanced, and area-optimized designs, respectively – to amplify the outputs to better match the input-range of the off-chip ADC. In contrast to the case using the off-chip amplifier, the on-chip DSCDA amplifier directly generates  $V_{DIFF}$ , which is digitized by the ADC. fig. 2.17(a) shows the measured error of the three types of sensor front ends. When the on-chip amplifier in the SR mode is used worst-case errors are 6.3°C (-0.6 < error < +5.7°C), 7.1°C (-3.6 < error < +3.5°C), and 9.6°C (-1.4 < error < +8.2°C)

for the accuracy-optimized, balanced, and area-optimized designs, respectively.

The measurements show that the sensor front ends with larger footprints can achieve higher accuracy. Increasing the footprint of the sensor reduces worst-case error. As shown by the black curves (black circles) in fig. 2.17(b), the error-spread decreases from  $8.8^{\circ}$ C to  $5.4^{\circ}$ C when the footprint of a front end increases from  $115\mu m^2$  to  $400\mu m^2$ . The larger area reduces the variations on temperature slope, represented by the blue curves (blue squares) seen in fig. 2.17(b).

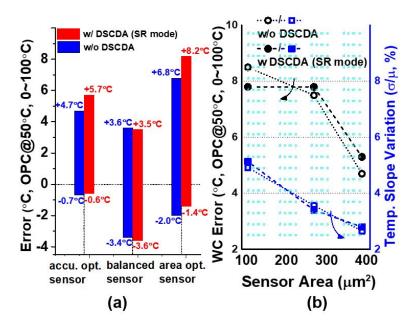

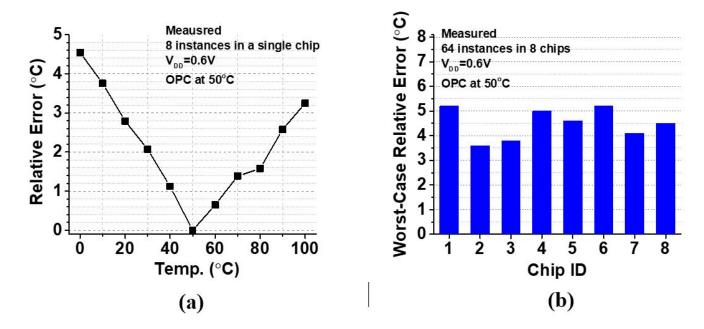

Figure 2.18: The relative error from measurements

We also measure the errors of the front ends relative to one another in a single chip (defined as relative errors [14]). As shown in fig. 2.18(a), the worst-case relative error in a chip is measured to be 4.5°C. We also find the relative errors across eight chips. As shown in fig. 2.18(b), the relative errors are measured to be from 3.6°C to 5.2°C. The accuracy can be improved further when two-temperature-point (20 and 80°C) calibration (TPC) is used. Worst-case errors with the TPC are measured to be 4.7°C, 3.8°C, and 7.8°C for the

accuracy-optimized, balanced, and area-optimized designs, respectively.

#### 2.6.2 VDD Scalability

Figure 2.19: VCC scalability measurements

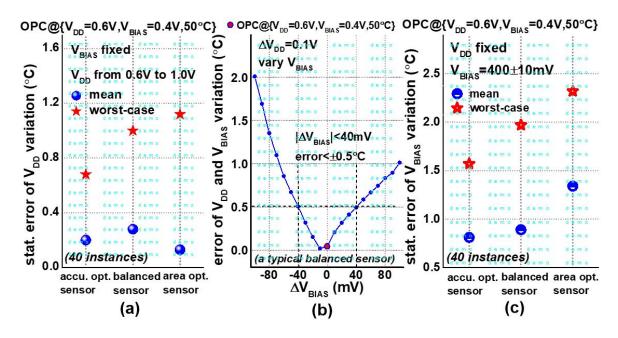

We measured the VDD scalability of the proposed sensor front-end designs. For each front end type we measured 40 instances across 5 chips, while sweeping the VDD from 0.6 to 1V. The OPC is performed at 0.6V, and the calibration settings are used across the entire voltage range. fig. 2.19(a) depicts the error measurements of three types of designs. The average- and worst errors of the balanced front end are 0.3°C and 1.0°C, respectively, across 0 to 100°C and 0.6 to 1V, when they are calibrated at VDD=0.6V. The VB used is 0.4V. fig. 2.19(a) also shows the errors of the other types of front ends. The average- and worst-case errors of the accuracy-optimized front ends are measured to be 0.2°C and 0.7°C, respectively.

We also considered the case where the VB has variations. As shown in fig. 2.19(b), a

typical balanced sensor with VB=0.4V has the LF-PSRR of -79dB and an error of 0.1°C over the voltage scaling from 0.6 to 1V. If VB fluctuates within a range of ±40mV from 0.4V, the LF-PSRR is measured to be <-55dB, which corresponds to an error of 0.5°C for the same voltage scaling. The measurement results for the area, power dissipation, temperature slope, LF-PSRR, and errors of the front ends are summarized in table 2.1. fig. 2.19(c) depicts the error measurements of three types of designs. The average- and worst errors of the balanced front end are 0.7°C and 1.6°C, respectively, across 0 to 100°C and VB varies from 390mV to 410mV, when they are calibrated at VDD=0.6V. fig. 2.19(c) also shows the errors of the other types of front ends. The average- and worst-case errors of the accuracy-optimized front ends, area-optimized front ends, are measured to be 0.8°C and 2.0°C, 1.4°C and 2.3°C respectively.

#### 2.7 Conclusion

We compare the proposed sensor circuits to the state-of-the-art designs. As shown in table 2.2, the balanced front end achieves a 14.3x smaller footprint than the 22nm design in [13], while it exhibits a worst error of less than 7.0°C (-3.4°C < error < 3.6°C), after OPC, across 64 sensors in 8 chips. The worst-case measured error among 8 sensors in a chip across 8 chips is 5.2°C. Our sensor can operate at VDDs from 0.6 to 1V, whereas none of the other designs in the comparison can operate below 1V. The average error incurred by the voltage scaling is 0.3°C. The area-optimized front end has a footprint of  $115\mu m^2$ , and a worst-case error of 8.8°C (-2.0 < error < 6.8°C) across 64 sensors in 8 chips after OPC. The accuracy-optimized front end exhibits the per-front-end area of  $400\mu m^2$  which is still 10x smaller than [13] and a worst-case error of 5.4°C (-0.7 < error < 4.7°C).

Table I. Summary of three sensor front-end circuits

| Type              | Area  | Power <sup>1</sup> (µW) | TC (mV/°C)    | LF-PSRR2 (dB)  | Operating     | Error (°C)         |

|-------------------|-------|-------------------------|---------------|----------------|---------------|--------------------|

| Туре              | (µm²) | min/max                 | Var. (σ/μ, %) | DC-Sen. (°C/V) | scenario      | min <u>./</u> max. |

|                   |       |                         |               |                | OPC w/o. Amp  | -0.7/4.7           |

| Accuracy          | 400   | 0.03/0.85               | 0.74          | 71             | OPC w. SR Amp | -0.6/5.7           |

| optimized         |       |                         | 2.7%          | 0.4            | TPC w/o. Amp  | -1.1/2.1           |

|                   |       |                         |               |                | TPC w. SR Amp | -1.6/3.1           |

| Accuracy          |       |                         |               |                | OPC w/o. Amp  | -3.4/3.6           |

| Accuracy-         | 279   | 0 04/0 92               | 0.57          | 67             | OPC w. SR Amp | -3.6/3.5           |

| area<br>balanced  | 213   | 0.04/0.92               | 3.6%          | 0.8            | TPC w/o. Amp  | -2.4/1.5           |

|                   |       |                         |               |                | TPC w. SR Amp | -1.9/1.9           |

|                   |       |                         |               |                | OPC w/o. Amp  | -2.0/6.8           |

| Area<br>optimized | 115   | 0.01/0.21               | 0.72          | 65             | OPC w. SR Amp | -1.4/8.2           |

|                   |       |                         | 5.1%          | 0.8            | TPC w/o. Amp  | -1.6/3.2           |

|                   | 3     |                         |               |                | TPC w. SR Amp | -2.3/5.5           |

<sup>&</sup>lt;sup>1</sup>The minimum and maximum powers are simulated at 0°C and 100°C, respectively; <sup>2</sup>Measurement results without the DSCDA;

Table 2.1: Summary table of three sensors

Table II. Comparisons of temperature sensors for dynamic thermal management techniques

|                                      | [1                  | 3]                  | [14]    | [15]           | [17]           | [18]      | Accu.opt.              | Balanced               | Area-opt              |

|--------------------------------------|---------------------|---------------------|---------|----------------|----------------|-----------|------------------------|------------------------|-----------------------|

| Technology                           | 32nm                | 22nm                | 32nm    | 90nm           | 90nm           | 160nm     | 65nm                   |                        |                       |

| V <sub>DD</sub> (V)                  | 1.4-1.8             | 1.35                | 1.05    | 1              | 1              | 1.35/1.8V | 0.6~1.0                |                        |                       |

| Sensor core                          | BJT                 | BJT                 |         |                |                | TD        | NMOS                   |                        |                       |

| Power<br>(total, <u>mW</u> )         | 3.78                | 1.35                | 1.6     | 1              | 1              | 3.6mW     |                        | 0.366                  |                       |

| Power<br>(front end, µW)             | 1                   | I                   | I       | 25             | 25             | 1         | 0.85 <sup>7</sup>      | 0.927                  | 0.217                 |

| Area <sup>1</sup> (μm <sup>2</sup> ) | 20000               | 6100                | 20000   | 1              | 1              | 4600      | <u>t</u>               | 1                      | 1                     |

| Area <sup>2</sup> (μm <sup>2</sup> ) | 11000*              | 4000*               | 4000*   | 48             | 48             | 1         | 400                    | 279                    | 115                   |

| Output temperature slope             | 4.23<br>[counts/°C] | 3.82<br>[counts/°C] | I       | 1.8<br>[mV/°C] | 1.8<br>[mV/°C] | I         | <b>0.74</b><br>[mV/°C] | <b>0.57</b><br>[mV/°C] | <b>0.72</b><br>[mV/°C |

| Range (°C)                           | 20~110              | -10~110             | -10~110 | 50~125         | 50~125         | -10~125   | 0~100                  |                        |                       |

| Resolution (°C)                      | 0.19                | 0.25                |         |                |                | 0.6       |                        | 1                      |                       |

| Error <sup>3</sup> (°C)              | 1                   | 1                   | <5      | 1              | 1              | ±6.5      |                        | 1                      |                       |

| Error⁴ (°C)                          | <4.5                | 1                   | 1       | 1              | 1              | -1.5/+1.5 | -0.7/+4.7              | -3.4/+3.6              | -2.0/+6.              |