# CROSSTALK COMPUTING: CIRCUIT TECHNIQUES, IMPLEMENTATION AND POTENTIAL APPLICATIONS

## A DISSERTATION IN

Computer and Electrical Engineering and Computer Science

Presented to the Faculty of the University of Missouri–Kansas City in partial fulfillment of the requirements for the degree

DOCTOR OF PHILOSOPHY

by

Naveen Kumar Macha

B.TECH., Jawaharlal Nehru Technological University Hyderabad, Telangana, India, 2014

Kansas City, Missouri 2020 CROSSTALK COMPUTING: CIRCUIT TECHNIQUES, IMPLEMENTATION, AND

POTENTIAL APPLICATIONS

Naveen Kumar Macha, Candidate for the Doctor Of Philosophy Degree

University of Missouri-Kansas City, 2020

**ABSTRACT**

This work presents a radically new computing concept for digital Integrated Circuits

(ICs), called Crosstalk Computing. The conventional CMOS scaling trend is facing device scaling

limitations and interconnect bottleneck. The other primary concern of miniaturization of ICs is the

signal-integrity issue due to Crosstalk, which is the unwanted interference of signals between

neighboring metal lines. The Crosstalk is becoming inexorable with advancing technology nodes.

Traditional computing circuits always tries to reduce this Crosstalk by applying various circuit and

layout techniques. In contrast, this research develops novel circuit techniques that can leverage this

detrimental effect and convert it astutely to a useful feature. The Crosstalk is engineered into a logic

computation principle by leveraging deterministic signal interference for innovative circuit

implementation. This research work presents a comprehensive circuit framework for Crosstalk

Computing and derives all the key circuit elements that can enable this computing model.

Along with regular digital logic circuits, it also presents a novel Polymorphic circuit approach

unique to Crosstalk Computing. In Polymorphic circuits, the functionality of a circuit can be altered

using a control variable. Owing to the multi-functional embodiment in polymorphic-circuits, they find

many useful applications such as reconfigurable system design, resource sharing, hardware security,

and fault-tolerant circuit design, etc. This dissertation shows a comprehensive list of polymorphic logic

iii

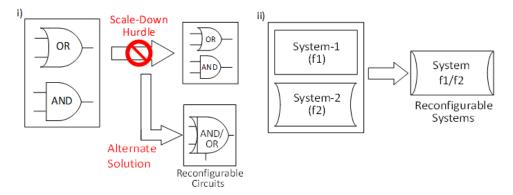

gate implementations, which were not reported previously in any other work. It also performs a comparison study between Crosstalk polymorphic circuits and existing polymorphic approaches, which are either inefficient due to custom non-linear circuit styles or propose exotic devices. The ability to design a wide range of polymorphic logic circuits (basic and complex logics) compact in design and minimal in transistor count is unique to Crosstalk Computing, which leads to benefits in the circuit density, power, and performance. The circuit simulation and characterization results show a 6x improvement in transistor count, 2x improvement in switching energy, and 1.5x improvement in performance compared to counterpart implementation in CMOS circuit style.

Nevertheless, the Crosstalk circuits also face issues while cascading the circuits; this research analyzes all the problems and develops auxiliary circuit techniques to fix the problems. Moreover, it shows a module-level cascaded polymorphic circuit example, which also employs the auxiliary circuit techniques developed. For the very first time, it implements a proof-of-concept prototype Chip for Crosstalk Computing at TSMC 65nm technology and demonstrates experimental evidence for runtime reconfiguration of the polymorphic circuit. The dissertation also explores the application potentials for Crosstalk Computing circuits. Finally, the future work section discusses the Electronic Design Automation (EDA) challenges and proposes an appropriate design flow; besides, it also discusses ideas for the efficient implementation of Crosstalk Computing structures. Thus, further research and development to realize efficient Crosstalk Computing structures can leverage the comprehensive circuit framework developed in this research and offer transformative benefits for the semiconductor industry.

#### APPROVAL PAGE

The faculty listed below, appointed by the Dean of the School of Graduate Studies, have examined a thesis titled "Crosstalk Computing: Circuit Techniques, Implementation and Potential Applications" presented by Naveen Kumar Macha, candidate for the Doctor Of Philosophy degree, and certify that in their opinion it is worthy of acceptance.

# **Supervisory Committee**

Mostafizur Rahman, Ph.D., Committee Chair Department of Computer Science & Electrical Engineering

Masud Chowdhury, Ph.D.

Department of Computer Science & Electrical Engineering

Ghulam Chaudhry, Ph.D. Department of Computer Science & Electrical Engineering

Dianxiang Xu, Ph.D.

Department of Computer Science & Electrical Engineering

Md Yusuf Sarwar Uddin, Ph.D. Department of Computer Science & Electrical Engineering

# CONTENTS

| ΑĒ  | SSTRACT                                                 | iii |

|-----|---------------------------------------------------------|-----|

| ILI | LUSTRATIONS                                             | X   |

| TA  | BLES                                                    | .XV |

| ΑC  | CKNOWLEDGEMENTS                                         | xvi |

| 1.  | INTRODUCTION AND MOTIVATION                             | 1   |

| 2.  | MORE MOORE AND RELEVANT BEYOND CMOS RESEARCH DIRECTIONS | 8   |

|     | 2.1. More Moore Research Directions                     | 8   |

|     | 2.2. Relevant Beyond CMOS Computing approaches          | 11  |

|     | 2.2.1. Neuromorphic Computing                           | 12  |

|     | 2.2.2. Emerging Nanoelectronic Devices for Logic        | 15  |

|     | 2.2.2.1. Quantum Dot Cellular Automata                  | 15  |

|     | 2.2.2.2. Single-Electron Transistors                    | 16  |

|     | 2.2.2.3. Nanomagnetic and Spintronic Logic Devices      | 17  |

|     | 2.3. Crosstalk Computing vs. Beyond CMOS approaches     | 17  |

| 3.  | CROSSTALK COMPUTING                                     | 20  |

|     | 3.1. Pilot Circuits based on pass transistors           | 20  |

| 4.  | CROSSTALK CIRCUITS BASED ON PERCEPTRON MODEL            | 27  |

|     | 4.1. Basic Logic Gates                                  | 27  |

|     | 4.2. Complex Logic Gates                                | 31  |

| 5.  | CROSSTALK CIRCUIT TYPES                                 | 34  |

|     | 5.1. Positive Transition Crosstalk Circuits             | 34  |

|     | 5.2. Negative Transition Crosstalk Circuits             | 35  |

|     | 5.3. Dual Transition Crosstalk Circuits                                          | 36 |

|-----|----------------------------------------------------------------------------------|----|

|     | 5.4. Bypass Branch Circuits                                                      | 38 |

| 6.  | CASCADING CIRCUIT ISSUES AND SOLUTIONS                                           | 41 |

|     | 6.1. Cascading Circuit Issues                                                    | 41 |

|     | 6.2. Solutions to fix Mismatch Nodes                                             | 42 |

|     | 6.2.1. Auxiliary Initializer Circuits to fix Mismatch Nodes                      | 43 |

|     | 6.2.2. Leveraging Crosstalk Circuit types to fix Mismatch Nodes                  | 45 |

|     | 6.2.3. Crosstalk Circuits with inherent output initializers                      | 49 |

| 7.  | EXISTING POLYMORPHIC CIRCUIT APPROACHES                                          | 51 |

| 8.  | CROSSTALK POLYMORPHIC CIRCUITS                                                   | 54 |

|     | 8.1. Crosstalk Polymorphic Logic Gates                                           | 54 |

|     | 8.2. Cascaded Polymorphic Circuits                                               | 61 |

|     | 8.2.1. Fine-grained Cascaded Polymorphic Circuit                                 | 61 |

|     | 8.2.2. Module-level Cascaded CT-Polymorphic Circuit                              | 63 |

| 9.  | COMPARISON AND BENCHMARKING OF CROSSTALK CIRCUITS                                | 66 |

|     | 9.1. Comparison                                                                  | 66 |

|     | 9.2. Benchmarking                                                                | 70 |

| 10. | PRACTICAL REALIZATION OF CROSSTALK GATES                                         | 73 |

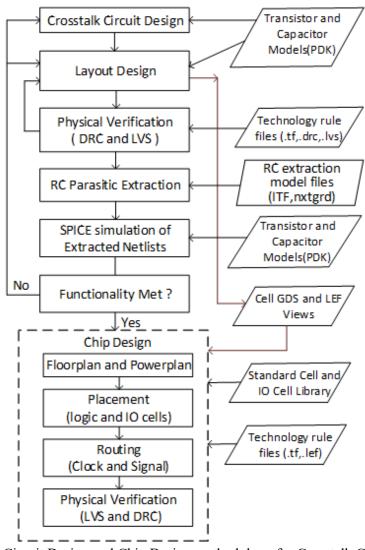

|     | 10.1. Prototype Circuit Design Flow                                              | 73 |

|     | 10.2. PVT Variation Analysis                                                     | 75 |

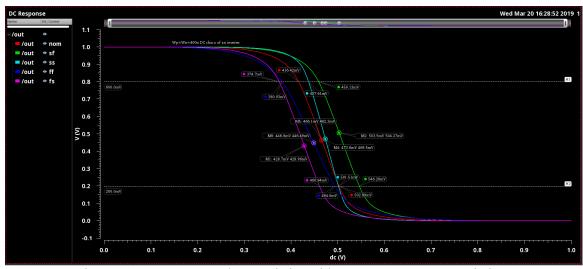

|     | 10.2.1. Inverter DC characteristics at TSMC 65nm node at different PVT corners   | 76 |

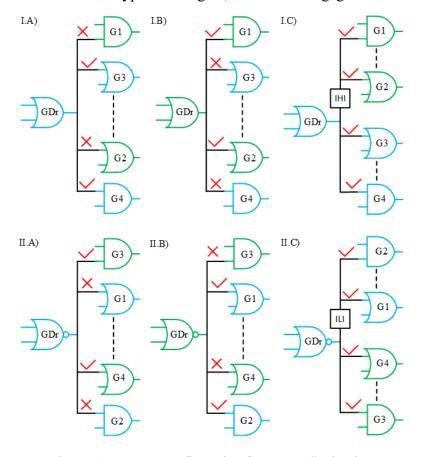

|     | 10.2.1.1. Considering only process variation                                     | 76 |

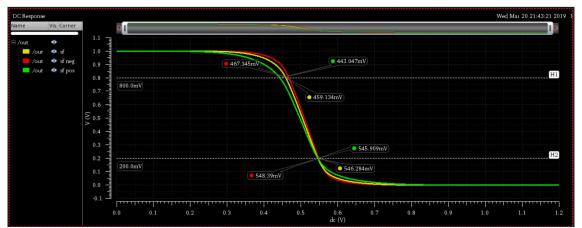

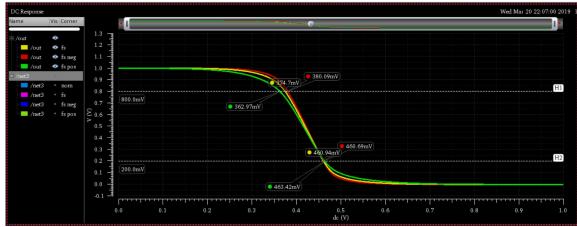

|     | 10.2.1.2. Considering Process and Temperature Variations                         | 78 |

|     | 10.2.2. Effect of the functionality margins on the fan-in of the crosstalk gates | 79 |

|    | 10.2.3. A solution to fix the variation effect on the functionality and achieve high far circuits |      |

|----|---------------------------------------------------------------------------------------------------|------|

|    | 10.3. Prototype Chip Design Flow                                                                  | 80   |

|    | 10.4. Details of the Full-Chip                                                                    | 82   |

|    | 10.5. Measurement of fabricated Chip                                                              | 83   |

| 11 | . POTENTIAL APPLICATIONS                                                                          | 87   |

|    | 11.1. Resource sharing                                                                            | 87   |

|    | 11.2. Fault Tolerance                                                                             | 88   |

|    | 11.2.1. Block-level reconfigurable fault-tolerant scheme                                          | 89   |

|    | 11.2.2. System-level reconfigurable fault-tolerant scheme                                         | 90   |

|    | 11.3. Hardware Security                                                                           | 92   |

|    | 11.4. Radiation Hardening                                                                         | 95   |

|    | 11.4.1. Radiation effects on Integrated Circuits                                                  | 97   |

|    | 11.4.2. A new integrated circuit fabric for radiation-hardened digital ICs                        | .100 |

|    | 11.4.3. Methodology for characterizing transient and permanent faults and their mitigation        | .102 |

|    | 11.4.3.1. Charge Sharing in Crosstalk circuits to Minimize the Radiation Effects                  | .103 |

|    | 11.4.3.2. Temporal Hardening through the periodic discharge                                       | .106 |

|    | 11.4.4. Comparison and Summary                                                                    | .107 |

| 12 | . CONCLUSION AND FUTURE WORK                                                                      | .109 |

|    | 12.1. EDA development for Crosstalk Computing                                                     | .110 |

|    | 12.1.1. EDA flow for Crosstalk Computing                                                          | .110 |

|    | 12.1.2. Crosstalk Standard Cell Library Characterization                                          | .110 |

|    | 12.1.3. Synthesis and Place-and-Route Flow                                                        | .112 |

|    | 12.2. Crosstalk Computing specific 3-D capacitances and devices                                   | .113 |

| REFERENCES | 117 |

|------------|-----|

| VITA       | 135 |

# ILLUSTRATIONS

| Figure                                                                                            |

|---------------------------------------------------------------------------------------------------|

| Figure.1.1 Historical Scaling trends: i) Intel Process Technologies [5], ii) TSMC Process .1      |

| Figure 1.2 Crosstalk Signal Interference                                                          |

| Figure.1.3 Summation of Crosstalk signal interferences                                            |

| Figure 1.4 Abstract view of the Crosstalk computing fabric                                        |

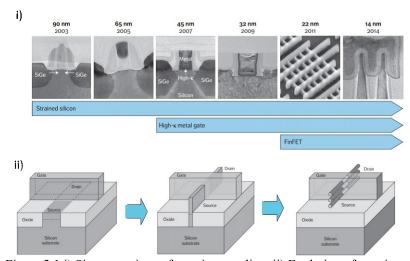

| Figure.2.1 i) Six generations of transistor scaling, ii) Evolution of transistor structure: Plana |

| MOSFET, FinFET, Gate All Around Nanowire (GAANW) transistor9                                      |

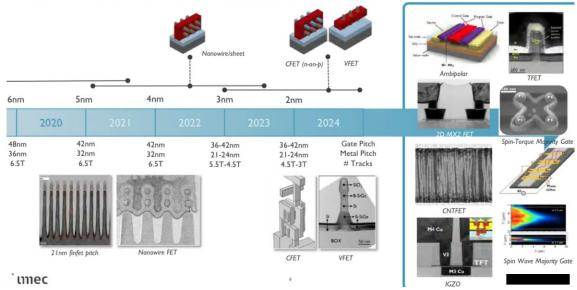

| Figure 2.2 Imec Transistor road map                                                               |

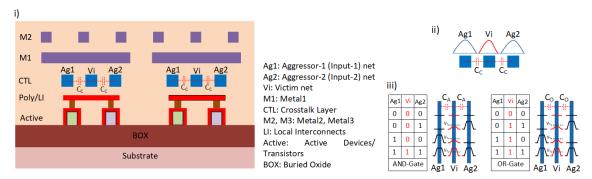

| Figure.3.1 (i) Overview of Crosstalk computing fabric, (ii) Crosstalk Computing Mechanism         |

| (iii) Implementing Logic Gates through crosstalk Computing                                        |

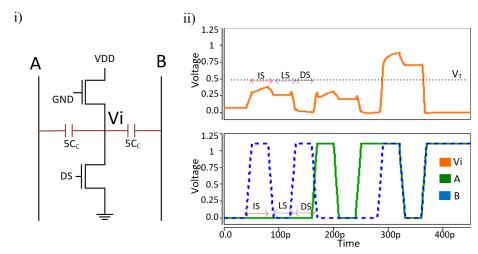

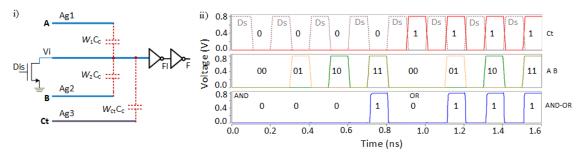

| Figure.3.2 Crosstalk based AND gate: i) Circuit schematic, i)Simulation response22                |

| Figure.3.3 Crosstalk based OR gate: i) Circuit schematic, i)Simulation response22                 |

| Figure.3.4 Crosstalk based XOR gate: i) Circuit schematic, i)Simulation response23                |

| Figure.3.5 Crosstalk based Carry Logic gate: i) Circuit schematic, i)Simulation response23        |

| Figure.3.6 Stick diagrams for Carry Circuit: i) 2D CMOS circuit style ii) Crosstalk circuit       |

| style22                                                                                           |

| Figure.4.1 Perceptron Model                                                                       |

| Figure.4.2 Crosstalk Basic Gates: (i) AND gate schematic, (ii) OR gate schematic, (iii)           |

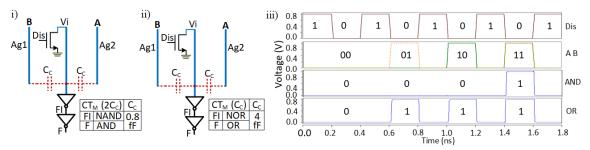

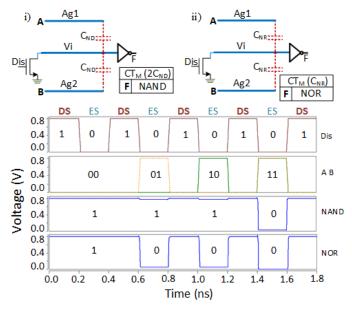

| Simulation response of AND and OR gates                                                           |

| Figure.4.3 Capacitive Network of a Generic Crosstalk Gate                                         |

| Figure 4.4 Crosstalk Complex logic Gates: (i) A generic schematic representing all 3-input        |

| complex logic functions ii) Simulations response of 3-input complex logic functions                |

|----------------------------------------------------------------------------------------------------|

| (AND3, CARRY, OR3, AO21, OA21)                                                                     |

| Figure 5.1 Positive Transition Crosstalk Circuits                                                  |

| Figure 5.2 Negative Transition Crosstalk Circuits                                                  |

| Figure 5.3 Dual Transition Crosstalk Circuits                                                      |

| Figure 5.4 Bypass branch Crosstalk Circuits                                                        |

| Figure 6.1 Cascading Circuit issues: i)No Transition issue by connecting nodes with same           |

| initial state (0) ii) Mismatch node by connecting initial-state-one output to initial-state-zero   |

| input iii) No Transition issue by connecting nodes with same initial-state (1) iv) Mismatch        |

| node by connecting initial-state-zero output to initial state-one input41                          |

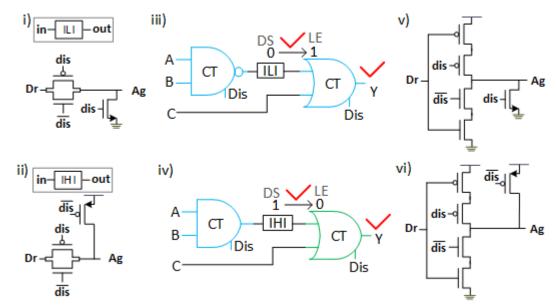

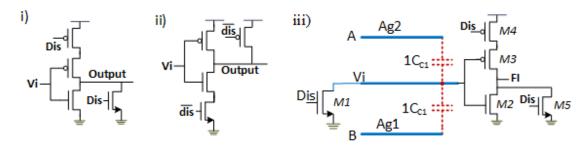

| Figure.6.2 Initializers: i) Input-Low-Initializer, ii) Input-High-Initializer, iii) Using ILI, iv) |

| Using IHI, v) Regenerative ILI, vi) Regenerative IHI, vii) in-built output low initializer,        |

| viii) in-built output high initializer                                                             |

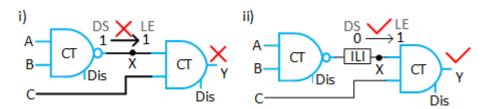

| Figure.6.3 Cascading Circuit issues and solutions: i) Logic 1 mismatch node, ii) Employing         |

| ILI circuit to fix mismatch node                                                                   |

| Figure.6.4 Simulation response of the circuits Figure.5.3(i) and Figure.5.3(ii)44                  |

| Figure.6.5 Legal and illegal connections for cascading Crosstalk circuits45                        |

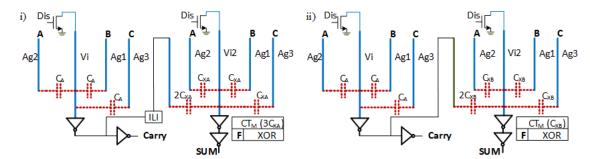

| Figure.6.6 Two different cascading styles for implementing Full Adder. i) Implementation           |

| of Full Adder using initializers, ii) Implementation of Full Adder using dual transition SUM       |

| circuit47                                                                                          |

| Figure.6.7 Fan-out configuration for Crosstalk circuits                                            |

| Figure.6.8 i) Output Low Initializer (OLI), ii) Output High Initializer (OHI), iii) Crosstalk      |

| Gate with inhere output low initializer                                                            |

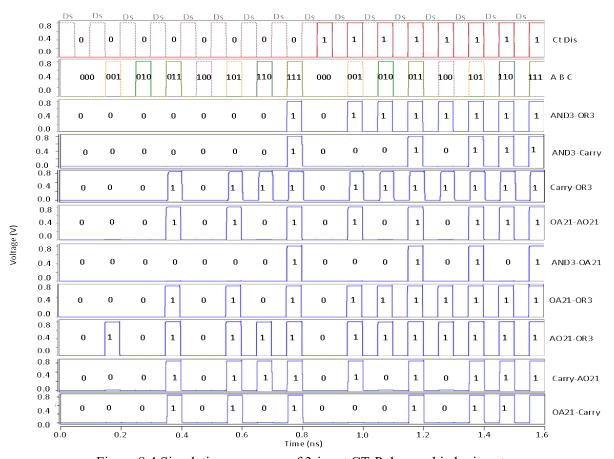

| Figure.8.1 Circuit Schematic of a Generic Crosstalk Polymorphic Gate                    |

|-----------------------------------------------------------------------------------------|

| Figure 8.2 2-input Crosstalk-Polymorphic Logic Gate: i) AND2-OR2 Schematic, ii) AND2-   |

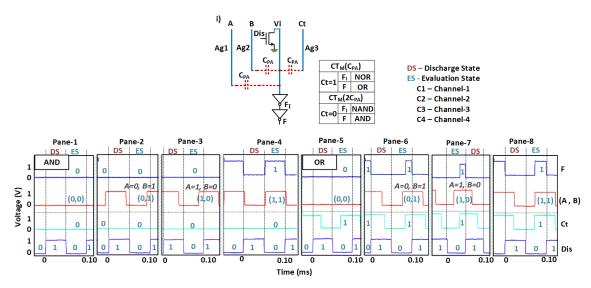

| OR2 Simulation response                                                                 |

| Figure.8.3 Generic 3-input Crosstalk-Polymorphic Logic Gate Schematic                   |

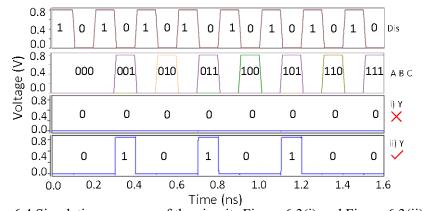

| Figure.8.4 Simulation responses of 3-input CT-Polymorphic logic gates                   |

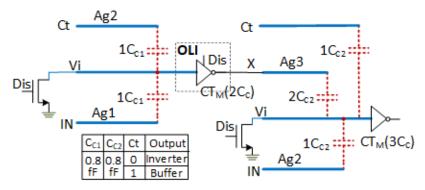

| Figure.8.5 CT-Polymorphic Inverter-Buffer Circuit schematic                             |

| Figure.8.6 Simulation response CT-Polymorphic Inverter-Buffer Circuit                   |

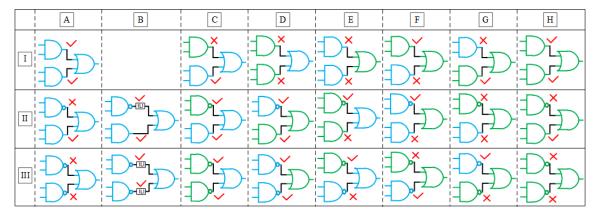

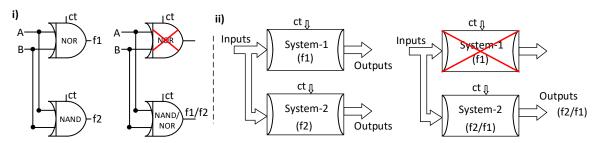

| Figure.8.7 Three CT-Polymorphic Gates cascaded to generate 16 functions                 |

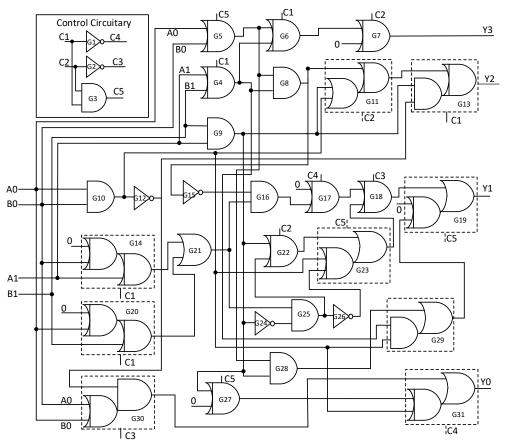

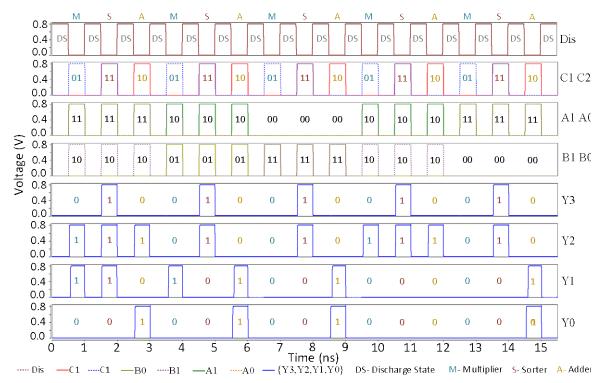

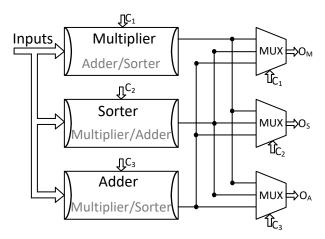

| Figure. 8.8 Crosstalk Polymorphic Multiplier-Adder-Sorter circuit                       |

| Figure.8.9 Crosstalk Polymorphic Multiplier-Adder-Sorter circuit simulation response65  |

| Figure.10.1 Circuit Design and Chip Design methodology for Crosstalk Circuit research74 |

| Figure.10.2 Inverter DC characteristics with SF, SS, TT, FS, FF variations76            |

| Figure.10.3 Inverter DC characteristics with SF process and Temperature variations78    |

| Figure.10.4 Inverter DC characteristics with FS process and Temperature variations78    |

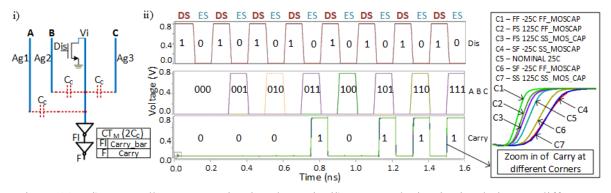

| Figure.10.5. i) Crosstalk CARRY Circuit Schematic, ii) Extracted Circuit Simulations at |

| different Corners                                                                       |

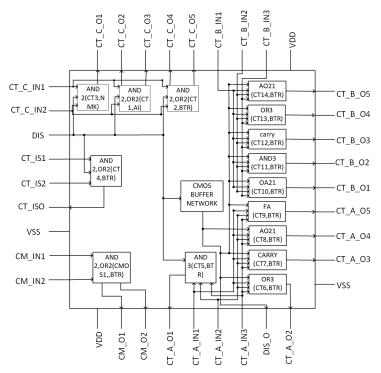

| Figure.10.6 Full Chip block diagram                                                     |

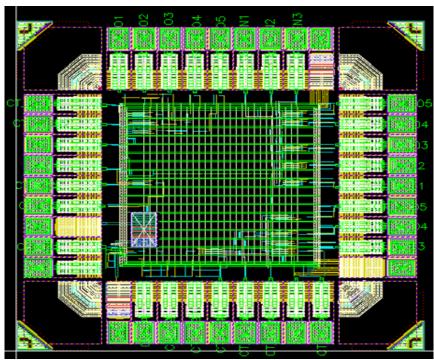

| Figure.10.7 Full chip layout diagram                                                    |

| Figure.10.8 Fabricated chip                                                             |

| Figure.10.9 Experimental results of Crosstalk Logic gates                               |

| Figure.10.10 Experimental results of Crosstalk Reconfigurable gate                      |

| Figure 11.1 Resource sharing using Crosstalk reconfigurable circuits                    |

| Figure 11.2 Polymorphic/Re-configurable circuit based Fault Tolerance concept, i) Gate- |

| level, ii) System-level                                                                       |

|-----------------------------------------------------------------------------------------------|

| Figure.11.3. Block-Level Polymorphic Fault Tolerant scheme                                    |

| Figure 11.4 System-Level Polymorphic Fault Tolerant scheme                                    |

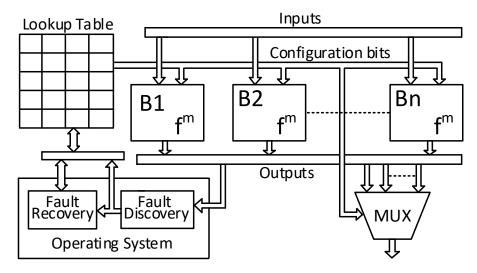

| Figure.11.5 Algorithmic Flow chart for proposed system level fault tolerance scheme91         |

| Figure 11.6 Algorithm steps for proposed system level fault-tolerance scheme93                |

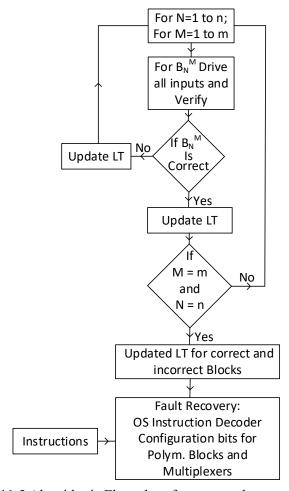

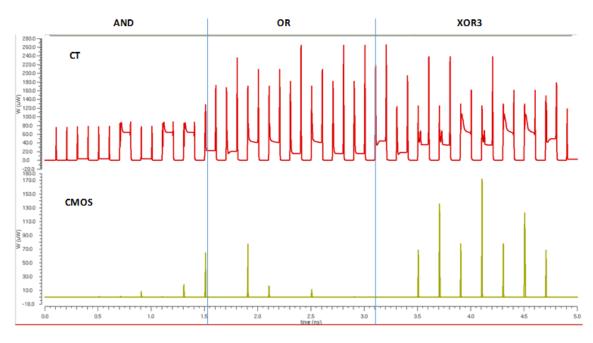

| Figure.11.7 i) Crosstalk AND Gate Schematic and Layout, ii) Crosstalk OR Gate Schematic       |

| and Layout94                                                                                  |

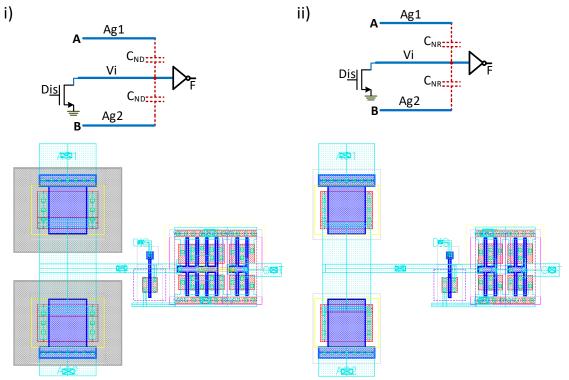

| Figure.11.8 Instantaneous power profile for Crosstalk and CMOS gates with same inputs.        |

| 95                                                                                            |

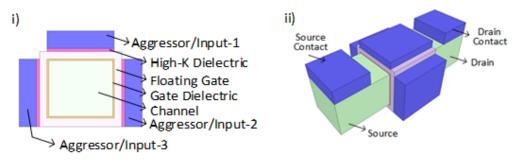

| Figure 11.9 Crosstalk NAND gate 3-D view                                                      |

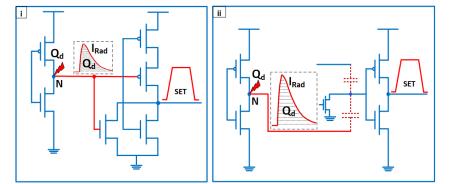

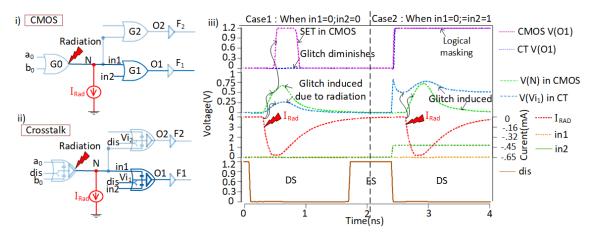

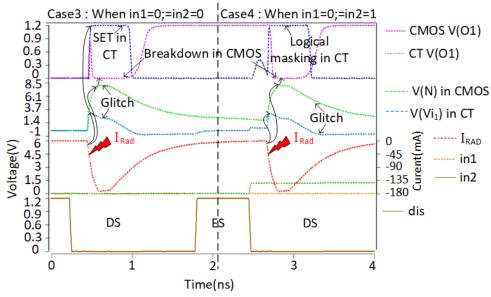

| Figure.11.10 Transient Faults in circuits due to Radiation: i) CMOS cascaded circuit; ii)     |

| Crosstalk cascaded circuit                                                                    |

| Figure.11.11 Simulation of Transient Errors: i) CMOS cascaded circuit, ii) Crosstalk cascaded |

| circuit iii) Simulation results                                                               |

| Figure.11.12 Simulation of Permanent Fault in CMOS and Crosstalk Circuits105                  |

| Figure.11.13 Temporal Hardening in Crosstalk circuits                                         |

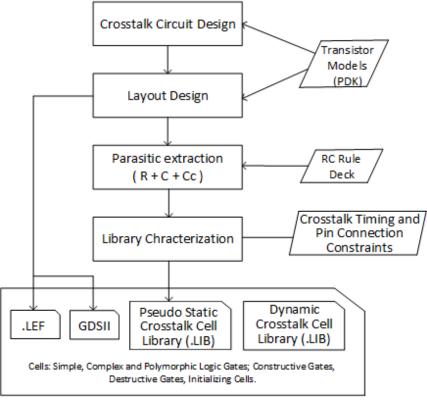

| Figure.12.1 Crosstalk Cell Library Characterization Methodology                               |

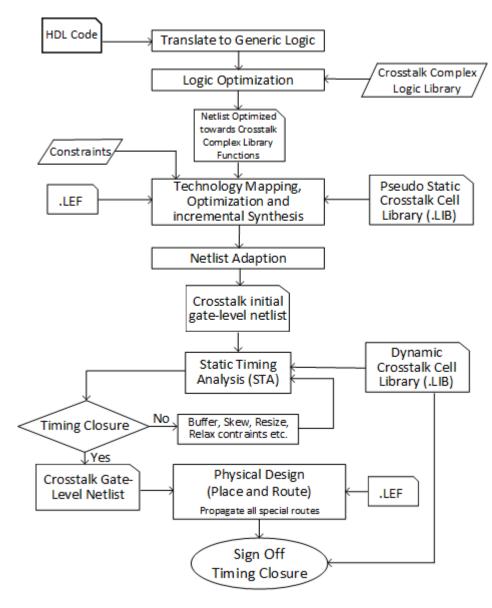

| Figure 12.2 Synthesis and Place-and-Route Flow for Crosstalk Computing112                     |

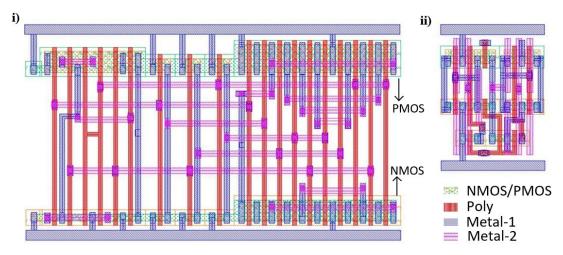

| Figure 12.3 i) 3-D Layout for efficient Crosstalk Circuit implementation, ii) Different       |

| dielectric materials (K) vs Coupling Capacitances                                             |

| Figure.12.4 Layouts of Full Adder Circuit (Sum and Carry): i) CMOS Layout ii) Crosstalk       |

| Layout                                                                                        |

|                                                                                               |

| dielectric used for Crosstalk Couplings | 1. | 5 |

|-----------------------------------------|----|---|

|-----------------------------------------|----|---|

# **TABLES**

| Tables                                                                               | Page |

|--------------------------------------------------------------------------------------|------|

| Table.3.1 Transistor Count and Area Measurement for CMOS and CT AND, OR, XOR gates   | 25   |

| Table.4.1 Crosstalk Logic Design Table for Basic Gates                               | 28   |

| Table.4.2 Crosstalk Logic Design Table for Complex Gates                             | 32   |

| Table.8.1 Crosstalk Logic Design Table for AND2-OR2 Gate                             | 57   |

| Table.8.2 Crosstalk Logic Design Table for 3-input Polymorphic Gates                 | 58   |

| Table.8.3 Sixteen Reconfigurable functions for the Polymorphic Circuit in Figure 5.6 | 63   |

| Table.9.1 Comparison of Polymorphic Technologies                                     | 66   |

| Table.9.2 Transistor Count Comparison                                                | 68   |

| Table.9.3 Benchmarking of Crosstalk Logic Gates with Respect to CMOS                 | 71   |

| Table.10.1 Transistor Parameters                                                     | 73   |

| Table.11.1 Summary of Different Computing Approaches and Radiation Hardening         |      |

| Techniques                                                                           | 108  |

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my advisor Dr. Mostafizur Rahman for his consistent support and guidance throughout my Ph.D. program. His insight and envision in research and discussions brainstorming the new ideas have enhanced my out-of-the-box thinking mindset in solving the research problems. His enthusiastic encouragement, motivation, and patience have enabled me to accomplish my research goals and helped me improve the skills that I lacked. I would also like to thank my committee members, Dr. Ghulam Chaudhry, Dr. Masud Chowdhury, Dr. Dianxiang Xu, and Dr. Md Yusuf Sarwar Uddin, for their guidance and insightful comments.

I appreciate all the assistance I got from my colleagues in Nano-Computing Lab for this research work. To conclude, I cannot forget to thank my family and friends for all the unconditional support and motivation throughout my Ph.D. program.

#### CHAPTER 1

#### INTRODUCTION AND MOTIVATION

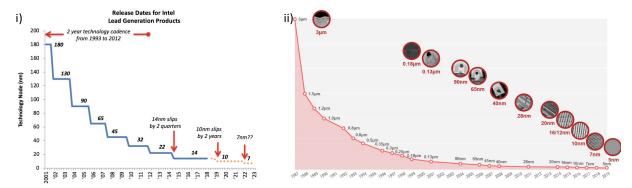

Miniaturization of Integrated Circuits (ICs), conventionally referred by Moore's Law [1][2], has been offering unprecedented socio-economic benefits. Thus, the past few decades have seen exponential growth in digital electronics capabilities primarily due to the ability to scale ICs to smaller dimensions while attaining power and performance benefits. This scalability is now being challenged [3] due to the lack of scaled transistors' performance, leakage, and manufacturing complexities [4]. Specifically, the challenges are device and material fundamental limitations such as quantum mechanical effects [5][6], short channel effects [7], process variation [3], and device parasitics [3], etc. Fig.1.1 shows the historical scaling trend of leading Chip manufacturers, TSMC [8] and Intel [9]. It can be observed from trends that the scaling used to be steep until ~130nm node, which slowed down later. Subsequently, the gate length scaling has saturated in the sub 10 nm regime facing the fundamental limitations. However, foundries were able to scale other dimensions; thus, the technology node numbers marked no longer reflect the exact channel length but the degree to which features are miniaturized. The current technology node in ramp-up (production) is 5nm,

Figure.1.1 Historical Scaling trends: i) Intel Process Technologies [5], ii) TSMC Process Technologies [6]

and 3nm is in development. But the future beyond the 3nm node is gloomy.

Based on the recent research demonstrations, the potential options to continue the scaling benefits can be categorized into three types, 1) Structural innovations of the transistor, such as FINFETs [10], Gate All Around (GAA) Nanowire transistors [13-23], 2) Employing novel materials to improve power and performance [24-27], and 3) Architectural changes of transistors, such as leveraging quantum phenomena for transistor operational mechanism, ex: Tunnel FET (TFET) [28], Negative Capacitance FET (NCFET) [29], etc. (details discussion on these options is presented in the next chapter). Though these techniques might push Moore's law for few more generations, we will soon reach the ultimate atomic and quantum mechanical scaling limit irrespective of the novel channel material choices or structural and architectural changes in transistors [30].

Therefore, industry and academic researchers are actively pursuing various Beyond Moore computing researches to sustain the scaling trend and meet the ever-increasing demand for computational resources on VLSI (Very Large-Scale Integrated circuits) Chips. Some of the directions are neuromorphic computing [34-41], Quantum-dot Cellular Automata (QCA) [42], Single-Electron Transistors (SET) [43], nanomagnetic and spintronic devices [44][45], Quantum Computing [134], etc. Though these directions are promising, they lack significant technology and ecosystem development (from device and circuit to chip design) and suffer from reliability and variability issues (detailed discussion of these directions is presented in the next chapter). Moreover, some of these approaches, like Quantum Computing and Neuromorphic Computing, from their current device and circuit development, reveal that they cannot serve as a complete replacement solution for CMOS digital Chips but can only solve some specific problems efficiently. Therefore, there is a need to explore alternate computing

approaches that are based not only on nanoscale mechanisms/effects but also possess the strong merits of conventional CMOS computing and provide Power, Performance, and Area (PPA) improvements over CMOS. This research uses nanoscale crosstalk signal interference for logic computation and achieves PPA benefits over CMOS. Unlike other approaches, it retains the CMOS technology by augmenting it. The next section introduces the signal interference concept, followed by the Crosstalk Computing concept.

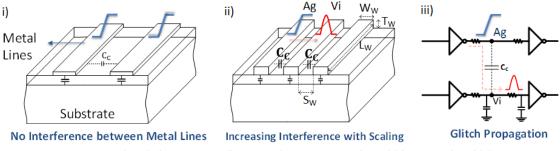

Apart from device scaling limits discussed above, another major concern the advanced technology nodes face is the interconnect bottleneck dominating current Chips' power and performance. Moreover, dense placement of devices and interconnects with advancing technology nodes leads to the adverse proximity effect of increasing interference among neighboring signal lines due to strong capacitive coupling [135]. This phenomenon of unwanted signal interference between nearby signal carrying metal lines is traditionally called Crosstalk [136]. Figure 1.2(ii&iii) depicts the Crosstalk effect. The amount of Crosstalk induced noise is proportional to the Coupling capacitance, which is given by,

$$C_C = \epsilon \frac{(L_W x T_W)}{S_W} \dots Eq. 2(i)$$

where  $\epsilon$  is the permittivity of the dielectric,  $L_W$  is the length of the wire,  $T_W$  is the thickness of the wire, and  $S_W$  is the spacing of the wire. As shown in Figure.1.2(i), the interconnects were spaced apart in older technologies; hence, signal interference was not a critical issue. However, in advanced technology nodes, as shown in Figure.1.2(ii), the signal interference among adjacent metal lines is becoming a crucial issue because of the close spacing (S<sub>W</sub>) of interconnects. Moreover, with advancing technology nodes, increasing the vertical thickness of metal lines (T<sub>W</sub>) has been the solution to maintain the contradictory requirement of lateral

$\label{eq:coupling} \mbox{ Aggressor, Vi-Victim, $C_C$-Coupling Capacitance, $W_W$-Wire Width, $T_W$-Wire Thickness, $S_W$-Wire Spacing, $L_W$-Wire Length}$

Figure.1.2 Crosstalk Signal Interference: i) No signal interference in older technologies, ii) Increasing signal interference in advanced technology nodes; Aggressor-Victim scenario, iii) Circuit equivalent of Aggressor-Victim scenario

shrinkage of metal lines (Ww) and low sheet resistance (Rsq). But increasing vertical thickness, Tw, of metal lines further increases the lateral capacitance, Cc, hence exacerbates the crosstalk noise. Besides, increasing lengths of semi-global and global interconnects in current IC Chips aggravate Crosstalk issues [137]. Various circuit and layout techniques [138][139] and material choices are applied by industry to damp the crosstalk; however, crosstalk is becoming incrementally inevitable in sub 10nm nodes [138]. In interconnect terminology (as shown in Figure 1.2(ii)), the driving inputs would be called Aggressors (*Ag*), and the interference capturing line would be called the Victim (*Vi*). Figure 1.2(iii) shows the equivalent circuit representation of the Aggressor-Victim scenario.

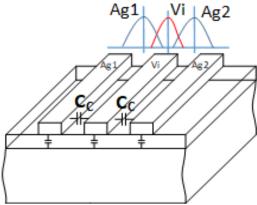

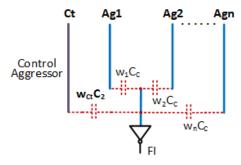

Conventionally, we treat the Crosstalk as a detrimental effect in circuits and always filter it out. However, the Crosstalk Computing style astutely tries to turn this unwanted coupling capacitance into a computing principle for digital logic gates [56][57]. Figure.1.3 shows a Vi net in between two aggressors Ag1 and Ag2. The signal transitions on Ag1 and Ag2 nets will induce an effective summation signal on the Vi net through coupling capacitances Cc. The magnitude of the signal induced depends on coupling capacitance values. From Eq.2(i), the coupling

Figure.1.3 Summation of Crosstalk signal interferences

strength is inversely proportional to the distance of separation of metal lines ( $S_W$ ) and directly proportional to the permittivity of the dielectric and lateral area of metal lines (which is the length ( $L_W$ ) x vertical thickness ( $T_W$ ) of metal lines). Tuning the coupling capacitance values using its variables discussed above provides the engineering freedom to tailor the induced summation signal to specific logic implementation or as an intermediate signal for further circuitry. A host of simple and complex logic gates are implemented using the Crosstalk Computing concept. This deterministic, tunable, and controllable signal-interference concept for computing is also extended to implement compact and efficient reconfigurable logic gates (a unique feature to Crosstalk Computing).

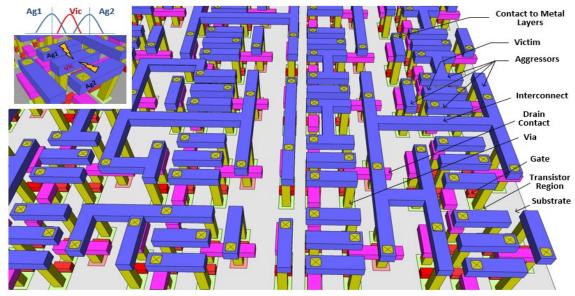

The innovation in this research centers on the computing principles, circuit design principles, physical structures, layout arrangements, and scaling. Figure 1.4 shows Crosstalk Computing fabric; an overview of envisioned IC implementation using Crosstalk Circuits. The interference between metal nano-lines occurs in the bottom metal layer/layers, where logic computation majorly happens. The arrangement of nanometal lines, as depicted in the inset figure, is according to logic/circuit needs. The bottom layer is for transistors required to control the output line's floating behavior and maintain signal integrity. As logic computation happens in metal lines, Crosstalk Computing requires fewer transistors to implement logic gates (regular and reconfigurable),

Figure 1.4 Abstract view of the Crosstalk computing fabric. The inset figure shows Crosstalk principle, where two aggressors (Ag1 and Ag2) are transitioning and as a result charges are induced in Victim line (Vi).

which is the foundation for PPA improvements. Therefore, Crosstalk circuits relax the aggressive transistor scaling requirement by alternately scaling down the circuits, which increases the circuit density.

This work also presents the design and analysis aspects of Crosstalk Circuits (simple, complex, and reconfigurable logic gates) along with simulations. The simulations and analysis work revealed tremendous opportunities for density improvements; the benchmarks showed over 48%, 57%, and 10% improvements in density, power, and performance over CMOS implementations. Along with the density and power efficiency benefits for mainstream digital electronics, our configurable circuits could also spur novel solutions in the realm of hardware security, fault tolerance, resource sharing, and radiation hardening. For example, the rise in connected devices due to the advances in Integrated Circuits (ICs) has also increased sophisticated cybersecurity threats. The ability to hack into ASIC hardware due to the de-

centralized assembly of ICs makes them directly vulnerable. The Crosstalk Computing and its polymorphic circuit implementations inherently possess dynamic operation and obscurity features that can enhance hardware-security.

Therefore, with looming scaling limitations, security vulnerabilities, and lack of efficient circuit techniques for fault resilience, radiation tolerance, and resource sharing, this technology's successful realization can be transformative for the semiconductor industry.

The rest of the thesis is organized as follows. Chapter 2 discusses the current research directions and potential candidates for More Moore integrated circuits and beyond CMOS options. It finally motivates how inevitable scaling limitations of all these approaches necessitate exploring alternate novel and fundamental computing approaches like Crosstalk Computing. Chapter 3 introduces the crosstalk computing concept and presents initial pilot circuits designed to show the computing concept envisioned. Because of the pilot circuit's practical limitations, Chapter 4 develops an improved Crosstalk Computing concept and circuit style inspired by the perceptron model, which overcomes the functional limitations, and feasible. Chapter 5 presents various flavors of Crosstalk circuits possible within perceptron type circuit style. These circuits face some cascaded circuit issues that lead to functional failure. Chapter 6 discusses the problems in detail and presents the three solutions to fix these issues. The solutions are based on different perceptron type circuits, auxiliary circuits, and inherent circuit modifications. They are discussed in detail with examples, alongside trade-offs.

Chapter 7 introduces the concept of polymorphic circuits, i.e., multifunctional circuits, and surveys the existing polymorphic circuit approaches in the literature. Chapter 8 details the polymorphic/reconfigurable computing concept in Crosstalk Computing and presents a list of

polymorphic circuits designed. The circuit design aspects are also detailed, along with simulations. It also shows the cascaded polymorphic circuit examples at gate-level and module-level, which establishes the feasibility of large scale Polymorphic Crosstalk circuits. Next, Chapter 9 discusses the comparison and benchmark results for Crosstalk circuits with respect to CMOS circuits and other polymorphic approaches. Chapter 10 presents the prototype demonstrating feasibility of Crosstalk Computing. The details of the Custom circuit and Chip design, post-silicon functional test, and run-time results are presented in this chapter.

Thanks to the unique, versatile polymorphism feature of Crosstalk circuits, they can be useful for mainstream digital logic circuits and some niche applications. Chapter 11 discusses these potential applications. Finally, Chapter 12 presents future work, where EDA, device, and material researches are proposed for efficient Crosstalk Computing implementation.

#### CHAPTER 2

#### MORE MOORE AND RELEVANT BEYOND CMOS RESEARCH DIRECTIONS

#### 2.1 More Moore Research Directions

Figure.2.1(i) shows the six generations of transistor scaling [31] that are used to continue miniaturization in the sub 100nm regime. Strained Silicon and High-k metal gate stack are the material techniques. The strained silicon improved the planar MOSFETs' performance by increasing the channel mobility. The high-k metal gate stack reduced the unwanted gate tunneling current; it improved the gate control over the channel region, alleviating the short-channel-effects/drain-to-source-leakage, thus enhanced power and performance. But beyond 32nm, the techniques over planar transistor structure fall short. Because of the unsurmountable short channel effects in the planar transistors [3], the tri-gated 3-D FinFET transistors [10] were introduced from the 22nm technology node. Figure.2.1(ii) shows the planar MOSFET and FinFET structures. The 3-D structure of FinFET, with gate wrapping on three sides of the elevated fin/channel region, improves the electrostatic control of the channel region, which has bought some time for the semiconductor industry to continue

Figure.2.1 i) Six generations of transistor scaling, ii) Evolution of transistor structure: Planar MOSFET, FinFET, Gate All Around Nanowire (GAANW) transistor

miniaturization. But FinFET scaling runs out of steam beyond 5nm technology due to unviable amounts of leakage power and poor performance [11-13].

To gain ultimate electrostatic control, Gate-All-Around (GAA) nanowire/nanosheet transistors [14] ( as shown in Figure.2.1(ii)) are the ultimate structural innovation with gate wrapping on four sides of the channel region. Nanowire transistors, as shown in Figure.2.2 [33], are already in the roadmap of the semiconductor industry for beyond 5nm technologies. The nanowire transistor might enable a few more generations of scaling of transistor dimensions, but the current Silicon (Si) transistor-based technology will eventually reach its

Figure 2.2 Imec Transistor road map (the figure is used from [33] with permission)

performance and power limits [15]. Beyond that, there are two directions that the industry and academic researchers are pursuing to sustain Moore's law: 1) 3-D integrated circuits through vertical stacking of devices [16][17], 2) Energy-efficient transistors based on novel materials and architectures [15].

The vertical stacking feature of nanowires (Figure.2.2) can open up a new thirddimensional avenue to pack multiple devices vertically and increase density [18]. For example, multiple lateral fins required in traditional FinFET based circuits (for drive strength purpose) can now be achieved by nanowires in a single vertical stack, thus offer density improvements [15]. Also, researchers are developing fabrication methods and tools to enable large scale production of Complementary FETs (CFETs) [19][20], as shown in Figure.2.2. In CFETs, both p-type and n-type devices are vertically stacked in a single nanowire/nanosheet footprint. This complementary stackability enables Stacked horizontal Nanowire based 3-D (SN3D) [21] integrated circuit approaches. In SN3D, both standard cell logic gates [21] and memory (SRAM) [22] circuits can be implemented into just one or two stacks of nanowires and achieve PPA benefits. Though the nanowire stacks of more than 20 layers were demonstrated, the main factors that hurdle the number of vertical stacks are thermal issues [15] [23], mechanical strength [15], and Parasitic Coupling [15], which limits the density benefits achievable through these 3-D approaches. However, combining the 3-D IC architectures with the futuristic energy-efficient transistors and novel materials (to enhance performance and power) [15] can further push the boundaries.

The potential energy-efficient transistor candidates demonstrated in research labs are based on either novel materials or nanoscale/quantum operation mechanisms. Figure.2.2 also shows these options in the semiconductor industry roadmap [33]. Transistors based on Novel Channel Materials: germanium transistors [24], compound material (group III-V) transistors [25], emerging 2-D material transistors [26], Carbon-Nanotube FETs (CNT FETs) [27], etc. Transistors based on Novel Architectures: Tunnel FETs (TFETs) [28], Negative Capacitance FETSs (NCFETs) [29], CNT TFETs [27-28], etc. The current Si-based IC fabrication technology is very matured over 60 years and cost-effective. These emerging transistor technologies need the development of reliable manufacturing methods and tools for cost-

effective mass production, and they should overcome variability issues before they can serve as a replacement solution to traditional Si-based transistors. Nevertheless, combinations of novel materials, 3-D structures, and energy-efficient architectures are the only option the semiconductor industry has for pushing the incumbent CMOS computing paradigm's boundaries.

The goal of all More Moore approaches (material, structural, and architectural innovations discussed above) is to improve the PPA of transistor-based digital ICs. Crosstalk Computing also uses transistors for threshold operation and signal boosting purposes. Therefore, Crosstalk Computing can take advantage of any innovations or transistor adoptions of future More Moore technologies. As long as the technology is transistor-based, Crosstalk Computing is implementable and can competitively provide PPA improvements over its counterpart CMOS logic implementation. However, as transistor scaling is eventually bound to hit the miniaturization and 3-D stacking limits, there are different Beyond CMOS Computing approaches pursued by researchers, which propose novel nanoelectronic devices. Some relevant beyond CMOS approaches are discussed next, and Crosstalk Computing is compared with them.

# 2.2 Relevant Beyond CMOS Computing approaches

Developing novel Beyond CMOS Computing approaches leveraging the atomic level phenomena or nanoscale effects can be game-changers for future digital VLSI circuits. The important research directions are Neuromorphic Computing, Emerging nanoelectronic devices for logic, and Quantum Computing. However, Quantum Computing is not considered here for discussion since it can only solve specific problems based on Quantum algorithms efficiently but not a good substitute for classical CMOS digital circuits [134].

# 2.2.1. Neuromorphic Computing

Neuromorphic Computing is bio-inspired and imitates the brain-like information processing to attain energy-efficient computation. The brain is 2 to 6 orders of magnitude energy efficient in certain tasks (image recognition, voice recognition, etc.) compared to the most cutting-edge supercomputers today [34]. This efficiency is because of the massive parallel computing and non-von Neumann computing architecture of the brain, where neurons act as computing elements, and their synaptic connections act as memory elements. The analog computation model and massive connections (parallelism) through synapses acting as non-volatile memory give the brain efficient computation capability. Though the software implementation of neural networks on traditional CMOS computing chips is advancing the Artificial Intelligence (AI) capabilities, they are not energy efficient because of Von Neumann architecture. Memory and computing elements are separate in Von Neumann computing, leading to significant power and performance overhead in moving data back and forth. The binary storage of data in conventional Chips also demands extensive resources on Chip, whereas the synapses in the brain store the data in analog format. Therefore, there are significant research efforts and progress in this area, where biological or artificial(software) neural-network type computing models/architectures are attempted to implement directly on hardware.

The key enabler of Neuromorphic Computing is Memristor [35], which is the memory plus resistor. The resistance of the memristor changes with the application of Voltage. Both magnitude and duration/time of the voltage changes the resistance. The resistance state is retained with the removal of voltage, thus acts as non-volatile resistive memory. Multiple reliable resistance states achievable in memristor enable it to be aptly applicable as a synapse

for neuromorphic computing. Nevertheless, it can also be used as a resistive switching memory element (RAM) [36]. The popular memristor structure is comprised of Metal-Insulator-Metal layers [37]. Two metal layers are electrodes accessible as two terminals for voltage application. The input voltage varies the devices' resistance by forming and dissolving the conductive bridge of ions in the Insulator layer, the phenomenon identified as resistive switching [37].

Memristors achieving resistive switching based on different nanoscale physical phenomena are demonstrated in the literature and reviewed in detail [38]. The major ones are, i) Filamentary devices: formation of the conductive bridge of metal ions or oxide ions changes the resistance; (ii) phase-change memory: the extend of voltage-controlled amorphous region changes the resistance; (iii) heterostructure graphene/MoSO/graphene: concentration of oxygen vacancies controlled by input signal changes the resistance; (iv) Ferroelectric memristors: control of intrinsic polarization for ferroelectric materials with a control signal changes the resistance; (v) Organic electrochemical device: concentration of positive ions in an electrolyte layer changes the resistance; (vi) Spintronic devices: a) Josephson junction: the magnetic order in the tunneling barrier changes the resistance, (b) Magnetic tunnel junction: the relative orientation of the magnetic layers changes the resistance, (c) spintronic oscillators [38], etc. As all these device operations are non-charge based nanoscale phenomena, and the computation and storage are analog or multivalued, orders (>100x) of energy efficiency are projected [38]. Along with potentials, they do suffer challenges, which are discussed next.

We can mainly implement digital logic gates, neural networks, in-memory/state-full logic circuits, and memory circuits using memristors. Though it is possible to build combinational and state-full logic gates solely using memristors [39], they face severe

disadvantages such as static power consumption due to current leakage, poor noise margins, signal degradation due to lack of regenerating circuit. A circuit-style combining CMOS and Memristors circuits [39] can achieve signal restoration using CMOS repeaters but still suffer from static power and noise margin issues. Therefore, the current memristor devices are inefficient in implementing logic gates. Hence in state-full logic, a hybrid implementation, where logic gates are CMOS and memory is the memristor, is efficient [40].

Similarly, to implement neural networks in hardware, a hybrid memristor plus CMOS approach is efficient [40]. In this approach, memristor crossbars serve as massively parallel synaptic connections, and neurons are implemented using CMOS based digital and analog circuits. Deep Neural Networks (DNN) are conventionally implemented in software. Although accuracy is more in software implementation, the power consumption is large, and operation is slow due to Von Neumann architecture's memory wall problem. But in hardware implementation, memristors can store multiple voltage levels or even analog levels, which increases the memory density for weights storage on Chip, thus overcomes the memory wall problem and achieves energy-efficient computation. We can write weights into the memristors in three ways [40], offline training, partially offline and partially online training, and fully online training. The training is performed offline on software in the offline method, and final weights are configured/written onto the Memristor crossbar arrays. The system is then used during the test or inference stage. An additional benefit of memristors is that we can inherently perform weighted summation of neuron inputs using current summation in crossbar columns (voltages through rows are the input signals, and memristors' conductances are the previously configured weights). Also, a hybrid approach of partially offline and partially online training is implemented [40]. A fully online technique lacks accuracy because of the device limitations

such as variability in fabrication, asymmetry in memristor behavior, noise, IR drop in crossbar network, etc. [40][41].

So far, only single memristor fabrications and small scale and medium scale crossbar network prototypes are demonstrated [40]. A great deal of technological development is needed to achieve a large-scale reliable crossbar network that enables practical applications. Current full Chip memristor issues to be solved are variability, non-uniformity, asymmetry, and low yield [41][40]. Also, the power consumption of biological synapse is still orders of magnitude lower than is current memristors [40], which signifies the need for further research and improvements. Thus, Neuromorphic computing is a striving field where there are many future opportunities and potentials with ongoing research.

# 2.2.2. Emerging Nanoelectronic Devices for Logic

Some of the important emerging device technologies for denser logic circuit implementation are Quantum Dot Cellular Automata (QCA) [42], Single-Electron Transistors (SET) [43], Nanomagnetic Logic [44], Spin Logic [45], and Ambipolar Transistors [46], etc. 2.2.2.1 Quantum Dot Cellular Automata

In QCA, four quantum dots are arranged as a square, while two electrons are free to tunnel between any of these four dots/wells. The binary data is encoded as the position of these two electrons. Because of Coulombic repulsion, the electrons can only take the diagonal positions; thus, two diagonal positions possible are encoded as 0 and 1. The fundamental gates, such as the inverter and the Majority gate, can be formed using geometric layout techniques. The majority gate, hence majority logic, becomes the underpinning logic style for the QCA computing. The information propagates in the QCA wires through Coulombic coupling. Quantum dots made up of metals [47][48], molecular [49][50], magnetic [51][52],

and semiconductor [53] are experimentally demonstrated. The benefits of QCA computing technology are high device density, ultra-low power, performance up to Thz (Terahertz). But two major drawbacks are thermal fluctuations at room temperature and defects during fabrication [42][54]. Among all, Molecular QCA might be favorable because they can operate at room temperature. The challenges to be solved to enable practical applications are catastrophic high sensitivity to defect density and variation, reliability, and fault-tolerance. Moreover, four clock signals in QCA circuits slow down the large scale designs due to sequencing and synchronization [54].

# 2.2.2.2 Single-Electron Transistors

Single-Electron Transistors (SET) structure is similar to regular transistors, but instead of a channel between source and drain, we have an island of potential well/dot. A single electron will tunnel from source to quantum dot at a time, then form the dot to drain. The gate voltage from the metal gate on top controls the available energy levels for electrons in the quantum dot. In the off state, when the gate voltage is 0, the dot's energy levels are higher than the source energy levels; hence, tunneling is hampered. But in on state, when the gate voltage is above a threshold, the dot's energy levels are lowered to an extent to facilitate the tunneling. Then, another electron tunnels similarly, and so on, thus conducts a single electron at a time. SET devices can be significantly miniaturized, and power consumption will be very low. They do not need some auxiliary CMOS and analog circuits to makes the signals reliable and robust [43]. However, significant challenges to overcome are sensitivity to thermal fluctuations and process variation. As SET operates at one electron's scale, the thermal fluctuations at room temperature make the electron tunneling random/stochastic. Therefore, in their current development form, these devices need cryogenic temperatures to operate

deterministically, making them unsuited for regular digital Chip applications at room temperature.

### 2.2.2.3 Nanomagnetic and Spintronic Logic Devices

Many device ideas are proposed in the literature to implement nanomagnetic logic (NML) circuits[44] and spintronic logic circuits[45]. They use two ferromagnetic layers (one fixed and one flexible layer) or magnetic tunnel junctions to create ON and OFF states similar to the transistor. The flexible layer's magnetization direction is altered using nanoscale phenomena of spin-current, such as Spin-Hall-Effect, Spin-Transfer-Torque, and Domain-Wall-Motion. If two layers' magnetization is in the same direction (parallel), the stack offers low resistance, leading to ON state, and vice-versa in OFF state. The drawbacks of these technologies are i) switching speed is slower than CMOS, ii) static leakage and ohmic dissipations due to current based operation, which decreases the power savings, and iii) poor reliability and interconnect speed.

# 2.3 Crosstalk Computing vs. Beyond CMOS approaches

Unlike Neuromorphic computing, Crosstalk Computing serves as a replacement solution to the CMOS logic implementation. Memristors cannot implement logic circuits efficiently and reliably, but Crosstalk logic circuits are efficient and reliable. Thus, Crosstalk Circuits can also be used in the neuromorphic circuits in place of CMOS digital logic circuits. The improvements over CMOS are 5x density, 2x switch energy and 1.5x performance. However, crosstalk circuits cannot perform the analog or current summation-based computations like memristors, and the multistate/analog non-volatility feature is unique to memristors.

As QCA operates at the electrons' level, they are projected to improve Power greater

than five orders, Performance and Area, 10x and 50x, respectively [55]. Similarly, Nanomagnetic and Spintronic devices can also offer enormous power and area improvement, but they are slower than CMOS and Crosstalk implementations [44][45]. Though Crosstalk Computing cannot offer energy-efficient operations as projected for emerging beyond CMOS devices, they do provide significant improvements over CMOS and coexist with CMOS technology.

Interestingly, Crosstalk Computing does not require complete technology development, as in the case of emerging technologies. It can be realized with the established manufacturing setups of foundries; it leverages the existing fabrication flows, techniques, tools, and materials. As Crosstalk Computing uses the Silicon-based fabrication technology matured over 60 years, the defects and variability issues will be less and not as catastrophic as other emerging technologies; thus, reliability and fault tolerance will be better compared to the other emerging nanoelectronics devices and circuits. Like CMOS, Crosstalk Computing uses the capacitance charge to encode information. Hence it is not fatally sensitive to thermal fluctuations; consequently, it does not need cold or cryogenic temperatures to operate. Nevertheless, if the challenges faced in emerging technologies are overcome in the future, these atomic-scale devices and circuits will obviously have great potential to replace the incumbent CMOS digital circuits. Motivated by immediate solution and benefits of Crosstalk Computing, the subsequent chapters develop the comprehensive circuit technology, promising for More Moore and Beyond CMOS computation paradigms.

#### **CHAPTER 3**

#### CROSSTALK COMPUTING

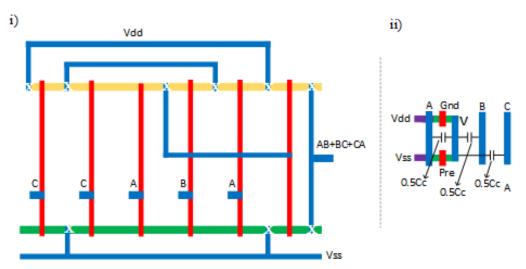

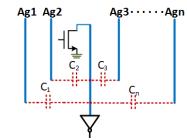

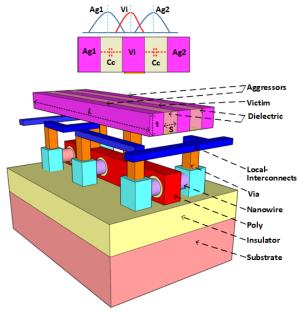

Figure 3.1(i) shows an overview of Crosstalk Computing Fabric, which majorly comprises four components, Crosstalk Layer, Active Devices, Interconnects, and Vias. The Crosstalk layer that computes the logic is a metal layer/layers composed of capacitively coupled metal lines called Aggressors (inputs) and Victim (output). Interconnects and Vias serve their common purpose, along with their contribution to coupling capacitance in Crosstalk Layer. The active devices depicted are FinFETs on SOI substrate. The transistors' goal is to accurately control and reconstruct signals, which would be discussed in the following sections. Figure 3.1(ii) illustrates the aggressor-victim scenario of crosstalk-logic. It shows the capacitive interference of the signals for logic computation—the transition of the signals on two rare end aggressor metal lines (AgI and Ag2) induce a resultant summation charge/voltage on the victim metal line (Vi) through capacitive coupling  $C_C$ . Since this phenomenon follows the charge conservation principle, the victim net voltage is deterministic and possesses the information about signals on two aggressor nets; its magnitude depends on the coupling strength between the aggressors and the victim net. The coupling capacitance is directly proportional to the relative permittivity of the dielectric and lateral area of metal lines (length times the vertical thickness of metal lines) and inversely proportional to the distance of separation of metal lines. Tuning

Figure 3.1 (i) Overview of Crosstalk computing fabric, (ii) Crosstalk Computing Mechanism, (iii) Implementing Logic Gates through crosstalk Computing

the coupling capacitance values using the variables mentioned above provides the engineering freedom to tailor the induced summation signal to the specific logic implementation.

The notion of implementing logic gates using crosstalk signal interference is depicted in Figure 2.1(iii) with AND and OR gate examples. Input signal transitions induce a voltage proportional to coupling capacitances. For AND gate, C<sub>A</sub> (Figure .3.1(iii)) can be chosen such that the magnitude of the voltage induced is greater than a selected threshold voltage V<sub>T</sub> (which differentiates logic levels 0 and 1) only when both inputs transition  $0\rightarrow 1$  (i.e., input combination 11). For single-input changes (input combinations 01 and 10), the voltage induced on the victim net is below the V<sub>T</sub>; hence, the output can be considered logic 0. Thus, as shown in Figure 3.1(iii), AND gate functionality can be realized using the crosstalk signal interference mechanism. Similarly, OR gate functionality can be realized by increasing the coupling capacitance, which can be done by appropriately tuning the physical dimensions or choice of high-k dielectric material or both. The intuition for OR gate implementation is also shown in Figure 3.1(iii). The coupling capacitance Co for the OR gate is greater than the AND gate (i.e., Co > CA), such that the transition of either of the input signal from 0 to 1 is sufficient to induce a voltage above the logic threshold (V<sub>T</sub>). Therefore, input combinations, 01, 10, and 11, computes to logic output 1, as an OR gate. Practical realization of Crosstalk logic circuits and their reliable and robust operation in cascaded topology requires additional circuit techniques to be augmented to the intuitive idea described above, which is presented next.

# 3.1 Pilot Circuits based on pass transistors

The first version of Crosstalk circuits, the pilot circuits, is built solely by employing the Crosstalk Computing principle to demonstrate the deterministic logic behavior. The practical challenges,

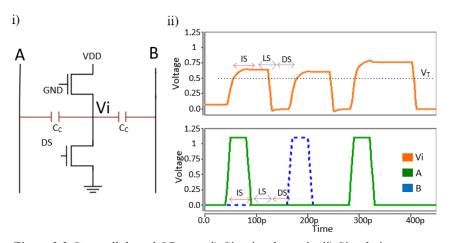

Figure.3.2 Crosstalk based AND gate: i) Circuit schematic, ii) Simulation response

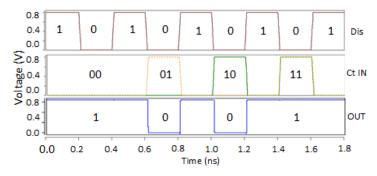

however, are addressed in later chapters, incrementally improving the circuits. A simple AND gate implementation is shown in Figure 3.2(i) [56]. The circuit operation contains three states: Input State (IS) when Inputs are fed through aggressor nets (Ag1 and Ag2); Logic State (LS) when logic is evaluated; and Discharge State (DS) when floating nodes in the circuit are periodically discharged to ground hence gaining control over the floating nodes. Figure 3.2(ii) shows the simulation response of the AND gate. It can be noticed from the figure that inputs A and B transition on aggressor nets during IS, while logic is evaluated during LS, and during DS, the Vi node is discharged to zero. The output

Figure.3.3 Crosstalk based OR gate: i) Circuit schematic, ii) Simulation response

(Vi) node voltage goes above the selected threshold  $V_T$  only when inputs combination is (1,1); the low bumps during (0,1) and (1,0) inputs are assumed to be 0 as they are below the threshold. Figure.3.3 shows the Crosstalk OR gate implementation [56]. Figure.3.3(i) depict schematic, and Figure.3.3(ii) is the simulation response. It can be seen that the Vi node voltage goes above the  $V_T$  for all three input combinations (0,1), (1,0), (1,1); thus, it creates the OR logic pattern.

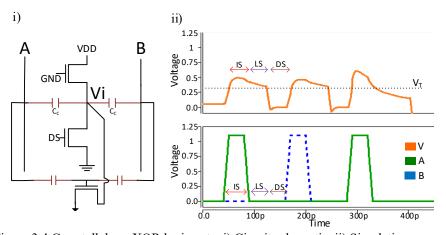

Similarly, the logic implementation of a non-linear circuit like XOR is shown in Figure.3.4 [56]. Figure.3.4(i) is the schematic, and Figure.3.4(ii) is the simulation response. For the XOR gate, the

Figure.3.4 Crosstalk base XOR logic gate: i) Circuit schematic, ii) Simulation response

Figure.3.5 Crosstalk base CARRY logic gate: i) Circuit schematic, ii) Simulation response

output during input combination (1,1) reaches zero gradually during LS. Figure 3.5 shows the Crosstalk implementation of CARRY logic [56], whose Boolean expression is (AC+B(A+C)). As shown in the schematic Figure 3.5(i), a third aggressor net would serve as the C input. The simulation response of the CARRY circuit is shown in Figure 3.5(ii). We can observe that the output is above the selected threshold, i.e., 1, when two or more inputs are 1.

Figure 3.6 shows the stick diagrams of the CARRY circuit in CMOS circuit style (Figure 3.6(i))

Figure 3.6 Stick diagrams for Carry Circuit i) 2D CMOS circuit style ii) Crosstalk circuit style

and Crosstalk circuit style (Figure.3.6(ii)). It can be observed that Crosstalk circuits need only 2 transistors while CMOS needs 12 transistors, and Crosstalk logic consumes less footprint of .044 mm<sup>2</sup> while CMOS consumes 0.13 mm<sup>2</sup> footprint (the area numbers are estimated from stick diagram applying the minimum rules). The CARRY circuit implementation presented shows the potential of Crosstalk circuits with high fan-in logic. Table.3.1 shows transistor count and area comparisons of all logic circuits. Also, emerging 3-D approaches [4] provide additional 3-D architectural benefits to implement Crosstalk Logic circuits. However, these circuits can only demonstrate the Crosstalk Computing concept but suffer significant drivability and signal integrity issues in practical circuits. The *Vi* node, which is assumed to be the output node, might be connected to any fanout load in actual

TABLE 3.1

Transistor Count and Area Measurement for CMOS and Crosstalk AND, OR, XOR Gates

| Logic Gate | Transistor Count |    | Area  |       |  |

|------------|------------------|----|-------|-------|--|

| Logio dato | CMOS             | СТ | смоѕ  | СТ    |  |

| AND        | 6                | 2  | 0.069 | 0.011 |  |

| OR         | 6                | 2  | 0.089 | 0.011 |  |

| XOR        | 14               | 3  | 0.24  | 0.018 |  |

| Carry      | 12               | 2  | 0.13  | 0.015 |  |

circuits. In that case, the voltage induced on Vi net itself depends on the ratio of Aggressor-to-Victim (Input-to-Output) Coupling capacitance to total capacitance on the Vi net, which is,

$$V_{Vi} = \left(\frac{k.\,C_C}{n.\,C_C + C_P + C_I}V_{DDD}\right)$$

where,  $C_C$  is the unit coupling capacitance value specific to each gate. All input aggressors receive coupling strengths in multiples of  $C_C$ . k is the integer multiple that quantifies the amount of total coupling strength through which Vi net experiences voltage induction, i.e., 0 to 1 transition. n is the integer multiple that quantifies the total coupling capacitance associated with the Vi net.  $C_L$  is the next stage fanout load attached to the Vi net.  $C_P$  is the internal/cell-level device and net parasitic capacitance on the Vi net. Assuming  $C_{Int} = n$ .  $C_C + C_P$ , which is the total internal load on Vi net, the voltage induced becomes,

$$V_{Vi} = \left(\frac{k.\,C_C}{C_{Int} + C_L}V_{DDD}\right)$$

Therefore, if the fanout load increases, the *Vi* net voltage will reduce. Thus, a gate logically functioning correct standalone, i.e., zero loads, will not work functionally correct when loaded. Also, as the output node is floating during IS and LS, it lacks drive-strength to drive any output load in the

actual circuits, and it is vulnerable to noise. Thus, the output node faces signal integrity issues. The next chapter discusses a different circuit-style that overcomes the above signal integrity challenges and creates robust signals at the output node.

### **CHAPTER 4**

#### CROSSTALK CIRCUITS BASED ON PERCEPTRON MODEL

The majority of the conventional digital circuits adopted the CMOS circuit style for reliability and robustness reasons. The CMOS circuit-style implements the logic gates by using transistors as gated devices/switches. However, an artificial neural network model, such as a perceptron model (inspired by biological neural networks), shown in Figure 4.1, can serve as a mathematical model that can inspire to implement computing circuits differently. Figure 4.2(i&ii) shows the Crosstalk Circuits implemented based on the mathematical model of perception [57]. The aggressor signals are the inputs, coupling strengths are the weights, summation happens through signal interference, and a CMOS inverter acts as an activation function. As any logical operation can be implemented using one or more Perceptrons, any logical function can also be implemented with the Crosstalk (CT) Circuits.

Figure.4.1 Perceptron Model

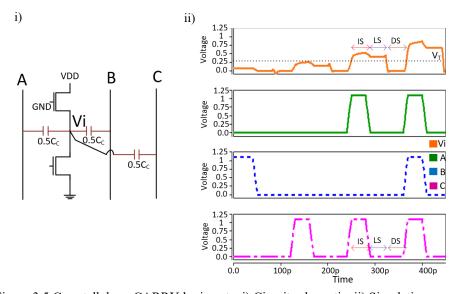

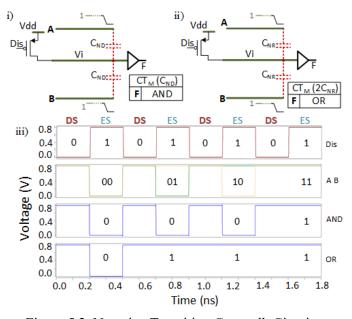

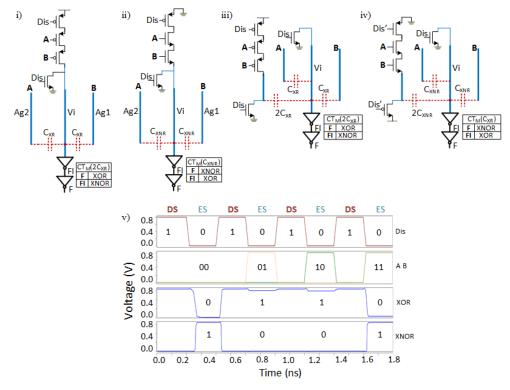

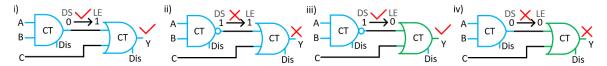

# 4.1 Basic Logic Gates

Although properly engineered coupled nano-metal-lines and very few pass transistors are sufficient to emulate the logic behavior in Crosstalk Computing [56], the output net (Vi) collecting the crosstalk charge needs to satisfy three conditions to achieve deterministic functionality in all sorts of real circuit environments. First, the Vi net needs to start from a

Figure.4.2 Crosstalk Basic Gates: (i) AND gate schematic, (ii) OR Gate Schematic, (iii) Simulation response of AND and OR gates.

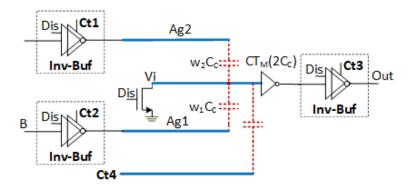

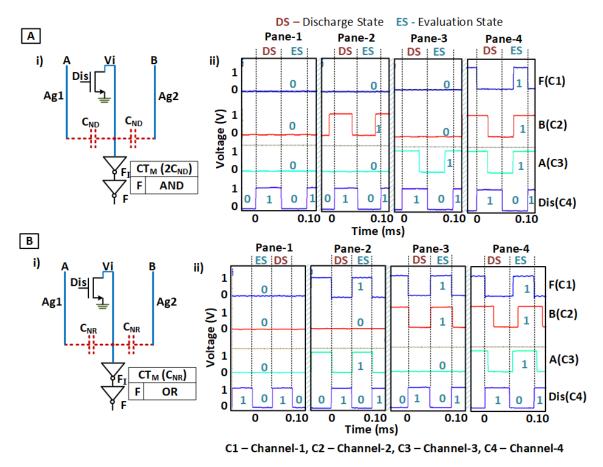

known initial state. Second, it should remain floating during logic evaluation to collect the crosstalk charge. Third (as discussed in the previous chapter), the output node should be able to drive the fanout gates in real circuits and maintain the signal integrity of binary voltage levels. As shown in Figure.4.2(i)&(ii), the first two conditions are met by connecting a discharge transistor to the Vi net, and the third condition is met by adding an inverter to the Vi net. Figure.4.2(i) shows the 2-input AND gate in which input aggressor nets (A and B acting as AgI and Ag2) are coupled to Vi net through coupling capacitances of value Cc (Cc values are given in Table.4.1). The Dis signal drives the discharge transistor. The Crosstalk logic gates operate in two alternate states, Discharge state (DS) and logic Evaluation state (ES).

TABLE 4.1 Crosstalk Logic Design Table for Basic Gates

| Gate | C <sub>c</sub> (fF) | Aggressor Weights |    | Margin                             | Width Ratio |  |  |  |  |  |

|------|---------------------|-------------------|----|------------------------------------|-------------|--|--|--|--|--|

|      |                     | w1                | w2 | Fuction                            | (PMOS:NMOS) |  |  |  |  |  |

| AND2 | 0.8                 | 1                 | 1  | CT <sub>M</sub> (2C <sub>c</sub> ) | 1:1         |  |  |  |  |  |

| OR2  | 4                   | 1                 | 1  | $CT_M(C_c)$                        | 1:3         |  |  |  |  |  |

During DS (enabled by *Dis* signal), the floating victim node is shorted to ground through the discharge transistor and starts with a known initial condition, i.e., 0. The alternate DS states ensure the correct logic operation during every ES state by clearing the previous logic operation's charge. During ES state (*Vi* net is floating), the rise transitions on aggressor nets induce a proportional linear summation voltage on the *Vi* net, connected here to a CMOS

inverter. The inverter acts as a regenerative threshold function. That is if the voltage computed on Vi net is above the inverter's threshold-voltage/trip-point  $(V_{INV})$ , it outputs the logic level 0, and vice-versa; It regenerates the signals and restores them to full swing. Also,  $V_{INV}$  is tunable by changing PMOS to NMOS width ratios if required. The Crosstalk logic gates presented in this paper are designed using the 16nm Predictive Technology Modeling (PTM) [58] transistors and simulated on SPICE. The simulation response of the designed AND gate is shown in Figure 4.2(iii), where the first panel shows the discharge signal (Dis), the second panel shows two input signals (A and B) with 00, 01, 10, and 11 combinations given through successive ES stages (i.e., when Dis=0). The third panel shows the output response of the AND gate. For all the circuits, the FI node gives inverting logic output (NAND, NOR, etc.), and the F node gives a noninverting logic result (AND, OR, etc.). Similarly, OR gate implementation is shown in Figure 4.2(ii), and the simulation response is shown in panel-4 of Figure.4.2(iii) (the input signals in panel-1 and panel-2 are shown common for both the circuits to limit the space). The difference between AND and OR gates is their coupling strength ( $C_C$ ). As given in Table.4.1,  $C_C$  is greater for OR gate than AND, i.e., 0.8fF for AND and 4fF for OR. Cc is the quantized capacitance specific to each gate. The input aggressors would receive the coupling strengths in integer multiples of  $C_C$ .

Crosstalk logic gates' operation would be represented functionally using a crosstalk-margin function,  $CT_M(C_C)$ , specifying that the Crosstalk gate's inverter flips its state only when the victim node sees the input transitions through the total coupling greater than or equal to  $C_C$ . For example, as shown in the table adjacent to the schematic (Figure.4.2(i)), AND gate CT-margin function is  $CT_M(2C_C)$ . It states that the inverter flips its state only when the victim node sees the input transitions through total coupling greater than or equal to  $2C_C$ , which only

happens when both inputs are high. Similarly, for the OR gate (Figure 4.2(i)), the CT-margin function is  $CT_M(C_C)$ , which means the transition of any one of the aggressors is sufficient to flip the inverter, thus execute the OR behavior.

The Crosstalk circuit design and working mechanism for all logic types will be explained using the CT-margin function in this thesis. Therefore, to further elucidate the relationship between CT-margin function and working mechanism of CT-logic gates, consider a generic crosstalk capacitive network with 'n' number of input aggressors, as shown in Figure 4.3. The

Figure.4.3 Capacitive Network of a Generic Crosstalk Gate

voltage induced on the victim net can be calculated by applying KVL, as follows,

$$V_{Vi} = \left(\frac{c_1}{c_T}V_1 + \frac{c_2}{c_T}V_2 \dots + \frac{c_n}{c_T}V_n\right) \dots (Eq \ 4.I)$$

where,  $C_1$ ,  $C_2$  ...  $C_n$ , are capacitances from respective aggressors to the Vi net.  $C_T$  is the total capacitance on Vi net, which is,

$$C_T = C_1 + C_2 ... + C_{INV} + C_{ds};$$

$C_{INV}$  = Inverter Gate Capacitance,

$C_{ds}$  = Discharge transistor drain to source capacitance

The final voltage levels on input aggressors, which are given by  $V_1, V_2 \dots V_n$  in equation (4.1), can be formulated as voltage sources, given by,

$$V_i = L_i V_{DD};$$

where,  $L_i$  represents the logic level, i.e.,

$$L_i = \begin{cases} 0 & if \ logic \ 0 \\ 1 & if \ logic \ 1 \end{cases}$$

The capacitances given to input aggressors are in integer multiples of a constant  $C_C$  specific to each gate. Therefore,  $C_i = w_i * C_C$ ; where,  $w_i$  is the integer multiplying factor representing the weighted strength of each aggressor. The equation (I) now modifies to

$$V_{Vi} = \frac{c_C}{c_T}.V_{DD}.m...(4.II)$$

where  $m = w_1L_1 + w_2L_2... + w_nL_n$ ; m evaluates to integer values. The CT-margin function of each gate can be related to Vi net voltage as follows. Consider a given logic gate is associated with the CT-margin function  $CT_M(k, C_C)$ , where k takes integer values. Then for all the input combinations that produce logic output 0, the Vi net voltage computed is greater than the inverter trip point  $(i.e., V_{Vi} > V_{INV})$  and m is greater than or equal to k (i.e.,  $m \ge k$ ). Conversely, for all input combinations that produce logic output 1, m is less than k (i.e.,  $m \le k$ ), and Vi net voltage is less than the inverter trip-point  $(V_{Vi} < V_{INV})$ . Table 4.1 gives the logic design table for AND2 and OR2 gates, which lists the  $C_C$  values, aggressor weights, and margin function. It also lists the PMOS to NMOS ratio for two gates. The logic design table summarizes the mechanism and circuit aspects of crosstalk logic gates.

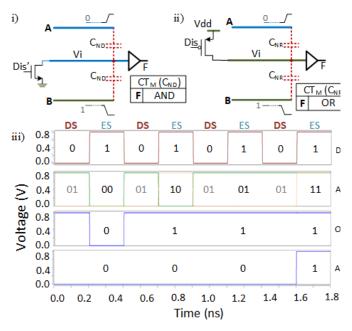

### 3.1 Complex Logic Gates

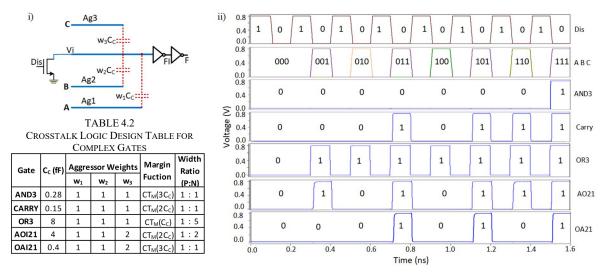

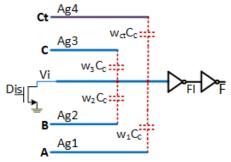

More interesting complex logic functions can be realized by increasing the fan-in (i.e., the number of input aggressors) because of the increased coupling capacitances and CT-margin function choices. The circuit schematic of a generic 3-input Crosstalk gate is shown in Figure 4.4(i). Table 4.2 is a Logic Design table that lists  $C_C$  and  $w_i$  values, CT-margin

Figure.4.4 Crosstalk Complex logic Gates: (i) A generic schematic representing all 3-input complex logic functions ii) Simulations response of 3-input complex logic functions (AND3, CARRY, OR3, AO21, OA21).

function, and PMOS to NMOS width ratio for all 3-input complex-logic functions that are implemented. For logic design, each gate receives a specific quantized  $C_C$  value and different aggressor weights( $w_i$ ) as given in the table. The input aggressors can be assigned equal or unequal coupling capacitances. Gates with equally coupled aggressors are called homogeneous Crosstalk logic gates, and unequally coupled aggressors are called heterogeneous Crosstalk logic gates. These homogeneous and heterogeneous coupling choices further enhance the scope of complex logic functions that can be implemented efficiently through the Crosstalk Computing mechanism. Starting with homogeneous input aggressor weights, that is when  $w_1=w_2=w_3=1$ , the Crosstalk margin function of  $CT_M(3C_C)$  implements a 3-input AND gate, which implies output is 1 only when all three inputs are 1. A CT-margin function of  $CT_M(2C_C)$  implements CARRY(AB+BC+CA) logic, which means output is 1 when any of the two inputs or all three inputs are 1. The CT-margin function of  $CT_M(CC)$  implements a 3-input OR gate, which implies output is 1 when any one or two or all three inputs are 1. The simulation responses of 3-input Crosstalk logic gates designed are shown in

Figure 4.4(ii). The first panel shows Dis pulse, the second panel shows the three input signals, A, B, and C, feeding all input combinations from 000 to 111 in successive ES states (i.e., when Dis=0). The third, fourth, and fifth panels show the simulation responses of Crosstalk AND3, CARRY, and OR3 gates, respectively, for the corresponding inputs in panel-1 and panel-2. Next, by giving weighted/heterogeneous couplings to the input aggressors such that one input has stronger capacitance than the other two (i.e.,  $w_1=w_2=1$  and  $w_3=2$ ), the functions like AO21 and OA21 can be realized as given in Table.4.2. Logic expression of AO21 (AB+C) evaluates to 1 when either AB or C, or both are 1. That means the output is biased towards the input C; the output is 1 when C is 1 irrespective of A and B values. Therefore, input C has twice the coupling capacitance than A and B. Similarly, for OA21 function (A+B)C, the output is again biased towards input C, i.e., for output to be 1, C should be 1 along with A+B. Therefore, as in the previous case, C receives twice the coupling  $(w_3=2)$  than A and B. To satisfy the above logic relations, the margin functions for AO21 and OA21 gates are  $CT_M(2C_C)$  and  $CT_M(3C_C)$ , respectively. The simulation responses of AO21 and OA21 gates, satisfying the logic for all input combinations (000 to 111), are shown in panel-6 and panel-7. Thus, it can be observed from the CT-logic-design table (Table.4.2) that a variety of complex logic functions can be generated by engineering the aggressor weights and inverter threshold-voltage.

### **CHAPTER 5**

#### CROSSTALK CIRCUIT TYPES

The Crosstalk signal interference between two signal-carrying metal lines will happen only when there is a relative change in the two nets' potential/voltage. Therefore, Crosstalk circuits can detect a new logic-level only through signal transition, and logic computation can happen only when input signal changes. The types of signal transitions can be positive  $(0 \rightarrow 1)$ , negative  $(1 \rightarrow 0)$ , or both. Thus, based on the different transition types of signals, the Crosstalk circuits have been classified as the following styles.

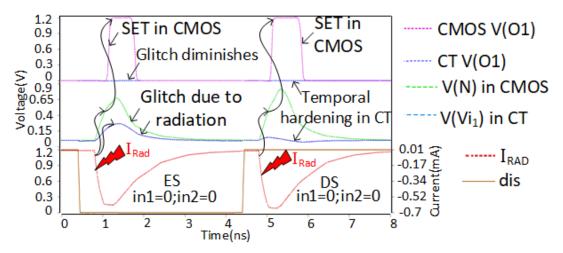

# 5.1 Positive-Transition Crosstalk Circuits