# Deterministic Scheduling of Real-Time Tasks on Heterogeneous Multicore Platforms

©2021

Waqar Ali

Submitted to the graduate degree program in Department of Electrical Engineering and Computer Science and the Graduate Faculty of the University of Kansas in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Dr. Heechul Yun, Chairperson

Dr. Prasad Kulkarni

Committee members

Dr. Esam Eldin Mohamed Aly

Dr. Drew Davidson

Dr. Shawn Keshmiri

Date defended: \_\_\_\_\_ December 15, 2020

The Program Committee for Waqar Ali certifies that this is the approved version of the following dissertation :

Deterministic Scheduling of Real-Time Tasks on Heterogeneous Multicore Platforms

Dr. Heechul Yun, Chairperson

Date approved: \_\_\_\_\_ December 15, 2020

# Abstract

In recent years, the problem of real-time scheduling has increasingly become more important as well as more complicated. The former is due to the proliferation of safety critical systems into our day-to-day life; such as autonomous vehicles, fueled by the recent advances in artificial intelligence. The latter is caused by the increasing demand for high performance which is driving the adoption of highly integrated complex heterogeneous system-on-chip (SoC) processors to deliver the performance while meeting strict size, weight, power (SWaP) and cost constraints. Motivated by these trends, this dissertation tackles the following main question: how can we guarantee predictable real-time execution on heterogeneous multicore SoCs while preserving high utilization?

The fundamental problem in preserving the determinism of the real-time system realized on a heterogeneous multicore SoC is ensuring that the worst-case execution time (WCET) of each task, measured in isolation, will stay within a reasonable bound during the actual execution of the system. The primary challenge in achieving this goal—tightly bounding task WCETs—is that the execution time of a task can be highly non-deterministic, often varying significantly depending on which tasks are co-scheduled and how they contend on various shared hardware resources in the memory hierarchy. The particular scheduling requirements (e.g., non-preemption) of the different computing resources (e.g., integrated GPU) in the heterogeneous SoC and the possible cross-contention among their workloads can also exacerbate this problem.

In light of these considerations, this dissertation presents new real-time scheduling techniques for predictable and efficient scheduling of mixed criticality workloads on heterogeneous SoCs. The contributions of this dissertation include the following: 1) A novel CPU-GPU scheduling framework that ensures predictable execution of critical GPU kernels on integrated CPU-GPU platforms. 2) A novel gang scheduling framework which guarantees deterministic execution of parallel realtime tasks on the multicore CPU cluster of a heterogeneous SoC. 3) Optimal and heuristic algorithms for gang formation that increase real-time schedulability under the RT-Gang framework and their extension to incorporate scheduling on accelerators in a heterogeneous SoC. 4) Concrete evaluation results using simulated tasksets as well as real-world workloads that demonstrate the analytical and practical benefits of the proposed techniques. To my parents, my wife and my daughter

# Acknowledgements

I am thankful to a number of people for helping me get through the doctoral program at the University of Kansas. First and foremost, I want to thank my mentor Dr. Heechul Yun for diligently advising me throughout the course of my PhD program. I would not have reached this point in my pursuit of knowledge—had it not been for your guidance. I also want to sincerely thank the members of my Ph.D. program committee; Dr. Prasad Kulkarni, Dr. Drew Davidson, Dr. Esam Eldin Mohamed Aly and Dr. Shawn Keshmiri, for bearing with me in the scheduling of my Ph.D. exams in these trying times. Special thanks are due to the EECS graduate program coordinator Joy Grisafe-Gross and her predecossor Pam Shadoin for always being there for me whenever I needed guidance with respect to a particular milestone of the KU doctoral program.

I would like to express my thanks and appreciation to all the current and former students, Farzad Farshchi, Prathap Kumar Valsan, Prasanth Vivekanandan Veerapan Chattir, Jacob Michael Fustos, Michael Garrett Bechtel and Ahmet Soyyigit, in the Computer Systems Lab (CSL) at ITTC, KU. Specially, I want to thank Michael for first creating the DeepPicar test-bed and then meticulously conducting the RT-Gang case-study with DeepPicar that I have used extensively in my work, as well as in the writing of this dissertation. Also, I want to thank Ahmet for taking up my work with the RT-Gang framework and keeping it going into the future. I hope that this work is fruitful to you as it has been for me.

I am specially indebted to Dr. Rodolfo Pellizzoni, from University of Waterloo, for helping me with a particularly difficult problem in my research. Without your input, a major portion of this dissertation would be missing or would not have reached the level of quality that it has in its current form.

Finally, I am indubitably thankful to my wife, for following me all the way around the world and for never doubting me through the ups and downs of my student life. This would not have been possible without you.

# Contents

| 1 | Intr | oductio  | n                                                         | 1  |

|---|------|----------|-----------------------------------------------------------|----|

|   | 1.1  | The Pe   | erformance Isolation Challenge                            | 2  |

|   | 1.2  | The N    | uances of Heterogeneous Computing                         | 3  |

|   | 1.3  | Thesis   | Statement                                                 | 4  |

|   | 1.4  | Contri   | butions                                                   | 5  |

|   |      | 1.4.1    | Safe Real-Time Execution on the Integrated GPU            | 5  |

|   |      | 1.4.2    | Deterministic Real-Time Task Scheduling on Multicore CPUs | 5  |

|   |      | 1.4.3    | Virtual Gang Scheduling of Parallel Real-Time Tasks       | 6  |

|   | 1.5  | Organi   | zation                                                    | 7  |

| 2 | Bac  | kground  | l and Prior Work                                          | 8  |

|   | 2.1  | Real-T   | ime Task Models                                           | 8  |

|   |      | 2.1.1    | Task Models for Multicore Systems                         | 9  |

|   | 2.2  | Respon   | nse Time Analysis                                         | 12 |

|   |      | 2.2.1    | Priority based Scheduling Policies                        | 13 |

|   |      | 2.2.2    | The Multicore Scheduling Problem                          | 13 |

|   | 2.3  | Perform  | mance Isolation in Multicore Platforms                    | 15 |

|   |      | 2.3.1    | The Shared Cache Hierarchy                                | 16 |

|   |      | 2.3.2    | Bandwidth and Main-Memory                                 | 18 |

|   |      | 2.3.3    | Performance Isolation on Integrated GPUs                  | 20 |

|   | 2.4  | Summ     | ary                                                       | 21 |

| 3 | Real | l-Time ] | Execution on Integrated CPU-GPU SoC Platforms             | 23 |

|   | 3.1         | Introdu | uction                                        | 23 |

|---|-------------|---------|-----------------------------------------------|----|

|   | 3.2         | System  | n Model                                       | 26 |

|   |             | 3.2.1   | Task Model                                    | 26 |

|   |             | 3.2.2   | CPU Scheduling                                | 27 |

|   | 3.3         | BWLC    | OCK++                                         | 28 |

|   |             | 3.3.1   | Overview                                      | 28 |

|   |             | 3.3.2   | Automatic Instrumentation of GPU Applications | 29 |

|   |             | 3.3.3   | Throttle Fair CPU Scheduler (TFS)             | 32 |

|   | 3.4         | Implen  | nentation                                     | 39 |

|   |             | 3.4.1   | BWLOCK++ System Call                          | 40 |

|   |             | 3.4.2   | Per-Core Memory Bandwidth Regulator           | 40 |

|   | 3.5         | Evalua  | tion                                          | 41 |

|   |             | 3.5.1   | Setup                                         | 42 |

|   |             | 3.5.2   | Effect of Memory Bandwidth Contention         | 42 |

|   |             | 3.5.3   | Determining Memory Bandwidth Threshold        | 44 |

|   |             | 3.5.4   | Effect of BWLOCK++                            | 45 |

|   |             | 3.5.5   | Throughput improvement with TFS               | 46 |

|   |             | 3.5.6   | Overhead due to BWLOCK++                      | 47 |

|   | 3.6         | Schedu  | ılability Analysis                            | 47 |

|   | 3.7         | Discus  | sion                                          | 48 |

|   | 3.8         | Conclu  | ision                                         | 49 |

| 4 | Dool        | Time    | Gang Scheduling on Multicore CPUs             | 50 |

| 4 | <b>4</b> .1 |         |                                               |    |

|   |             |         |                                               |    |

|   | 4.2         |         | Study: Non-Determinism in Multicores          |    |

|   | 4.3         | e       | Overview                                      |    |

|   |             | 4.3.1   | One-Gang-at-a-Time Policy                     |    |

|   |             | 4.3.2   | Safe Best-Effort Task Co-Scheduling           | 56 |

|   | 4.4                                           | Illustra                                                                                   | ative Example                                    | 57                                                                                                                     |

|---|-----------------------------------------------|--------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|

|   | 4.5                                           | Impler                                                                                     | nentation                                        | 60                                                                                                                     |

|   |                                               | 4.5.1                                                                                      | Gang Lock Acquisition                            | 60                                                                                                                     |

|   |                                               | 4.5.2                                                                                      | Gang Lock Release                                | 61                                                                                                                     |

|   |                                               | 4.5.3                                                                                      | Gang Preemption                                  | 62                                                                                                                     |

|   |                                               | 4.5.4                                                                                      | Main Gang Scheduling Algorithm                   | 62                                                                                                                     |

|   |                                               | 4.5.5                                                                                      | Memory Bandwidth Throttling of Best-Effort Tasks | 64                                                                                                                     |

|   | 4.6                                           | Evalua                                                                                     | tion                                             | 64                                                                                                                     |

|   |                                               | 4.6.1                                                                                      | Synthetic Workload                               | 65                                                                                                                     |

|   |                                               | 4.6.2                                                                                      | DNN Workload                                     | 67                                                                                                                     |

|   |                                               | 4.6.3                                                                                      | Overhead                                         | 69                                                                                                                     |

|   | 4.7                                           | Discus                                                                                     | ssion                                            | 70                                                                                                                     |

|   | 4.8                                           | Conclu                                                                                     | usion                                            | 71                                                                                                                     |

|   |                                               |                                                                                            |                                                  |                                                                                                                        |

| 5 | Vint                                          | ual Car                                                                                    | a Sabaduling of Davallal Dool Time Teaks         | 72                                                                                                                     |

| 5 |                                               |                                                                                            | ng Scheduling of Parallel Real-Time Tasks        | 72                                                                                                                     |

| 5 | <b>Virt</b><br>5.1                            |                                                                                            | ng Scheduling of Parallel Real-Time Tasks        |                                                                                                                        |

| 5 |                                               |                                                                                            |                                                  | 73                                                                                                                     |

| 5 |                                               | Requir                                                                                     | rements for Virtual Gang Scheduling              | 73<br>74                                                                                                               |

| 5 |                                               | Requir<br>5.1.1<br>5.1.2                                                                   | rements for Virtual Gang Scheduling              | 73<br>74<br>75                                                                                                         |

| 5 | 5.1                                           | Requir<br>5.1.1<br>5.1.2<br>System                                                         | rements for Virtual Gang Scheduling              | 73<br>74<br>75<br>76                                                                                                   |

| 5 | 5.1                                           | Requir<br>5.1.1<br>5.1.2<br>System                                                         | rements for Virtual Gang Scheduling              | 73<br>74<br>75<br>76<br>77                                                                                             |

| 5 | 5.1                                           | Requir<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2                                       | rements for Virtual Gang Scheduling              | 73<br>74<br>75<br>76<br>77                                                                                             |

| 5 | 5.1<br>5.2                                    | Requir<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2                                       | rements for Virtual Gang Scheduling              | <ul> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> <li>77</li> <li>78</li> </ul>                         |

| 5 | 5.1<br>5.2                                    | Requir<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>The R                              | rements for Virtual Gang Scheduling              | <ul> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> <li>77</li> <li>78</li> </ul>                         |

| 5 | 5.1<br>5.2                                    | Requir<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>The R<br>5.3.1<br>5.3.2            | rements for Virtual Gang Scheduling              | <ul> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> <li>77</li> <li>78</li> <li>79</li> </ul>             |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Requir<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>The R<br>5.3.1<br>5.3.2            | rements for Virtual Gang Scheduling              | <ul> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> </ul> |

| 5 | <ul><li>5.1</li><li>5.2</li><li>5.3</li></ul> | Requir<br>5.1.1<br>5.1.2<br>System<br>5.2.1<br>5.2.2<br>The R<br>5.3.1<br>5.3.2<br>Virtual | rements for Virtual Gang Scheduling              | <ul> <li>73</li> <li>74</li> <li>75</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>80</li> <li>81</li> </ul> |

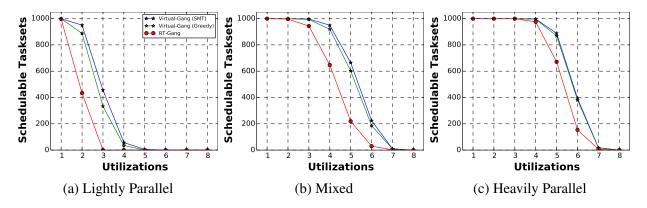

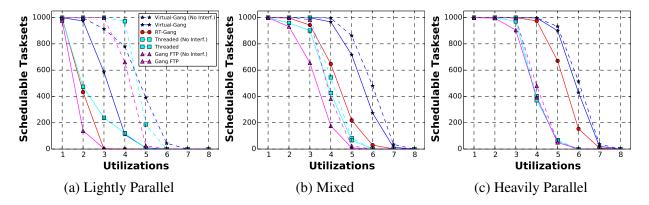

|   |      | 5.5.1    | Simulation Study                                             | 86  |

|---|------|----------|--------------------------------------------------------------|-----|

|   |      | 5.5.2    | Schedulability Results                                       | 88  |

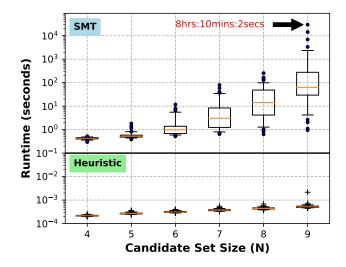

|   |      | 5.5.3    | SMT and Heuristic Gang Formation Runtime                     | 90  |

|   | 5.6  | Evalua   | tion                                                         | 91  |

|   |      | 5.6.1    | Setup                                                        | 91  |

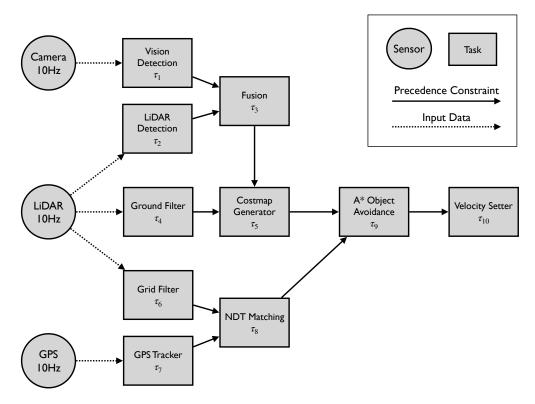

|   |      | 5.6.2    | Case-Study                                                   | 92  |

|   |      | 5.6.3    | Overhead                                                     | 95  |

|   | 5.7  | Discus   | sion                                                         | 95  |

|   | 5.8  | Conclu   | usion                                                        | 96  |

| 6 | Exte | nsions a | and Future Directions                                        | 97  |

| Ū | 6.1  |          | ary of Contributions                                         |     |

|   |      |          | •                                                            |     |

|   | 6.2  | The Ac   | ccelerator Scheduling Problem                                | 99  |

|   |      | 6.2.1    | Hardware Level Scheduling in the Accelerator                 | 99  |

|   |      | 6.2.2    | Performance Isolation between Accelerators and CPU Workloads | 100 |

|   | 6.3  | Virtual  | Gang Scheduling with Accelerator using Tasks                 | 102 |

|   |      | 6.3.1    | System Model                                                 | 102 |

|   |      | 6.3.2    | Virtual Gang Formation                                       | 105 |

|   | 6.4  | Implen   | nentation Changes in the RTG-Sync Framework                  | 108 |

|   |      | 6.4.1    | Gang Scheduling Data-Structure                               | 110 |

|   |      | 6.4.2    | Non-Preemption System Call                                   | 111 |

|   |      | 6.4.3    | Gang Preemption Protocol                                     | 112 |

|   | 6.5  | Future   | Work                                                         | 113 |

| 7 | Con  | clusion  |                                                              | 115 |

# List of Figures

| 2.1  | A Prototypical Periodic Real-Time Task                                | 9  |

|------|-----------------------------------------------------------------------|----|

| 2.2  | Fork-Join and DAG Models of Parallel Tasks                            | 10 |

| 2.3  | A Typical Rigid Real-Time Gang Task                                   | 12 |

| 2.4  | Block diagram of NVIDIA's Jetson TX2 Board                            | 16 |

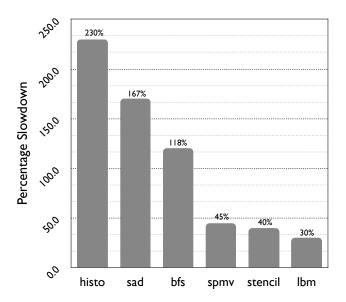

| 3.1  | Slowdown of a GPU Benchmark in a Heterogeneous System                 | 24 |

| 3.2  | BWLOCK++ System Architecture                                          | 28 |

| 3.3  | Phases of GPU Application under CUDA Runtime                          | 30 |

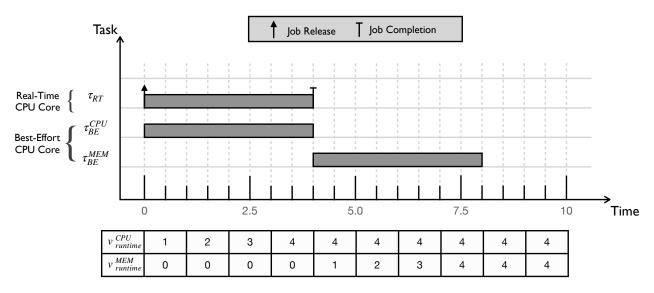

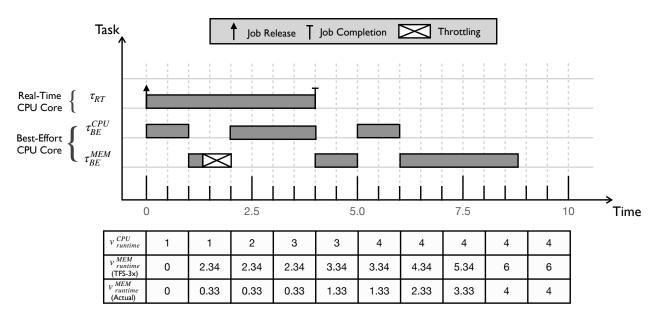

| 3.4  | Illustrative Example: Schedule under CFS                              | 35 |

| 3.5  | Illustrative Example: Ideal Schedule with Zero Throttling             | 36 |

| 3.6  | Illustrative Example: Schedule under TFS with $\rho = 3$              | 37 |

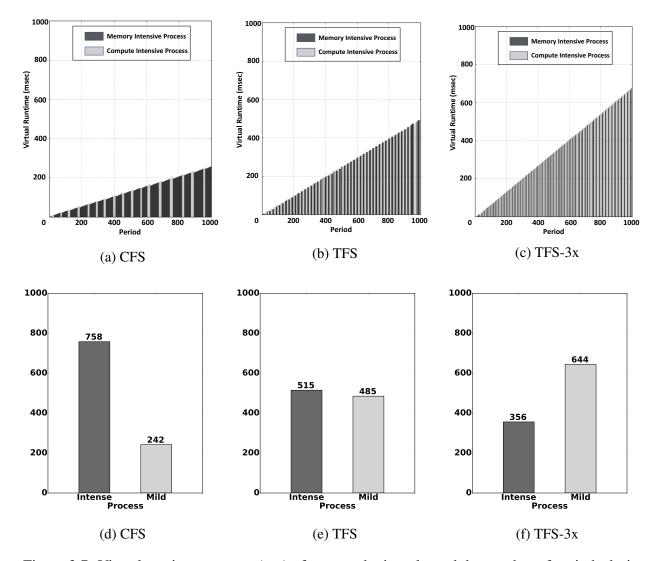

| 3.7  | Virtual Runtime Progression under TFS                                 | 38 |

| 3.8  | Slowdown of GPU Benchmarks under Memory Bandwidth Contention          | 43 |

| 3.9  | Determining the Budget for Best-Effort Tasks under BWLOCK++           | 44 |

| 3.10 | BWLOCK++ Evaluation Results                                           | 45 |

| 3.11 | Effect of TFS in Improving System Throughput                          | 46 |

| 4.1  | Case-Study Illustrating Shared Resource Contention in Multicores      | 53 |

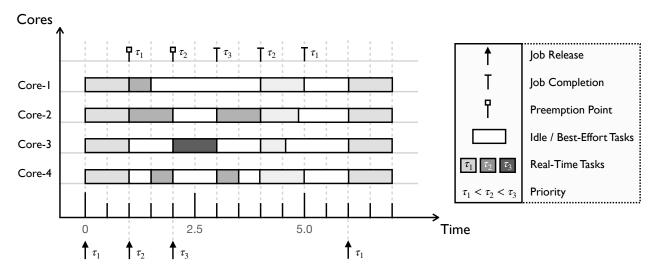

| 4.2  | Illustration of Scheduling under RT-Gang                              | 55 |

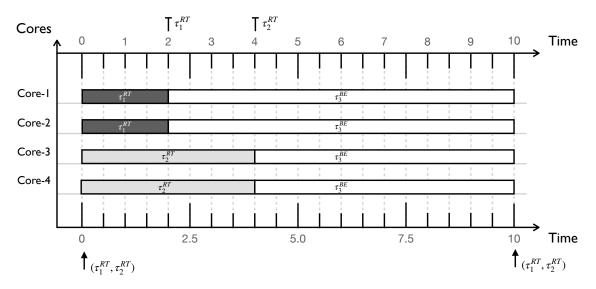

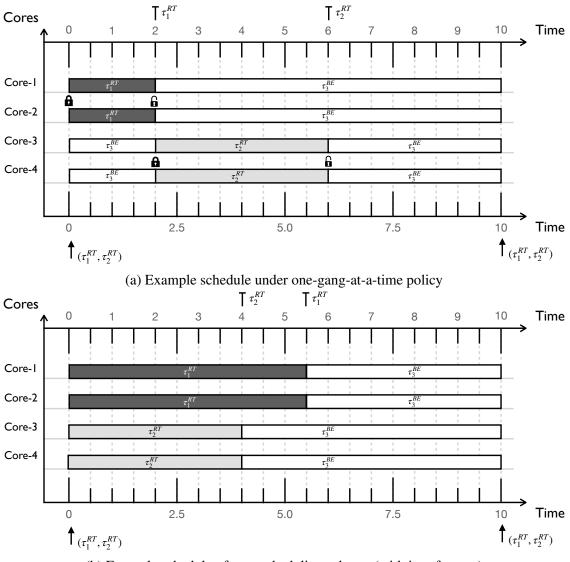

| 4.3  | Illustrative Example (a): Ideal Schedule without Interference         | 58 |

| 4.4  | Illustrative Example (b): Practical Schedule with and without RT-Gang | 59 |

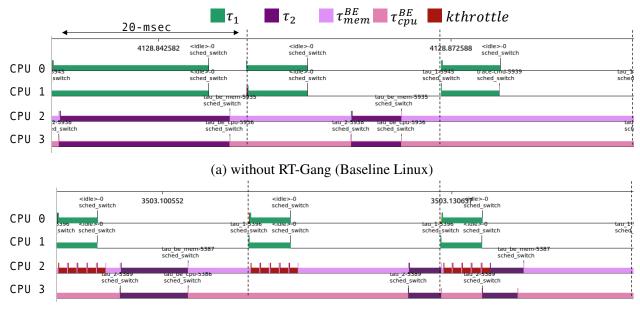

| 4.5  | RT-Gang Demonstration with Synthetic Workload in Linux                | 66 |

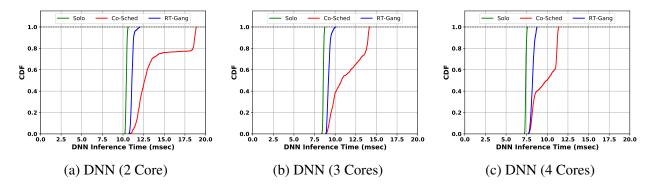

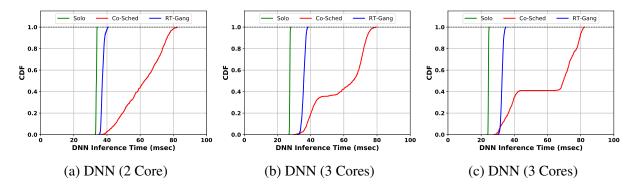

| 4.6  | Performance Evaluation of RT-Gang on Jetson TX2                       | 68 |

| 4.7  | Performance Evaluation of RT-Gang on Raspberry Pi 3                   | 69 |

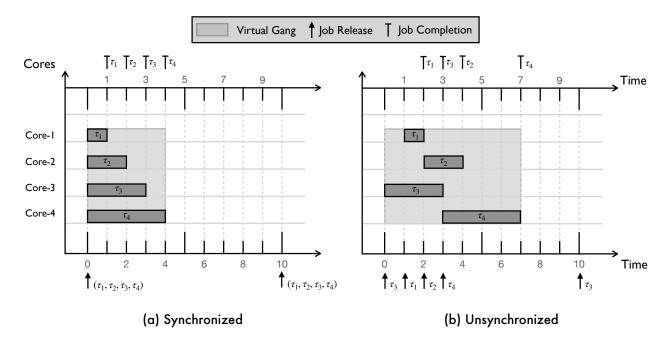

| 5.1 | Need of Synchronization in Virtual Gang Scheduling                         | 74  |

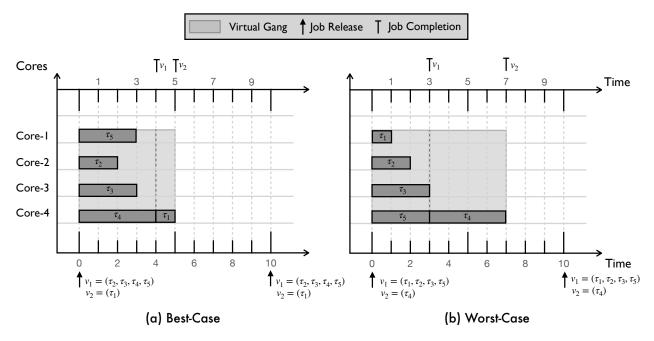

|-----|----------------------------------------------------------------------------|-----|

| 5.2 | Illustration of the Virtual Gang Formation Problem                         | 75  |

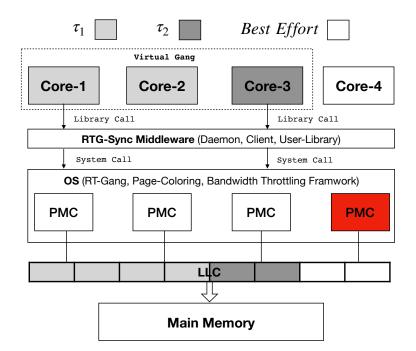

| 5.3 | System Level Architecture of RTG-Sync Framework                            | 79  |

| 5.4 | Schedulability under RTG-Sync with Precedence Constraints                  | 89  |

| 5.5 | Schedulability under RTG-Sync of Independent Tasks                         | 90  |

| 5.6 | Virtual Gang Formation Run-time Comparison                                 | 91  |

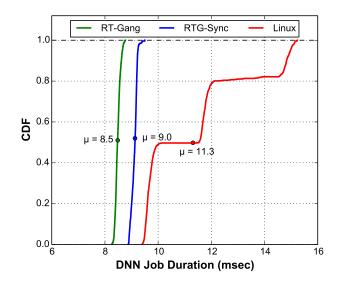

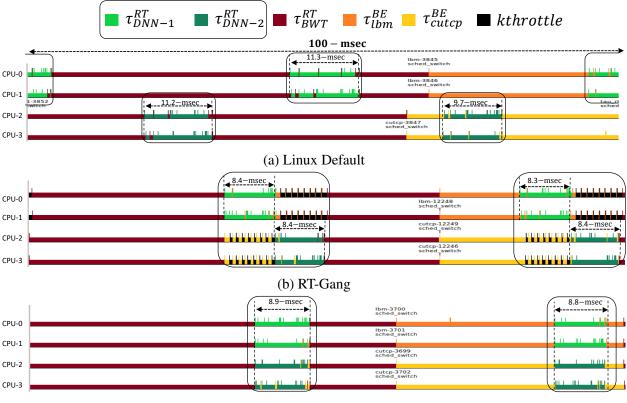

| 5.7 | CDF of DNN Workload under RTG-Sync                                         | 93  |

| 5.8 | Kernel Traces Demonstrating RTG-Sync Scheduling in Linux                   | 94  |

| 6.1 | Example Taskset to Illustrate the New RTG-Sync Task Model                  | 104 |

| 6.2 | Problematic Nested Locking of a Virtual Gang under Non-Preemptive Protocol | 109 |

| 6.3 | Desired Locking Behavior of a Virtual Gang                                 | 110 |

# List of Tables

| 3.1 | Automatic Instrumentation of CUDA APIs under BWLOCK++                         |

|-----|-------------------------------------------------------------------------------|

| 3.2 | Illustrative Taskset for TFS Demonstration                                    |

| 3.3 | Timing Characteristics of Selected GPU Benchmarks                             |

| 4.1 | Taskset Parameters for Illustrating RT-Gang Scheduling Policy    57           |

| 4.2 | DNN Taskset for RT-Gang Evaluation                                            |

| 4.3 | RT-Gang Overhead in Linux                                                     |

| 5.1 | Taskset for RTG-Sync Evaluation    92                                         |

| 6.1 | Sample Taskset Parameters to Illustrate the New RTG-Sync Task Model 105       |

| 6.2 | Sample Taskset Parameters to Illustrate the Need of Implementation Changes in |

|     | the RTG-Sync Framework                                                        |

# List of Algorithms

| 1  | BWLOCK++ System Call                     | 39  |

|----|------------------------------------------|-----|

| 2  | Memory Bandwidth Regulator               | 41  |

| 3  | RT-Gang Lock Acquisition Protocol        | 61  |

| 4  | RT-Gang Lock Release Protocol            | 61  |

| 5  | Gang Preemption Protocol under RT-Gang   | 62  |

| 6  | RT-Gang Scheduling Algorithm             | 63  |

| 7  | Virtual Gang Formation Heuristic         | 84  |

| 8  | Updated Virtual Gang Formation Heuristic | 107 |

| 9  | Non-Preemption System Call               | 111 |

| 10 | Updated Gang Preemption Protocol         | 112 |

# Chapter 1

## Introduction

With the recent advances in the field of artificial intelligence, a new class of real-time applications has emerged which simultaneously demands high performance as well as high safety, predictability, and determinism. Examples of such applications, among others, include autonomous driving cars, unmanned aerial vehicles and robotics. To meet the performance demand of these applications, modern *commercial-of-the-shelf* (COTS) multicore platforms integrate a variety of computing resources in a small form factor system-on-a-chip (SoC). Hence, these days, it is common to come across embedded computing platforms which, in addition to the multicore CPU cluster, contain one or more GPUs as well as special deep learning accelerators and FPGAs. An example of such a platform is NVIDIA's Jetson TX2 [1] board which contains a multicore CPU cluster and an integrated GPU in a single SoC. Due to the varied nature of the computing resources present in such platforms, they are termed as heterogeneous computing platforms and their architecture is called heterogeneous system architecture (HSA).

Although heterogeneous computing platforms offer plenty of raw performance, guaranteeing predictable execution timing of real-time tasks on these platforms is extremely challenging. The primary goal of this dissertation is to investigate the nature of the aforementioned challenges and propose a practically viable solution that can enable efficient usage of these platforms in safety critical real-time applications. We begin by briefly describing the aforementioned challenges in the following.

## **1.1 The Performance Isolation Challenge**

The performance isolation challenge, in using heterogeneous multicore platforms for real-time use-cases, refers to the difficulty in ensuring that the runtime performance of a real-time task will not get affected—or the effect will be within a measurable bound—by the execution of *corunning* tasks in the system. Due to the size, weight, power (SWaP) and cost constraints inherent from their target use-cases, heterogeneous computing platforms contain a memory subsystem that is commonly shared among all the computing elements integrated into the SoC. However, the memory subsystem is often optimized for average performance and in the worst-case, can exhibit extremely poor bottleneck behaviors [2, 3, 4]. For this reason, the runtime performance of applications which are executing simultaneously in such a system, is dependent on how they collectively make use of the shared memory subsystem. This makes it difficult to reliably, and without excessive pessimism, determine the worst-case execution time of the real-time applications which make use of a heterogeneous computing platform; that is instrumental in performing a schedulability test of the system as explained below.

For a critical real-time system, determining the worst-case execution time (WCET) of critical tasks is important and often required for certification [5, 6]. In unicore based systems, the standard method is a two-step approach: (1) obtain the WCET of each task independently from the rest of the system either by using static analysis tools or experimental measurements; (2) perform schedulability analysis based on the obtained WCETs. Applying this approach to heterogeneous multicore SoCs, however, is problematic because of the interference among corunning tasks in the shared memory hierarchy, as mentioned above.

To tackle this problem without requiring modifications to the underlying hardware architecture of the COTS multicore platform, a common approach adopted in a plethora of real-time literature is to partition the most common shared resources in the memory subsystem, such as the last level cache (LLC), the main memory bandwidth and the DRAM etc. However, there is a fundamental limitation of the partitioning based solutions; not all shared resources can be partitioned through software only approaches. Due to intellectual property related issues, the vendors of the COTS multicore platforms do not disclose all the implementation details of their respective platforms. As a result, the users of these platforms have to treat most of the memory subsystem as a blackbox. To safely use such a platform in realizing hard real-time systems, it is imperative to consider all the possible ways in which the tasks in the system can interfere with each other through the shared memory subsystem. This makes the execution of the real-time tasks coupled with each other through the scheduling policy and the underlying hardware architecture of the heterogeneous multicore platform. This coupling can necessitate extremely pessimistic estimation of the interference aware WCET, e.g., up-to 300x of the solo WCET [4], of real-time tasks which can, in turn, severely reduce the overall schedulability of the system. For this reason, in the use-cases where hard real-time guarantees are a must (e.g., avionics), it is recommended to disable all but one core of a multicore processor [6], which obviously defeats the purpose of using a multicore platform in the first place.

## 1.2 The Nuances of Heterogeneous Computing

In a heterogeneous computing platform, the presence of an accelerator such as an integrated GPU introduces a new facet of complications to the real-time scheduling problem. First of all, the method of using the accelerator can be different from the well-understood CPU usage model. For example, in the case of traditional GPU scheduling, an application running on the CPU acts as a master and drives all the computations on the GPU by copying data between CPU and GPU memories (in the case of discrete GPUs) and triggering computations on the GPU as needed. Moreover, due to the often data driven nature of the computation on the accelerators, the computation may have to be performed non-preemptively; as opposed to the conventional CPU scheduling in which a high priority task, barring any locking protocol [7] related requirements, can preempt a low priority task at any time, to take control of the CPU. These nuances necessitate the use of specialized task models which are usually significantly more complicated than the historical periodic task model for CPU only tasksets<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>An overview of relevant real-time task models is provided in Section 2.

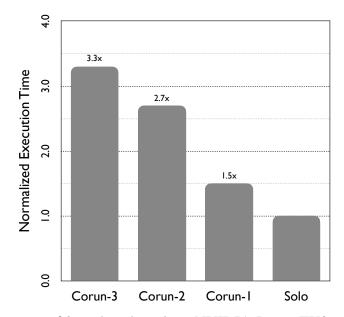

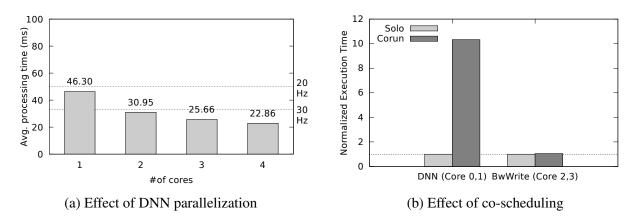

The presence of an accelerator also complicates the performance isolation challenge which is already quite difficult to tackle. In a typical heterogeneous platform, the main memory bus and the main memory itself is shared among all the computing resources i.e., multicore CPU cluster and the accelerators. Due to the limited bandwidth and capacity of the main memory, it becomes possible for workloads running on accelerators to contend for the main memory with those running on the CPU cluster and vice-versa e.g., our work [8] shows that real-time workloads running on the accelerator (i.e., integrated GPU) in NVIDIA's Jetson TX2 platform can suffer up-to 3.3x slowdown due to co-executing memory intensive CPU tasks. However, ensuring performance isolation in this case is even more difficult (as compared to the multicore CPU only case) because of the particular scheduling requirements of different accelerators (e.g., non-preemption) may make it difficult or even impossible to apply traditional performance isolation techniques to solve this problem. We discuss the accelerator scheduling problem in depth in Sec. 6.2 of this dissertation.

### **1.3** Thesis Statement

Motivated by the aforementioned discussion, we present the following thesis statement which forms the basis of this dissertation:

The problem of deterministic scheduling of real-time tasks on heterogeneous computing platforms demands a novel scheduling framework which can eliminate shared resource interference by design. Such a framework must also allow deterministic usage of the accelerators, such as the integrated GPU, in the heterogeneous computing platforms and must be accompanied with an applicable task model, system model and an easy to use schedulability test that can cater to the diverse range of real-time applications that can run on these platforms. Moreover, to be of practical use, the implementation of such a framework must be light-weight and easily portable to the commodity operating systems.

#### **1.4 Contributions**

In the following, we summarize the main contributions of this research.

#### **1.4.1** Safe Real-Time Execution on the Integrated GPU

We present the **BWLOCK++** framework which provides a mechanism to automatically protect real-time GPU kernels in a heterogeneous SoC while minimizing the throughput impact to CPU tasks. This is done by adopting a restrictive scheduling scheme which allows execution of real-time tasks only on a single core in the multicore CPU cluster and using a bandwidth throttling technique to limit the interference from best-effort CPU tasks to the real-time GPU kernel. We make the following contributions in this work: 1) We apply memory bandwidth throttling technique to the problem of protecting GPU accelerated real-time tasks from memory intensive CPU tasks on integrated CPU-GPU architecture. 2) We identify a negative feedback effect of memory bandwidth throttling when used with Linux's CFS [9] scheduler. We propose a throttling-aware CPU scheduling algorithm, which we call Throttle Fair Scheduler (TFS), to mitigate the problem. 3) We introduce an automatic GPU kernel instrumentation method that eliminates the need of manual programmer intervention to protect GPU kernels. 4) We implement the proposed framework on a real platform, NVIDIA Jetson TX2, and present detailed evaluation results showing practical benefits of the framework. 5) We show how the proposed framework can be integrated into the existing CPU focused real-time schedulability analysis framework.

#### **1.4.2** Deterministic Real-Time Task Scheduling on Multicore CPUs

We present **RT-Gang**: a novel real-time gang scheduling framework that enforces a *one-gang-at-a-time* policy. Our goal, in designing RT-Gang, is to enable analyzable and practical parallel real-time task scheduling on multicore platforms. We make the following contributions in this work: 1) A novel gang scheduling algorithm which enables predictable execution on multicore platforms while also providing simpler analysis. 2) Integration of memory bandwidth throttling technique into the

gang scheduler to allow safe co-execution of best-effort CPU tasks. 3) Implementation of our framework on top of the commodity Linux kernel and thorough evaluation on two representative embedded multicore platforms that shows dramatic improvement in the overall predictability of the system under RT-Gang and very low over-head.

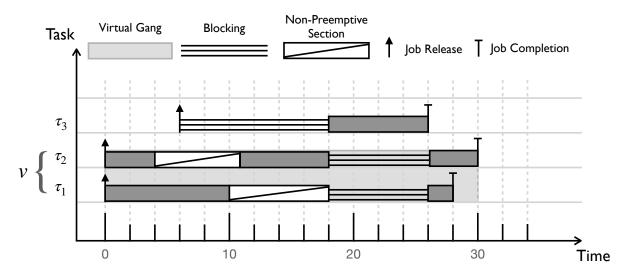

### 1.4.3 Virtual Gang Scheduling of Parallel Real-Time Tasks

We present the **RTG-Sync** framework which allows static grouping of real-time tasks into discrete scheduling entities-called virtual gangs-for scheduling under the one-gang-at-a-time policy of RT-Gang. Our goal, in this case, is to improve the real-time schedulability under the RT-Gang framework when real-time tasks are not perfectly parallelized while preserving the analysis simplicity and runtime determinism proffered by RT-Gang. We make the following contributions in this work: 1) We consider the scheduling of real-time gang tasks with precedence constraints and present the virtual gang abstraction to group certain tasks for co-execution as discrete schedulable units. 2) We present optimal and greedy algorithms for forming virtual gangs from a set of realtime tasks and show how to perform schedulability analysis of a set of virtual gangs using unicore response time analysis. 3) We conduct thorough schedulability study using simulated tasksets and compare the results under our approach against state-of-the-art multicore real-time task scheduling techniques. The results show significant improvement in schedulability under our approach as compared to the competition. 4) We further investigate the requirements of supporting the virtual gang abstraction in a practical system and show that synchronous release of the virtual gang members is necessary to gain practical benefits from virtual gangs. 5) We extend the implementation of the RT-Gang framework to support the virtual gang abstraction and create a middleware framework to enforce the synchronous release of the virtual gang member tasks. 6) We evaluate the extended RT-Gang framework—called RTG-Sync—on the Jetson TX2 platform with a realistic case-study and demonstrate the practical benefits of our approach. Our work is the first one which enables schedulability analysis of real-time gang tasks that are bound by precedence constraints.

## 1.5 Organization

The rest of this dissertation is organized as follows. We present necessary background and a summary of related prior work in Chapter 2. We describe the BWLOCK++ framework and its design, implementation and evaluation results in Chapter 3. In Chapter 4, we present the RT-Gang framework and demonstrate, with an illustrative example as well as a real-world case-study using an autonomous driving test-bed, the benefits of the one-gang-at-a-time scheduling policy in improving the determinism of a real-time system realized on a multicore CPU based platform. We also concretely describe the implementation details of the RT-Gang framework inside the Linux kernel and present the evaluation results on two representative embedded multicore platforms. We begin Chapter 5 by elucidating the need of virtual gang scheduling for improving the real-time schedulability under the RT-Gang framework. We then expressly discuss the practical requirements of virtual gang scheduling with illustrative examples and describe the design of RTG-Sync framework and how it fulfills the said requirements. We also present the virtual gang formation algorithms and present analytical schedulability results from a simulation study as well as empirical evaluation results showcasing the benefits of the virtual gang scheduling in improving the schedulability of an RT-Gang managed real-time system. We provide a summary of our contributions, discuss the limitations of our techniques, the extensions we have already implemented to ameliorate some of those limitations and the possible directions of future research based on our work in Chapter 6. Finally, we conclude our discussion in Chapter 7.

# Chapter 2

## **Background and Prior Work**

In this chapter, we present prior work, in real-time scheduling theory and its practical applications, performance isolation and real-time scheduling on GPU.

#### 2.1 Real-Time Task Models

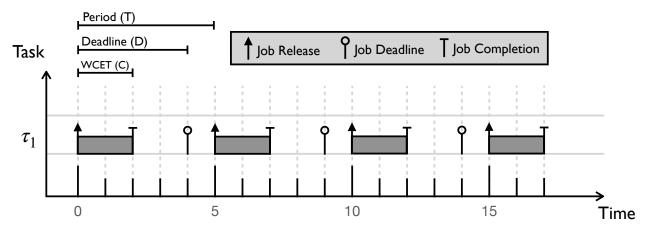

Liu and Layland's Recurrent Task Model: It can be said that the modern research into realtime systems began with Liu and Layland's seminal work [10] in which, among other things, they presented the recurrent real-time task model. As per this model, a real-time task ( $\tau$ ) comprises an infinite sequence of jobs ( $J_1, J_2, \dots, J_i, \dots$ ), each of which is characterized by the time it takes to complete its execution on a target hardware platform. The task itself is characterized by its maximum execution time *C*, period *T* and deadline *D*. The maximum execution time, also called the worst-case execution on a target hardware platform. The value of the period describes the separation between any two consecutive jobs of the task and the deadline quantifies the time interval, measured from the instant when a job arrives, during which the job should finish its execution; for the task to be deemed schedulable. The task is considered a *hard real-time* task if it must always meet its deadline; for the timing correctness of the system. If the task can tolerate the deadline misses to some extent, then it is called a *soft real-time* task. In this dissertation, when we refer to a real-time task, we mean a hard real-time task unless explicitly stated otherwise.

In Liu and Layland's original proposal, the value of the period is fixed, in the sense that the jobs of the real-time task are released exactly T time-units apart and the resulting task model is

Figure 2.1: Activation diagram of a periodic real-time task

called the *periodic task model*. In a later relaxation of this model, the value *T* delineates the minimum separation between any two jobs of the task and the task model is called the *sporadic task model* [11]. Moreover, based on the relationship between the period and the deadline, the task model is further classified as *implicit deadline* or *constrained deadline*. In the former, for each job of the task, the deadline is equal to the period whereas for the latter, the deadline must be less than or equal to the period value. An activation diagram showing a prototypical constrained deadline periodic real-time task, with a WCET of 2, a deadline of 4 and a period of 5, is shown in Figure 2.1.

Despite several decades that have passed since the time it was presented, Liu and Layland's work is still relevant today and almost every major work in real-time scheduling theory makes use of their presented task model, in one form or another, based on some specific use-case. In that sense, their work is a canon in the subject area.

## 2.1.1 Task Models for Multicore Systems

The classical periodic task model applies to systems that contain a single processing element e.g., a unicore CPU based platform. By virtue of that, in such a system, each job of the real-time task must execute entirely on the single processing entity. In a modern embedded computing system, there can be multiple processing elements, such as a multicore CPU cluster, an integrated GPU and additional purpose built accelerators, all integrated into a compact System-on-a-Chip (SoC)

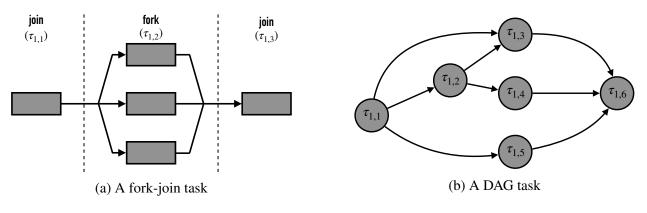

Figure 2.2: Parallel real-time task models

configuration. Consequently, real-time applications which make use of these platforms can have diverse computing requirements which cannot be expressed adequately using the classical periodic task model. In this section, we discuss three representative task models, from real-time scheduling literature, that can be used to express real-time workloads that make use of a multicore CPU based computing platforms. Importantly, we describe the real-time gang task model in detail which is used extensively throughout this dissertation.

#### 2.1.1.1 The Fork-Join Model

In the fork-join model of parallel real-time tasks [12, 13, 14, 15, 16], the execution of each job of a real-time task consists of a sequence of serial and parallel execution phases. In the serial (*join*) phase, the job requires only a single CPU core to execute whereas in the parallel (*fork*) phase, the job can execute simultaneously on multiple CPU cores. The different phases of execution of a fork-join task have a linear precedence relationship among them: phase (i+1) can begin execution only after phase (i) has completed. Figure 2.2a shows an illustration of a task that can be expressed using the fork-join model. Despite its simplicity, the fork-join model is quite popular and supported by a number of parallel programming frameworks [17, 18, 19].

#### 2.1.1.2 The DAG Model

In the DAG model [20, 21, 13], each job of the periodic real-time task is represented as a directed acyclic graph (DAG). The nodes of the DAG represent the execution phases of the job and the edges represent the precedence constraint relationship among the execution phases. Each execution phase is itself sequential i.e., it executes entirely on a single CPU core. Figure 2.2b shows an illustration of a task that can be expressed using the DAG model. In essence, the DAG model is a generalization of the fork-join model and it is suitable to express real-time workloads which have more complicated relationship among the phases of execution that cannot be expressed using the linear scheme of the fork-join model.

#### 2.1.1.3 The Gang Model

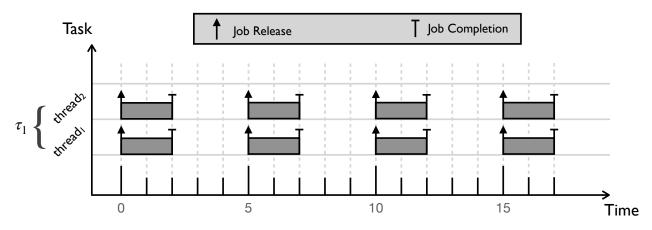

In the gang model of parallel real-time tasks [22, 23, 24, 25], each job of the task is characterized by the number of cores m it needs to execute; in addition to its execution demand c and the period p value as per the classical periodic task model. Based on the nature of the core requirement parameter m, the gang task model is further divided into a number of categories which are described in the following.

**Rigid Gang**: In the rigid gang model, the number of cores required to execute the gang are determined off-line and they stay the same for all of the jobs of the gang throughout its execution. Figure 2.3 shows the activation diagram of an implicit deadline periodic rigid gang task.

**Moldable Gang**: If the number of cores required to execute a gang are determined on-line, on a per job basis, by the scheduler but once determined, the core requirement stays the same throughout the job's execution, then the resulting model is called the moldable gang model.

**Malleable Gang**: If the number of cores required to execute the gang can change during the execution of the job, then such a gang task model is called the malleable gang model.

**Bundled Gang**: The bundled gang model, introduced recently [25], is a generalization of the rigid gang model. As per this model, the execution of each job of a rigid gang task is sub-divided into

Figure 2.3: Activation diagram of an implicit deadline rigid gang task

multiple execution segments—or bundles—each of which can have a distinct core requirement, determined off-line, that can be different from one bundle to another. The bundles are bound by a linear precedence requirement i.e., bundle (i+1) cannot start before bundle (i) has finished its execution.

For the purpose of this dissertation, the rigid gang model is most relevant and will be discussed in more detail, in the context of real-time gang scheduling, in Chapter 4 and Chapter 5.

#### 2.2 **Response Time Analysis**

In real-time scheduling, it is of utmost importance to know *a-priori* whether a real-time task will meet its deadlines in a particular use-case. A large body of literature in real-time scheduling theory revolves around devising offline analytical tests that, given a set of tasks parameterized as per a suitable task model, can be used to determine whether each task in the taskset will be able to meet its deadline. The process of analytically determining the schedulability of a real-time taskset is called *response-time analysis* [26, 27, 28]; for the reason that the tests involved in this procedure determine the response-time of the real-time tasks which is defined as the time interval since the arrival of a job of a task to the time that the job completes its execution. Integral to the response-time analysis is the scheduling policy of the target system which determines which task(s) to execute on the available computing resources from a group of tasks that are ready to

execute, based on the notion of *priority*. In the following, we discuss most widely used priority based scheduling policies from real-time scheduling literature that are relevant to the discussion presented in the later chapters of this dissertation.

## 2.2.1 Priority based Scheduling Policies

Priority based scheduling of real-time tasks can be broadly divided into two categories, based on how the priority of each job of a given task is determined. In fixed priority scheduling, the priority of each job of the task is statically determined offline and does not change throughout the task's execution. An example of fixed priority scheduling is *rate-monotonic* (RM) policy [28], in which, a task with a smaller period is given a higher static priority value. In contrast, in dynamic priority scheduling, the priority of each job of the task is determined online dynamically before the job starts executing. An example of such scheduling scheme is *earliest deadline* first (EDF) policy [10] in which, as the name implies, a job with the closest deadline is given the highest scheduling priority.

In comparing different policies for scheduling real-time tasks, the notion of *feasibility* and *optimality* are of vital importance. A taskset is said to be feasible under a specific scheduling policy if it can be analytically proven that all tasks in the taskset will always be able to meet their deadlines if scheduled according to that policy. A scheduling policy, for a specific priority assignment scheme, is considered optimal if it can schedule all feasible tasksets under that scheme. An optimal scheduling scheme is highly desirable in scheduling hard real-time tasks. For single-core based platforms, it has been proven that rate-monotonic policy is optimal for fixed priority scheduling and EDF policy is optimal for dynamic priority scheduling [10]. For platforms with multiple cores, the problem is considerably more complicated as explained in the next section.

## 2.2.2 The Multicore Scheduling Problem

In a multicore system, a significant source of complication to the real-time task scheduling problem arises because of the presence of multiple computing cores that can be used to run a ready task. Moreover, the task models used to describe multicore workloads can be considerably more intricate and hence conceptually difficult to handle than the classical sequential periodic tasks, as described in the earlier sections of this chapter. Based on the scope of problem, the multicore scheduling is divided into three types; each of which is briefly discussed in the following.

#### 2.2.2.1 Global Scheduling

In global scheduling [29, 15, 30], real-time tasks are opportunistically scheduled on the first available core in a multicore platform. If no such core is available, then the lowest priority task running in the platform is preempted in favor of the highest priority ready task, if the priority of the latter is greater than the former. From implementation point of view, global scheduling requires a single ready-queue to keep all the ready tasks in the system and it can select tasks from the readyqueue based on their assigned priority value; as per a fixed priority or dynamic priority assignment scheme. Although conceptually simple, global scheduling is usually avoided in commodity operating systems due to the runtime overheads e.g., cache management and synchronization, associated with this policy in multicore platforms.

#### 2.2.2.2 Partitioned Scheduling

Contrary to the global scheduling paradigm, in partitioned scheme [31, 32], the scheduling problem is divided into two parts. In the first (offline) part, the tasks are statically assigned to the different cores available in the target hardware platform. In the second (online) part, each core in the target platform executes the task present in its ready-queue using an appropriate priority assignment scheme, just like a unicore system. From the implementation and analysis point of view, partitioned scheduling is straight forward because in a partition scheduled system, each core can operate locally on the tasks in its ready-queue without considering the other cores and the schedulability of the tasks in a core's ready-queue can be determined using well-known unicore response-time analysis techniques. However, partitioned scheduling has its own caveats due to its offline task-to-core mapping phase which requires solving a bin-packing like problem that is known to be NP-hard in the strong sense [33].

#### 2.2.2.3 Clustered Scheduling

This scheme is a generalization of the global and partitioned scheduling policies. In clustered scheduling [34, 35], the multicore platform is divided into clusters of computing cores. Tasks are statically partitioned among the clusters and inside the clusters, the assigned tasks are scheduled using the global policy. Based on the size of the clusters, this scheduling policy transforms into partitioned scheduling if the number of clusters is equal to the number of cores in the target platform and it becomes equivalent to global scheduling when there is only one cluster containing all the cores.

Each of the scheduling policy described above, when coupled with an appropriate task model and a priority assignment scheme, has a known response-time analysis formula for determining the schedulability of a given set of real-time tasks and each such combination has an associated set of trade-offs which make it more suitable for a particular real-time scheduling use-case than others. *Common to all these scheduling schemes, is the fundamental characteristic that any real-time task can conceptually get co-scheduled with any other real-time task present in the system; there is no inherent restriction that limits the possible co-scheduling of particular real-time tasks across different cores of a multicore platform.* In the following section, we will elaborate why this can be problematic and from there, we will motivate the need for a novel *interference-aware* scheduling policy that is one of the main contributions of this dissertation.

#### 2.3 Performance Isolation in Multicore Platforms

The type of multicore platforms that we focus on in this dissertation can be characterized as sharedmemory based multicore platforms, due to the reason that in the architecture of these platforms, the memory hierarchy is shared to varying extent among all the computing resources. An example

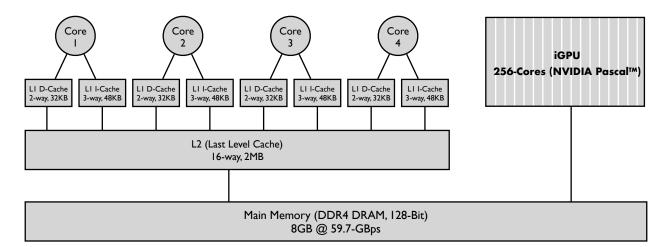

Figure 2.4: Illustration of the shared memory subsystem in NVIDIA's Jetson TX-2 heterogeneous computing board

of such a platform is NVIDIA's Jetson TX-2<sup>1</sup> board [1], which contains a quad-core CPU complex and an integrated GPU, as shown in Figure 2.4. Due to the size, weight, power (SWaP) and cost constraints, in these platforms, the hardware resources are at a premium and there is a strong desire to utilize all these resources to their fullest potential. Unfortunately, this results in a memory subsystem that is geared to optimize the most common use-cases and usually cannot provide any determinism guarantees in situations when the system is heavily loaded due to hardware level interference among co-scheduled applications. In the following, we describe the most important and well-studied sources of this *shared resource interference* in the use of shared-memory based multicore platforms in real-time systems; along with the state-of-the-art techniques proposed in prior works to mitigate the respective problems that arise from such interference.

#### 2.3.1 The Shared Cache Hierarchy

In modern computer architecture, a processor cache is a fast memory block that provides handy and quick access to the most frequently accessed memory items [36, 37]. Caches are usually structured in levels in the form of a hierarchy; with the level closest to the processor containing caches that are the fastest, relatively smallest and local to the processor and the caches in subsequent levels being

<sup>&</sup>lt;sup>1</sup>Technically, the TX-2 board contains 6 CPU cores (2 Denver + 4 Cortex A57). However, we only use the Cortex A57 cores when scheduling real-time tasks on TX-2 and the block diagram also reflects the same.

increasingly larger in size, slower in speed and shared to a certain extent among multiple processing cores in the SoC. For example, in Figure 2.4, the multicore CPU cluster in TX-2 contains a 32-KB core local data cache, a 48-KB core local instruction cache and a 2-MB L2 cache that is shared among all the four cores. From a performance isolation point-of-view, the shared last level cache (L2 in the case of TX-2) is important because a *cache miss* in the LLC requires a data item to be fetched from main memory which is an order of magnitude slower than the cache hierarchy [38]. Unfortunately, since the LLC has limited space and it is shared among all the CPU cores, it is possible for tasks executing on one core to evict the data cached in the LLC of a task executing in another core. When the task whose data items got evicted, tries to access that data again, it will incur *cache misses* and its execution time will get adversely affected because of that. This is one source of interference that can arise because of how the LLC is utilized simultaneously by co-executing tasks in a multicore platform.

Apart from conflict misses, co-executing task in a multicore platforms can interfere with each other in more ways based on how they utilize the shared LLC. One such interference arises due to a limited resource inside one type of LLC common in modern COTS multicore platforms— a non-blocking cache—which comes into play when there are multiple outstanding LLC misses that need to be serviced from the main memory. These structures are called *miss-status holding registers* (MSHRs) and they are usually limited in number. It has been shown [3] that interference due to MSHRs can cause up-to 21x slowdown of real-time tasks.

Yet another source of interference due to the shared LLC arises due to the limited capacity of the write-back buffers inside the cache. Like MSHRs, write-back buffers are used in a *write-back* cache to keep track of outstanding memory write requests. When a write-back buffer fills up, it can cause lock-up of the LLC and can adversely delay all the cache requests—even those for whom the data is already present in the LLC i.e., cache hits. Interference due to write-back buffer can be extremely severe; it has been shown [4] to cause more than 300x slowdown to the performance of real-time tasks in a well-known and widely used COTS multicore platform.

Mitigating LLC Interference: Due to the importance and severity of the interference that can

arise due to the shared LLC in a multicore system, both software [39, 40, 41, 42, 43, 44, 45, 46, 47, 48] and hardware based techniques [49, 50, 51, 52] have been extensively studied in prior works to mitigate the extent of this problem. Most such techniques employ some form of LLC space partitioning, through purely software based mechanisms or with software / hardware co-design, to isolate the data of co-executing tasks inside the LLC. Among software based techniques, page*coloring* is a well-known mechanism to enforce LLC space partitioning and has been shown to be effective in a number of existing studies [53, 40, 47, 48]. In hardware based techniques, the lockdown by line feature in the older generation ARM architecture based CPUs [50] and the recently introduced cache allocation technology (CAT) feature [51] in the Intel architecture are noteworthy. Existing work that makes use of the former to address LLC interference includes [54] whereas for the latter, [55] is a framework that makes use of Intel CAT to ensure quality-of-service (QoS) among real-time tasks. The authors of [3], who first identified the MSHR contention problem, also proposed a hardware based solution to mitigate it and demonstrated its effectiveness in a cycle accurate full-system simulator. Similarly, the authors of [4] proposed a rate-limiting approach using hardware performance monitoring counter (PMCs) to mitigate the interference due to writeback buffers inside the LLC.

#### 2.3.2 Bandwidth and Main-Memory

After the shared cache hierarchy, modern COTS multicore platforms contain a large main memory that is connected with the last level cache through a high speed memory bus. In addition to the CPU cores in the embedded multicore platforms, the main memory is usually shared among all the computing resources present on the chip. For example, in the NVIDIA's Jetson TX-2 board shown in Figure 2.4, the main memory is used by all the cores in the CPU cluster as well as the integrated GPU. This introduces another facet of challenge in deterministically using this resource in real-time scheduling ; in addition to the co-executing CPU applications, interference at the level of main memory can happen among the workloads running on the accelerators such as integrated GPU and those running on the CPU cores. The authors of [56] demonstrate the performance

deterioration of the workloads running on the CPU from the interfering memory traffic of the GPU using workloads in NVIDIA Jetson boards. In [57] and [8], the converse effect—the interference on the performance of real-time GPU applications due to CPU side memory traffic—is shown. Due to these challenges, deterministically utilizing the main memory for real-time applications in modern multicore SoCs can be extremely arduous.

Mitigating Memory Level Interference: Similar to the solutions for mitigating shared LLC interference, proposed approaches to address main memory level interference also fall into software based and hardware based techniques. In the software based approaches, page-coloring has been shown to be effective [48, 58, 59, 54] in enforcing space partitioning of the main memory banks among co-executing applications; albeit the fact that this method is only applicable if certain architectural details of the main memory are known or can be inferred through reverse engineering. Moreover, space partitioning cannot ameliorate the interference that can arise due to the limited bandwidth of the main memory bus. To address the latter, a fundamental approach used in a number of prior works is memory bandwidth throttling [2, 60, 54] which uses hardware performance monitoring counters (PMCs) to limit the memory usage quota of co-executing applications. Although effective to a certain extent, memory bandwidth throttling has two fundamental limitations. First, it is difficult to analyze the impact of throttling on the execution of real-time tasks; an analysis [61, 62] that takes the effect into account is bound to be severely pessimistic. For this reason, a throttling based mechanism is commonly used to isolate the performance of real-time tasks from lower criticality best-effort tasks only. Second, a software based throttling mechanism requires the system designer to have the ability to enact preemption of an offending workload; irrespective of where it is executing. Although preemption of CPU using workloads is straight forward, the same is not true for accelerators such as GPU where preempting a currently executing workload can incur unacceptable overheads and hence software based preemption control is traditionally not made part of the GPU's programming model. In such a case, memory bandwidth throttling is not possible to ensure performance isolation among applications that are simultaneously using the main memory.

In the hardware based solutions to the memory level performance isolation challenge, the deterministic memory abstraction [63] is notable in which, the authors design a new memory abstraction for expressing the criticality of memory requests. To enforce deterministic access to the critical memory areas, they propose fundamental changes to the OS and the hardware. Although effective, the deterministic memory solution is not applicable to COTS multicore platforms in which, making changes to the hardware after it has been designed and shipped, is not feasible. Recently, Intel introduced the memory bandwidth allocation (MBA) technology [64] to enforce quality-of-service measure in accessing the main memory on Intel platforms where this feature is available [65]. At the time of this writing, we are not aware of an authoritative work that makes use of MBA to effectively address the main memory level performance isolation.

#### 2.3.3 Performance Isolation on Integrated GPUs

Integrated GPU based platforms have recently gained much attention in the real-time systems community. In [66, 67], the authors investigate the suitability of NVIDIA's Tegra X1 platform for use in safety critical real-time systems. With careful reverse engineering, they have identified undisclosed scheduling policies that determine how concurrent GPU kernels are scheduled on the platform. In SiGAMMA [56], the authors present a novel mechanism to preempt the GPU kernel using a high-priority spinning GPU kernel to protect critical real-time CPU applications. Their work is orthogonal to ours (in Chapter 3) as it solves the problem of protecting CPU tasks from GPU tasks while our work solves the problem of protecting GPU tasks from CPU tasks.

More recently, GPUGuard [68] and HePREM [69] have been presented to provide a mechanism for deterministically arbitrating memory access requests between CPU cores and GPU in heterogeneous platforms containing integrated GPUs. They extend the PREM execution model [70], in which a (CPU) task is assumed to have distinct computation and memory phases, to model GPU tasks. The fundamental approach, in these works, to provide deterministic memory access to realtime GPU kernels, is to ensure that only a single PREM memory phase is in execution at any given time. Although this approach can provide strong isolation guarantees, the drawback is that it may require significant restructuring of application source code to be compatible with the PREM model.

## 2.4 Summary

In addition to the most widely studied sources of interference in real-time scheduling literature and presented in this chapter, there can be other hardware structures which can cause runtime coupling among simultaneously executing tasks in a shared-memory based multicore platform such as the translation look-aside buffer (TLB) [71], the main memory controller, the hardware prefetchers etc. Unfortunately, there is no comprehensive list of all the hardware resources that can potentially become sources of shared resource interference in modern COTS multicore platforms; due to the proprietary and often closed-source nature of the underlying hardware architecture. This means that even in a meticulously designed use-case where all the known sources of hardware level shared resource interference are fully partitioned—a requirement that is almost impossible to meet due to the aforementioned challenges—all the possible co-schedules of hard real-time tasks have to be thoroughly investigated; to make sure that a previously unknown hardware resource suddenly does not become a bottleneck in a particular situation.

Unfortunately, in any multicore scheduling policy presented in real-time literature so far and available in a commodity operating system, there are numerous ways in which real-time tasks can potentially get co-scheduled. Hence even after rigorously testing a multicore system scheduled under an optimal multicore scheduling policy, a system designer can not be sure that the timing guarantees will be met 100% of the time in the actual deployment of the system. This fact makes it imperative to turn off all but one cores in a multicore system deployed in an extremely safety critical use-case (e.g., avionics); to meet with safety certification guidelines [5] which makes it all but futile to use a multicore platform in the first place; a phenomenon that has been termed as the *one-out-of-m* [72] core problem in existing real-time literature. This realization has motivated us to design a novel *interference-aware* scheduling policy for hard real-time systems that can guarantee determinism—even at the potential cost of a possible CPU utilization loss—in the presence of

shared hardware resource interference on COTS multicore platforms which will be discussed in the subsequent chapters of this dissertation.

# Chapter 3

# **Real-Time Execution on Integrated CPU-GPU SoC Platforms**<sup>1</sup>

Heterogeneous SoC based multicore platforms, containing an integrated GPU in addition to the multicore CPUs, have become the go-to choice for running high performance embedded work-loads these days. In this chapter, the challenges inherent in deterministically using these SoCs for realizing real-time systems are discussed in detail. A restrictive scheduling and software level throttling framework, called BWLOCK++, is described which can guarantee deterministic execution on the integrated GPU in a heterogeneous SoC. The implementation of the framework, on top of the commodity Linux kernel, is explained and its evaluation results are elucidated on NVIDIA's Jetson TX2 platform which is an exemplar of heterogeneous embedded computing platforms.

## 3.1 Introduction

As mentioned in the Chapter 1, heterogeneous computing platforms contain one or more accelera-

tors in addition to the CPU; to speed up the processing of specialized workloads. A characteristic

The following work was inspired by the framework presented in this chapter: [74] Homa Aghilinasab, **Waqar Ali**, Heechul Yun, Rodolfo Pellizzoni (2020). Dynamic Memory Bandwidth Allocation for Real-Time GPU-Based SoC Platforms. In *Proceedings of the ACM/IEEE International Conference on Embedded Software (EMSOFT)*, pages 3348–3360

<sup>&</sup>lt;sup>1</sup>The following publication inspired the performance isolation technique presented in this chapter: [60] Heechul Yun, **Waqar Ali**, Santosh Gondi and Siddhartha Biswas (2017). BWLOCK: A Dynamic Memory Access Control Framework for Soft Real-Time Applications on Multicore Platforms. *IEEE Transactions on Computers* (*TC*), Vol: 66, Issue: 7, pages 1247–1252

Contents of this chapter have previously appeared in the following publications: [73] **Waqar Ali** and Heechul Yun (2017). Work-In-Progress: Protecting Real-Time GPU Applications on Integrated CPU-GPU SoC Platforms. *Proceedings of the IEEE International Conference on Real-Time and Embedded Technology and Applications Symposium Work-In-Progress (RTAS-WIP)*

<sup>[8]</sup> **Waqar Ali** and Heechul Yun (2018). Protecting Real-Time GPU Kernels on Integrated CPU-GPU SoC Platforms. In *Proceedings of the 30th Euromicro Conference on Real-Time Systems (ECRTS)*, pages 19:1–19:22

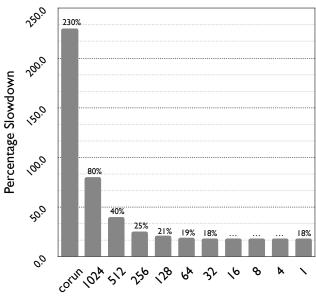

Figure 3.1: Performance of histo benchmark on NVIDIA Jetson TX2 with CPU corunners

of many such workloads—e.g., robotics and artificial intelligence—is their data-parallel nature and it has been shown [66] that graphical processing units (GPUs) are tremendously efficient in processing this type of workloads. Consequently, a number of heterogeneous embedded computing platforms (e.g., NVIDIA's Jetson [75] series) these days integrate a GPU alongside the multicore CPU cluster to accelerate the processing of data-parallel applications. The integration of CPU and GPU into a single SoC with a certain level of resource sharing in the memory hierarchy is attractive for the target embedded use-cases where size, weight, power (SWaP) and cost is at a premium. However, this also makes it more challenging to guarantee deterministic execution on heterogeneous computing platforms which is a must for safety critical real-time systems.

The challenge in deterministically using heterogeneous SoCs for real-time applications arises due to contention in the shared hardware resources (e.g., memory bandwidth) which can significantly alter the applications' timing characteristics. On an integrated CPU-GPU platform, such as NVIDIA Jetson TX2, the CPU cores and the GPU typically share a single main memory subsystem. This allows memory intensive batch jobs running on the CPU cores to significantly interfere with the execution of critical real-time GPU tasks (e.g., vision based navigation and obstacle detection) running in parallel due to memory bandwidth contention. To illustrate the significance of the problem stated above, we evaluate the effect of co-scheduling memory bandwidth intensive synthetic CPU benchmarks on the performance of a GPU benchmark *histo* from the parboil benchmark suite [76] on the NVIDIA Jetson TX2 platform (See Table 3.3 in Section 3.5 for the detailed time breakdown of *histo*.)

We first run the benchmark alone and record the solo execution statistics. We then repeat the experiment with an increasing number of interfering memory intensive benchmarks on the idle CPU cores to observe their impact on the performance of the *histo* benchmark. As can be seen in the Figure 3.1, co-scheduling the memory intensive tasks on the idle CPU cores significantly increase the execution time of the GPU benchmark—an up-to  $3.3 \times$  increase—despite the fact that the benchmark has exclusive access to the GPU. The main cause of the problem is that, in the Jetson TX2 platform, both CPU and GPU share the main memory and its limited memory bandwidth becomes a bottleneck. As a result, even though the platform offers plenty of raw performance, no real-time execution guarantees can be provided if the system is left on its own.

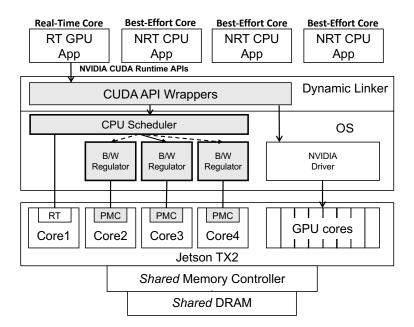

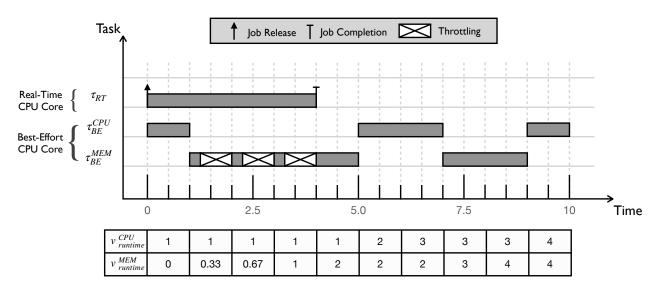

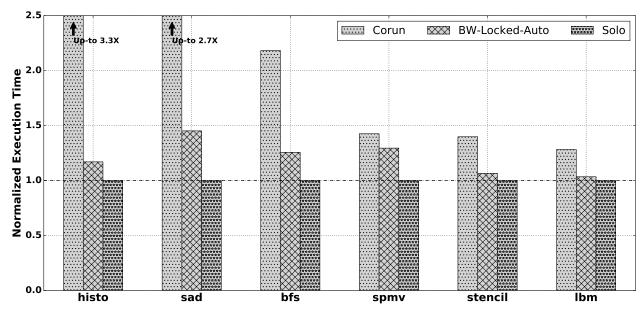

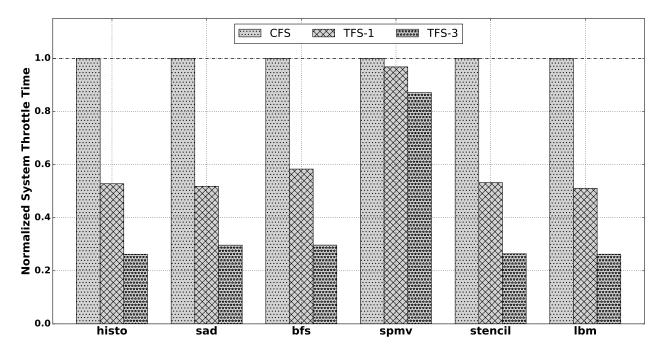

Our solution to the problem just described is a software framework called BWLOCK++ which is designed to mitigate the memory bandwidth contention problem in heterogeneous system architecture based embedded computing platforms. More specifically, we focus on protecting real-time GPU tasks from the interference of non-critical but memory intensive CPU tasks. BWLOCK++ dynamically instruments GPU tasks at run-time and inserts a *memory bandwidth lock* while critical GPU kernels are being executed on the GPU. When the bandwidth lock is being held by the GPU, the OS throttles the maximum memory bandwidth usage of the CPU cores to a certain threshold value to protect the GPU kernels. The threshold value is determined on a per GPU task basis and may vary depending on the GPU task's sensitivity to memory bandwidth contention. Throttling CPU cores inevitably negatively affects the CPU throughput. To minimize the throughput impact, we propose a throttling-aware CPU scheduling algorithm, which we call Throttle Fair Scheduler (TFS). TFS favors CPU intensive tasks over memory intensive ones while the GPU is busy executing critical tasks in order to minimize CPU throttling. Our evaluation shows that BWLOCK++ can provide good performance isolation for bandwidth intensive GPU tasks in the presence of memory

intensive CPU tasks. Furthermore, the TFS scheduling algorithm reduces the CPU throughput loss by up to 75%. We further show how BLWOCK++ can be incorporated in existing CPU focused response time analysis frameworks to analyze schedulability of real-time tasksets, utilizing both CPU and GPU. Finally, we discuss the limitations of our approach, its existing as well as possible extensions and how it can incorporate heterogeneous SoCs containing accelerators other than the integrated GPU.

### **3.2** System Model

Although the design philosophy of BWLOCK++ is applicable to any heterogeneous computing platform that contains a single on-chip accelerator; in order to have a concrete discussion about the design and implementation of the framework in this chapter, we primarily limit our discussion to heterogeneous SoCs containing an integrated GPU as an accelerator. Hence we assume an integrated CPU-GPU architecture based platform, which is composed of multiple CPU cores and a single GPU that share the same main memory subsystem. We consider independent periodic real-time tasks with implicit deadlines and best-effort tasks with no real-time constraints.

## 3.2.1 Task Model

In our system, we assume that each real-time task is composed of at least one CPU execution segment and zero or more GPU execution segments. We assume that *GPU execution is non-preemptible* and we do not allow concurrent execution of multiple GPU kernels from different tasks at the same time. Simultaneously co-scheduling multiple kernels is called GPU co-scheduling, which has been avoided in most prior real-time GPU management approaches [77, 78, 79] as well due to unpredictable timing. According to [66], preventing GPU co-scheduling does not necessarily hurt—if not improve—performance because concurrent GPU kernels from different tasks are executed in a time-multiplexed manner rather than being executed in parallel.<sup>2</sup>

<sup>&</sup>lt;sup>2</sup>Another recent study [80] finds that GPU kernels can only be executed in parallel if they are submitted from a single address space. In this work, we assume that a task has its own address space, whose GPU kernels are thus

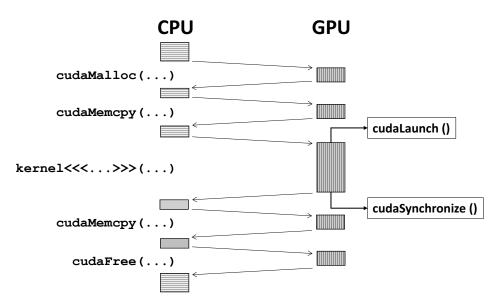

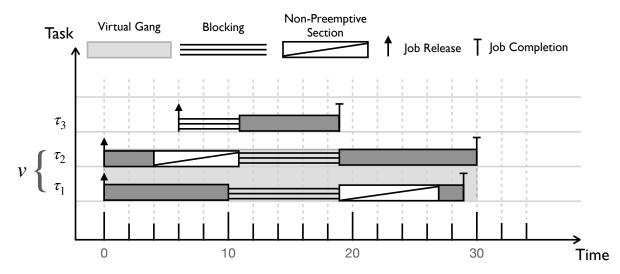

Executing GPU kernels typically requires copying considerable amount of data between the CPU and the GPU. In particular, synchronous copy directly contributes to the task's execution time, while asynchronous copy can overlap with GPU kernel execution. Therefore, we model synchronous copy separately. Lastly, we assume that a task is single-threaded with respect to the CPU. With these assumptions, we can model a real-time task as follows: