**Electronic Theses and Dissertations**

Electronic Theses and Dissertations from 2009

2021

# High-power medium-voltage motor drive: converter topology, modulation, and control

Le, Hoang

https://knowledgecommons.lakeheadu.ca/handle/2453/4904 Downloaded from Lakehead University, KnowledgeCommons

# HIGH–POWER MEDIUM–VOLTAGE MOTOR DRIVE: CONVERTER TOPOLOGY, MODULATION, AND CONTROL

By

### Hoang Le

B. Eng., Danang University of Science and Technology, Vietnam, 2018

A thesis presented to Lakehead University in partial fulfillment of the requirements for the degree of Master of Science in the program of Electrical and Computer Engineering

Thunder Bay, Ontario, Canada, 2021

©Hoang Le, 2021

## AUTHOR'S DECLARATION

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners.

I authorize Lakehead University to lend this thesis to other institutions or individuals for the purpose of scholarly research.

I further authorize Lakehead University to reproduce this thesis by photocopying or by other means, in total or in part, at the request of other institutions or individuals for the purpose of scholarly research.

I understand that my thesis may be electronically available to the public.

# HIGH–POWER MEDIUM–VOLTAGE MOTOR DRIVE: CONVERTER TOPOLOGY, MODULATION, AND CONTROL

Hoang Le Master of Science Electrical and Computer Engineering Lakehead University, Thunder Bay, 2021

### ABSTRACT

THE output power quality, device voltage sharing, power converter flying capacitor voltage ripple and motor torque ripple at low-frequency/ speed operation are the major issues in high-power medium-voltage (MV) motor drives. In this thesis, a new four-level multilevel converter (4L-MLC) is proposed for MV drive applications. The proposed converter does not require series connection of devices, thereby the voltage sharing problems will be eliminated. Also, the new MLC does not require any isolated direct current (DC) sources and eliminates the need of complex phase-shifting transformer. Furthermore, the proposed MLC is also suitable for back-to-back operation due to the presence of a common DC-link.

In addition, a simple voltage balancing approach with reduced complex-

ity is proposed to regulate the flying capacitors voltage in the proposed MLC. The proposed approach eliminates the unwanted device switchings, thereby the device switching frequency is limited to the carrier frequency only. Also, a generalized pulse width modulator is developed to integrate the proposed voltage balancing approach with different multi-carrier pulse width modulation schemes (PWM) to control the MLC. The performance of the proposed voltage balancing approach is verified with phase-disposition PWM (PD-PWM) scheme.

The MLC flying capacitors will have very high voltage ripple under lowfrequency/speed operation. To minimize these ripples, a modified multicarrier PWM scheme is proposed. With this approach, the converter flying capacitors can handle a wide range of frequency/speed operation with a smaller capacitance value. Hence, the overall system cost and required space for installation will be low. The proposed converter and modified multicarrier PWM scheme are applied to variable-speed motor drive application. The field-oriented control (FOC) in synchronous reference frame is implemented to control the motor speed/torque and flux. Finally, the simulation studies are presented to validate the dynamic and steady-state performance of the proposed variable-speed MV drive.

### **Index Terms**

- Capacitor voltage balancing.

- Capacitor voltage ripple.

- Field oriented control.

- Multilevel converters.

- Motor drive system.

- Pulse width modulation schemes.

- Reference frame theory.

- Total harmonic distortion.

### ACKNOWLEDGEMENTS

First and foremost, I would like to express a deep sense of gratitude and whole-hearted thanks to my supervisor, Dr. Apparao Dekka for his invaluable guidance, unwavering support, constant encouragement, and consistent kindness throughout the course of this work. His enthusiasm, vision, and profound technical insight have been the greatest source and motivation to make possible the accomplishment herein. It has been a genuine privilege to have worked with him, and I am very grateful that I have pursued my Master's studies under his excellent supervision.

I am highly obliged to my parents for their incessant love and sacrifice all throughout my life. Their unconditional assistance and lucid guidance can not be depicted by words, particularly in my periods of hardships and difficulties. Special thanks to my brother Thanh Le who helped me in tough times and provided me with encouraging words to achieve my goals. Without their help, the completion of my studies may not have been possible.

Last but not least, financial support from Dr. Apparao Dekka and Lakehead University is immensely acknowledged.

Thunder Bay, Ontario, Canada December, 2021.

# TABLE OF CONTENTS

|                | ABS                | STRAC  | Т                            | iii |

|----------------|--------------------|--------|------------------------------|-----|

|                | ACI                | KNOW   | LEDGEMENT                    | v   |

|                | LIS                | T OF F | IGURES                       | xi  |

| LIST OF TABLES |                    |        | ABLES                        | xv  |

|                | LIST OF ACRONYMS x |        |                              | vii |

|                | LIS                | Γ OF S | YMBOLS                       | xix |

| 1              | OV                 | ERVIE  | W OF MEDIUM-VOLTAGE DRIVES   | 1   |

|                | 1.1                | Mediu  | ım-Voltage Drive Structure   | 3   |

|                | 1.2                | Requi  | rements of MV Drive          | 4   |

|                |                    | 1.2.1  | Line-Side Requirements       | 4   |

|                |                    | 1.2.2  | Motor-Side Requirements      | 5   |

|                |                    | 1.2.3  | Switching Device Constraints | 6   |

|                |                    | 1.2.4  | Drive System Requirements    | 7   |

|                | 1.3                | Power  | Converters for MV Drive      | 8   |

|   |                                | 1.3.1                                                                                                           | Diode Clamped Converter                                                                                                                                                                                                                                                                                                                                                           | 10                                                                                                                                 |

|---|--------------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

|   |                                | 1.3.2                                                                                                           | Flying Capacitor Converter                                                                                                                                                                                                                                                                                                                                                        | 11                                                                                                                                 |

|   |                                | 1.3.3                                                                                                           | Nested Neutral-Point Clamped Converter                                                                                                                                                                                                                                                                                                                                            | 13                                                                                                                                 |

|   |                                | 1.3.4                                                                                                           | Hybrid Active Neutral-Point Clamped Converter                                                                                                                                                                                                                                                                                                                                     | 14                                                                                                                                 |

|   |                                | 1.3.5                                                                                                           | Hybrid Clamped Converter                                                                                                                                                                                                                                                                                                                                                          | 15                                                                                                                                 |

|   |                                | 1.3.6                                                                                                           | Nested T-type Converter                                                                                                                                                                                                                                                                                                                                                           | 16                                                                                                                                 |

|   |                                | 1.3.7                                                                                                           | Modular Multilevel Converter                                                                                                                                                                                                                                                                                                                                                      | 17                                                                                                                                 |

|   | 1.4                            | Pulse                                                                                                           | Width Modulation Schemes                                                                                                                                                                                                                                                                                                                                                          | 18                                                                                                                                 |

|   |                                | 1.4.1                                                                                                           | Multi-carrier PWM Schemes                                                                                                                                                                                                                                                                                                                                                         | 19                                                                                                                                 |

|   |                                | 1.4.2                                                                                                           | Space Vector Modulation Schemes                                                                                                                                                                                                                                                                                                                                                   | 20                                                                                                                                 |

|   | 1.5                            | Thesis                                                                                                          | Objectives                                                                                                                                                                                                                                                                                                                                                                        | 21                                                                                                                                 |

|   |                                |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                   | 24                                                                                                                                 |

|   | 1.6                            | Thesis                                                                                                          | Outline                                                                                                                                                                                                                                                                                                                                                                           | <b>4</b> 4                                                                                                                         |

| - |                                |                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                   | 24                                                                                                                                 |

| 2 | VOI                            | LTAGE                                                                                                           | BALANCING AND MODULATION OF FOUR-LEVEL                                                                                                                                                                                                                                                                                                                                            | 24<br>26                                                                                                                           |

| 2 | VOI                            | LTAGE<br>LTILEV                                                                                                 | BALANCING AND MODULATION OF FOUR-LEVEL                                                                                                                                                                                                                                                                                                                                            | 26                                                                                                                                 |

| 2 | VOI<br>MU                      | LTAGE<br>LTILEV                                                                                                 | BALANCING AND MODULATION OF FOUR-LEVEL<br>EVEL CONVERTER<br>Four-Level Multilevel Converter                                                                                                                                                                                                                                                                                       | <b>26</b><br>27                                                                                                                    |

| 2 | VOI<br>MU                      | LTAGE<br>LTILEV<br>New F                                                                                        | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration                                                                                                                                                                                                                                                             | <b>26</b><br>27<br>28                                                                                                              |

| 2 | VOI<br>MU                      | LTAGE<br>LTILEV<br>New F<br>2.1.1                                                                               | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States                                                                                                                                                                                                                           | <b>26</b><br>27<br>28<br>29                                                                                                        |

| 2 | VOI<br>MU                      | LTAGE<br>LTILEN<br>New F<br>2.1.1<br>2.1.2                                                                      | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States<br>Analysis of Flying Capacitors Voltage                                                                                                                                                                                  | <b>26</b><br>27<br>28<br>29<br>30                                                                                                  |

| 2 | <b>VOI</b><br><b>MU</b><br>2.1 | <b>LTAGE</b><br><b>LTILEV</b><br>New F<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4                                      | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States<br>Analysis of Flying Capacitors Voltage<br>Comparison of 4L-MLCs                                                                                                                                                         | <b>26</b><br>27<br>28<br>29<br>30<br>32                                                                                            |

| 2 | VOI<br>MU                      | <b>LTAGE</b><br><b>LTILEV</b><br>New F<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>Level-                            | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States<br>Analysis of Flying Capacitors Voltage<br>Comparison of 4L-MLCs<br>Shifted Carrier Pulse Width Modulation Scheme                                                                                                        | 26<br>27<br>28<br>30<br>32<br>33                                                                                                   |

| 2 | <b>VOI</b><br><b>MU</b><br>2.1 | <b>LTAGE</b><br><b>LTILEV</b><br>New F<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>Level-<br>2.2.1                   | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States<br>Analysis of Flying Capacitors Voltage<br>Comparison of 4L–MLCs<br>Shifted Carrier Pulse Width Modulation Scheme<br>Generation of Modulation Signals                                                                    | 26<br>27<br>28<br>29<br>30<br>32<br>33<br>33<br>34                                                                                 |

| 2 | <b>VOI</b><br><b>MU</b><br>2.1 | <b>LTAGE</b><br><b>ITILEV</b><br>New F<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>Level-<br>2.2.1<br>2.2.2          | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States<br>Operation and Switching States<br>Analysis of Flying Capacitors Voltage<br>Comparison of 4L–MLCs<br>Shifted Carrier Pulse Width Modulation Scheme<br>Generation of Modulation Signals<br>Generation of Carrier Signals | <ul> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> </ul>             |

| 2 | <b>VOI</b><br><b>MU</b><br>2.1 | <b>LTAGE</b><br><b>ITILEV</b><br>New F<br>2.1.1<br>2.1.2<br>2.1.3<br>2.1.4<br>Level-<br>2.2.1<br>2.2.2<br>2.2.3 | BALANCING AND MODULATION OF FOUR-LEVEL<br>VEL CONVERTER<br>Four-Level Multilevel Converter<br>Converter Configuration<br>Operation and Switching States<br>Analysis of Flying Capacitors Voltage<br>Comparison of 4L–MLCs<br>Shifted Carrier Pulse Width Modulation Scheme<br>Generation of Modulation Signals                                                                    | <ul> <li>26</li> <li>27</li> <li>28</li> <li>29</li> <li>30</li> <li>32</li> <li>33</li> <li>34</li> <li>35</li> <li>36</li> </ul> |

|   |              | 2.3.1  | Implementation of Voltage Balancing Method       | 38 |

|---|--------------|--------|--------------------------------------------------|----|

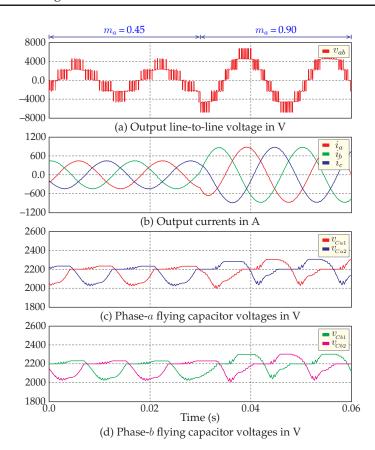

|   |              | 2.3.2  | Performance with Step Change in Modulation Index | 40 |

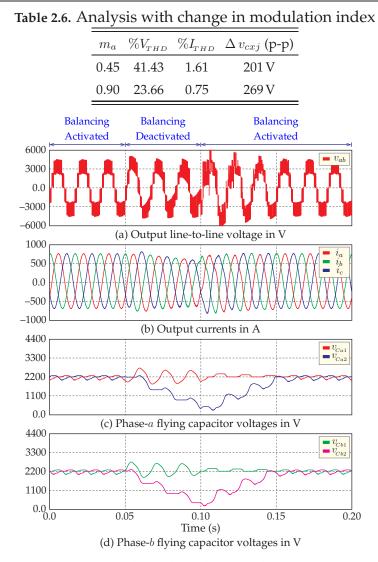

|   |              | 2.3.3  | Performance with and without Voltage Balancing   | 42 |

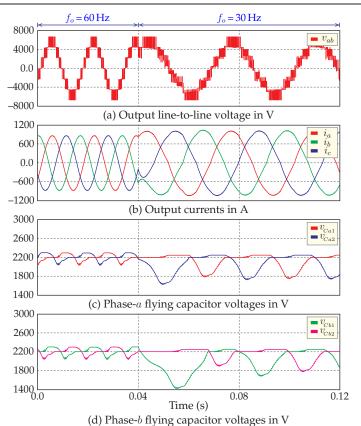

|   |              | 2.3.4  | Performance with Step Change in Output Frequency | 43 |

|   |              | 2.3.5  | Performance at Different Load Power Factors      | 45 |

|   | 2.4          | Modif  | ied Carrier PWM Scheme                           | 47 |

|   |              | 2.4.1  | Performance with Change in Modulation Index      | 48 |

|   |              | 2.4.2  | Performance with Change in Output Frequency      | 49 |

|   | 2.5          | Summ   | nary                                             | 51 |

| 3 | <b>A N</b> T | EWEO   | UR-LEVEL MULTILEVEL CONVERTER FED MEDIUM-        |    |

| 3 |              |        | DRIVE                                            | 52 |

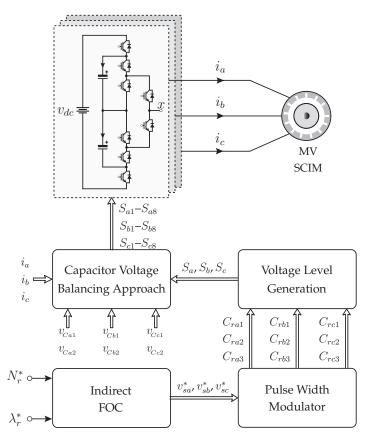

|   | 3.1          | Funda  | amentals of 4L-MLC fed Motor Drive               | 53 |

|   |              | 3.1.1  | System Configuration                             | 53 |

|   |              | 3.1.2  | Drive Control Schemes                            | 54 |

|   | 3.2          | Indire | ct Field Oriented Control                        | 55 |

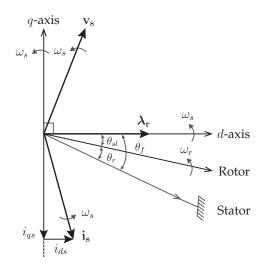

|   |              | 3.2.1  | Principle of Field Orientation                   | 55 |

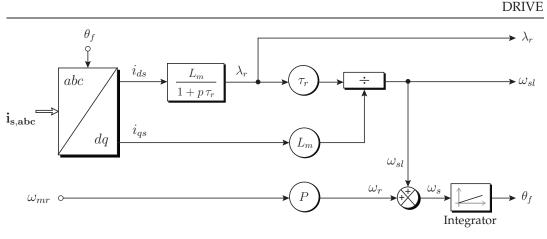

|   |              | 3.2.2  | Estimation of Rotor Flux Vector                  | 57 |

|   |              | 3.2.3  | Block Diagram of IFOC Scheme                     | 60 |

|   | 3.3          | Simula | ation Results                                    | 61 |

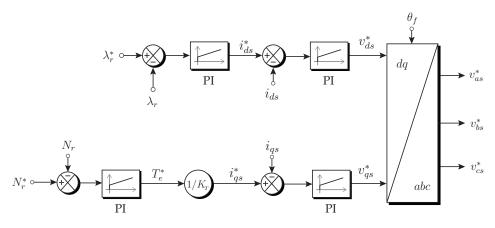

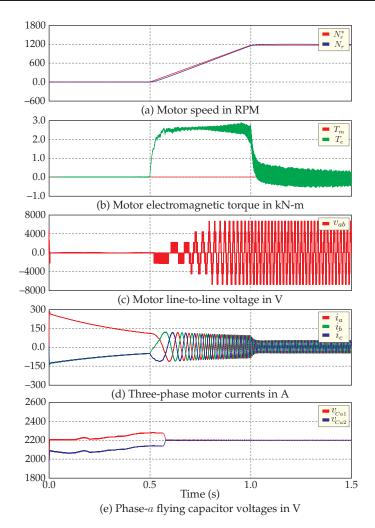

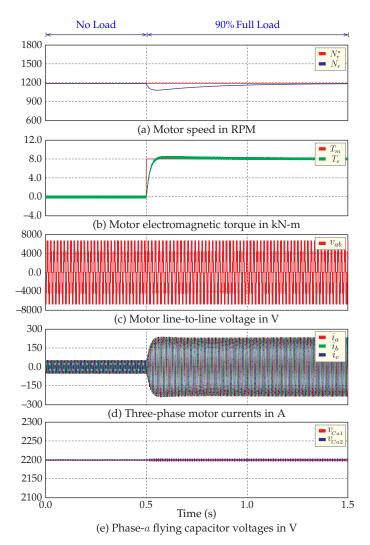

|   |              | 3.3.1  | Start-up Operation                               | 62 |

|   |              | 3.3.2  | Transient Operation                              | 62 |

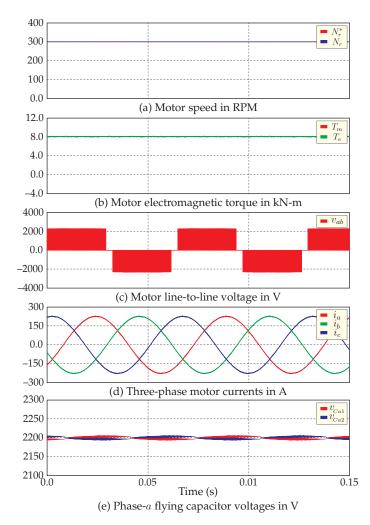

|   |              | 3.3.3  | Low-Speed Operation                              | 65 |

|   | 3.4          | Summ   | nary                                             | 66 |

| Л | CO           | NCLUS  |                                                  | 67 |

| 4 | CO           | NCLUS  |                                                  | 67 |

| BIBI | LIOGRAPHY                     | 70 |

|------|-------------------------------|----|

| 4.2  | Future Work                   | 69 |

| 4.1  | Contributions and Conclusions | 67 |

# LIST OF FIGURES

| 1.1  | Applications of MV drives                                        | 1   |

|------|------------------------------------------------------------------|-----|

| 1.2  | Structure of MV drive.                                           | 3   |

| 1.3  | Common mode voltage in MV drive                                  | 5   |

| 1.4  | Classification of voltage source power converters for MV drives. | 7   |

| 1.5  | Two-level converter fed MV drive.                                | 9   |

| 1.6  | Four-level DCC fed MV drive.                                     | 10  |

| 1.7  | Four-level FCC fed MV drive                                      | 11  |

| 1.8  | Four-level SFCC fed MV drive.                                    | 12  |

| 1.9  | Four-level NNPC converter fed MV drive                           | 13  |

| 1.10 | Four-level HANPC converter fed MV drive                          | 14  |

| 1.11 | Four-level HCC fed MV drive.                                     | 15  |

| 1.12 | Four-level nested T-type converter fed MV drive                  | 16  |

| 1.13 | Four-level MMC fed MV drive                                      | 18  |

| 1.14 | Summary of thesis directions/objectives                          | 21  |

| 1.15 | Summary of the thesis                                            | 24  |

| 0.1  |                                                                  | ~ - |

| 2.1  | Proposed 4L-MLC with a passive load                              | 27  |

| 2.2  | Basic operation of 4L-MLC.                                       | 30  |

| 2.3  | Impact of states <b>A</b> and <b>D</b> , and phase current on flying capaci-<br>tor voltages.          | 31 |

|------|--------------------------------------------------------------------------------------------------------|----|

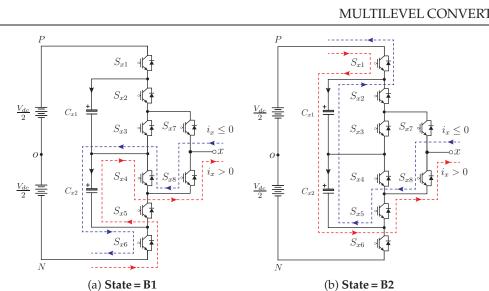

| 2.4  | Impact of states <b>B1</b> and <b>B2</b> , and phase current on flying capac-<br>itor voltages.        | 32 |

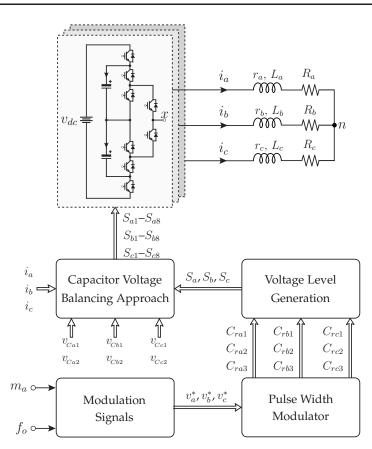

| 2.5  | Control block diagram of the proposed 4L-MLC                                                           | 35 |

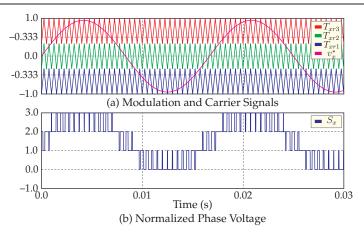

| 2.6  | Representation of modulation and carrier signals in PD-PWM                                             | 36 |

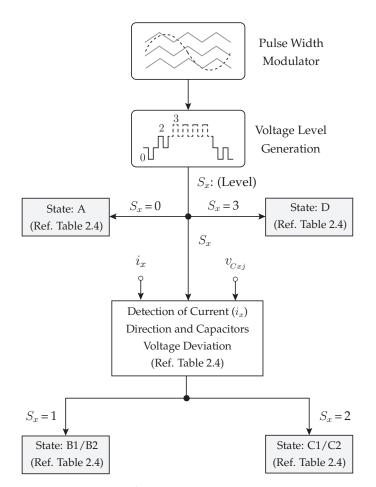

| 2.7  | Implementation of the proposed voltage balancing approach                                              | 37 |

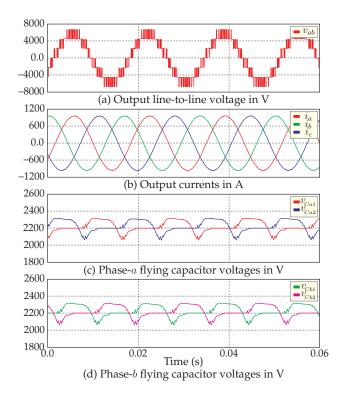

| 2.8  | Step response with change in modulation index ( $f_o = 60$ Hz and PF = 0.80 (lag)).                    | 41 |

| 2.9  | Step response with and without balancing approach ( $m_a = 0.75$ , $f_o = 60$ Hz and PF = 0.80 (lag)). | 42 |

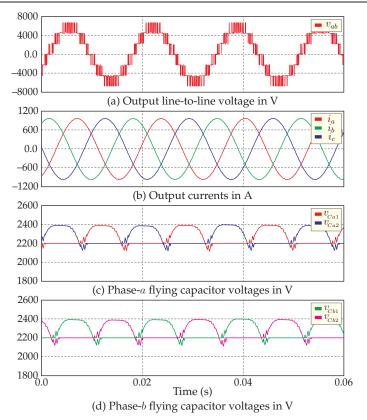

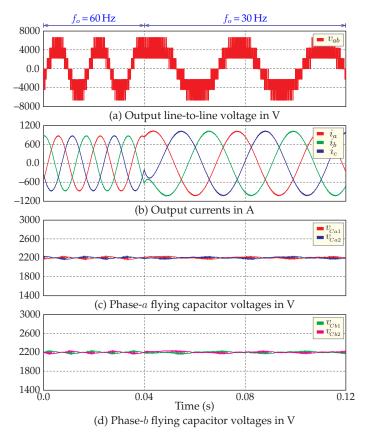

| 2.10 | Step response with change in output frequency ( $m_a = 0.9$ and PF = 0.80 (lag)).                      | 44 |

| 2.11 | Steady-state response at $m_a = 0.99$ , $f_o = 60$ Hz, and PF = 0.8 (lag)                              | 45 |

| 2.12 | Steady-state response at $m_a = 0.99$ , $f_o = 60$ Hz, and PF = 0.45 (lag).                            | 46 |

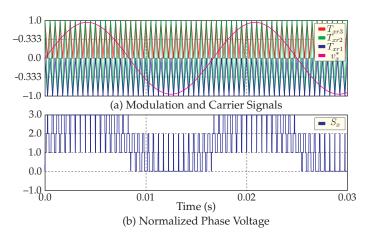

| 2.13 | Representation of modulation and carrier signals in modified carrier PWM                               | 47 |

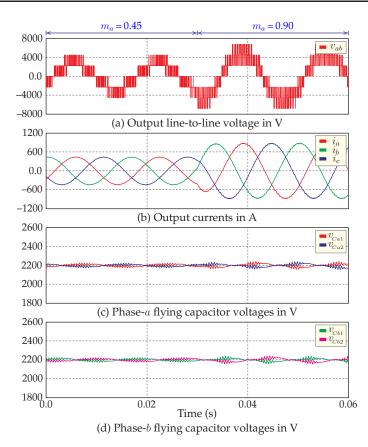

| 2.14 | Step response with change in modulation index ( $f_o = 60$ Hz and PF = 0.80 (lag)).                    | 49 |

| 2.15 | Step response with change in fundamental frequency ( $m_a = 0.9$ and PF = 0.80 (lag))                  | 50 |

| 3.1  | Proposed 4L-MLC fed MV drive.                                                                          | 53 |

| 3.2  | Control block diagram of the proposed 4L-MLC fed MV drive                                              | 54 |

| 3.3  | Space phasor diagram of field orientation.                                                             | 56 |

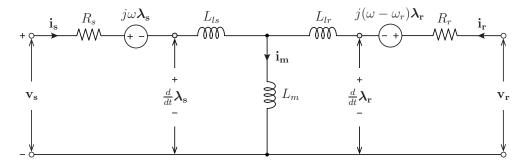

| 3.4  | Space vector model of induction motor in the arbitrary refer-<br>ence frame.                           | 57 |

| 3.5 | Estimation of rotor flux magnitude and position ( $\lambda_r$ and $\theta_f$ ) | 60 |

|-----|--------------------------------------------------------------------------------|----|

| 3.6 | Control block diagram of IFOC.                                                 | 60 |

| 3.7 | Startup performance of the proposed MV drive                                   | 63 |

| 3.8 | Transient performance of the proposed MV drive                                 | 64 |

| 3.9 | Low-speed (25% of synchronous speed) operation of the pro-<br>posed MV drive   | 65 |

# LIST OF TABLES

| 2.1  | Switching states of a new 4L-MLC              | 28 |

|------|-----------------------------------------------|----|

| 2.2  | Flying capacitors voltage variation           | 31 |

| 2.3  | Comparison of four-level converters           | 33 |

| 2.4  | Selection of redundancy switching states      | 39 |

| 2.5  | Simulation system parameters                  | 39 |

| 2.6  | Analysis with change in modulation index      | 42 |

| 2.7  | Analysis with change in fundamental frequency | 44 |

| 2.8  | Analysis with change in load power factor     | 46 |

| 2.9  | Analysis with change in modulation index      | 48 |

| 2.10 | Analysis with change in output frequency      | 51 |

| 3.1  | Three-phase SCIM Specifications               | 61 |

# LIST OF ACRONYMS

| 2L    | Two-level                              |

|-------|----------------------------------------|

| 3L    | Three-level                            |

| 4L    | Four-level                             |

| 5L    | Five-level                             |

| AC    | Alternating current                    |

| ANPC  | Active neutral point clamped           |

| APOD  | Alternate phase-opposition disposition |

| CHB   | Cascaded H-bridge                      |

| CMV   | Common-mode voltage                    |

| CNPC  | Cascaded neutral-point clamped         |

| CSC   | Current source converter               |

| CSI   | Current source inverter                |

| DC    | Direct current                         |

| DCC   | Diode-clamped converter                |

| DFOC  | Direct field oriented control          |

| DTC   | Direct torque control                  |

| FCC   | Flying capacitor converter             |

| FOC   | Field oriented control                 |

| GTO   | Gate turn-off thyristor                |

| HANPC | Hybrid active neutral point clamped    |

| HCC   | Hybrid clamped converter               |

| HP    | Horse power                            |

|       |                                        |

| HV      | High voltage                                 |

|---------|----------------------------------------------|

| HVDC    | High-voltage direct current                  |

| IFOC    | Indirect field oriented control              |

| IGBT    | Insulated-gate bipolar transistor            |

| IGCT    | Integrated gate-commutated thyristor         |

| LSC-PWM | Level-shifted carrier pulse width modulation |

| MLC     | Multilevel converter                         |

| MMC     | Modular multilevel converter                 |

| MV      | Medium voltage                               |

| NNPC    | Nested neutral point clamped                 |

| NTC     | Nested T-type converter                      |

| PD      | Phase-disposition                            |

| PF      | Power factor                                 |

| PI      | Proportional-integrator                      |

| POD     | Phase-opposition disposition                 |

| PSC-PWM | Phase-shifted carrier pulse width modulation |

| PWM     | Pulse width modulation                       |

| RMS     | Root mean square                             |

| RPM     | Revolutions per minute                       |

| SCIM    | Squirrel cage induction motor                |

| SFCC    | Single flying capacitor converter            |

| SHE     | Selective harmonic elimination               |

| SM      | Submodule                                    |

| SVM     | Space vector modulation                      |

| THD     | Total harmonic distortion                    |

| VSC     | Voltage source converter                     |

| VSI     | Voltage source inverter                      |

|         |                                              |

# LIST OF SYMBOLS

### Superscript

^ Peak quantity

\* Reference quantity

### Subscript

| j                   | Capacitor index number  |

|---------------------|-------------------------|

| $x \in \{a, b, c\}$ | AC output quantities    |

| r                   | Motor rotor quantities  |

| s                   | Motor stator quantities |

| d                   | <i>d</i> -axis quantity |

| q                   | <i>q</i> -axis quantity |

### System Quantities

| Amplitude modulation index       |

|----------------------------------|

| Number of voltage levels         |

| Fundamental frequency (Hz)       |

| Phase angle of phase- $x$ (rad)  |

| Rotor flux vector position (rad) |

| Carrier comparison output        |

| Carrier frequency (Hz)           |

| Motor pole pairs                 |

|                                  |

#### **System Quantities**

- $\lambda_r$ Rotor flux linkage

- $T_e$ Motor electromagnetic torque (N-m)

- $T_m$  Motor load torque (N-m)

- Motor rotor speed (RPM)  $N_r$

- $\mathbf{S}_{\mathbf{x}}$ Phase-*x* state

- Rotating reference frame speed (rad/sec) ω

- Rotor angular speed (rad/sec)  $\omega_r$

- Stator angular speed (rad/sec)  $\omega_s$

- Motor slip-speed (rad/sec)  $\omega_{sl}$

#### **Voltage and Current Quantities**

| $V_{dc}$                                                    | DC-link voltage (V)                              |

|-------------------------------------------------------------|--------------------------------------------------|

| $v_{\!\scriptscriptstyle Cx1},v_{\!\scriptscriptstyle Cx2}$ | Flying capacitor voltages in phase- <i>x</i> (V) |

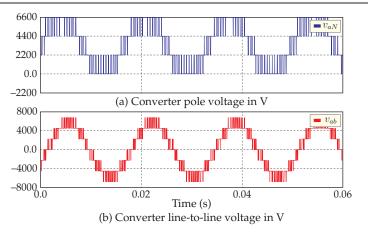

| $V_{xN}$                                                    | Pole voltage of phase- $x$ (V)                   |

| $v_{ab}, v_{bc}, v_{ca}$                                    | Three-phase line-to-line voltages (V)            |

| $v_{cmr}, v_{og}$                                           | Rectifier common-mode voltage (V)                |

| $v_{cmi}, v_{no}$                                           | Inverter common-mode voltage (V)                 |

| $v_{cmv}, v_{ng}$                                           | Common-mode voltage (V)                          |

| $v_{ds}, v_{qs}$                                            | Stator $dq$ -axis voltages (V)                   |

| $v_{sa}, v_{sb}, v_{sc}$                                    | Stator <i>abc</i> -axis voltages (V)             |

| $i_x$                                                       | AC output current of phase- $x$ (A)              |

| $i_{ds}$ , $i_{qs}$                                         | Stator $dq$ -axis currents (A)                   |

| $i_{dr}$ , $i_{qr}$                                         | Rotor $dq$ -axis currents (A)                    |

| $i_x$                                                       | AC output current of phase- $x$ (A)              |

| $i_{Cx1}, i_{Cx2}$                                          | Flying capacitor currents in phase- $x$ (A)      |

#### **Passive Elements**

| Passive Elements |                                                                 |

|------------------|-----------------------------------------------------------------|

| $L_x$            | Load Inductor of phase- $x$ (H)                                 |

| $r_x$            | Internal resistance of load inductor of phase- $x$ ( $\Omega$ ) |

| $R_x$            | Load resistor of phase- $x$ ( $\Omega$ )                        |

| $C_{dc}$         | DC-link capacitance (F)                                         |

| $C_{x1}, C_{x2}$ | Flying capacitor capacitance of phase- $x$ (F)                  |

# CHAPTER 1

### OVERVIEW OF MEDIUM-VOLTAGE DRIVES

HIGH -power converters and medium-voltage (MV) drives have enjoyed an increasing attention since the invention of high-voltage semiconductor devices such as gate turn-off thyristor (GTO), integrated gate-commutated thyristor (IGCT), and insulated gate bipolar transistors (IGBT) [1]. These switching devices are widely used in high-power electronic applications owing to their optimal characteristics, low power losses, ease of gate control, and snubber less operation [2].

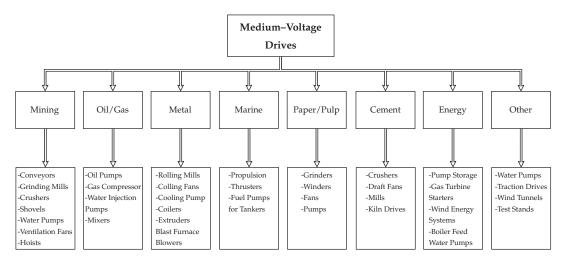

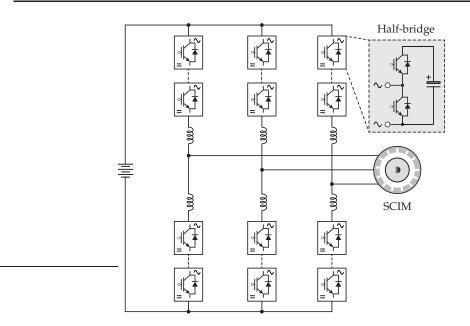

Figure 1.1. Applications of MV drives.

The MV drives have witnessed a great deal of development since 1980 in terms of power capacity and voltage rating, boosting their presence in almost all industrial sectors. MV drives are commercially available in single or parallel modules ranging from a power capacity of 0.4–40 MW at a voltage level of 2.3–13.8 kV. Nevertheless, the installed MV drives dominated the commercial applications with a power rating of 1–4 MW at a voltage level of 3.3–6.6 kV [3]. The MV drive applications cover a wide range of industry sectors such as mining, oil/gas, metal, paper/pulp, cement, power/energy, and other emerging areas as shown in Fig. 1.1. Around 85% of MV drives are used in pumps, fans, compressors, and conveyors as their technical requirements are relatively simple and can be achieved with standard MV drives [4].

The MV drives are available in both fixed and variable speed operations. With the advancement of high-power converters, the variable speed operation of MV drives is widely accepted in industry due to the increase in productivity together with significant saving of energy cost. However, the variable speed MV drives need a sophisticated and reliable power converters to handle MV operation, pulse width modulation (PWM) schemes to improve the output power quality and reduce the common-mode voltage stress, and high-performance closed-loop control methods [5].

In this thesis, a new multilevel converter (MLC) topology is proposed for high-power MV drive. The new topology eliminates the need of phaseshifting transformer and device voltage sharing problems, and reduces the control complexity. Several conventional and advanced PWM schemes which can improve power quality, reduce common-mode voltage stress, and minimize capacitor voltage ripple are developed and studied for new high-power MV drive. Also, a simple voltage balancing method is proposed to control the new MLC topology.

This chapter is organized as follows: the structure and technical challenges of MV drive are presented in Sections 1.1 and 1.2, respectively. In MV drive, the power converter plays a key role to attain various objectives along with power conversion process. The overview of power converters and PWM schemes for MV drive are presented in Sections 1.3 and 1.4, respectively. The thesis objectives are given in Section 1.5. In Section 1.6, the outline of thesis is presented.

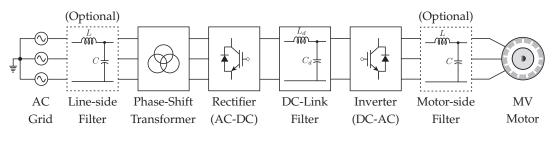

#### 1.1 Medium-Voltage Drive Structure

The medium-voltage (MV) drive system consists of AC-DC power conversion (rectification) and DC-AC power conversion (inversion) stages as shown in Fig. 1.2. The rectification stage includes an AC-grid, line-side filter, phaseshifting transformer, and AC-DC converter (rectifier). On the other hand, the inversion stage includes a DC-link filter, DC-AC converter (inverter), motorside filter, and MV motor [6]. The line-side and motor-side filters are optional, and their presence depends on the type of power converter employed and system harmonic requirements. The phase-shifting transformer with multiple secondary windings is employed, thereby the lower order harmonics such as 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup> will be cancelled to minimize the line-side harmonic distortion to meet the IEEE-519 harmonic standards and to block the drive common-mode current [7,8]. The rectifier converts utility AC-grid voltage to DC voltage with fixed or adjustable magnitude. The commonly used rectifier topologies are multipulse diode-bridge rectifiers, multipulse thyristor rectifiers, and PWM rectifiers.

Figure 1.2. Structure of MV drive.

The DC-link filter is formed with either capacitor or inductor as shown in Fig. 1.2. The capacitor provides a stiff DC voltage to the inverter and it is referred to as voltage source inverter (VSI), whereas the inductor provides a smooth DC current to the inverter and it is referred to as current source inverter (CSI). The VSI converts DC voltage to AC voltage with adjustable magnitude and frequency [9]. On the other hand, the CSI converts DC current to three-phase AC currents with adjustable magnitude and frequency [10]. The selection of inverter topology depends on the motor-side requirements, available switching devices, and type of control and PWM scheme employed.

#### 1.2 Requirements of MV Drive

The demand for variable speed MV drives is continuously growing in industry due to their efficiency and sustainability along with economical benefits. However, the design and control of MV drives are still a challenging task as they need to fulfil various requirements related to power quality and grid interaction of line-side converters, design and control of motor-side converters, switching device constraints, and drive system requirements [11].

#### 1.2.1 Line-Side Requirements

The current and voltage distortion, poor power factor, and LC resonance are the major issues on the line-side of the MV drive. Normally, the MV drives are connected to AC-grid through a line-side converter, which draws a distorted current and produces notches in voltage waveform. These waveforms cause false tripping of computer-controlled industrial processes, malfunction of control and protection circuits, heating of transformers, and equipment failure. Particularly, the false tripping of industrial process and protection circuits cause a longer downtime leading to a loss of production and revenue. Hence, the line-side converters are designed with LC filters or phase-shifting transformer to meet the harmonic standards such as IEC 1000-3-2 and IEEE-519, 2014 [7, 12].

Furthermore, the high power factor on the line-side is an important requirement in high-power MV drives as it represents the efficiency of energy utilization. The use of capacitor banks is a simple and cost-effective solution to improve the line-side power factor [13]. However, the capacitor banks form LC resonant circuit with line inductance of the system. Due to the low resistance of MV system, the lightly damped LC resonance cause oscillations leading to overheating and excessive noise when the drive is not running [14]. Therefore, the design and control of line-side converters are key aspect in MV drive to achieve an efficient and reliable operation [15].

#### **1.2.2 Motor-Side Requirements**

The higher dv/dt, common-mode voltage (CMV), motor derating, and LC resonance are the major issues on motor-side of the MV drives. The motor-side converters are switched at a faster rate leading to high dv/dt at the falling and rising edge of motor-side converter output voltage [16]. The high dv/dt can cause premature failure of the motor winding insulation due to partial discharges. It also induce rotor shaft voltage due to stray capacitance between stator and rotor, which produces a current flowing to the shaft bearing leading to their premature failure [17]. The high dv/dt cause a voltage doubling effect due to the wave reflections in long cables. This may increase the voltage stress on the motor.

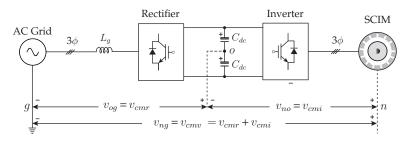

Figure 1.3. Common mode voltage in MV drive.

The switching action of line-side and motor-side converters generate CMV, which is normally a zero-sequence voltage superimposed with switching noise. If the CMV is not mitigated, it appears on the motor neutral with respect to the ground as shown in Fig. 1.3. The CMV increases the motor volt-

age stress leading to the premature failure of the motor winding system [18]. The replacement of a damaged MV motor is costly. Some of the CMV minimization methods are the use of isolation transformer and CMV filters, but they are costly and require extra space to install in the drives. On the other hand, the PWM schemes with flexible switching sequences are developed to minimize the CMV [19–21]. However, these methods are not effective and unable to mitigate it completely. Hence, the minimization of CMV is one of the research issues in MV drives.

In addition, the switching action of motor-side converters generate a large amount of harmonics in voltage and current waveforms. These harmonics cause power losses in the motor winding and magnetic core. As a consequence, the motor is derated and cannot operate at its full capacity. Thereby, the filters are installed at the motor terminals to reduce the dv/dt and harmonics [22]. However, the filters form LC resonant circuit with the motor inductances. Even though, the winding resistance provides damping, but this problem should be addressed at the design stage of the drive [23].

#### **1.2.3** Switching Device Constraints

The higher switching frequency of semiconductor devices in line-side and motor-side converters cause significant power losses in MV drive. These power losses increase the MV drive cooling requirements along with physical size, and manufacturing and operating cost. In addition, the higher switching frequency affects the device thermal resistance that may prevent efficient heat transfer from the device to its heatsink [24]. Hence, the switching frequency is limited to less than 1 kHz in MV drives. However, the low switching frequency operation leads to higher harmonic distortion in voltage and current waveforms [25].

Furthermore, the switching devices are often connected in series for MV operation. However, they may not share the total voltage equally due to different static and dynamic characteristics of devices and gate drivers [26, 27]. Hence, the voltage equalization circuits are needed to protect the switching

devices and enhance the system reliability.

#### **1.2.4** Drive System Requirements

The general requirements of MV drive are low manufacturing cost, high efficiency and reliability, small physical size, easy installation, fault protection, and minimum downtime for repairs [28]. In addition, the MV drive should meet various application requirements such as high dynamic response, regenerative braking capability, and four-quadrant operation [29].

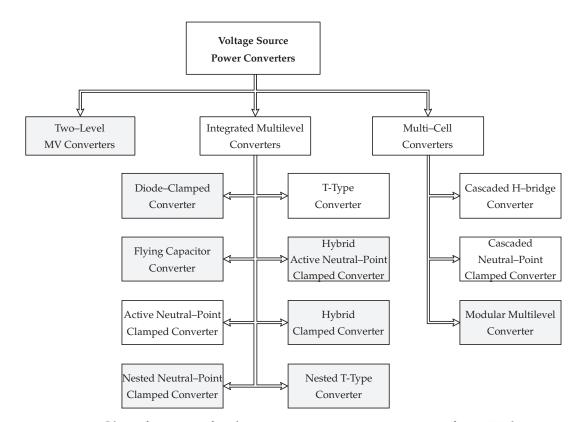

Figure 1.4. Classification of voltage source power converters for MV drives.

#### **1.3** Power Converters for MV Drive

The power converters play a key role in the development of high-performance MV drives. These converters are categorized into current source converters (CSCs) and voltage source converters (VSCs) depending on the DC-link filter. Among them, the VSC technology is highly matured and exhibited higher market penetration compared with CSC technology [30].

Some of the developments in VSC technology are shown in Fig. 1.4. The two-level (2L) converter is a standard VSC, and it is widely used for low-voltage (LV) and low-power applications. For high-power applications, the 2L-VSC requires either devices in parallel to increase the current carrying capacity at LV operation or devices in series to achieve MV operation at low current carrying capacity [31]. The latter approach is highly preferred due to the availability of semiconductor devices and the reduction of power losses as shown in Fig. 1.5. However, this approach does not reduce the dv/dt, CMV, and power quality on the motor-side. Furthermore, they need output LC filters to meet the motor-side requirements, but it causes LC resonance problem. Also, the voltage equalization circuits are needed to ensure the equal voltage sharing among the devices during blocking mode [32].

On the other hand, the power converters which use low-cost semiconductor devices; known as multilevel converters are developed for high-power applications. These converters effectively meet the MV drive requirements including low dv/dt and harmonic distortion, low common-mode voltage, high efficiency due to low switching losses, elimination of output filters and series connection of devices [33]. There are several developments in multilevel converter technology, and they are categorized into integrated and multi-cell converters depending on their structure. The integrated multilevel converters are available in three-level (3L) to five-level (5L) operation and can handle an operating voltage of 2.3–4.16 kV. These converters need either a significant amount of modifications or step-up transformer to increase their operating voltage, and it is not cost-effective. Also, they have a longer down-

Figure 1.5. Two-level converter fed MV drive.

time under faults leading to a loss of production and revenue [34]. Some of the integrated multilevel converters are diode-clamped converter (DCC), flying capacitor converter (FCC), active neutral-point clamped (ANPC) converter, nested neutral-point clamped (NNPC) converter, T-type converter, hybrid ANPC converter, hybrid clamped converter (HCC), and nested T-type converter [35].

The multi-cell converters have a modular structure and can reach an operating voltage up to 13.8 kV. Moreover, the multi-cell converter output voltage levels are easy to increase by connecting identical modules in series. Also, they can continuously operate with reduced capacity even under faults [9]. Some of the popular multi-cell converters are cascaded H-bridge (CHB) converter, cascaded neutral-point clamped (CNPC) converter, and modular multilevel converter (MMC) [36]. Among them, the CHB and CNPC converters are available in odd voltage level operation. These topologies require isolated DC sources, which are generated with the help of multiple secondary phase-shifting transformer and rectifier system. The transformer increases the physical size and cost of the system [37]. On the other hand, MMC can reach an operating voltage up to 400 kV without transformer, and it does not require isolated DC sources. Also, MMC is suitable for fault-tolerant operation, and reduce dv/dt and harmonic distortion without output filters [38]. However, it requires a large number of semiconductor devices and passive components.

This thesis mainly focused on the four-level (4L) operation of integrated and multi-cell converters, and their limitations and challenges for MV drive applications.

#### 1.3.1 Diode Clamped Converter

Diode clamped converter (DCC) is one of the most popular and established standard multilevel converters. It is commercially available in three-level with an operating voltage of 2.3–3.3 kV. For higher operating voltages, the DCC requires a higher number of output voltage levels to meet the motor-side requirements [39]. Fig. 1.6 shows the 4L-DCC fed MV drive, which generates a voltage waveform with four-levels of 0,  $V_{dc}/3$ ,  $2V_{dc}/3$ , and  $V_{dc}$ . The number of clamping diodes, DC-link capacitors, and control complexity of DCC drastically increases with output voltage levels [40].

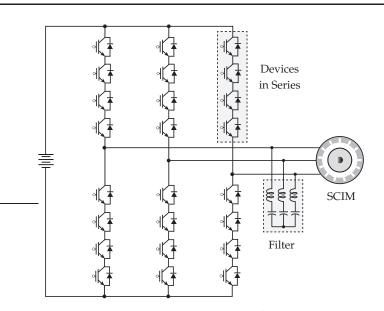

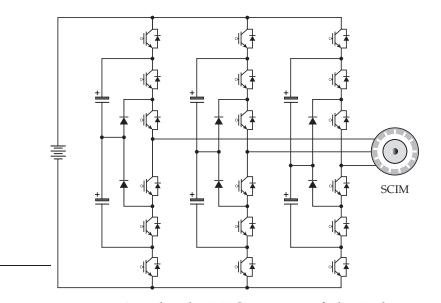

Figure 1.6. Four-level DCC fed MV drive.

The 4L-DCC consists of a DC-link with multiple neutral points, thereby it is not attractive for back-to-back operation. Also, it is difficult to achieve the DC-link voltage balancing with multi-carrier PWM schemes due to the lack of redundancy switching states [41]. This topology also exhibits unequal device power losses and requires a complex PWM scheme such as space vector modulation (SVM) scheme to overcome the above problems [42,43]. Thereby, the 4L-DCC is not commercially popular for more than three-level operation.

#### **1.3.2** Flying Capacitor Converter

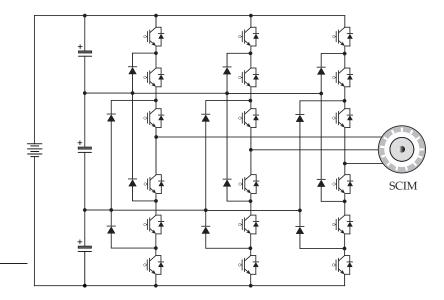

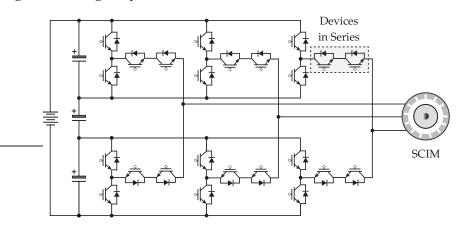

Fig. 1.7 shows the structure of a four-level flying capacitor converter (4L-FCC), in which each flying capacitor together with a pair of semiconductor devices form a power cell. The output voltage levels can be increased by adding power cells to the converter, thus it is considered as a modular structure converter [44]. Unlike 4L-DCC, the 4L-FCC topology does not require any clamping diodes, thereby the DC-link neutral points are eliminated to form a common DC-link bus for back-to-back operation.

Figure 1.7. Four-level FCC fed MV drive.

The 4L-FCC requires two flying capacitors with different voltage ratings.

These capacitors have zero initial voltage and should be pre-charged during the startup process of the converter. Hence, the 4L-FCC needs additional precharging circuits or switching method to charge the flying capacitors [45]. In addition, it needs a voltage balancing method to regulate the flying capacitor voltages at their nominal values during steady-state [46, 47]. The natural balancing of voltage balancing can be achieved with a phase-shifted carrier PWM (PSC-PWM) scheme with high switching frequency [48]. In addition, the PSC-PWM scheme ensures equal loss distribution among the devices and makes the topology is more attractive for high-speed applications.

However, the capacitor voltage ripple at low-frequency operation is a severe issue in the 4L-FCC fed MV drive. These converters need either a large capacitance value or a high-switching frequency operation [49, 50]. The former solution increases the cost and physical size of the system, whereas the latter solution increases the power losses and affects the system efficiency. These issues limit the 4L-FCC to the medium switching frequency applications only. The 4L-FCC is commercially available for traction and water pump applications.

Figure 1.8. Four-level SFCC fed MV drive.

The outer flying capacitors in the conventional 4L-FCC topology are eliminated and resulting in a new topology named as a four-level single flying capacitor converter (4L-SFCC) as shown in Fig. 1.8. The elimination of flying capacitor improves reliability, and reduce the cost and physical size of the converter. However, this approach leads to the series-connection of switching devices and causes the device voltage sharing problems [51]. Also, the 4L-SFCC loose the redundancy switching states and increases the complexity of flying capacitor voltage balancing capability with conventional multicarrier PWM scheme [52].

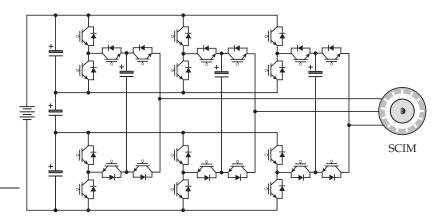

#### 1.3.3 Nested Neutral-Point Clamped Converter

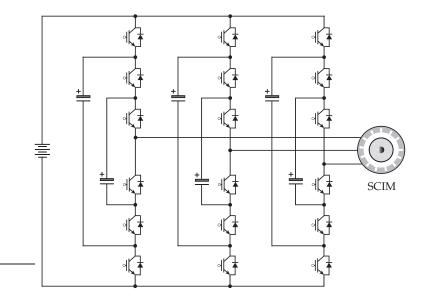

Fig. 1.9 shows the structure of a four-level nested neutral-point clamped converter (4L-NNPC). This topology combines the structure of DCC and FCC, where the clamping diodes split the flying capacitors into two equal parts as shown in Fig. 1.9. The 4L-NNPC uses an identical rating of clamping diodes, semiconductor devices, and flying capacitors, thereby its manufacturing and maintenance cost is low [53].

Figure 1.9. Four-level NNPC converter fed MV drive.

In addition, the 4L-NNPC has redundancy switching states to achieve the voltage balancing with multi-carrier PWM schemes. However, the balancing capability is limited to higher power factors and fundamental frequency only [54]. Furthermore, the flying capacitor voltage ripples are quite high during low-frequency operation [55]. Several modified PWM schemes based on the carrier and space vector philosophies are developed to improve the balancing capability while minimizing capacitor voltage ripple at lowfrequency operation [56, 57]. However, these methods increase the device switching frequency leading to higher switching power losses and poor converter efficiency.

#### 1.3.4 Hybrid Active Neutral-Point Clamped Converter

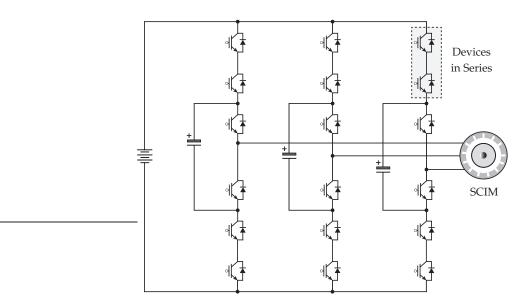

The structure of a four-level hybrid active neutral-point clamped converter (4L-HANPC) is shown in Fig. 1.10. This topology requires a lesser number of switching devices and no need of clamping diodes and flying capacitors. Unlike DCC topology, the DC-link neutral points in HANPC converter are formed with active semiconductor devices and require DC-link neutral point voltage balancing only [58].

Figure 1.10. Four-level HANPC converter fed MV drive.

Due to the lack of redundancy switching states, it is difficult to achieve DC-link voltage balancing with conventional multi-carrier PWM schemes.

The zero-sequence voltage injection with a modified carrier PWM scheme is developed to control the DC-link capacitor voltages. However, the injected zero-sequence voltage increases the converter CMV magnitude leading to the failure of bearing and winding insulation. In addition, the 4L-HANPC require a series-connection of switching devices to manufacture the converter with identical voltage rating devices [58]. This will lead to voltage sharing problems and require additional voltage equalization circuits.

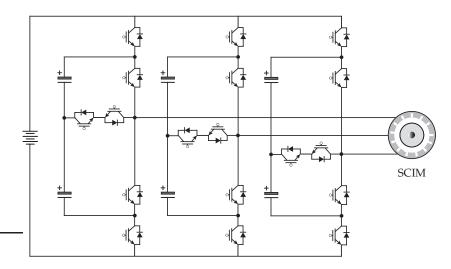

#### 1.3.5 Hybrid Clamped Converter

The hybrid clamped converter (HCC) is realized by connecting a flying capacitor across the series connected switches in each phase of the HANPC converter. Fig. 1.11 shows the configuration of a 4L-HCC fed MV drive system. Due to the presence of flying capacitors, the series-connection of devices will be eliminated, and there is no need of voltage equalization circuits.

Figure 1.11. Four-level HCC fed MV drive.

Unlike HANPC, the redundancy switching states are available in HCC for flying capacitors voltage regulation [59]. However, the need of additional voltage sensors to measure flying capacitors voltage will increase the converter cost and affect its reliability. The flying capacitors have higher voltage ripples at low-frequency operation, which will be minimized by injecting common-mode voltage [60]. The injected common-mode voltage is also used

to regulate the DC-link neutral point voltage similar to the HANPC [61]. The injected common-mode voltage increases the voltage stress on the winding insulation and leading to its failure over a long run.

# 1.3.6 Nested T-type Converter

Fig. 1.12 shows the structure of a four-level nested T-type converter [62]. This topology combines the structure of FCC and T-type converter, where the anti-series connection of semiconductor devices splits the flying capacitors into two equal parts as shown in Fig. 1.12. The anti-series connection of devices needs voltage equalizing circuits to ensure equal voltage sharing during blocking mode. The nested T-type converter does not require clamping diodes and it uses identical voltage rating of semiconductor devices and flying capacitors only [63]. Thereby, it is easy to manufacture and conduct maintenance during faults.

Figure 1.12. Four-level nested T-type converter fed MV drive.

The control philosophy of nested T-type converters is similar to 4L-NNPC, where the redundancy switching states are utilized to achieve the flying capacitor balancing with multi-carrier PWM scheme [53]. However, the voltage balancing capability is limited to higher power factors and fundamental fre-

quency. In addition, the nested T-type converter has a voltage ripple problem under the low-frequency operation, which make them less attractive for MV drive applications. The predictive control methods are investigated for lowfrequency operation of nested T-type converter. Even though, these methods are highly effective but they cause variable switching frequency operation which is not desirable for high-power MV drives [64].

#### 1.3.7 Modular Multilevel Converter

Fig. 1.13 illustrates the structure of modular multilevel converter (MMC). Modular multilevel converter is one of the most promising topologies for medium to high-voltage (HV) and high-power applications. Some of the main features are modular construction, voltage and power scalability, fault-tolerant operation with submodule (SM) redundancy, and direct connection to HV networks without line-frequency transformers [65]. These features attracted a wide range of industry applications including high-voltage direct current (HVDC) transmission, motor drives, power quality, railway power supplies, wind energy, and photovoltaic systems [66]. Each phase of MMC is realized by connecting identical SMs in cascade, and these modules does not require any isolated DC sources unlike CHB topology. Moreover, it is possible to use various SM configurations to realize MMC depending on the application requirements [67].

On the other hand, design constraints, SM capacitor voltage control, minimization of circulating currents, SM capacitor voltage ripple, and SM capacitor pre-charging process are the major technical challenges associated with the operation and control of MMC [68]. Hence, MMC requires a complex control system to achieve these control objectives. Moreover, MMC requires a larger number of semiconductor devices and passive components, which will increase the cost and affect the system reliability and efficiency. Besides, when applied in MV drives, the MMC suffers from low-frequency fluctuation in the SM floating capacitors [69, 70]. The high-frequency circulating current and common-mode voltage are injected into the system to minimize

Figure 1.13. Four-level MMC fed MV drive.

the low-frequency fluctuation [71, 72]. This leads to higher device current stress and power losses along with an increase in voltage stress on motor winding. Hence, the MMC is not an attractive solution for MV drives.

# 1.4 Pulse Width Modulation Schemes

Pulse width modulation (PWM) schemes play a key role in generating AC output voltage with adjustable magnitude and frequency. This is achieved by controlling the turn-on and turn-off process of the switching devices in the power converters. In AC drives, the PWM schemes are selected based on the machine type, power level, type of switching devices used in the power converters, performance, and cost [73]. Furthermore, the PWM schemes are designed to achieve control objectives of AC drives such as power converters DC-link/flying capacitor voltage balancing, drive common-mode voltage minimization, and output power quality improvement.

PWM schemes have been an intensive research topic during the past few

years, and several methods are developed to meet the MV drive requirements. Some of the popular PWM schemes are carrier-based PWM, space vector modulation (SVM), selective harmonic elimination (SHE), staircase modulation, and optimal PWM methods [25]. Among them, the carrierbased PWM and SVM schemes are widely used for MLC-fed MV drive applications due to the ease of digital implementation, flexibility in switching vector selection, and excellent steady-state and dynamic response.

#### 1.4.1 Multi-carrier PWM Schemes

The carrier PWM scheme is also referred to as sine-triangle PWM, and it is well established for two-level converters. In this scheme, the three-phase modulation signals are compared with a single triangular carrier signal to generate the gating signals for the switching devices in two-level converters. This approach is relatively easy to implement using digital control platforms [74]. The carrier PWM schemes are extended to multilevel converters and they are referred to as multi-carrier PWM schemes. In this approach, the three-phase modulation signals are compared with multiple triangular carrier signals to generate the gating signals for the switching devices in multilevel converters. The multi-carrier PWM schemes are categorized into level-shifted carrier (LSC-PWM) and phase-shifted carrier (PSC-PWM) PWM depending on the carrier arrangement [75,76].

The LSC-PWM is further categorized into phase-disposition (PD-PWM), phase-opposition disposition (POD-PWM), and alternate phase-opposition disposition (APOD-PWM) schemes [75]. Among them, the PD-PWM generates output voltage with the lowest harmonic distortion compared to POD-PWM and APOD-PWM schemes. However, the LSC-PWM schemes do not have natural flying capacitor voltage balancing capability and cause uneven loss distribution among the devices. Recently, the modified LSC-PWM schemes are studied, focusing on low-frequency operation, even loss distribution, and natural voltage balancing of MLC flying capacitors [77, 78]. However, these methods increase the effective switching frequency of the converter leading

to higher switching losses.

On the other hand, the PSC-PWM scheme can achieve natural voltage balancing capability with high carrier frequency and is widely studied for multi-cell converters [79, 80]. With an optimal selection of phase-shift, it is possible to achieve harmonic cancellation with PSC-PWM thereby the output power quality of MLCs can be improved [81–83]. However, the higher carrier frequency increases the effective switching frequency of the converter. Moreover, the elimination/minimization of drive common-mode voltage is difficult to achieve with multi-carrier PWM schemes.

#### 1.4.2 Space Vector Modulation Schemes

Space vector modulation (SVM) is one of the preferred real-time modulation schemes and is widely used for the digital control of two-level and multilevel converters. The SVM scheme allows the direct control of converter line-to-line voltages, which in turn produces the phase voltages [84]. SVM has the flexibility of selecting the best switching vector from the redundant switching vectors, which can be used to achieve multiple control objectives such as DC-link/flying capacitor voltage control, elimination/minimization of common-mode voltage, and minimization of switching frequency [85,86].

Furthermore, the SVM provides better DC-link bus utilization and harmonic performance compared with carrier PWM schemes [87]. However, the SVM is quite difficult to implement for more than three-level converters due to the presence of a large number of switching vectors. There are several simplified multilevel SVM methods in *abc*-coordinates, *gh*-coordinates, and two-level SVM-based philosophy are developed to address the computational complexity issues. The simplified SVM methods do not involve the selection of redundancy switching vectors, hence these methods will loose the inherent features of conventional multilevel SVM [88–92].

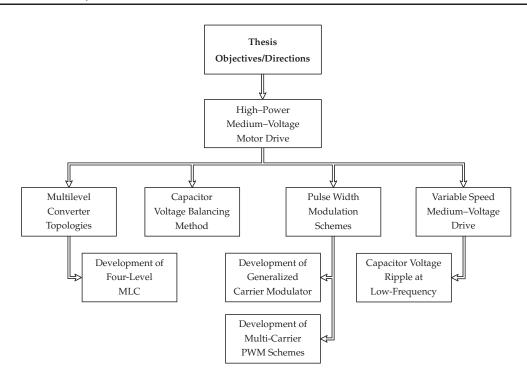

Figure 1.14. Summary of thesis directions/objectives.

# **1.5** Thesis Objectives

Aforementioned technical issues and requirements of high-power multilevel converters and MV drives are addressed in this thesis. The research objectives and contributions of this thesis are summarized in Fig. 1.14. The first problem addressed in this thesis is the development of a four-level multilevel converter (4L-MLC) to handle an operating voltage up to 4.16 kV without using the transformer and series connection of switching devices. The second important aspect is the development of high-performance voltage balancing methods with reduced complexity for 4L-MLCs. The third aspect is the development of a generalized pulse width modulator to integrate the voltage balancing method with different carrier-based PWM schemes to control the 4L-MLC. Finally, the challenges associated with the low-speed operation of MV drives are addressed through the development of a modified pulse width modulation scheme. The main contributions of this thesis are as follows:

# 1) Research on Four-Level Multilevel Converter Topologies for MV Applications

The existing 4L-MLCs need a series-connection of devices, which leads to device voltage sharing problems. These converters have a complex structure with a large number of semiconductor devices, clamping diodes, and flying capacitors. Hence, their manufacturing and maintenance cost are quite high. Also, the existing MLCs need a complex control scheme due to the lack of redundancy switching states. Some of the topologies have multiple DC-link neutral points, which makes them less attractive for back-to-back operation.

Considering the above issues, a new 4L-MLC without a series-connection of devices is proposed for MV applications. Hence, the proposed topology does not require voltage equalization circuits. It also requires a lesser number of semiconductor devices and flying capacitors, and they do not need any clamping diodes. Furthermore, the proposed topology has redundancy switching states, which can be used to achieves the voltage balancing objective. Hence, it does not require a complex control system. Moreover, the proposed topology is suitable for back-to-back operation due to the presence of a common DC-link.

#### 2) Research on Voltage Balancing Methods for 4L-MLCs

In the existing 4L-MLCs, the DC-link/flying capacitor voltage balancing is necessary for reliable operation. The voltage balancing is achieved at the modulation stage with zero-sequence voltage injection or by using an external balancing method with redundancy switching states. The former method increases the load voltage stress leading to their premature failure over a long run. The latter method balancing capability is limited to higher power factors and fundamental frequency only. In addition, the existing methods cause unwanted device switchings leading to higher switching frequency operation, thereby higher switching power losses in the converter.

Considering the above issues, a new voltage balancing method is proposed for 4L-MLC. The proposed method uses redundancy switching states to achieve the balancing of flying capacitors voltage. This method does not cause unwanted device switchings unlike existing methods. Moreover, its balancing capability is extended to low power factors and low fundamental frequencies as well. The proposed method is designed such that it can be implemented with both multi-carrier PWM and SVM schemes.

#### 3) Research on Pulse Width Modulation Schemes for 4L-MLCs

Multi-carrier PWM and SVM schemes are the preferred choices for MLC control. Among them, the multi-carrier PWM schemes are widely used and easy to implement for 4L-MLC compared with SVM scheme. However, there is no unique structure of pulse width modulator in the literature to study the various multi-carrier arrangements for 4L-MLC. The carrier arrangement directly affects the converter output voltage and current harmonic distortion, and flying capacitor voltage ripple.

Considering the above issues, an unique structure of the pulse width modulator is proposed to control the 4L-MLC. With the proposed structure, it is easy to integrate the proposed voltage balancing method and study the performance of various multi-carrier arrangements for 4L-MLC.

#### 4) Research on Low-Speed Operation of MV Drives

Several industrial applications need MV drives with the capability of developing rated torque under a wide range of rotational speeds. In MV drives, the power converters generate AC voltages/currents with adjustable magnitude and frequency at the motor terminals, thereby the motor rotational speed and torque production is varied as per the load requirements. The quality of output AC voltages/currents directly depends on flying capacitor voltage ripple, which in turn causes motor speed and torque ripple leading to a poor load performance. To achieve high-performance MV drive, it is necessary to limit the converter flying capacitor voltage ripple (peak-to-peak) within 5% of their nominal voltage. Considering the above issues, a modified multi-carrier PWM scheme is proposed to keep the flying capacitor voltage ripple within its limits throughout the MV drive operation. By doing so, the converter generates voltage/current waveforms with a less harmonic distortion, which in turn leads to a smaller ripple in motor speed and torque. The field-oriented control (FOC) in the rotor flux reference frame is applied to achieve the closed-loop control of motor speed/torque and flux in the proposed 4L-MLC fed MV drive system.

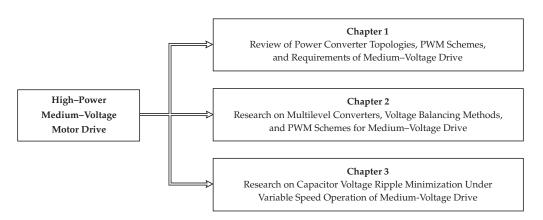

# **1.6** Thesis Outline

The research presented in this thesis is organized into four chapters. The research outline of the thesis is summarized in Fig. 1.15. The work carried out in each chapter is summarized as follows:

Figure 1.15. Summary of the thesis.

• **Chapter-1:** In this chapter, the fundamentals of MV drives and their requirements are presented. Also, the existing four-level multilevel converters, pulse width modulation schemes and their issues are discussed. Finally, the research objectives and outline of this thesis are presented.

- **Chapter-2:** In this chapter, a new 4L-MLC is proposed for MV applications. Also, a new voltage balancing approach along with a simple pulse width modulator structure is proposed. The dynamic and steady-state performances of the proposed balancing approach are verified on 4L-MLC with the PD-PWM scheme. To handle low-frequency operation, a modified carrier PWM is scheme is proposed and its performance is compared with the PD-PWM scheme.

- Chapter-3: In this chapter, a new 4L-MLC fed MV drive is proposed. A modified multi-carrier PWM scheme is proposed to limit the flying capacitor voltage ripple within 5% of their nominal voltage. Finally, the FOC scheme is implemented to achieve closed-loop control of motor speed/torque and flux. The start-up, steady-state and dynamic performances of the MV drive are presented with modified multi-carrier PWM scheme.

- **Chapter-4**: The main contributions and conclusions of this thesis are summarized in this chapter. The future directions to the research presented in this thesis are also suggested.

# CHAPTER 2

# VOLTAGE BALANCING AND MODULATION OF FOUR-LEVEL MULTILEVEL CONVERTER

MULTILEVEL converters (MLCs) have significant advantages compared with two-level converters at medium-voltage operation. These converters generate high-quality output voltage with low dv/dt, output current with a smaller ripple, and low common-mode voltage (CMV). MLCs have higher energy conversion efficiency and use low-cost and low-voltage semiconductor technology to handle medium-voltage (MV) operation. Furthermore, the MLCs use a smaller size of output filters (if needed) due to their superior harmonic performance [36, 37, 39, 93].

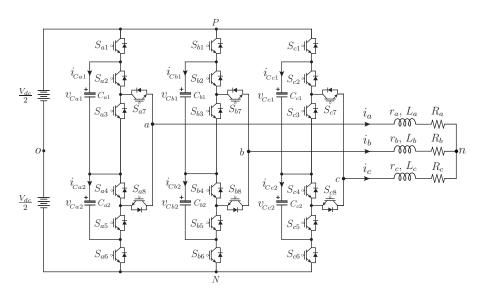

In this chapter, a new four-level MLC (4L-MLC) without a series connection of switching devices is proposed for MV applications. The new MLC uses flying capacitors to achieve multilevel operation. These flying capacitors are pre-charged to their nominal values during start-up operation and maintained at their nominal values during normal operation. To achieve the voltage balancing, a simple balancing method based on logical functions is proposed for 4L-MLC. This method guarantees the voltage balancing without an increasing device switching frequency and eliminates the unwanted device switchings compared with existing methods. In addition, a simple carrier-based pulse width modulator is developed to implement the balancing approach with different carrier arrangements. The steady-state and dynamic performances of the proposed 4L-MLC and voltage balancing approach are verified through simulation studies. The conventional carrier PWM scheme leads to a larger capacitor voltage ripple at low-frequency operation. In this chapter, a modified carrier PWM scheme is proposed to reduce the capacitor voltage ripple at low-frequency operation. The simulation studies are presented to verify the effectiveness of the proposed modified carrier PWM scheme.

# 2.1 New Four–Level Multilevel Converter

The circuit configuration of a new four-level multilevel converter (4L-MLC) and its operation and switching states are discussed in the following subsections. Also, the detailed comparison of new 4L-MLC with existing multilevel converters is presented.

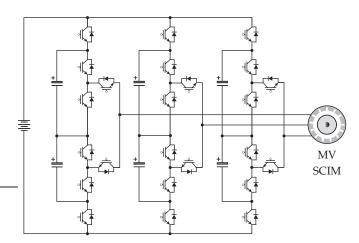

Figure 2.1. Proposed 4L-MLC with a passive load.

# 2.1.1 Converter Configuration

The configuration of the proposed 4L-MLC connected to a passive load is shown in Fig. 2.1. Each phase of the proposed topology is designed with eight switching devices  $(S_{x1}-S_{x8})$  of  $V_{dc}/3$  rating each, and two flying capacitors  $(C_{x1}-C_{x2})$  with a nominal voltage of  $V_{dc}/3$  each, where  $x \in \{a, b, c\}$ denotes the phase. In the proposed 4L-MLC, the switching devices are not connected in series, hence the voltage equalization circuits are not needed. The positive (P) and negative (N) DC-link terminals are connected to a DCsource of  $V_{dc}$  rating. The DC source is divided into two equal parts and its midpoint is denoted as o. The three-phase AC terminals of the proposed 4L-MLC are connected to a balanced three-phase star-connected passive load. Each phase of the passive load is realized using a series connection of resistive  $(R_x)$  and inductance  $(L_x)$  with internal resistance  $(r_x)$  as shown in Fig. 2.1.