Knowledge Commons, http://knowledgecommons.lakeheadu.ca

**Electronic Theses and Dissertations**

Electronic Theses and Dissertations from 2009

2021

# Power loss investigation of series-connected current source inverters

Jiang, Bowen

https://knowledgecommons.lakeheadu.ca/handle/2453/4903 Downloaded from Lakehead University, KnowledgeCommons

# Power Loss Investigation of Series-Connected Current Source Inverters

by

Bowen Jiang

A thesis

presented to Lakehead University

in partial fulfillment of the requirements for the degree of

Master of Science

in the Program of

Electrical and Computer Engineering

Thunder Bay, Ontario, Canada, 2021

© Bowen Jiang, 2021

## **AUTHOR'S DECLARATION**

I hereby declare that I am the sole author of this thesis. This is a true copy of the thesis, including any required final revisions, as accepted by my examiners. I understand that my thesis may be made electronically available to the public.

## Abstract

Current-source inverters (CSIs) are a type of direct current (DC) to alternating current (AC) converters that generate a defined AC output current waveform from a DC current supply. As the counterpart of voltage source inverters (VSIs), they feature a simple converter structure, low switching dv/dt on the ac-side, and reliable short-circuit protection. These advantages have made CSIs widely used in high power medium voltage drives. Besides, they have also been studied in other applications, such as wind energy conversion systems, superconducting magnetic energy storage (SMES) systems, and microgrid systems. Different topologies of CSIs and modulation schemes have been evolved to tailor various application requirements. For those applications with a higher power rating, two or more CSIs can be connected in series to form series-connected CSIs (SC-CSIs) to increase the power handling capability. To the best of the author's knowledge, three topologies of SC-CSIs have been developed so far. The first topology referred to as topology A is constructed by connecting several identical CSIs in series. These CSIs are identical in terms of topology, modulation, and control. A multi-winding transformer is employed at the output to provide a clear current path for each CSI and step up the voltage if necessary. In the second topology designated as topology B, the multi-winding transformer is replaced by a phase-shifting transformer, and a phase-shifting modulation scheme is implemented. This topology features an increased DC current utilization, decreased switching losses, and reduced passive components. The third topology denominated as topology C adopts a different arrangement of switches leading to a reduced number of switching devices. A multi-winding transformer is used at the output in this topology. Power losses are an important attribute of SC-CSIs since they have a significant impact on the efficiency of the system. Besides, it is necessary to find out the power loss distribution of inverters to design an appropriate cooling system. However, the power losses and the power loss distribution of these three topologies have not been figured out.

In this thesis, the power losses and the power loss distribution of each topology are investigated in a comparative method. This is divided into two parts. In the first part, the power losses of the switching device used in SC-CSIs are introduced. The factors which can influence the power losses of SC-CSIs are analyzed in detail. The parameter of each factor is compared in the three topologies of SC-CSIs. The power loss distribution of each topology is figured out. The total power losses of these three topologies are compared under one modulation scheme first to find out the topology which has the fewest total power losses. In the second part, three typical pulse width modulation (PWM) schemes and how they influence the power losses of SC-CSIs are analyzed. The power losses of the three topologies are compared under different modulation schemes. The topology and the modulation scheme with the fewest power losses are recommended. Simulations are used to assist the investigation and verify the results.

## ACKNOWLEDGMENTS

I would like to express my most sincere gratitude to my supervisor, Dr. Qiang Wei, for providing his guidance, constructive suggestions, and kindly encouragement throughout my study.

I also thank the Graduate Coordinator of the Electrical and Computer Engineering Department, Dr. Yushi Zhou and other committee members, Dr. Amir Ameli and Dr. Farhan Ghaffar for their feedback, advice, and support.

I also wish to thank Dr. Krishnamoorthy Natarajan and other professors who provided insightful guidance and helpful advice in my graduate study.

I am also extremely grateful to my parents and friends for their invaluable support and continued encouragement throughout my study.

## **Publications**

- B. Jiang, Z. Wang, and Q. Wei, "Power Loss Investigation of Series-Connected Current Source Inverters," *IECON 2021 – 47th Annual Conference of the IEEE Industrial Electronics Society*, pp. 1-6, Oct. 2021.

- [2] Z. Wang, B. Jiang, and Q. Wei, "DC-link Inductor Investigation for Series-Connected Current Source Converter," 2021 IEEE Energy Conversion Congress and Exposition (ECCE), pp. 3211-3215, Oct. 2021.

- [3] B. Jiang "Power Loss Investigation of Series-Connected Current Source Inverters with Different Modulation Schemes." (To be submitted)

# **Table of Contents**

| Abstract                                                              | iii |

|-----------------------------------------------------------------------|-----|

| ACKNOWLEDGMENTS                                                       | v   |

| Publications                                                          | vi  |

| List of Tables                                                        | X   |

| List of Figures                                                       | xi  |

| List of Symbols                                                       | xiv |

| List of Abbreviations                                                 | XV  |

| Chapter 1                                                             | 1   |

| Introduction                                                          | 1   |

| 1.1 Current source inverter topology                                  | 2   |

| 1.1.1 Three-level current source inverter                             | 2   |

| 1.1.2 Multilevel current source inverter                              | 4   |

| 1.1.3 Parallel current source inverters                               | 12  |

| 1.1.4 Series-connected current source inverters                       | 14  |

| 1.2 Power losses of SC-CSIs                                           | 19  |

| 1.3 Dissertation objectives                                           | 19  |

| Chapter 2                                                             |     |

| Power Loss Investigation of Series-Connected Current Source inverters |     |

| 2.1 Power losses of IGBTs and diodes                                  |     |

| 2.1.1 Conduction losses                                               |     |

| 2.1.2 Switching losses                                                |     |

| 2.2 Factors related to power losses                                   |     |

| 2.2.1 Modulation scheme                                               |     |

| 2.2.2 Modulation index                                                                                                                                                                                                                                                                                                       |                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 2.2.3 Switching frequency                                                                                                                                                                                                                                                                                                    |                                                               |

| 2.2.4 Conduction current                                                                                                                                                                                                                                                                                                     |                                                               |

| 2.2.5 Voltage stress of the switching devices                                                                                                                                                                                                                                                                                |                                                               |

| 2.2.6 Characteristics of the switching device                                                                                                                                                                                                                                                                                |                                                               |

| 2.3 Total power losses and power loss distribution                                                                                                                                                                                                                                                                           |                                                               |

| 2.3.1 Total power losses comparison                                                                                                                                                                                                                                                                                          |                                                               |

| 2.3.2 Power loss distribution                                                                                                                                                                                                                                                                                                |                                                               |

| 2.4 Simulation investigation                                                                                                                                                                                                                                                                                                 |                                                               |

| 2.4.1 Simulation results                                                                                                                                                                                                                                                                                                     |                                                               |

| 2.4.2 Comparison between simulated and calculated results                                                                                                                                                                                                                                                                    |                                                               |

| 2.5 Summary                                                                                                                                                                                                                                                                                                                  |                                                               |

|                                                                                                                                                                                                                                                                                                                              |                                                               |

| Chapter 3                                                                                                                                                                                                                                                                                                                    | 46                                                            |

| Power Loss Investigation of Series-Connected Current Source Inverters w                                                                                                                                                                                                                                                      |                                                               |

|                                                                                                                                                                                                                                                                                                                              | ith Different                                                 |

| Power Loss Investigation of Series-Connected Current Source Inverters w                                                                                                                                                                                                                                                      | ith Different                                                 |

| Power Loss Investigation of Series-Connected Current Source Inverters w<br>Modulation Schemes                                                                                                                                                                                                                                | ith Different<br>46<br>46                                     |

| Power Loss Investigation of Series-Connected Current Source Inverters w<br>Modulation Schemes                                                                                                                                                                                                                                | ith Different<br>46<br>46<br>46                               |

| Power Loss Investigation of Series-Connected Current Source Inverters w<br>Modulation Schemes                                                                                                                                                                                                                                | ith Different<br>46<br>46<br>47<br>47                         |

| Power Loss Investigation of Series-Connected Current Source Inverters w<br>Modulation Schemes                                                                                                                                                                                                                                | ith Different<br>46<br>46<br>47<br>47<br>49<br>50             |

| Power Loss Investigation of Series-Connected Current Source Inverters w<br>Modulation Schemes                                                                                                                                                                                                                                | ith Different<br>46<br>46<br>47<br>49<br>50<br>53             |

| Power Loss Investigation of Series-Connected Current Source Inverters w<br>Modulation Schemes                                                                                                                                                                                                                                | ith Different<br>46<br>46<br>47<br>49<br>50<br>53<br>54       |

| Power Loss Investigation of Series-Connected Current Source Inverters w         Modulation Schemes         3.1 Modulation schemes for CSIs.         3.1.1 TPWM         3.1.2 SHE         3.1.3 SVM         3.2 Power losses with different modulation schemes         3.2.1 Conduction losses                                | ith Different<br>46<br>46<br>47<br>49<br>50<br>53<br>54<br>57 |

| Power Loss Investigation of Series-Connected Current Source Inverters w         Modulation Schemes         3.1 Modulation schemes for CSIs.         3.1.1 TPWM         3.1.2 SHE         3.1.3 SVM         3.2 Power losses with different modulation schemes         3.2.1 Conduction losses         3.2.2 Switching losses | ith Different<br>46<br>46<br>47<br>49<br>50<br>53<br>54<br>57 |

| 3.4 Summary                       |    |

|-----------------------------------|----|

| Chapter 4                         |    |

| Conclusions                       |    |

| 4.1 Contributions and conclusions |    |

| 4.2 Future work                   | 83 |

| Reference                         |    |

# **List of Tables**

| Table 2-1 Simulation parameters of the SC-CSIs                          | 32 |

|-------------------------------------------------------------------------|----|

| Table 2-2 Parameters of the employed IGBTs and diodes in topology A     | 33 |

| Table 2-3 Parameters of the employed IGBTs and diodes in topology C     | 34 |

| Table 2-4 Simulated power losses of the switching devices in topology A | 37 |

| Table 2-5 Simulated power losses of the switching devices in topology B | 40 |

| Table 2-6 Simulated power losses of the switching devices in topology C | 42 |

| Table 2-7 Simulated and calculated power losses of the SC-CSIs          | 43 |

| Table 2-8 Comparison among the three topologies                         | 45 |

|                                                                         |    |

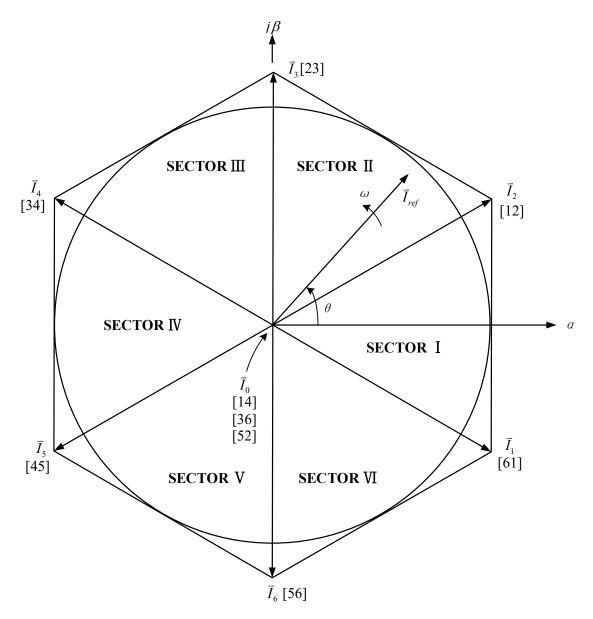

| Table 3-1 Switching States and Space Vectors [3]        | 52 |

|---------------------------------------------------------|----|

| Table 3- 2 Parameters of the SC-CSIs.                   | 58 |

| Table 3-3 Switching frequency in each modulation scheme | 58 |

| Table 3-4 Simulated power losses in topology A          | 71 |

| Table 3-5 Simulated power losses in topology B          | 73 |

| Table 3-6 Simulated power losses in topology C          | 78 |

## **List of Figures**

| Figure 1-1 The typical three-phase PWM current source inverter [3]                      | 3  |

|-----------------------------------------------------------------------------------------|----|

| Figure 1-2 Three-phase five-level single-rating inductor CSI with four inductors of the | he |

| same rating [35].                                                                       | 5  |

| Figure 1-3 Five-level single-rating inductor CSI with two interphase inductors [35]     | 6  |

| Figure 1-4 Three-phase five-level CSI with two multi-rating inductors [22]              | 7  |

| Figure 1-5 Three-phase paralleled H-bridge five-level CSI [22]                          | 8  |

| Figure 1-6 Three-phase five-level buck-boost derived multilevel CSI [38]                | 9  |

| Figure 1-7 Modified five-level buck-boost derived multilevel CSI [38]                   | 10 |

| Figure 1-8 Ćuk-derived five-level CSI [38]                                              | 11 |

| Figure 1-9 Three-phase CS-MMC topology with its inductor-based cells [35]               | 12 |

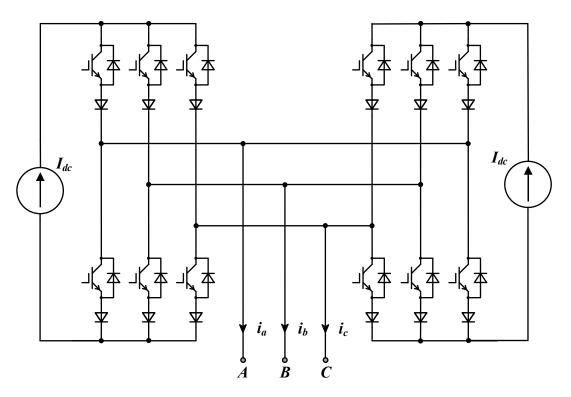

| Figure 1-10 Parallel current source inverters with a three-phase load [3]               | 13 |

| Figure 1-11 Topology A of SC-CSIs [31]                                                  | 15 |

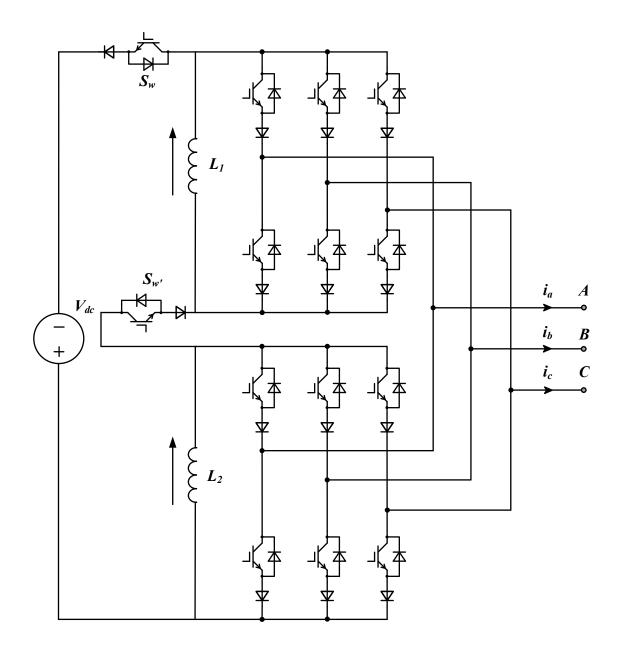

| Figure 1-12 SC-CSIs with switching frequency of 60 hertz (topology B) [31]              | 16 |

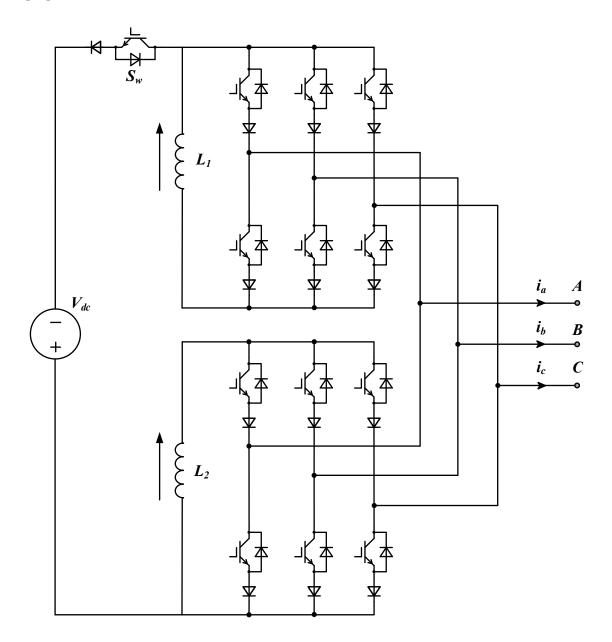

| Figure 1-13 Topology C of SC-CSIs [32]                                                  | 18 |

|                                                                                         |    |

|                                                                                         |    |

Figure 2-1 Typical output characteristics of IGBTs and diodes [45].

22

Figure 2-2 The typical power diode current and voltage waveforms during turn-off [47].

24

Figure 2-3 The equivalent circuit of SC-CSIs in topology A [32].

28

Figure 2-4 The equivalent circuit of SC-CSIs in topology B [32].

29

Figure 2-5 The turn-on energy losses *E*<sub>on</sub> and the turn-off energy losses *E*<sub>off</sub> of the IGBTs [49], [50].

30

Figure 2-6 Simulation circuit of topology A.

34

Figure 2-7 Simulation circuit of topology B.

35

Figure 2-8 Simulation circuit of topology A.

36

Figure 2-9 Simulated currents in topology A.

37

Figure 2-10 Simulated currents in topology B.

38

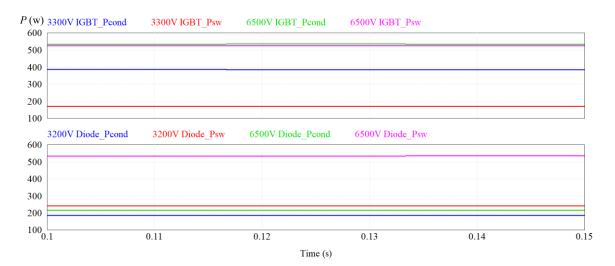

| Figure 2-12 Simulated power losses of the switching devices in topology B | 39 |

|---------------------------------------------------------------------------|----|

| Figure 2-13 Simulated currents in topology C                              | 41 |

| Figure 2-14 Simulated power losses of the switching devices in topology C | 42 |

| Figure 2-15 Comparison between the simulated and calculated power losses  | 44 |

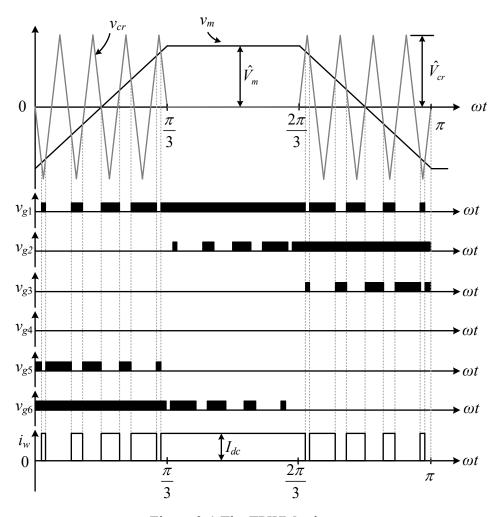

| Figure 3-1 The TPWM scheme                                                                      | -8 |

|-------------------------------------------------------------------------------------------------|----|

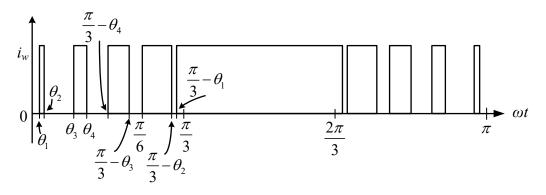

| Figure 3-2 The SHE modulation scheme5                                                           | 0  |

| Figure 3-3 Space vector diagram for CSIs [3]5                                                   | 1  |

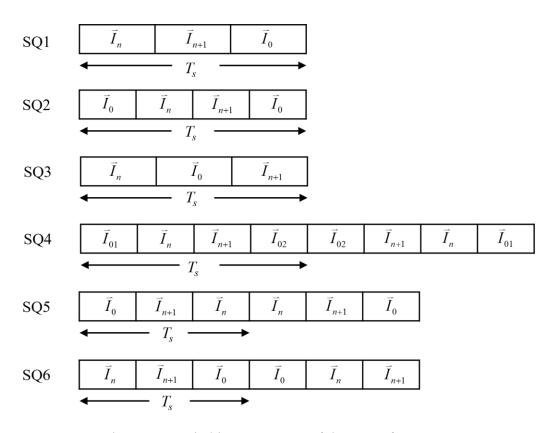

| Figure 3-4 Switching sequences of the SVM for CSIs5                                             | 3  |

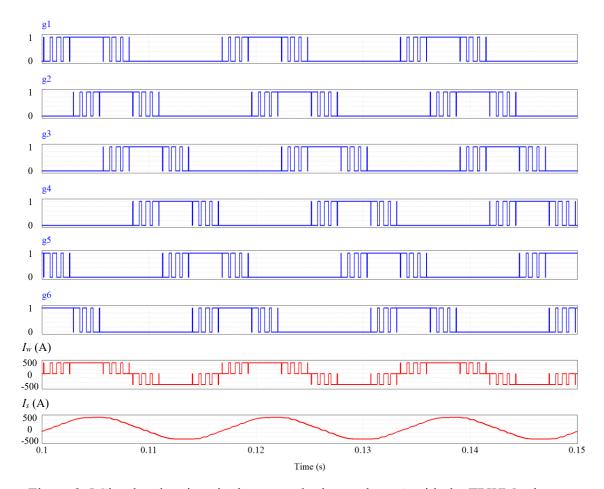

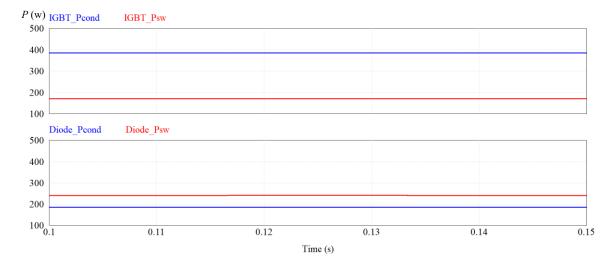

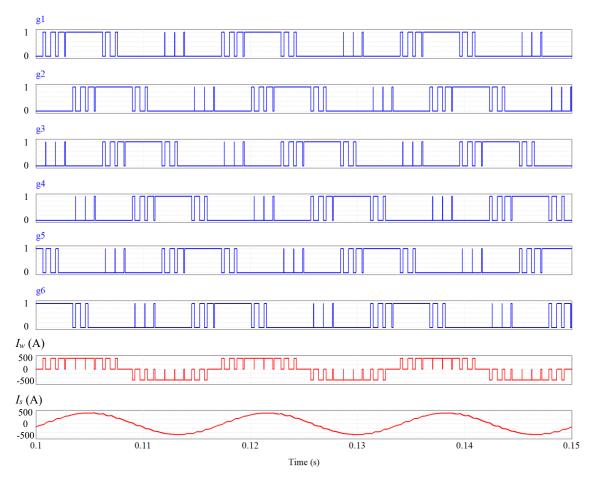

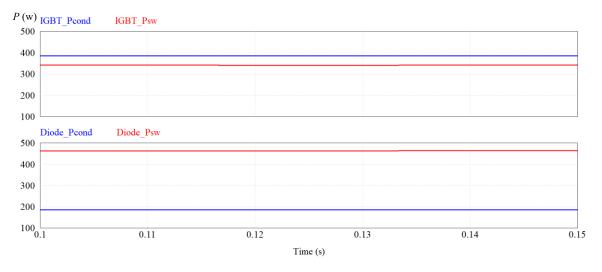

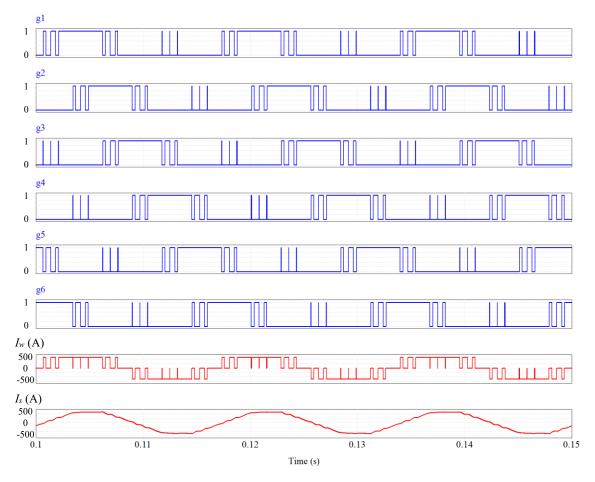

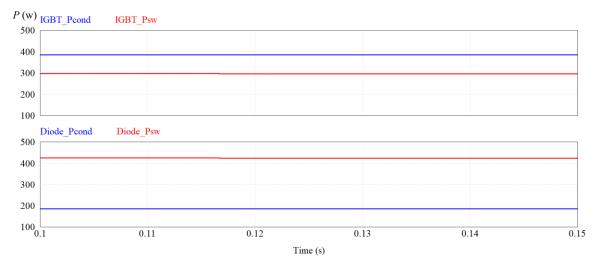

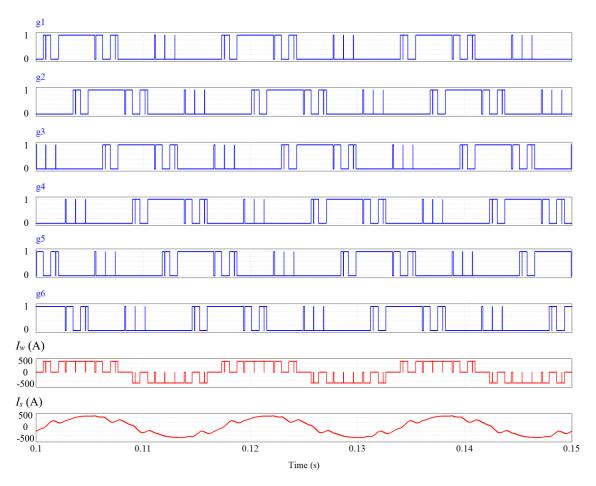

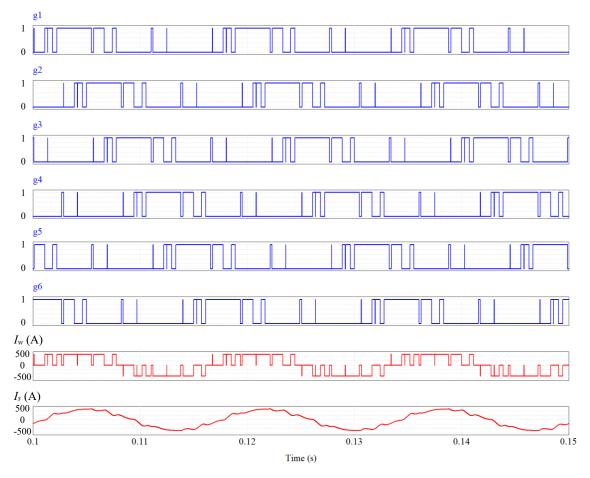

| Figure 3-5 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the TPWM scheme 5     | 9  |

| Figure 3-6 Simulated power losses of one switching device in topology A with the TPWN           | М  |

| scheme                                                                                          | 0  |

| Figure 3-7 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SHE scheme 6      | 1  |

| Figure 3-8 Simulated power losses of one switching device in topology A with the SH             | E  |

| scheme                                                                                          | 1  |

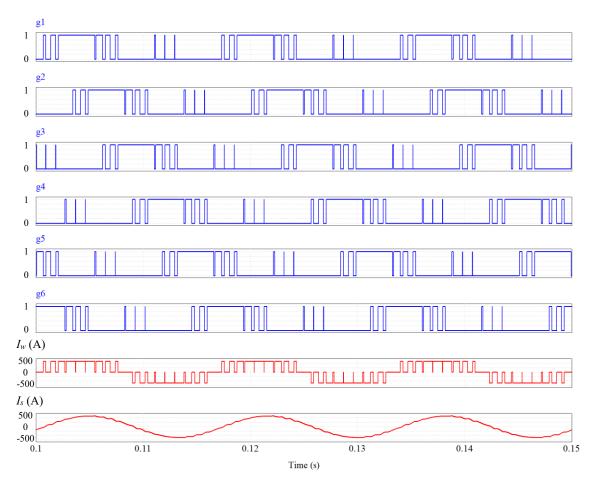

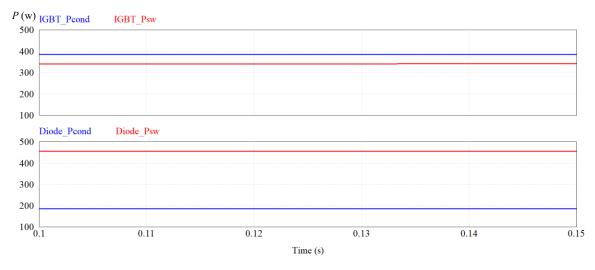

| Figure 3-9 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SVM (SQ1) scheme  | e. |

|                                                                                                 | 2  |

| Figure 3-10 Simulated power losses of one switching device in topology A with the SVM           | v  |

| (SQ1) scheme                                                                                    | 3  |

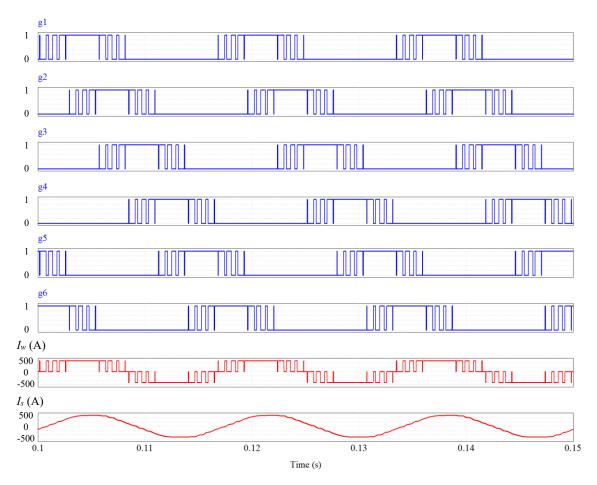

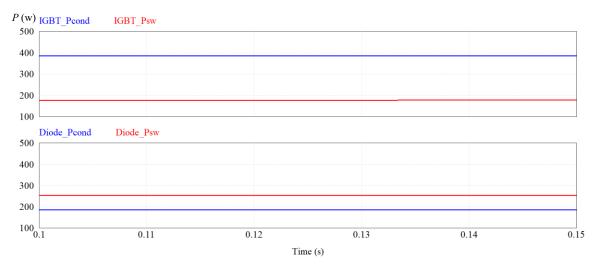

| Figure 3-11 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SVM (SQ2) scheme | e. |

|                                                                                                 | 4  |

| Figure 3-12 Simulated power losses of one switching device in topology A with the SVM           | v  |

| (SQ2) scheme                                                                                    | 4  |

| Figure 3-13 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SVM (SQ3) scheme | e. |

|                                                                                                 | 5  |

| Figure 3-14 Simulated power losses of one switching device in topology A with the SVM           | v  |

| (SQ3) scheme                                                                                    | 6  |

| Figure 3-15 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SVM (SQ4) scheme | e. |

|                                                                                                 | 7  |

| Figure 3-16 Simulated power losses of one switching device in topology A with the SVM           | M  |

| (SQ4) scheme                                                                                    | 7  |

|                                                                                                 |    |

| Figure 3-17 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SVM (SQ5) scheme. |

|--------------------------------------------------------------------------------------------------|

|                                                                                                  |

| Figure 3-18 Simulated power losses of one switching device in topology A with the SVM            |

| (SQ5) scheme                                                                                     |

| Figure 3-19 Simulated gating singles, $i_w$ , and $i_s$ in topology A with the SVM (SQ6) scheme. |

|                                                                                                  |

| Figure 3-20 Simulated power losses of one switching device in topology A with the SVM            |

| (SQ6) scheme                                                                                     |

| Figure 3-21 Simulated power losses in topology A with different modulation schemes. 72           |

| Figure 3-22 Simulated gating singles, $i_w$ , and $i_s$ in topology B with the square-wave       |

| operation                                                                                        |

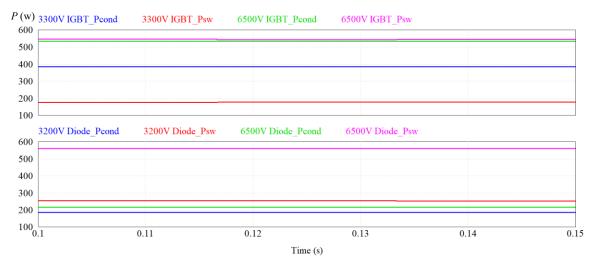

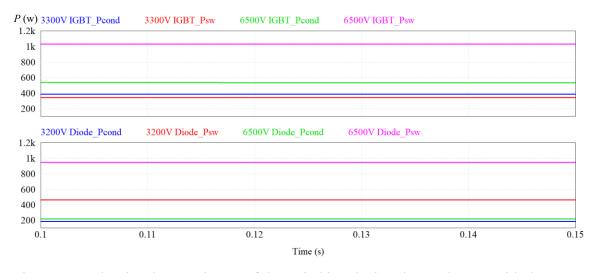

| Figure 3-23 Simulated power losses of the switching devices in topology C with the TPWM          |

| scheme                                                                                           |

| Figure 3-24 Simulated power losses of the switching devices in topology C with the SHE           |

| scheme                                                                                           |

| Figure 3-25 Simulated power losses of the switching devices in topology C with the SVM           |

| (SQ1) scheme                                                                                     |

| Figure 3-26 Simulated power losses of the switching devices in topology C with the SVM           |

| (SQ2) scheme                                                                                     |

| Figure 3-27 Simulated power losses of the switching devices in topology C with the SVM           |

|                                                                                                  |

| (SQ3) scheme                                                                                     |

| Figure 3-28 Simulated power losses of the switching devices in topology C with the SVM           |

| (SQ4) scheme                                                                                     |

| Figure 3-29 Simulated power losses of the switching devices in topology C with the SVM           |

| (SQ5) scheme                                                                                     |

| Figure 3-30 Simulated power losses of the switching devices in topology C with the SVM           |

| (SQ6) scheme                                                                                     |

| Figure 3-31 Simulated power losses in topology C with different modulation schemes. 79           |

| Figure 3-32 Simulated power loss comparison of SC-CSIs with different modulation                 |

| schemes                                                                                          |

# List of Symbols

| Symbol                                              | Meaning                                     |

|-----------------------------------------------------|---------------------------------------------|

| А, В, С                                             | inverter output terminals                   |

| $C_{f}, C_{1}C_{n}$                                 | CSI output filter capacitance               |

| dv/dt                                               | voltage rate-of-change                      |

| $E_{off}$                                           | the turn-off energy losses of IGBTs         |

| Eon                                                 | the turn-on energy losses of IGBTs          |

| Err                                                 | reverse recovery energy losses of diodes    |

| F <sub>sw</sub>                                     | switching frequency                         |

| <i>g</i> 1 <i>g</i> 6                               | gating signals                              |

| ia, ib, ic                                          | phase currents                              |

| Ic                                                  | conduction current                          |

| Idc                                                 | dc-link current                             |

| İs                                                  | inverter output current                     |

| <i>i</i> <sub>w</sub>                               | inverter output PWM current                 |

| $L_1L_n$                                            | inductance                                  |

| ma                                                  | modulation index                            |

| Pcon                                                | conduction losses                           |

| P <sub>sw</sub>                                     | switching losses                            |

| Qrr                                                 | Reverse recovery charge of diodes           |

| $R, R_1R_n$                                         | resistance                                  |

| $S_1 \ldots S_6$                                    | switching devices of inverters              |

| $S_1 \ldots S_6, S_{n1} \ldots S_{n6}, S_w, S_{w'}$ | switching devices of inverters              |

| $T_s$                                               | sampling period                             |

| V <sub>AB</sub>                                     | line to line voltage                        |

| $V_B$                                               | reverse blocking voltage                    |

| Von                                                 | saturation voltage                          |

| heta                                                | angle of a vector in the space vector plane |

| ω                                                   | fundamental angular frequency               |

|                                                     |                                             |

# List of Abbreviations

| Abbreviation | Meaning                                           |

|--------------|---------------------------------------------------|

| AC           | alternating current                               |

| APOD         | alternative phase opposition disposition          |

| CH7          | current source H7 inverter                        |

| CMV          | common-mode voltage                               |

| CSI          | current source inverter                           |

| CS-MMC       | current source modular multilevel converter       |

| CSR          | current source rectifier                          |

| DC           | direct current                                    |

| GCT          | gate commutated thyristors                        |

| GTO          | gate turn-off thyristors                          |

| IGBT         | insulated-gate bipolar transistor                 |

| MCSI         | multilevel current source inverter                |

| MOSFET       | metal-oxide semiconductor field-effect transistor |

| MV           | medium voltage                                    |

| MVSI         | multilevel voltage source inverter                |

| NS-SVM       | natural sampling SVM                              |

| PU           | per unit                                          |

| PWM          | pulse width modulation                            |

| SC-CSIs      | series-connected current source inverters         |

| SGCT         | symmetric gate commutated thyristors              |

| SHE          | selective harmonics elimination                   |

| SMES         | superconducting magnetic energy storage           |

| SQ1          | sequence 1                                        |

| SQ2          | sequence 2                                        |

| SQ3          | sequence 3                                        |

| SQ4          | sequence 4                                        |

| SQ5          | sequence 5                                        |

| SQ6          | sequence 6                                        |

| SVM  | space vector modulation            |

|------|------------------------------------|

| TPWM | trapezoidal pulse width modulation |

| UPS  | uninterruptable power system       |

| VSI  | voltage source inverter            |

## Chapter 1 Introduction

The PWM CSI was proposed in the early 1970s [1] and has been receiving more and more attention. It produces a defined three-phase AC current waveform from a stiff DC current source. The input DC current can be obtained by connecting a relatively large inductor in series with a DC voltage supply. CSIs use switching devices with self-extinguishable capability and bipolar voltage blocking capability. By implementing an appropriate switching control strategy, the magnitude and the frequency of the output current can be controlled. Compared with voltage source inverters (VSI), CSIs exhibit several advantages, such as a simple converter structure, low switching dv/dt on the output side, inherent four-quadrant operation, and reliable overcurrent and short-circuit protection [2]. They have been widely used in high power medium voltage (MV) drives [2]–[7] in industry and drawing increasing attention in other applications, such as wind energy conversion systems [8]–[11], superconducting magnetic energy storage systems [12]–[13], microgrid systems [14]–[15], and photovoltaic power system [16]–[17].

Different topologies of CSIs have been developed to satisfy various application requirements since the beginning of power electronics. In general, CSIs can be classified into three-level CSIs, multilevel CSIs, parallel CSIs, and SC-CSIs. The three-level CSI can only generate three current levels in each phase (line current) [18]. The typical three-leg CSI is the basic structure of three-level CSIs. Based on this, other topologies such as four-leg CSI [19], five-leg CSIs [20], and current source H7 (CH7) inverters [17] have been developed to improve the inverter performance, including reducing the common-mode voltage (CMV) and improving the reliability. Besides, the output current waveforms of CSIs can be multilevel. Unlike multilevel VSIs (MVSIs) which have been widely studied and commercialized, the research on multilevel CSIs (MCSIs) is a recent subject [21]. The topologies of MCSIs can be classified into single-rating inductor MCSIs, multi-rating inductor MCSIs, paralleled H-bridge MCSIs, two-stage MCSI, buck-boost derived MCSIs, Ćuk-derived MCSIs, and current source modular multilevel converter (CS-MMC) [21]. Among them, the topologies of single-rating inductor, multi-rating inductor, and paralleled

H-bridge MCSIs are developed from classical MVSIs by applying the principle of duality [21]. The two-stage MCSI consists of a three-level DC-DC boost converter stage and an Hbridge inverter stage [21], which is a single-phase inverter. Thus, it will not be discussed in this thesis. The main advantages of MCSIs are the improved output power quality and the reduced current stress of the switching devices [22]. In MCSIs, many topologies can be seen as parallel CSIs since several CSI modules are connected in parallel to increase the number of the levels of the output current waveforms. Besides, parallel CSIs are also used in applications with high power ratings due to the increased power handling capability of the inverter [23]–[25]. Apart from parallel CSIs, two or more CSIs can also be connected in series [9], [25]–[32] to increase the power rating of the inverter. To the best of the author's knowledge, three types of SC-CSIs have been developed so far.

This chapter starts with a review of the CSI topologies, including three-level CSI, multilevel CSIs, parallel CSIs, and SC-CSIs. Then the power losses of SC-CSIs are discussed, and the objectives of the dissertation are defined.

## **1.1 Current source inverter topology**

According to the number of the levels of the inverter output current, CSIs can be divided into three-level CSIs and multilevel CSIs. Besides, two or more CSIs can be connected in parallel or in series to increase the power rating of the inverter. Based on the connection manner, CSIs can be classified into single CSI, parallel CSIs, and SC-CSIs.

#### **1.1.1 Three-level current source inverter**

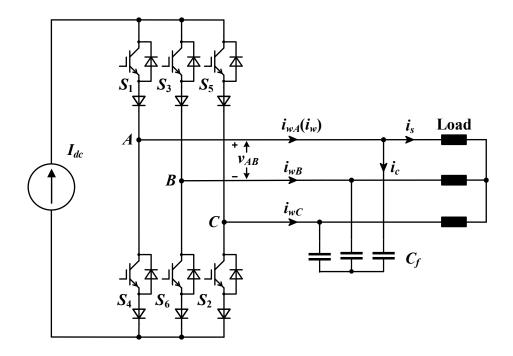

Figure 1-1 shows the configuration of a conventional three-phase current-source inverter with a three-phase balanced load [3]. It is the typical topology in CSIs. The function of the CSI is converting the DC current to a defined three-phase PWM output current  $i_w$ . The DC side of the CSI is a stiff DC current source  $I_{dc}$ . In practice, the DC current source  $I_{dc}$  can be obtained by a current source rectifier (CSR), and a DC choke is needed to make the DC current smooth and continuous. The inverter consists of six switching devices which are composed of insulated-gate bipolar transistors (IGBTs) series connected with diodes. By using an appropriate switching control strategy, the frequency and the magnitude of the output current can be controlled. The inverter output has three current levels in each phase (line current). Normally, a three-phase capacitor  $C_f$  is employed at the output side to assist the commutation of the switching devices and filter out the harmonics in the output current.

Figure 1-1 The typical three-phase PWM current source inverter [3].

CSIs use switching devices with self-extinguishable capability and these switching devices must have bipolar voltage blocking capability. Before the advent of gate commutated thyristors (GCTs), symmetric gate turn-off thyristors (GTOs) were the main switching device for CSIs. They were gradually replaced by symmetric gate commutated thyristors (SGCTs) which were developed from GTO devices with improved switching characteristics and lower losses. However, SGCTs can hardly be found in the current market. IGBTs and power MOSFETs are advanced switching devices with superior switching characteristics. Both of them need to be connected with diodes in series when used for CSIs. The series-connected diodes provide the reverse voltage blocking capability. Nevertheless, the voltage ratings of power MOSFETs are comparatively low, which limits the application of power MOSFETs. By contrast, the voltage ratings of IGBTs can reach

6500 V [39]. Therefore, IGBTs series-connected with diodes become a promising switching device for CSIs in high power MV applications.

The CSI exhibits several advantages compared with VSIs. It features a simple converter topology since the antiparallel freewheeling diodes are not needed for switching devices. Besides, the high switching dv/dt issue in VSIs does not exist in CSIs. The output current and voltage waveforms are close to sinusoidal after being filtered by the capacitor. Furthermore, it has inherent reliable overcurrent and short-circuit protection because the rate of rising of the DC current is limited by the dc choke, which provides sufficient time for protection circuits to work once a short circuit happens at the output terminals. However, the dynamic performance of CSIs is limited since the DC current cannot be changed instantaneously during transients.

#### **1.1.2 Multilevel current source inverter**

MCSIs use a couple of inductors to divide the input current into several equal parts to generate multilevel output currents. The topologies of MCSIs can be classified into singlerated inductor MCSIs, multi-rating inductor MCSIs, paralleled H-bridge MCSIs, two-stage MCSIs, buck-boost derived MCSIs, Cuk-derived MCSIs, and CS-MMCs. Figure 1-2 shows a five-level single-rating inductor MCSI [35]. It is composed of two modules to generate five-level output current waveforms. The number of the output current levels can be increased by employing more modules. The input DC current is equally shared in these modules. There are two inductors used in each module to smooth the current in the module and provide equal impedance among phases. And all the inductors in this topology have the same current rating. The high current capacity, low conduction losses, and good harmonics performance are the main advantages of this topology [21]. However, the unbalancing of the inductor currents is one issue in these modules. Several solutions have been proposed to deal with this issue by improving the modulation schemes or control [33]-[34]. Another challenge is the great number of inductors make the inverter bulky. An improved configuration of the five-level single-rating inductor MCSI is shown in Figure 1-3 [35]. The modified topology employs interphase inductors to replace the single-rating inductors leading to the reduction of current ripples and overall system size.

Figure 1-2 Three-phase five-level single-rating inductor CSI with four inductors of the same rating [35].

Figure 1-3 Five-level single-rating inductor CSI with two interphase inductors [35].

The topology of a three-phase multi-rating inductor MCSI is shown in Figure 1-4 [22]. It consists of two H6 CSI modules with two multi-rating inductors and can produce fivelevel current waveforms at the ac output side. The number of the output current levels can be increased by adding more modules and inductors. In this topology, the DC current is divided into different current ratings by these inductors. The inductor current balancing is also an issue in three-phase multi-rating inductor MCSIs. The imbalanced currents can be caused by the mismatched resistances of the inductors. The problem can be solved by utilizing an appropriate modulation technique or applying closed-loop control techniques [36].

Figure 1-4 Three-phase five-level CSI with two multi-rating inductors [22].

The paralleled H-bridge topology is shown in Figure 1-5 [22]. It is different from the single-rated inductor MCSI and the multi-rating inductor MCSI since it utilizes independent current sources. Therefore, the circulating current and current imbalance issues do not exist in this topology [37]. However, it is complicated to derive multiple current sources, particularly in drive applications [21].

Figure 1-5 Three-phase paralleled H-bridge five-level CSI [22].

Buck-boost derived CSIs are one of the emerging topologies of MCSIs. Different from other MCSIs which aspire to boost the voltage, this topology utilizes the buck-boost technique to extend the operating range. As shown in Figure 1-6 [38], The five-level buck-boost derived CSI consists of a voltage source and two inductors with two CSIs. Two additional semiconductor devices  $S_W$  and  $S_{W'}$  are employed to isolate the input dc rails preventing the current circulation between the two CSIs.

Figure 1-6 Three-phase five-level buck-boost derived multilevel CSI [38].

The two switching devices are turned on or off simultaneously, which leads to discontinuous inductive charging. When they are both turned on, the inductors are charged by the voltage source charges simultaneously resulting in no current flowing through the inverters. When they are both turned off, the proposed CSI can operate in voltage-buck or voltage-boost state as designed, and the circuit operates like the directly cascaded inverter [38]. One advantage of this topology is the dc-link inductor currents are naturally balanced within each switching cycle without additional hardware or control manipulation [22].

Furthermore, the number of the components can be reduced by removing the switch  $S_{W}$  with applying the alternative phase opposition disposition (APOD) modulation [38]. Both input and output performances are not degraded. The modified topology is shown in Figure 1-7 [38].

Figure 1-7 Modified five-level buck-boost derived multilevel CSI [38].

To further enhance the current buck-boost capability, the single voltage source can be replaced by a current source parallel-connected with a capacitor which stores inductive charging energy for DC current boosting. This topology is denominated as Ćuk-derived five-level CSI and is shown in Figure 1-8 [38]. The operational principle for the rear-end inverters in this topology is the same as that in the buck-boost derived CSI, whereas the current boost principles are different [38]. When the switching device  $S_W$  is off, the current source would charge the capacitor. When  $S_W$  is on, both the input current and the capacitor current flow through inductors. Therefore, the current stress of the front-end voltage source and the series inductor can be reduced, which is the advantage of this topology [38].

Figure 1-8 Ćuk-derived five-level CSI [38].

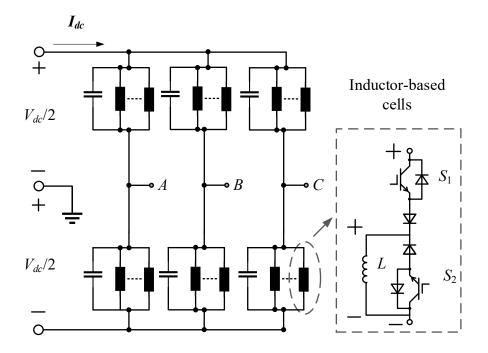

The CS-MMC is another topology of MCSIs. Several inductor-based cells are employed in this topology and connected in parallel to produce multilevel output waveforms as shown in Figure 1-9 [35]. The advantage of this topology is its high-power operation capability. However, this topology is costly due to a great number of power devices and inductors.

Figure 1-9 Three-phase CS-MMC topology with its inductor-based cells [35].

## **1.1.3 Parallel current source inverters**

In MCSIs, parallel connection is a way to produce more levels of the output current waveforms and improve the power quality. All the topologies mentioned in MCSIs in this thesis can be seen as parallel CSIs. Those topologies connect several CSI modules in parallel except the CS-MMC which utilizes several paralleled inductor-based cells on each arm. Parallel CSIs can also produce three-level output currents by using adequate modulation schemes. Apart from increasing the number of the levels of the output current waveforms to reduce harmonics, the parallel connection also increases the power rating of the inverter since the current stress of the switching devices is shared. The DC source in parallel CSIs can be a single input DC source or several independent input DC sources. One example of the parallel CSIs using two independent current sources is the three-phase paralleled H-bridge five-level CSI which has been shown in Figure 1-5. Different from the topology

presented in Figure 1-5. A new configuration of three-phase parallel CSIs which only employs a single input DC source is shown in Figure 1-10. In this topology, every inverter has its own DC choke. A three-phase filter capacitor is shared by the two inverters at the output. The values of the DC choke must be identical to promise the balanced currents in two inverters.

Figure 1-10 Parallel current source inverters with a three-phase load [3].

Parallel CSIs are suitable for high power applications with high current levels. They can be adopted in uninterruptable power system (UPS) applications, such as high-speed elevators, high power electric drives, and distributed generation systems, due to the increased power rating, improved fault tolerance, and high reliability [40]-[43]. However, in practice, unbalanced dc currents are one of the main issues in parallel CSIs. It can be caused by several reasons, including unequal on-state voltages of the semiconductor devices, variations in time delay of the gating signals of the two inverters, and manufacturing tolerance in dc choke parameters. This problem can be solved by using the SVM-based DC current balance control algorithm [23]. And the circulating current may exist in this topology due to the common input DC source. Besides, the CMV and commonmode (CM) resonances are also the challenges in parallel CSIs. Unfortunately, most methods of CMV suppression reported in the literature focus on single CSI and are not valid for parallel CSIs. Few studies have been done in the literature [24].

#### **1.1.4 Series-connected current source inverters**

In addition to the parallel operation for high power applications, several CSIs can also be connected in series to form SC-CSIs to increase the power rating and DC voltage level of the inverter. SC-CSIs have been studied in CSC-based offshore wind farm systems. So far, three topologies of SC-CSIs have been developed in the literature.

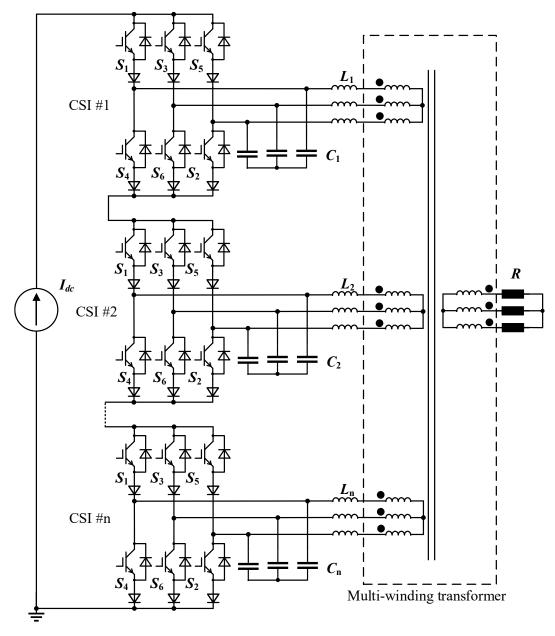

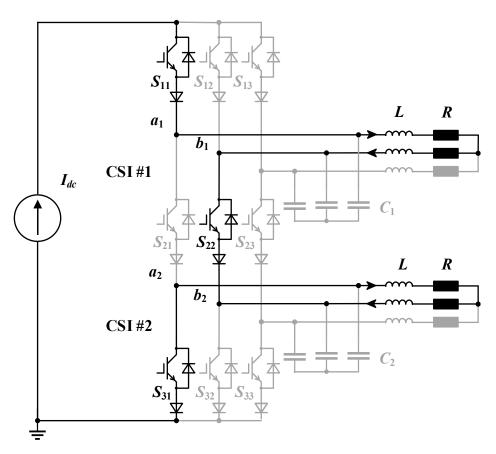

#### (a) Topology A

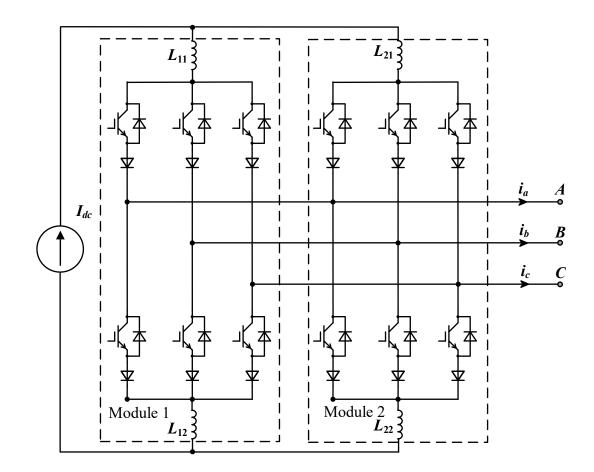

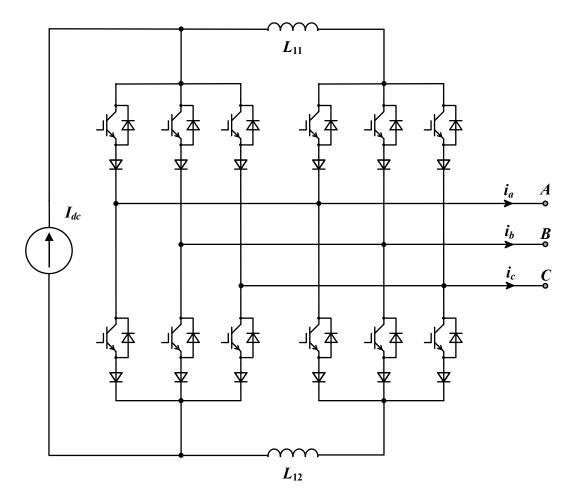

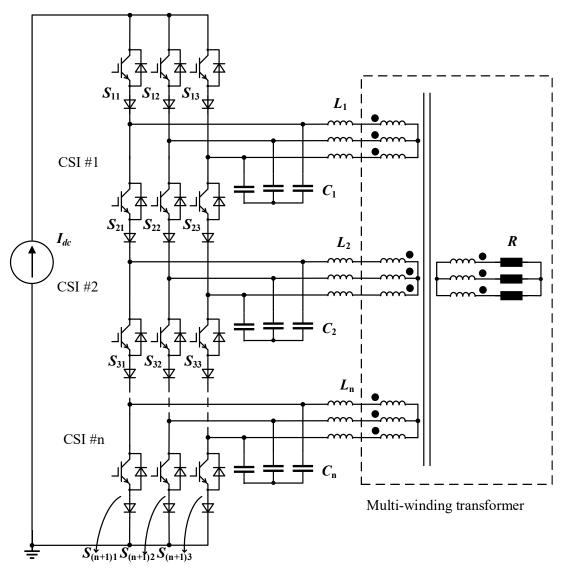

As shown in Figure 1-11 [31], several identical CSIs are connected in series composing topology A [9], [29]. These CSIs are identical in terms of topology, modulation, and control. Each CSI consists of six switches. The total number of the switches employed in topology A which is constructed by *n* CSIs is 6*n*. The switching frequency of these switches depends on the power rating of each CSI and the employed switching device. For high power applications, such as high-power (megawatt-level) MV drives, the switching frequency is usually limited to around 500 Hz [1]. Besides, a multi-winding transformer is required at the output. The functions of the multi-winding transformer are providing a clear current path for each CSI and stepping up the voltage if necessary.

Figure 1-11 Topology A of SC-CSIs [31].

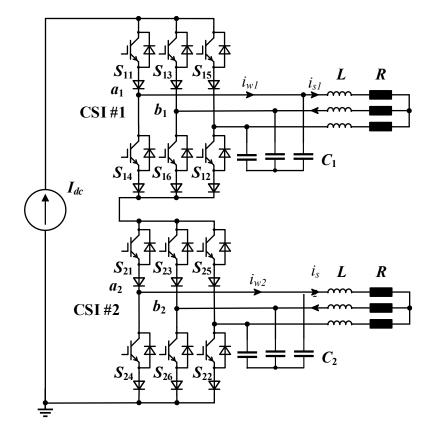

#### (b) Topology B

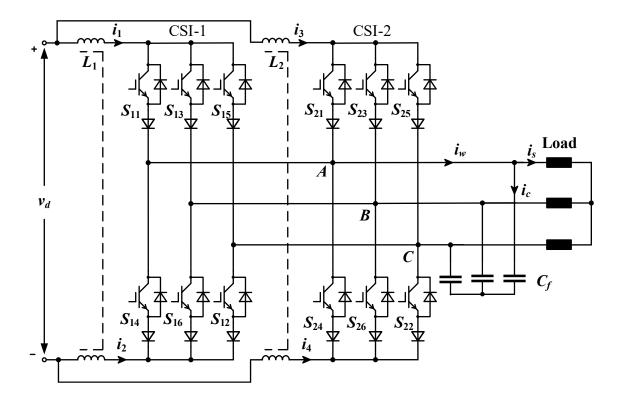

In [31], A SC-CSIs with a switching frequency of 60 hertz was proposed. The configuration of this topology is shown in Figure 1-12 [31]. Compared with topology A, the switching frequency of the switches used in topology B is decreased to 60 Hz. However, the low switching frequency results in significant low-order harmonics in the output PWM currents. The significant low-order harmonics can be filtered out by using the combination

of phase-shifting modulation and the phase-shifting transformer. Besides, the LC filter is reduced by utilizing the phase-shifting transformer to eliminate the harmonics. And a reduction in the DC inductor is realized because of the phase-shifting modulation.

Compared with topology A, topology B has several advantages, including lower switching losses, a higher DC current utilization, and reduced passive components. However, the phase-shifting transformer has a complicated winding connection which may increase the cost. Besides, the input current  $I_{dc}$  cannot be controlled by the proposed modulation scheme.

Figure 1-12 SC-CSIs with switching frequency of 60 hertz (topology B) [31].

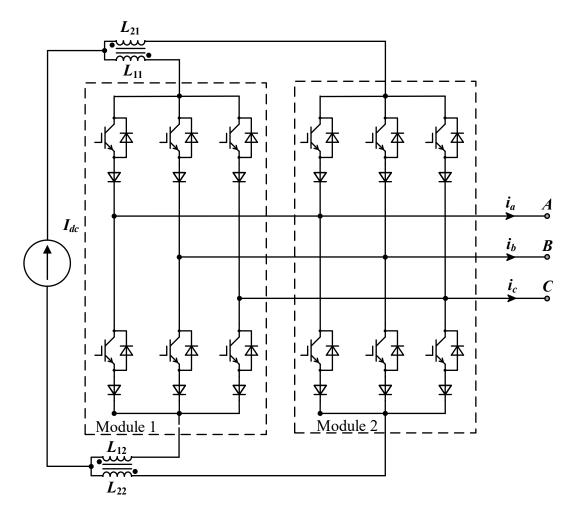

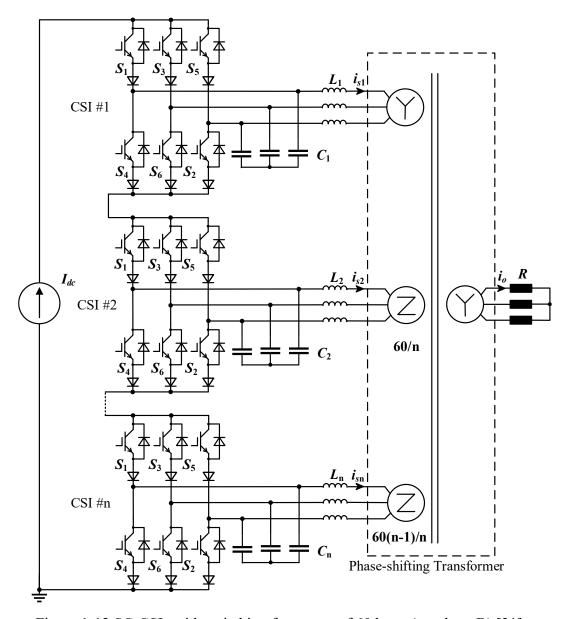

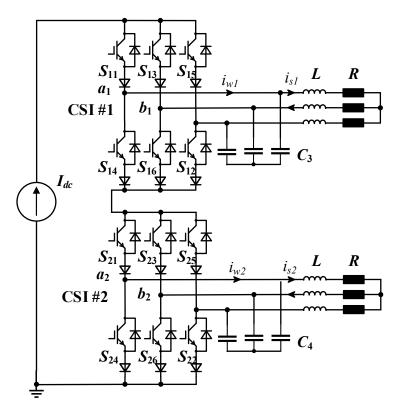

(c) Topology C

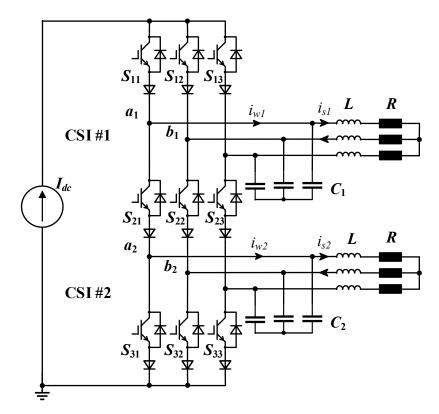

To reduce the number of switching devices, a new topology using fewer switches with a developed modulation scheme was proposed in [32]. The configuration of this topology is presented in Figure 1-13 [32]. In topology C, each CSI is composed of six switches, and adjacent two CSIs share three switches. For example, shown in Figure 1-13, CSI#1 is constructed by the switches  $S_{11}$ ,  $S_{12}$ ,  $S_{13}$ ,  $S_{21}$ ,  $S_{22}$ , and  $S_{23}$ , and CSI#2 is formed by the switches  $S_{21}$ ,  $S_{22}$ ,  $S_{23}$ ,  $S_{31}$ ,  $S_{32}$ , and  $S_{33}$ . The switches  $S_{21}$ ,  $S_{22}$ , are shared by CSI#1 and CSI#2. Due to this arrangement, the total number of the employed switches is reduced from 6n ( $n \ge 2$ ) in topology A to 3(n+1) in topology C.

However, the output currents of any two adjacent CSIs have a phase shift of 180° due to the developed modulation scheme. This phase shift can be eliminated by employing a multiwinding transformer that has a different configuration of the inverter-side transformer windings at the output. This transformer is the same as the transformer used in topology A except for the connection of the inverter-side windings. After the transformer, the currents are in phase. Compared with topology A, topology C features fewer switches and lower complexity. The comparison among the three topologies of SC-CSIs is shown in Table 1-1.

Figure 1-13 Topology C of SC-CSIs [32].

| Table 1-1 The | comparison | among the | three topologies | of SC-CSIs |

|---------------|------------|-----------|------------------|------------|

|               |            |           |                  |            |

|                           | 1             | 1 0            |                       |  |

|---------------------------|---------------|----------------|-----------------------|--|

| Aspect                    | Topology A    | Topology B     | Topology C            |  |

| The number of switches    | 6 <i>n</i>    | 6 <i>n</i>     | 3( <i>n</i> +1)       |  |

| (involving <i>n</i> CSIs) | 01            | 01             | S(n+1)                |  |

| Output current            | In phase      | In phase       | 180° phase shift      |  |

| Sulput current            | in phase      | in phase       | between adjacent CSIs |  |

| Transformer type          | Multi-winding | Phase-shifting | Multi-winding         |  |

| Switching frequency       | Around 500 Hz | 60 Hz          | Around 500 Hz         |  |

## **1.2 Power losses of SC-CSIs.**

Among various CSIs, SC-CSIs are suitable for applications with high power ratings and high DC voltage levels. In high power applications, power losses are one of the important attributes of SC-CSIs since they have a significant impact on the efficiency of the system. The fewer power losses of the SC-CSIs lead to the higher efficiency of the system, which can lower the operation cost. Besides, it is very important to figure out the power loss distribution of SC-CSIs to design an appropriate cooling system.

The power losses of SC-CSIs can be influenced by several factors, including the conduction current, the line-to-line voltage, the switching frequency, the modulation scheme, the modulation index, and the characteristics of the switching device, such as the saturation voltage and the turn-on and turn-off energy losses. Some of these factors are different in the three topologies of SC-CSIs, which can result in different total power losses and power loss distributions. Therefore, SC-CSIs in different topologies probably have different efficiencies and power loss distributions.

## **1.3 Dissertation objectives**

As mentioned earlier, the power losses of SC-CSIs are one of the important parameters in high power applications since they are not only related to the efficiency of the system but also crucial for cooling system design. Different topologies of SC-CSIs probably result in different total power losses and power loss distributions. However, it has not been studied which topology of SC-CSIs has the fewest total power losses. Therefore, this thesis aims at investigating the power losses of SC-CSIs and finding out the topology and the modulation scheme that have the best performance in terms of efficiency.

The main objectives of this dissertation are summarized as follows:

(1) Power loss investigation of SC-CSIs.

In Chapter 2, the power losses of the switching device (IGBTs series connected with diodes) will be analyzed. The factors that can influence the power losses of SC-CSIs will be discussed in detail and will be compared in the three topologies of SC-CSIs. The power

loss distribution of each topology will be analyzed. The power losses and the efficiencies of the SC-CSIs in these three topologies will be compared under one typical modulation scheme.

(2) Power loss investigation of SC-CSIs with different modulation schemes.

In Chapter 3, three typical PWM modulation schemes are introduced, including trapezoidal pulse width modulation (TPWM), selective harmonic elimination (SHE), and space vector modulation (SVM). How different modulation schemes influence the power losses of SC-CSIs will be investigated. The power losses and the efficiencies of the SC-CSIs with different modulation schemes will be compared in the three topologies. The topology and the modulation scheme with the lowest power losses will be found out and recommended.

# **Chapter 2 Power Loss Investigation of Series-Connected Current Source inverters**

As mentioned in the previous chapter, power losses are an important attribute of SC-CSIs because they directly affect the efficiency of the system. Besides, it is crucial to figure out the power loss distribution of SC-CSIs to design an appropriate cooling system. So far, three topologies of SC-CSIs have been developed. However, the power losses of SC-CSIs have not been studied yet. Therefore, the objective of this chapter is to investigate the power losses of the SC-CSIs in these three topologies.

This chapter starts with an introduction of the power losses in the switching device, IGBTs connected with diodes in series. Then analyzing the factors that can influence the power losses of the switching device. Each factor is investigated and compared in the three topologies in detail. Finally, the power losses of the SC-CSIs in each topology are analyzed in a comparative method. And the power loss distribution of topology C is figured out. Simulation results are provided to assist and verify the analysis.

## 2.1 Power losses of IGBTs and diodes

The losses in a semiconductor component, such as an IGBT or a diode, can be classified into conduction losses, switching losses, and blocking (leakage) losses. The blocking losses are normally neglected since the leakage current is negligibly small during the off-state of the device [44]. Only conduction losses and switching losses are considered in the power losses of IGBTs and diodes. Therefore, the total power losses of a switching device are the sum of the conduction losses and the switching losses of the IGBT and the diode.

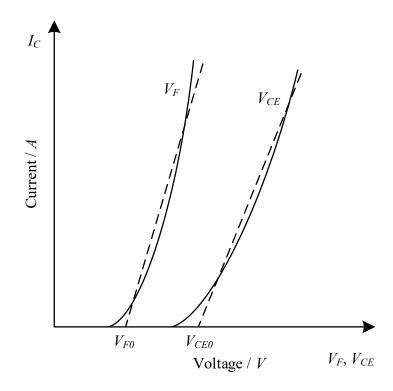

## 2.1.1 Conduction losses

Conduction losses are the losses that occur when a semiconductor device is on-state and conducting current. The value of the conduction losses is based on the output characteristic

of the device [45]. The instantaneous value of the conduction losses in an IGBT or a diode can be calculated by [52]

$$P_{CON}(t) = V_{ON}(t) \times I_C(t)$$

(2-1)

where  $V_{ON}$  is the on-state saturation voltage of the device and  $I_C$  is the conduction current. The on-state saturation voltage of an IGBT can be approximated as a DC voltage source, which represents the IGBT on-state zero-current collector-emitter voltage  $V_{CE0}$ , connected with a collector-emitter on-state resistance  $R_C$  in series. Therefore, the on-state saturation voltage of an IGBT  $V_{CE}$  can be approximated as a linear function of the conduction current [52]

$$V_{CE}(I_C) = V_{CE0} + R_C \times I_C \tag{2-2}$$

The same approximation can be used for the series-connected diode [52]

$$V_F(I_C) = V_{F0} + R_D \times I_C$$

(2-3)

where  $V_F$  is the forward on-state voltage of the diode,  $V_{F0}$  is the zero-current on-state voltage, and  $R_D$  is the on-state resistance of the diode.

Figure 2-1 Typical output characteristics of IGBTs and diodes [45].

The relation between the instantaneous values of the on-state saturation voltage and the conduction current is the output characteristic of the IGBT or the diode. The typical output characteristics of IGBT and diode are shown in Figure 2-1 [45]. The instantaneous value of the IGBT conduction losses  $P_{CI}$  and the instantaneous value of the diode conduction losses  $P_{CD}$  can be calculated by [52]

$$\begin{cases} P_{CI}(t) = V_{CE}(t) \times I_{C}(t) = V_{CE0} \times I_{C}(t) + R_{C} \times I_{C}^{2}(t) \\ P_{CD}(t) = V_{F}(t) \times I_{C}(t) = V_{F0} \times I_{C}(t) + R_{D} \times I_{C}^{2}(t) \end{cases}$$

(2-4)

Therefore, the average value of IGBT conduction losses  $P_{Clav}$  and the average value of the diode conduction losses  $P_{CDav}$  are [52]

$$\begin{cases} P_{Clav} = \frac{1}{T} \int_{0}^{T} P_{Cl}(t) dt = V_{CE0} \times I_{Cav} + R_{C} \times I_{Crms}^{2} \\ P_{CDav} = \frac{1}{T} \int_{0}^{T} P_{CD}(t) dt = V_{F0} \times I_{Cav} + R_{D} \times I_{Crms}^{2} \end{cases}$$

(2-5)

where  $I_{Cav}$  is the average value of the conduction current, and  $I_{Crms}$  is the rms value of the conduction current. From the equation (2-5), it can be seen that the total average conduction losses of the switching device depend on the duty cycle, the on-state saturation voltage, and the conduction current.

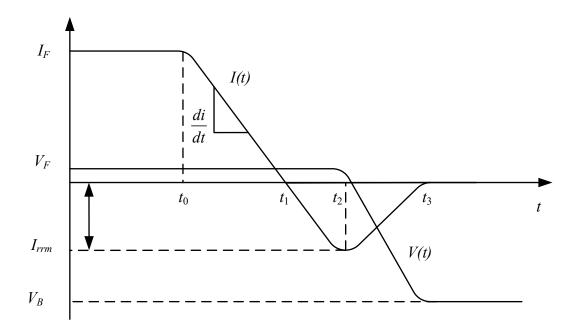

## 2.1.2 Switching losses

Switching losses are the power dissipation of a power device during turn-on and turn-off switching transitions. The IGBT switching losses *P*<sub>SWI</sub> can be calculated by [32]

$$P_{SWI} = (E_{on} + E_{off}) \times F_{sw} \times \frac{V}{V_{nom}} \times \frac{I}{I_{nom}}$$

(2-6)

where  $E_{on}$  is the turn-on energy losses per pulse of the IGBT,  $E_{off}$  is the turn-off energy losses per pulse of the IGBT,  $F_{sw}$  is the switching frequency of the device,  $V_{nom}$  and  $I_{nom}$  are the rated voltage and current of the IGBT, V and I are the instantaneous values during switching/conducting.

Figure 2-2 The typical power diode current and voltage waveforms during turn-off [47].

When calculating the diode switching losses, the turn-on losses are usually neglected in practice, but the turn-off losses also named reverse recovery losses should be considered due to the reverse recovery current caused by the carrier storage effect [46]. The typical power diode current and voltage waveforms during turn-off are shown in Figure 2-2 [47]. The reverse current reaches its maximum  $I_{rrm}$  at  $t_2$ . The diode switching losses  $P_{SWD}$  can be calculated by [45]

$$P_{SWD} = P_{REC} = E_{rr} \times F_{Doff} \times \frac{V_B}{V_{Bnom}}$$

(2-7)

where  $E_{rr}$  is the reverse recovery energy losses of the diode,  $F_{Doff}$  is the diode turn-off frequency,  $V_B$  is the reverse blocking voltage, and  $V_{Bnom}$  is the rated reverse blocking voltage. Sometimes, the reverse recovery energy losses  $E_{rr}$  are not provided. Alternatively, the figure presents the relationship between the reverse recovery charge  $Q_{rr}$  and the current slope di/dt with the forward current  $I_F$  is given. In this way, the reverse recovery losses of diodes can be calculated by [46]

$$P_{REC} = k_E \times V_B \times Q_{rr} \times \frac{S}{S+1} \times F_{Doff}$$

(2-8)

where  $Q_{rr}$  is the recovered charge, S is the reverse recovery softness factor, and  $k_E$  is a constant unique to each circuit that compensates for non-ideal voltage switching waveform. The value of  $k_E$  is decided by not only the characteristics of the diode but also the commutation circuit [46]. If experimental loss values are available,  $k_E$  can be chosen to provide a good match between the calculated and experimental values. If not,  $k_E$  can be assumed a value between 0.5 to 1 [46].

## **2.2 Factors related to power losses**

The power losses of the switching device are decided by the current and voltage waveforms of the IGBT and the diode and can be approximately calculated by using the above equations. Under a certain temperature, the power losses of the switching device can be influenced by several factors. The conduction losses of the SC-CSIs can be influenced by the conduction current and the saturation voltage of the switching devices. The switching losses of the SC-CSIs can be affected by the modulation scheme, the modulation index, the switching frequency, the current and voltage of the switching device when switching, and the turn-on and turn-off energy losses of the switching devices.

## 2.2.1 Modulation scheme

The switching pattern of the switching device is decided by the applied modulation scheme. In other words, the applied modulation scheme determines when the switches should be turned on and off. For high power CSIs operating with a switching frequency of around 500 Hz, three typical PWM schemes have been developed, including TPWM, SHE, and SVM [3]. Different modulation schemes have different principles to generate various gating signals. These different gating signals influence the switching moments and lead to different current and voltage waveforms of the switching device, which can result in different instantaneous values of the voltage on the switching device, which can affect the IGBT switching losses shown in equation (2-6). How the different modulation schemes influence the power losses of SC-CSIs will be analyzed in chapter four in detail. To make

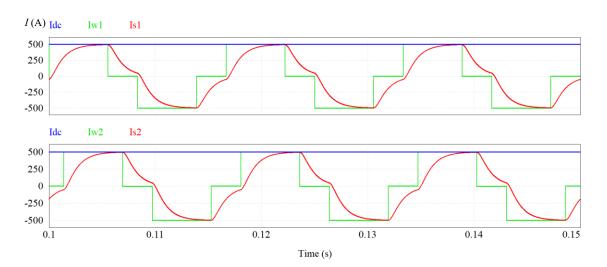

SC-CSIs with different topologies have the same operating conditions, one modulation scheme SVM with switching sequence 1 (SQ1) is used in topology A and C in this chapter. Since topology B operates with a fundamental switching frequency of 60 Hz, the modulation proposed in [31] is adopted in topology B.

## **2.2.2 Modulation index**

Modulation index  $m_a$  is an important part of modulations. It is defined by

$$m_a = \frac{\hat{I}_{w1}}{I_{dc}} \tag{2-9}$$

where  $\hat{I}_{w1}$  is the peak value of the fundamental frequency component in the output PWM current  $i_w$ , and  $I_{dc}$  is the value of the input DC current. The CSI output currents can be directly controlled by adjusting modulation index  $m_a$ . However, this method is rarely used because it causes additional power losses due to the bypass operation [3]. In practice, the CSI output currents are regulated by controlling the input DC current through the front-end rectifiers. Therefore, to lower the power losses, the modulation index  $m_a$  is set to its maximum value of 1 in this thesis.

## 2.2.3 Switching frequency

Switching frequency has a significant impact on switching losses. It can be seen from equations (2-6) and (2-7) that a higher switching frequency results in more switching losses. In the industry, the switching frequency of CSIs for high-power applications is usually limited to around 500 Hz to reduce the switching losses and satisfy the thermal requirements [3]. In this thesis, a switching frequency of 540 Hz is adopted in topology A and topology C. The switching frequency in topology is reduced to 60 Hz as introduced in Chapter 1.

## 2.2.4 Conduction current

As shown in equations (2-5) and (2-6), both the conduction losses and the switching losses of a switching device can be affected by the conduction current  $I_c$ . The power losses

of the SC-CSIs will increase if raising the conduction current. In the three topologies of SC-CSIs, all the CSIs are connected in series and every CSI satisfies the switching constraint to operate normally. At any instant of time (excluding commutation intervals) only two switches are conducting in a CSI, one in the top half of the bridge and the other in the bottom half [3]. Therefore, every switching device in these three topologies has the same conduction current, which is equal to the dc-link current  $I_{dc}$ .

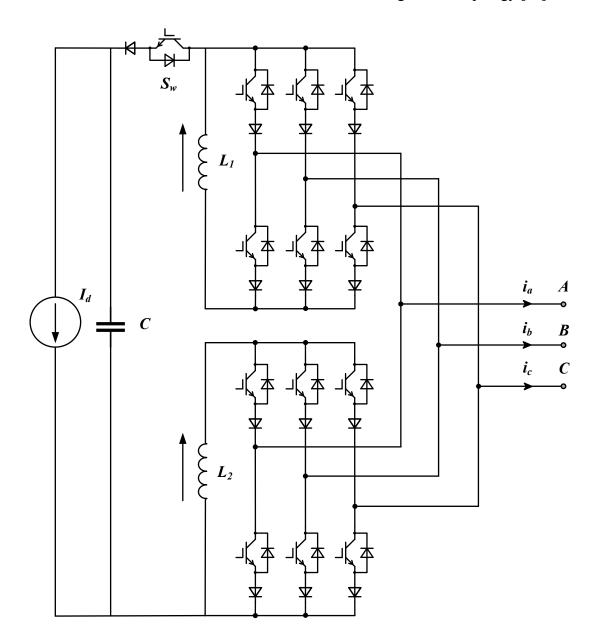

## 2.2.5 Voltage stress of the switching devices

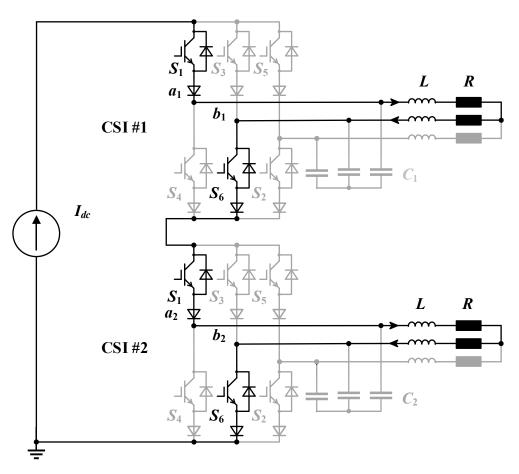

Switching devices will produce more switching losses when they are suffering higher voltage stress during switching/conducting. This can be seen from equations (2-6) and (2-7). To illustrate the voltage stress of the switches in these topologies, the equivalent circuits of topology A and topology C under one switching state are presented. The equivalent circuit of topology B is the same as topology A. The voltage stress of these switching devices under other switching states is the same as the one illustrated here.

As shown in Figure 2-3, switches  $S_1$  and switches  $S_6$  are conducting. The voltage stress of the switch  $S_3$  in CSI # 1 is  $V_{a1b1}$ . In CSI # 2, the voltage stress of the switch  $S_3$  is  $V_{a2b2}$ . Since the CSIs are identical in topology A, they have the same output line-to-line voltage.

$$V_{a1b1} = V_{a2b2} = V_{anbn} \tag{2-10}$$

Therefore, all the switches  $S_3$  have the same voltage stress, which is the output line-toline voltage. The same conclusion can be found in other switches in topology A under different switching states. Since all the switches in topology A have the same voltage stress, conduction current, and switching frequency, they generate the same power losses. The same conclusion can be found in topology B.

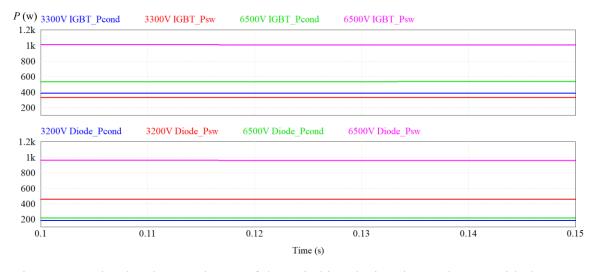

The equivalent circuit of topology C is shown in Figure 2-4. The voltage stress of the switches on the first and last rows ( $S_{11}$ ,  $S_{12}$ ,  $S_{13}$  and  $S_{31}$ ,  $S_{32}$ ,  $S_{33}$ ) is the same as that in topology A, which is also the output line-to-line voltage. However, the voltage stress of the inner switches in topology C is double. For instance, the voltage stress of the switch  $S_{12}$  in topology C is  $V_{a1b1}$ , which is the output line-to-line voltage. The voltage stress of the switch  $S_{21}$  in topology B is  $V_{a1a2}$ . Note that there is a 180° phase shift between any two adjacent

CSIs in topology C due to the modified modulation scheme. The voltage stress of the switch  $S_{21}$  is the twice output line-to-line voltage. The same result can also be found in any other inner switches in topology C.

$$\begin{cases} V_{a1a2} = V_{a1b1} + V_{b2a2} \\ V_{b2a2} = V_{a1b1} \\ V_{a1a2} = 2V_{a1b1} \end{cases}$$

(2-11)

The identical IGBTs and diodes can be used in topology A and on the first and last rows in topology C due to the same conduction current and voltage stress, whereas the IGBTs and diodes with the double-voltage rating should be chosen as the inner switches in topology C since the voltage stress of its inner switches is twice that of other switches.

Figure 2-3 The equivalent circuit of SC-CSIs in topology A [32].

Figure 2-4 The equivalent circuit of SC-CSIs in topology B [32].

## 2.2.6 Characteristics of the switching device

As analyzed before, the conduction losses of IGBTs and diodes are related to their output characteristics. Besides, the switching losses of IGBTs can be affected by the turn-on and turn-off energy. And the switching losses of diodes can be influenced by the reverse recovery energy. Under the same current rating, switching components with a higher voltage rating usually have a higher saturation voltage  $V_{on}$ . Nevertheless, the saturation voltage  $V_{on}$  of the IGBT with the double voltage rating is less than twice that of the IGBT with the original voltage rating. This can also be found in power diodes. The value of  $V_{on}$  is ranging from 3 to 4.2 V for 6600 V IGBTs, 2.4 to 3.28 V for 3300 V IGBTs, and 1.95 to 2.45 V for 1700 V IGBTs [39].

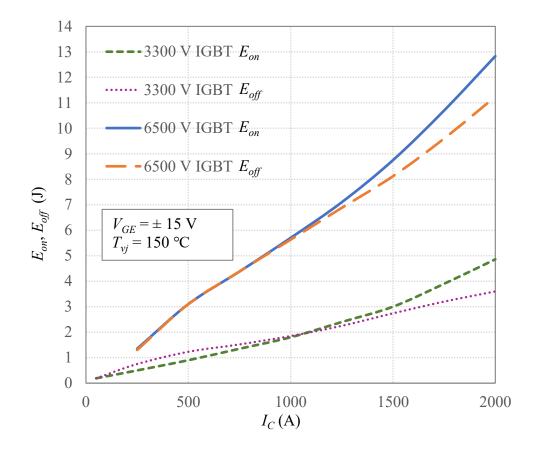

However, the turn-on energy losses  $E_{on}$  and the turn-off energy losses  $E_{off}$  of the IGBT with the double voltage rating are approximately three to six times that of the IGBT with the original voltage rating. For example, a comparison of turn-on energy losses  $E_{on}$  and the

turn-off energy losses  $E_{off}$  between a 3300 V IGBT and a 6500 V IGBT is shown in Figure 2-5 [49], [50]. The IGBTs have the same current rating of 1000 A. With a conduction current  $I_c$  of 500 A, the sum of the turn-on energy losses  $E_{on}$  and the turn-off energy losses  $E_{off}$  of the 6500V IGBT is around 6.1 J, which is approximately triple that of the 3300V IGBT. Furthermore, the recovered charge  $Q_{rr}$  of the diode with the double-voltage rating is usually more than that in the diode with the original voltage rating.

Figure 2-5 The turn-on energy losses  $E_{on}$  and the turn-off energy losses  $E_{off}$  of the IGBTs [49], [50].

## 2.3 Total power losses and power loss distribution

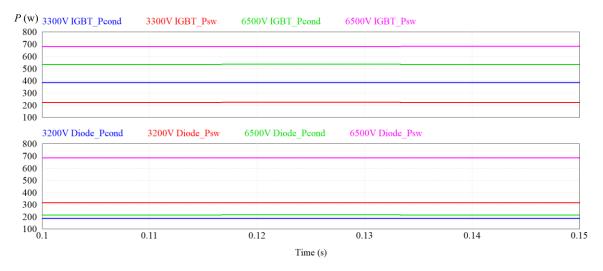

Under the same operating conductions, the factors analyzed above are the same in topology A and topology B except modulation schemes and switching frequencies. The switching devices are identical in topology A and topology B with the same conduction current and duty cycle. Thus, topology B has the same conduction losses as topology A. Whereas the switching losses are reduced by nine times in topology B since the switching frequency is reduced from 540 Hz in topology A to 60 Hz in topology B. The power losses of topology B can be figured out if knowing the conduction losses and switching losses of topology A. Therefore, the following analysis is mainly focusing on the comparison between topology A and topology C.

When the SC-CSIs in topology A and topology C operate under the same conditions, every switch on the first and last rows in both topology A and topology C produces the same power losses. However, the total power losses of the inner switches in these two topologies are different because of the different voltage stresses, characteristics, and quantities. Therefore, to compare the total power losses of these topologies, the power losses of inner switches are crucial.

## 2.3.1 Total power losses comparison

Firstly, the total conduction losses of the inner switches in topology C are fewer than that in topology A. This is because:

1) The number of the inner switches is halved in topology C.

2) The saturation voltage  $V_{on}$  of the switch with the double-voltage rating is less than twice that of the switch with the original voltage rating.

Secondly, the total switching losses of the inner switches in topology C are more than that in topology A. The reasons are:

1) The number of inner switches is halved in topology C.

2) The voltage stress of each inner switch in topology C is twice that of any inner switch in topology A.

3) The turn-on energy losses  $E_{on}$  and the turn-off energy losses  $E_{off}$  of the IGBT with the double voltage rating are approximately three to six times that of the IGBT with the original voltage rating when they have the same current rating. Moreover, the recovered charge  $Q_{rr}$  of the diode with the double voltage rating is more than that in the diode with the original voltage rating.

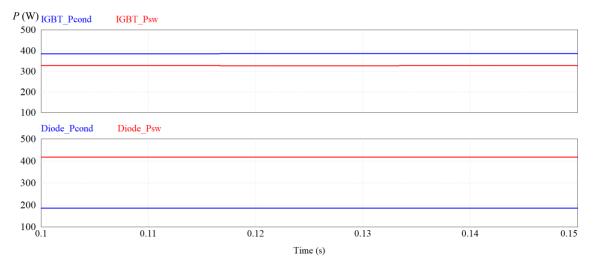

## 2.3.2 Power loss distribution

In topology A, every switch has the same power losses since they are identical and have the same condition current, voltage stress, and switching frequency. The same power loss distribution can be found in topology B. However, the power loss distribution in topology C is different. In topology C, every inner switch generates more power losses than any switch on the first and last rows. This is because the voltage stress of the inner switch is doubled. Moreover, the inner switch has a higher saturate voltage  $V_{on}$ , more turn-on energy losses  $E_{on}$ , and more turn-off energy losses  $E_{off}$  than the switch on the first and last rows.

## 2.4 Simulation investigation

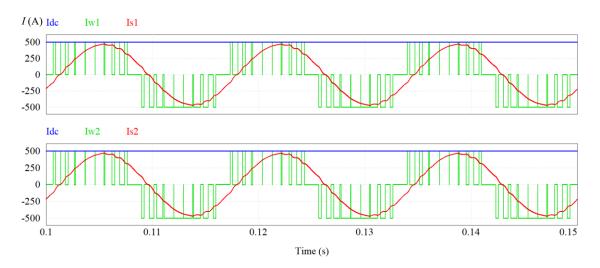

To verify the analysis and compare the total power losses among the SC-CSIs in the three topologies. A simulation investigation is conducted. The simulation models are built based on PSIM\_2021a. The simulation parameters of the SC-CSIs are presented in Table 2-1. Each SC-CSIs consists of two PWM CSIs, and each CSI is loaded with a three-phase balanced inductive load. The inductors are employed as the leakage inductance from the transformers. Filter capacitors are employed at the output side of each inverter to assist the commutation of the switching devices and filter out harmonics. The filter capacitor is larger in topology B to filter out the significant low-order harmonics.

| Parameters                       | Topology A and topology C | Topology B            |

|----------------------------------|---------------------------|-----------------------|

| DC link current (A)              | 500                       | 500                   |

| Line voltage (V <sub>rms</sub> ) | 1150                      | 1150                  |

| Number of CSIs                   | 2                         | 2                     |

| Modulation scheme                | SVM (SQ1)                 | Square-wave operation |

| Modulation index                 | 1                         | 1                     |

| Switching frequency (Hz)         | 540                       | 60                    |

| Resistance (pu)                  | 1                         | 1                     |

| Inductance (pu)                  | 0.1                       | 0.1                   |

| Capacitance (pu)                 | 0.3                       | 0.5                   |

Table 2-1 Simulation parameters of the SC-CSIs

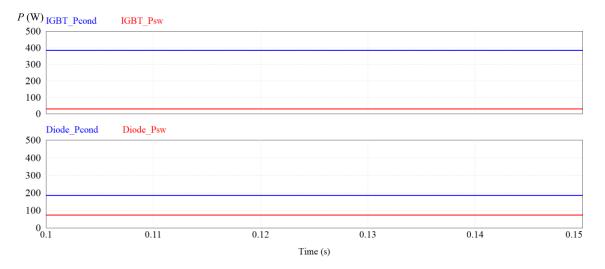

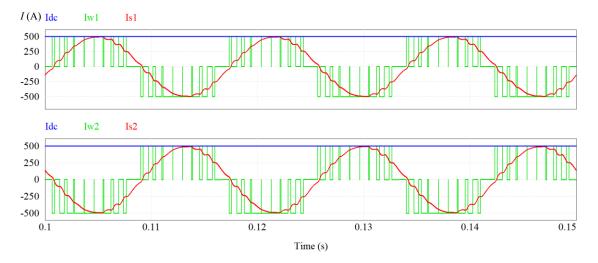

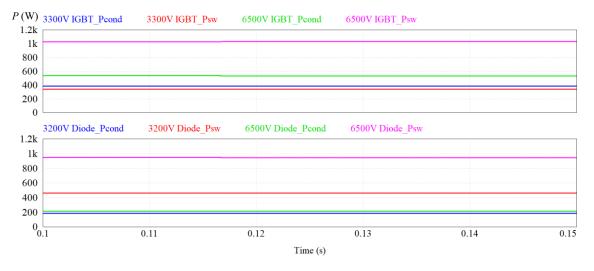

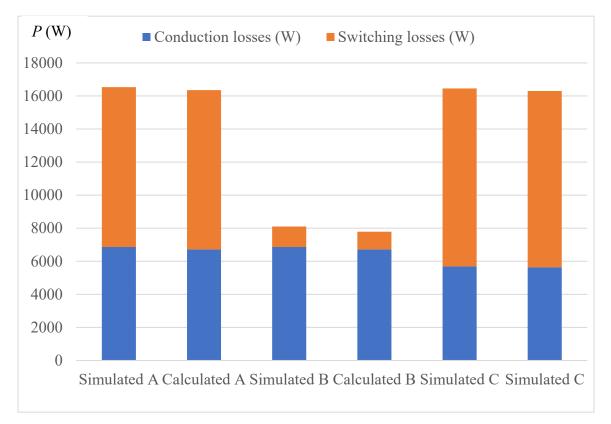

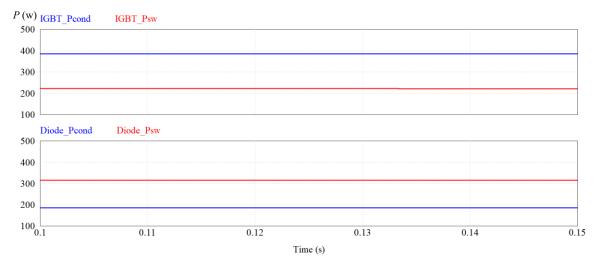

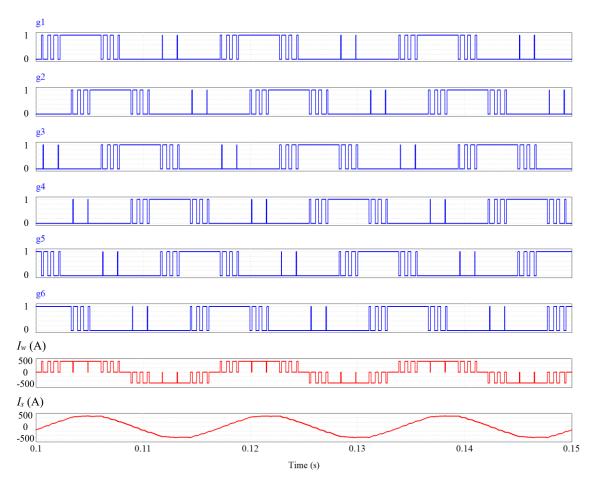

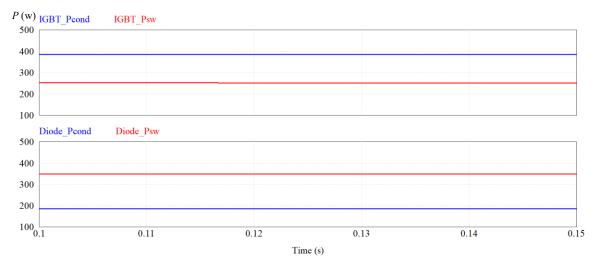

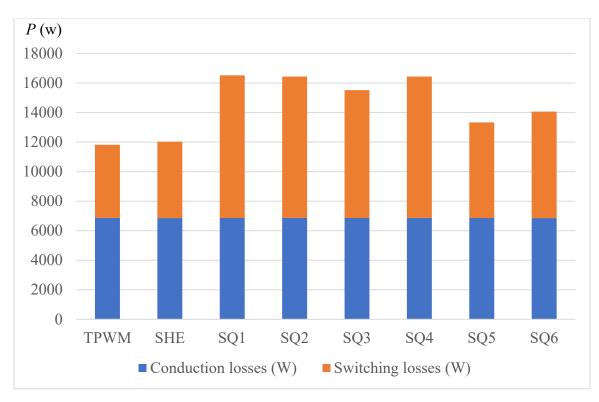

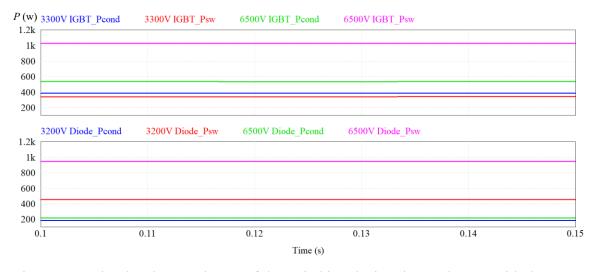

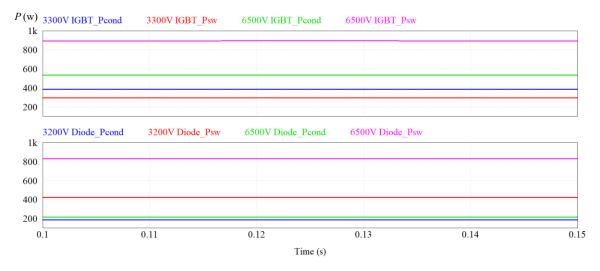

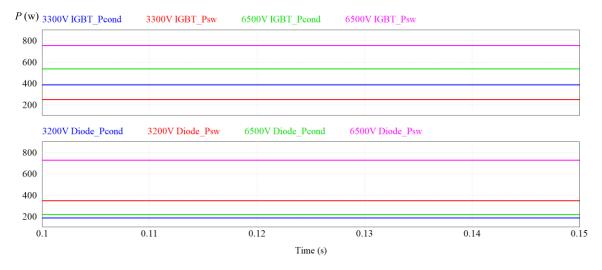

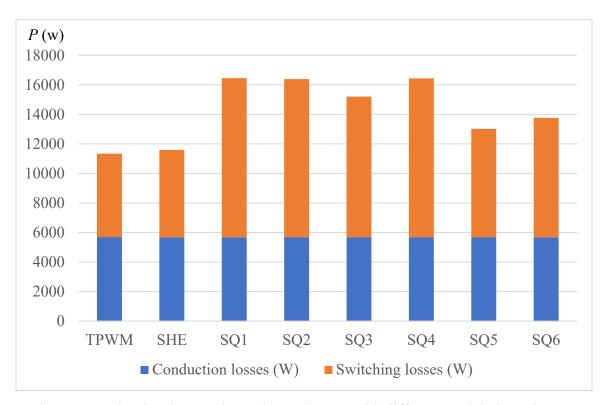

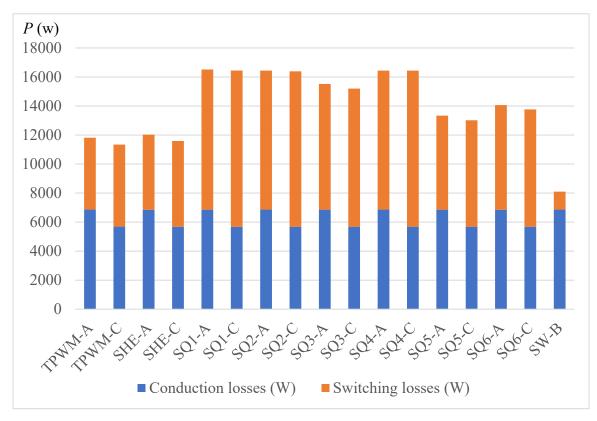

The parameters are the same in each topology to promise the SC-CSIs in the three topologies operating under the same conditions except the filter capacitance, the modulation scheme, and the switching frequency in topology B since topology B operates with a switching frequency of 60 Hz. The SVM (SQ1) scheme is used in topology A and topology C. The square-wave operation is adopted in topology B.