**Electronic Theses and Dissertations**

Electronic Theses and Dissertations from 2009

2015

# Improving Performance of Transactional Applications through Adaptive Transactional Memory

Jeyakumaran, Thireshan

http://knowledgecommons.lakeheadu.ca/handle/2453/708 Downloaded from Lakehead University, KnowledgeCommons

## Improving Performance of Transactional Applications through Adaptive Transactional Memory

Thireshan Jeyakumaran

Supervisor: Dr. Ehsan Atoofian

Department of Electrical and Computer Engineering Lakehead University

> Thunder Bay, Ontario, Canada Sept, 2015

|       |                       | Lakehead                                                                                  |   |

|-------|-----------------------|-------------------------------------------------------------------------------------------|---|

|       |                       | • OKTOLKOTTI                                                                              |   |

|       | ·                     | FACULTY OF GRADUATE STUDIES                                                               |   |

|       |                       |                                                                                           |   |

|       | NAME OF STUDENT       | r: Thireshan Jeyakumaran                                                                  |   |

|       | DEGREE:               | ECE                                                                                       |   |

|       | ACADEMIC UNIT:        |                                                                                           |   |

|       | TITLE OF THESIS:      | Improving Performance of Transactional Applications through Adaptive Transactional Memory | ĩ |

|       |                       |                                                                                           |   |

|       |                       |                                                                                           |   |

|       |                       | This thesis has been prepared                                                             |   |

|       |                       | under my supervision and                                                                  |   |

|       |                       | the candidate has complied with                                                           |   |

|       |                       | the Master's thesis process regulations.                                                  |   |

|       |                       | A                                                                                         |   |

|       |                       |                                                                                           |   |

|       |                       | Signature of Supervisor                                                                   |   |

|       |                       |                                                                                           |   |

|       |                       | Det. 2 - 7,15                                                                             |   |

|       |                       | Date                                                                                      |   |

|       |                       |                                                                                           |   |

| Super | visor's Name (Printed | Ehsan Atoofian                                                                            |   |

#### Abstract

With the rise of chip multiprocessors (CMPs), it is necessary to use parallel programming to exploit computational power of CMPs. Traditionally, lock-based mechanisms have been used to synchronize shared variables in parallel programs. However, with the complexity associated with locks, writing a correct parallel program is a huge burden for programmers. As an alternative, Transactional Memory (TM) is gaining momentum as a parallel programming model for multi-core processors. TM provides programmers with an atomic construct (transaction), which can be used to guarantee atomicity of accesses to shared variables, as the synchronization is handled through the underlying system. Transactional memory comes in two variants: Software transaction memory (STM) and Hardware transaction memory (HTM). Both STM and HTM systems have advantages and disadvantages that either enhance or penalize performance in transactional applications.

In this thesis, the focus is on implementing an adaptive system that exploits both STM and HTM at transaction granularity. The goal is to achieve performance gain by incorporating the benefits of both TM systems. A synchronization technique is developed to seamlessly switch between HTM and STM based on the characteristics of a transaction. We exploit decision tree to predict the optimum system for each transaction in a given application. The decision tree is a form of supervised machine learning to classify transactions based on parameters such as transaction size, transaction write ratio, etc. From the evaluations using STAMP, NAS, and DiscoPoP benchmark suites, the proposed adaptive system is able to improve speed of transactional applications by 20.82% on average.

## **Table of Contents**

| Abstract                                                                                                                                                                                                                                                                                                           | ii                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| List of Abbreviations                                                                                                                                                                                                                                                                                              | viii                                               |

| Chapter 1 - Introduction<br>1.1 Parallel Programming/Computing<br>1.2 Shared Memory Architecture (SMA)<br>1.3 Lock based Synchronization<br>1.4 Transactional Memory<br>1.4.1 Software Transactional Memory (STM)<br>1.4.2 Hardware Transactional Memory (HTM)<br>1.5 Motivation and Purpose<br>1.6 Thesis Outline | 2<br>5<br>6<br>8<br>9<br>. 10<br>. 10              |

| <ul> <li>Chapter 2 - Background and Related Work</li></ul>                                                                                                                                                                                                                                                         | 13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21 |

| Chapter 3 - Adaptive System Design<br>3.1 Transaction Granularity<br>3.2 Restricted Transaction Memory (RTM)<br>3.3 Synchronization of RTM and STM<br>3.4 Implementing Source Code<br>3.5 Implementation of Decision tree<br>3.5.1 Training Phase<br>3.5.2 Testing Phase                                           | 29<br>30<br>34<br>36<br>37<br>37                   |

| <ul> <li>Chapter 4 - Experimental Results</li></ul>                                                                                                                                                                                                                                                                | . 43<br>. 43<br>. 44<br>. 45<br>. 46<br>. 47       |

| 4.3 Evaluation of Adaptive system                                                                                                                                                                                                                                                                                  | . 50                                               |

| 4.3.1 Adaptive system vs. TinySTM                      | 50 |

|--------------------------------------------------------|----|

| 4.3.2 Adaptive system vs. RTM                          |    |

| 4.3.3 Decision Tree Predictions for Testing Benchmarks |    |

| Chapter 5 - Conclusion                                 | 58 |

| 5.1 Summary of Contributions                           |    |

| 5.2 Future Work                                        |    |

| Appendix                                               | 60 |

| Bibliography                                           | 68 |

## List of Figures

| Figure 1.1: Block Diagram of Parallel Program with four threads                     |

|-------------------------------------------------------------------------------------|

| Figure 1.2: Ordering of Parallel-Programming Tasks                                  |

| Figure 1.3: Block Diagram of Shared Memory5                                         |

| Figure 1.4: Programmability analogy of Lock mechanisms                              |

| Figure 2.1: RTM Pseudo code example16                                               |

| Figure 2.2: State diagram of MESI protocol19                                        |

| Figure 3.1: Program Counter Code sequence30                                         |

| Figure 3.2: RTM fallback policy32                                                   |

| Figure 3.3: EAX status bits found in RTM Header file                                |

| Figure 3.4: Implementation of EAX status register                                   |

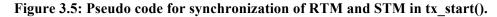

| Figure 3.5: Pseudo code for synchronization of RTM and STM in tx_start()35          |

| Figure 3.6: Pseudo code for synchronization of RTM and STM in tx_commit()<br>       |

| Figure 3.7: Pseudo code for implementing RTM and STM APIs                           |

| Figure 3.8: Decision tree output for 2 Threads                                      |

| Figure 3.9: Decision tree output for 4 Threads                                      |

| Figure 3.10: Decision tree output for 8 Threads40                                   |

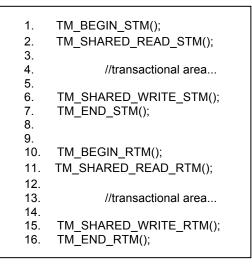

| Figure 4.1: Normalized Transactional Execution time of RTM relative to<br>TinySTM46 |

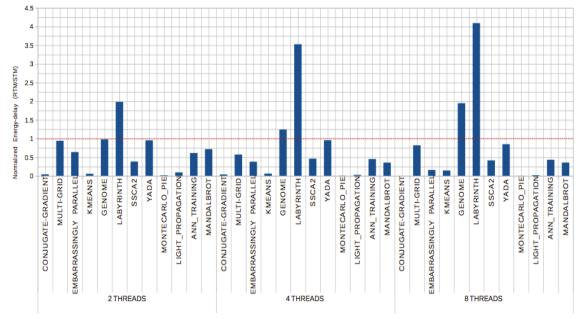

| Figure 4.2: Normalized Energy-delay of RTM relative to TinySTM47                    |

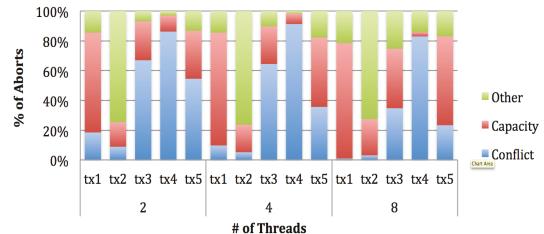

| Figure 4.3: Distribution of Transactional Aborts for Benchmark GENOME49             |

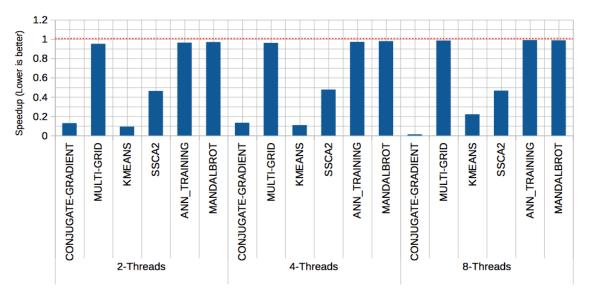

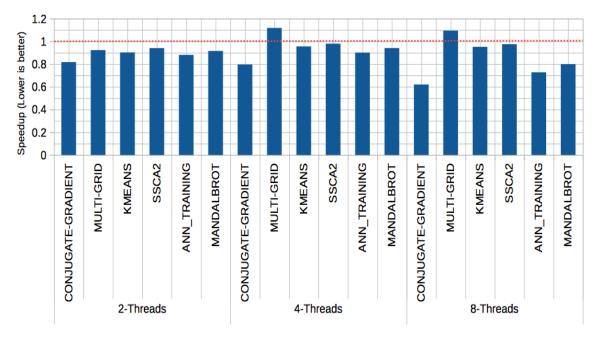

| Figure 4.4 Normalized Speedup Comparison between Adaptive system and<br>TinySTM     |

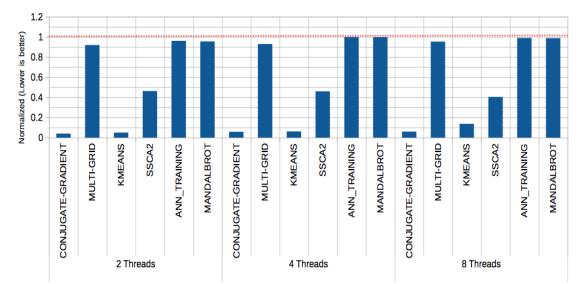

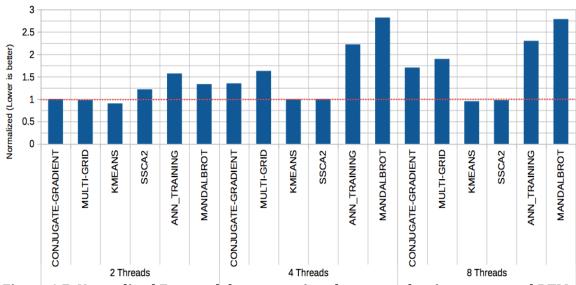

| Figure 4.5: Normalized Energy-delay comparison between adaptive system and TinySTM  |

| Figure 4.6: Normalized Speedup comparison between adaptive system and RTM53         |

| Figure 4.7: Normalized Energy-delay comparison between adaptive system and RTM54    |

## List of Tables

| Table 2.1: RTM Abort status using EAX abort codes                                                        | 17 |

|----------------------------------------------------------------------------------------------------------|----|

| Table 3.1: Characteristics of benchmark YADA consisting of five transaction                              |    |

| Table 3.2: Decision tree prediction based on Transaction Granularity for<br>Benchmark Conjugate-Gradient | 41 |

| Table 4.1: Characteristics of Benchmark LABYRINTH at two threads                                         | 48 |

| Table 4.2: Characteristics of Benchmark GENOME at two threads                                            | 49 |

| Table 4.3: Transaction parameters and execution time for Multi-Grid         benchmark                    | 53 |

| Table 4.4: Benchmark Conjugate-Gradient comparing Decision Tree         prediction with Optimum system   | 55 |

| Table 4.5: Benchmark Multi-Grid comparing Decision Tree prediction with         Optimum system           | 56 |

| Table 4.6: Benchmark KMEANS comparing Decision Tree prediction with         Optimum system               | 56 |

| Table 4.7: Benchmark SSCA2 comparing Decision Tree prediction with         Optimum system                | 56 |

| Table 4.8: Benchmark ANN_TRAINING comparing Decision Tree prediction           with Optimum system       | 56 |

| Table 4.9: Benchmark MANDALBROT comparing Decision Tree prediction         with Optimum system           | 57 |

### List of Abbreviations

| Abbreviat | ion Meaning                                              |

|-----------|----------------------------------------------------------|

| СМР       | Chip Multiprocessor                                      |

| ТМ        | Transactional Memory                                     |

| STM       | Software transactional Memory                            |

| HTM       | Hardware Transactional Memory                            |

| RTM       | Restricted Transactional Memory                          |

| HLE       | Hardware Lock elision                                    |

| TSX       | Transactionally synchronized extensions                  |

| VLSI      | Very-large-scale integration                             |

| ILP       | Instruction Level Parallelism                            |

| SMA       | Shared Memory Architecture                               |

| WAW       | Write after Write dependency                             |

| WAR       | Write after Read dependency                              |

| RAW       | Read after Write dependency                              |

| SMC       | Synchronization control mechanism                        |

| TL2       | Transactional Locking 2                                  |

| GVC       | Global-versioning counter                                |

| RV        | Read version                                             |

| CU        | Computational unit                                       |

| LR        | Linear Regression                                        |

| STAMP     | Stanford Transactional Applications for Multi-Processing |

| API       | Application Program Interface (APIs – plural)            |

| RAPL      | Runtime Average Power Limit                              |

| TX#       | Transactional number (e.g. TX1)                          |

|           |                                                          |

#### **Chapter 1**

#### Introduction

Over the past several decades, the performance of general-purpose processors has increased rapidly. This rapid improvement has come both from advances in the technology used to build processor chips and also innovations in architecture of processors. Over the years, improvements in VLSI technology led to smaller and faster transistors and this helped computer architects to increase clock frequency of processors. Furthermore, the number of transistors integrated on a single die is expected to grow according to Moore's law [11] for the foreseeable future. This provides an ample opportunity for processor designers to incorporate more resources in architectural level and boost performance of processors.

The conventional way of processor design was single core processor in which all hardware resources were dedicated to a single processing core. Each generation of processor had larger and more sophisticated components such as caches and reorder buffers. However, by 2005 the performance of single-core processors started to slowdown in computation performance due to "3 Walls": Power Wall, Memory Wall and instruction level parallelism (ILP) Wall [8].

As the single-core processor became more complex, certain limitations made it technologically impossible to achieve better performance. The power wall limitation is met due to increased clock frequency which results in significant heat dissipation. This means that the single-core processor has reached the practical power limit in commodity microprocessors. As for the memory wall, the limitation exists in the gap between the processor and the memory speeds. This gap is increasing over time, requiring the cache sizes inside the processor to be larger in-order to mask the latency of memory. The third wall is related to the dependency of instructions. Single-core processors search stream of sequential instructions and execute independent instructions in parallel. However, the amount of independent instructions found in sequential programs is limited, causing the third wall: ILP wall. The 3 walls together ultimately led to the rise of chip multiprocessors (CMP).

The architecture of a CMP consists of having 2 or more processors integrated onto a single circuit die. This overcomes the limitations of the power wall, memory wall and IPL wall. For Power wall, CMPs are energy efficient and silicon-area efficient due to smaller and less complex cores incorporated into a single chip. For Memory-wall, the computations amongst the cores are overlapped with memory accesses, resulting in better performance. For ILP-wall, there is an increased performance throughput by exploiting parallelism between the cores. Due to these several advantages, the CMP architecture has been the choice of semiconductor manufacturers.

For the last few years, CMPs have taken over the industry by storm. In our present day, CMPs are becoming a necessity in all of our everyday electronics. The cheapest PC/laptop in the market today all consist of at least a dual-core processor. Smart-phones nowadays all have dual-core, quad-core or even octa-core processors. Multi-core processors do not stop there. New cars of today are equipped with multicore systems due to the excessive amount of technologies such as adaptive cruise control, lane departure assistance, self-parking, etc. In present day, new CMPs have transistors of 14nm wide, and the industry is now hitting physical limits. Circuits are now so small that escaping heat is a major problem. While Moore's law may survive another few processor generations, chip manufacturers are starting to change their views on frequency scaling and applying it to core-scaling. This means that instead of focusing on increasing the clock frequency to increase performance of processors, it is now necessary to apply the concept of parallel programming and utilize computational power of multiple cores to boost performance. By utilizing all processing cores of CMPs, it is possible to achieve further performance gain in applications.

#### 1.1 Parallel Programming/Computing

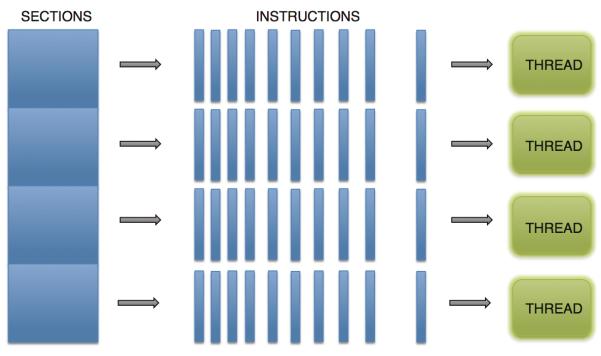

In general terms, parallel programming is the simultaneous use of cores to execute a computational application. Figure 1.1 displays a parallel program consisting of four threads.

Figure 1.1: Block diagram of a parallel program with four threads

First, the application is broken down into sections that can be executed in parallel (concurrent). Second, each section is broken down further into a series of instructions. Third, these instructions from each part execute concurrently on different threads. Although, this procedure may look simple, it actually consists of a complex order of steps in order to successfully exploiting parallelism in an application. However, there are certain problems that a programmer may face when developing parallel programs. Paul E. McKenny [32] discusses 4 categories that a programmer must take into account while developing parallel programs.

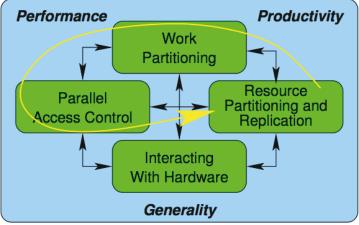

Figure 1.2: Ordering of Parallel-Programming Tasks [32]

- 1) Work Partitioning is the task of splitting the code or algorithm into discrete sections that can be distributed to be run in parallel across all threads.

- Resource Partitioning this ensures that the required resources are partitioned for the parallel tasks.

- Hardware Interactions identifying the resources associated with parallel tasks, such as the operating system, the compiler, number of cores/threads, and other software infrastructures

- 4) Control of Parallel Accesses is the task of avoiding conflicts such as race conditions on shared memory resources. The programmer needs to synchronize the sequence of the parallel tasks, and often requires serialization (locks) for certain parts of the program. The programmer must also take into account of data dependencies where the order of executions can affect the final results of the program. In shared memory, data dependence occurs from multiple use of the same-shared location accessed by different threads/cores.

Due to these steps and constraints, parallel programming has known to be difficult in applying, or in other terms it is very difficult to get a sequential program and making it parallel.

#### 1.2 Shared Memory Architecture (SMA)

For this thesis, the focus was on Shared Memory Architecture [20] as this is the architecture used in CMPs. SMA is a platform where all threads within a program/application work in a shared space meaning that the memory address space is shared between the threads. In contrast, Distributed Memory (DM) is a method where all threads working in parallel do not share a unified memory address space. Instead, DM uses private memory space for each thread and must communicate with each other explicitly [18].

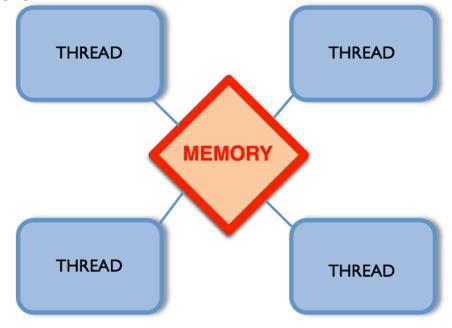

Figure 1.3: Block diagram of Shared Memory

With shared memory, there are some constraints in which a programmer must take into consideration. In SM, threads execute independently but they share the same memory address. It is necessary to have synchronization between the threads that are reading from and writing to SM. This is mainly due to the constraint of only one thread can access the shared memory locations at a time.

SM's major advantage is fast and efficient data sharing amongst the threads as all threads can communicate through a shared memory. One of the major disadvantages of SM is limitation of memory bandwidth where an increased number of threads will require a higher memory bandwidth or else it will cause a bottleneck in performance. Another disadvantage of SM is that it is very prone to data races in which the programmer is responsible for correct synchronization using locks, mutex, semaphores, etc.

#### 1.3 Lock based Synchronization

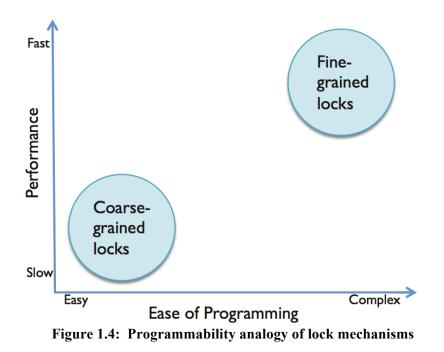

With shared-memory, there is a high probability that race occurs in programs. This happens when two or more threads are accessing the same address in shared memory. These data races can be classified as dependences: read-after-write (RAW), write-after-write (WAW) or write-after-read (WAR). To avoid these types of data races, a synchronization control mechanism (SCM) must be used. There are many SCMs that can be implemented such as locks, mutexes and semaphores. Locks are the most frequently used SMC in parallel programming. Locks allow a single thread to lock a variable which initiates ownership of a specific shared variable. Once the thread has completed its operation on that shared variable, it unlocks the variable allowing other threads to access the variable. If a lock is being held, other threads cannot access or attempt to acquire the same lock and must wait until it becomes unlocked. There are two types of lock structures that are commonly used: Fine grained locking and Coarse-grained locking.

Fine-grained Locking is used to achieve greater parallelism which leads to better performance. Each fine-grained lock will lock a single shared variable (or very few). Instead of holding a lock for a long time, each thread will hold the lock for a small amount of time while providing protection. Even though fine-grained locking achieves better performance, it has its own drawbacks. Firstly, parallel programming using finegrained locking is complicated for average programmers. Another major disadvantage of fine-grained locking is high overhead due to the amount of traffic activity taking place with many locks being locked and unlocked.

On the other side, coarse-grained locking is used to lock an entire section of a code instead of a single shared variable. This allows programmers to write correct parallel programs with less complexity because there is only one lock to deal with which means there is less chance of synchronization error. The drawback of coarse-grained

locking is less parallelism (low concurrency), which in return leads to low performance. Figure 1.3 shows the general depiction of performance vs. ease of programmability between fine-grained locking and coarse-grained locking.

The main challenge in lock-based programming (in particular fine-grained) is tricky synchronization bugs such as deadlock, live-lock and priority inversion. Deadlock occurs when multiple threads stall/wait for each other to release the locks corresponding to the shared variables. This results in a stall, as there is no possibility of forward progress until the lock has been released. For example, thread A holds a lock on resource X and is waiting for resource Y. While thread B holds a lock on resource Y and is waiting for resource X. Both thread A and thread B are waiting and neither of them can proceed.

Live-lock is similar to deadlock as the threads are unable to make forward progress. In deadlock the threads are blocked while in live-lock the threads are not blocked, rather they are busy responding to each other. Priority inversion takes place when a high priority process is blocked (waiting) while a low priority process is executed. Due to these circumstances, this system can become unbalanced and eventually crash. Fine-grained lock-based synchronizing mechanism does promote performance gains but the constraints caused by complex programmability and synchronization bugs prevent it from becoming mainstream.

#### **1.4 Transactional Memory**

Transactional processing is not a new discovery; it has been around since the early 1960's known as transactional processing system (TPS). The first TPS was used on American Airlines SABRE computing system, which automated the way the airlines booked reservations for flights [13]. The main idea of TPS was to provide a database of transactions that followed ACID properties:

ACID - Atomicity, Consistency, Isolation and Durability [12]

**Atomicity** – Each Transaction is atomic which means that if any part of the transaction fails then the entire transaction fails while the state of the system is unchanged.

**Consistency** – It is necessary in TM where the memory must remain in a consistent state while a transaction is executing. In the case a transaction exits in an inconsistent state, then the transaction is not allowed to complete and will be aborted.

**Isolation** – Other transactions cannot access data that has been changed by a transaction currently in progress. Isolation is necessary in order to avoid invalid results during execution of a transaction.

**Durability** – Once a transaction has successfully committed, it cannot be lost in the event of a system crash.

This led to the discovery of Transactional Memory (TM). TM is a parallel programming model, which achieves comparable performance to fine-grained locking while providing ease of programmability of coarse-grained locking [27]. With TM, a programmer only specifies the critical sections of the code to run atomically, while the underlying system will take care of correct execution of the program, reducing the complexity of parallel programming. Transactional memory consists primarily of two

types: software transactional memory and hardware transactional memory. In present day, there has been countless amount of research done in this field, due to the fascinating amount of potential it consists of.

#### 1.4.1 Software Transactional Memory (STM)

In software transactional memory, transactions are strictly implemented in software. Shavit and Touitou [30] introduced the first implementation of software transactional memory. STM works by providing a programming model where code is executed in a series of read-sets and write-sets in shared memory. While these reads and writes are being executed their intermediate state is not visible to other transactions. This decreases the probability of conflicts as the window in which transactions execute simultaneously is reduced.

Since the mid-2000, the research in STM has evolved with numerous amounts of concepts and optimizations. These concepts were introduced to further enhance performance of STM systems and also to enhance the ease of programmability. For example in STM, programmers no longer have to handle the case where a transaction aborts. The underlying system of STM will guarantee that the system would eventually commit every transaction by retrying and executing aborted transactions. In present day, there is still ongoing research on STM which shows that there is still potential for further improvements on practical implementations.

There are numerous implementations of STMs. Among those, two are more popular than the rest. The first implementation is Transactional Locking II (TL2) by Nir Shavit et al. [6]. The second implementation of software transaction memory is TinySTM by Pascal Felber et al [31]. TinySTM follows the same structure as TL2 but with enhanced design strategies that achieve even greater performance. Further analysis of TL2 and TinySTM is found in Chapter 2.

#### **1.4.2 Hardware Transactional Memory (HTM)**

Hardware transactional memory is the concept of executing transactions in hardware. The primary advantage of HTM is low overhead since it only relies on hardware resources. Recently, HTM has become largely available in commodity processors. Although these implementations have always been best effort meaning that there is no guarantees for forward progress. Some examples of HTM supported by commodity processors include, AMD's advanced Synchronization Series [5], IBM's Blue Gene/Q [1], and Sun's ROCK processor [33]. The recent release of Haswell processor with Intel's TSX (Transactionally Synchronized Extensions) results the widespread availability of HTM on the mass consumer market.

In this thesis, the focus has been on Intel's implementation of HTM called Restricted Transaction Memory (RTM) [15]. Further analysis of RTM is found in Chapter 2.

#### **1.5 Motivation and Purpose**

Both STM and RTM have benefits and limitations that either improve or penalize performance in certain applications. One of the most important differences between RTM and STM is transactional overhead. In RTM, the processor is responsible for transactional execution and this reduces timing overhead and better overall performance. On the other side, in STM, there is extra overhead for software based conflict detection and data versioning (such as initiating a transaction, validating transactional data, transactional commits, etc. [30]). This greatly hampers the overall performance in STM systems. Another important difference between the two systems is flexibility. In RTM, the processor oversees all memory accesses, which in-hand provides strong isolation but relies solely on hardware resources (not scalable). This results in complexity issues (fallback policy is needed) that lead to a higher probability of transactional aborts and in certain cases a performance slowdown when compared to STM. On the other hand, STM delivers a flexible system in which there is no resource constraint and the underlying system deals with majority of the complex synchronization issues, leading to less transactional aborts and a better overall performance in some cases when compared to

RTM.

In this thesis, the focus is on implementing an adaptive system that exploits both STM and HTM at transaction granularity. The goal is to achieve performance gain by incorporating the benefits of both systems. Typically, in parallel applications, the number of transactions can vary, anywhere from a single transaction to a large number of transactions. It is important to note that not all transactions are identical. Each transaction has its own characteristics in terms of transaction, either HTM or STM can be a better choice for implementation. We exploit the decision tree [22] to predict whether HTM or STM is faster for a given transaction. The decision tree receives input parameters (such as transaction size, transaction write ratio, etc.) and predicts the source code of the application based on predictions made by the decision tree. Our adaptive system supports both HTM and STM with the aim of reducing execution time of transactions with different characteristics.

In summary, we make the following contributions:

- We show that there is no single TM system that works well across all applications.

Depending on applications' characteristics, one system might be better than the other.

- We propose an adaptive system, which predicts the optimum TM system for a given transaction, statically. The adaptive system relies on the prediction of the decision tree to select either HTM or STM.

- Our evaluations using STAMP [2], NAS [4], and DiscoPoP [37] benchmark suites reveal that on average, the adaptive system is able to improve speed of transactional applications by 20.82%.

#### 1.6 Thesis Outline

The rest of the thesis is organized as follows. Chapter 2 reviews background information as well as research studies relating to TM. Chapter 3 explains design of the proposed adaptive system. Chapter 4 presents the experimental work including methodology and results. Finally, Chapter 5 concludes the thesis and discusses future work.

#### **CHAPTER 2**

#### **Background and Related Work**

This chapter reviews background information on existing STM systems, Intel's restricted transaction memory (RTM) and the decision tree prediction module. This chapter also examines related literature work focusing on optimization techniques for both HTM and STM.

#### 2.1 Software Transactional Memory

In this section, we explain two popular implementations of software transactional memory. The first implementation is Transactional Locking II (TL2) by Nir Shavit et. al [6]. The second implementation of software transactional memory is TinySTM by Pascal Felber et. al [30].

#### 2.1.1 Transactional Locking II [6]

TL2 is a state-of-the-art word-based Software transaction memory system that uses notion of time to impose order among transactions and guarantee consistency of transitional data. The main feature of TL2 is the ability to handle read and write operations in separate fashion. In TL2, the read operations are invisible; this means that when a transaction reads a shared variable, it will not indicate other transactions that a read operation is taking place. For write operations, TL2 postpones the update to the commit time. This means that TL2 does not perform the update as soon as it executes a transactional write operation; instead, the write operation updates are logged into a local list. Once the transaction is ready to commit, the operation will attain the instruction from the local list. Performance of a STM system is sensitive to the write operations as write operations are the major source of conflicts. By deferring the write operation to the commit time, TL2 reduces the total amount of transactional conflicts in an application. TL2 also utilizes conventional locks and a global-versioning counter (GVC) to validate transactional data. A lock is associated with each shared variable. When a transaction attempts to commit, it obtains the lock corresponding to the variable. GVC is a global counter and is used as timestamp for shared variables. When a transaction starts it copies

the current value of GVC into a local variable called read version (rv). The transaction uses rv to validate transactional reads. When a transaction commits it performs an increment-and-fetch on GVC and uses the new value of GVC to tag lock entries corresponding to transactional writes. TL2 is proven to have similar performance to finegrained locking [6].

#### 2.1.2 TinySTM

The second implementation of software transaction memory is TinySTM. This thesis integrates TinySTM's open source implementation of STM and incorporates it for switching between hardware and software transactions. TinySTM was chosen because it is currently the best performing STM system [31].

TinySTM shares many similarities with TL2. It is also a word-based STM implementation that uses conventional locks to protect the shared memory locations from simultaneous accesses. TinySTM uses the same time-based implementation as TL2, which guarantees transactional consistency. On the contrary, TinySTM contains a different design strategy that differentiates itself from the other STM implementations.

TinySTM uses encounter-time locking which is beneficial for detecting conflicts earlier (increasing transaction throughput). When compared to commit-time locking, conflicts that are detected during commit phase cannot be solved without at least one transaction being aborted. Also, encounter-time locking allows efficient handling of read and write operations without requiring complex mechanisms. For transactional write operations, TinySTM implements two new strategies: Write-through and Write-back. For write-through policy, a transaction writes directly to memory and keeps the old values in a log to reverse updates in the case of an abort. For Write-back policy, a transaction updates memory in the commit phase. TinySTM also provides memory-management functions, which allow transactions to use dynamic memory. This allows the ability to keep track of memory that has been freed (not disposed until abort). From these design tweaks, TinySTM has become one of the most efficient implementations of software transaction memory [31]

#### 2.2 Hardware Transactional Memory

Hardware transactional memory is the concept of speculative transactions being executed using hardware resources. The primary advantage of HTM is low overhead, since it only uses hardware resources such as level 1 cache, level 2 cache, etc. Recently, HTM has become broadly available in commodity processors. Some examples of HTM supported commodity processors include, AMD's advanced Synchronization Series [5], IBM's Blue Gene/Q [1], and Sun's ROCK processor [33]. Amongst these implementations, the recent release of Haswell processor with Intel's TSX (Transactionally Synchronized Extensions) [15] results the widespread availability of HTM on the mass consumer market.

HTM implementations have always been best effort meaning that they do not provide forward progress. In other words, there is no guarantee that a transaction will successfully commit in hardware; essentially requiring a fallback path to successfully execute an application in the event of an abort. Generally, a fallback path is an alternative software policy to guarantee successful execution. This software policy can be as simple as acquiring a lock and executing it non-transactionally.

In 2013, Intel released the first commercially available chip-multiprocessor with HTM support, named Haswell [15]. Along with it, Intel released TSX (Transactionally Synchronized Extensions) to their processor's instruction set. These extensions provide two software interfaces Hardware Lock Elision and Restricted Transaction Memory. [b.6].

- Hardware Lock Elision: a legacy compatible instruction set that provides instructions to lock/unlock shared variables using hardware resources.

- Restricted Transaction Memory: A new instruction set interface, where a programmer identifies a region of code to be executed transactionally. RTM provides no forward progress. Therefore, a program must always provide fallback code to handle a transactional abort that can either restart a transaction or take a non-transactional path (such as locks).

#### 2.2.1 Restricted Transaction Memory

For this thesis, the focus is on Intel's Restricted Transactional Memory (RTM). The proposed Adaptive system uses RTM's intrinsics along with TinySTM, which is used to switch between the two systems. The programming model of Intel's RTM is fairly straightforward to use. In RTM, a transaction is commenced with the instruction XBEGIN. Inside of the transaction, read-sets and write-sets are constructed while other computation operations (branching, arithmetic operations, etc.) can also be executed inside of a transaction. The consistency of read and write sets are maintained in the granularity of cache lines.

If a transaction's read-set/write-set is modified by another transaction, then conflict occurs. In the event of conflict, all the transactions are aborted and only one can proceed. In RTM, a fallback path is needed to guarantee forward process in order to avoid the application or program to stall. To initiate the end of a transaction, the instruction XEND is used. The XEND instruction commits any changes to the shared memory and thus successfully executes the transaction in RTM. RTM provides four transactional instructions:

- XBEGIN initiates the start of a transaction.

- XEND completes a transaction and successfully commits changes to memory

- XABORT aborts the current transaction using an explicit failure code.

- 1. while(1){ //loop 2. int status = XBEGIN; //set status bit and start Txn 3. if(status == \_XBEGIN\_STARTED){ //status == \_XBEGIN\_STARTED 4. //increment shared global variable (\*g)++; //end transaction 5. XEND; 6. break: //break on success 7. } 8. else{ 9. //software fallback code is executed on Txn abort . . . . 10. } 11. } Figure 2.1: RTM Pseudo code example

- XTEST determines if it is executing within a transaction or not.

Figure 2.1 shows a sample RTM pseudo code sequence in which all the important instructions are implemented. Inside of the RTM header file, it contains the intrinsics that are used to enable hardware transactional execution. Line 1 starts with a while loop. Inside the loop, there is a status variable that is equal to *XBEGIN*. In line 3, there is an 'if statement' to check if the *status variable* == *xbegin\_started*. if this is true, then the transaction is initiated. Inside the transaction (line 4), there is a shared global variable that is incremented. In line 5, the instruction *XEND* is used to end the transaction. In line 8, in the case of a transactional abort, a fallback path is necessary since RTM does not guarantee forward progress (further information can be found in Section 2.2.3).

#### 2.2.2 RTM Conflict detection and EAX register bits

RTM uses the CPU caches (L1 cache) to track read-sets and write-sets. The conflict detection is handled through the existing cache coherence protocol of the chip multiprocessors. RTM uses eager conflict detection as it keeps transactions in a consistent state by detecting conflicts when a read/write operation to memory has been performed. In RTM, transaction aborts are flagged in the EAX register. The EAX register carries an 8-bit code that specifies the cause of the transactional abort. When a transaction is aborted, all the changes made to the memory are discarded and a flag is sent to the EAX register with an abort code. Table 2.1 states the abort codes with brief explanation.

| EAX Status Bit | ABORT           | Description                                   |

|----------------|-----------------|-----------------------------------------------|

| 0              | XABORT_EXPLICIT | Explicit instruction to abort transaction     |

|                |                 |                                               |

| 1              | XABORT_RETRY    | Transaction is likely to succeed if retried   |

|                |                 |                                               |

| 2              | XABORT_CONFLICT | Interference from another TX                  |

|                |                 |                                               |

| 3              | XABORT_CAPACITY | Overflow of cache and hardware buffers        |

|                |                 |                                               |

| 4              | XABORT_DEBUG    | Debug breakpoint                              |

|                |                 |                                               |

| 5              | XABORT_NESTED   | Transaction aborted within nested transaction |

Table 2.1: RTM Abort status using EAX abort codes

Conflict and capacity aborts take up the majority of transactional aborts in RTM. Conflict aborts occur when a transaction interferes with concurrent memory operations (read/write) performed by another transactions. Once this abort is triggered, the processor will abort the transaction by discarding all the updates done to the shared memory. Capacity aborts occur where there is an overflow of buffers and the capacity of the cache has been reached which results in an automatic transaction abort.

#### 2.2.3 Cache Coherency Conflict Detection

In RTM, the conflict detection is handled through the cache coherency protocol. If two transactions access a shared memory location and if at least one of them writes into the same location, the cache coherency protocol detects the conflict. In the event of conflict, only one transaction can proceed, while the rest should abort. RTM follows the eager policy [17] to resolve conflicts. In eager policy, as soon as a transactional write operation results in conflict, RTM will then abort the conflicting transactions and allows only one transaction proceed. Eager policy improves utilization of processor resources as a conflicting transaction is aborted immediately and is not postponed to the commit time. RTM follows the MESI protocol for cache coherency.

#### 2.2.3.1 MESI protocol [34]

MESI is a type of invalidation-based protocol, which supports write-back caches. MESI is the acronym for the four states that each cache line can transition to:

- Invalid This is considered the non-valid state. This means that the data is not located in the cache or the local copy of the data is incorrect due to another process updating the memory.

- Shared This state is used for those cache blocks that are not changed by any processor.

- Exclusive The state is exclusive when a cache is the only one that has the correct value of the block.

- Modified This state is used for those cache blocks that are written by processors..

Figure 2.2 depicts MESI state diagram. The following is a brief explanation of how the MESI protocol works. The initial state of a cache block is invalid. When a processor writes to a cache block for the first time, the state changes to modified as there are no copies of the block in other caches. If a processor reads a block for the first time, it broadcasts BusRd command on the interconnection network. The cache that has the block sends it to the requester. Also, the state of the block changes to shared in both requester and the sender as more than one cache hold the data. If processor reads a block and no other cache has the block, then the memory provides the corresponding data and state changes to exclusive.

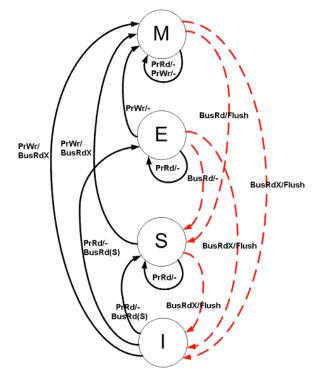

Figure 2.2: State diagram of MESI protocol [34]

#### 2.2.4 RTM Restrictions and Limitations

Intel's Restricted Transactional Memory has the term 'restricted' because it is very prone to transactional conflicts, which are primarily due to both hardware and software operations. There are many operations in RTM that are labeled as restricted and if a restricted operation is attempted then the transaction is aborted and the fallback path is executed. These are some restrictions in RTM:

- Debugging tools are not supported meaning that if any breakpoints are located inside of a transaction, it will be automatically aborted.

- Interrupts located inside of a transaction will cause an abort before the calling of the interrupt handler

- Input/output statements will cause an automatic transaction abort. For example, a 'printf' statement will causes RTM to abort.

- Software/System operations such as context switching and page faults cause transactional aborts.

- Hardware resources that exceed the capacity of the cache will cause a transaction abort. If a transaction's read-set or write-set does not fit in the CPU cache, it will result in a transaction abort due to the overflow of the internal processor buffers.

- Cache size in Haswell is 32KB with 8-way associativity.

- Unnecessary aborts due to false sharing of cache lines.

- If two transactions share a cache line and one of them aborts due to conflict over a shared variable in the cache line, the other transaction is aborted too.

#### 2.2.5 RTM's Fallback Path

Commodity chip multiprocessors (such as Haswell processor) that support hardware transactional memory, use the 'best-effort' mechanism. This basically means that there is no guarantee for a transaction to succeed even if there is no conflict. In RTM, a fallback policy is necessary to provide forward progress. A fallback policy is typically executed after the threshold of RTM's retry count has been met. The retry count is the number of times an aborted transaction retries execution. This is important since transactions in RTM have an abundant reasons to abort (refer to section 2.2.4). By retrying an aborted transaction 'x' number of times, there is a possibility that the transaction can eventually commit in hardware. Once the retry threshold is reached, the fallback policy is applied. Further information on fallback path can be found in Section 3.3.1.

#### 2.3 Decision Tree

For this thesis, the focus is on switching between hardware transactional memory and software transactional memory at transaction granularity. By using Decision Tree C4.5 [23], we are able to predict which system is the best choice for a given transaction.

Decision tree uses groups of input datasets and generates a tree as output that resembles a tree diagram where each branch is a decision. Ross Quinlan developed the early stages of the Decision Tree in 1979 (ID3 algorithm) [22]. In 1993, the C4.5 algorithm was developed to increase accuracy of Decision Tree. The C4.5 builds decision trees from a set of training dataset using information entropy. The decision tree consists of three nodes which are root, branch and leaf. At each branch of a tree, the C4.5 algorithm attains the attribute of the data that effectively splits the set of samples into sub-group in each specific class. This splitting process is referred to as information gain (differences in entropy). The input dataset contains the parameters of a function. In this thesis, the focus is targeted on transactional parameters such as transaction size, read-set size, etc. The output of the decision tree results in a binary value of 0 or 1, which represents the predicted outcome. For this thesis, the outcome of the decision tree represents whether RTM or STM will be used to execute a transaction.

#### 2.4 Related Work

Irina Calciu et al. [14] presented Invyswell, a hybrid transactional memory system that incorporates RTM and InvalSTM. InvalSTM is a modified STM system that was created [21] previously. One of the key differences between InvalSTM and other STMs is that it performs commit-time invalidation. This approach identifies conflicts with other concurrently executing transactions during its commit-phase. InvalSTM also implements bloom filters for conflict detection between HTM and STM. For Invyswell, each transaction is first tried in hardware. If the hardware abort status suggests that a transaction is unlikely to succeed in hardware, then it is retried in InvalSTM. They also investigate RTM's limitations and restrictions and provide InvalSTM as a fallback policy instead of using lock mechanism. They also incorporate optimizations such as *failfast*. This optimization is used for an application with high contention, which results in a higher probability of hardware resources reaching capacity limit. It is used to identify certain cases when RTM is wasting work with too many retries which eventually calls the fallback policy once the retry threshold has been met.

In our study, we do not use STM as a fallback policy for RTM; instead, we implement independent switching between RTM and STM. Also, our adaptive system is static and its runtime overhead is low. Furthermore, Invyswell is not evaluated from energy point of view. On the other side, we examine energy efficiency of our adaptive system and compare it with both HTM and STM.

M. Wang et al. [29] exploited Intel's restricted transaction memory to implement a molecular dynamics simulator called Moldyn. They explore several important relationships between transaction size and write ratio inside transactions as well as retry count and transaction abort rate. They investigate how these parameters affect the overall performance of an application. They introduce code transformations such as computation splitting and privatization for improving performance. Computation splitting/merging is the basis of transactional aborts caused by the size of a transaction, which can lead to low performance. In this paper, they identify a 'sweet-spot' in the Moldyn application where they compute each pair of molecule updates inside a single transaction as opposed to thousands of molecules or single molecule in a transaction. This 'sweet-spot' in transaction size increases performance in RTM.

For this thesis, we incorporated this paper's notion of the correlation between the transaction's characteristics and the performance impact. We exploited the parameters of a transaction such as transaction size, read-set size, write-set size, etc. and provided a TM system based on both HTM and STM. This is important because these parameters give information on a system's behavior and constraints. By using these factors, we are able to switch between HTM and STM at transaction granularity to achieve performance gain.

Pereira et al. [28] presented an extensive evaluation of Haswell's Transaction Memory performance. They focused on RTM's forward-progress polices since Intel's TSX does not guarantee that a transactional execution will commit. This technique retries the execution of a transaction with or without a time delay and attempts completing the transaction execution speculatively. They introduced three policies for forward progress: Maximum retry, Back-off and SerControl. Maximum retry is the simplest approach as it limits the number of times a transaction can be retried. Once a transaction reached the retry threshold, it will commence the fallback policy with a global lock. Back-off policy is based on a time delay in which an aborted transaction will wait for a time delay before restarting. The duration of this time delay is uniform as the time delay increases exponentially for every restart. Once again, there is a threshold for number of transactional retries and once it has reached the limit, the transaction will be executed using global lock. The next policy that was introduced in this paper is SerControl. This policy focuses on the type of transactional abort in RTM by using the EAX register status bit. If the transaction is aborted due to conflict or capacity consecutively, SerControl will serialize the transaction by using a lock. If the cause of abort is not conflict or capacity, then the maximum retry policy is applied. There are also other aborts that are considered such as page-fault that may occur again if the transaction is immediately retried so the back-off policy is applied after the threshold has been reached. It is important to note that this paper focuses on increasing the probability of executing transactions successfully in RTM.

In our thesis, we incorporate the ideas of the potential performance benefits of forward progress policies. Although, the notion of having an efficient forward progress policy is important, the actual performance gains are negligible. In this research paper [28], they do not show the comparisons between the proposed RTM forward progress policy and another TM system such as TinySTM. This would have clearly indicated the impact of this paper's proposed policies on performance. For our study, we conducted many experimental tests with a variety of retry counts for transactional aborts. By retrying an aborted transaction 'x' number of times, there is a possibility that the transaction can eventually commit in hardware. Once the retry threshold is reached, the fallback policy is applied. The fallback policy that is used is a global lock mechanism. In our adaptive system, the retry count is set at 4. Based on experimental simulations, the retry count of 4 is the best option that produces optimal performance. It is possible to have a higher retry count, but it can hurt performance as retrying a transaction that aborts over and over increases execution time. Also, having a low retry count can cause the fallback policy to be executed too early. Furthermore, in our work, we investigated the behavior of a transaction that best suits each TM system. If a transaction consists of a

very large transaction size as well as a very large working set size, having an optimized forward progress policy will not change the fact that RTM will perform poorly. In this case, our adaptive system will automatically execute the optimal system based on the parameters of a transaction.

M. Castro et al. [26] presented a dynamic approach to do efficient thread mapping using machine learning. This technique relies on matching the behavior of an application with the system characteristics. This technique is a dynamic approach and gathers information from the application and the STM system at specific time intervals. They compared dynamic approach with static thread mapping approach based on machine learning. For the Static approach, they used the decision tree learning method which was trained using datasets of input parameters. It will then output a decision tree that will predict a thread mapping strategy. The predictor chooses one of four different strategies: round-robin, scatter, compact and Linux. For dynamic Thread mapping, there are three phases: hardware topology analyzer (HTA), thread mapping predictor and transaction profiler. The HTA uses hardware locality library to get information from the underlying platform topology (hierarchy of caches and how they are shared among caches). The transaction profiler gets information from hardware counter and from the TM underlying system all during runtime at specific time intervals. The thread mapping predictor gets the data from the profiler and feed the data to a decision. Then, the predicted thread mapping strategy is applied. Whenever a TM operation starts, aborts or commits, the transaction profiler will be executed during these intervals and calls the thread mapping predictor to switch strategies when necessary. For the transaction profiler, only one concurrent running thread will be chosen for that task because it reduces stress on the system and there isn't any need for extra synchronization mechanisms for all threads. The experimental results shows that thread mapping strategies do have a major impact on performance. Out of the 56 TM applications, only 3 applications show no performance gain and 8 applications had performance loss. The maximum performance loss was 8% due to wrong predictions of the decision tree.

In our thesis, we incorporated the decision tree to predict the optimum system for a given transaction. This paper proves that by incorporating a decision tree, we are able to classify a transaction's parameters in order to predict the optimum system that achieves the best performance. The decision tree algorithm used in the paper is ID3 while in this thesis, the focus was on the C4.5 algorithm. C4.5 is an enhanced version of ID3, as it also supports continuous attribute that results in better performance. This paper also follows a procedure of attaining a training set of benchmarks and a testing set of benchmarks. By separating the training and testing, it is possible to achieve results based on the prediction of the decision tree itself. For our study, a training set of benchmarks consists of low, medium and large transaction sizes as well as low, medium and large working set size.

C. Wang et al. [3] presented optimizations for limiting overhead in software transaction memory. They focus on supporting transactional code in unmanaged languages such as C. Optimization of STM overhead in unmanaged languages is a challenging task as it requires implementing validation in the granularity of the cache block rather than an object. In this paper, they proposed techniques to allow programmers to initiate blocks to be executed atomically. They also exploit compiler-based optimization techniques such as in-lining (necessary for fast paths), eliminating redundant barriers and register checks. Our work is orthogonal and can be combined with this paper [3] to enhance performance further.

Z. Li et al. [37] presented a compiler-based tool, called DiscoPoP, to automatically identify regions of code that can be executed in parallel. It is designed to be able to find code regions with arbitrary granularity. It is important to note that DiscoPoP finds regions of a code in which data dependency does not exist. This is called CU (computational unit). In the next step, dependency graphs are then built. The nodes in the graph represent CUs and the edges represent the dependency between the CUs. By exploiting the dependency graph, DiscoPoP determines the potential parallelism that is available on different levels of the sequential code.

For this thesis, the DiscoPoP parallel benchmark suite was used to evaluate adaptive system. This Benchmark suite consisted of small and medium sized transactions that consisted of medium sized working set. For the decision tree training phase, it is important to have a wide range of transactional parameters to achieve greater accuracy in predictions.

D. Didona et al. [8] presented a self-tuning optimization technique to dynamically adjust the concurrency level in STMs. The purpose of this paper is to automatically

identify the optimal degree of parallelism which will maximize the throughput of the They introduced self-tuning methods for both shared-memory and applications. distributed STMs. The performance of a TM application varies based on different factors such as duration of transactions, level of data contention, ratio of update vs. read-only transactions, etc. By changing the number of threads at runtime, it can improve the performance of some applications instead of having a fixed number of threads. In this paper, they used the self-tuning method that combines exploration-based and modeldriven approaches. Shared-memory STMs use the exploration-based approach which consisted of three phases. The first phase is measurement phase. In this phase, the application runs with fixed number of threads and measures the number of commits and aborts. The second phase is decision phase. This phase decides whether to increase or decrease the number of threads until the maximum is reached. The third phase is transition phase. This phase is an external controller thread which either adds or removes threads from an application depending on the results from the decision phase. Distributed STM uses an analytical-based performance model which relies on a set of assumptions based on transaction conflict patterns.

For this thesis, a similar approach is taken regarding the evaluation phases that are introduced in this paper. The decision tree consisted of two phases, training and testing. This was done similar to this paper in order to have discrete evaluations based on the decision tree prediction module.

Y. Rughetti et al. [35] proposed a technique which automatically tunes the degree of parallelism in HTM. To achieve automatic tuning, the authors incorporated a machine leaning algorithm. This work focuses on a two-layered approach where the first-layer is the correction functions which is used to predict values of time. The second-layer consists of the performance predictor model that predicts the level of concurrency. There are existing STM approaches such as Hill-climbing techniques [24] and transaction scheduler [9] that optimize degree of parallelism. The hill-climbing technique changes the parallelism degree by reacting to throughput or abort rate. Transaction Scheduling is the basis of mapping transactions to threads dynamically to minimize data contention, and then the rescheduled threads are removed from the execution for that time interval. This approach gives different types of information from abort ratio to the details on a

transaction read/write set. In these approaches, the predicted value of the transaction wasted time is used to find the system throughput. This allows predicting the optimal value to achieve the expected maximum throughput. In STM, it is easier to access via software instrumentation to monitor specific parameters. However, these parameters are not supported in HTM, and implementing it in HTM via software would create overheads and lower the performance severely, especially since an advantage of HTM is supposed to avoid any costly additional software instrumentation (overhead). The techniques are not compatible for HTM since all of these models for STM do not take into account the transaction aborts in which HTM is very vulnerable to conflicts. In this study, the authors implement a classification approach comparing two different machine-learning methods: Decision tree and Neural Networks. This approach consists of constructing a training set for a specific application. The training set is constructed by executing a few runs of the application with different inputs of configuration parameters. For each input, the application is executed for a range of threads. By implementing this for each workload tested during the training phase, it becomes possible to determine the best performing concurrency level. The major benefit of this approach is that it follows the one-step layered approach meaning that it does not require the usage of correction functions.

In this thesis, we use machine learning to determine which TM system is appropriate for a transaction. This paper also shows the importance of overheads associated with HTM systems in which careful analysis must be taken or else it will cause performance penalties. Furthermore, our adaptive system does not execute both HTM and STM, simultaneously. As this process incurs extra overhead. Thus, the adaptive system avoids this performance penalty by allowing a transaction to execute in either hardware or software. (Further information can be found in section 3.3)

Y. Xiao et al. [36] proposed an optimization technique that statically decides on transactional parameters to improve performance of STM in parallel applications. By focusing on a transaction's characteristics (such as transaction size, read set size and write set size), it is possible to achieve speedup in applications. The transaction size is a crucial parameter that can have significant impact on performance and it is important to have an optimum size to achieve speedup. If the transaction size is too small, it can lead to overhead that exceeds the performance gain of parallel execution (results in slowdown

when compared to sequential programs). If the transaction size is too large, it can lead to an excess amount of rollbacks due to a higher probability of transactional aborts in applications. Thus, it is important to have the optimum 'sweet spot' of transaction size. This approach of optimizing each parameter manually can be a tedious and time consuming process. To overcome this issue, the authors propose two optimization techniques that are designed to automatically determine the optimal transaction size. The first technique exploits Linear Regression (LR) to predict the transaction size. The LR works by attaining the transaction parameters such as transaction size, read-set size, write-set size and predicts the optimum transaction size. However due to the simplicity of implementing LR, the accuracy is quite low. In order to improve the accuracy, multiple LR models are used to predict transaction size. In addition, a decision tree prediction model determines which LR model is appropriate for a given transaction. Overall, these optimization techniques improved the performance of STM based applications.

For this thesis, the adaptive system incorporates both HTM and STM to enhance performance of parallel applications. A decision tree is implemented to predict the optimum system based on a transaction's characteristics. With the optimization techniques proposed by Yang et al. [35], there is an opportunity to enhance the adaptive system by optimizing STM and RTM separately based on the transactional characteristics (such as transaction size, read-set size, write-set size, etc.).

#### **Chapter 3**

#### Adaptive System Design

This chapter describes the design of the proposed Adaptive system. Section 3.1 explains the importance of transaction granularity for the proposed adaptive system. Section 3.2 analyses the programmability aspects of RTM. Section 3.3 revolves around the synchronization technique that is used to seamlessly switch between RTM and TinySTM. Section 3.4 depicts how the adaptive system is implemented into a specific source code. Finally, section 3.5 explains the implementation of the decision tree prediction module.

#### 3.1 Transaction Granularity

One of the features of the adaptive system is that it switches between HTM and STM in transaction granularity. In parallel computing, the term granularity is defined as the amount of real work in a parallel task. With transaction granularity, the focus is on the basis of individual transactions rather than an entire application. This fine-grained granularity system increases performance gains while a coarse-grained granularity system misses many opportunities for speedup. However, to avoid overhead, the adaptive system does not execute HTM and STM simultaneously. Simultaneous execution of HTM and STM requires communication between in-flight hardware and software transactions. A metadata should record transactional data and each transaction should check the metadata when it accesses a transactional variable. Doing so significantly increases execution time and hurts performance, especially in applications with low conflict rate. To avoid this performance penalty, we allow a transaction to execute in either hardware or software, but not both.

In order to achieve transaction granularity, program counter (PC) was used to distinguish each and every transaction. While executing an application/benchmark, we are able to attain the parameters of each transaction. These parameters include elapsed execution time, the static size of transaction, transactional data, the number of aborts, etc. From these parameters, it is possible to further understand the behaviors of both RTM and TinySTM.

uint32\_t eip1 = 0;

\_\_asm\_\_\_volatile\_\_("movl \$., %0" : "=r"(eip1));

Figure 3.1: Program counter Code sequence

Figure 3.1 shows the code sequence used to read PC. When a transaction is initiated this code returns address of the first instruction in the transaction. Line 1 initializes *eip1* (a local variable). Line 2 retrieves the value of the program counter to identify each transaction. This is crucial for the adaptive system as it switches TM systems from one transaction to another.

#### 3.2 Restricted Transaction Memory (RTM)

The implementation of RTM programs was based on the programmability references from Intel's TSX manual [17]. The key factors of an RTM program is the following:

- Retry count

- Fallback policy

- Transactional abort status

The retry count is the maximum number of times an aborted transaction is rolled back and retries execution. This is important in RTM since transactions have an abundant reasons to abort (refer to Section 2.2.4). By retrying an aborted transaction 'x' number of times, there is a possibility that the transaction can eventually commit in hardware. Once the maximum retry threshold is reached, the fallback policy is applied. It is important to be able to execute a transaction using hardware resources as often as possible in order to use the performance benefits of RTM. In our adaptive system, the retry count is set to 4. Based on our experimental simulations, the retry count of 4 is the best option that produces optimal performance. It is possible to have a higher retry count, but it can hurt performance as retrying a transaction that aborts over and over increases execution time due to wasted work. For example, if the retry count is 12 and the application triggers capacity aborts, the program will keep retrying the execution until the threshold of retires is met. This wastes processor cycles and the outcome is performance slowdown. Also, having a low retry count can cause the fallback policy to be executed too prematurely. This means that RTM does not have a chance to be executed, which is detrimental for performance gain. By conducting experimental test cases, having a retry count of 4 is a 'sweet-spot' for optimal performance.

In RTM, it is necessary to incorporate a fallback policy to guarantee that an application will successfully execute. A sample code sequence of RTM's fallback policy is found in figure 3.2. This code sequence is placed inside a header file (tm.h in STAMP) and is executed when RTM is called upon. The tm.h file contains the APIs necessary for transactional execution for both software and hardware transactions. For this thesis, these APIs are modified to support TinySTM and RTM.

This code sequence in figure 3.2 only focuses on the lock mechanism that is used in the case of an RTM transactional abort. This fallback policy consists of a global pthread lock. In line 4, if the number of tries is less than 0, then the fallback path is initialized by acquiring a lock. This sequence happens during  $TM\_BEGIN\_RTM$ . Once the  $TM\_END\_RTM$  is called, the code sequence will try to commit a transaction in RTM only if the number of tries is greater than 0. Otherwise, in line 11, the pthread lock that was held previously is released and the transaction is executed using locks. This guarantees forward progress as the transaction will eventually commit after the threshold of retires has been met and eventually executes the transaction using locks.

```

1. #define TM_BEGIN_RTM()

2.

...

3.

tries --:

4.

if (tries \leq 0)

pthread_mutex_lock(&global_rtm_mutex);

5.

6.

7.

8. #define TM END RTM()

if (tries > 0)

9.

10.

else

11.

12.

pthread mutex unlock(&global rtm mutex);

13.

```

Figure 3.2: RTM fallback policy

In RTM, there are many constraints that result in a transactional abort. To track these aborts, RTM uses the EAX status register to specify the exact cause of an abort. Once a transaction aborts, the EAX register will send an abort code with the reason of abort (further information on EAX abort codes can be found in Section 2.2.4).

To measure the cause of aborts, we use an array to keep track of all the different kinds of transactional aborts inside an application. Once the application executes, the total number and type of aborts will be printed out. This feature is an important aspect for understanding the behaviors of RTM. From initial evaluation of RTM, the benchmarks that perform poorly tend to have a higher abort rate with the majority being capacity aborts. While the benchmarks that show performance gain have minimal abort rate, along with minimal capacity aborts. Capacity aborts are detrimental to RTM's performance as the hardware resources are bounded with constraints. A benchmark that consists of a large working set size, and/or large transaction size, has a higher probability of getting capacity aborts in RTM, thus decreasing performance. Figure 3.3 depicts the EAX status bits located in the RTM header file.

| 1. /* Status bits */                       |                      |

|--------------------------------------------|----------------------|

| 2. #define XABORT_EXPLICIT_ABORT           | (1<<0)               |

| 3. #define XABORT_RETRY                    | (1<<1)               |

| 4. #define XABORT_CONFLICT                 | (1<<2)               |

| 5. #define XABORT_CAPACITY                 | (1<<3)               |

| <ol><li>#define XABORT_DEBUG</li></ol>     | (1<<4)               |

| <ol><li>#define XABORT_STATUS(x)</li></ol> | (((x) >> 24) & 0xff) |

|                                            |                      |

Figure 3.3: EAX status bits found in RTM header file

| 1.  |                               |

|-----|-------------------------------|

| 2   | (                             |

| 3.  | (tx->num_abort)++;            |

| 4.  |                               |

| 5.  | if((eax_regg & 0x01) == 0x01) |

| 6.  | (tx->abort_explicit)++;       |

| 7.  | if((eax_regg & 0x02) == 0x02) |

| 8.  | (tx->abort_retry)++;          |

| 9.  | if((eax_regg & 0x04) == 0x04) |

| 10. | (tx->abort_conflict)++;       |

| 11. | if((eax_regg & 0x08) == 0x08) |

| 12. | (tx->abort_capacity)++;       |

| 13. | if((eax_regg & 0x10) == 0x10) |

| 14. | (tx->abort_debug)++;          |

| 15. | if((eax_regg & 0x20) == 0x20) |

| 16. | (tx->abort_nested)++;         |

| 17. |                               |

Figure 3.4: Implementation of EAX status register

The EAX status bits are implemented in conjunction with RTM's header file that consists of the definitions of the aborts. This code sequence is placed inside RTM\_stats function to attain all the metadata of a transaction. In line 3 (figure 3.4), the total number of aborts is accumulated. From line 5 to line 16, there are if statements to check whether EAX status bit are initialized. For example, if there is an abort, it will check each status bit and once the status bit is found, it will determine the cause of abort. These abort metadata is then accumulated in the array structure to attain all the aborts of a transaction within an application.

#### 3.3 Synchronization of RTM and STM