Lakehead University

Knowledge Commons, http://knowledgecommons.lakeheadu.ca

Electronic Theses and Dissertations

Electronic Theses and Dissertations from 2009

2015-06-16

# System formulation for parallel circuit analysis

Savalia, Tapankumar Kishorbhai

http://knowledgecommons.lakeheadu.ca/handle/2453/649 Downloaded from Lakehead University, KnowledgeCommons

## System Formulation for Parallel Circuit Analysis

by

Tapankumar Kishorbhai Savalia

A Thesis

Presented to Lakehead University in Partial Fulfilment of the Requirement for the Degree of Master of Science

in

Electrical and Computer Engineering

Thunder Bay, Ontario, Canada

May 2014

## Abstract

Advances in communication systems and VLSI circuits increase the performance requirements and complexity of circuits. During the design process, there is a need to perform computationally demanding numerical simulations to verify the functionality of circuits under design. One way to reduce computing time is to use parallel processing. This thesis discusses different techniques for parallel circuit analysis with emphasis in the formulation of equations for a circuit decomposed in subcircuit blocks.

For manually decomposed circuit, this thesis introduces two approaches to formulate circuit equations. The two formulations allow to independently analyze each subcircuit block by periodically exchanging information with a master process. A node-tearing process is used to divide the system Jacobian in blocks. The first formulation is based on the nodal voltages and currents at the interface nodes. The second formulation is presented in this thesis for the first time and uses scattering waves to exchange information between subcircuits. The two formulations are described in detail and implemented in a general circuit simulator.

Simulation results comparing the performance of the proposed formulations for different circuits are presented. These results indicate that there is no advantage in using waves to exchange information between subcircuits. Moreover, at least with the current software implementation the formulation based on nodal variables is significantly more efficient. This thesis concludes with a road map for future work.

## Acknowledgments

There are no enough words to convey my deep gratitude and respect for my thesis and research advisor, Dr. Carlos Christoffersen, for his valuable guidance, encouragement and support throughout my graduate studies. Also, I am grateful to Dr. Ehsan Atoofian and Dr. Xiaoping Liu for reviewing my thesis and providing me with valuable comments.

I would like to thank all my friends who have provided me with joy and warmth through these years. I would also like to thank my parents and my younger brother. They were always supporting me and encouraging me with their best wishes. Finally, I would like to thank my wife, Purvi Bhatt. She was always there cheering me up and stood by me through the good times and bad.

Tapankumar Kishorbhai Savalia

tsavalia@lakeheadu.ca

## Contents

| List of Figures                                               | V    |

|---------------------------------------------------------------|------|

| List of Tables                                                | vii  |

| List of Symbols                                               | viii |

| List of Abbreviations                                         | ix   |

| Chapter 1                                                     |      |

| Introduction                                                  |      |

| 1.1 Motivation and Objective of This Study                    |      |

| 1.2 Thesis Overview                                           | 4    |

| Chapter 2                                                     |      |

| Literature Review                                             |      |

| 2.1 Introduction                                              | 5    |

| 2.2 Basic Concepts                                            | 6    |

| 2.2.1 Newton Method                                           | 6    |

| 2.2.2 Nodal Analysis                                          |      |

| 2.2.4 Diakoptics                                              |      |

| 2.3 Formulations Based on Domain Decomposition                |      |

| 2.3.1 Multilevel Newton Method [7]                            |      |

| 2.3.2 New Approach for Parallel Circuit Simulation [9]        |      |

| 2.3.3 Formulation with Binary Link [11]                       |      |

| 2.4 Other Formulations                                        |      |

| Chapter 3                                                     |      |

| Circuit Decomposition for Efficient Parallel Circuit Analysis |      |

| 3.1 Formulation Based on Nodal Voltages and Currents          |      |

| 3.1.1 Diakoptics Applied to Node Tearing  |

|-------------------------------------------|

| 3.1.2 Algorithm Flowchart                 |

| 3.1.3 Complete Example                    |

| 3.2 Formulation Based on Scattering Waves |

| 3.2.1 Formulation Details                 |

| 3.2.2 Algorithm Flowchart                 |

| 3.2.3 Complete Example                    |

| 3.3 Code Implementation                   |

| 3.4 Simulation Results and Discussion     |

| 3.4.1 Linear Circuit                      |

| 3.4.2 Nonlinear Circuit                   |

| 3.4.3 Soliton Line                        |

| 3.4.4 Summing Amplifier                   |

| 3.4.5 Microwave Low Noise Amplifier       |

| 3.4.6 Transistor Amplifier                |

| Chapter 4                                 |

| Conclusion and Future Research            |

| Appendix A                                |

# **List of Figures**

| 2.1  | Newton's Method                                                                          | 7  |

|------|------------------------------------------------------------------------------------------|----|

| 2.2  | Example circuit to explain nodal analysis                                                | 8  |

| 2.3  | General Circuit Diagram to explain diakoptics                                            | 10 |

| 2.4  | Example circuit for Diakoptics                                                           | 12 |

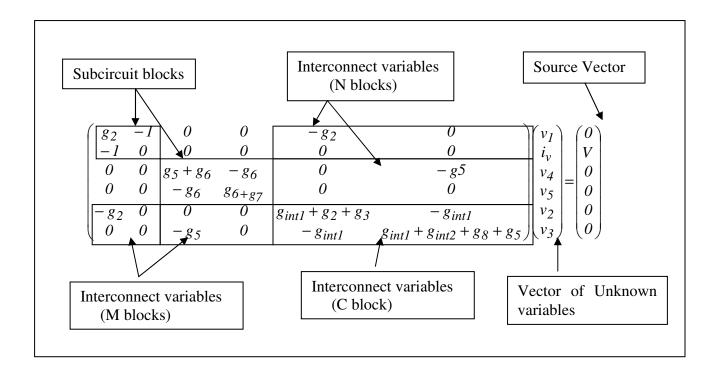

| 2.5  | System of equation                                                                       | 12 |

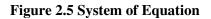

| 2.6  | Example circuit network $(\prod)$ to explain macromodel                                  | 14 |

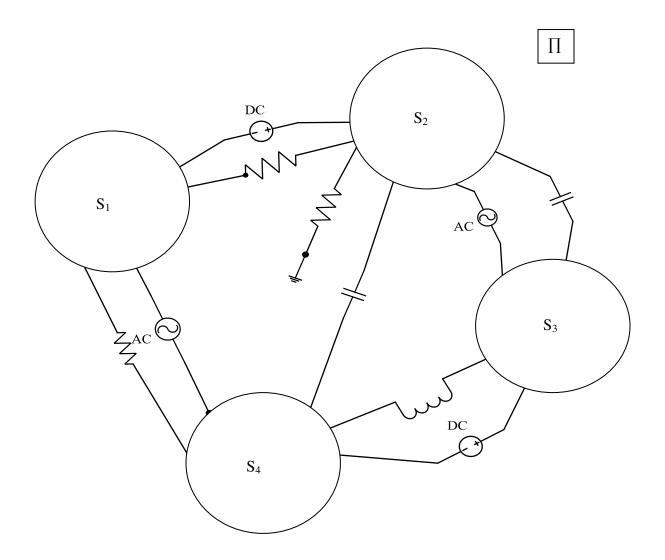

| 2.7  | Example of macromodel (a) subnetwork S of circuit network $\prod$                        |    |

|      | (b) Macromodel of subcircuit S which represents its external behaviour                   | 15 |

| 2.8  | Parallel Newton's algorithm                                                              | 18 |

| 2.9  | Thévenin equivalent measurement to find external current                                 |    |

|      | (a) Example of node tearing (b) measurement of $V_{th}$                                  |    |

|      | (c) Link current $i_1$ measurement                                                       | 22 |

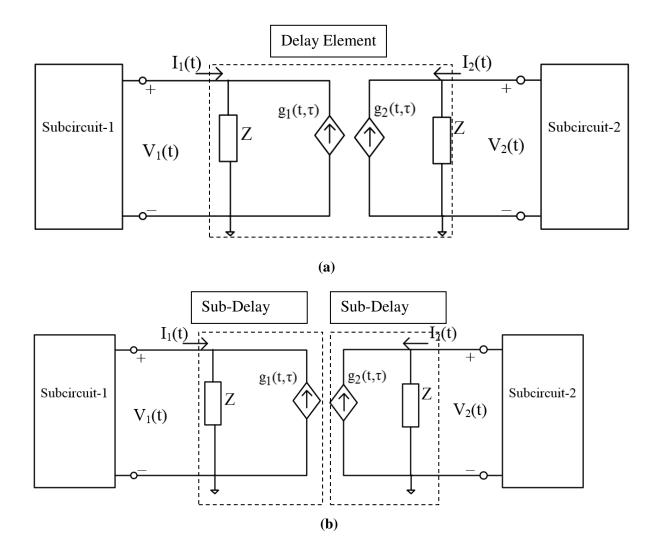

| 2.10 | Delay elements. (a) Ideal state variable based delay element.                            |    |

|      | (b) Ideal lossless transmission line                                                     | 26 |

| 2.11 | Partition of two subcircuits with delay element                                          | 27 |

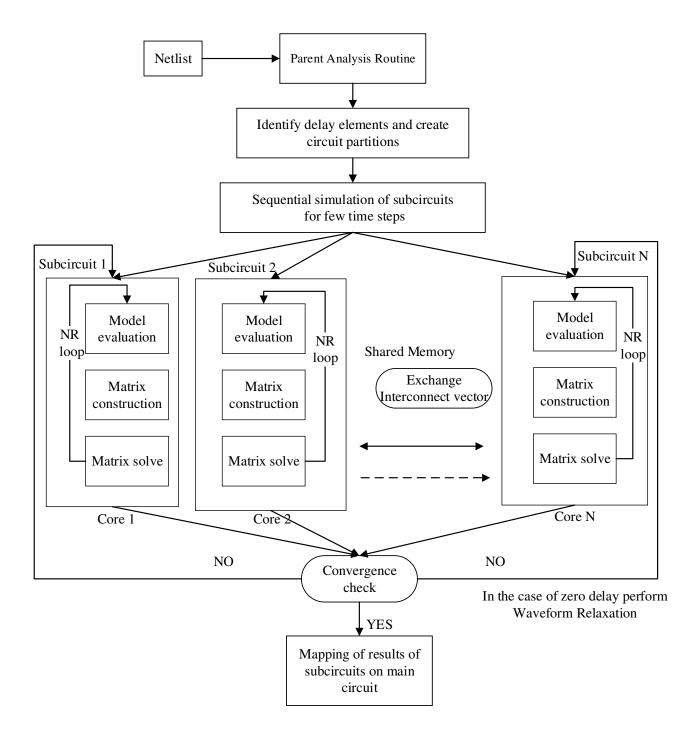

| 2.12 | Flowchart of parallel simulation of delay based partitioning                             | 28 |

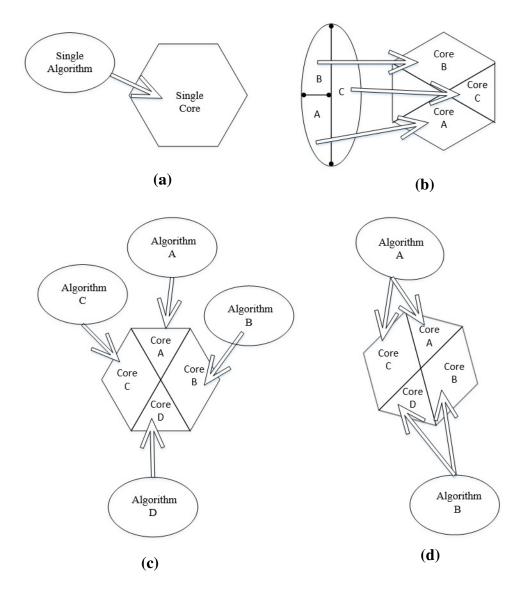

| 2.13 | Possible computing models of circuit simulation approaches                               |    |

|      | (a) Single algorithm on single core processor                                            |    |

|      | (b) Single algorithm on multi-core CPU                                                   |    |

|      | (c) Multialgorithm on multicore CPU and (d) Hierarchical multialgorithm on multicore CPU | 32 |

| 3.1  | Example circuit network                                                                  |    |

| 3.2  | System of equations                                                                      | 36 |

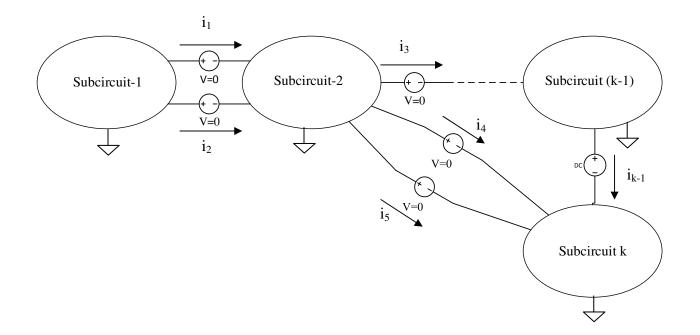

| 3.3  | General circuit diagram to explain partition approach                                    |    |

| 3.4  | Jacobian matrix block                                                                    |    |

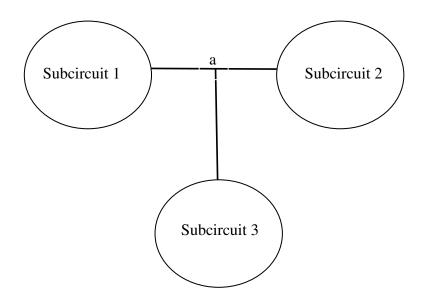

| 3.5  | General circuit diagram of three subcircuits sharing same node a                         | 39 |

| 3.6  | External currents arrangement in N blocks                                       |

|------|---------------------------------------------------------------------------------|

| 3.7  | General circuit diagram of partitioned circuit for derivation                   |

| 3.8  | Algorithm of analysis based on nodal variables                                  |

| 3.9  | Algorithm flowchart of Newton method                                            |

| 3.10 | Partitioned linear circuit with nodal variables                                 |

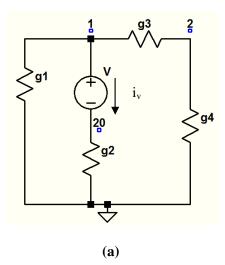

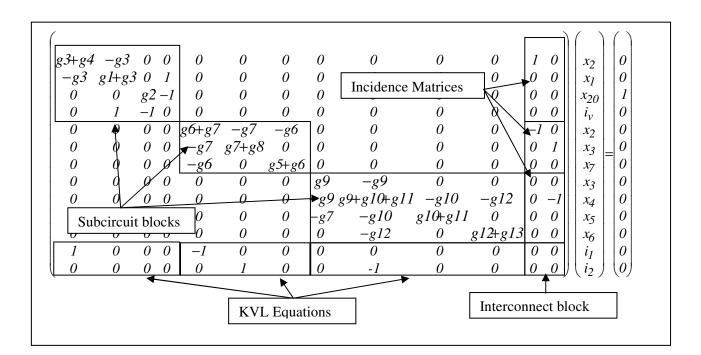

| 3.11 | Example (a) Subcircuit block (b) Nodal matrix blocks                            |

| 3.12 | System of equations                                                             |

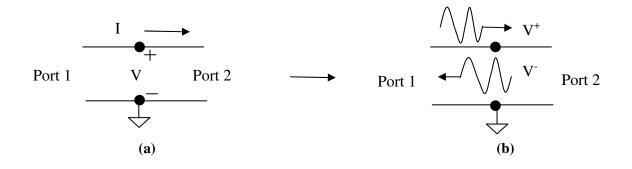

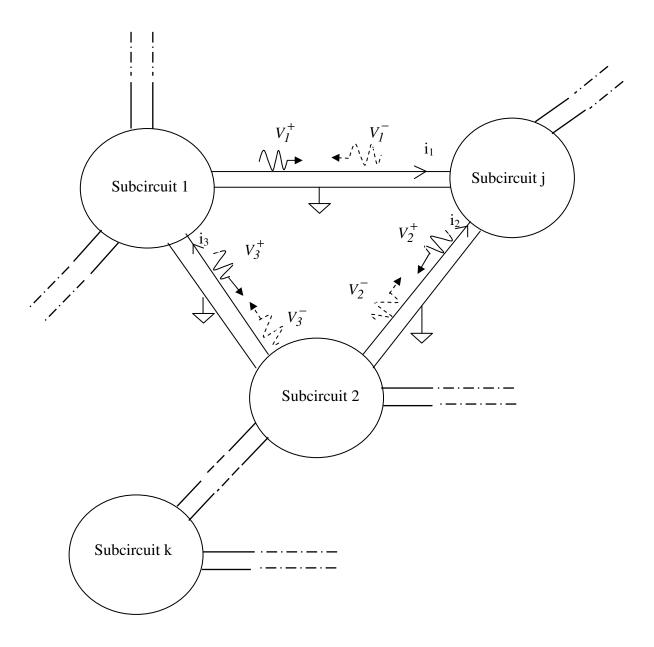

| 3.13 | Wave transformation from voltage and current variables                          |

|      | (a) voltage and current at external port (b) voltage waves at external port 50  |

| 3.14 | General circuit diagram for limitation of analysis based on waves               |

| 3.15 | General circuit diagram of partitioned circuit with waves                       |

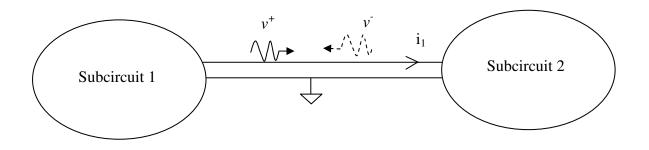

| 3.16 | General circuit network partitioned into two subcircuits                        |

| 3.17 | Reference algorithm flowchart of analysis based on scattering waves             |

| 3.18 | Partitioned linear circuit with waves                                           |

| 3.19 | Netlist example (a) Subcircuit block (b) Netlist of subcircuit                  |

| 3.20 | General circuit diagram with compensation network for EOP analysis              |

| 3.21 | Flowchart of EOP analysis                                                       |

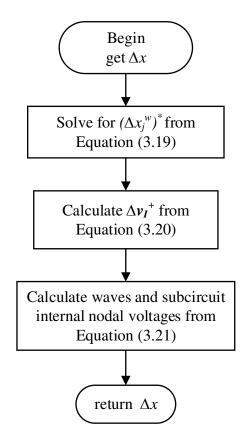

| 3.22 | Flowchart of WAVEOP analysis                                                    |

| 3.23 | Reference analysis code lines                                                   |

| 3.24 | Nonlinear circuit partitioned into two subcircuits                              |

| 3.25 | Soliton circuit network divided in four subcircuits                             |

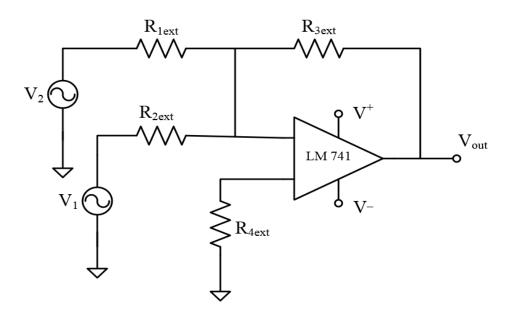

| 3.26 | Summing amplifier73                                                             |

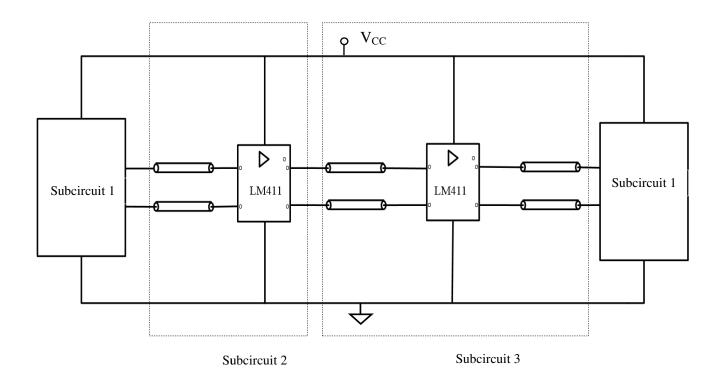

| 3.27 | Low noise microwave amplifier circuit                                           |

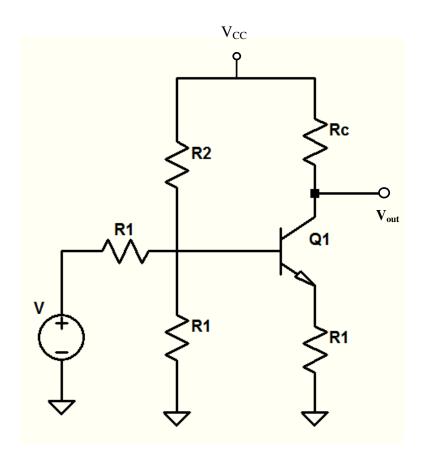

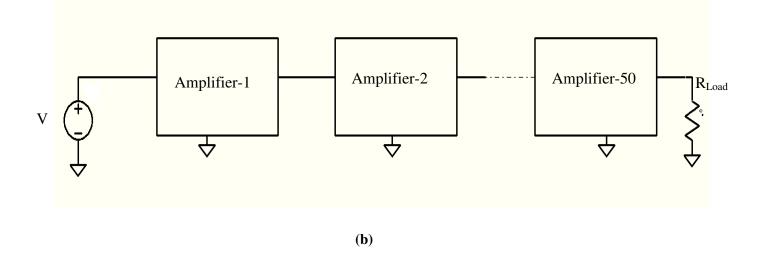

| 3.28 | Circuit example (a) Transistor amplifier circuit (b) 50 cascade amplifier chain |

## **List of Tables**

| 2.1  | Simulation results of PANEM, PANEM_MUL and                                      |    |

|------|---------------------------------------------------------------------------------|----|

|      | PANEM_MUL_L for circuit industry 1                                              | 20 |

| 2.2  | Simulation results for circuit Industry 5 (large industry                       |    |

|      | circuit having approx. 50k MOSFETs)                                             | 20 |

| 2.3  | Simulation results of modified multilevel Newton method                         | 21 |

| 2.4  | Performance results with 8 processors                                           | 25 |

| 2.5  | Percentage of total simulation time taken by various                            |    |

|      | steps during simulation on a single core                                        | 30 |

| 2.6  | Percentage reduction in the various steps of simulation in                      |    |

|      | delayed partitioned parallel simulation on multiple cores w.r.t.                |    |

|      | unpartitioned simulation on a single core                                       | 30 |

|      |                                                                                 |    |

| 3.1  | Parameters and their default values                                             | 62 |

| 3.2  | Simulation result summary of linear circuit                                     | 68 |

| 3.3  | Simulation result summary of nonlinear circuit                                  | 70 |

| 3.4  | Simulation result summary of soliton network divided in 4 subcircuits           | 71 |

| 3.5  | Simulation result summary of soliton network divided in 12 subcircuits          | 72 |

| 3.6  | Simulation result summary of summing amplifier circuit                          | 73 |

| 3.7  | Simulation result summary of low noise amplifier circuit                        | 75 |

| 3.8  | Simulation result summary of 50 cascade amplifiers                              | 77 |

| 3.9  | Simulation result summary of 500 cascade amplifiers divided in 500 subcircuits  | 77 |

| 3.10 | Simulation results summary of 500 cascade amplifiers divided in 5 subcircuits   | 78 |

| 3.11 | Simulation results summary of 500 cascade amplifiers divided into 5 subcircuits |    |

|      | with dense matrix                                                               | 79 |

# **List of Symbols**

- *x* Unknown nodal vector

- *b* Right hand side vector of linear matrix equation

- *x* Scalar variable

- $Z_0$  Reference impedance

- *s* Source vector

- $v^+$ ,  $v^-$  Voltage waves

- $i_k$  Nonlinear current vector of subcircuit k

- $i_I$  Interconnect current vector

- *n* Newton iteration index

- $A_j$  Subcircuit matrix block j

- $J_j$  Jacobian matrix of subcircuit j

- *k* Number of subcircuits

- *j* Subcircuit index

- $\Delta x$  Newton-Raphson update

# **List of Abbreviations**

| CPU         | - Central Processing Unit.                        |  |  |

|-------------|---------------------------------------------------|--|--|

| RF          | - Radio Frequency                                 |  |  |

| DC          | - Direct Current                                  |  |  |

| KCL         | - Kirchhoff's Current Law                         |  |  |

| KVL         | - Kirchhoff's Voltage Law                         |  |  |

| CAD         | - Computer Aided Design                           |  |  |

| NR          | - Newton-Raphson                                  |  |  |

| MLNA        | - Multilevel Newton Analysis                      |  |  |

| MLNR        | - Multilevel Newton-Raphson                       |  |  |

| DD          | - Domain Decomposition                            |  |  |

| PANEM       | - Parallel Newton Method                          |  |  |

| PANEM_MUL   | - Parallel Multilevel Newton Method               |  |  |

| PANEM_MUL_L | - Parallel Multilevel Newton Method with Latency  |  |  |

| OP          | - Operating Point Analysis                        |  |  |

| EOP         | - Operating Point Analysis with nodal variables   |  |  |

| WAVEOP      | - Operating Point Analysis with waves             |  |  |

| HMAPS       | - Hierarchical Multialgorithm Parallel Simulation |  |  |

# Chapter 1 Introduction

## 1.1 Motivation and Objective of This Study

As one of the most critical forms of pre-silicon simulation and verification, transistor-level circuit simulation (e.g., SPICE) is essential for the design of a very broad range of integrated circuits and systems such as custom digital integrated circuits (ICs), memories, analog, mixed signal, and radio-frequency (RF) designs [1]. Circuit simulation predicts circuit performance and makes it possible to disqualify a failing design for expensive chip fabrication. Equally, the ability of predicting circuit performance through simulation is at the core of any design process; it makes the implementation of complex integrated circuits technically feasible and economically viable while relaxing any heavy need for prototyping.

Performing expensive transistor- level circuit analysis consumes lots of CPU time. The simulation bottleneck significantly limits pre- silicon verification and design space exploration, contributing to long design turnaround time, suboptimal designs and even chip failures. With the advent of more complex device models and increased design complexity, high-capacity circuit simulation is strongly desirable in order to boost design productivity. One of the most effective ways to reduce the computing time is to use parallel processing. The necessary requirement for parallel processing is parallel hardware. Traditionally, the parallel processing was performed in supercomputers with multiple processors, but these computer is used as a processing unit and data is transferred via a local area network, like Ethernet. In the meantime, the industry's shift to the multi-core processor technology and emergence of new types of accelerators has introduced new challenges and opportunities for addressing today's CAD problems, including circuit simulation. Because the slowdown in single-core clock frequency scaling, there are limits in the performance of single-threaded CAD applications, new parallel algorithms and tools, which are able to utilize parallel hardware, have attracted great renewed interest. Parallel circuit

simulation naturally comes into the picture under this context. To this end, the main challenge is to develop highly scalable parallel simulation techniques so as to tackle computationally challenging simulation tasks while maintaining high accuracy and robustness across a wide range of circuit applications.

Simulation of large circuits suffers from excessive computational cost. In general, simulation cost is proportional to  $S^a$ , where S represents the original matrix size and a depends on the sparsity of the circuit matrix. For typical circuits, a varies from 1.1 to 2.4 [3]. The computational cost would be high if the S is large. For modern electronic circuits, S can be very large, in the range of several millions. Hence, it is desirable to approach the circuit simulation problem by dividing the original circuit into several smaller subcircuits, and solving each smaller subcircuit independently and in parallel. Merging the subcircuit results will get the solution of the original circuit.

Hence, what is needed is a method for accurate and fast analysis of large circuits and formulations that effectively partition the given problem while providing a mechanism requiring minimum computational cost to synchronize the solution among different partitions/processors. There have been earlier attempts to develop parallel simulation capabilities on multiprocessors, and supercomputers, either custom built or commercially available [4], [5], [6], [7], [8], [9]. On the other hand, the recent industry's shift to multi and many core processor technology has literally made every modern-day desktop, server, and laptop a parallel computer [10], [11], [12], [13]. This shift toward chip multiprocessors (CMPs) reflects the fundamental performance and power tradeoffs in lieu of VLSI technology scaling. The main contribution of this thesis is to investigate the performance of some circuit decomposition techniques for efficient parallel circuit simulation. Effective parallel circuit simulation requires minimal communication between processors. This thesis presents two main approaches : Circuit decomposition based on nodal variables and based on scattering waves. In the former approach partitioned subcircuits exchange nodal variables i.e. voltage and current, while in the latter approach subcircuits exchange scattering waves.

A node-tearing process is used to divide the system Jacobian in blocks. The first formulation is based on the nodal voltages and currents at the interface nodes. Although this formulation is not new, until recently branch-tearing was preferred because it requires less number of variables. It will be shown in this thesis that the node-tearing approach results in a simpler matrix structure that is more convenient for parallel analysis. In addition, the node-tearing formulation can be modified to use scattering wave variables at the subcircuit interfaces instead of voltages and currents. This approach is also explored in this work. A formulation based on wave variables is attractive because they can handle open- and short-circuit conditions without the numerical problems that may arise when using voltage and currents. For example, if a non-zero voltage is assumed across a short-circuit, the corresponding current is infinite. The use of waves also enables the use of a simpler convergent relaxation approach [3] to exchange information between subcircuits. Both reference algorithms have been implemented in the Cardoon circuit simulator [14].

## **1.2 Thesis Overview**

The thesis is composed of four chapters. The basic concepts and literature review is presented in Chapter 2. Chapter 3 shows design procedure and simulation results of circuit decomposition based on nodal variables and scattering waves. In the last chapter conclusion and proposed direction of future work is discussed.

# Chapter 2 Literature Review

## **2.1 Introduction**

As circuit sizes increase, it is essential to improve the performance of simulations without sacrificing the accuracy of the results. The larger the circuit, the larger the computational cost. For modern electronics, circuits can be very large, in the range of several millions nodes. Hence it is desirable to approach the circuit simulation problem by dividing the original circuit into several small subcircuits by decomposition. The decomposition can be performed using specific partitioning algorithms. Here, we do not consider how the partition is performed but, as a guideline, the optimal partition has only a few connections when compared with the size of the subcircuit should be of about the same size for load balancing. This thesis focuses on how system of equations can be solved effectively in parallel assuming circuit is partitioned into several subsystems and hence this chapter presents different approaches to solve nodal equations efficiently in blocks rather than the partitioning approach. In all approaches it is assumed that circuit is readily partitioned into subcircuits.

In the following section, basic concepts like Newton method, nodal analysis and Diakoptics are explained, formulations based on domain decomposition are summarized in Section 2.3 and other formulations are discussed in Section 2.4.

## **2.2 Basic Concepts**

## 2.2.1 Newton Method

Newton's method often called Newton-Raphson method, particularly in the engineering literature is the most successful method for the numerical solution of nonlinear problems provided with some differentiability. Because its idea of successive linearization is so fundamental, there are many possible applications.

Suppose that a solution of a nonlinear equation

$$f(x) = 0 \tag{2.1}$$

is to be found, where *f* is a differentiable function for which a root is sought. Newton's Method solves this nonlinear equation iteratively. Let, f'(x) be derivative of function *f*, and iteration index is *n*. At *n*+1 iteration, by taking first order Taylor's expansion, we approximate nonlinear function f(x) into linear function:

$$f(x^{n+1}) = f(x^n) + f'(x^n)(x^{n+1} - x^n).$$

(2.2)

This is linearization of f(x) around n+1. Newton's method in one dimension is obtained by making  $x^{n+1}$  equal to the root of the linear approximation at n+1 iteration. The correction  $(\Delta x^{n+1})$  at iteration n+1 is given by:

$$\Delta x^{n+1} = x^{n+1} - x^n = -\frac{f(x^n)}{f'(x^n)}.$$

(2.3)

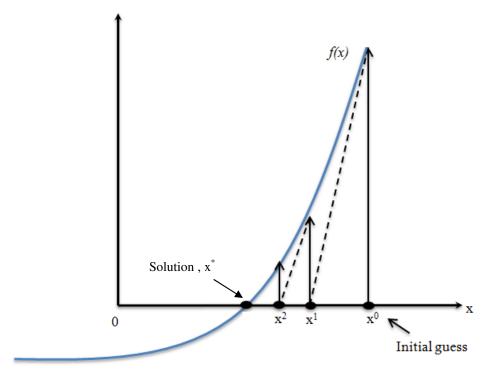

Figure 2.1 explains Newton's method. Suppose that solution of the function f(x) is to be found then Newton method iterates with initial guess  $x^0$ .  $x^1$  and  $x^2$  are the approximations to the solution of f(x) at iteration 2 and 3, respectively.  $x^*$  is the solution of f(x).

Figure 2.1 Newton's Method

Now for multidimensional Newton method, consider nonlinear system of equation,

$$F(x) = 0 \tag{2.4}$$

where x is nodal voltage vector, F(x) is a differentiable vector function. The correction at each iteration is the following:

$$\Delta x^{n+1} = x^{n+1} - x^n = -J_F(x^n)^{-1}F(x^n)$$

(2.5)

where  $J_F$  is Jacobian matrix of F and it is defined as,

$$\boldsymbol{J}_{F} = \begin{bmatrix} \frac{\partial F_{I}(x)}{\partial x_{I}} & \cdots & \frac{\partial F_{I}(x)}{\partial x_{k}} \\ \vdots & \ddots & \vdots \\ \frac{\partial F_{k}(x)}{\partial x_{I}} & \cdots & \frac{\partial F_{k}(x)}{\partial x_{k}} \end{bmatrix}.$$

Equation (2.5) is solved iteratively until convergence. Convergence check is done by checking condition  $\|\Delta x\| \le tolerance$ , where  $\|\Delta x\| = x^{n+1} - x^n$ . When iterations get close to the solution *i.e.*  $\|\Delta x\| \approx tolerance$  then convergence rate is quadratic.

## 2.2.2 Nodal Analysis

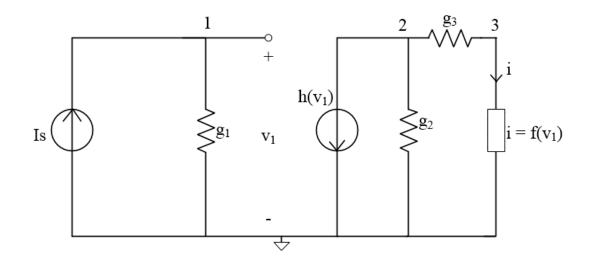

The circuit equations can be created using nodal analysis [15]. Nodal equations are created by formulating Kirchhoff current law (KCL) for all nodes, except for the reference node. These nodal voltages are assigned with respect to a reference node. This reference node is denoted as ground. A simple circuit example for nodal analysis is shown in Figure 2.2.

Figure 2.2 Example circuit to explain Nodal analysis

To write a nodal analysis for a circuit shown in Figure 2.2 first identify nodes and assign one node as the reference node. After that write KCL at each node. All nodal equations can be expressed as:

$$i = f(v). \tag{2.6}$$

Writing KCL for circuit shown in Figure 2.2 for each node except reference node gives:

KCL at node 1:  $g_1 v_1 - I_s = 0$ KCL at node 2:  $h(v_1) + g_2 v_2 + g_3(v_2 - v_3) = 0$ KCL at node 3:  $-g_3(v_2 - v_3) + f(v_1) = 0.$  (2.7)

A set of equations (2.8) can be written in matrix form as:

$$\begin{pmatrix} g_{1} & 0 & 0 \\ 0 & g_{2} + g_{3} & -g_{3} \\ 0 & -g_{3} & g_{3} \end{pmatrix} \begin{pmatrix} v_{1} \\ v_{2} \\ v_{3} \end{pmatrix} + \begin{pmatrix} 0 \\ h(v_{1}) \\ f(v_{1}) \end{pmatrix} = \begin{pmatrix} I_{s} \\ 0 \\ 0 \end{pmatrix}$$

(2.8)

Now let the nonlinear system of equations be

$$F(x) = s$$

$$F(x) - s = 0$$

(2.9)

where x is nodal voltage vector, F is a differentiable function and s is source vector. Now comparing Equation (2.8) and (2.9) yields :

$$F(\mathbf{x}) = \underbrace{\begin{pmatrix} g_1 & 0 & 0 \\ 0 & g_2 + g_3 & -g_3 \\ 0 & -g_3 & g_3 \end{pmatrix}}_{\mathbf{G}} \underbrace{\begin{pmatrix} v_1 \\ v_2 \\ v_3 \end{pmatrix}}_{\mathbf{x}} + \underbrace{\begin{pmatrix} 0 \\ h(v_1) \\ f(v_1) \end{pmatrix}}_{\mathbf{i}(\mathbf{x})}, \ \mathbf{s} = \begin{pmatrix} I_s \\ 0 \\ 0 \end{pmatrix}$$

Hence from Equation (2.9)

$$F(x) - s = G x + i(x) - s = 0$$

(2.10)

where, Gx is linear contribution of the function F and i(x) is nonlinear contribution of function F. Applying Newton's method to Equation (2.10) will get :

$$x^{n+1} = x^n - J_F^{-1} \left( F(x^n) - s \right)$$

$$J_F \Delta x^{n+1} = - \left( F(x^n) - s \right) = s - Gx^n - i(x^n)$$

(2.11)

But  $J_F = G + J_i$ . where  $J_F$  is Jacobian of function F and  $J_i$  is Jacobian of current vector i(x). Using this relation Equation (2.11) can be written as:

$$[G+J_i] \Delta x^{n+1} = s - Gx^n - i(x^n).$$

(2.12)

9

## 2.2.4 Diakoptics

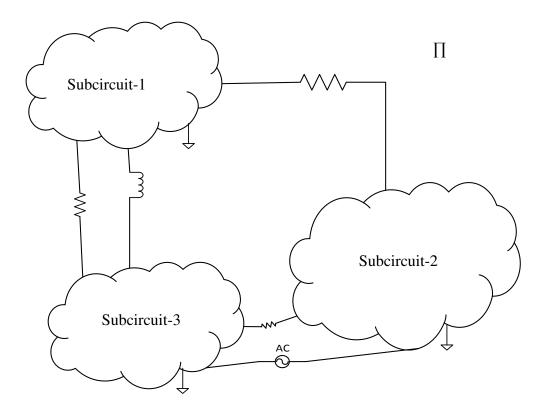

Diakoptics [16] is tearing down an electric network into sub-systems, in other words the circuit is partitioned into subcircuits. Figure 2.3 shows a circuit network  $\prod$  partitioned into three subcircuits. Components outside of subcircuits are part of the interconnect block.

Figure 2.3 General Circuit Diagram to explain Diakoptics

Kron [17], [18] derived the equations resulting after partitioning a network into k subcircuits. Now suppose linear circuit network  $\prod$  is defined by:

$$A x = b \tag{2.12}$$

where A is nodal matrix, x is unknown voltage vector and b is source vector. Now Equation (2.12) could be partitioned into k subsystems :

where,  $A_j$  with j=1, 2, ..., k, is a matrix representing subcircuit j, depending on circuit partitioning approach the interconnect network spreads in  $A_j$ ,  $N_j$ ,  $M_j$  and C,  $x_1, x_2, ..., x_k$  are unknown internal nodal voltage vectors of subcircuits,  $x_{k+1}$  is interconnect nodal voltage vector,  $b_1, b_2, ..., b_k$  are source vectors of subcircuits and  $b_{k+1}$  is the source vector for interconnect block. There are two types of circuit decomposition is possible: branch tearing and node tearing. If circuit decomposition is done using branch tearing, links connecting to subcircuits are distributed to  $A_j$ ,  $N_j$ ,  $M_j$  and C blocks and create dependency between subcircuits. Node tearing will be discussed in detail in Chapter 3.

To solve Equation (2.13), unknown voltage vector for  $j^{th}$  subcircuit is found :

$$\boldsymbol{x}_{j} = \boldsymbol{A}_{j}^{-1} (\boldsymbol{b}_{j} - \boldsymbol{N}_{j} \, \boldsymbol{x}_{k+1})$$

(2.14)

Interconnect nodal voltages can be found as follows:

$$\sum_{j=1}^{k} M_{j} A_{j}^{-1} (b_{j} - N_{j} x_{k+1}) + C x_{k+1} = b_{k+1}$$

$$\left[ C - \sum_{j=1}^{k} M_{j} A_{j}^{-1} N_{j} \right] x_{k+1} = b_{k+1} - \sum_{j=1}^{k} M_{j} A_{j}^{-1} b_{j}$$

(2.15)

Now to evaluate system of equations (2.13), interconnect nodal voltage  $x_{k+1}$  is calculated first from Equation (2.15) and then subcircuit nodal voltage  $x_i$  can be found from Equation (2.14).

For an example of Diakoptics consider a linear circuit network shown in Figure 2.4. This circuit is divided in three subsystems: two subcircuits and one interconnect block.

### Figure 2.4 Example Circuit for Diakoptics

Likewise, for a nonlinear circuit, Diakoptics is applied to solve each Newton iteration.

## **2.3 Formulations Based on Domain Decomposition**

Domain decomposition method refer to a collection of divide-and-conquer techniques which have been primarily developed for solving Partial Differential Equations [19], [20]. Domain decomposition refers to a class of methods for solving linear or nonlinear systems of equations, primarily arising from the discretization of partial differential equations (PDEs). In a way that is mostly relevant to the focus of this thesis, a domain decomposition method finds the solution to a large system by subdividing it into smaller sub-domains and solving these sub-domains separately. This section discusses different domain decomposition approaches.

## 2.3.1 Multilevel Newton Method [21]

#### **Multilevel Newton Method**

To speed-up simulation, one possible improvement that can be achieved from NR method is parallelization. In order to further improve the speed, other iteration methods than NR iteration may be utilized. Digital circuits are usually modular, latent, and unidirectional *i.e.* loosely coupled. Because block, waveform, and nonlinear relaxation methods utilize these properties, they have been found suitable for this kind of circuits. These methods cannot apply effectively to the analog circuits, which usually are tightly coupled. Multilevel Newton method is one of the methods that can be effectively applied in parallel processing [21].

Two characteristics of many electronic circuits are discussed for a more efficient analysis :

- 1. Many electronic circuits consist of identical repetitive sub-networks. This characteristic is utilized by macromodeling.

- 2. Many electronic networks contain sub-networks which are inactive *i.e.* their electrical variables are constant most of the simulation time.

#### Macromodels

A macromodel of a network is defined as a set of nonlinear and/or time varying elements simulating external behaviour of the sub-network. It consists of a set of nonlinear and/or time

varying elements. Some papers e.g. [22] use macromodels represented by circuit elements or equations which approximate the external behaviour of subnetwork whereas reference [21] define macromodel such that the external behaviour of the circuit is exactly represented by the macromodel.

Consider an example for macromodel: Let  $\prod$  be the large-scale network composed of interconnected sub-networks  $S_i = S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$  (Figure 2.6).

Figure 2.6 Example circuit network (  $\prod$  ) to explain macromodel

Let S be a subnetwork (Figure 2.7(a)) of whole circuit network  $\prod$  (Figure 2.6) to be represented by macromodel. Figure 2.7(b) is macromodel of subnetwork S.

Figure 2.7 Example of macromodel (a) subnetwork S of circuit network ∏ (b) Macromodel of subcircuit S which represents its external behaviour.

The algorithm of multilevel newton method using Macromodel is as follows:

Let the equations describing behaviour of circuit network  $\prod$  having only one subcircuit S,

$$F(u, G(x_{int}), x_{ext}) = 0$$

(2.16)

where u is the vector of inputs,  $x_{int}$  is internal variables of subcircuit S,  $G(x_{int})$  is a macromodel of subnetwork S,  $x_{ext}$  is the vector of interconnect (external) variables in  $\prod$  not communicating with S.

Applying Newton's algorithm to Equation (2.16) by updating only outer variables and keeping internal variables of macromodel  $G(x_{int})$  constant will get :

$$x_{ext}^{n+1} = x_{ext}^n - (J_F(x_{ext}^n))^{-1} F(x_{ext}^n)$$

(2.17)

where  $J_F$  is Jacobian of function F (Equation 2.16) with respect to variable  $x_{ext}$  ( $x_{int}$  is constant),  $x_{ext}^{n+1}$  is value at next Newton iteration step,  $x_{ext}^n$  is previous value of Newton iteration and n is iteration index.

Now, to evaluate macromodel  $G(x_{int})$  another Newton method is applied to equations representing macromodel. Equation (2.18) represents macromodel :

$$H(u, x_{int}, y) = 0$$

(2.18)

where y is output vector. In this Newton method only update inner variables  $x_{int}$  and keep outer variables u constant :

$$x_{int}^{n+1} = x_{int}^{n} - (J_H(x_{int}^{n}))^{-1} H(x_{int}^{n})$$

(2.19)

$J_H$  is Jacobian of macromodel with respect to  $x_{int}$  and y. Keep iterating until it converges. Convergence condition is given by :

$$|\Delta x_{int}|| < |\Delta x_{ext}||$$

where  $\Delta x_{int} = x_{int}^{n+1} - x_{int}^{n}$  is error in subcircuit nodal voltages and  $\Delta x_{ext} = x_{ext}^{n+1} - x_{ext}^{n}$  is error in interconnect nodal voltages. Here, Newton's algorithm applied twice on Equations (2.16) and (2.18), that's why this method is called multilevel Newton's algorithm.

#### Latency

The second characteristic of the network is latency. Suppose that in the electrical network to be analyzed, at any particular time  $t_1$ , most of the subcircuits are latent *i.e.* the value of their electrical variables remain constant. Latency is used to speed up the analysis in logic simulation when only the active part of the circuit is analysed which is called event driven simulation. Basically, when any subcircuit is found to be latent at a certain instant of time e.g.  $t_2$ , then obviously no function or Jacobian evaluations are needed to find the value of the subcircuit variables at all the subsequent time steps until a change in the input variables of the subnetwork occurs. In other words, the corresponding element in Jacobian of the circuit equation are not evaluated at  $t_2$  and the value of the subcircuit variables is set to the one taken at time  $t_1$  [21]. Latency approach is more effective for digital circuits as they are usually modular and latent. Use of latency can achieve significant savings in computer time. An additional advantage is that it can easily deal with asynchronous designs. Latency can be used for timing analysis including the usage of multi-delay model. This aspect is not implemented in this thesis.

## 2.3.2 New Approach for Parallel Circuit Simulation [23]

A new approach for parallel simulation of very large scale integration (VLSI) circuit on a transistor level is presented [23]. Authors proposed circuit partitioning algorithms along with formulation for parallel circuit simulation. Three algorithms are presented:

- I. Parallel Newton Method

- II. Parallel Multilevel Newton Method

- III. Parallel Multilevel Newton Method with Latency

Supose that linear system of equations to be solved at each Newton iteration is presented by :

$$Ax = b \qquad (2.20)$$

Diakoptics [17] is used to implement parallel simulation. These three algorithms are implemented on Equations (2.14) and (2.15) mentioned in Section 2.2.4 Diakoptics. For quick reference equations are rewritten below :

$$x_{j} = A_{j}^{-1} (b_{j} - N_{j} x_{k+1})$$

$$\left[ C - \sum_{j=1}^{k} (M_{j} A_{j}^{-1} N_{j}) \right] x_{k+1} = b_{k+1} - \sum_{j=1}^{k} M_{j} A_{j}^{-1} b_{j}.$$

Decomposition of Equation (2.20) leads to the decoupled nonlinear system:

$$F(\boldsymbol{x}_j, \boldsymbol{x}_{k+1}) = \boldsymbol{0} \tag{2.21}$$

$$\boldsymbol{G}(\boldsymbol{x}_{j}, \boldsymbol{x}_{k+1}) = \boldsymbol{0} \tag{2.22}$$

where j = 1, ..., k, F is subcircuits (A blocks) and G is interconnect (coupling) system whose elements are spread in M, N and C blocks (Equation 2.13). Every subcircuit j is represented by its own nonlinear system (2.21) and dependencies between each subcircuits are given by Equation (2.22). Figure 2.8 shows Newton's method for the decoupled nonlinear equation systems (Equations (2.21) and (2.22)) [23]. Computation is divided between master and slave processors.

```

Start : (x_1^0, \dots, x_i^0, x_{k+1}^0); n = 0

repeat

Slaves:

Do parallel j=1,\ldots,k

J = L_j U_j

(LU decomposition)

S_{j}^{n} = M_{j} * (A_{j})^{-I} * N_{j} (Forward and backward substitution)

w_{j}^{n} = M_{j} * (A_{j})^{-1} * b_{j}

send S_{j}^{n} and w_{j}^{n} to master

endi

Master:

S^n = C - \sum_{i=1}^k S_j^n

w^{n} = G(x_{1}^{n}, ..., x_{k}^{n}, x_{k+1}^{n}) - \sum_{i=1}^{k} w_{j}^{n}

S^n * \Delta x_{k+1}^n = w^n

(Serial computation of linear system)

send \varDelta x_{k+I}^n to slaves to calculate internal nodal voltages.

Slaves:

Do parallel k=1,\ldots, j

Do forward and backward substitution

\Delta x_{j}^{n} = (J)^{-1} * (F_{j}(x_{k}^{n}, x_{k+1}^{n}) - N_{j} * \Delta x_{k+1})

\Delta x_i^{n+1} = x_i^{n+1} - x_i^n

(Update)

endj

```

## Figure 2.8 Parallel Newton's algorithm

The algorithms shown in Figure 2.8 can be classified in three main steps:(i) Slave processors calculate  $S_j$  and  $w_j$  for each subcircuit and sent these variables to master processor. (ii) Master processor calculates  $S^n$ ,  $w^n$ , interconnect nodal voltage vector  $x_{k+1}$  and send  $x_{k+1}$  to slave processors. (iii) Slave processors calculates subcircuit nodal voltages for each subcircuit using  $x_{k+1}$ . However, this simple approach has the following potential limitation. Since several Newton iterations may be needed before the solution to the nonlinear system converges, there may be a considerable amount of inter-processor communication, which limits the efficiency of the parallel simulation.

A trade-off can be made between communication and computation by introducing the multilevel Newton Method. In this case, one Newton iteration consists of an inner iteration loop and an outer Newton update step. In the inner iteration loop, each local nonlinear equation is iteratively solved to converge under a fixed outer (interface) variable vector  $\Delta \mathbf{x}_{k+1}$  to update all local variables  $\mathbf{x}_1$ ,  $\mathbf{x}_2$ ....,  $\mathbf{x}_k$ . Then an outer Newton step is taken to update outer variable vector  $\Delta \mathbf{x}_{k+1}$  based on the solutions received from the slaves. Finally, to complete one Newton iteration for the entire system, a Newton step is taken to correct all local variables  $\mathbf{x}_1$ ,  $\mathbf{x}_2$ ....,  $\mathbf{x}_k$  using the updated  $\Delta \mathbf{x}_{k+1}$ . Since more work is done at the slave level in the above multilevel Newton method, the number of top-level Newton iterations may be reduced, leading to less communication between the slaves and the master. The conditions under which the multilevel Newton method maintains local quadratic convergence was provided in [21].

Latency can be also exploited under this multilevel framework [21], [23]. PNAM\_MUL method is efficient if there is a sufficient decrease of the interconnect variables in the outer iteration, in that case slave processors do not need to evaluate the outer derivative. Sending the matrices  $S_j$  to the master processor causes the main part of the communication. In case of latency, these matrices do not have to be sent to the master process. Only the inner variables have to be transmitted to the master. One condition latency = *true* is added in PANEM\_MUL algorithm. If this condition satisfies then slave neither have to evaluate  $S_j$  matrices nor have to send it to the master process.

### **Simulation Results**

The parallel multilevel Newton method was demonstrated as part of the TITAN simulator, running on both computer clusters and shared-memory multiprocessors [23]. Good parallel speedups were demonstrated up to eight processors. Table 2.1 shows the comparison of three algorithms PANEM, PANEM\_MUL AND PANEM\_MUL\_L with required number of iterations to simulation CPU time to simulate circuit industry 1. Table 2.2 shows the CPU time for simulation, speedup and number of interconnect for circuit industry 5.

Table 2.1 Simulation results of PANEM, PANEM\_MUL and PANEM\_MUL\_L for circuit industry

1

| Method      | #iterations(DC/TR) | Real simulation CPU-time (min:sec) |

|-------------|--------------------|------------------------------------|

| PANEM       | 59/222             | 34:35                              |

| PANEM_MUL   | 11/158             | 27:28                              |

| PANEM_MUL_L | 11/158             | 21:59                              |

Table 2.2 Simulation results for circuit Industry 5(large industry circuit having approx. 50k MOSFETs)

|                                               | 1 processor | 4 processors | 8 processors |

|-----------------------------------------------|-------------|--------------|--------------|

| Real simulation<br>CPU-<br>time(hour:min:sec) | 5:07:12     | 1:17:49      | 0:39:26      |

| Speedup                                       | -           | 3.95         | 7.79         |

| #interconnect                                 | -           | 7            | 8            |

#### Modified Multilevel Newton Method [24]

The New Multilevel Newton-Raphson Method is modified from the multilevel Newton method [21]. Good global convergence can be achieved by adjusting inner iterations and local quadratic convergence is achieved [24].

Authors used Diakoptics [17] method to implement parallel circuit simulation as discussed in Section 2.2.4. This approach is slightly modified from Reference [21]. It is the exact same process from Equations (2.10) to (2.12) without defining a macromodel. In New Multilevel

Newton Method, instead of taking global NR steps [24], the iterations are taken at multiple levels. Between each outer NR step only fixed number of inner iterations (q) are taken to synchronise local and global convergence *i.e.* for load balancing. At each outer iteration instead of updating only outer variables, update all variables. In this way overall convergence would be faster by achieving local quadratic convergence.

#### Simulation Results of modified Multilevel Newton Method

Simulation Results of modified Multilevel Newton Method for a circuit with 1440 BJTs and 7746 nodes is shown in Table 2.3, where p is number of outer iterations and q is the number of inner iterations. This circuit is partitioned into 3 subcircuits and simulated with three processors. Processing time is the time to decompose the whole circuit network into subcircuits, symbolic recording of sparse matrix etc.

| q | р  | Preprocessing<br>time | Iteration time | total |

|---|----|-----------------------|----------------|-------|

| 0 | 19 | 9.0 s                 | 2.6 s          | 11.6  |

| 1 | 13 | 9.0 s                 | 2.6 s          | 11.6  |

| 2 | 6  | 9.0 s                 | 1.9 s          | 10.9  |

| 3 | 5  | 9.0 s                 | 1.7 s          | 10.7  |

Table 2.3 Simulation results of modified multilevel Newton method

Even though load balancing can be achieved by fixed number of iterations, total number of iterations for small subcircuits will be different than big subcircuit blocks *i.e.* small subcircuit may converge faster than big subcircuit block having more internal nodes compare to small subcircuits.

## 2.3.3 Formulation with Binary Link [25]

This algorithm formulates the interface vectors between partitions, through binary vectors, leading to enhanced parallelism, scalability and reduced CPU costs while synchronizing the solutions between various partitions. The CPU cost per iteration as a function of the number of links *L* between subcircuits is in the order of  $L^2$ . That leads to poor scalability as its complexity increases. This reference [25] proposed an algorithm that exhibits superior scalability as its complexity increases only in order of *L*.

#### Chapter 2 Literature Review

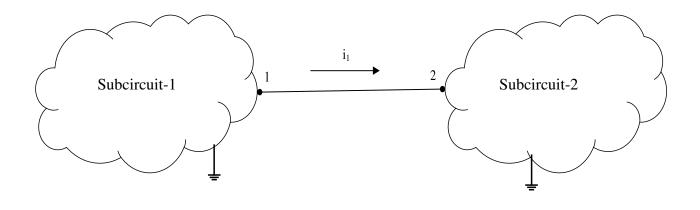

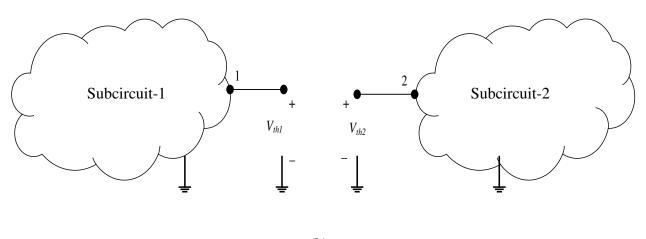

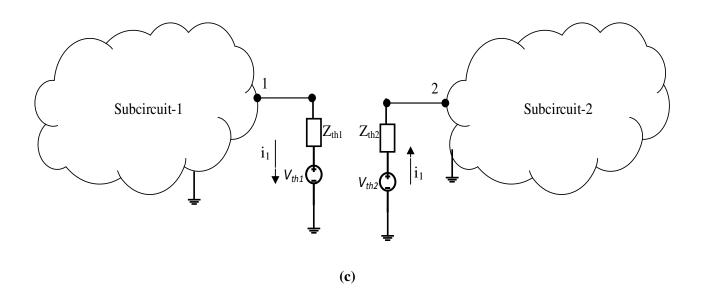

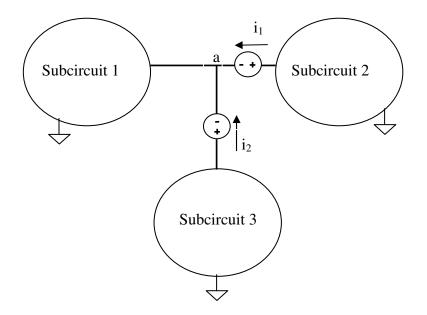

Node tearing (decomposition) technique [16], [26] is used to partition circuit into several subcircuits. Consider a circuit divided in two subcircuits using node tearing as shown in Figure 2.9. Figure 2.9 shows procedure to find out external current along this link (current  $i_1$ ) by finding Thévenin equivalent. Open circuit port voltages  $V_{th1}$  and  $V_{th2}$  can be found with independent sources of subcircuits enabled as show in Figure 2.9 (b). Thévenin equivalent impedance for each subcircuit can be calculated by connecting a unit current source to each port and deactivate the independent sources of circuits. Now from open circuit voltages  $V_{th1}$  and  $V_{th2}$  and Thévenin equivalent impedance ( $Z_{th1}$  and  $Z_{th2}$ ) external current  $i_1$  flowing from subcircuit-1 to subcircuit-2 can be found by

$$i_{I} = \frac{V_{thI} - V_{th2}}{Z_{thI} + Z_{th2}} .$$

(2.23)

**(a)**

#### Chapter 2 Literature Review

**(b)**

## Figure 2.9 Thévenin equivalent measurement to find external current (a) Example of node tearing (b) Measurement of V<sub>th</sub> (c) Link current (i<sub>1</sub>) measurement (Equation 2.23)

A binary selector column vector  $N_1$  is constructed where the row of *node 1* is +1 and rest are zero. Number of rows are equal to subcircuit block  $A_1$ , which is MNA matrix for subcircuit 1. Likewise binary selector column vector  $N_2$  is constructed for subcircuit 2 where row of *node 2* is -1 and rest are zero.

The system of equations for the circuit shown in Figure 2.9 is :

$$\begin{pmatrix} A_1 & \boldsymbol{0} & N_1 \\ \boldsymbol{0} & A_2 & N_2 \\ N_1^T & N_2^T & \boldsymbol{0} \end{pmatrix} \begin{pmatrix} \boldsymbol{v}_1 \\ \boldsymbol{v}_2 \\ \boldsymbol{i}_1 \end{pmatrix} = \begin{pmatrix} \boldsymbol{b}_1 \\ \boldsymbol{b}_2 \\ \boldsymbol{b}_3 \end{pmatrix}.$$

(2.24)

Now the overall matrix for k subcircuits will have the following form :

$$F(\mathbf{x}) = \begin{pmatrix} A_1 & & N_1 \\ & A_2 & & N_2 \\ & & \ddots & & \vdots \\ & & & A_k & N_k \\ N_1^T & N_2^T & \cdots & N_k^T & \mathbf{0} \end{pmatrix} \begin{pmatrix} \mathbf{x}_1 \\ \mathbf{x}_2 \\ \vdots \\ \mathbf{x}_k \\ \mathbf{i}_E \end{pmatrix} = \begin{pmatrix} \mathbf{b}_1 \\ \mathbf{b}_2 \\ \vdots \\ \mathbf{b}_k \\ \mathbf{0} \end{pmatrix}$$

(2.25)

where,  $i_E$  is external current vector flowing from one subcircuit to another. Now rewriting Equations (2.14) and (2.15) using notation used in Equation (2.25)

$$\boldsymbol{x}_{j} = \sum_{j=1}^{k} \boldsymbol{A}_{j}^{-1} (\boldsymbol{b}_{j} - \boldsymbol{N}_{j} \boldsymbol{i}_{E})$$

(2.26)

$$(-\sum_{j=1}^{k} (N_{j}^{T} (A_{j})^{-1} N_{j}) i_{E} = -\sum_{j=1}^{k} N_{j}^{T} (A_{j})^{-1} b_{j}$$

(2.27)

Now for more than two subcircuits (e.g. k subcircuits) the Thévenin equivalent impedance matrix defined is:

$$Z = -\sum_{j=1}^{k} (N_{j}^{T} (A_{j})^{-1} N_{j}$$

(2.28)

and the external currents flowing from one subcircuit to another is given by

$$i_E = -Z^{-1} \sum_{j=1}^k N_j^T (A_j)^{-1} b_j.$$

(2.29)

using relation given in (2.28) in Equation (2.27). Now the entire system can be solved by two Equations (2.26) and (2.29) iteratively. Matrices  $M_j$ ,  $N_j$  and C in Equation (2.13) for [21], [23] and [24] approaches contain original nodal variables and are non-binary matrices. Consequently, solution cost of interconnecting equations (solved on a master processor) as well as the

#### Chapter 2 Literature Review

communication cost among slaves and the master processor grow rapidly with the increasing number of partitions. This causes poor scalability with the increasing number of processors and partitions. Reference [25] minimizes the computations required for interfacing various parallel blocks as well as minimizes the communication overhead between the processors involved. This is accomplished by efficient form of node splitting, during Newton Raphson iterations, at any time point. At each NR iteration, since the resulting circuit is linear, the technique of node tearing can be applied at the identified partitioning nodes, leading to coupling vectors (linking various resulting subcircuits) that are purely binary in nature, and an impedance matrix whose dimension depends on the number of links between various partitions.

This approach is similar to the formulations presented in Section 3.1 of this thesis. That formulation was developed independently of this reference.

#### **Simulation Results**

Here each circuit network is simulated with two implementations : one using node tearing and other using branch tearing. The circuit partitioning is performed by hMETIS [27], [28]. Each subcircuit was simulated on a single processor. In reference [25] simulation is done using up to 16 CPUs but here to summarize simulation result with only 8 processors are shown in Table 2.4 with analysis time and speed up. The speedup is measured relative to a standard simulation using a traditional LU solver, with no parallelism or partitioning. Table 2.4 shows simulation result summary of DSP example, SRAM, dual SRAM and Array Multiplier Example.

| Examples         | Branch Tearing |          | Node Tearing  |          |

|------------------|----------------|----------|---------------|----------|

|                  | Analysis Time  | Speed up | Analysis time | Speed up |

| DSP              | 480.4 s        | 2.0      | 187.2s        | 5.1      |

| SRAM             | 399.0 s        | 1.9      | 148.2s        | 4.6      |

| Dual SRAM        | 378.0s         | 2.2      | 139.0s        | 6.0      |

| Array Multiplier | 682.1s         | 1.9      | 261.3s        | 4.8      |

Table 2.4 Performance results with 8 processors

## **2.4 Other Formulations**

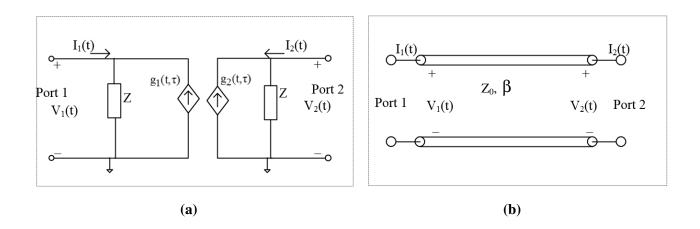

The technique proposed in [29] exploits the inherent delay present within some circuits. This delay element is used to partition a circuit network into several subcircuits and these subcircuits can be simulated on different cores of a shared-memory CPU. A delay element interfacing subcircuits is used to formulate the whole domain simulation.

Figure 2.10 shows delay elements. Figure 2.10(a) shows state-variable model of an ideal delay element and Figure 2.10(b) shows electrical circuit equivalent of the ideal lossless transmission line. The state variable model replicates a bidirectional delay so that circuit behavior at either port of the element does not affect the circuit at the opposite port until after a delay,  $\tau$ .

Figure 2.10 Delay Elements. (a) Ideal state variable based delay element. (b) Ideal lossless transmission line.

The simulated behavior of the delay element is given by the behavior of the state variables  $g_1$  and  $g_2$ , which depend upon the past voltage and current at ports 2 and 1, respectively. Figure 2.11 (a) shows two subcircuits connected with a delay element. This delay element partitioned into subdelay elements as shown in figure 2.11 (b) and those partitions can be iterated independently.

Figure 2.11 Partition of two subcircuits with delay element

To interface the NR-based iterations of each of the circuit partitions, a delay-based iterative scheme is used. In the case of finite delay, the top-level simulator iterates at the delay elements until voltages and currents at the delay element ports become consistent with the subcircuits connected to them. In the case of an instantaneous connection, *i.e.*, zero delay, equations are solved by means of waveform relaxation [30]. All subcircuits are solved independently and relaxation iterations at the delay elements match the voltages at the ports of the delay element. Figure 2.12 shows flowchart of parallel simulation of delay based partitioning [29].

Figure 2.12 Flowchart of parallel simulation of delay based partitioning

First of all, the netlist is analyzed by the parent analysis routine. Then, the delay elements whose two ports belong to different LRGs are identified. These delay elements represent the temporal isolation between the subcircuits connected to the corresponding delay element. The delay elements are then divided into two sub-delay elements which is also called partner sub-delay elements, as shown in Figure 2.11, resulting in two circuit partitions belonging to different LRGs. The circuit partitions thus formed are simulated sequentially in their circuit topological order initially for a few time steps ( $\Delta T$ ) within the parent routine. This builds history, which enables efficient automated parallel simulation of circuit partitions for the rest of the simulation time points. After initial sequential simulation, multiple child threads are allocated from the parent routine with the number of threads. The number of allocated threads depends on the number of circuit partitions and the number of available cores of the shared-memory multicore processor. Each child thread is assigned one circuit partition and directed to one of the available cores. Likewise, if *N* cores are available then *N* circuit subcircuits can be run in parallel [29]. Each circuit partition is simulated for  $D_F\Delta T$  time period, where  $D_F$  is delay factor described by relationship show in Equation (2.30) and  $\Delta T$  is fixed time step.

$$D_F = \frac{[\min(\tau_1, \tau_2, ..., \tau_N)]}{\Delta T}$$

(2.30)

The two partner sub-delay elements exchange their current and past state-variable-based current source values (called the interconnect vector) after each  $\Delta T$  time duration. The interconnect vectors are stored in a shared memory data structure. The individual circuit partitions are solved using the direct method that comprises three steps:

- 1) Model evaluation (linearization of nonlinear device characteristics and Jacobian matrix calculation)

- 2) Matrix build (construction of a sparse matrix equation)

- 3) Matrix solve (The solution of matrix equation coupled in an NR loop)

An error criterion is formulated in the parent routine to check convergence. In the case of zero delay element perform waveform relaxation. Each subcircuit iterates for  $D_F\Delta T$  time then sends results to the other subcircuits. Each subcircuit then will check whether it is consistent with previous solution. If the previous solution is not same as the current solution then iterate again till find consistent solution. At the end, subcircuit voltages and currents are mapped to the parent circuit voltages and currents after convergence is achieved.

#### **Simulation Results**

Simulation results for 8 different circuits are presented in [29] and 4 of them are listed in Table 2.5 with percentage of total simulation time taken by model evaluation, matrix build and matrix solve. Simulation results for unpartitioned chain of 12 frequency divider circuit, chain of 8 frequency multipliers, soliton line and 20-bit ripple carry adder are shown. Table 2.6 shows percentage of total simulation time reduced by partitioning circuit and simulated on different number of processors 2 and 8.

Table 2.5 Percentage of Total Simulation Time Taken by Various Steps During Simulation On a Single Core

| Circuits                        | Model Evaluation | Matrix build | Matrix Solve |

|---------------------------------|------------------|--------------|--------------|

| Chain of 12 frequency dividers  | 64               | 31.53        | 3.96         |

| Chain of 8 frequency multiplier | 32.20            | 56.93        | 10.34        |

| Soliton Line                    | 2.24             | 85.26        | 11.90        |

| 20 Bit Ripple Counter           | 54.9             | 40.53        | 4.21         |

Table 2.6 Percentage reduction in the various steps of simulation in delayed partitioned parallel simulation on multiple cores w.r.t. unpartitioned simulation on a single core

|                                    | Model E | valuation | Matri | x Build | Matri | x Solve |

|------------------------------------|---------|-----------|-------|---------|-------|---------|

| Cores                              | 2       | 8         | 2     | 8       | 2     | 8       |

| Chain of 12 frequency<br>dividers  | 50.81   | 90.10     | 74.83 | 98.6    | 45.93 | 90.83   |

| Chain of 8 frequency<br>multiplier | 47.10   | 86.36     | 76.81 | 97.93   | 48.51 | 86.23   |

| Soliton Line                       | 46.73   | 87.85     | 73.73 | 98.02   | 44.93 | 85.51   |

| 20 Bit Ripple Counter              | 56.11   | 89.33     | 71.65 | 96.54   | 51.61 | 83.87   |

There are two main parallelization overheads in proposed method [29]. The first one is sequential simulation. In order to create history, sequential simulation has to be performed at the beginning of the simulation that enables parallel simulation at subsequent time points. The second overhead is locks and barriers implemented at each  $D_F\Delta T$ . After every  $D_F\Delta T$  time frame the circuit is synchronised, which reinitializes the parallel simulation to a sequential simulation.

This overhead increases as the number of subcircuits increases, because now more number of subcircuits will access the shared memory data, resulting in longer waiting times due to the lock on the data structure. Efficiency of this approach depends on partition and it depends on specific type of circuits having delay elements. If there is no delay element in circuit then waveform relaxation is performed. In waveform relaxation each subcircuit has to iterate for several time for the same time interval until it converges and hence it is not efficient.

# HMAPS [31]

All literature discussed till now suffers two main disadvantages. First one, all parallel approaches are intra-algorithm, *i.e.* parallel computing is only applied to expedite intermediate computational steps within a single algorithm. This choice often leads to fine grained parallel algorithm which requires a significant amount of data dependency analysis and programming efforts.

Second common disadvantage is load balancing. Circuit may not be partitioned evenly *i.e.* each partitioned subcircuit blocks may have different number of nodes and elements. For example, one circuit network is divided in three subcircuits and Subcircuit 1 is smaller than other two. These subcircuits are assigned to three different processors. Now, processor with small subcircuit will complete its calculations faster than other two processors with big subcircuit blocks. Processor with smaller subcircuit has to wait for information from other processors. Hence parallel simulation of such circuit is not efficient for all approaches discussed till now. However this depends on the circuit partition, which is not the focus of this thesis.

Circuit behaviours to be simulated are complex functions of circuit types, structures and input excitations. Furthermore, for a fixed circuit, the circuit behaviour may vary significantly over the time, exhibiting varying amount of switching activities and because of nonlinearities. It is not difficult to predict that the characteristics of circuit behavior have a definite influence on how such characteristics may be simulated by different families of simulation algorithms. However, in practice, it is difficult to select a single best algorithm that fits all type of circuits or even one complete simulation run for a given circuit.

This observation of variations in the performance of a single simulation algorithm over the time and different types of circuit suggests that it is beneficial to run multiple algorithms in parallel [31]. There are four different computing models possible for circuit simulation: (i) single algorithm on single core processor (Figure 2.13(a)) (ii) single algorithm on multi-core CPU (Figure 2.13(b)) (iii) multialgorithm on multicore CPU and (iv) hierarchical multialgorithm on multicore CPU.

Figure 2.13 Possible computing models of circuit simulation approaches (a) Single algorithm on single core processor (b) Single algorithm on multi-core CPU (c) Multialgorithm on multicore CPU and (d) Hierarchical multialgorithm on multicore CPU

In this work, the researchers propose a hierarchical multi-algorithm (MA) parallel circuit simulation framework for parallel time-domain transistor level circuit simulation. Their

framework exploits the advantageous characteristics of the recent multi-core processor computing platforms such as small inter-processor communication cost, flexible shared memory programming environment to achieve good runtime performance.

Unlike conventional approaches where a single (parallel) algorithm is employed for a given application, in HMAPS, multiple algorithms with varying characteristics are launched to process the same simulation task. In their framework, they implemented two levels of parallelism. For a simulation task, multiple different simulation algorithms begin in parallel. Parallel speedups are obtained by having these algorithms interact with each other in a cooperative manner on the fly. This opens up a somewhat unorthodox angle to approach parallel circuit simulation as it allows one to explore a combination of intra- and interalgorithm parallelism. This combination of different levels of parallelism not only opens up new opportunities, but also explore advantages that are simply not possible when working within one fixed algorithm. Each algorithm in the multi-algorithm framework uses multiple CPU cores to do its own computing tasks. By using this hierarchical multi-algorithm parallel circuit simulation framework, super-linear speedup is achieved for some test circuits [31].

#### **Other Contribution in Parallel Circuit Simulation**

An adaptive sparse matrix solver called NICSLU is proposed by paper [33]. They proposed matrix solver called NICSLU, which uses multithread parallel LU factorization algorithm on shared memory computers with multicore CPUs to accelerate circuit simulators. A simple method is proposed to predict whether a matrix is suitable for parallel factorization.

Another reference [32] proposes a new method for transient analysis of nonlinear circuits based on power waves instead of voltages and currents. The circuit is partitioned into two parts : linear and nonlinear. This method uses relaxation approach to decouple the calculation in each part. The advantage using power waves is that iterations can never diverge to infinity. The use of waves results in guaranteed convergence for any linear passive circuit and some types of nonlinear circuits. Another advantage using power waves is, this method does not require large matrix decomposition if time step is constant. This method was implemented in the *fREEDA* [29] circuit simulator. Because of the concurrent calculations of this approach, the method can be adopted to solve in parallel.

# **Chapter 3 System Formulation for Parallel Circuit Analysis**

This chapter discusses the proposed two circuit decomposition methods for efficient parallel analysis, one is based on nodal variables and another based on scattering waves. Both approaches have been implemented in two analysis types in a circuit simulator: EOP and WAVEOP.

The formulation for each approach is presented first, followed by details about the software implementation. The performance of both formulations is then evaluated with simulation examples.

## **3.1 Formulation Based on Nodal Voltages and Currents**

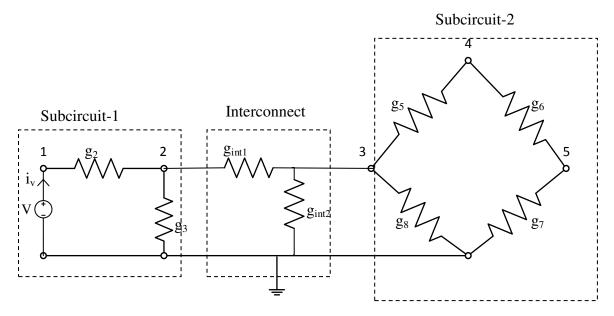

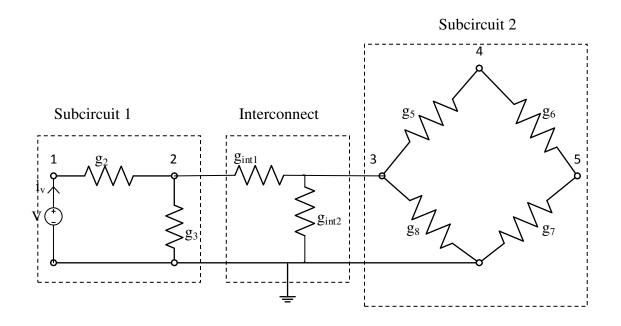

If circuit partition is performed using branch tearing then elements shared by subcircuit block and interconnect block create dependency between each other. Branch tearing causes additional process interdependencies and thus increases simulation time. Let's consider an example circuit diagram Figure 2.5 and Equation (2.9) used in Section 2.2.4 which is shown again in Figure 3.1 and Equation (3.1) for quick reference.

**Figure 3.1 Example Circuit Network**

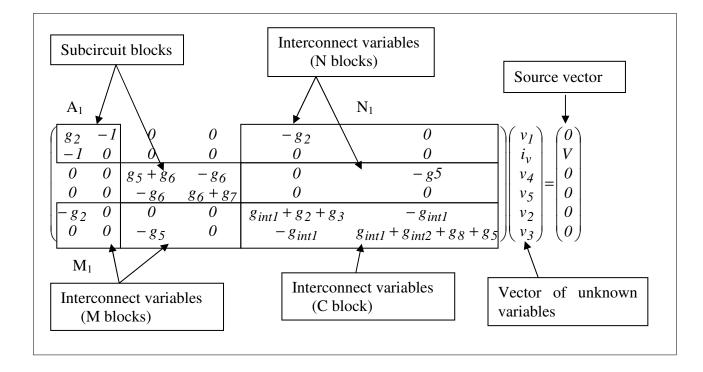

Figure 3.2 System of equation

From Figure 3.2 it is clear that conductance  $g_2$  is shared by Blocks  $A_1$ ,  $M_1$ ,  $N_1$  and C. Hence change in that element in  $A_1$  will affect all other blocks. Linear components will not change after each Newton iteration but nonlinear elements change at every Newton iteration which increases information exchange between processors sharing same nonlinear element. Furthermore, if interconnect network is large it increases amount of information exchange between processors and also increases the complexity of the interconnect system. In the proposed method, the interconnect block is successfully removed from Jacobian matrix.

The node tearing approach is described next. The following derivation assumes that:

- 1. Circuit network is manually partitioned in blocks.

- 2. Each subcircuit has a ground connection.

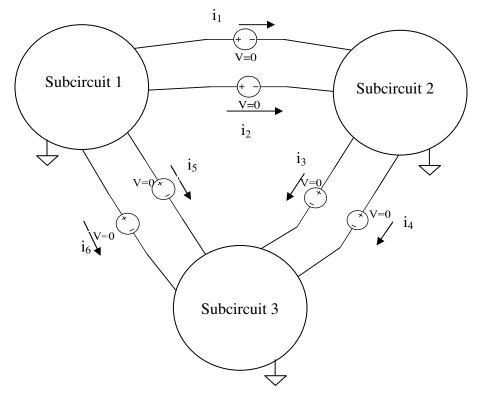

Figure 3.3 shows the general circuit diagram using node tearing [17]. Each interface node is separated into two nodes by means of ideal voltage source.

Figure 3.3 General circuit diagram to explain partition approach

Connections between subcircuits appear as single node in nodal equations. So, we split these nodes by adding ideal voltage sources having 0V. According to MNA, adding an ideal voltage

#### Chapter 3 System Formulation for Parallel Circuit Analysis

source in circuit needs an extra variable to solve nodal admittance matrix [34] and hence we added external current as an extra variable. This addition does not change the overall response of the circuit. Adding external subcircuit currents duplicates the amount of common nodal voltages between subcircuits and hence dependency between blocks is reduced.

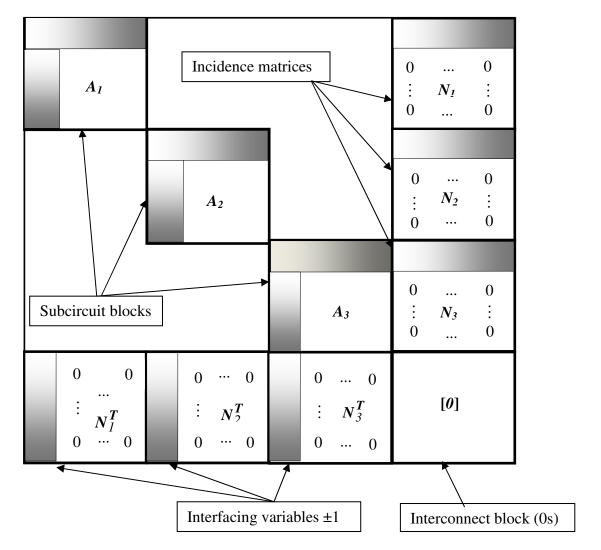

Now from Figure 3.3 the nodal admittance matrix for circuit partitioned into three subcircuits has the form shown in Figure 3.4.  $A_I$ ,  $A_2$ , and  $A_3$  represent individual subcircuits,  $N_I$ ,  $N_2$ , and  $N_3$  are incidence matrices. Most entries of incidence matrices are '0', except that there is a '±1' in each row corresponding to an external connection (shaded part in  $N_j$  and  $N_j^T$  blocks).

Figure 3.4 Jacobian matrix block (shaded parts are matrix entries that correspond to subcircuit interconnections)

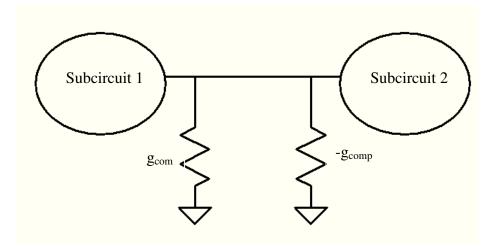

In Figure 3.4,  $N_j$  and  $N_j^T$  blocks are constant and interconnect block (*C*) is zero. This not only results in less information exchange between processors but also in simpler matrix structure. Another advantage of this partitioning approach is that a pair of voltage and current at external port of each subcircuit is available. This is useful for a later objective of exchanging information between subcircuits using scattering waves and for waves both voltage and current are required.

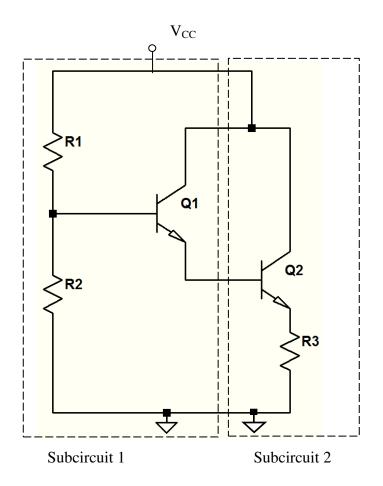

This approach is also compatible with the connection where more than two subcircuits are connected to one node. This is handled by inserting ideal voltage sources having 0 volts to the external ports of any k-1 subcircuits if there are k subcircuits connected to one node. Figure 3.5 shows such an example where three subcircuits are sharing one node a. In this case two ideal voltage sources and two external currents are assigned to Subcircuit 2 and Subcircuit 3.

Figure 3.5 General circuit diagram of three subcircuits sharing same node a

Node *a* would appear in each of three subcircuit blocks  $A_1$ ,  $A_2$ ,  $A_3$  (Figure 3.4) and  $N_j$  blocks would have two columns as shown in Figure 3.6.

|                | $i_1$       | $i_2$       |  |

|----------------|-------------|-------------|--|

|                | -1          | -1          |  |

| N <sub>1</sub> | 0<br>:<br>0 | 0<br>:<br>0 |  |

|                | 1           | 0           |  |

| $N_2$          | 0<br>:<br>0 | 0<br>:<br>0 |  |

|                | 0           | 1           |  |

| $N_3$          | 0<br>:<br>0 | 0<br>:<br>0 |  |

Figure 3.6 External currents arrangement in N blocks

## 3.1.1 Diakoptics Applied to Node Tearing

Assume that a circuit is partitioned into k subcircuits separated by zero-volt ideal voltage sources as shown in Figure 3.7.

#### Figure 3.7 General circuit diagram of partitioned circuit for derivation

From Figure 3.7 a generalized system of equation can be written as:

$$\begin{pmatrix} G_{I} & & N_{I} \\ G_{2} & & N_{2} \\ & \ddots & & \vdots \\ & & G_{k} & N_{k} \\ N_{I}^{T} & N_{2}^{T} & \cdots & N_{k}^{T} & \boldsymbol{0} \end{pmatrix} \begin{pmatrix} \boldsymbol{x}_{I} \\ \boldsymbol{x}_{2} \\ \vdots \\ \boldsymbol{x}_{k} \\ \boldsymbol{i}_{I} \end{pmatrix} + \begin{pmatrix} \boldsymbol{i}_{I}(\boldsymbol{x}_{I}) \\ \boldsymbol{i}_{2}(\boldsymbol{x}_{2}) \\ \vdots \\ \boldsymbol{i}_{k}(\boldsymbol{x}_{k}) \\ \boldsymbol{0} \end{pmatrix} = \begin{pmatrix} \boldsymbol{s}_{I} \\ \boldsymbol{s}_{2} \\ \vdots \\ \boldsymbol{s}_{k} \\ \boldsymbol{0} \end{pmatrix}$$

(3.1)

where  $G_j$  is subcircuit block,  $N_j$  is incidence matrix block,  $i_1(x_1), i_2(x_2), ..., i_k(x_k)$  are internal currents of nonlinear components inside subcircuits,  $i_I$  is external current vector and  $s_1, s_2, ..., s_k$  are subcircuit source vectors. Notice that there is neither interconnect matrix block nor interconnect source vector in Jacobian matrix written in Equation (3.1). Now applying Newton's method on Equation (3.1) and using F(x) = Gx + i(x) and hence  $J_F = G + J_i$ , the following is obtained:

$$\begin{pmatrix}

G_{1} + J_{1} & N_{1} \\

G_{2} + J_{2} & N_{2} \\

\vdots & G_{k} + J_{k} & N_{k} \\

M_{1}^{T} & N_{2}^{T} & M_{k} \\

G + J_{i}

\end{pmatrix}

\begin{pmatrix}

Ax_{1} \\

Ax_{2} \\

\vdots \\

Ax_{k} \\

Ai_{I}

\end{pmatrix} = \begin{pmatrix}

s_{1} \\

s_{2} \\

\vdots \\

s_{k} \\

0

\end{pmatrix} - \begin{pmatrix}

G_{1}x_{1}^{n} + N_{1}i_{I} + i_{1}(x_{1}^{n}) \\

G_{2}x_{2} + N_{2}i_{I} + i_{2}(x_{2}) \\

\vdots \\

G_{k}x_{k} + N_{k}i_{I} + i_{k}(x_{k}) \\

\sum_{j=1}^{k} N_{j}^{T} x_{j}^{n} \\

\sum_{j=1}^{k} N_{j}^{T} x_{j}^{n} \\

-(Gx + i(x))

\end{pmatrix} (3.2)$$

where  $J_i$  is Jacobian matrix of current vector i(x), n is iteration index and  $\Delta i_I^{n+1}$  is external (interconnect) current vector.

For each subcircuit let

$$\begin{cases} f_k(x_k^n) = G_k x_k^n + i_k(x_k^n) \\ A_k = G_k + J_k \end{cases}$$

(3.3)

Using relations shown in Equations (3.3) in an Equation (3.2) results in:

$$\begin{pmatrix} A_{I} & & N_{I} \\ & A_{2} & & N_{2} \\ & & \ddots & \vdots \\ & & A_{k} & N_{k} \\ N_{I}^{T} & N_{2}^{T} & \dots & N_{k}^{T} & 0 \end{pmatrix} \begin{pmatrix} Ax_{I}^{n+1} \\ Ax_{2}^{n+1} \\ Ax_{k}^{n+1} \\ AiI_{I}^{n+1} \end{pmatrix} = \begin{pmatrix} s_{I} \\ s_{2} \\ \vdots \\ s_{k} \\ 0 \end{pmatrix} - \begin{pmatrix} f_{I}(x_{I}^{n}) \\ f_{2}(x_{2}^{n}) \\ \vdots \\ f_{k}(x_{k}^{n}) \\ 0 \end{pmatrix} - \begin{pmatrix} N_{I}i_{I}^{n} \\ N_{2}i_{I} \\ \vdots \\ N_{k}i_{I} \\ \sum_{j=1}^{k} N_{j}^{T}x_{j} \end{pmatrix} .$$

(3.4)

Now consider the system of equation for  $j^{th}$  subcircuit. First

$$\Delta x_{j}^{*} = A_{j}^{-1} (s_{j} - f_{j}(x_{j}^{n}) - N_{j} i_{I}^{n})$$

(3.5)

is found. where, j=1, 2, ..., k. Unknown nodal voltages of subcircuit *j* can be found using Equation (3.5) from:

Chapter 3 System Formulation for Parallel Circuit Analysis

$$\Delta \boldsymbol{x}_{j}^{n+1} = \Delta \boldsymbol{x}_{j}^{*} - \boldsymbol{A}_{j}^{-1} \boldsymbol{N}_{j} \Delta \boldsymbol{i}_{I}^{n+1}$$

(3.6)

where,  $\Delta x_j^{n+1}$  is  $j^{th}$  subcircuit nodal voltage. The equation related to interconnect blocks is :

$$\sum_{j=1}^{k} N_{j}^{T} \Delta \mathbf{x}_{j}^{n+1} = -\sum_{j=1}^{k} N_{j}^{T} \mathbf{x}_{j}^{n}$$

(3.7)

Replace  $\Delta x_j^{n+1}$  from Equation (3.6) into Equation (3.7) and rearrange equation to get :

$$\sum_{j=I}^{k} N_{j}^{T} \Delta \mathbf{x}_{j}^{*} - \sum_{j=I}^{k} (N_{j}^{T} A_{j}^{-1} N_{j}) \Delta \mathbf{i}_{I}^{n+I} = -\sum_{j=I}^{k} N_{j}^{T} \mathbf{x}_{j}^{n}$$

$$\sum_{j=I}^{k} (N_{j}^{T} A_{j}^{-1} N_{j}) \Delta \mathbf{i}_{I}^{n+I} = \sum_{j=I}^{k} N_{j}^{T} \Delta \mathbf{x}_{j}^{*} + \sum_{j=I}^{k} N_{j}^{T} \mathbf{x}_{j}^{n}$$

$$\left(\sum_{j=I}^{k} N_{j}^{T} A_{j}^{-1} N_{j}\right) \Delta \mathbf{i}_{I}^{n+I} = \sum_{j=I}^{k} N_{j}^{T} (\mathbf{x}_{j}^{n} + \Delta \mathbf{x}_{j}^{*})$$

(3.8)

The practical implementation of the above process has been developed to solve system of Equation (3.1). First Equation (3.5) is solved, followed by interconnect current vector which can be obtained from Equation (3.8) and then subcircuit nodal voltages can be found from Equation (3.6) using Equations (3.5) and (3.8).

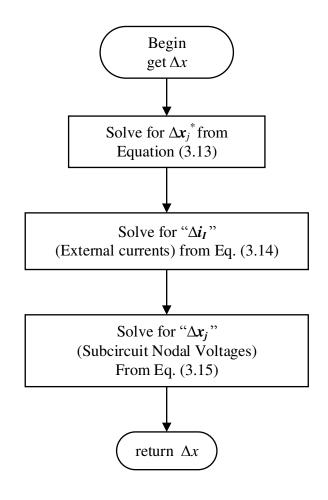

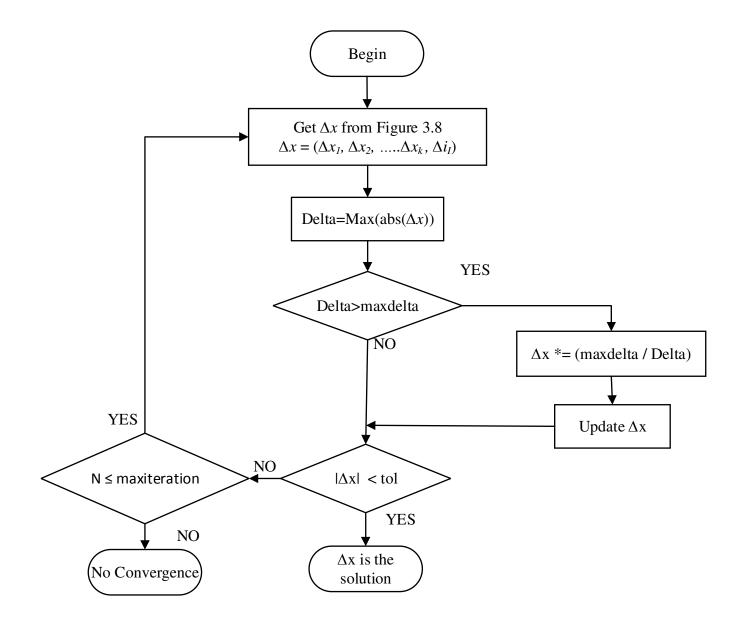

## **3.1.2 Algorithm Flowchart**

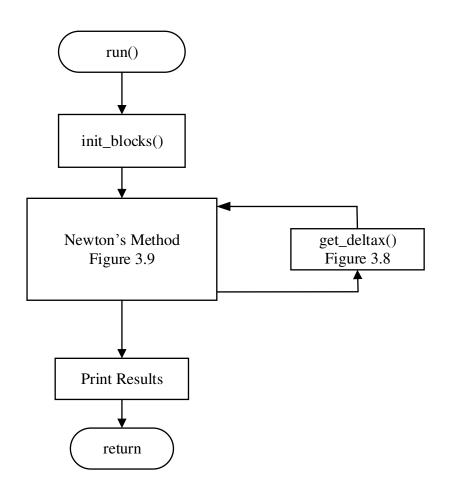

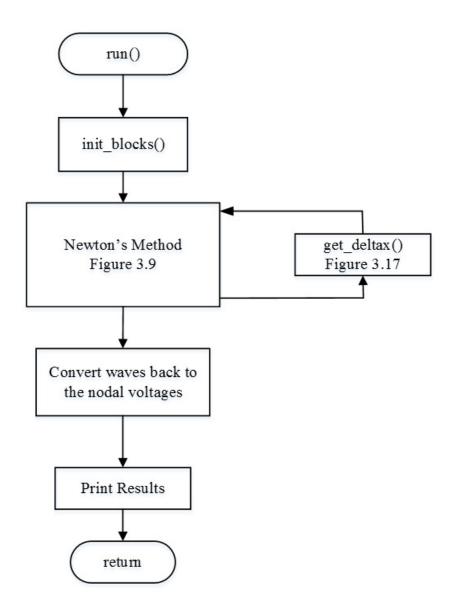

The flowchart of the analysis based on nodal voltages and currents is shown in Figure 3.8.

Figure 3.8 Algorithm of analysis based on nodal variables

A flow diagram of Newton method is shown in Figure 3.9. It uses  $\Delta x$  variable from analysis based on nodal variables and perform Newton method to check convergence.

Figure 3.9 Algorithm flowchart of Newton method

#### **Inter-processor Communication Analysis**

Since the parallel algorithm is not implemented in this thesis, as a guideline, possible way to implement parallel algorithm is discussed briefly. Parallel algorithm for the proposed approach is the same as shown in Figure 2.8. The key difference between algorithm shown in Figure 2.8 and analysis with nodal variables is that, in proposed approach interconnect block (*C*) and interconnect source vector ( $b_{k+1}$ ) are zero. In the case of algorithm presented in Figure 2.8, a nonlinear element connected to an external node in Subcircuit *j*, will produce entries in  $N_j$ ,  $M_j$  and *C* blocks. If this element in Subcircuit *j* changes then slave processor has to communicate this change with master processor to update *C* block, as interconnect nodal voltage vector is solved by master processor (Equation 2.15). But in proposed analysis,  $N_j$  blocks are constant and *C* block is zero. So there is less communication between master and slave processors compared to algorithm shown in Figure 2.8. And also because of the simpler structure of  $N_j$  blocks, there is less work for each slave processor to perform. In proposed analysis,  $M_j = N_j^T$  and  $\Delta x_{k+1}^{n+1} = \Delta i_I^{n+1}$ . Slave processors calculate  $x_j^*$ ,  $S_j^n$ ,  $w_j^n$  and send that information to master processor which calculates  $S^n$ ,  $w^n$  and  $\Delta i_I^{n+1}$  (Equation 3.8). where,

$$S^{n} = -\sum_{j=1}^{k} S_{j}^{n}$$

and  $w^{n} = -\sum_{j=1}^{k} w_{j}^{n}$ .

And at last, slave processors retrieve  $\Delta i_I^{n+1}$  from master processor and calculate  $\Delta x_j^{n+1}$  (Equation 3.6).

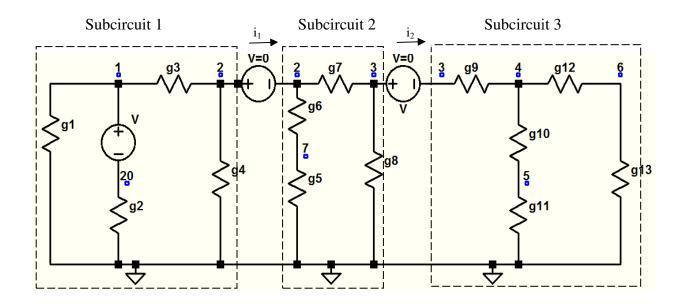

## 3.1.3 Complete Example

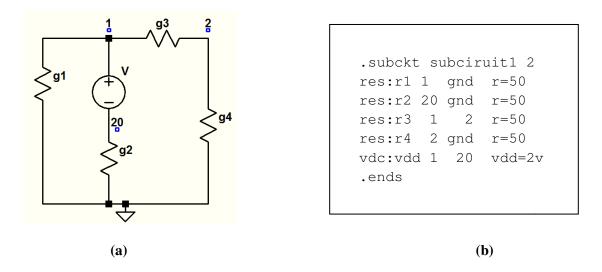

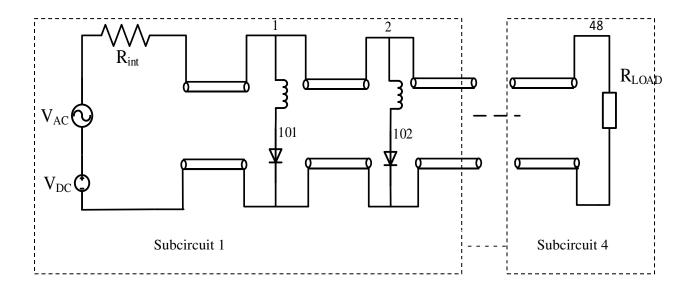

A linear circuit example is discussed here with the whole process from partitioning circuit to writing a netlist file for simulation. Figure 3.10 shows linear circuit with conductances, one ideal voltage source and 8 nodes. Subcircuits 1 and 2 have 3 nodes each, whereas Subcircuit 3 has 4 nodes. This circuit is partitioned into three subcircuits separated using ideal voltage sources with 0 volts as shown in Figure 3.10.  $i_1$  and  $i_2$  are the external currents.

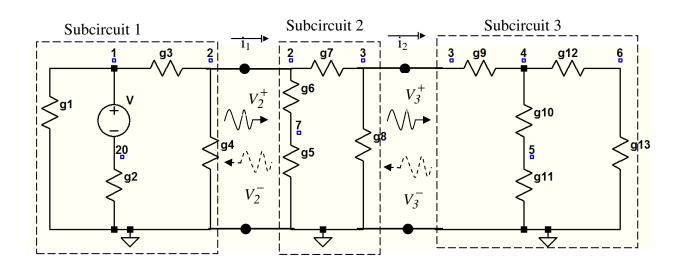

Figure 3.10 Partitioned linear circuit with nodal variables (Numbers shown above square dots are node numbers)

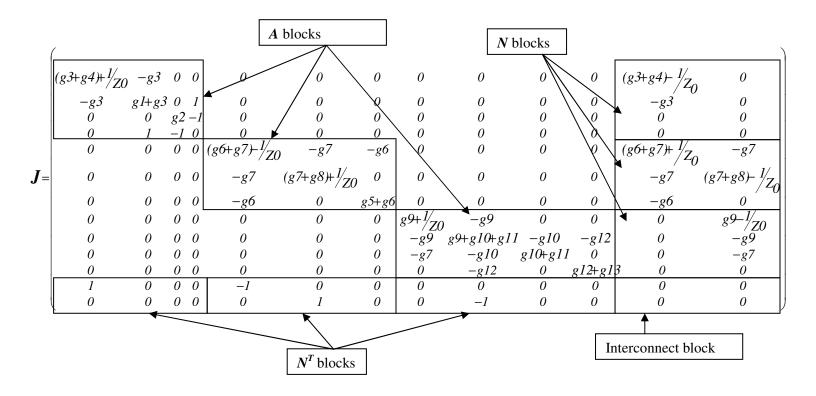

To simulate this circuit, it should be described in netlist format. Full netlist file is given in Appendix A. For reference Jacobian matrix block of Subcircuit 1 of Figure 3.10 is shown in Figure 3.11. Figure 3.11(b) shows Jacobian matrix of Subcircuit 1 shown in Figure 3.11 (a) [34].

**(b)**

Figure 3.11 Example (a) Subcircuit block (b) Nodal matrix blocks

#### Chapter 3 System Formulation for Parallel Circuit Analysis

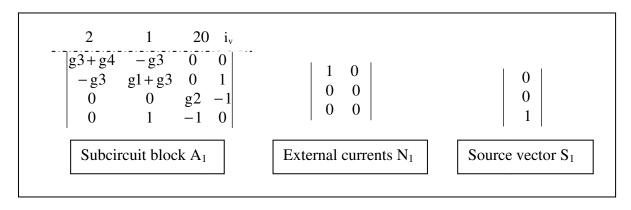

Now the Jacobian matrix for the whole circuit (Figure 3.11) with system of equation can be written as shown in Figure 3.12.

Figure 3.12 System of equations

There are two important main differences between equations shown in Figure 3.2 and Figure 3.12: (i) Interconnect block is zero in Figure 3.12 and (ii) Incidence matrices are independent of subcircuit components . Hence proposed partitioning approach reduces dependencies between subcircuit blocks.

## **3.2 Formulation Based on Scattering Waves**

#### **Basic Concepts**