# UNIVERSIDAD DE SEVILLA

#### DEPARTAMENTO DE ELECTRÓNICA Y ELECTROMAGNETISMO

# DISEÑO CMOS DE UN SISTEMA DE VISIÓN "ON-CHIP" PARA APLICACIONES DE MUY ALTA VELOCIDAD

Memoria presentada por:

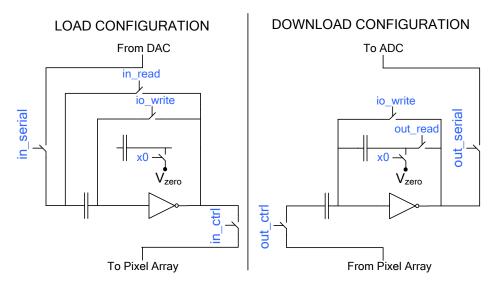

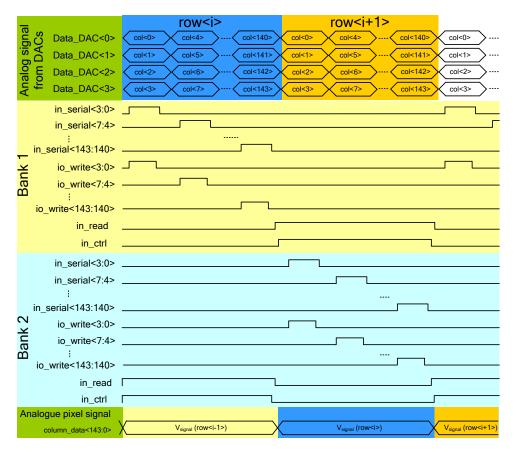

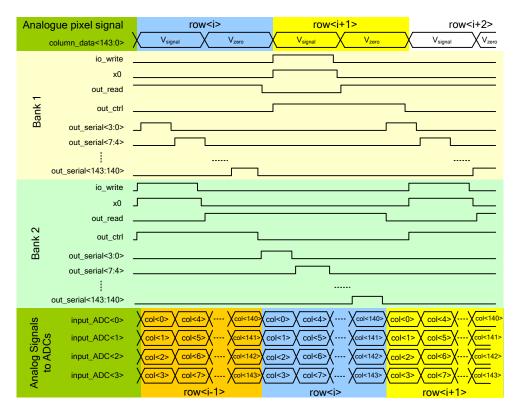

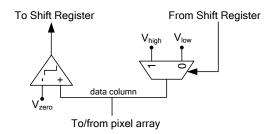

FRANCISCO JOSÉ JIMÉNEZ GARRIDO

Para optar al grado de Doctor

Sevilla, 2015

Memoria presentada por:

#### FRANCISCO JOSÉ JIMÉNEZ GARRIDO

para optar al grado de Doctor

Sevilla, Octubre de 2015

Dirigida por:

Ángel Rodríguez Vázquez

Rafael Domínguez Castro

Tutora:

Belén Pérez Berdú

Departamento de Electrónica y Electromagnetismo

Universidad de Sevilla

# **CONTENTS**

| Resumen D   | e La Tesis                                            | 9  |

|-------------|-------------------------------------------------------|----|

| Thesis Sum  | mary                                                  | 11 |

| Resumen E   | xtendido, Motivaciones y Conclusiones                 | 13 |

| Chapter 1 - | Introduction and Motivations                          | 27 |

| 1.1. Int    | roduction                                             | 27 |

| 1.2. Ou     | utline of the Thesis                                  | 31 |

| Chapter 2 – | Basic Concepts, Definitions and Terms                 | 37 |

| 2.1. Fro    | om Light Radiation to Picture Elements                | 37 |

| 2.1.1.      | Imagers: Concept and Basic Terms                      | 37 |

| 2.1.2.      | Basic Radiometric Concepts                            | 41 |

| 2.1.3.      | Lenses                                                | 43 |

| 2.2. Ba     | sic Photosensors                                      | 45 |

| 2.2.1.      | Photon Absorption                                     | 45 |

| 2.2.2.      | Accumulation Mode Photo-Sensors                       | 47 |

| 2.2.3.      | Other CMOS Photo-sensors                              | 50 |

| 2.3. Pix    | kels                                                  | 51 |

| 2.3.1.      | Passive Pixels                                        | 51 |

| 2.3.2.      | In-pixel readout electronics (APS)                    | 53 |

| 2.3.3.      | In-pixel processing electronics                       | 58 |

| 2.4. Diç    | gital Imagers, Camera Systems, Vision Systems         | 61 |

| 2.4.1.      | Concept of Digital Imagers and Camera Systems         | 61 |

| 2.4.2.      | Concept of Vision Systems and Basic Vision Operations | 64 |

| 2.4.3.      | Hardware-software co-design                           | 66 |

| 2.4.4.      | Design of Hardware/Software systems                   | 67 |

| 2.4.5.      | Vision Systems Architectures                          | 68 |

| 2.5. Ty     | pical specs for camera and vision systems             | 72 |

| 2.5.1.      | Application requirements, system specifications       | 72 |

| 2.5.2.      | Camera specifications                                 | 75 |

| 2.5.3.      | Optics                                                | 76 |

| 2.5.4.      | Camera Functionality                                  | 77 |

| 2.5.5.      | Camera Image Quality                                  | 78 |

| 2.6. Pre    | edecessors of the Q-eye                               | 87 |

| 2.6.1.      | The CNN paradigm                                      | 87 |

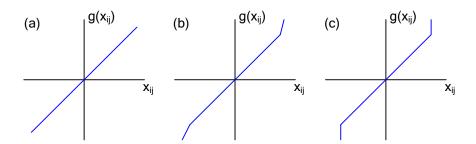

| 2.6.2.      | Leon O. Chua and Lin Yang model                       | 89 |

| 2.6.3.      | Full Signal Range (FSR) model                         | 90 |

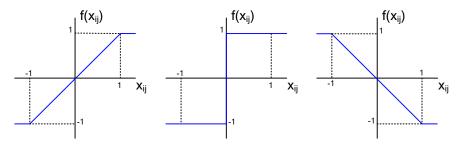

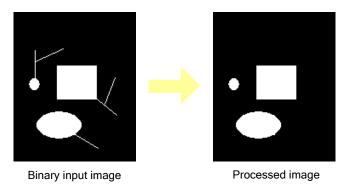

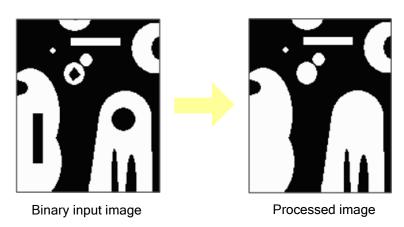

| 2.6.4.      | Image processing based on CNN template                | 91 |

| 2.6     | .5.            | CNN templates design                                                      | 93  |

|---------|----------------|---------------------------------------------------------------------------|-----|

| 2.6     | .6.            | The ACE and CACE chips                                                    | 93  |

| 2.6     | .7.            | Limitations of the ACE and CACE chips                                     | 99  |

| 2.6     | .8.            | Other types of computational sensors                                      | 101 |

| 2.7.    | Cha            | allenges for cameras and vision systems. Overview of the state-of-the-art | 103 |

| 2.7     | .1.            | Cameras-on-chip                                                           | 105 |

| 2.7     | .2.            | Vision systems-on-chip                                                    | 106 |

| Chapter | r 3 - T        | he Q-Eye pixel                                                            | 109 |

| 3.1.    | Q-E            | ye cell architecture                                                      | 109 |

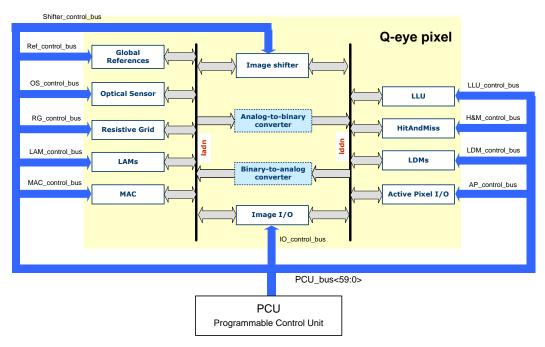

| 3.1     | .1.            | Block diagram and embedded operators                                      | 109 |

| 3.1     | .2.            | Dataflow, signal formats and control of the Q-Eye cell                    | 112 |

| 3.1     | .3.            | Rationale for selection of the Q-Eye operators                            | 115 |

| 3.1     | .4.            | Illustrating data reduction through the Q-Eye                             | 116 |

| 3.2.    | Circ           | cuit implementation of the Q-Eye cell operators                           | 118 |

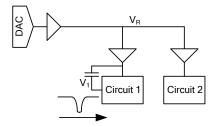

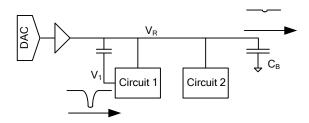

| 3.2     | .1.            | Global Analogue References                                                | 118 |

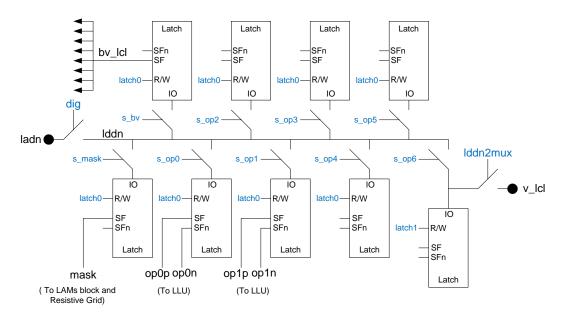

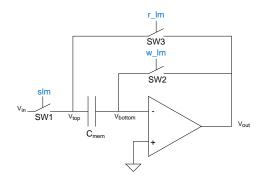

| 3.2     | .2.            | Data storage and transfer                                                 | 119 |

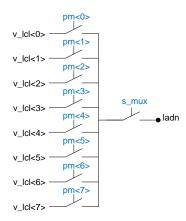

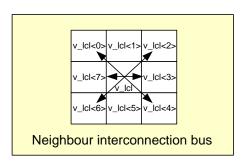

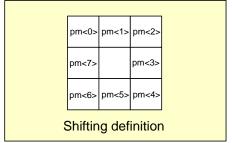

| 3.2     | .3.            | Image shifting                                                            | 123 |

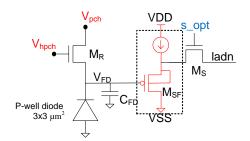

| 3.2     | .4.            | Optical sensor                                                            | 125 |

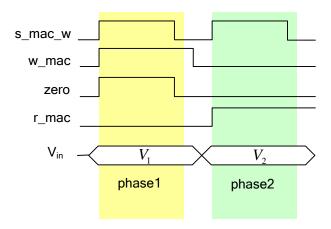

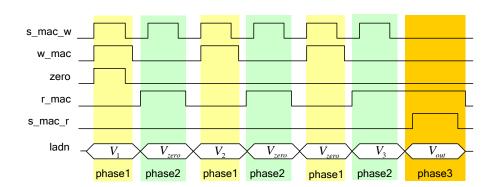

| 3.2     | .5.            | Multiplier-Accumulator Circuit (MAC)                                      | 128 |

| 3.2     | .6.            | Logic and morphological operators                                         | 131 |

| 3.2     | .7.            | Convolutions                                                              | 134 |

| 3.2     | .8.            | Diffusion grid                                                            | 136 |

| 3.3.    | Cha            | aracterization and modeling of errors                                     | 141 |

| 3.3     | .1.            | Analogue memory errors                                                    | 141 |

| 3.3     | .2.            | MAC errors                                                                | 154 |

| 3.3     | .3.            | Resistive grid errors                                                     | 165 |

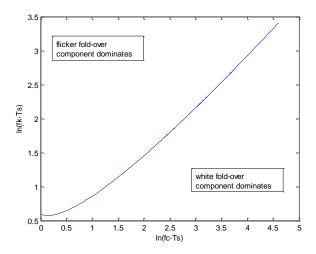

| 3.3     | .4.            | Errors in The Optical Sensor                                              | 166 |

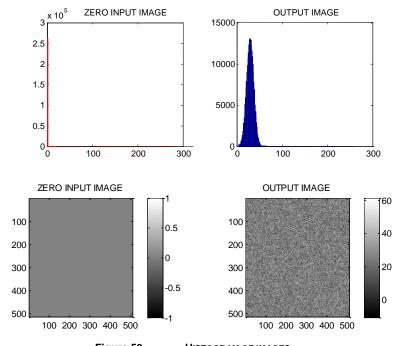

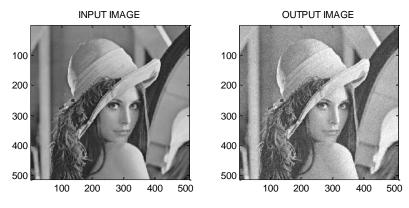

| 3.4.    | Exe            | mplary results of degradation caused by errors                            | 173 |

| 3.4     | .1.            | time-invariant errors                                                     | 174 |

| 3.4     | .2.            | time-variant errors                                                       | 177 |

| 3.4     | .3.            | Practical recommendations for processing in the presence of errors        | 180 |

| Chapter | r <b>4 - T</b> | he Q-Eye chip                                                             | 183 |

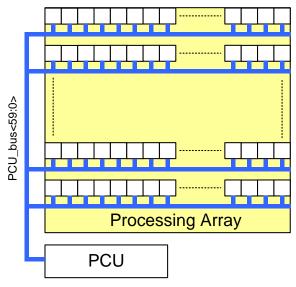

| 4.1.    | The            | Q-Eye chip block diagram and architecture                                 | 183 |

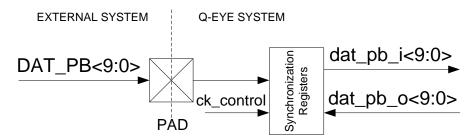

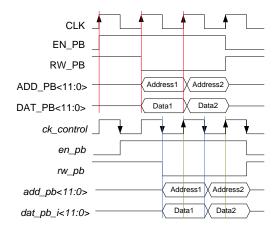

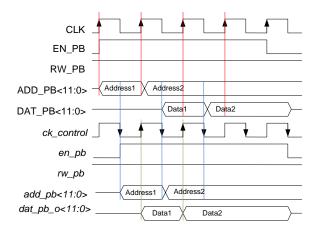

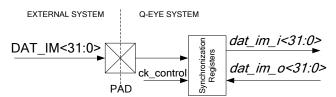

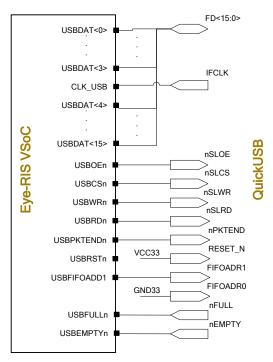

| 4.1     | .1.            | External interfaces of the Q-Eye                                          | 185 |

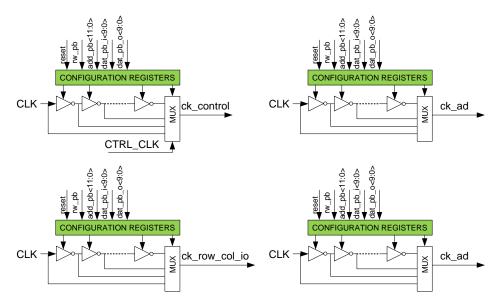

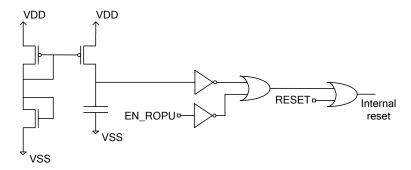

| 4.1     | .2.            | Control strategies: Configuration registers and Programmable Control Unit | 192 |

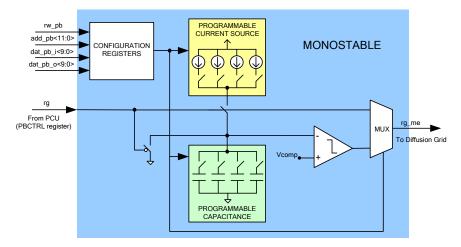

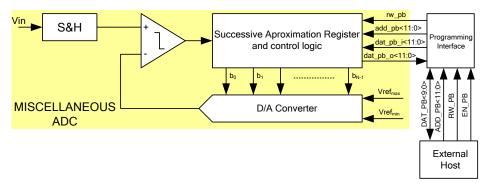

| 4.1     | .3.            | Miscellaneous blocks                                                      | 195 |

| 4.2.    | The            | Q-Eye read-out                                                            | 204 |

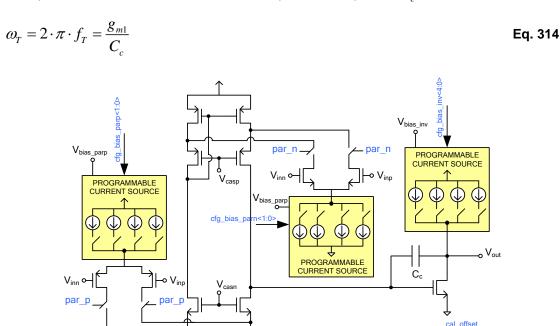

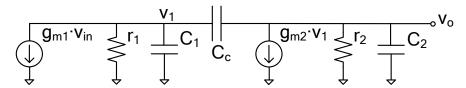

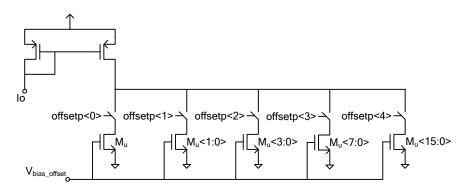

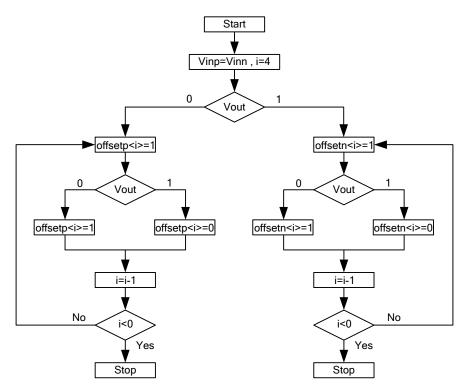

| 12      | 1              | About the readout channel architecture                                    | 205 |

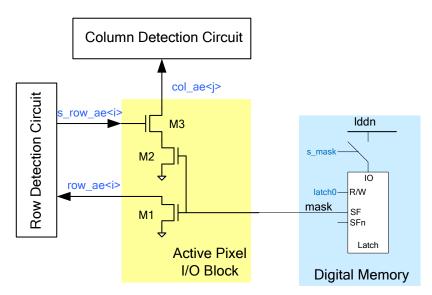

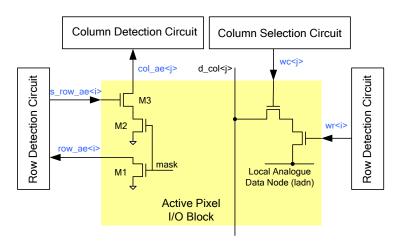

| 4.3.       | Address-event read-out                                                               | 221 |

|------------|--------------------------------------------------------------------------------------|-----|

| 4.3        | .1. Asynchronous downloading of images. Address-event reading                        | 221 |

| 4.3        | .2. Random access to load data in array. Address-event writing                       | 223 |

| 4.3        | .3. Global mean of images                                                            | 224 |

| 4.4.       | Supply and biasing in the Q-Eye                                                      | 225 |

| 4.4        | .1. Power supply and packaging                                                       | 225 |

| 4.4        | .2. Substrate noise                                                                  | 228 |

| 4.4        | .3. Power and reference distribution                                                 | 231 |

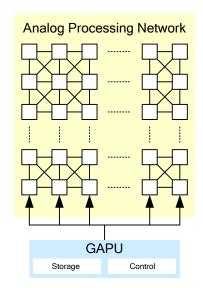

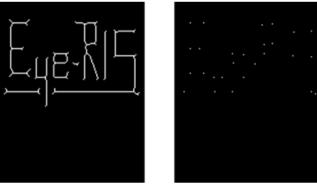

| Chapter    | <sup>r</sup> 5 - The Eye-RIS Vision System                                           | 237 |

| 5.1.       | Eye-RIS systems architectures                                                        | 237 |

| 5.1        | .1. Generalities about the processing chain of vision                                | 237 |

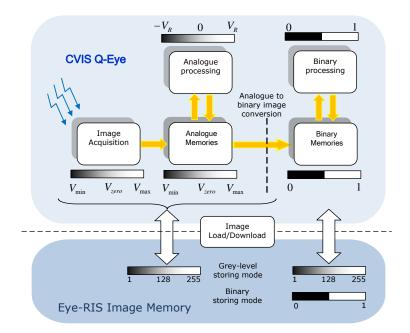

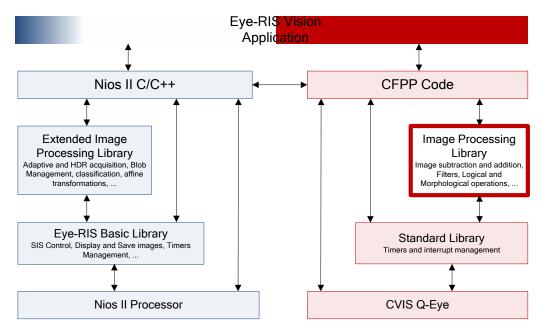

| 5.1        | .2. Progressive processing, CVIS-based architectural concept                         | 240 |

| 5.1        | .3. Eye-RIS architecture outlines                                                    | 242 |

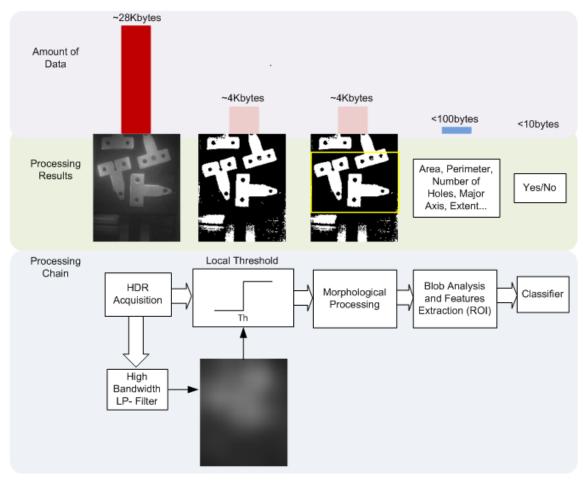

| 5.2.       | Illustrating progressive, distributed processing: part-finding application           | 243 |

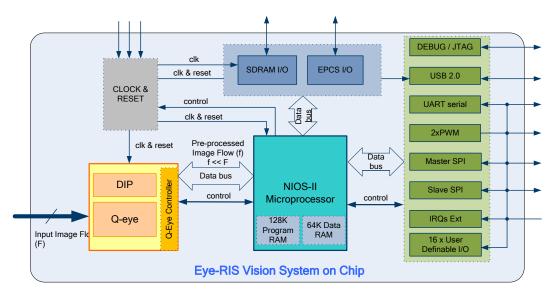

| 5.3.       | The Eye-RIS_v1                                                                       | 249 |

| 5.3        | .1. NIOS-II Processor                                                                | 250 |

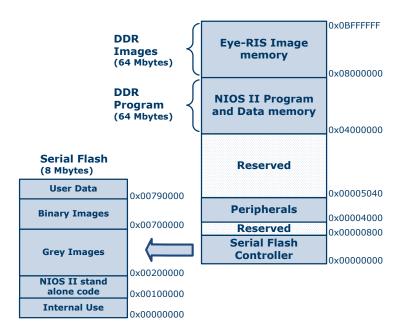

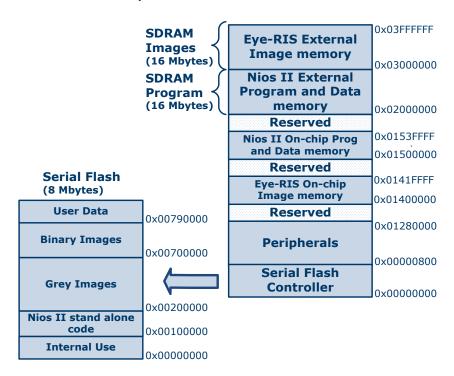

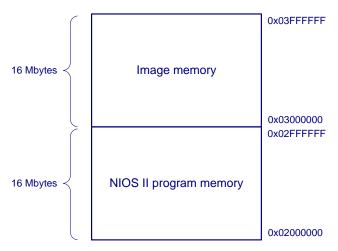

| 5.3        | .2. Memory Map                                                                       | 250 |

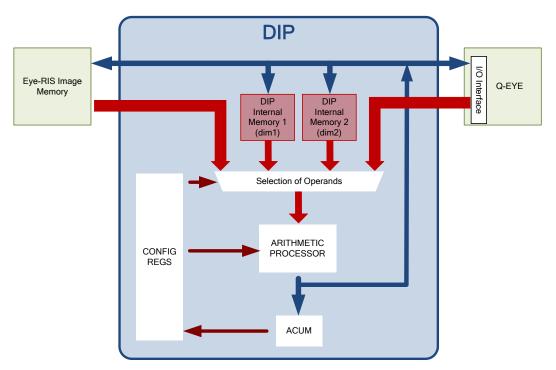

| 5.3        | .3. Digital Image Processor                                                          | 251 |

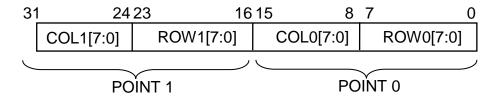

| 5.3        | .4. Digital Input/Output ports                                                       | 252 |

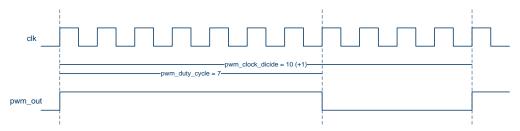

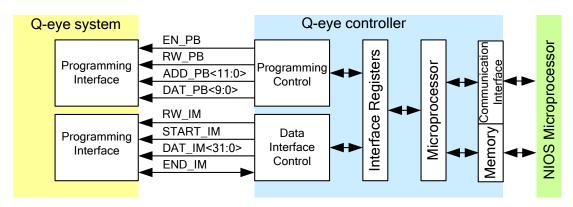

| 5.3        | .5. Q-eye controller                                                                 | 255 |

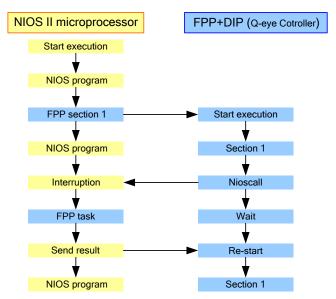

| 5.3        | .6. NIOS-Q-Eye controller communication                                              | 257 |

| 5.3        | .7. Controller memory                                                                | 258 |

| 5.3        | .8. Controller microprocessor                                                        | 259 |

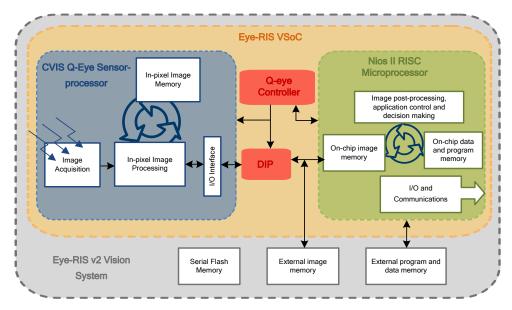

| 5.4.       | The Eye-RIS_v2                                                                       | 259 |

| 5.4        | .1. Architecture and control overview of task scheduling                             | 260 |

| 5.4        | .2. Pre-processing and post-processing implementation issues                         | 264 |

| 5.4        | .3. External interfaces                                                              | 265 |

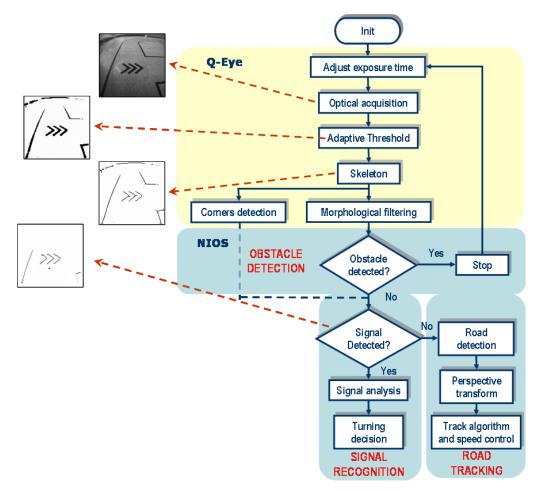

| 5.5.       | The Q-eye and the Eye-RIS in operation                                               | 269 |

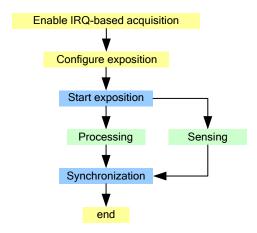

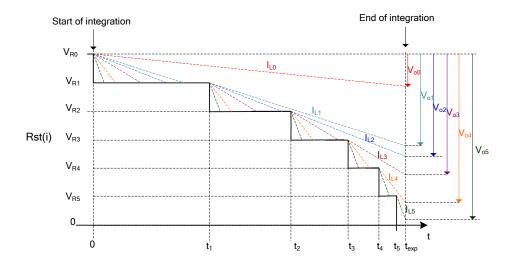

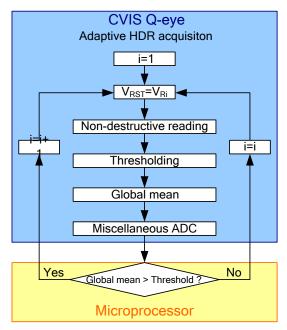

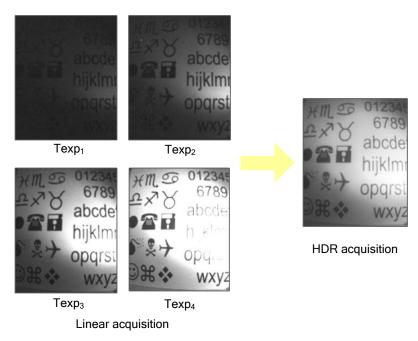

| 5.5        | .1. HDR signal acquisition                                                           | 269 |

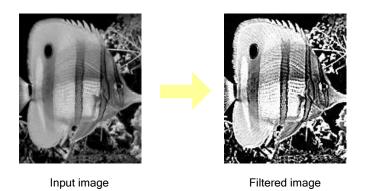

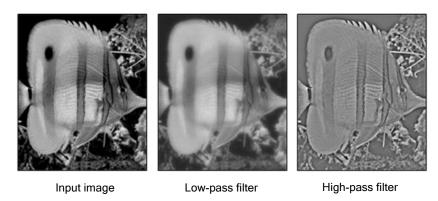

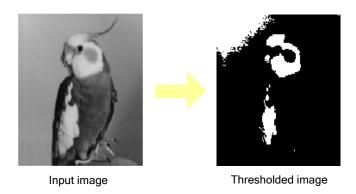

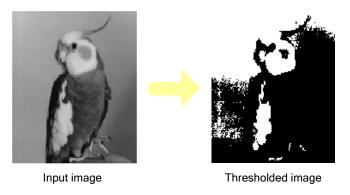

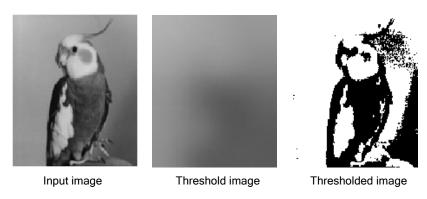

| 5.5        | .2. Spatial filtering                                                                | 271 |

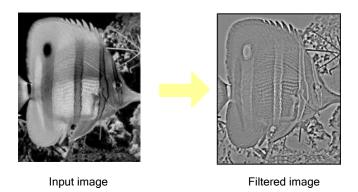

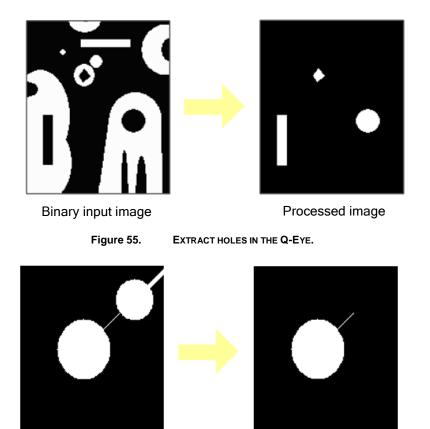

| 5.5<br>rep | .3. Extraction of images features and calculation of intermediate image resentations | 275 |

| 5.5        | .4. Decision making                                                                  | 283 |

| Append     | lices                                                                                | 287 |

| Append     | lix A – Settling errors in gregorian's s&h                                           | 287 |

| Append     | lix B – DC errors in MAC operation                                                   | 291 |

| Referen    | ces                                                                                  | 299 |

| Abbrevi    | ations and constants                                                                 | 314 |

### RESUMEN DE LA TESIS

Esta Tesis presenta arquitecturas, circuitos y chips para el diseño de **SENSORES DE VISIÓN CMOS** con procesamiento paralelo embebido. La Tesis reporta dos chips, en concreto:

- El chip Q-Eye

- El chip Eve-RIS VSoC

y dos sistemas de visión construidos con estos chips y otros sistemas "off-chip" adicionales, como FPGAs, en concreto:

- El sistema Eye-RIS\_v1

- El sistema Eve-RIS v2

Estos chips y sistemas están concebidos para ejecutar tareas de visión a muy alta velocidad y con consumos de potencia moderados. Los sistemas resultantes son, además, compactos y por lo tanto ventajosos en términos del factor SWaP cuando se los compara con arquitecturas convencionales formadas por sensores de imágenes convencionales seguidos de procesadores digitales. La clave de estas ventajas en términos de SWaP y velocidad radica en el uso de sensores-procesadores, en lugar de meros sensores, en la interface de los sistemas de visión. Estos sensores-procesadores embeben procesadores programables de señal-mixta dentro del pixel y son capaces por tanto de adquirir imágenes como de pre-procesarlas para extraer características, eliminar información redundante y reducir el número de datos que se transmiten fuera del sensor para su procesamiento ulterior.

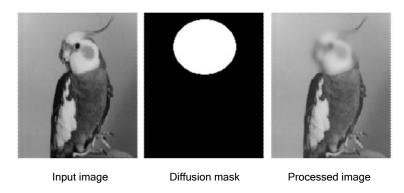

El núcleo de la tesis es el sensor-procesador Q-Eye, que se usa como interface en los sistemas Eye-RIS. Este sensor-procesador embebe una arquitectura de procesamiento formada por procesadores de señal-mixta distribuidos por pixel. Sus píxeles son por tanto estructuras multifuncionales complejas. De hecho, son programables, incorporan memorias e interactúan con sus vecinos para realizar una variedad de operaciones, tales como:

- Convoluciones lineales con máscaras programables.

- Difusiones controladas por tiempo y nivel de señal, a través de un "grid" resistivo embebido en el plano focal.

- · Aritmética de imágenes.

- Flujo de programación dependiente de la señal.

- Conversión entre los dominios de datos: imagen en escala de grises e imagen binaria

- Operaciones lógicas en imágenes binarias.

- Operaciones morfológicas en imágenes binarias.

- etc.

Con respecto a otros píxeles multi-función y sensores-procesadore anteriores, el Q-Eye reporta entre otras las siguientes ventajas:

- mayor calidad de la imagen y mejores prestaciones de las funcionalidades embebidas en el chip;

- mayor velocidad de operación y mejor gestión de la energía disponible;

- mayor versatilidad para integración en sistemas de visión industrial.

De hecho, los sistemas Eye-RIS son los primeros sistemas de visión industriales dotados de las siguientes características:

- Procesamiento paralelo distribuido y progresivo.

- Procesadores de señal-mixta fiables, robustos y con errores controlados.

- · Programabilidad distribuida.

La Tesis incluye descripciones detalladas de la arquitectura y los circuitos usados en el pixel del Q-Eye, del propio chip Q-Eye y de los sistemas de visión construidos en base a este chip. Se incluyen también ejemplos de los distintos chips en operación.

# THESIS SUMMARY

This Thesis presents architectures, circuits and chips for the implementation of **CMOS VISION SENSORS** with embedded parallel processing. The Thesis reports two chips, namely:

- · Q-eye chip,

- Eye-RIS\_VSoC chip,

and two vision systems realized by using these chips and some additional "off-chip" circuitry, such as FPGAs. These vision systems are:

- Eye-RIS\_v1 system,

- Eye-RIS v2 system.

The chips and systems reported in the Thesis are conceived to perform vision tasks at very high speed and with moderate power consumption. The proposed vision systems are also compact and advantageous in terms of SWaP factors as compared with conventional architectures consisting of standard image sensor followed by digital processors. The key of these advantages in terms of SWaP and speed lies in the use of sensors-processors, rather than mere sensors, in the front-end interface of vision systems. These sensors-processors embed mixed-signal programmable processors inside the pixel. Therefore, they are able to acquire images and process them to extract the features, removing the redundant information and reducing the data throughput for later processing.

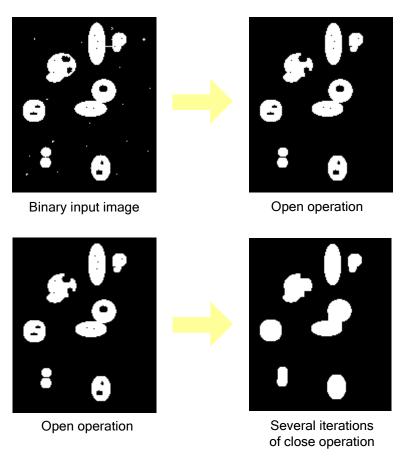

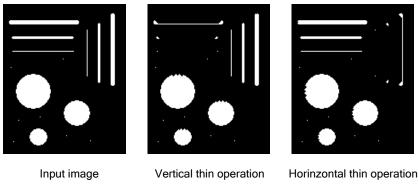

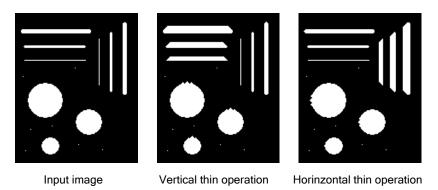

The core of the Thesis is the sensor-processor Q-Eye, which is used as front-end in the Eye-RIS systems. This sensor-processor embeds a processing architecture composed by mixed-signal processors distributed per pixel. Then, its pixels are complex multi-functional structures. In fact, they are programmable, incorporate memories and interact with its neighbors in order to carry out a set of operations, including:

- Linear convolutions with programmable linear masks.

- Time- and signal-controlled diffusions (by means of an embedded resistive grid).

- Image arithmetic.

- Signal-dependent data scheduling.

- Gray-scale to binary transformation.

- Logic operation on binary images.

- Mathematical morphology on binary images.

- etc.

As compared with previous multi-function pixels and sensors-processors, the Q-Eye brings among other the following advantages:

- higher image quality and better performances of functionalities embedded on chip;

- higher operation speed and better management of energy budget;

- more versatility for integration in industrial vision systems.

In fact, the Eye-RIS systems are the first industrial vision systems equipped with the following characteristics:

- Parallel distributed and progressive processing.

- Reliable, robust mixed-signal processors with handled errors.

- Distributed programmability.

This Thesis includes detailed descriptions of architecture and circuits used in the Q-Eye pixel, in the Q-Eye chip itself and in the vision systems developed based on this chip. Also, several examples of chips and systems in operation are presented.

# RESUMEN EXTENDIDO, MOTIVACIONES Y CONCLUSIONES

#### 1. Introducción

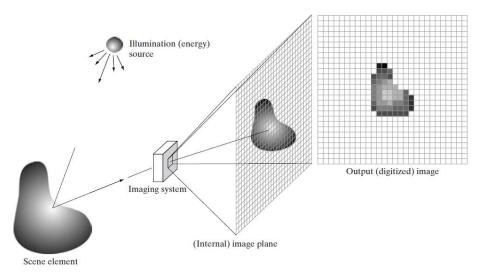

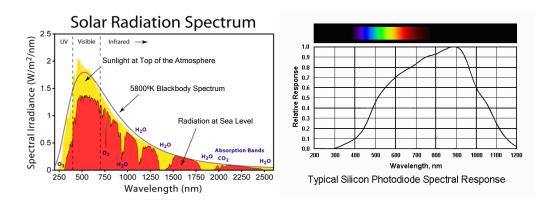

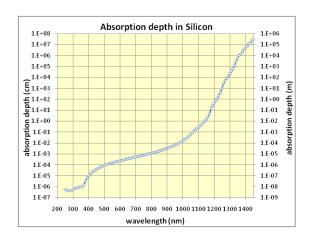

Esta Tesis aborda aspectos del diseño de circuitos integrados CMOS para la adquisición y el procesamiento de imágenes. Los <u>sensores de imágenes</u> integrados en tecnologías CMOS se identifican por las siglas CIS (<u>C</u>MOS <u>I</u>mage <u>S</u>ensors). Estos sensores generan una imagen cuando son irradiados por luz en las bandas del visible y del infrarrojo cercano, aproximadamente [400nm <  $\lambda$  < 1000nm].

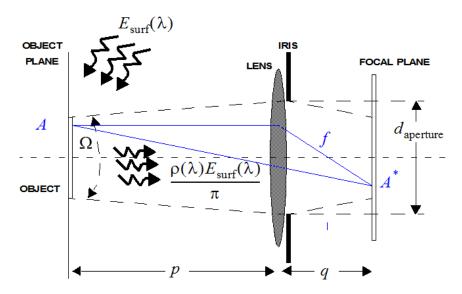

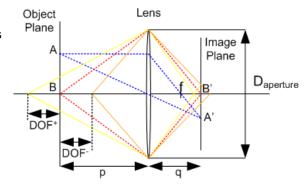

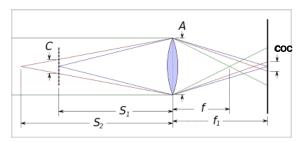

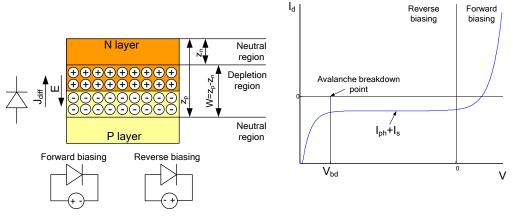

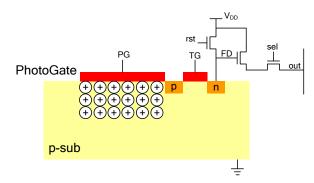

La captura de imágenes por sensores CIS implica, entre otros procesos, la *absorción* de los fotones y la *transformación* fotón-carga eléctrica. Estos dos procesos ocurren en dispositivos foto-sensores realizados dentro de un substrato semiconductor, en concreto Silicio. Por tanto este substrato constituye un "plano" activo, fotosensible, sobre el cual la luz es enfocada por una conjunto óptico formado por lentes para crear imágenes nítidas. Esta es la razón por la cual suele usarse el término *plano focal* para referirse a dicho plano.

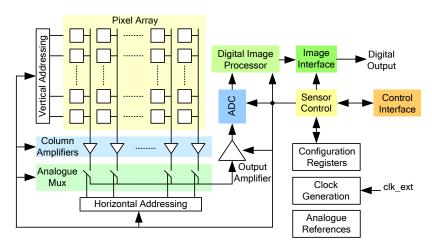

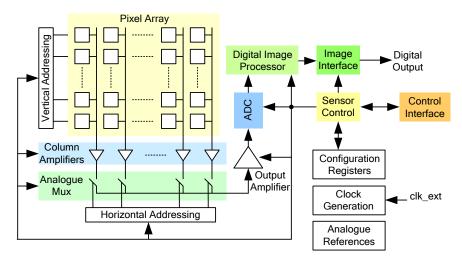

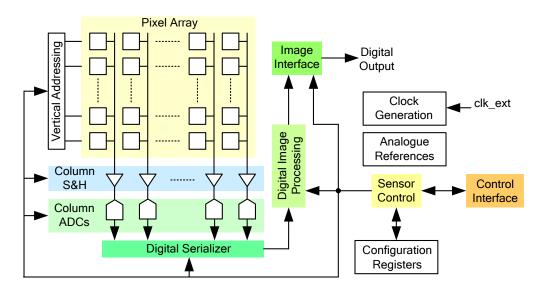

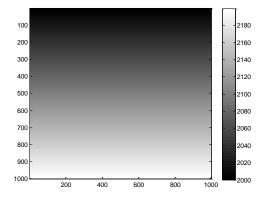

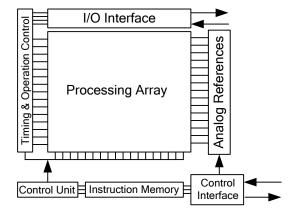

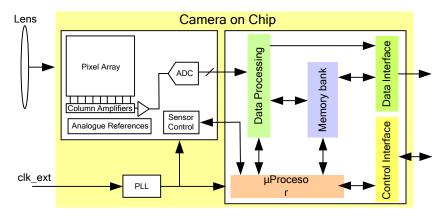

FIGURA 1. SENSOR DE IMAGEN CMOS DIGITAL.

Todas los bloques se supone que están realizados en el mismo substrato semiconductor

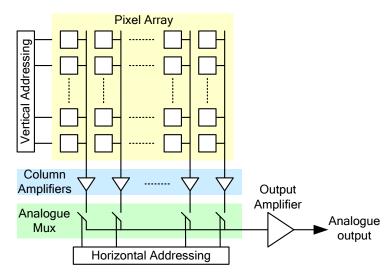

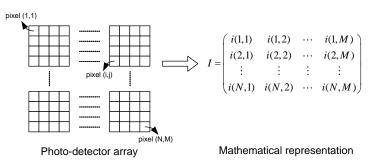

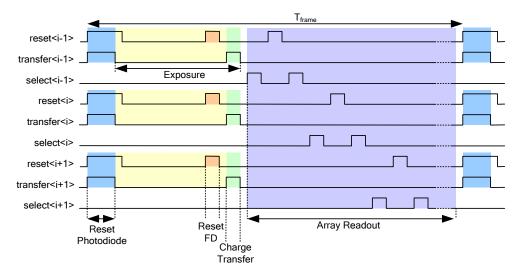

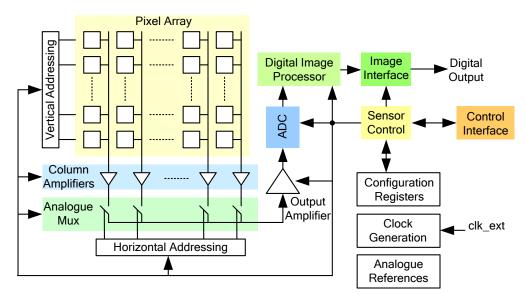

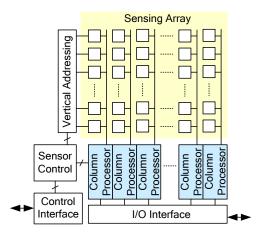

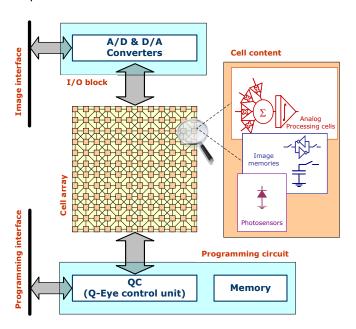

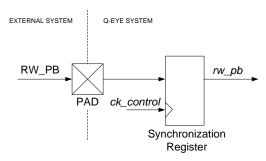

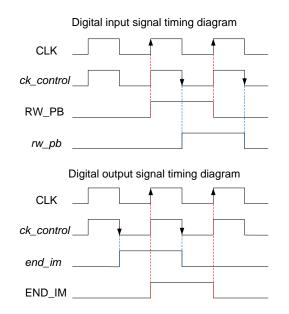

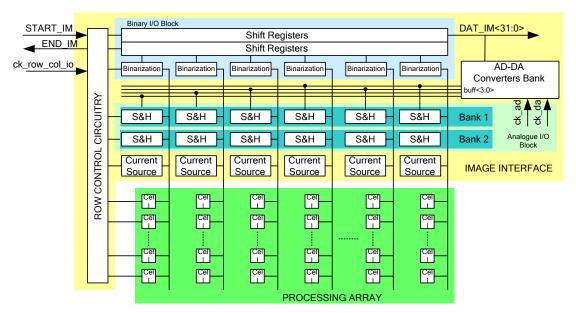

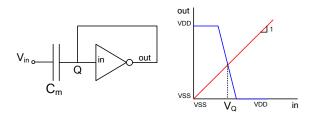

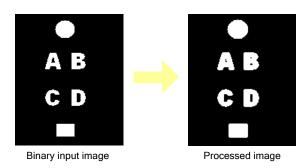

El plano focal incluye además circuitos no foto-sensibles, empleados con distintos propósitos. Esto se ilustra en la Figura 1, que describe conceptualmente un diagrama de bloques de un sistema CIS concebido para adquirir imágenes y codificarlas digitalmente [ANAFOCUS]. Cuando los CISs se fabrican en una *tecnología planar* <sup>1</sup>, donde todos los circuitos están implementados

en el plano focal, sólo la matriz de *píxeles* debe ser fotosensible. Esta es la parte etiquetada "Pixel Array", sobre fondo amarillo en la Figura 1. La matriz de píxeles consiste en un conjunto de dispositivos foto-sensores ubicados en una estructura regular, cada uno de los cuales captura una *muestra espacial* de la imagen incidente. El resto de los bloques del sensor se distribuyen por la periferia de la matriz foto-sensora y deben ser cubiertos ópticamente con objeto de reducir el impacto de la generación parásita de pares electrón-hueco fotoinducidos fuera del área foto-sensible o activa.

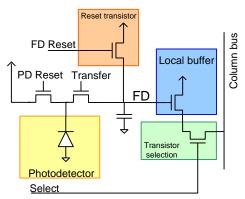

Los píxeles en sí incluyen también dispositivos foto-sensibles y circuitos no foto-sensibles. La figura de la derecha muestra conceptualmente la distribución de dispositivos en un pixel CIS,

<sup>&</sup>lt;sup>1</sup> El término planar indica que solo hay un substrato activo, por contraposición a las tecnologías con varios substratos interconectados verticalmente.

\_

donde el área activa, marcada en amarillo, constituye aproximadamente el 45% del área total del pixel. Este porcentaje se denomina "fill factor", mientras que el término "'pixel pitch" se usa para definir las dimensiones del pixel.

Reducir el "pixel pitch" y el aumentar el "fill factor" marcan tendencia en las actividades académicas e industriales sobre el diseño de CIS. Estas tendencias implican reducir la circuitería no foto-sensibles embebida en el pixel y dominan la investigación y el desarrollo de sensores para electrónica de consumo [Font11] [ISW13] [IS14] [Elmg14]. Sin embargo, en aplicaciones de "machine vision" los sensores de imágenes pueden contener una parte significativa de circuitería no foto-sensibles dentro del pixel. Los chips en esta Tesis pertenecen a este último grupo. En concreto, dichos chips incluyen circuitería no foto-sensible en el plano focal y el pixel para procesar las imágenes concurrentemente con su adquisición. Esta es la razón por la cual se usa el término SENSOR-PROCESADOR EN PLANO FOCAL [Rosk01] [Zara11] para referirse a este tipo de circuitos.

En general, los circuitos empleados en el acondicionamiento y procesamiento de señal en los sensores de imagen pueden ser integrados a diferentes niveles [Ohta08]:

- pixel.

- columna,

operar en modo FSI.

chip.

Los chips presentados en esta Tesis combinan estas tres estrategias [Rodr10b].

Los sensores CIS pueden ser iluminados por el frente (Front Side Illumination – FSI), o desde atrás, a través del substrato (Back Side Illumination - BSI). Las diferencias entre estos dos métodos se ilustran, para un único pixel, en la figura de la derecha. En el caso BSI, la superficie posterior de la oblea de semiconductor incluye micro-lentes ópticas y la luz alcanza directamente el silicio, donde los foto-sensores están integrados, sin interferir con las capas empleadas para interconexión y aislamiento en el IC. En el caso FSI. las micro-lentes ópticas son emplazadas sobre la superficie frontal del chip y la luz debe propagarse a través de las capas y estructuras que constituyen el circuito integrado antes de alcanzar el dispositivo foto-sensible localizado en el substrato de la oblea. El estudio de las ventajas y desventajas de ambas alternativas no es objeto de esta Tesis. Los lectores interesados pueden

consultar, por ejemplo, [Prov11]. Los chips descritos en esta Tesis han sido concebidos para

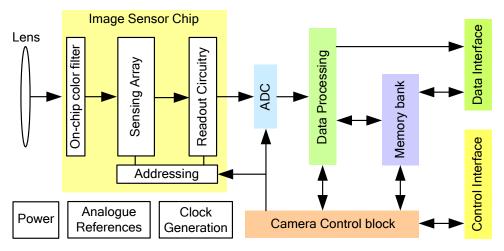

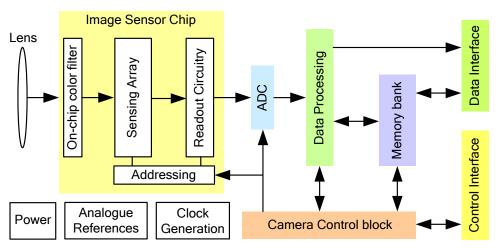

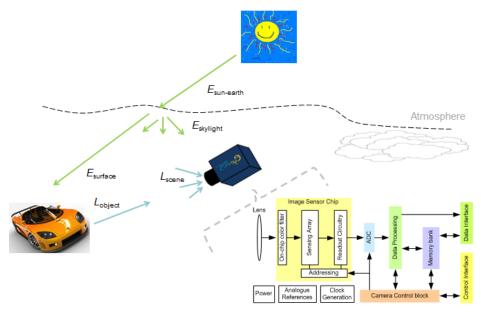

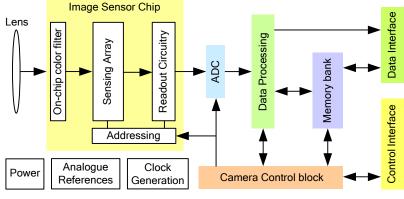

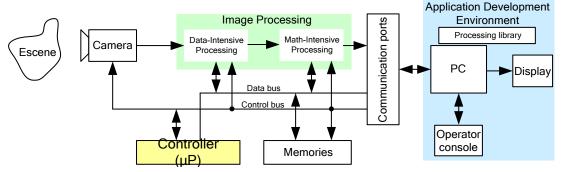

Los sensores de imágenes son las interfaces de entrada ("front-end") de las CÁMARAS y los SISTEMAS DE VISIÓN. . Los sensores de imagen suelen estar por tanto embebidos en una cámara o en un sistema de visión. La Figura 2 muestra el diagrama de bloques de una cámara incluyendo la óptica, la interfaz de entrada constituida por el sensor de imagen, y un número de bloques encargados del control, el almacenamiento de datos y las comunicaciones.

Aparte de los sensores de imágenes y todas las estructuras funcionales requeridas para el control, comunicación e integración del sistema, las cámaras pueden incluir circuitos y sistemas para analizar el flujo de imágenes y extraer información del mismo. Estos sistemas son entes complejos tanto en términos de "hardware" como de "software" y su diseño requiere explotar las sinergias entre ambas facetas — "hardware-software co-design". En cualquier caso, conviene recordar que por muy compleja que sea una cámara o un sistema de visión, su calidad y capacidad de operación van a depender críticamente de las prestaciones del sensor de imagen usado para la interface de entrada, ya que la calidad de las imágenes adquiridas está básicamente determinada por dicho sensor.

Aunque las contribuciones de esta Tesis, están mayormente en el diseño de chips, las consideraciones sobre el diseño de cámaras y sistemas de visión, incluyendo "smart cameras" [Belb09], están presentes en todos los capítulos, con énfasis especial en el Capítulo 5. A modo de ejemplo, la figura del margen izquierdo muestra una de las versiones del sistema de visión Eye-RIS descrito en dicho capítulo. Destaca la compacidad de un sistema que tiene la capacidad de ejecutar tareas de visión de forma autónoma. Esta compacidad, junto con la operación a muy alta velocidad son atributos conferidos por las arquitecturas y los circuitos propuestos en la Tesis.

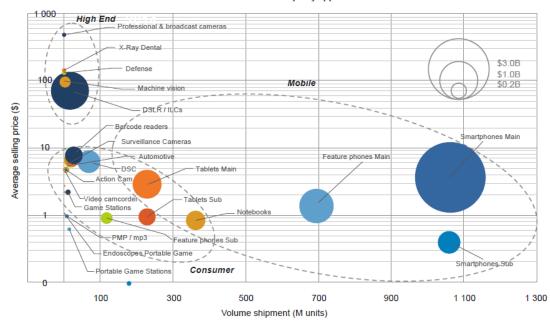

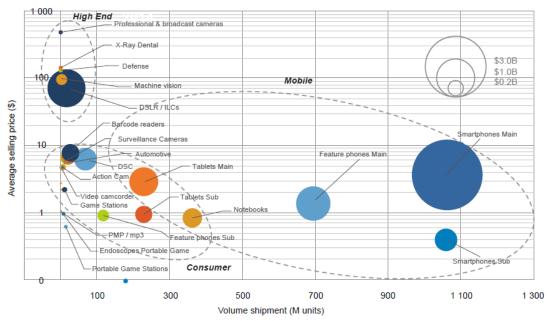

En este punto es pertinente preguntarnos: ¿por qué merece la pena abordar y estudiar los sensores de imágenes, cámaras y sistemas de visión y las tecnologías relacionadas? La experiencia de la vida cotidiana nos proporciona una respuesta intuitiva. No hay duda de que la capacidad de capturar, analizar e interpretar imágenes ópticas es crucial para la interacción con el entorno de cualquier sistema, natural o artificial, incluyendo los seres humanos. De hecho, los sensores de imágenes de estado sólido se utilizan en un número cada vez mayor de aplicaciones, con una previsión de volumen global de mercado de aproximadamente 3 mil millones de unidades para el año 2015 [Yole14a-b]. Además de la amplia utilización de dispositivos de visión en teléfonos móviles y dispositivos electrónicos personales, otros sectores de aplicación con un fuerte potencial de crecimiento están evolucionando rápidamente, tales como medicina, defensa, automoción, vigilancia, robótica, industria y similares.

FIGURA 2. DIAGRAMA DE BLOQUES DE UNA CÁMARA.

Entre otras razones, la actual proliferación de sensores de imagen de estado sólido está impulsada por las capacidades de las tecnologías CMOS modernas para integrar sistemas con tamaño reducido, poco peso y consumo de potencia, gran velocidad de operación, y amplias capacidades funcionales y flexibilidad. Estos sensores CIS son parte esencial de los modernos sistemas InfoTech *portátiles*, y una característica esencial en estos sistemas portátiles es poseer un factor SWaP (Size, Weight and Power) pequeño — conferido por el uso de tecnologías CMOS.

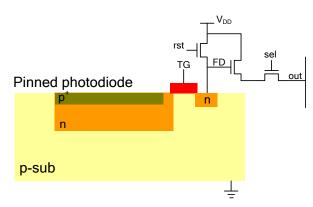

Sin embargo, hasta aproximadamente mediados de la década de los noventa, la expansión de los sistemas de visión CMOS se vio obstaculizado por la menor calidad de los dispositivos fotosensores compatibles con estas tecnologías en comparación con las tecnologías CCD (Charge Coupled Devices) [Naka06] [Ohta08]. En resumen, las imágenes captadas por los fotosensores CMOS primitivos no eran lo suficientemente buenas para numerosas aplicaciones industriales. En tal escenario las tecnologías CCD dominaron la realización industrial de cámaras y sistemas de visión y las CMOS quedaron relegadas a un segundo plano. Esta desventaja se atenuó de forma significativa con la mejora de los foto-sensores CMOS. Por ejemplo con los "pinned photodiode"s se alcanzaron niveles de calidad similares al CCD, haciendo viable al CMOS para múltiples aplicaciones prácticas. De hecho, pese a que las tecnologías CCD puedan quizás adquirir mejores imágenes, las ventajas de las tecnologías CMOS en términos de tamaño, peso, consumo de potencia, coste de producción, velocidad y capacidad para la integración de funcionalidades en sistemas embebidos, entre otras, han sido decisivas para que los sensores CMOS hayan ganado finalmente el duelo frente a los CCDs.

Actualmente, los sistemas de visión CMOS copan más del 90% del mercado de sensores de imagen de área, donde el término sensor de área se usa en contraposición a sensor de línea o sensor lineal. El primero captura las señales ópticas usando una matríz bidimensional de detectores, mientras que el segundo emplea un vector unidimensional de detectores, como los requeridos para aplicaciones de escaneado. Además, el volumen total de mercado para sistemas de visión CMOS está previsto que crezca significativamente durante los próximos

años, con una previsión total de mercado próxima a los 17 billones para 2018 [Yole14a-b]. La Figura 3 muestra los volúmenes de producción para sistemas CIS en diferentes campos de aplicación. Las principales ventajas de las tecnologías CMOS pueden resumirse en los siguientes puntos:

- · Coste,

- Tamaño,

- · Consumo de potencia,

- Velocidad,

- · Flexibilidad funcional.

Esta Tesis se centra en el estudio de los sistemas de vision basados en tecnología CMOS y no pretende analizar ni cuantificar las ventajas y desventajas de los sistemas CMOS frente a los sistemas CCD. Los lectores interesados en sensores de imágenes basados en tecnologías CCD pueden consultar, entre otras muchas referencias, a [Theu95].

2014 - CIS market landscape by application

FIGURA 3. PREVISIÓN DE VENTAS DE SENSORES CIS POR CAMPOS DE APLICACIÓN

Predicción realizada por Yole Development

Los avances tecnológicos en los sistemas de visión CMOS han sido impulsados principalmente por las aplicaciones de consumo. Estas condicionan también los desafíos técnicos de industrias y universidades en relación con los sistemas CIS. Como ya se mencionó, el mercado de consumo demanda píxeles con un "pitch" cada vez menor y con resolución espacial (número de píxeles) cada vez mayor. Además de este aumento en la resolución, otros retos tecnológicos para los sensores de imágenes CMOS son:

- a) mejora de la calidad de imagen a través de la mejora de los circuitos analógicos de lectura; acondicionamiento de la señal, conversión AD (<u>A</u>nalógico/<u>D</u>igital) y procesamiento digital de la señal;

- b) aumento de la velocidad de transmisión de datos, mejorando los circuitos de comunicación;

- c) reducción del área, potencia y coste a través de la integración de circuitos embebidos en un único chip ("system on chip") [ISW13] [Elmg14] [IS14].

Los avances recientes incluyen sensores de varios millones de píxeles con "pixel-pitch" del orden de  $1\mu m$ , velocidad de datos superior a los 10Gpx/s [Taka13], arquitecturas de lectura y conversión AD reconfigurables [Leñe14] [Kawa08], corrección de imagen [Chen12], gestión térmica y energética, etc.

Todos los desafíos tecnológicos citados anteriormente se centran en la adquisición de matrices de intensidad de luz que definen imágenes 2-D. Durante los últimos años también se han desarrollado técnicas y arquitecturas con el objetivo de incluir en los sistemas de visión la estimación de profundidad, es decir, información 3-D. Uno de los principales impulsores de estas actividades es el desarrollo de interfaces hombre-máquina para la industria del entretenimiento [Payb14], pero el potencial de estas tecnologías es enorme en campos de como vigilancia, inspección industrial, automoción y medicina. Además de las técnicas basadas en la estereoscopía, la triangulación y similares, se están haciendo esfuerzos significativos en el desarrollo de píxeles CMOS que sean capaces de capturar la información de profundidad a través de técnicas de tiempo de vuelo (Time of Flight). Entre las diferentes aproximaciones, los diodos de avalancha, Single Photon Avalanche Diodes (SPADs), están siendo objeto de un creciente interés [Seit11]. Aparte de tecnologías de pixel específicas para ToF (tales como SPADs, doble puerta de transferencia, etc.), las medidas de tiempo de vuelo requieren complejos esquemas de iluminación [Nicl11]— todavía lejos de una solución integrada en un solo chip para capturar imágenes en 3-D. Por otra parte, los sensores 3-D incorporan a fecha de hoy muchas menos capacidades de procesamiento "on-chip" que los actuales sensores de visión 2-D. En esta Tesis, no se abordan problemáticas relacionadas con la adquisición de imágenes 3-D.

Retomando el hilo de las ventajas del uso de tecnologías CMOS, tal vez la más relevante está conferida por la capacidad para diseñar sistemas de visión completos en un único chip ("system-on-chip") en lugar de sólo sensores de imagen. El concepto de cámara integrada en un único chip ("camera-on-chip") fue introducido en [Foss97]. Con referencia al diagrama de bloques de la Figura 2, este concepto implica la incorporación en un único substrato semiconductor del máximo número posible de los bloques funcionales necesarios para implementar una cámara. Por tanto, los sistemas de visión CMOS integrados en un único chip pertenecen a la categoría de sensores inteligentes — "smart sensors"; por ejemplo, sensores con inteligencia embebida [Meij01].

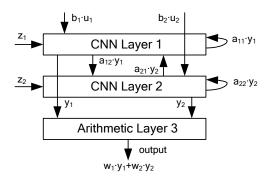

El concepto SENSORES INTELIGENTES es genérico y ambiguo. En general, la característica 'inteligente' hace referencia a cualquier tipo de circuito empleado para procesar las señales adquiridas por los sensores, ya sea en funciones como la lectura de datos y la corrección de errores, o para la extracción de información a partir de las imágenes. En la práctica pueden considerarse diferentes niveles de inteligencia. El más bajo implica básicamente funciones relacionadas con la lectura de las imágenes, corrección de errores y comunicaciones, que son las más utilizadas actualmente en la industria. En el mercado encontramos sensores de imágenes inteligentes con microprocesadores embebidos que generan imágenes de alta calidad completamente corregidas a velocidades del orden de miles de imágenes por segundo (Frames-per-Second, FpS) y con niveles de ruido equivalentes inferiores a un electrón [ANAFOCUS]. Niveles de inteligencia superiores, como los requeridos para extraer e interpretar la información contenida en las imágenes, y generar las decisiones y acciones correspondientes, han sido estudiados y desarrollados en el ámbito académico durante años [Eklu96] [Rodr04] [Abbo08] [Fern11] [Lopi11], y es solo ahora cuando empiezan a implementarse en sistemas industriales [ANAFOCUS]. Entre las razones de este retraso podemos citar la falta de estandarización en las soluciones arquitecturales, en su programación y en los formatos de salida [Khro13]. Sin embargo, los problemas arquitecturales pueden abordarse mediante el uso de arquitecturas celulares y, en particular, a través de la utilización del paradigma de redes celulares no lineales (Cellular Nonlinear Network, CNN. Este paradigma se adapta a las características específicas del problema, en conreto:

- gran cantidad de datos con una estructura matricial regular que contiene propiedades e información distribuida en la globalidad, y

- que pueden ser extraídas a través de interacciones y operaciones locales,

- basadas en la propagación y procesamiento de señales en el espacio, a lo largo y ancho de cada imagen, y en el tiempo, a lo largo de la secuencia de imágenes [Rosk01] [Chua02].

Dependiendo del nivel de inteligengia integrada, distinguiremos dos tipos de sensoresprocesadores CMOS:

- Sensores de imágenes CMOS inteligentes (<u>S</u>mart <u>C</u>MOS <u>I</u>mage <u>S</u>ensors) denominados SCIS.

- Sensores de visión CMOS (CMOS VIsion Sensors) denominados CVIS.

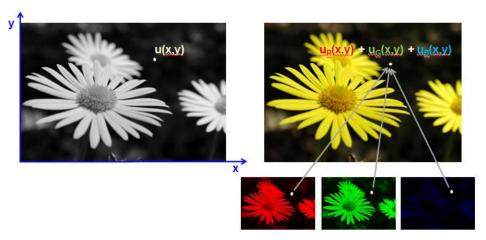

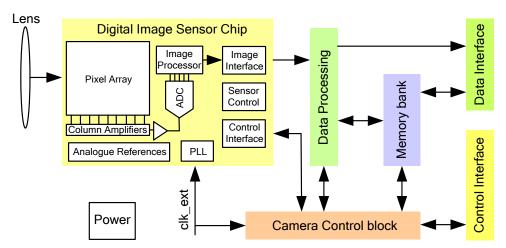

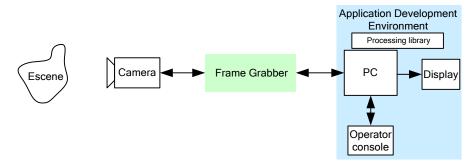

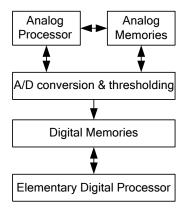

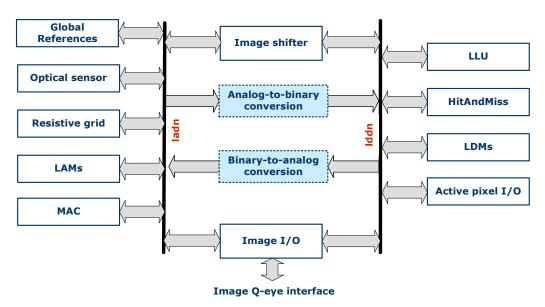

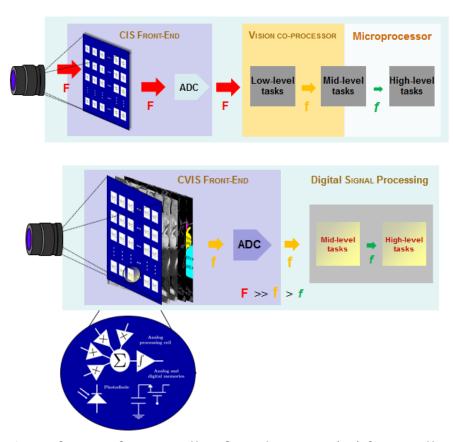

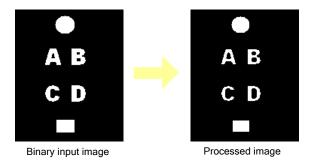

La Figura 4 ilustra las diferencias entre SCIS, por un lado, y CVIS, por otro lado. Aunque las entradas de ambos circuitos integrados son imágenes capturadas por foto-sensores localizados en el plano focal, sus salidas son de naturaleza diferente.

En el caso de los sistemas SCIS, los resultados básicos de la cadena de procesamiento son imágenes; bien en escala de grises o en color, en formato analógico o digital, sin o con correcciones, etc. Por el contrario, los resultados de los sistemas CVIS pueden no ser imágenes sino *características* <sup>2</sup> o incluso decisiones basadas en el análisis espacio-temporal de la información contenida en la escena.

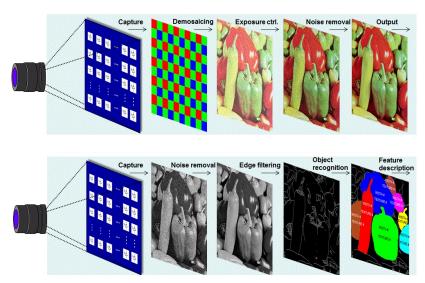

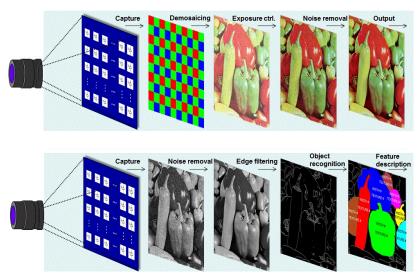

FIGURA 4. ILUSTRACIÓN DE LAS DIFERENCIAS ENTRE LOS SISTEMAS SCIS (ARRIBA) Y CVIS (ABAJO)

Pese a las diferencias funcionales, los sistemas SCISs y CVISs son estructuralmente similares en que ambos combinan dos tipos diferentes de sub-sistemas integrados en un substrato de silicio común:

- Los usados para la adquisición de imágenes: por ejemplo, la captura de la potencia lumínica y su transducción en tensión o corriente. Estos consisten esencialmente en uniones pn polarizadas en inversa (foto-diodos) y en circuitos de señal-mixta que controlan la operación del sensor.

- Los que se utilizan para la lectura de los resultados del proceso de transducción de la luz, acondicionamiento de la señal y conversión AD, los empleados en la corrección y procesamiento, en el control global del sistema y las comunicaciones. Estos subsistemas están constituidos por circuitos analógicos, de señal-mixta y circuitos puramente digitales.

Estas similitudes pueden ser explotadas durante la fase de diseño ya que muchos conceptos, arquitecturas y circuitos son compartidos por ambos tipos de sistemas y pueden ser reutilizados por los diseñadores. Este hecho queda reflejado a lo largo de la Tesis.

#### 2. RESUMEN DE LA TESIS

Como se ha mencionado anteriormente, el mercado de sistemas de visión, incluyendo sectores como vigilancia, visión industrial, sistemas de transporte inteligentes, electrónica de consumo, quiado de vehículos, redes inalámbricas de sensores, etc., demanda:

- reducción de los costes de producción a nivel de sistema;

- aumento del nivel de integración, con implementaciones físicas compactas, de tamaños reducidos y con el menor número posible de componente;

\_

<sup>&</sup>lt;sup>2</sup> Características de una imagen pueden ser interpretadas como manifestaciones de la información contenida en una imagen; por ejemplo, el número de objetos presentes en una imagen, localización de objetos, etc.

- mayor calidad de la imagen y mejores prestaciones de las funcionalidades embebidas en los chips;

- mayor velocidad de operación;

- mejor uso posible del presupuesto de potencia disponible.

- etc.

Esta Tesis describe sensores de visión CMOS (CVISs), y sistemas basados en dichos chips, para alcanzar los objetivos anteriores mediante:

- arquitecturas concebidas para el procesamiento paralelo de las imágenes;

- el uso de procesadores de señal-mixta, en lugar de meramente digitales, distribuidos por pixel.

Las razones que subvacen a estas soluciones se detallan a continuación.

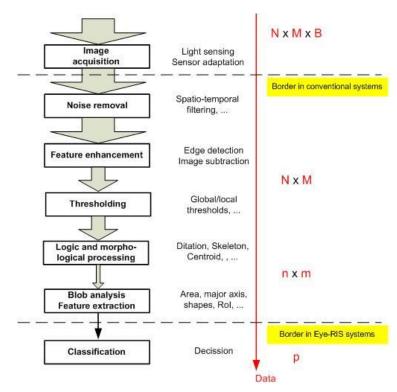

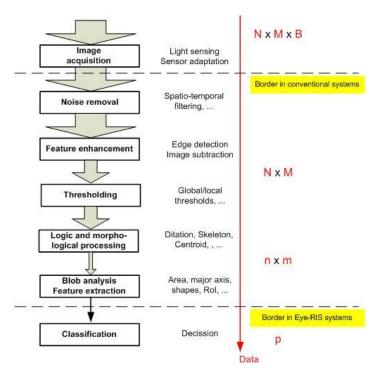

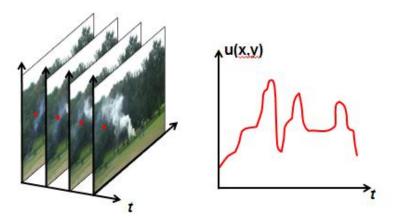

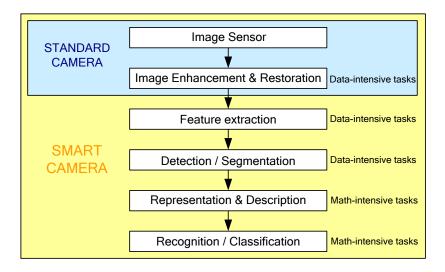

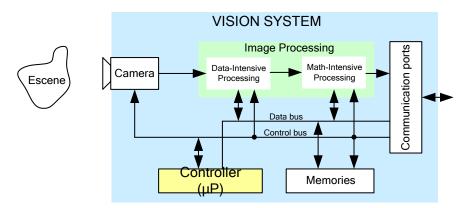

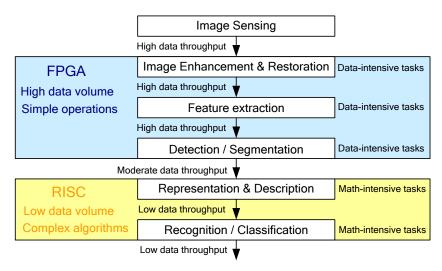

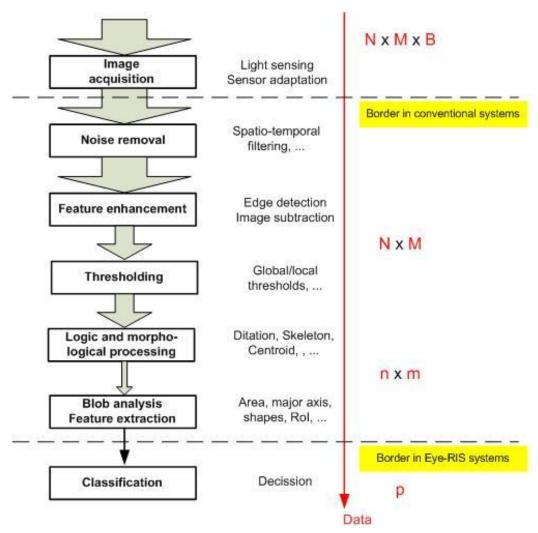

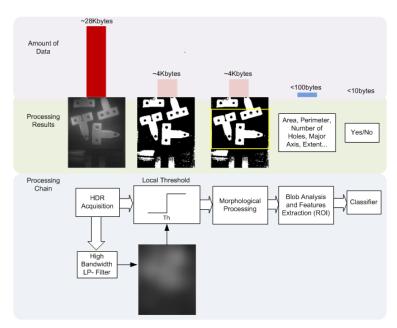

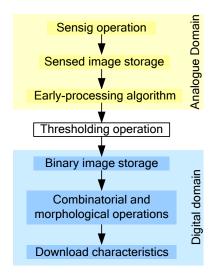

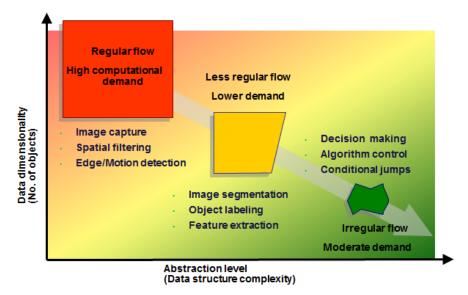

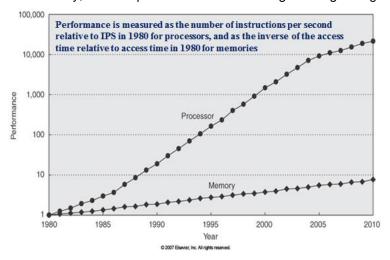

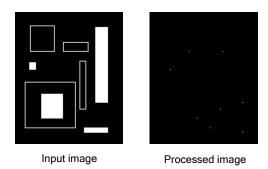

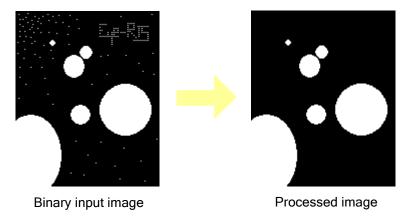

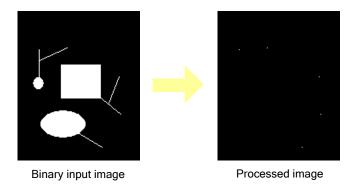

El PROCESAMIENTO PARALELO es muy adecuado para manejar la gran cantidad de datos presentes en las primeras etapas de la cadena de procesamiento de imágenes. Tal como se ilustra en la Figura 5, en las etapas iniciales de la cadena de procesamiento de la visión, el número de datos puede ser muy elevado pues es proporcional a la resolución espacial y al número de bits por dato de píxel. Además, muchos de los datos son redundantes y por lo tanto inútiles para los fines de extracción de información y la realización de tareas de visión. Sin embargo, el número de datos decrece a medida que se ejecutan los flujos de información y detección de características a través de la cadena de procesamiento. En realidad, en la toma de decisión final del sistema de visión están implicados muy pocos datos. Por ejemplo, en aplicaciones de vigilancia, las decisiones van a depender principalmente de si la escena contiene algún objeto sospechoso o no.

FIGURA 5.- CADENA DE PROCESAMIENTO EN ALGORITMOS DE VISIÓN.

Empezando arriba con las imágenes captadas por el sensor (datos en crudo), la cantidad de datos decrece y el nivel de abstracción aumenta. N representa el número de filas, M el número de columnas y B el número de bits usado por dato de pixel: n<N; m>M and p<(n,m). Las arquitecturas propuestas en esta Tesis mapeas esta estructura de datos en capas mediante el uso de estrategias de procesamiento específicas para cada paso de la cadena.

En las arquitecturas de sistemas de visión convencionales la frontera entre sensores y procesadores está localizada en un punto done la cantidad de datos a transmitir es grande (ver la linea discontinua en la parte superior de la Figura 5). De hecho, los sistemas convencionales

descargan imágenes completas de los sensores para su posterior procesamiento, por lo que requieren una cantidad significativa de memoria y tienen una demanda computacional elevada. Por ejemplo, para una imagen con formato de alta definición para TV, con una resolución espacial 1920x1080 y una longitud de palabra de 10 bits por pixel, el número de datos asociados a una escena ("frame") es 20.74Mbits, equivalente a 2.6Mbytes. Por tanto, la velocidad del flujo de datos asociada a la transmisión de esta imagen en un sistema operando según el estandar de video (30FpS) es 622Mbits por segundo. Para sistemas operando a altas velocidades, por ejemplo las aplicaciones de inspección industrial pueden requerir 1000FpS, el tratamiento de esta gran cantidad de datos puede llegar a convertirse en un obstáculo insuperable.

Sin embargo, usando sistemas CVISs como los propuestos en esta Tesis, la frontera o interfaz entre el sensor <sup>3</sup> y los procesadores digitales está localizada en un punto donde la cantidad de datos a transmitir es pequeña, pues se transmiten características presentes en la escena en lugar de los datos de pixeles completos de la imagen (ver la linea discontinua en la parte inferior de la Figura 5). Supongamos que nuestra aplicación objetivo consiste en seguir objetos que se mueven a una velocidad de 40m/s en la escena. Esto requiere capturar y analizar imágenes a una razón de 2000Fps. En el resultado del proceso de captura y análisis el único dato pertinente es la posición predicha de los objetos. Esta es en realidad la única información transmitida al procesador digital. Pero para extraer dicha información se deben realizar antes las siguientes tareas:

- Adquisición de imágenes,

- filtros paso de baja,

- · detección de actividad,

- estimación de movimiento,

- seguimiento del objeto,

- lazo de control y

- predicción de posición.

Los sistema CVISs propuestos en esta Tesis implementan estas y otras tareas directamente en el plano focal, evitando así los cuellos de bolleta en la comunicación de los datos y reduciendo los requerimiento de potencia de cálculo memorias asociados a las aqruitecturas convencionales. Consideremos por ejemplo el caso de una operación de *convolución* para un filtrado espacial linear. Esta operación implica 9 multiplicaciones y ocho sumas por pixel. Con lo cual, para el ejemplo previo del estándar de alta definición para TV (resolución espacial 1920x1080 a 30FpS) la velocidad de procesamiento requerida sería 1.06GOpS (<u>G</u>iga <u>O</u>perations <u>per S</u>econd). Y el filtrado es solo una de las muchas tareas que deben ser llevadas a cabo en las primeras etapas del procesamiento de imágenes.

En resumen, además de los problemas en la comunicación y almacenamiento de datos, los sistemas de visión convencionales neecistan potencias de cálculo elevadas. Es obvio que el problema es abordable con las tecnologías digitales actuales siempre que no existan limitaciones en el consumo de potencia y en el tamaño del sistema. Pero bajo fuertes restricciones de consumo de potencia, tamaño y velocidad de operación, es conveniente considerar arquitecturas alternativas como las porpuestas en esta Tesis.

Además del procesamiento paralelo, otra característica distintiva de las soluciones propuestas en esta Tesis, es el uso de **CIRCUITOS DE SEÑAL-MIXTA** para procesamiento. Esto circuitos operan a mayor velocidad y con mayor eficiencia energética que sus homólogos digitales, bajo el supuesto de que los requisitos de *precisión* sean moderados. Además, procesar en paralelo con circuitos analógicos es ventajoso, frente a la alternativa digital, en términos de la cantidad de operaciones realizables para un consumo de potencia y una velocidad de operación dadas [Carm13]. En resumen, las arquitecturas de sistemas de visión propuestas en esta disertación superan a las soluciones convencionales en términos de la figura de mérito SWaP así como en términos de la relación entre la potencia-de-cálculo y el consumo-de-energía. Estas características, junto con el coste, resultan ideales para reducir la brecha que existe entre los detectores binarios y los detectores de área en aplicaciones de inspección y visión artificial

-

<sup>&</sup>lt;sup>3</sup> Los sistemas CVISs no solo adquieren imágenes sino que las procesan. Por ello, un término más conveniente para ellos es el de sensor-procesador en lugar del de sensor.

ver Figura 6. Es decir, los sistemas propuestos en esta Tesis pueden, por coste, tamaño y velocidad, reemplazar a los sensores uni-dimensionales que se usan actualmente en muchas cadenas de producción, capacidad de procesamiento superiores en varios órdenes de magnitud.

# Cost Point detection (One dimension) (Two dimension) (Two dimension)

## Target Market

FIGURA 6.- POSICIÓN DEL SENSOR INTELIGENTE TOSHIBA-TELI SPS [TOSH14] EN EL PLANO DE MERCADO OBJETIVO COSTE FRENTE A FUNCIONALIDAD. ESTA CÁMARA DE TOSHIBA-TELI EMPLEA ARQUITECTURAS CVIS CONCEBIDAS EN ESTA TESIS.

Imagen tomada de http://www.toshiba-teli.co.jp/en/products/industrial/sps/sps.htm

Function

El sistema CVIS básico desarrollado en esta Tesis se llama Q-Eye. El píxel implementado en el sensor Q-Eye ha sido dotado de un alto nivel de capacidad de procesamiento y programación con el fin de implementar el mayor número posible de las funciones de procesamiento requeridas en las aplicaciones de *visión temprana* [Toma06]. Esta capacidad de programación del Q-Eye permite el desarrollo de cámaras inteligentes y sistemas de visión embebidos con una funcionalidad versátil. Es decir, el Q-Eye no está diseñado para una tarea específica sino que puede implementar una amplia variedad de algoritmos de visión mediante programación.

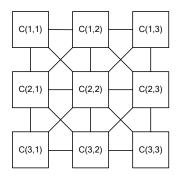

Los píxeles del sistema Q-Eye intercambian información con sus vecinos para realizar distintas operaciones, tales como:

- Convoluciones lineales con máscaras programables.

- Difusiones controladas por tiempo y nivel de sañal, a través de un grid resistivo embebido en el plano focal.

- Aritmética de imágenes.

- Flujo de programación dependiente de la señal.

- Conversión entre los dominios de datos: imagen en escala de grises e imagen binaria

- Operaciones lógicas en imágenes binarias.

- Operaciones morfológicas en imágenes binarias.

- · etc.

El <u>Capítulo 3</u> proporciona una descripción detallada de la arquitectura del píxel del Q-Eye. Esto incluye esquemas para todos los circuitos integrados dentro del píxel, la descripción del comportamiento nominal de los circuitos, el análisis de los errores principales de los circuitos, y ejemplos del impacto de estos errores en la operación del sistema.

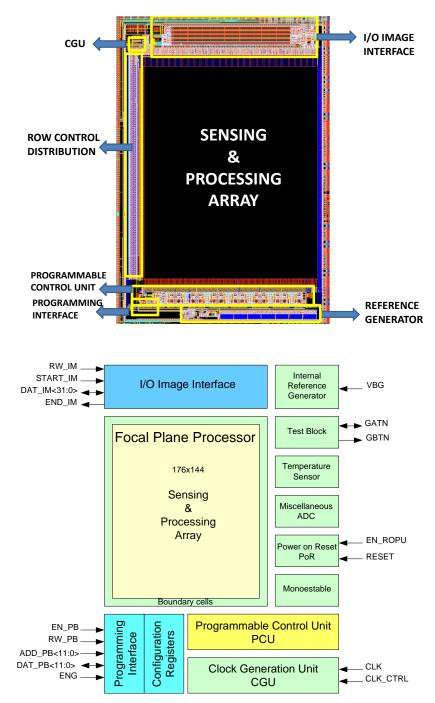

El <u>SISTEMA DE VISIÓN CMOS Q-EYE</u> es descrito en el <u>CAPÍTULO 4</u>, donde se explica en detalle los puertos de comunicación, la programabilidad del sistema, las arquitecturas de los canales de lectura y los bloques misceláneos. Este Capítulo 4 introduce también los aspectos a nivel de sistema que deben considerarse durante la fase de diseño.

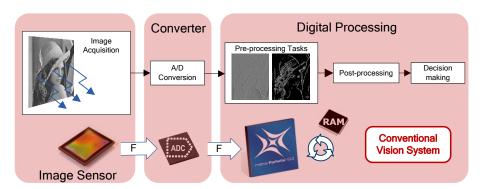

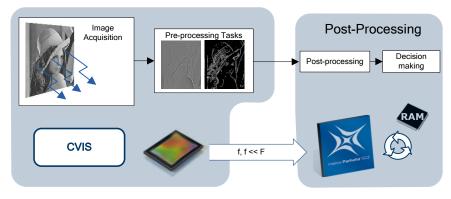

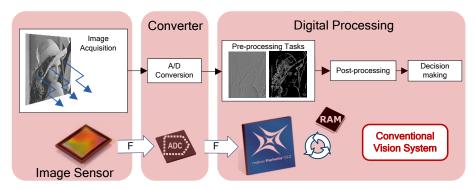

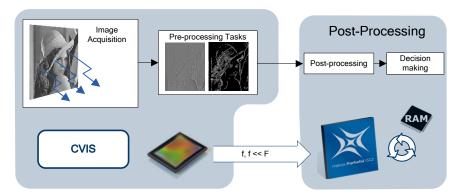

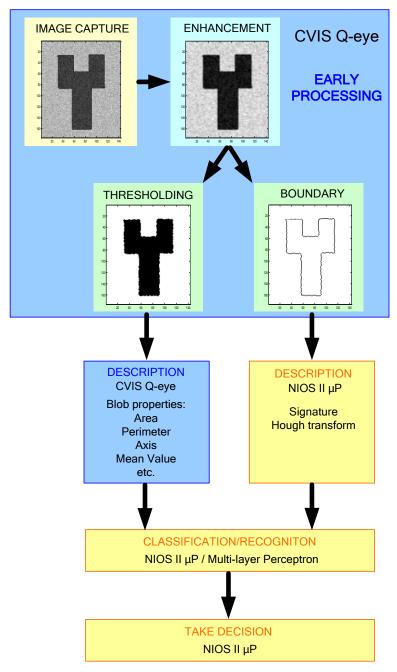

La Tesis también describe el desarrollo de sistemas de visión basados en el sensor CVIS Q-Eye. Las diferencias entre estos sistemas y sistemas de visión convencionales han sido presentadas anteriormente haciendo referencia a la localización de la interfaz de datos entre la interfaz física de entrada sensor-procesador y los procesadores digitales estándar dentro de la cadena de procesamiento – ver Figura 5. La Figura 7 y la Figura 8 complementan estas explicaciones.

Por un lado, la Figura 7 corresponde a un sistema de visión convecional. En este sistema, la interface de entrada captura la luz asociada a las imágenes de entrada y trasmite los datos de "frames" completos, representado por el símbolo **F**, para su posterior procesamiento. Como se mencionó anteriormente, la enorme cantidad de datos asociados a una imagen crea cuellos de botella en comunicaciones, memorias y potencia de cómputo.

FIGURA 7.- FLUJO DE DATO EN UN SISTEMA DE VISIÓN CONVENCIONAL

Por otro lado, la Figura 8 corresponde a los sistemas de visión considerados en esta Tesis. En este caso, la interfaz de entrada no sólo captura la imagen sino que además procesa la información contenida en la misma. Por tanto, la cantidad de información a transmitir, representada por el símbolo  $f \ll F$ , a los posteriores bloques de procesamiento es mucho menor. En realidad, en la arquitectura de la Figura 8, el procesamiento se lleva a cabo de forma progresiva, distribuyendose las tareas de procesamiento entre la interfaz de entrada y el núcleo de procesadores digitales. La interfaz de entrada sensor-procesador realiza un pre-procesado de los datos ejecutando los algoritmos de procesamiento en paralelo directamente en la matriz de píxeles. Estos algoritmos deben tratar una gran cantidad de datos y son muy demandantes en términos de potencia y velocidad, por lo que se benefician del uso de circuitos de señalmixta. Respecto al pos-procesamiento, éste trata una menor cantidad de datos pero requiere lógica compleja con numerosos puntos de decisión, diferentes caminos de ejecución, etc. El pos-procesamiento consiste en complejos algoritmos los cuales requiren programabilidad y reconfigurabilidad. La carga computacional no es alta porque la cantidad de datos a procesar es mucho menor, relajándose las especificaciones de los procesadores digitales incluido en el sistema de visión. En definitiva, las diferentes secciones de la arquitectura propuesta se adaptan a la naturaleza de los datos a tratar, y el sistema final es mucho más eficiente que uno convencional.

FIGURA 8.- FLUJO DE DATOS EN UN SISTEMA BASADO EN EL CVIS Q-EYE.

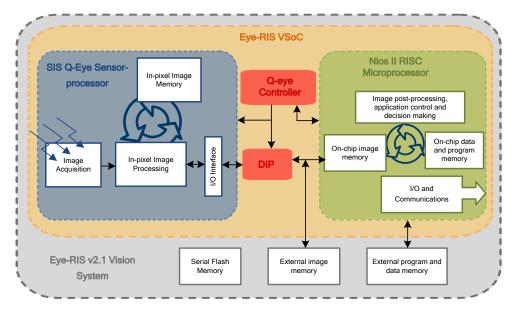

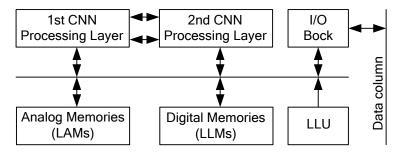

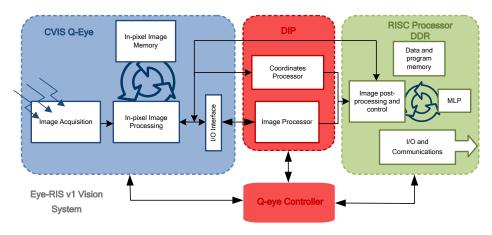

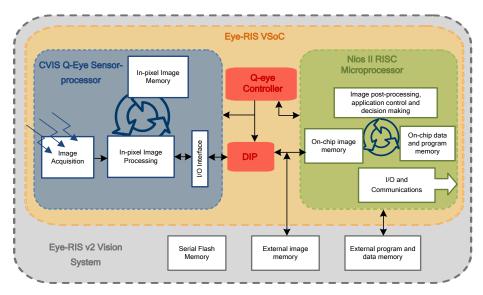

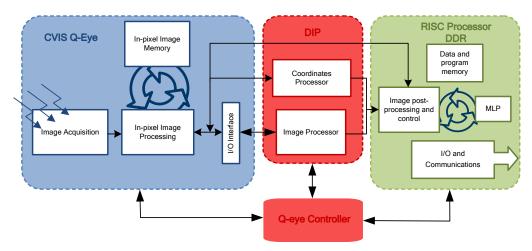

En el <u>Capítulo 5</u>, se describen dos sistemas de visión desarrollados sobre el Q-Eye, en base al concepto representado en la Figura 8. Dichos sistemas son:

- Eye-RIS v1 y

- Eye-RIS v2 (Vision System on Chip),

Estos sistemas sirven como demostradores de la viabilidad técnica y las ventajas de incorporar CVIS al diseño de sistemas de visión embebidos.

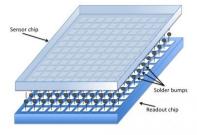

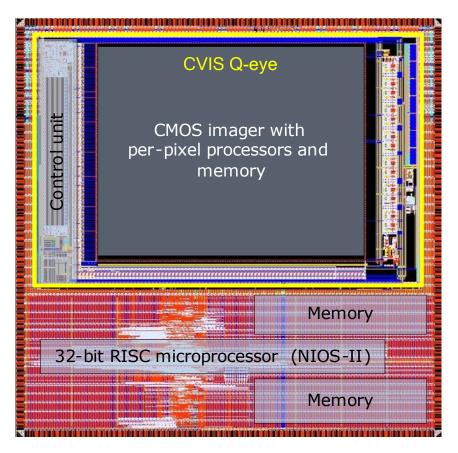

Las diferencias entre ambos sistemas están en el nivel de integración. El segundo sistema (Eye-RIS\_v2) integra sobre el mismo silicio el sensor-procesador Q-Eye y el microprocesador RISC, mientras que el primero (Eye-RIS\_v1) integra el microprocesador RISC en una FPGA fuera del silicio. El Capítulo 5 incluye también secciones que muestran estos sistemas en operación.

Esta Tesis es completada con un <u>CAPÍTULO 2</u> dedicado a introducir conceptos básicos relacionados con la adquisición y procesamiento de imágenes y a explicar los principios de las aproximaciones arquitecturales empleadas a lo largo de esta Tesis.

#### 3. CONCLUSIONES Y CONTRIBUCIONES

Con esta Tesis se demuestra la viabilidad técnica del desarrollo e implementación de sensores CVIS (CMOS Vision Image Sensors) con procesadores paralelos de señal-mixta "per-pixel" y de sistemas de visión basados en dichos sensores para aplicaciones industriales. Las ventajas principales de estos sistemas de visión respecto a las arquitecturas convencionales de sistemas de visión son:

- aumento del nivel de integración de las implementaciones físicas permitiendo en última instancia la realización de sistemas de visión compactos, en un solo chip;

- mayor velocidad de operación;

- mejor uso posible de la potencia y la energía disponibles.

Las contribuciones de la Tesis producen desde la base del diseño e implementación de una arquitectura específica de sistema CVIS – el sensor-procesador Q-Eye. El estudio realizado para el diseño del Q-Eye ha considerado los diferentes niveles de jerarquía y campos de conocimiento que lleva asociado el desarrollo de un sistema de estas características. Dichos niveles van desde la definición de su arquitectura y especificaciones en base a las necesidades determinadas por las aplicaciones objetivo, hasta el análisis y diseño de los bloques de circuito que implementan sus funciones básicas usando técnicas de circuitos integrados.

Partiendo del Q-Eye se han concebido e implementado dos sistemas de visión que usan a dicho CVIS como interface. Estos sistemas son:

- Eye-RIS\_v1 y

- Eye-RIS\_v2.

Este último es un claro exponente del nivel de integración que puede alcanzarse con las técnicas propuestas en la Tesis pues s trata básicamente de un sistema de visión implementado íntegramente en un único chip (Vision System on Chip).

A continuación se resumen las aportaciones principales de la Tesis:

• Definición de un conjunto de operaciones básicas que pueden implementarse con circuitos a nivel de pixel y que permiten la implementación de las funciones de bajo nivel usualmente utilizadas en las primeras fases del procesamiento de imágenes. Poseer este conjunto de operaciones básicas dota al sensor-procesador de la versatilidad y programabilidad adecuados para desarrollar un elevado número de algoritmos en una amplia gama de aplicaciones. En concreto, el pixel del Q-Eye tiene mayor nivel de programabilidad que la mayoría de sus predecesores, muchos de los cuales incluyen circuitería para desarrollar tareas específicas y no son adecuados por lo tanto para sistemas industriales. Los CVISs ACE y CACE tienen niveles de programabilidad semejantes pero sus implementaciones son mucho más costosa en términos de área y potencia.

- Implementación mediante circuitos de cada una de las operaciones básicas incluidas al nivel de pixel, garantizando un nivel de precisión moderado (8-bits), y optimizando consumos de potencia y área del pixel para conseguir la mayor resolución espacial y el mejor "fill factor" posible. El resultado de ello ha sido que el pixel del Q-Eye tiene uno de los mayores niveles de densidad de dispositivos por área entre todos los pixeles con procesamiento implementados hasta la actualidad. Además, tanto la operación básica como los circuitos que la implementan se han desarrollado para garantizar robustez en la ejecución de los algoritmos de procesamiento. Una operación robusta del sensor significa que los resultados de los algoritmos, y las configuraciones y secuencia de instrucciones asociadas a los mismos, se mantienen tanto de chip a chip, como para condiciones ambientales y de entorno cambiantes dentro de los límites especificados. De hecho, una demostración de esto, es que los sistemas de visión Eve-RIS basados en el sensor inteligente Q-Eye son los primeros sistemas de visión industriales con procesamiento masivamente paralelo de señal-mixta en el plano focal que son fiables, robustos y con errores controlados susceptibles de calibración. Esto ha propiciado su comercialización.

- Con objeto de garantizar la precisión de 8 bits, se ha llevado a cabo un análisis exhaustivo de los errores y no-idealidades asociadas a las implementaciones de las operaciones básicas. También se ha desarrollado una estrategia para implementar las funciones de procesamiento de bajo nivel de manera que se obtenga la menor acumulación posible de errores. Para ello se han generado modelos de las operaciones básicas a nivel de pixel y sus no-idealidades, para posteriormente estudiar el efecto de estos errores en los algoritmos de procesamiento. Esto se traduce en una gran precisión y reproducibilidad de la operación del Q-Eye "en campo".

- En base al pixel desarrollado, se ha diseñado el sensor CVSI Q-Eye en una tecnología 180nm estándar CMOS de 1.8V. Las funcionalidades más relevantes implementadas en el mismo se resumen a continuación:

- Este sensor-procesador adquiere y procesa imágenes de forma concurrente, extrayendo características a muy alta velocidad a partir de la información espaciotemporal contenida en la secuencia de imágenes. La alta velocidad de operación viene conferida por el uso de procesamiento masivamente paralelo.

- El Q-Eye se ha implementado en una arquitectura de procesador tipo <u>Single</u> <u>Instruction Multiple Data (SIMD)</u> que saca el máximo rendimiento de la capacidad de procesamiento de la matriz de píxeles multi-función.

- Las instrucciones a ejecutar por dicha matriz se aplican a través de una interfaz de programación y bloque de control. Estos últimos contienen memorias para almacenar micro-instrucciones, las cuales definen la secuencia de operaciones a desarrollar por la matriz de pixeles con procesamiento embebido. El contenido de dichas memorias puede ser actualizado por un "host" externo. Esta arquitectura permite que el micro-procesador del sistema de visión, en el cual se integra el sensor inteligente diseñado, pueda definir los algoritmos de procesamiento de imágenes de bajo nivel a desarrollar por el Q-Eye, el cual actúa como "hardware" específico de procesamiento o co-procesador.

- Las imágenes resultantes de este procesamiento son descargadas a través de la interface de imágenes. Esta interface se ha diseñado con un elevado grado de configurabilidad, pudiéndose cargar y descargar tres tipos de imágenes:

- ✓ Imágenes binarias que representan la información comprimida resultante del procesamiento de bajo nivel y que contienen las características necesarias para el procesamiento de alto nivel.

- ✓ Coordenadas de eventos o píxeles activos. Este protocolo de descarga es óptimo en velocidad para imágenes con puntos activos dispersos.

- ✓ Imágenes en niveles de gris con 8 bits de resolución. Esta interfaz se ha definido principalmente con propósito de test. Pero puede usarse como interfaz de entrada salida al utilizar al Q-eye sólo como co-procesador de imágenes en niveles de gris.

La capacidad de cargar y descargar imágenes permite utilizar al sistema Q-Eye sólo como co-procesador de imágenes (binaria y en niveles de gris)

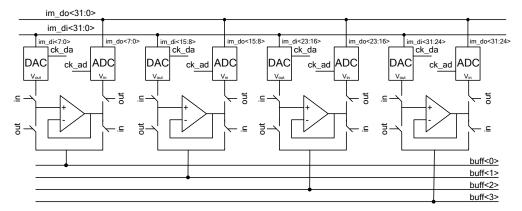

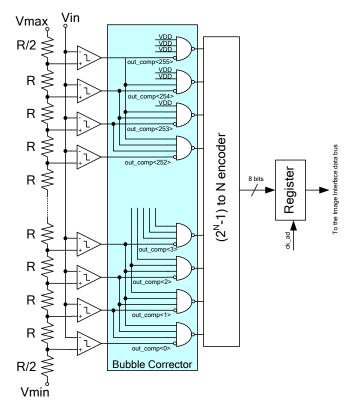

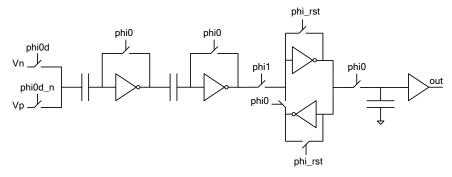

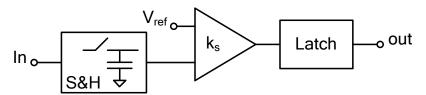

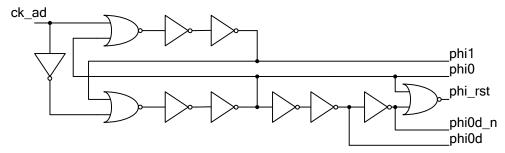

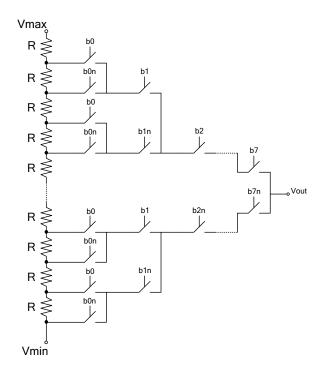

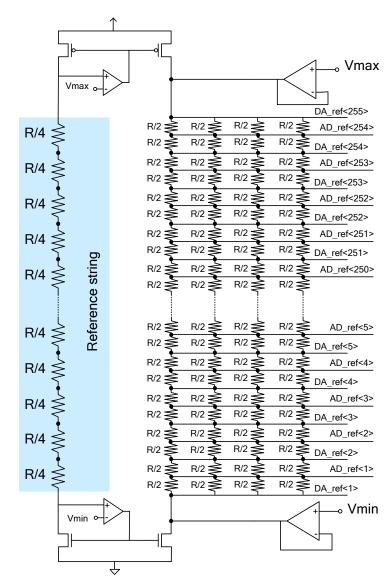

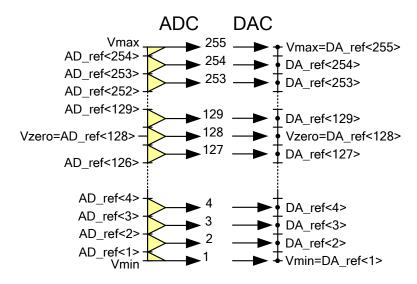

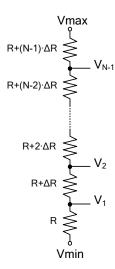

- Para la implementación física de la interface de imágenes se han diseñado bloques de señal mixta tales como:

- ✓ Convertidores AD Flash de 8 bits de resolución.

- ✓ Convertidores DA de 8 bits de resolución basados en decodificadores.

- ✓ Comparadores.

- ✓ Circuitos "Sample & Hold".

Como resultado del diseño se han descrito los aspectos más importantes a tener en cuenta para el diseño e la implementación de todos los sub-bloques y estructuras funcionales, sus no-idealidades y los efectos de las mismas sobre la calidad de imagen.

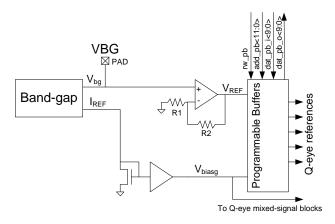

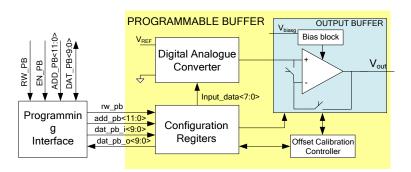

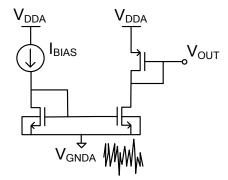

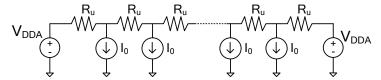

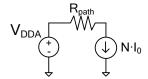

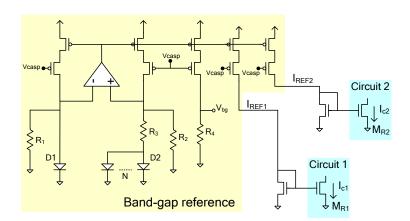

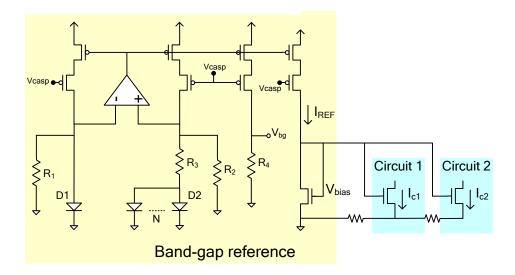

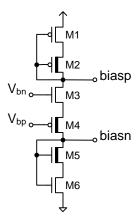

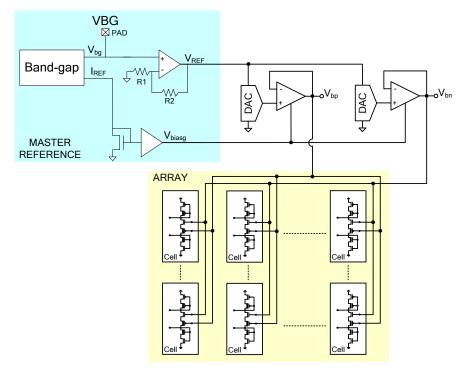

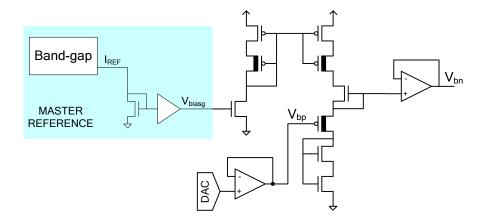

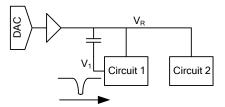

- La correcta operación de los circuitos de señal-mixta incluidos en la matriz de procesamiento e interfaz de imágenes requieren tensiones de referencias y corrientes/tensiones de polarización que han sido implementadas internamente a partir de un band-gap de alta precisión, convertidores DA y buffers. En relación con la polarización de los bloques de señal-mixta se ha desarrollado una estrategia de polarización y distribución de las referencias que garantiza un comportamiento robusto de los circuitos.

- Con el objetivo de dotar al sistema Q-Eye con funcionalidades adicionales útiles para la integración en un sistema de visión se ha incluido en el Q-Eye bloques como:

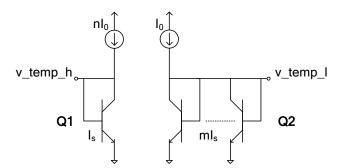

- Sensor de temperatura

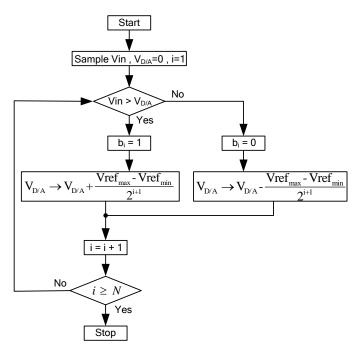

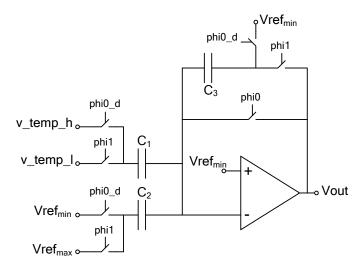

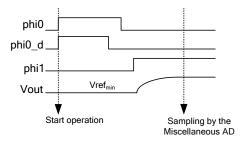

- Convertidor AD de aproximaciones sucesivas de propósito general conectado a distintos nudos internos que pueden se interesantes para un control automático del tiempo de exposición, procesos de calibración, etc.

- o "Power on Reset" para la aplicación de un "reset" inicial durante el encendido del sistema Q-Eye, garantizando un estado inicial conocido.

- o Unidad de generación de los relojes internos.

Estos bloques, junto con la generación interna de referencias, se integran en el Q-Eye ("on-chip") para reducir el número de componentes externos ("off-chip") requeridos para la operación del sensor consiguiendo el mayor nivel de compacidad posible en las cámaras y sistemas de visión que incorporen el Q-Eye.

- Se ha definido una arquitectura para un sistema de visión basado en el Q-Eye adecuada para su integración completa en un único chip, considerando la problemática que conlleva el diseño de sistemas embebidos. Esta arquitectura ha tenido en cuenta las características del sensor-procesador relativas a su configuración/programación y potencia de cálculo para realizar un co-diseño "hardware-software" óptimo. En una primera aproximación al problema se ha desarrollado el sistema de visión Eye-RIS\_v1 para verificar la arquitectura del sistema de visión propuesta. Este sistema de visión está compuesto en líneas generales por el sensor inteligente Q-Eye, un controlador que actúa de interface ente el sensor-procesador y el micro-procesador del sistema, circuitería digital de procesamiento específico, memorias de programa y datos e interfaces de comunicación. En este caso, tanto el micro-procesador como la circuitería de procesamiento específica y el controlador van implementados en una FPGA.

- Una vez verificada la arquitectura propuesta para el sistema de visión, se ha llevado a cabo el diseño e implementación física de una versión de dicho sistema en un único chip, utilizándose la misma tecnología 180nm estándar CMOS de 1.8V. Este sistema de visión "on-chip" se denomina Eye-RIS\_Vsoc. Durante la fase de desarrollo del mismo se han identificado y estudiado todos los aspectos críticos desde un punto de vista del diseño e implementación, confirmándose que son similares a los presentes en el desarrollo de cualquier sistema de visión embebido:

- Área: esta limitación implica una restricción en el número de recursos disponibles como son las memorias de programas y datos, condiciona la resolución espacial y la precisión del procesamiento, limita el número de "pads" para los interfaces de comunicación y alimentaciones, acota el número y complejidad de los procesadores, etc.

- Restricciones temporales: El sistema de visión tiene un conjunto de procesadores y controladores que deben realizar un determinado algoritmo en un tiempo determinado por la velocidad de operación requerida en la aplicación. Por ello, los

- procesadores y controladores tienen que realizar cada uno de ellos una determinada secuencia de tareas en un tiempo dado, y sincronizarse entre ellos buscando el mayor grado de paralelismo posible para optimizar la velocidad de operación.

- Consumo de potencia: Un presupuesto restrictivo del consumo de potencia implica una limitación en la precisión de los algoritmos y una limitación en la potencia de cálculo con su correspondiente penalización en la velocidad de operación. En le caso de los circuitos integrados, el consumo de potencia implica un aumento de temperatura del silicio. Para los sensores de imágenes este aumento de temperatura degrada significativamente la calidad de la imagen debido al efecto de la corriente oscura.

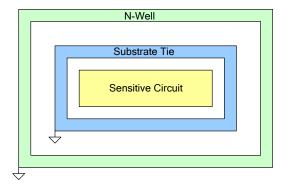

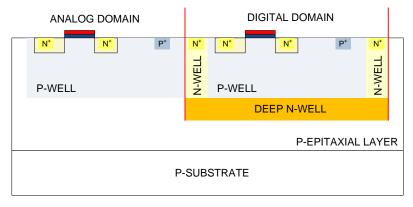

- o Integridad de las señales: En el caso de un sistema integrado en un único chip, circuitos analógicos y circuitos digitales se encuentran integrados sobre el mismo silicio. La actividad de estos últimos supone una fuente de ruido para las alimentaciones, lo cual puede suponer una limitación en la precisión alcanzada por los circuitos analógicos.

En el caso de una integración en silicio estas restricciones y condicionamientos son aún más restrictivos. Durante la fase de integración se han dado soluciones a estas limitaciones haciendo técnicamente viable el sistema de visón "on-chip" propuesto. Dicha implementación ha demostrado el nivel de integración y compacidad alcanzado con la aproximación CVIS propuesta basada en el sensor inteligente Q-Eye con procesamiento analógico masivamente paralelo en el plano sensor.

## **CHAPTER 1 - INTRODUCTION AND MOTIVATIONS**

#### 1.1. Introduction

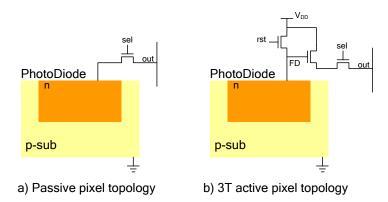

This Thesis deals with the design of chips conceived for sensing and processing images using CMOS technologies. [MAGE SENSORS] built in CMOS technology are usually referred to as CIS (from CMOS Image Sensors). CISs deliver images when irradiated by light at frequencies covering roughly the visible and the near infrared bands of the electromagnetic spectrum: [400nm <  $\lambda$  < 1000nm]. Image capture by CIS involves, among other processes, photon absorption and photon-to-charge transformation; these processes happen both at photo-sensor devices embedded into a *silicon* semiconductor substrate. Therefore this substrate becomes an *active*, photosensitive "plane" where light gets focused by optical lenses. This is the reason why this active semiconductor plane is sometimes called *focal plane*.

The focal-plane includes also non-sensitive circuits employed for different purposes. This is illustrated in Figure 1 which depicts a conceptual block diagram of a modern CIS chip conceived to deliver *digitally-encoded* images [ANAFOCUS]. When implemented in a *planar* technology all these blocks are embedded in the focal plane although only the so-called *pixel* array (part shadowed in yellow in Figure 1) must be photo-sensitive. The pixel array consists of a regular arrangement of photo-sensitive devices each capturing a spatial sample of an incoming image. The rest of chip functions are customarily located in the chip periphery and must be masked to reduce the impact of parasitic photon-induced electron-hole generation outside the photosensitive area.

Figure 1. DIGITAL CMOS IMAGE SENSOR.

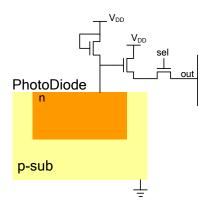

Regarding pixels themselves, they also include sensitive and non-sensitive devices and circuits. The figure at the right inset shows a conceptual footprint of a modern CIS pixel where the active, photo-sensitive area, (in yellow) amounts typically to 45% of the total pixel area. This percentage is called *fill factor*, while the term *pixel pitch* is employed to denote the length of the lateral pixel side. Some prevalent trends of CIS industry are decreasing pixel pitch and increasing fill factors. The latter one involves decreasing the amount of non-photosensitive circuits embedded at pixels. This trend is mostly observed in CISs devised for consumer applications [Font11] [ISW13] [IS14] [EImg14]. However, CISs employed for machine vision may contain significant portions of non-sensitive circuits within pixels. Chips presented in this Thesis belong to this latter category.

Actually, their pixels embed circuits intended for processing images right at the focal plane and concurrently with image capture. This is the reason why these circuits are sometimes referred to

as <u>FOCAL-PLANE SENSOR-PROCESSORS</u> [Rosk01] [Zara11]. In the more general case, non-sensitive circuit structures employed for sensor signal conditioning and processing can be incorporated at different levels [Ohta08]:

- per-pixel,

- · per-column,

- · per-chip.

Chips in this dissertation combine all these three strategies [Rodr10a, b].

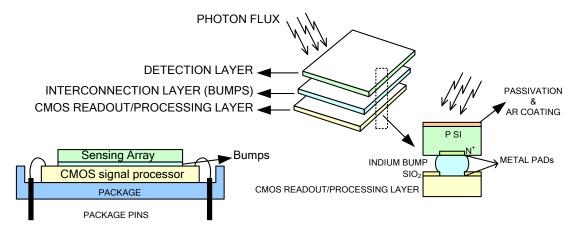

CIS chips can be illuminated either at the top (Front Side Illumination – FSI) or at the bottom (Back Side Illumination – BSI). Differences between these two cases are illustrated for a single pixel at the right figure inset. In the case of BSI, optical lenses are placed at the bottom surface of the semiconductor wafer and the light reaches directly the silicon (where photosensors are placed) without interfering with IC layers employed for interconnection and isolation. In the case of FSI, optical lenses are placed at the top surface and light must propagate throughout the top chip layers and structures before reaching the photosensitive silicon. Discussion of pros and counters of these alternatives is not a

topic of this dissertation and can be found elsewhere [Prov11]. Chips reported in in this Thesis are conceived to operate as FSIs.

Image sensors are placed at the *front-end* of <u>CAMERA SYSTEMS</u>. Figure 2 shows the block diagram of a camera system including optics, a front-end image sensor chip and a number of blocks for controlling, data storage and data communications. Image sensors cannot be used as isolated components but must be embedded into camera systems, called simply cameras for practical usage. Besides image sensors and all the functional structures required for control, communication and system integration, camera may also include circuits and systems to analyze image flows and extract

information from them. Despite how complex a camera system may be, it is clear that its ultimate image handling abilities will critically depend on the performance of the front-end image sensor because imaging quality is basically conferred by the image sensor. Although this Thesis is mostly focused on the design of image sensory-processing chips, consideration pertaining to camera design will also be made throughout the chapters. By the way of example, the figure at the left inset shows the appearance of one version of the Eye-RIS camera system described in Chapter 5 of this dissertation.

Figure 2. CAMERA SYSTEM BLOCK DIAGRAM.

We may wonder why are imagers, cameras and related technologies worth addressing? Daily life experience supports an intuitive answer to this guestion. Indeed, daily life shows that the

ability to capture, analyze and interpret optical images is likely to be crucial for systems to interact with man and the environment. Actually, *solid-state* image sensors are employed at an ever increasing number of applications. Thus, besides the extensive usage of imaging devices in cell phones and personal electronic appliances, other application sectors with large growing rate potentials are rapidly evolving such as medical, military, automotive, surveillance, robotics, machine vision, and the like.

Among other reasons, the currently witnessed proliferation of solid-state image sensors is driven by the potential of modern CIS technologies to design systems with reduced SWaP (Size, Weight and Power), low cost, large speed and large functional capabilities and flexibility. However, until approximately the mid 90's, the expansion of CMOS imaging systems was hampered by the lower quality of their compatible photo-sensing devices as compared to CCD (Charge Coupled Devices) counterparts [Naka06] [Ohta08]; i.e. images captured by earliest CMOS photo-sensors were not good enough for many industrial applications. In such a scenario CCD was the choice for imaging systems and the potential advantages of CMOS were sort of academic nuances. This drawback was attenuated with the advent of improved CMOS photo-sensors, specifically based on pinned photodiodes, and the subsequent enhancement of the quality of captured images above the feasibility thresholds required for practical applications. Once these thresholds were surpassed, and despite that CCDs may still provide larger quality at image acquisition, the CMOS advantages regarding SWaP, production cost, speed and embedded functionality became unbeatable weapons at the CMOS-CCD duel. Actually, CMOS-systems cope todays more than 90% of the market of area imager sensors, where the term area sensor is used here in contraposition to linear sensors; the former capture optical signals using a bi-dimensional detector array, while the latter employ a one-dimensional detector array as required for instance for scanning applications. Also, the total volume market for CIS is expected to grow significantly during the next few years, with an overall market forecast of around 3 billion units for 2015 and 17 billion for 2018 [Yole14a-b]. Figure 3 illustrates the share of CIS image acquisition systems shipment by applications as reported by Yole Development. This Thesis focuses on CMOS-based systems and does not attempt to analyze and quantify pros and counters of CMOS versus CCDs. Readers interested in solid-state imaging technologies with CCDs may refer among others to [Theu95].

2014 - CIS market landscape by application

Figure 3. CIS SHIPMENT FORECAST BY APPLICATIONS (YOLE DEVELOPMENT).

Major advantages of CMOS can be summarized in the following items:

- Cost

- Size.

- Power Consumption

- Speed

- Functional Flexibility

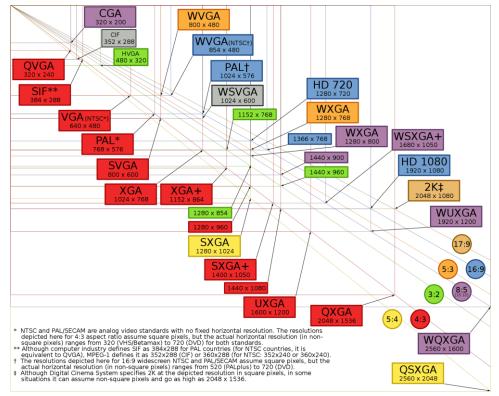

Advances in CIS are basically driven by consumer applications. These applications also condition the technical challenges pursued by industry and academia regarding CISs. On the one hand, as already mentioned, consumer markets call for ever smaller pixel pitch, and ever larger spatial image resolution (number of pixels). Besides the quest of reduced pitch, other prominent CIS challenges include:

- improving the image quality through enhanced readout, signal conditioning and image enhancement circuitry;

- improving the image downloading speed through enhanced communication circuitry and;

- reducing the area, power and cost through on-chip circuit embedding [ISW13] [EImg14] [IS14].

Recent advances include multi-million-pixel sensors with a pixel-pitch on the  $1\mu m$  range, data rates above 10Gpx/s [Taka13], advanced, reconfigurable A/D conversion and readout architectures [Leñe14] [Kawa08], image correction [Chen12], thermal and energy management, etc.

All previous challenges are focused on the acquisition of light intensity maps defining 2-D images. During the last few years we have also witnessed ever increasing activities towards adding the estimation of depth, i.e. 3-D information, to the 2-D scenes. One of the main drivers of these activities is the development of human-machine interfaces for the entertainment industry [Payb14], but the potentials of these technologies to surveillance, automotive, industrial inspection and medicine show large potentials for huge development. Besides techniques based on stereoscopy, triangulation and the like, significant efforts are being made towards modifying the CMOS pixels so that they are able to capture time information and estimate depth through Time-of-Flight (ToF) techniques. Among different approaches, Single Photon Avalanche Diodes (SPADs) are receiving significant interest [Seit11]. Despite the specific pixel technology employed (SPADs, double transfer gate, etc.), ToF measurements require complex active illumination schemes [Nicl11] — still far from the single-chip solution for 3-D imaging. Also, 3-D sensors are lacking behind mainstream CIS ones regarding the incorporation of on-chip processing circuitry.

Perhaps the most important asset of using CMOS is that it enables the design of complete imaging *systems on-chip* instead of just image sensors. An earlier realization of this possibility was the concept of *camera-system on-chip* introduced in [Foss97]. Referring to the block diagram of Figure 2, this concept involves embedding as many as possible of the functional blocks required to implement a camera within the same, common, silicon substrate. Therefore, CMOS imaging systems-on-chip belong to the general category of *smart sensors*; i.e. sensors with embedded *intelligence* [Meij01].

The concept of INTELLIGENT SENSORS is an undefined, ambiguous one. Generally speaking, the smartness feature embraces whatever kind of circuit structure employed to handle the signals acquired by sensors, despite such handling being used either for readout, for error correction, for calibration or for extracting information from the images, among others. Different levels of intelligence can be considered in practice. The "lowest" involves basically functions related to image readout, error correction and communications, and is the most exploited by industry up to now. Todays, smart CISs with embedded microprocessors that deliver fully-corrected digital images to the outside at thousand's Frames-per-Second (FpS) and with noise level below oneequivalent-electron are available [ANAFOCUS]. Higher intelligence levels, as required to extracting and interpreting the information contained into images and prompting sub-sequent reaction commands, have been explored for years at academia [Eklu96] [Rodr04] [Abbo08] [Fern11] [Lopi11], and industrial applications are recently ramping up [ANAFOCUS]. One important reason for that is the lack of standardization regarding both architectural solutions as well as output formats [Khro13]. The latter can be addressed by resorting to the usage of cellular architectures and, particularly, to the use of the Cellular Nonlinear Network (CNN) architectural paradigm as it fits to the specifics of the problem addressed, namely: large, regular array of data with properties emerging out the data collections and which can be disclosed through local interactions and signal propagation in space and in time [Rosk01] [Chua02].

Depending upon the level of intelligence embedded, two types of CMOS sensing-processing chips can be distinguish, namely:

- SCIS which stands for Smart CMOS Image Sensors, and

- CVIS which stands for CMOS VIsion Sensors.

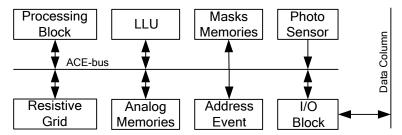

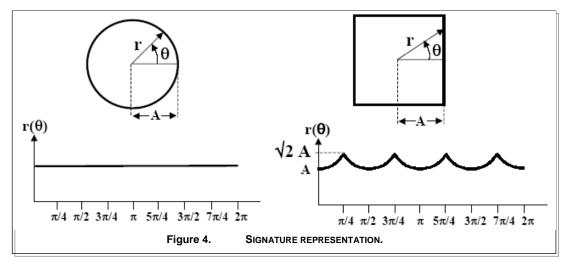

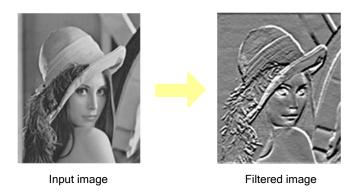

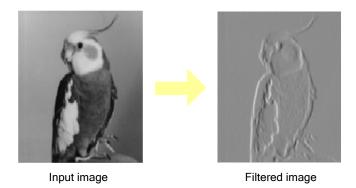

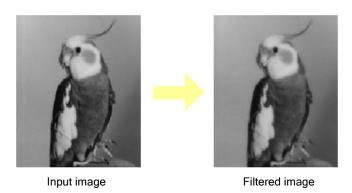

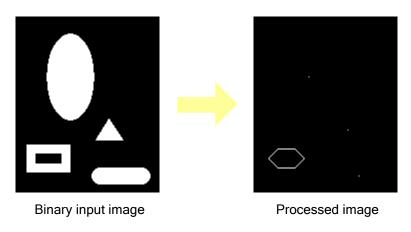

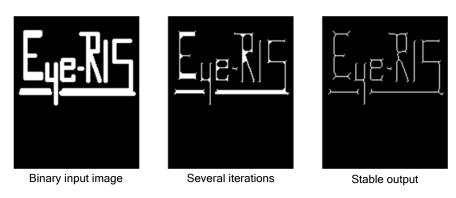

Figure 4illustrates differences between SCIS and CVIS at conceptual level. While the inputs of both chip types are images captured by photo-sensors placed in the *focal-plane* their primary outputs are of different nature.

In the case of SCIS, basic outcomes of the processing chain are just images; either grey-scale images or color images, in analog format or in digital format, *raw* or *corrected*, etc. On the contrary, the outcomes of CVIS may not be images but either image *features* <sup>4</sup> or even decisions based on the spatial-temporal analysis of the information contained into the scene. Both SCIS as well CVIS chips are conceived to be employed at the front-end of complex hardware-software camera systems. Considerations pertaining to the design of these camera systems, including topics like *smart cameras* [Belb09], are very wide and beyond the scope of this overview.

Figure 4. ILLUSTRATING DIFFERENCES BETWEEN SCIS (TOP) AND CVIS (BOTTOM).

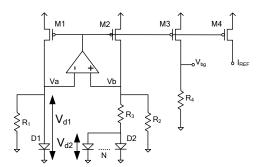

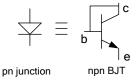

Despite their differences regarding function, SCISs and CVISs are structurally similar; specifically, both combine two different types of subsystems on a common silicon substrate:

- Those employed for sensing: i.e. for capturing light power and transducing it into either voltages or currents. They usually consist of reverse-biased *pn*-junctions (called photodiodes) together with some associated *mixed-signal* circuitry to control the sensor operation.

- Those employed for reading the outcome of the light transduction process, for signal conditioning, for <u>Analog-to-Digital Conversion</u> (ADC), for image correction and processing, for control and for communications. They consist of different analog, mixedsignal and digital circuits and subsystems.

These similarities can be exploited during the design phase as many concepts, architectures and circuits are shared by both kind of systems and can be re-used by designers. This fact is reflected throughout this dissertation.

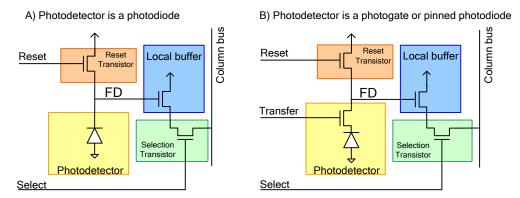

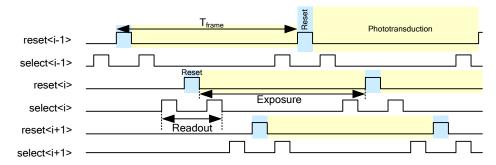

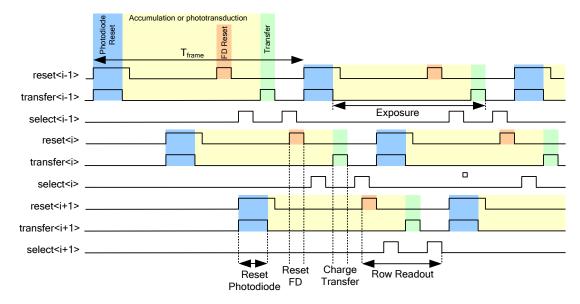

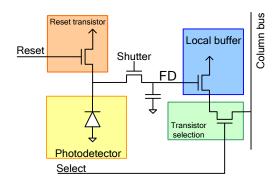

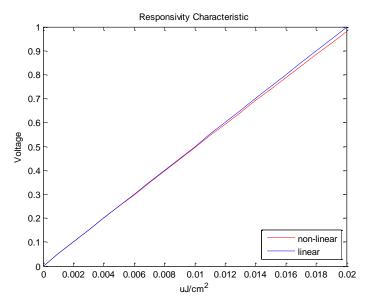

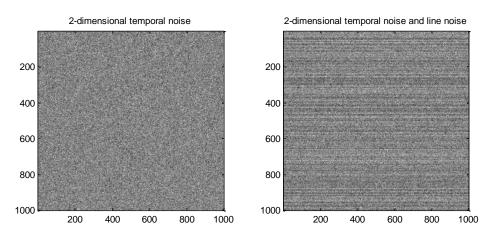

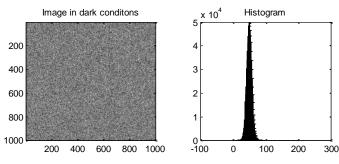

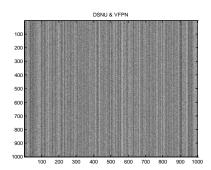

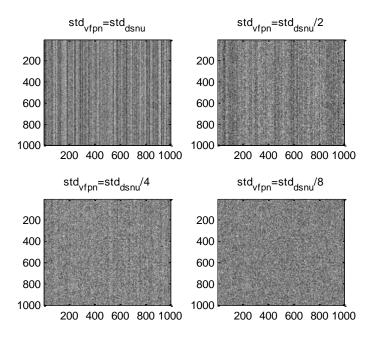

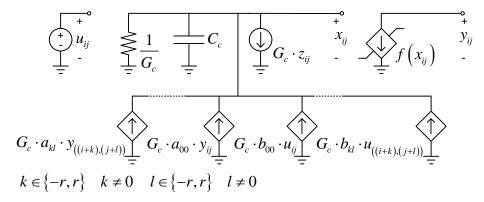

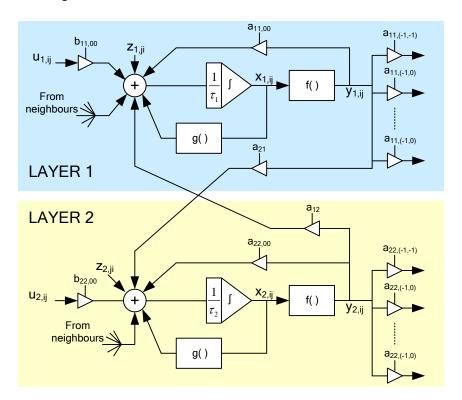

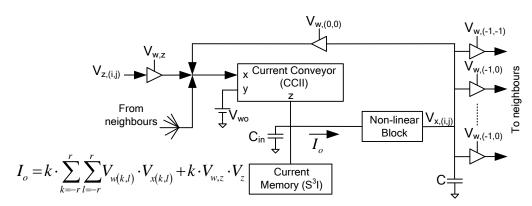

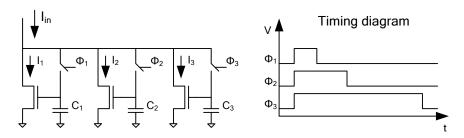

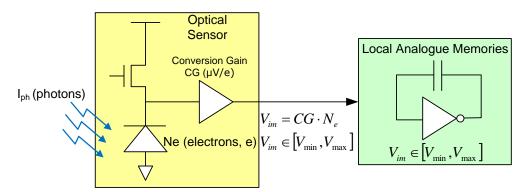

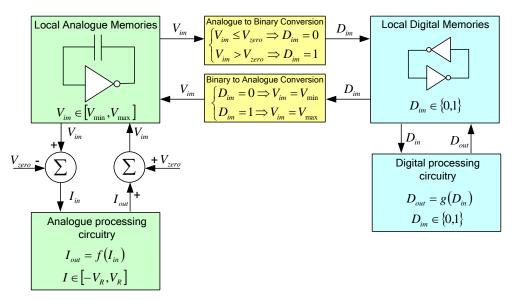

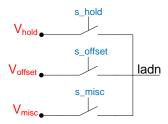

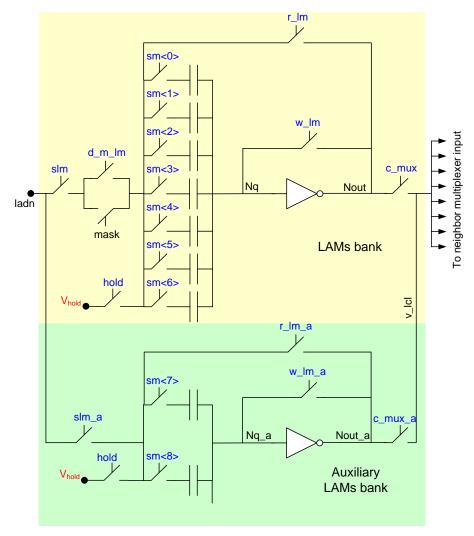

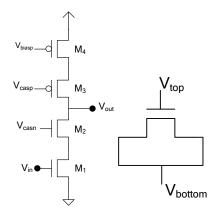

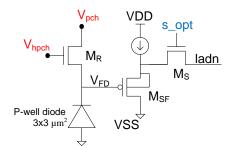

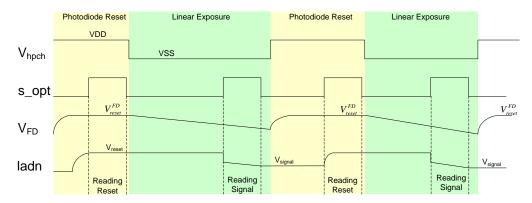

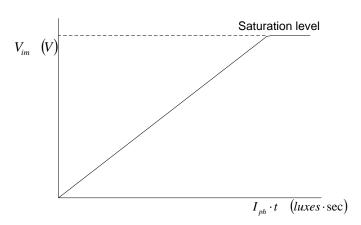

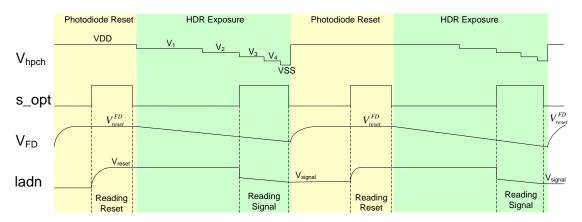

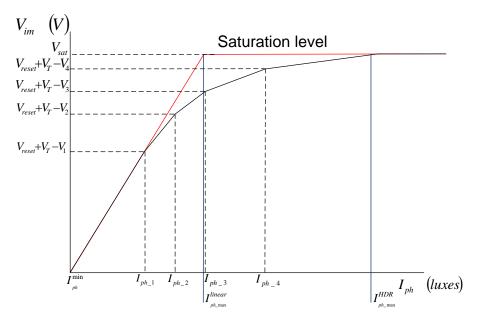

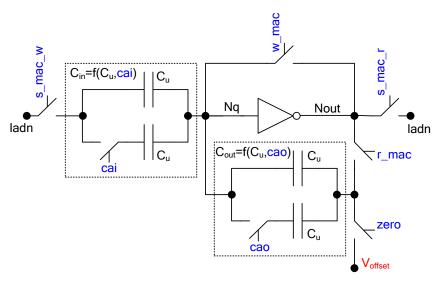

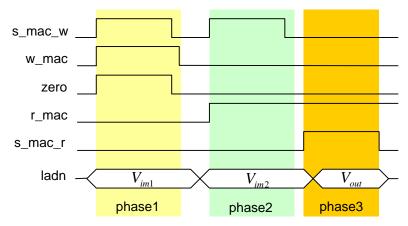

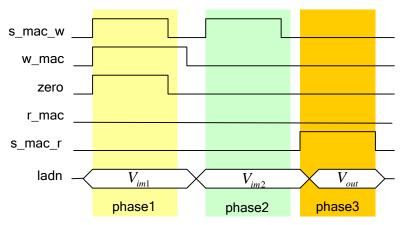

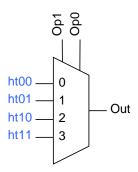

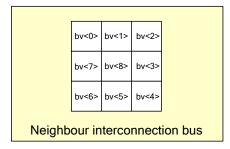

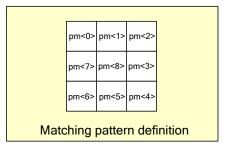

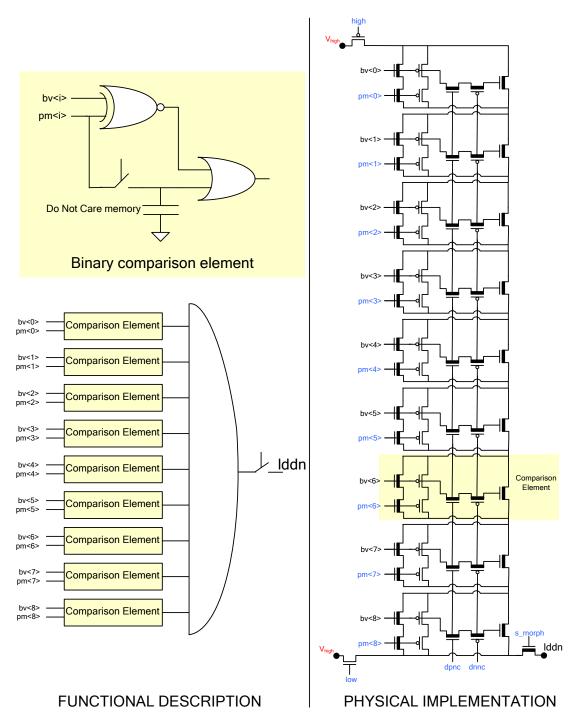

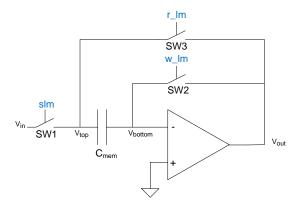

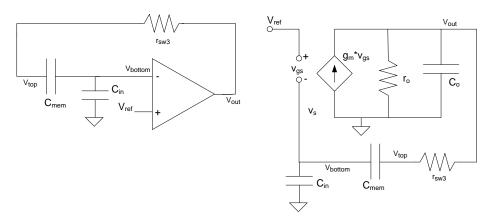

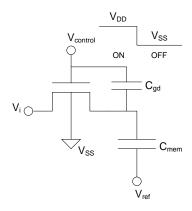

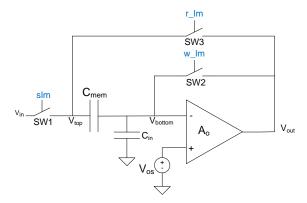

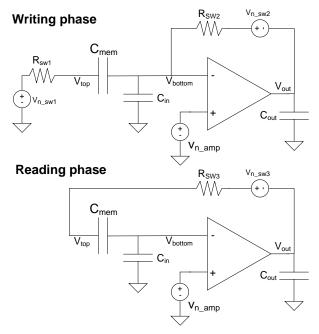

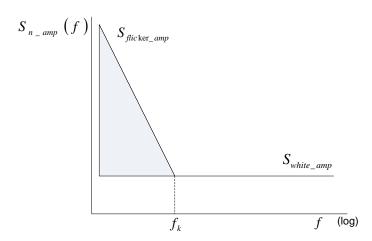

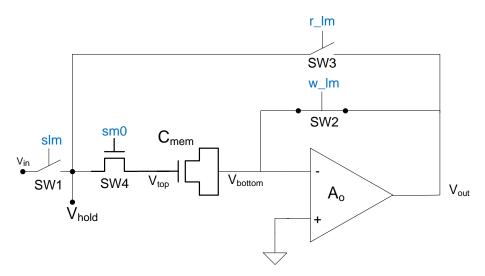

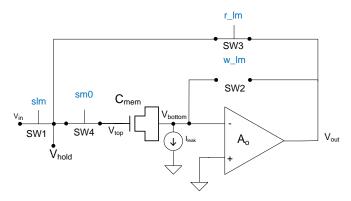

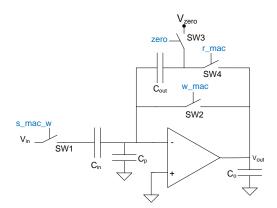

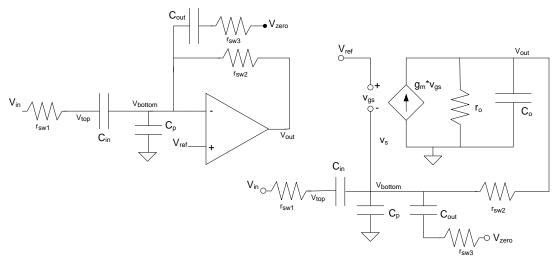

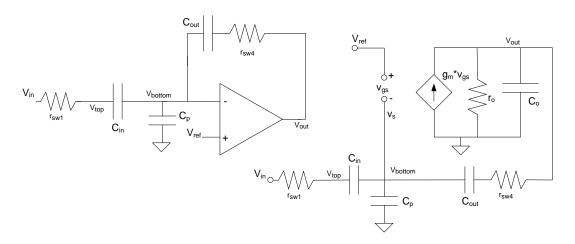

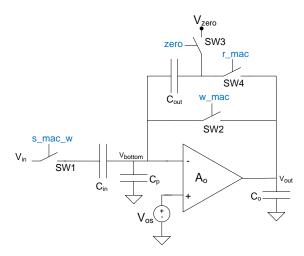

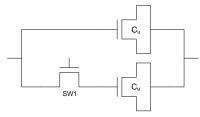

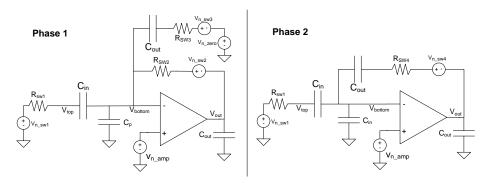

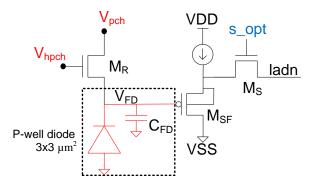

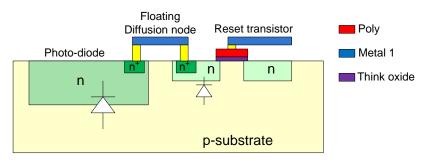

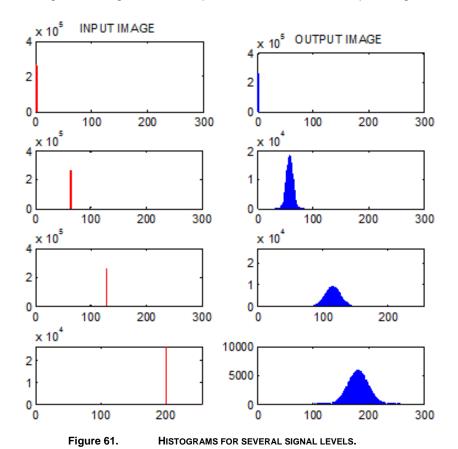

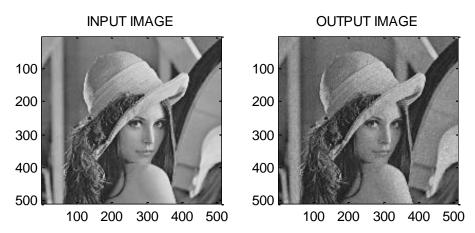

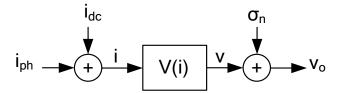

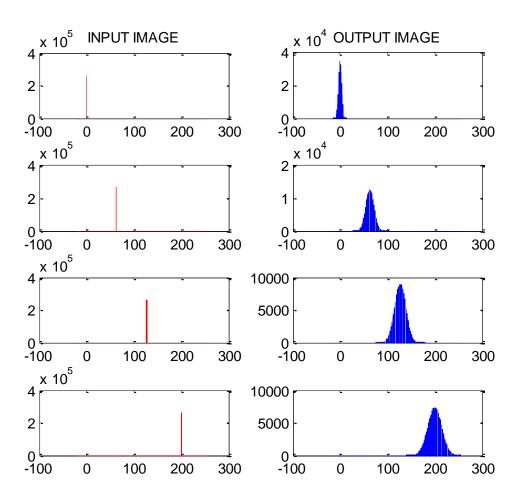

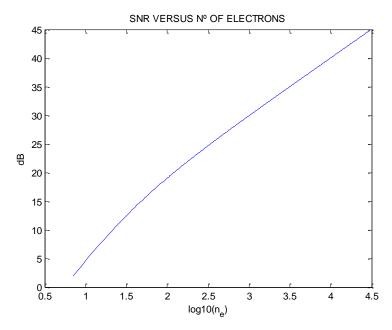

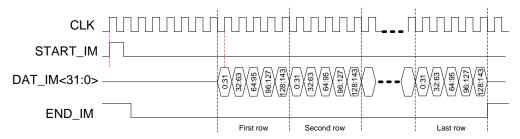

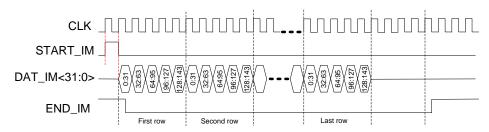

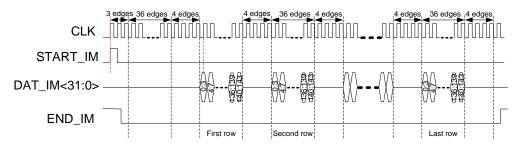

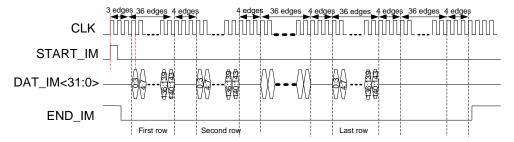

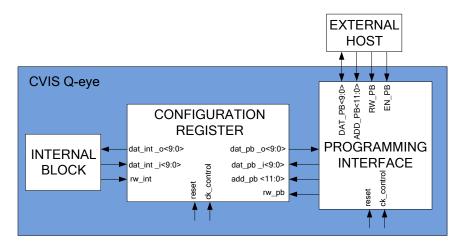

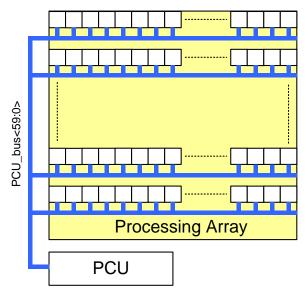

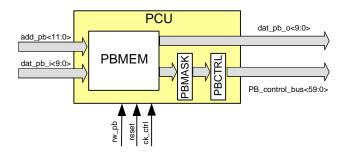

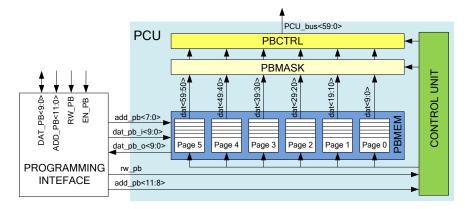

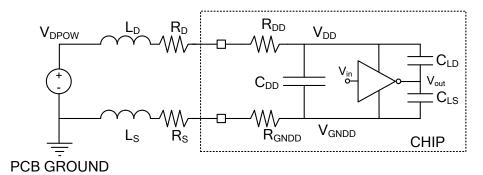

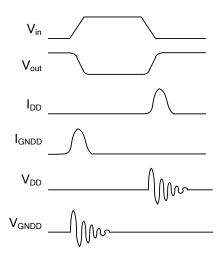

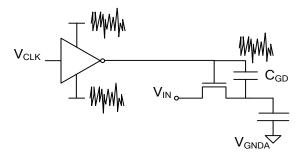

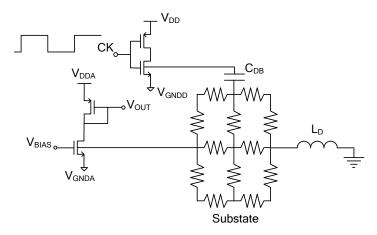

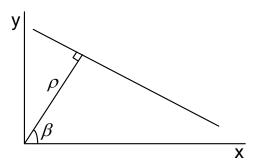

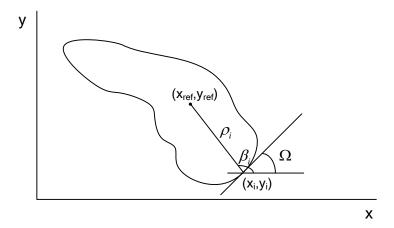

#### 1.2. OUTLINE OF THE THESIS