# A Digital Signal Processing Teaching Methodology Using Concept-Mapping Techniques

M. R. Martínez-Torres, F. J. Barrero García, *Senior Member, IEEE*, S. L. Toral Marín, *Member, IEEE*, and S. Gallardo Vázquez

Abstract—The main goal of this study is to develop a scientific method for designing a teaching methodology used in a basic digital signal processing (DSP) course. The proposed method is based on concept-mapping techniques, which applies multivariate statistic analysis to summarize the experience and knowledge of teachers involved in basic DSP teaching. As a result, a set of teaching methodologies is obtained. This result, as well as other information obtained related to the relative importance of the concepts to be covered, has been used to program the course. Moreover, different teaching tools have been developed to implement the proposed teaching methodology. Finally, the reliability of the method has been compared with similar studies to validate the proposed methodology.

*Index Terms*—Computer-based educational tools, concept mapping, digital signal processing (DSP), educational technology, electrical engineering.

#### I. Introduction

N recent years, there have been dramatic changes in engineering education, especially in electrical and computer engineering (ECE) education, both in terms of curriculum content (what is taught) and delivery of material (how it is taught) [1]–[5].

On the one hand, emphasis in the electrical engineering field has shifted significantly to the design of digital systems. A shift has been made from emphasizing continuous-time-linear time-invariant systems to discrete-time-linear time-invariant systems. Because of this emphasis on discrete-time systems, the use of digital system processing (DSP), real-time implemented using digital signal processors (DSP devices), is becoming more widespread. The higher educational institution commonly incorporates real-time DSP courses at the sophomore educational level. These courses usually present DSP fundamentals and theory—implementation of discrete-time systems, DSP device structure and programming, finite word length effects, fast Fourier transform (FFT) algorithms, finite impulse response (FIR) and infinite impulse response (IIR) design, multirate DSP, power spectrum estimation, linear prediction, and optimal filtering, etc.—along with a laboratory component that uses evaluation boards, including a DSP device.

On the other hand, technology is everywhere, but does it have a place in the classroom? Since the early days of computers, learning through computer-mediated environments

(hypermedia tools, web-based educational support, simulation environments, etc.) has dramatically increased [6]-[8]. However, there are conflicting claims about these learning environments. Some researchers state the validity, even the necessity, of these educational tools, although other authors are more sceptical about them. For instance, a tremendous increase in the use of computer simulation has been noted, sometimes even replacing hardware-based laboratory courses, causing students to miss out on the learning that can only take place in a traditional laboratory. Computer-based educational settings seem to have been implemented without any scientific criteria or, what is worse, without any real necessity. Nevertheless, the pedagogical value of computer-based educational tools has been demonstrated in particular situations. This study demonstrates that the simultaneous integration of traditional and computer-based educational techniques can substantially improve the teaching and learning process.

The need to revise the teaching methodology of engineering has often been discussed. Although many enhancement reformations have been put into practice over the years, not much attention has been paid to scientific analysis for improving the teaching process. The educational process has been evaluated and, at most, empirically improved. This paper presents the application of a scientific method, based on concept-mapping techniques, to design a teaching model of a DSP course, included in the electronic engineering curriculum at the University of Seville, Seville, Spain. The concept-mapping technique has sometimes been used for teaching evaluation [9], but it can also be used for teaching planning [10], as is proposed here. From the concept-mapping analysis, different teaching methods (clusters) have been established verifying many of the improvements that have been recently developed to reform engineering education—active or cooperative learning, technology enhancement, just-in-time learning, and curriculum integration.

This paper is organized as follows. First, the concept-mapping technique is presented in Section II. Then, in Section III, the subject, based on the study of a modern DSP device and its applications, is described, and the concept-mapping technique is used to develop the conceptual framework that guides the educational process. Afterwards, in Section IV, the teaching methodology obtained is analyzed. Finally, the conclusions are drawn.

### II. CONCEPT-MAPPING OVERVIEW

A concept map is a form of structured conceptualization that can be used by groups to develop the conceptual framework to guide an evaluation, an exercise, a plan, etc. [10], [11]. To develop the concept map, a procedure that used quantitative and qualitative features was applied. At the start, the participants generated information through brainstorming. As part of the process, the data was structured, quantified, and analyzed using statistical methods that include a multidimensional scale and clusters analysis. Concept-mapping shows the main categories of mathematically determined ideas derived from the participants' input. Each subset of ideas is represented on the map in cluster form. Those clusters that are closest to each other are said to be more directly linked. The maps represent the opinion of the participants.

The following procedure to develop the concept map is laid out in the following phases [12]:

- 1) selecting and preparing the participants;

- 2) brainstorming items (concepts) that deal with the topic matter;

- 3) structuring and rating those items;

- 4) representing those items on a concept map (using a multidimensional scale and clusters analysis);

- 5) interpreting the maps.

#### III. APPLICATION TO DSP TEACHING

The concept-mapping technique has been applied to obtain the teaching methodologies that are best suited for an undergraduate intermediate DSP subject at the University of Seville. This subject focuses on the design of advanced embedded digital systems, DSP devices, and their applications. Special attention is paid to microprocessor architecture and functionality and to practical applications related to digital signal processing algorithms.

The Texas Instruments C3X family has been selected as the DSP device architecture that can fully accomplish the objectives of the subject. The internal structure of C3X family is used to explain complex embedded systems and their utility in DSP area.

The TMS320C3X family is a 32-b floating point, general-purpose, digital signal processor generation from Texas Instruments (TI).1 The family architecture features present a central processing module that is common to all family members and has been designed to execute commonly used DSP benchmarks in minimum time for single-multiplier architecture. The internal buses and special DSP instruction set of the TMS320C3x have the speed and flexibility to execute up to 150 MFLOPS (million floating-point operations per second). It optimizes speed by implementing functions in hardware that other processors implement through software or microcode. This hardware-intensive approach provides performance previously unavailable on a single chip. This DSP can perform parallel multiplications and arithmetic logic unit (ALU) operations on integer or floating-point data in a single cycle. Each processor also possesses a general-purpose register file, a program CACHE, dedicated auxiliary register arithmetic units (ARAUs), internal dual-access memories, one direct memory access (DMA) channel supporting concurrent input-output (I/O), and a short machine-cycle time. High performance and ease of use are results of these features. General-purpose

applications are enhanced greatly by the large address space, multiprocessor interface, internally and externally generated wait states, two external interface ports, two timers, serial ports, and a multiple-interrupt structure. Moreover, this environment supports a wide variety of system applications, from host processor to dedicated coprocessor, including high-level language (implemented through its register-based architecture, large address space, powerful addressing modes, flexible instruction set, and well supported, floating-point arithmetic).

The general procedure for concept-mapping development, outlined in the following subsections, is based on the five stages that were described in Section II.

## A. Selection and Preparation of the Participants

One of the most important tasks in developing a concept map is deciding who will participate in the process. Experiments demonstrate that conceptualization is better when the process includes a wide range of expert people. A broad, heterogeneous participation helps to ensure that the different points of view will be considered, thus encouraging "constructing" the right conceptual framework.

For this study, teachers with contrasting work experiences in DSP teaching, particularly with the family TMS320C3X, have been selected. A total of 14 teachers participated, all of whom had both teaching and DSP application development experience. This number of people is within the adequate limits, between ten and 20 [10].

## B. Brainstorming

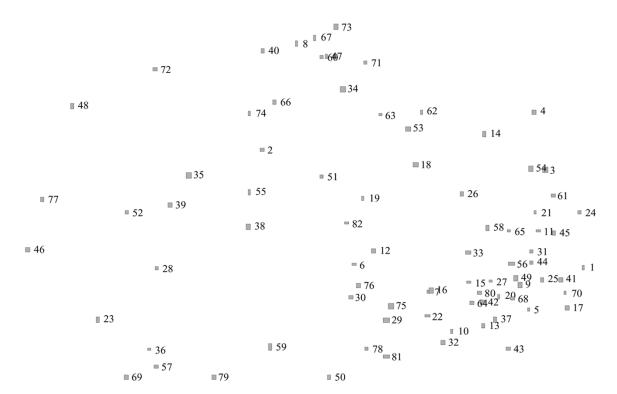

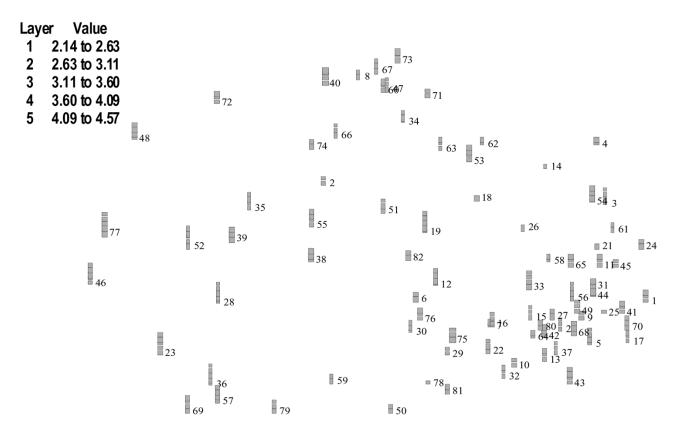

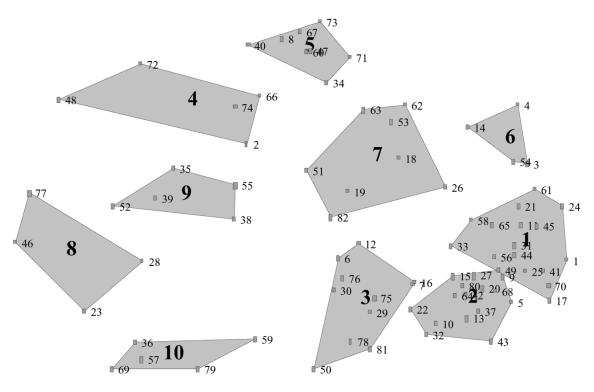

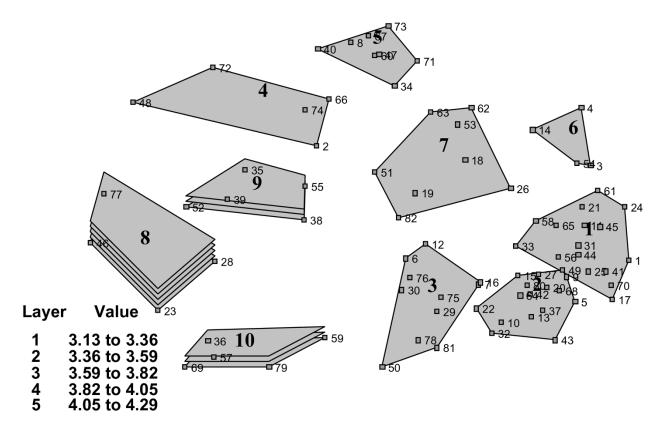

The next stage consisted of establishing a list of items related to the teaching of the proposed course. Using the brainstorming technique, the work group identified a list of 82 items, shown in Table I.

## C. Structuring and Rating the Items

When a set of items that describes the conceptual domain of the given topic is established, one must provide information about how they are interrelated and measured in relation to the topic. Both tasks make up the stage of item structuring throughout the concept-mapping development process.

The first task of the working group consisted of classifying the 82 items in several groups based on their affinity with respect to some common teaching methodology. Each of the participants applies his or her personal experience to define the number of groups and the teaching methodology. A similarity matrix, defined as  $S_{n\times n}$  with n=82, is obtained as follows: the value of the (i,j) element is equal to 1 if the ith and the jth items are grouped together and is equal to 0 otherwise. The total similarity matrix, defined as  $T_{n\times n}$ , is obtained as the addition of all the similarity matrixes.

The second task involved rating each item according to its contribution to the goals of the course. The items then had to be entered on the scoring table in Likert scale form, with a range of 1 to 5, considering that 1 = "little contribution," 5 = "a lot of contribution," and the numbers in between referred to intermediate contributions. A "zero-contribution" score was not possible, since the brainstorming stage specifically asked for those

TABLE I LIST OF IDENTIFIED ITEMS

| Seria port (CF) operation & control registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Serial port (SP) operation               | TMS320C3x architecture                                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------------------------------------|--|--|--|--|

| DSK30 overview  DSK30-PC communication  Low power modes in TMS320C3x: Solution in designing a microprocessor system: discussion Branch with delay  Timers: low frequency clock generation Stack in a microprocessor  SIM3x SP programming  Low power modes in TMS320C3x: CPU waking up Microprocessor technological evolution waking up Microprocessor technological evolution waking up Microprocessor technological evolution Micropoperations in TMS320C3x Despiration description Dispersed addressing mode Micropoperation: pipelining Micr |                                          |                                                         |  |  |  |  |

| DSK30-PC communication Harvard architecture: TMS320C3x. Solution in designing a microprocessor system: discussion Branch with delay Timers: low frequency clock generation SIM3x SP programming Parallel instructions FP programming Parallel instructions FP programming Parallel instructions FP programming FR programming FR programming Parallel instructions FR programming the DIMA FR programming |                                          | '                                                       |  |  |  |  |

| Harvard architecture: TMS320C3x. Branch with delay Stack in a microprocessor SIMOx SP programming Parallel instructions SP programming Low power modes in TMS320C3x: CPU waking up TMS320C3x family: C30, C31, C32 and VC33 Pipeline conflicts External peripheral interface Reset and interrupt vectors Boot-loader DSP device special instructions and addressing modes AIC (TLC32040) configuration MCBL versus MP modes DMA: internal structure DMA: internal registers DMA: internal registers External access timing DMA: control of the timers Diate management in TMS320C3x Pipelining methodology in DSP devices Diate matoricus and addressing mode CACHE memory in TMS320C3x Internal bus operation: pipelining AIC (TLC32040) coveriew DSP application: 2ACHE memory in TMS320C3x Data management in TMS320C3x Data management in TMS320C3x Diate methodology in DSP devices DAIC (TLC32040) overview DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x Timers: internal structure DSP device application: a digital wave generator Interpoperations Direct addressing mode Interrupt year and residency in the DSK30 Description of DSP devices-based real projects Timing diagrams in read or write operations Direct addressing mode Interrupt year and residency in the programming using DSK30 Description of a microprocessor system components DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Final cost of a digital design based on a TMS320C3x Interrupt vector table Implementing digital filtering using the DSK30 Computer architecture evolution DSK30                                                                                                                                                                                                                                                                                                                                                                           |                                          |                                                         |  |  |  |  |

| Branch with delay Stack in a microprocessor SIM3x SP programming Parallel instructions  Microprocessor technological evolution waking up  TMS320C3x family: C30, C31, C32 and VC33 Pipeline conflicts Reset and interrupt vectors BSP device special instructions and addressing modes AIC (TLC32040) configuration MCBL versus MP modes Addressing modes DMA: internal structure DMA: internal structure DMA: internal registers DSP device special instructions and addressing modes AIC (TLC32040) configuration ROBL versus MP modes Addressing modes DMA: internal structure DMA: internal structure DMA: internal registers External access using TMS320C3x Deta management in TMS320C3x Bit-reversed addressing mode Programming the timers Dasaed projects Circular indirect addressing mode AIC (TLC32040) overview Internal to soperation: pipelining DSP devices DSP devices and scape and scription DSP devices DSP devices and scape and scription of DSP devices and scription DSP devices and scape and scription of DSP devices and scription of DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x Design of digital systems based on TMS320C3x Design of digital systems based on TMS320C3x Timers: internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Direct addressing mode I |                                          |                                                         |  |  |  |  |

| Stack in a microprocessor SP programming Low power modes in TMS320C3x: CPU Waking up TMS320C3x family: C30, C31, C32 and VC33 Pipeline conflicts Reset and interrupt vectors Boot-loader DSP device special instructions and addressing modes ALC (TLC32040) configuration MCBL versus MP modes Addressing modes DSP device applications MCBL versus MP modes Addressing modes DSP device applications MCBL versus MP modes Addressing modes DSP device applications DMA: internal structure DMA: internal registers External access timing DSP device applications DSP devices imanufacturers External access using TMS320C3x Programming the timers Data management in TMS320C3x Repeat mode Programming the DMA Address space Using the DMA: An example Working methodology in DSP devices based projects DSS device special instructions DSS device applications DSP devices in TMS320C3x CPU internal bus operation: pipelining Boot-loader DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Interior diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Description of DSP devices-based real projects Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Description of microprocessor system components DSP devices in commercial world (their tillity in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Final cost of a digital design based on a TMS320C3x Interrupt vector table Implementing digital filtering using the DSK30                                                                                                                                                                                                      |                                          |                                                         |  |  |  |  |

| SP programming Low power modes in TMS320C3x: CPU waking up TMS320C3x family: C30, C31, C32 and VC33 Pipeline conflicts Reset and interrupt vectors SP device special instructions and addressing modes AIC (TLC32040) configuration MCBL versus MP modes AIC (TLC32040) configuration MICBL versus MICBL ve |                                          |                                                         |  |  |  |  |

| Low power modes in TMS320C3x: CPU Microprocessor technological evolution waking up TMS320C3x family: C30, C31, C32 and Interrupt vectors, considerations in microcomputer mode VC33 Pipeline conflicts External peripheral interface Reset and interrupt vectors Boot-loader DSP device special instructions and addressing modes AIC (TLC32040) configuration RDY signal MCBL versus MP modes External access timing Addressing modes DSP device applications DMA: internal structure Interrupts: context switching DMA: internal registers DSP devices: manufacturers External access using TMS320C3x Programming the timers Data management in TMS320C3x Repeat mode Bit-reversed addressing mode Programming the DMA Address space Using the DMA: An example CACHE memory in TMS320C3x Internal bus operation: pipelining Boot-loader using SP: an example AIC (TLC32040) overview DSP application: a digital wave generator Interlock instructions Machine cycle in TMS320C3x CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the DMSA  Reseat management in TMS320C3x Design of digital systems based on TMS320C3x CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal registers Circular addressing mode: an example CPU-peripheral interface using data, control, and addressing buses Description of a microprocessor system components Design of a digital system using a TMS320C3x and some functional specifications Using the debugger and the DSK30 Timers: internal structure Circular addressing mode: an example CPU-peripheral interface using data, control, and addressing buses Description of a digital system using a TMS320C3x and some functional specifications Instruction set Interconnecting DSP devices Final cost of a digital design based on a TMS3 | ·                                        |                                                         |  |  |  |  |

| TMS320C3x family: C30, C31, C32 and Interrupt vectors, considerations in microcomputer mode VC33  Pipeline conflicts External peripheral interface  Reset and interrupt vectors Boot-loader  DSP device special instructions and addressing modes  AIC (TLC32040) configuration RDY signal  MCBL versus MP modes External access timing  Addressing modes DSP device applications  DMA: internal structure Interrupts: context switching  DMA: internal registers DSP devices: manufacturers  External access using TMS320C3x Programming the timers  Data management in TMS320C3x Repeat mode  Bit-reversed addressing mode Programming the DMA  Address space Using the DMA: An example  Working methodology in DSP devices based projects  Circular indirect addressing mode  Internal bus operation: pipelining Boot-loader using SP: an example  AIC (TLC32040) overview DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x  CPU internal registers Integer versus floating point format  Timing diagrams in read or write operations  Direct addressing mode Interrupt generation in SIM3x  Timers: internal structure Circular addressing mode: a example  CPU-peripheral interface using data, control, and addressing based on a TMS320C3x and some functional peripheral interface using a TMS320C3x and some functional peripheral interface using a TMS320C3x and some functional peripheral using position at Timers: internal registers Pinal cost of a digital system using a TMS320C3x and some functional specifications  Das devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard Instruction set Final cost of a digital design based on a TMS320C3x Interrupt vector table Implementing digital filtering using the Computer architecture evolution DSK30                                                                                                                                                                                                                    |                                          |                                                         |  |  |  |  |

| TMS320C3x family: C30, C31, C32 and VC33 Pipeline conflicts Reset and interrupt vectors Boot-loader DSP device special instructions and addressing modes AIC (TLC32040) configuration MCBL versus MP modes Addressing modes DMA: internal structure Interrupts: context switching DMA: internal registers External access using TMS320C3x Programming the timers External access using TMS320C3x Internal space addressing mode Programming the DMA Address space Using the DMA: An example CACHE memories: general description DAM: an example CACHE memory in TMS320C3x Internal bus operation: pipelining Alc (TLC32040) overview DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x Design of digital systems based on TMS320C3x Design of digital systems based on TMS320C3x CPU internal registers Intergal registers In |                                          | Microprocessor technological evolution                  |  |  |  |  |

| Pipeline conflicts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          | Interrupt vectors, considerations in microcomputer mode |  |  |  |  |

| Pipeline conflicts   External peripheral interface   Reset and interrupt vectors   Boot-loader   Sovice special instructions and addressing modes   AIC (TLC32040) configuration   RDY signal   RDY si   |                                          | Interrupt vectors, considerations in microcomputer mode |  |  |  |  |

| Reset and interrupt vectors DSP device special instructions and addressing modes AIC (TLC32040) configuration MCBL versus MP modes AIC system and systems and addressing modes DSP device applications DMA: internal structure DMA: internal registers DSP devices: manufacturers External access using TMS320C3x Programming the timers Data management in TMS320C3x Programming the timers Data management in TMS320C3x Repeat mode Bit-reversed addressing mode Working methodology in DSP devices Cache memories: general description DAIC (TLC32040) overview Internal bus operation: pipelining Distructions DSP application: a digital wave generator Interlock instructions DSP application: a digital wave generator Interlock instructions Direct addressing mode Internal registers Integer versus floating point format Timing diagrams in read or write operations in TMS320C3x Using the debugger and the DSK30 Timers: internal registers  RDY generation DSP devices in commercial world (their underessing based on a TMS320C3x and some fulling and some programming using a TMS320C3x and some fulling and some programming and addressing buses  RDY generation DSP devices in commercial world (their underessing based on a TMS320C3x and some fulling and some programming using a TMS320C3x and some fulling in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Final cost of a digital design based on a TMS320C3x Interrupt vector table Implementing digital filtering using the Computer architecture evolution Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          | External peripheral interface                           |  |  |  |  |

| DSP device special instructions and addressing modes  AIC (TLC32040) configuration  MCBL versus MP modes  Addressing modes  DMA: internal structure  DMA: internal registers  DSP devices insurant access timing  DMA: internal registers  DSP devices insurant access timing  DMA: internal registers  DSP devices insurant access timing  DMA: internal registers  DSP devices insurant access in in internal registers  DSP devices insurant access using TMS320C3x  Programming the timers  Data management in TMS320C3x  Repeat mode  Address space  Using the DMA: An example  Acceptable DMA: An example  CACHE memory in TMS320C3x  Internal bus operation: pipelining  Boot-loader using SP: an example  AIC (TLC32040) overview  Interlock instructions  Machine cycle in TMS320C3x  Design of digital systems based on TMS320C3x  CPU internal registers  Integer versus floating point format  Timing diagrams in read or write operations in TMS320C3x  CPU internal registers  Interrupt generation in SIM3x  Micro-operations in TMS320C3x  Using the debugger and the DSK30  Timers: internal structure  Timers: internal structure  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  DSP devices in commercial world (their Using a digital passed on a TMS320C3x and some functional specifications  External access timing  Addressing based on a TMS320C3x  Interrupt vector table  Inplementing digital filtering using the Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                              |                                          |                                                         |  |  |  |  |

| addressing modes AIC (TLC32040) configuration RCBL versus MP modes Addressing modes DMA: internal structure DSP devices: manufacturers External access using TMS320C3x Programming the timers Data management in TMS320C3x Repeat mode Repeat mode Address space Using the DMA: An example Working methodology in DSP devices based projects Circular indirect addressing mode AIC (TLC32040) overview Internal bus operation: pipelining AIC (TLC32040) overview DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal structure Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Final cost of a digital design based on a TMS320C3x Interrupt vector table Implementing digital filtering using the Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                          |                                                         |  |  |  |  |

| AIC (TLC32040) configuration  MCBL versus MP modes  Addressing modes  DMA: internal structure  DMA: internal registers  External access using TMS320C3x  Data management in TMS320C3x  Bit-reversed addressing mode  Address space  Working methodology in DSP devices based projects  Circular indirect addressing mode  AIC (TLC32040) overview  Interlock instructions  Design of digital systems based on TMS320C3x  CPU internal registers  DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard  Interlock instruction sexperiments of the digital filtering using the DSA30  Design of digital filtering using the DSA30  DSP devices in computed the External access timing access |                                          | Walt State generation                                   |  |  |  |  |

| MCBL versus MP modes Addressing modes DMA: internal structure DMA: internal registers DSP device applications DSP devices: manufacturers External access using TMS320C3x Data management in TMS320C3x Programming the timers Data management in TMS320C3x Repeat mode Rit-reversed addressing mode Address space Using the DMA Address space Using the DMA: An example Working methodology in DSP devices based projects Circular indirect addressing mode Internal bus operation: pipelining AIC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal registers CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering diety in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Inplementing digital filtering using the DSK30 Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | RDY signal                                              |  |  |  |  |

| Addressing modes DMA: internal structure DMA: internal registers External access using TMS320C3x Data management in TMS320C3x Data management in TMS320C3x Bit-reversed addressing mode Address space Working methodology in DSP devices based projects Circular indirect addressing mode AIC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Internal registers Internal registers Interrupt generation in SIM3x Micro-operations in TMS320C3x Timers: internal structure CPU-peripheral interface using data, control, and addressing bSP devices in Instruction set Interconnecting DSP devices Internal registers Internal registers Interrupt generation of a digital system some functional specifications Description of a digital system based on The programming using DSK30 CPU internal registers Interrupt generation in SIM3x Direct addressing mode Interrupt generation in SIM3x Direct addressing mode: an example Direct addressing mode: an example Timers: internal registers CPU-peripheral interface using data, control, and addressing buses  RDY generation Description of a microprocessor system components Description of a microprocessor system components Description of a digital system using a TMS320C3x and some functional specifications  Instruction set Instruction set Instruction set Instruction set Instruction set Instruction set Inplementing digital filtering using the Dosk30 Computer architecture evolution                                                                                                                                                                                                                                                                     |                                          |                                                         |  |  |  |  |

| DMA: internal structure DMA: internal registers DSP devices: manufacturers External access using TMS320C3x Programming the timers Data management in TMS320C3x Repeat mode Bit-reversed addressing mode Address space Using the DMA: An example Working methodology in DSP devices Circular indirect addressing mode AlC (TLC32040) overview Internal bus operations Design of digital systems based on TMS320C3x Design of digital systems based on Description of DSP devices-based real projects Internal registers Integer versus floating point format Assembler programming using DSK30 Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal structure Circular addressing mode: an example CPU-peripheral interface using data, control, and addressing company) Von-Neumann versus Harvard Interconnecting DSP devices Interque versus VLIW Implementing digital filtering using the Computer architecture evolution DSR320C3x Interrupt vector table Implementing digital filtering using the Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -                                        |                                                         |  |  |  |  |

| External access using TMS320C3x Programming the timers  Data management in TMS320C3x Repeat mode  Bit-reversed addressing mode Programming the DMA  Address space Using the DMA: An example  Working methodology in DSP devices based projects  Circular indirect addressing mode  AlC (TLC32040) overview DSP application: a digital wave generator  Internal bus operation: pipelining Boot-loader using SP: an example  AlC (TLC32040) overview DSP application: a digital wave generator  Interlock instructions Machine cycle in TMS320C3x  CPU internal registers Integer versus floating point format  Timing diagrams in read or write operations  Direct addressing mode Interrupt generation in SIM3x  Micro-operations in TMS320C3x Using the debugger and the DSK30  Timers: internal structure Circular addressing mode: an example  Timers: internal registers  RDY generation Description of a microprocessor system components  DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard Instruction set Interrupt vector table SK30  Implementing digital filtering using the Computer architecture evolution  DSR devices: manufacture manufacture separation by Acceptance in the state of the sta |                                          |                                                         |  |  |  |  |

| External access using TMS320C3x Data management in TMS320C3x Repeat mode Bit-reversed addressing mode Address space Using the DMA: An example Working methodology in DSP devices based projects Circular indirect addressing mode Internal bus operation: pipelining AIC (TLC32040) overview DSP application: a digital wave generator Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal structure Circular addressing mode: an example Timers: internal registers CPU-peripheral interface using data, control, and addressing buses RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Interupt vector table Implementing digital filtering using the DSK30  Programming the DMA  Address general description Bot -loader using SP: an example DSP devices-based real projects  Integer versus floating point format Assembler programming using DSK30  Description of DSP devices an example Circular addressing mode: an example Circular addressing buses  RDY generation Description of a microprocessor system components Description of a digital system using a TMS320C3x and some functional specifications  Instruction set Instruction set Interconnecting DSP devices Final cost of a digital design based on a TMS320C3x  Interrupt vector table Computer architecture evolution                                                                                                                                                                                                                                       |                                          |                                                         |  |  |  |  |

| Data management in TMS320C3x Bit-reversed addressing mode Address space  Working methodology in DSP devices based projects  Circular indirect addressing mode AlC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers  Timing diagrams in read or write operations Direct addressing mode Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x  Timers: internal structure Timers: internal registers  RDS qeneration DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interpolation in TMS320C3x Lising the DMA Address manple CACHE memory in TMS320C3x Doscription of Machine cycle in TMS320C3x DSP an example DSP an example CACHE memory in TMS320C3x DSP an example DSP an example DSP application: a digital wave generator Intergot using SP: an example Description of DSP devices-based real projects  Integer versus floating point format Assembler programming using DSK30 Description in SIM3x Using the debugger and the DSK30  Timers: internal structure Circular addressing mode: an example CPU-peripheral interface using data, control, and addressing buses  RDY generation Description of a microprocessor system components Description of a digital system using a TMS320C3x and some functional specifications  Instruction set Interrupt vector table Instruction set Interrupt vector table Using the DMA  Using the DMA: An example  CPU-peripheral interface using data, control, and addressing buses  Final cost of a digital design based on a TMS320C3x  Interrupt vector table Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                          |                                          |                                                         |  |  |  |  |

| Bit-reversed addressing mode Address space Using the DMA: An example CACHE memories: general description based projects Circular indirect addressing mode Internal bus operation: pipelining AIC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Ining diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal structure Circular addressing mode: an example CPU-peripheral interface using data, control, and addressing buses RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interrupt vector table Interrupt versus floating point format Assembler programming using DSK30  Interrupt generation in SIM3x Using the debugger and the DSK30 CPU-peripheral interface using data, control, and addressing buses RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interrupt vector table Interrupt vector table CRCHE memories: general description DSP devices an example CACHE memories: general description DSP devices-based real projects Machine cycle in TMS320C3x Description of DSP devices and the DSK30  Interrupt vector table Instruction set Interrupt vector table Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                          |                                                         |  |  |  |  |

| Address space Working methodology in DSP devices based projects Circular indirect addressing mode Internal bus operation: pipelining AIC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x CPU internal registers Ining diagrams in read or write operations Direct addressing mode Direct addressing mode Direct internal registers Interns: internal registers RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Implementing digital filtering using the DSR OACHE memory in TMS320C3x CACHE memory in TMS320C3x CACHE memory in TMS320C3x Description of TMS320C3x Description: a digital wave generator InterS320C3x Description of DSP devices-based real projects TMS320C3x Description of DSP devices-based real projects Integer versus floating point format Assembler programming using DSK30 Interrupt generation in SIM3x Micro-operations in TMS320C3x Using the debugger and the DSK30 Circular addressing mode: an example Circular addressing mode: an example CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Instruction set Interrupt vector table Using the DMS An example CACHE memory in TMS320C3x Interrupt vector table Useription of a digital design based on a TMS320C3x Superscalar versus VLIW Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ů                                        | '                                                       |  |  |  |  |

| Working methodology in DSP devices based projects  Circular indirect addressing mode  Internal bus operation: pipelining  AIC (TLC32040) overview  Interlock instructions  Design of digital systems based on TMS320C3x  CPU internal registers  Integer versus floating point format  Timing diagrams in read or write operations  Direct addressing mode  Interrupt generation in SIM3x  Micro-operations in TMS320C3x  Using the debugger and the DSK30  Timers: internal structure  Circular addressing mode: an example  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard  Interconnecting DSP devices  Final cost of a digital design based on a TMS320C3x  Implementing digital filtering using the DSK30  CACHE memory in TMS320C3x  CACHE memory in TMS320C3x  Boot-loader using SP: an example  DSP devices-based real projects  Machine cycle in TMS320C3x  Description of DSP devices and projects  Interrupt vector table  Interconnecting DSP devices  Final cost of a digital design based on a TMS320C3x  Interrupt vector table  Implementing digital filtering using the DSK30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                          |                                                         |  |  |  |  |

| Circular indirect addressing mode Internal bus operation: pipelining AIC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x  CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Interrupt generation in SIM3x  Micro-operations in TMS320C3x  Timers: internal structure Circular addressing mode: an example  Timers: internal registers CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard Interconnecting DSP devices Interrupt vector table Implementing digital filtering using the DSK30  CACHE memory in TMS320C3x Dsod-loader using SP: an example  ABoot-loader using SP: an example  DSP application: a digital wave generator  Machine cycle in TMS320C3x  Description of DSP devices-in semilar using DSK30  Description of a microprocessor system components Design of a digital design based on a TMS320C3x  Instruction set Interrupt vector table Implementing digital filtering using the DSK30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          |                                                         |  |  |  |  |

| Circular indirect addressing mode Internal bus operation: pipelining Boot-loader using SP: an example AIC (TLC32040) overview Interlock instructions Design of digital systems based on TMS320C3x  CPU internal registers Integer versus floating point format Timing diagrams in read or write operations Direct addressing mode Micro-operations in TMS320C3x Using the debugger and the DSK30 Timers: internal structure Circular addressing mode: an example Timers: internal registers CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company) Von-Neumann versus Harvard Interconnecting DSP devices Interrupt vector table Implementing digital filtering using the DSK30  CACHE memory in TMS320C3x Boot-loader using SP: an example DSP anplication: a digital wave generator Machine cycle in TMS320C3x  Description of DSP devices-based real projects Integer versus floating point format Integer versus f |                                          | Green E momenes. general accomption                     |  |  |  |  |

| Internal bus operation: pipelining  AIC (TLC32040) overview  Interlock instructions  Design of digital systems based on TMS320C3x  CPU internal registers  Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Timers: internal structure  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard  Implementing digital filtering using the DSK30  DSP devices in digital filtering using the DSK30  Interrupt generation: a digital wave generator  Machine cycle in TMS320C3x  Description of DSP devices-based real projects  Integer versus floating point format  Assembler programming using DSK30  Using the debugger and the DSK30  CPU-peripheral interface using data, control, and addressing buses  RDY generation  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  design company)  Von-Neumann versus Harvard  Instruction set  Interconnecting DSP devices  Final cost of a digital design based on a TMS320C3x  Interrupt vector table  Superscalar versus VLIW  Implementing digital filtering using the Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          | CACHE memory in TMS320C3x                               |  |  |  |  |

| AIC (TLC32040) overview  Interlock instructions  Design of digital systems based on TMS320C3x  CPU internal registers  Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Interrupt generation in SIM3x  Micro-operations in TMS320C3x  Using the debugger and the DSK30  Timers: internal structure  Circular addressing mode: an example  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard  Interconnecting DSP devices  Interrupt vector table  Implementing digital filtering using the DSK30  Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                          |                                                         |  |  |  |  |

| Interlock instructions  Design of digital systems based on TMS320C3x  CPU internal registers  Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Timers: internal structure  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard  Interrupt vector table  Interrupt generation in SIM3x  Using the debugger and the DSK30  Circular addressing mode: an example  CPU-peripheral interface using data, control, and addressing buses  Boscription of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Instruction set  Interrupt vector table  Superscalar versus VLIW  Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                          | DSP application: a digital wave generator               |  |  |  |  |

| Design of digital systems based on TMS320C3x  CPU internal registers  Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Timers: internal structure  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  Description of DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard  Interrupt generation on SIM3x  Using the debugger and the DSK30  Circular addressing mode: an example  CPU-peripheral interface using data, control, and addressing buses  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Instruction set  Interrupt vector table  Instruction set  Instruction set  Interrupt vector table  Superscalar versus VLIW  Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                          | Machine cycle in TMS320C3x                              |  |  |  |  |

| TMS320C3x  CPU internal registers  Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Timers: internal structure  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  RDY generation  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Von-Neumann versus Harvard  Interconnecting DSP devices  Interrupt vector table  Interconputer architecture evolution  Integer versus floating point format  Assembler programming using DSK30  Interrupt generation in SIM3x  Using the debugger and the DSK30  Circular addressing mode: an example  CPU-peripheral interface using data, control, and addressing buses  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Timers: internal registers  CPU-peripheral interface using data, control, and addressing buses  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                          |                                                         |  |  |  |  |

| Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Timers: internal structure  Timers: internal registers  RDY generation  Description of a microprocessor system components  Description of a digital system using a TMS320C3x and some functional specifications  Timers: internal registers  RDY generation  Description of a digital design based on a TMS320C3x and some functional specifications  Instruction set  Interrupt generation in SIM3x  Using the debugger and the DSK30  Circular addressing mode: an example  CPU-peripheral interface using data, control, and addressing buses  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Instruction set  Interrupt vector table  Implementing digital filtering using the DSK30  Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                          |                                                         |  |  |  |  |

| Timing diagrams in read or write operations  Direct addressing mode  Micro-operations in TMS320C3x  Timers: internal structure  Timers: internal registers  RDY generation  Description of a microprocessor system components  Description of a digital system using a TMS320C3x and some functional specifications  Timers: internal registers  RDY generation  Description of a digital design based on a TMS320C3x and some functional specifications  Instruction set  Interrupt generation in SIM3x  Using the debugger and the DSK30  Circular addressing mode: an example  CPU-peripheral interface using data, control, and addressing buses  Description of a microprocessor system components  Design of a digital system using a TMS320C3x and some functional specifications  Instruction set  Interrupt vector table  Implementing digital filtering using the DSK30  Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | CPU internal registers                   | Integer versus floating point format                    |  |  |  |  |

| Direct addressing mode Direct addressing mode: an example CPU-peripheral interface using data, control, and addressing buses Description of a microprocessor system components Direct addressing mode: an example Direct a |                                          |                                                         |  |  |  |  |

| Direct addressing mode Micro-operations in TMS320C3x Using the debugger and the DSK30  Timers: internal structure Circular addressing mode: an example  Timers: internal registers CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard Interconnecting DSP devices Interrupt vector table Implementing digital filtering using the DSK30  Interrupt generation in SIM3x Using the debugger and the DSK30  CPU-peripheral interface using data, control, and addressing buses  Description of a microprocessor system components Design of a digital system using a TMS320C3x and some functional specifications  Instruction set Interrupt vector table Superscalar versus VLIW Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 0                                      |                                                         |  |  |  |  |

| Micro-operations in TMS320C3x Timers: internal structure Circular addressing mode: an example  CPU-peripheral interface using data, control, and addressing buses  RDY generation DSP devices in commercial world (their utility in a real electronic engineering design company)  Von-Neumann versus Harvard Interconnecting DSP devices Interrupt vector table Implementing digital filtering using the DSK30  Using the debugger and the DSK30  CPU-peripheral interface using data, control, and addressing buses Description of a microprocessor system components Design of a digital system using a TMS320C3x and some functional specifications  Instruction set Interconnecting DSP devices Final cost of a digital design based on a TMS320C3x  Superscalar versus VLIW Computer architecture evolution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                          | Interrupt generation in SIM3x                           |  |  |  |  |