# CMOS Operational Amplifiers with Continuous-time Capacitive Common Mode Feedback

Jaime Ramírez-Angulo and Ayesha Nargis Klipsch School of Electrical and Computer Engineering New Mexico State University Las Cruces, NM 88003-0001, USA jramirez@nmsu.edu, ayesha@nmsu.edu

Ramón G. Carvajal Escuela Superior de Ingenieros University of Seville 41092 Sevilla, Spain <u>carvajal@us.es</u>

Antonio López-Martín Depto. Ing. Eléctrica y Electrónica Univ. Pública de Navarra Campus Arrosadía, 31006 Pamplona, Spain <u>antonio.lopez@unavarra.es</u>

*Abstract*—A simple and power efficient approach for the implementation of continuous-time common mode feedback networks using a capacitive averaging network is introduced. It is shown that low voltage, continuous-time, fully differential rail to rail operation can be achieved using the proposed technique. This at the expense of very small additional hardware and no additional power dissipation One stage, two stage, telescopic and folded cascode op-amps are discussed as application examples.

#### I. INTRODUCTION

<sup>1</sup>Signal processing in modern analog and digital VLSI systems is performed mostly in fully differential fashion. This is due to the well know advantages of increased signal to noise ratio with signal swing scaled by a factor two and to common mode noise rejection in fully differential circuits. These two aspects are critical in fine line CMOS technology that operates from very low supply voltages approaching now  $V_{DD}$ ~1V. Operation with this low supply voltages severely limits signal swing or is not possible at all with most conventional circuits that have been in use for many years.

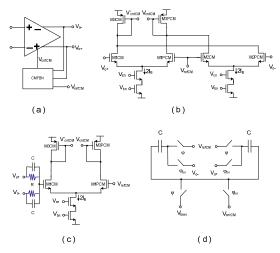

Fully differential operational amplifiers (Fig. 1a) require a common mode feedback network (CMFBN) to set the common mode output voltage to a reference value  $V_{refCM}$ . (Fig. 1a). Traditionally they have been based on continuous time CMFBNs (Fig. 1b and 1c) [1]-[6] or on discrete time switched capacitor CMFBNs (Fig. 1d) [6]-[7]. The later have a very simple architecture and use switched capacitor averaging networks to sense the output common mode voltage. Their main advantage is that they do not load resistively the output nodes. They can be used in one stage op-amps where the open loop gain is strongly dependent on

the load resistance at the output nodes, Their main disadvantage is the inherent speed limitation of sample data systems where signal frequencies must be kept typically a factor a 10-50 below the switching frequency that usually corresponds to the gain bandwidth product (GB) of the opamp. Switched capacitor CMFBNs are also subject to clock feed through and charge injection errors. Continuous-time CMFBNs can operate at much higher speeds (close to the GB of the op-amp) but they require a relatively large headroom  $HR^{MIN} = V_{GS} + V_{Dssat}$  (a transistor's gate-source voltage plus a drain-source saturation voltage) which severely limits the output swing. This headroom is required in order to keep the input circuitry in the CMFBN functional (usually a differential pair as in Figs. 1b and 1c or transistors operating in triode mode [1] are used as active devices to sense common mode output voltage variations). One example is the differential difference amplifier shown in Fig. 1b used commonly as CMFBN [3]-[4]. This circuit finds frequently application in one stage op-amps due to the fact that it does not load resistively the output nodes. The simpler continuous time CMFBN of Fig. 1c [2] can operate with larger output signal swing but requires a minimum headroom HR<sup>MIN</sup> =  $V_{\text{GS}} {+} V_{\text{DSsat}}$  . This circuit has also the disadvantage that it loads resistively the op-amp's output nodes. For this reason this circuit can be used only in two stage (Miller) or multistage fully differential op-amps and requires relatively large resistors R to prevent open loop gain degradation. Another disadvantage of continuous time CMFBNs (like those of Figs. 1b and 1c) is that they usually add significant power dissipation and Silicon area since the CMFBN must have a gain bandwidth product (GB<sub>CM</sub>) comparable to the gain bandwidth product (GB) of the main op-amp [6]. This requires bias currents and transistor sizes in the CMFN which are similar to those used in the main op-amp

In this paper we introduce a very compact continuous-time capacitive common mode feedback network. The proposed

<sup>&</sup>lt;sup>1</sup> This work has been partially supported by MICINN (RYC-2008-03185) and DGA (PI113/2009).

circuit can be considered the CT counterpart of the discrete time capacitive CMFBN of Fig. 1d. It can operate at similar speed as the main op-amp without clock feed-through or charge injection problems. It does not load resistively the opamp output nodes and only adds a very small capacitive load. It does not have headroom requirements, so that rail to rail op-amp output swing is possible. It is inherently stable since it is compensated with the op-amp load capacitance and for this reason it does not require additional compensation elements. Its implementation requires very small additional hardware (three small capacitors) and no extra power dissipation. Section II describes the proposed approach. Section III shows its application to some common op-amp architectures and discusses simulations that validate the approach. Section IV provides conclusions

#### II. CAPACITIVE COMMON MODE FEEDABCK

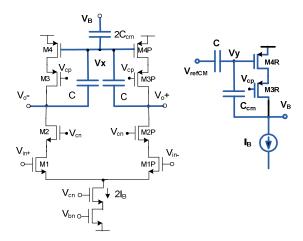

Fig. 2 shows a telescopic fully differential op-amp used to illustrate the proposed continuous-time capacitive common mode feedback network. The elements of the CMFBN are highlighted and include three capacitors: two of these have equal values C and are connected to the op-amp output nodes. The third capacitor has a value  $2C_{CM}$  and is connected to node  $V_B$ . The voltage at this node is constant. All capacitors are connected to a common node  $V_x$ . at the gates of M4 and M4P. The circuit also includes a DC replica bias circuit formed by transistors M4R and M3R. This is used to generate the DC voltage  $V_B$ . Based on charge conservation and assuming, zero net charge on  $V_x$  and  $V_y$  (a condition easily achievable using the layout technique described in [8]) the voltage  $V_x$  at the common gate of M4, M4P is given by:

$$V_{x} = [(V_{o+} + V_{o-})C + V_{b}2C_{CM}]/2(C + C_{CM} + C_{gs4})$$

(1)

where  $C_{gs4}$  is the gate-source capacitance of M4, M4P.

The voltage  $V_v$  in the replica bias circuit is given by

$$V_{v} = (V_{b}C_{CM} + V_{refCM}C)/(C_{CM} + C + C_{gs4})$$

(2)

Given that transistor M4R has the same current  $I_B$  as transistor M4 then assuming both transistors operate in saturation  $V_{GS4}{=}V_{GS4R}$ . This leads to

$$V_x = V_y \tag{3}$$

From (1) - (3) we arrive to

$$V_{refCM} = (V_{o^+} + V_{o^-})/2....$$

(4)

From (4) it can be seen that the output common mode voltage takes the value  $V_{\text{refCM}}$

### Remarks:

1) The actual CMFBN of the op-amp *consist only* of capacitors C and  $C_{CM}$  connected to  $V_x$ . and does not require additional power dissipation. The replica bias circuit and its associated power dissipation is not considered integral part of the common mode feedback network since it is used only to generate the DC voltage  $V_B$ . and can serve several (or all) op-amps in a chip. In the last case it can be buffered.

2) The CT capacitive CMFBN can operate on rail to rail output signals

3) The open loop gains of the differential and common mode feedback loops have similar values and are given by:

$$A_{ol} = g_{m1} R_{out}; \qquad A_{olCM} = a g_{m4} R_{out}$$

(5)

where "a" is an attenuation factor is given by:

$$a = C/(C + C_{CM} + C_{GS4}) \tag{6}$$

and the output resistance at  $V_{0+}$ ,  $V_{0-}$  is given by

$$R_{out} = (r_{o1}g_{m2}r_{o2}) || (r_{o3}g_{m4}r_{o4})$$

(7)

where  $g_{m1}, g_{m2}, g_{m3}, g_{m4}, r_{o1}, r_{o2}, r_{o3}$  and  $r_{o4}$  are the transconductance gains and output resistances of M1-M4 respectively. The dominant poles of the open loop gain of the differential and common mode feedback loops are given by

$$f_{pDOM} = 1/(2\pi R_{out}C_L)$$

(8)

where  $C_L$  is the load capacitance at  $V_{o+}$ ,  $V_{o-}$ . The gain bandwidth product (GB)for differential and common mode networks is given by

$$GB=g_{m1}/(2\pi C_L);$$

$GB_{CM}=ag_{m4}/(2\pi C_L)$  (9)

It can be seen that, as it is commonly required in fully differential op-amps, GB and  $GB_{CM}$  can have similar values. In practice attenuation values a~0.5 can be used. In this case the selection  $g_{m4}=2g_{m1}$  satisfies the condition  $GB=GB_{CM}$ . Capacitors C increase the effective capacitive output load and can cause GB (or phase margin) degradation. In practice they can have very small values C<<C<sub>L</sub>. In order to prevent a large attenuation factor "a" with the associated reduction in GB<sub>CM</sub> capacitors C and C<sub>CM</sub> can be a factor 5 to 10 larger than C<sub>GS4</sub>. Values C=C<sub>CM</sub>=1.5pF were used in all examples. They increased the silicon area of the op-amp by less than 20%.

Fig. 1 (a) Generic scheme of fully differential op-amp with common mode feedback network (CMFN) (b) Continuous-time CMFN with high input impedance (c) Continuous-time CMFBN with resistor averaging network (d) Discrete time switched capacitor implementation of CMFBN.

Fig. 2 Fully differential CMOS telescopic op-amp using continuous-time capacitive common mode feedback network

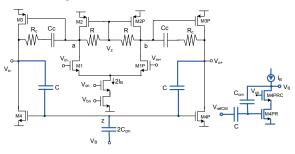

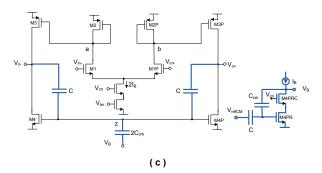

Fig. 3 Fully differential CMOS Operational amplifiers using continuous time capacitive common mode feedback networks (highlighted) (a)Two stage (Miller) op-amp with resistive local common mode feedback in first stage (b)Folded cascade op-amp (c)One stage (current mirror) op-amp

A continuous time capacitive Local CMFBN was reported in [9] that uses charge injection devices. These require generation of high voltages on chip. Additionally the circuit lacks a replica bias circuit and with this the possibility to set the common mode output voltage to a value  $V_{refCM}$ .

## III. APPLICATION EXAMPLES

Fig. 3a, 3b and 3c shows examples of a Miller op-amp, folded cascade and one stage (current mirror) op-amps with continuous time capacitive CMFBNs. The GB<sub>CM</sub> analysis and comments of previous section also apply to these circuits. The two stage op-amp of Fig. 3a uses conventional Miller compensation and resistive local common mode feedback (LCMFB) [10] with resistors R connected between nodes "a" ("b") to node V<sub>z</sub> of the input stage. In this case the gain of the first and second stages stage is given by  $A_I=g_{m1}(R||r_{o1}||r_{o2})$   $A_{II}=g_{m3}r_{o3}||r_{o4}$ . Given that under quiescent conditions no current flows in the LCMFB resistors R, then voltages  $V_z=V_a=V_b$  and  $V_{SGQ3}=V_{SG2Q}$  Therefore, the DC current in the output stage is well controlled since it mirrors the DC current in the input stage. The GB of this op-amp is given in this case by the conventional expression GB= $g_{m1}/(2\pi C_c)$ .

The circuits in Fig. 2 and Fig. 3 have been implemented in 0.5 $\mu$ m CMOS (MOSIS) technology. Post-layout simulations with Spectre–BSIM3v3.2 level 53 transistor models were performed using supply voltages V<sub>DD</sub>=0.6V, V<sub>SS</sub>=-0.9V I<sub>B</sub>=50uA, (W/L)<sub>NMOS</sub>=50/1, (W/L)<sub>PMOS</sub>=120/1, V<sub>inCM</sub>=0V, C<sub>L</sub>=10pF C<sub>C</sub>=10pF, Rc=2.5k $\Omega$ , C=C<sub>CM</sub>=1.5pF, V<sub>refCM</sub>=0V, C<sub>I</sub>=3pF, C<sub>F</sub>=0.6pF, C<sub>B</sub>=1pF, R=40k.

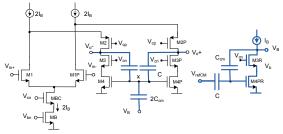

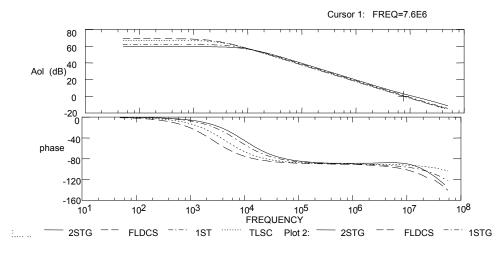

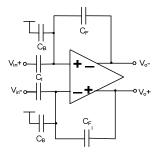

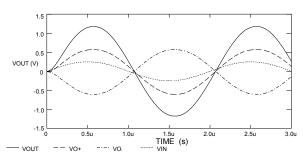

Fig. 4 shows the magnitude and phase response of the open loop gain of the op-amps of Figs. 2 and 3 and Table I summarizes some of their performance characteristics. Fig. 6 shows the scheme used to implement a low voltage amplifier with gain  $G=C_I/C_F$  This uses op-amps with floating gate transistors in the input differential stage. Capacitors C<sub>I</sub>,C<sub>F</sub> are used to set the gain and capacitors CB is used, according to the technique reported in [12], to shift the DC voltage of the op-amp input terminals to a higher value  $V_{i+}=V_{i-}$  $=V_{DD}C_B/(C_1+C_B+C_F)$ . This increases the HR for the input differential stage and allows operation with very low supply voltages. Fig. 6 shows the transient responses  $(V_{0+}, V_{0-}, V_{0})$ V<sub>in</sub>) of the two stage amplifier of Fig. 3a using the scheme of Fig. 5. The amplifier has a nominal gain G=5. It uses capacitors  $C_{I}=3pF$ ,  $C_{F}=0.6pF$ ,  $C_{B}=1pF$ . The input was a 500kHz 0.25Vp sinusoidal signal.

Table I. Simulated characteristics of op-amps of Figs 2 and 3

| Op-amp             | GB(MHz) | Aol(dB) | Phase<br>Margin<br>(deg) |

|--------------------|---------|---------|--------------------------|

| 2-stage            | 11.4    | 59.5    | 89                       |

| 1-stage            | 8.7     | 62.15   | 84                       |

| Folded-<br>Cascode | 7.6     | 69.1    | 81.4                     |

| Telescopic         | 8.7     | 67.15   | 87.7                     |

Fig. 4 Open loop and phase response of op-amps of Figs. 2 and 3

Fig. 5 Implementation of low voltage amplifier with gain G=-C<sub>I</sub>/C<sub>F</sub>

Fig. 6 Output waveforms  $V_{o^+}$ ,  $V_{o^-}$ ,  $V_{in}$  and  $V_o$  for low voltage amplifier with gain 5 according to Fig. 5 .

### IV. CONCLUSIONS

A continuous-time common mode feedback network using capacitors was introduced. It is very compact and allows rail to rail output signal swing. It does not load resistively the output terminals of the op-amp and increases only slightly the output capacitive load. It requires minimal hardware and no additional power dissipation. Its application in one, two stage, folded cascode and telescopic op-amps was discussed. The proposed circuits can operate with very low supply voltages as required in modern fine line technology. All op-amps were validated with simulations in 0.5µm CMOS technology.

#### REFERENCES

- T.C. Choi, R.T. Kaneshiro, R.W. Broderson, P.R. Gray. "High Frequency CMOS Switched Capacitor Filters for Communications Application," *IEEE Journal of Solid State Circuits*, vol. 18, No. 6, pages. 652-664, 1983

- [2] M. Banu, J.M. Khoury, and Y. Tsividis, "Fully Differential Operational Amplifers with Accurate Ouput Balancing," *IEEE Journal of Solid State Circuits*, vol. 23, No. 6, pages. 1410-1414, 1988.

- [3] P.W. Li, M.J. Chin, P.R. Gray and R. Castelo, "A Ratio Indpendent Alogrithmic Analog-Digital Conversion Technique," *IEEE Journal of Solid State Circuits*, Vol. 19, No. 6, pages 828-836, 1984

- [4] R.A. Whatley, "Fully Differential Operational Amplifer with DC Common Mode Feedback," U.S. Patent 4,573,020, 1986.

- [5] D. Hernandez-Garduno and J. Silva-Martinez, Continuous-time common-mode feedback for high-speed switched-capacitor networks *IEEE Journal of Solid State Circuits*, Vol. 40, No. 8, pages 1610-1617, 2005.

- [6] P.Gray, P.J. Hurst, S.H. Lewis, R.G. Meyer, Analysis and Design of Analog Integrated Circuits, Wiley, New York, 2009, section 12.5.

- [7] D. Senderowicz, S.F. Dreyer, J. H. Higgins, C.F. Rahim, and C.A. Laber, "A Family of Differential NMOS Analog Circuits for a PCM Codec Filter Chip," *IEEE Journal of Solid State Circuits*, vol. 17, No. 6, pages 1014-1023, 1982

- [8] E. Rodriguez-Villegas, and H. Barnes, "Solution to Trapped Charge in FGMOS Transistors," *Electronics Letters*, Vol. 39, No. 19, pages 1416-1417, 2003.

- [9] R. Chawla, F. Adil, G. Serrano and P.E. Hasler, Programmable Gm-C Filters Using Floating Gate Operational Transconductance Amplifers. *IEEE Transactions on Circuits and Systems I*, vol. 54, No. 3, pages 481-491, 2007.

- [10] J. Ramirez-Angulo and M. Holmes, "Simple technique using Local CMFB to enhance Slew Rate and bandwidth of one-Stage CMOS opamps," *Electronics Letters*, vol. 38, No 23, pages 1409-1411, 2002,

- [11] J. Ramirez-Angulo, R. G. Carvajal, J. Tombs, and A. Torralba, "Low-voltage CMOS Op-amp with rail-to-rail signal swing forcontinuous-time signal processing using multiple-input floating-gate transistors," *IEEE Transactions on Circuits and Systems II*, vol. 48, No. 1, pages. 110-116, 2001.