### Virginia Commonwealth University VCU Scholars Compass

Theses and Dissertations

**Graduate School**

2012

# Brain Controlled Switch

Dimple Bhuta Virginia Commonwealth University

Follow this and additional works at: http://scholarscompass.vcu.edu/etd Part of the <u>Biomedical Engineering and Bioengineering Commons</u>

© The Author

Downloaded from http://scholarscompass.vcu.edu/etd/2795

This Thesis is brought to you for free and open access by the Graduate School at VCU Scholars Compass. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

© Dimple Bhuta, 2012

All Rights Reserved

### **BRAIN CONTROLLED SWITCH**

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science at Virginia Commonwealth University.

by

DIMPLE BHUTA Bachelor of Engineering (Electronics), Mumbai University, India, 2009

#### Director: DING-YU FEI, PH.D. ASSOCIATE PROFESSOR, DEPARTMENT OF BIOMEDICAL ENGINEERING

Virginia Commonwealth University Richmond, Virginia August, 2009

#### ACKNOWLEDGEMENTS

I am extremely grateful to my advisor Dr. Ding-Yu Fei and my co-advisor Dr. Ou Bai for giving me an opportunity to work on this project. This thesis wouldn't have been possible without their continuous guidance, motivation and support at every step of my research. Throughout my project they have encouraged me to develop independent thinking and research skills. I would also like to thank my thesis committee member Dr. Azhar Rafiq. Thank you for your insightful comments and all your help in the completion of my project. I would like to thank Ms. Cai-Ting Fu for her knowledge and suggestions during my research.

I would really like to thank my lab mates and friends Deepak Kumbhare, Vaishnavi Karnad, Dandan Huang and Sayak Bhattacharya for making my graduate study such an enjoyable experience.

Last but not the least, I am really grateful to my parents Dr. Leena and Dr. Chitranjan Bhuta who always believed in me, supported me unconditionally and showed me that there is a great joy in the intellectual pursuit.

#### Table of Contents

| Acknowledgementsiii            |

|--------------------------------|

| List of Abbreviations vi       |

| List of Tables viii            |

| List of Figuresix              |

| Abstractxi                     |

| CHAPTER 1 Introduction1        |

| 1.1 Background1                |

| 1.2 Objective of this study4   |

| CHAPTER 2 Methods              |

| 2.1 Hardware Section           |

| 2.1.1 Protection Circuit11     |

| 2.1.2 Preamplifier12           |

| 2.1.3 Main amplifier13         |

| 2.1.4 Total Gain17             |

| 2.1.5 Driven-Right Leg Circuit |

| 2.1.6 Electrical Isolation18   |

| 2.2 Digital Section19          |

| 2.2.1 Interrupts and Timer     |

| 2.2.2 UART                     |

| 2.2.3 ADC                      |

| 2.2.4 Digital Filters60        |

| 2.2.5 Power Calculations                                                   | 64  |

|----------------------------------------------------------------------------|-----|

| 2.2.6 Experimental Paradigm                                                | 65  |

| 2.2.6.1 Beta Rebound based method                                          | 65  |

| 2.2.6.2 SSVEP based method                                                 | 67  |

| 2.2.7 Algorithms for design of SSVEP and ERD based Methods                 | 69  |

| CHAPTER 3 Results                                                          | 71  |

| 3.1 BCS device Signal Recording Module Evaluation                          | 71  |

| 3.2 BCS device Feature extraction Module Evaluation                        | 73  |

| 3.3 BCS performance Evaluation                                             | 75  |

| 3.3.1 Beta Rebound based method                                            | 75  |

| 3.3.2 SSVEP based method                                                   | 78  |

| CHAPTER 4 Discussions and Future Work                                      | 82  |

| 4.1 Discussion                                                             |     |

| 4.2 Future Work                                                            | 84  |

| Literature Cited                                                           | 87  |

| APPENDIX A: Analog section                                                 | 93  |

| APPENDIX B: Digital section                                                | 94  |

| APPENDIX C: Power supply section                                           | 95  |

| APPENDIX D: Basics of a computer system                                    | 96  |

| APPENDIX E: dsPIC30F4013                                                   | 100 |

| APPENDIX F: UART packets interfacing with hyperterminal, Matlab and BCI2VR |     |

| VITA                                                                       | 105 |

### LIST OF ABBREVIATIONS

| BCS   | Brain Controlled Switch device              |

|-------|---------------------------------------------|

| BCI   | Brain Computer Interface                    |

| EEG   | Electroencephalography                      |

| SSVEP | Steady-state visual evoked potentials       |

| ALS   | Amyotrophic lateral sclerosis               |

| FPR   | False positive rate                         |

| TPR   | True positive rate                          |

| ERS   | Event-related synchronization               |

| ERD   | Event-related desynchronization             |

| EMI   | Electromagnetic interference                |

| RF    | Radio frequency interference                |

| EMG   | Electromyography                            |

| ECG   | Electrocardiography                         |

| IA    | Instrumentation Amplifier                   |

| UART  | Universal Asynchronous receiver transmitter |

| ADC   | Analog to Digital Converter                 |

| LED   | Light Emitting Diode                        |

| ISR   | Interrupt Service Routine                   |

| IPCx  | Interrupt Priority Control Bits             |

| SPI                    | Serial Peripheral Interface     |

|------------------------|---------------------------------|

| I2C                    | Inter-Integrated Circuit        |

| IPEx                   | Interrupt Enable Bit            |

| IFSx                   | Interrupt Flag Status Bits      |

| <i>F<sub>OSC</sub></i> | System Clock Frequency          |

| T <sub>OSC</sub>       | System Clock Period             |

| $F_{CY}$               | Instruction Cycle Frequency     |

| $F_{Cy}$               | Instruction Cycle Period        |

| MIPS                   | Million Instructions Per Second |

| BPS                    | Bits Per Minute                 |

### LIST OF TABLES

| Table 1: Timer 1 control (T1CON) register bits description                         | 25  |

|------------------------------------------------------------------------------------|-----|

| Table 2: Timer 2 control (T2CON) register bits description                         | 29  |

| Table 3: UARTx mode control register bits description                              | .35 |

| Table 4: UARTx status and control register bits description                        | .37 |

| Table 5: BRG values at different baud rates for a 20MHz crystal oscillator4        | 40  |

| Table 6: UARTx transmit register bits description                                  | 42  |

| Table 7: A/D Control register 1 bits description                                   | 46  |

| Table 8: A/D Control register 2 bits description                                   | 50  |

| Table 9: A/D Control register 3 bits description                                   | 53  |

| Table 10: A/D Input select register bits description                               | 56  |

| Table 11: A/D port configuration register bits description                         | 57  |

| Table 12: Performance of the switch based on beta-rebound method in three sessions | 78  |

| Table 13: Performance of the switch based on SSVEP based method in three sessions  | 81  |

### LIST OF FIGURES

|                                                                                          | Page   |

|------------------------------------------------------------------------------------------|--------|

| Fig.1: Block diagram of the brain controlled switch device                               | 9      |

| Fig.2: Block diagram of the analog section                                               | 11     |

| Fig.3: Circuit diagram of the instrumentation amplifier                                  | 13     |

| Fig.4: Circuit diagram of the first-order band pass filters (Active low pass and passive | high   |

| pass)                                                                                    | 14     |

| Fig.5: Minimum and the maximum amplification provided by the bio-potential amplifier     | r to a |

| 50 $\mu$ V signal from the calibrator and displayed on the oscilloscope                  | 17     |

| Fig.6: Flow chart of digital section                                                     | 20     |

| Fig.7: Timer 1 control register                                                          | 25     |

| Fig.8: Timer 2 control register                                                          | 29     |

| Fig.9: UARTx mode control registers, where $x = 1$ or 2                                  | 35     |

| Fig.10: UARTx Status and control register, where x = 1 or 2                              | 37     |

| Fig.11: ADCON1: A/D Control register 1                                                   | 46     |

| Fig.12: ADCON2: A/D Control Register 2                                                   | 50     |

| Fig.13: ADCON3: A/D Control Register 3                                                   | 53     |

| Fig.14: ADCHS: A/D input select register                                                 | 56     |

| Fig.15: ADPCFG: A/D port configuration register                                          | 58     |

| Fig.16: ADCSSL: A/D input scan select register                                           | 59     |

| Fig.17: Prediction algorithm based on beta rebound based method                          | 66     |

| Fig.18: Prediction algorithm based on SSVEP based method                                 | 68     |

| Fig.19: Pure EEG signal measured from the scalp72                                              |

|------------------------------------------------------------------------------------------------|

| Fig.20: EEG signal saturation without the DRL circuit73                                        |

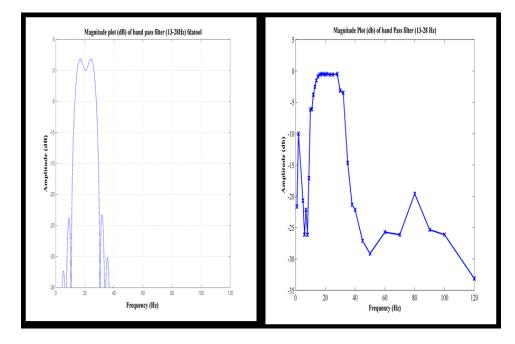

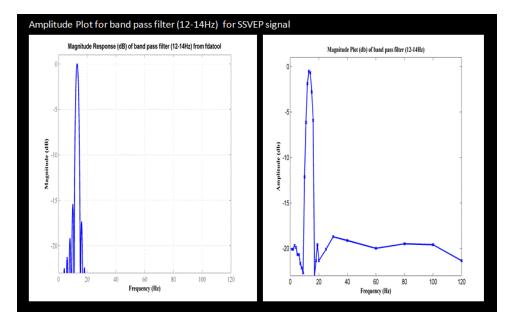

| Fig.21: Bode Plot of the beta band (13-28Hz) filter FIR Kaiser Window design                   |

| with taps =6474                                                                                |

| Fig.22: Bode Plot of the band pass (12-14Hz) filter for SSVEP signal of 13Hz, FIR Kaiser       |

| Window design with taps =12574                                                                 |

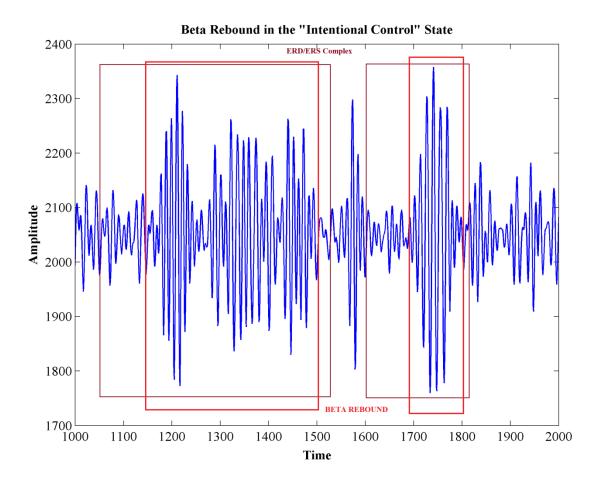

| Fig.23: Offline analysis of the session based on Beta-rebound based prediction algorithm76     |

| Fig.24: Offline analysis of the amplitude power spectrum for the "Intentional Control" and "No |

| Control" state based on beta-rebound based method77                                            |

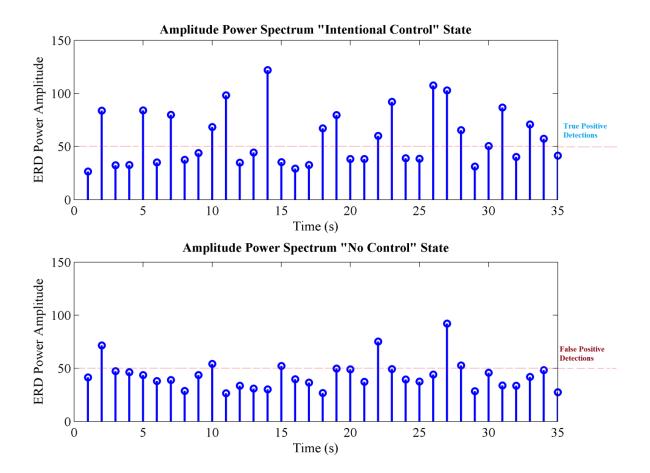

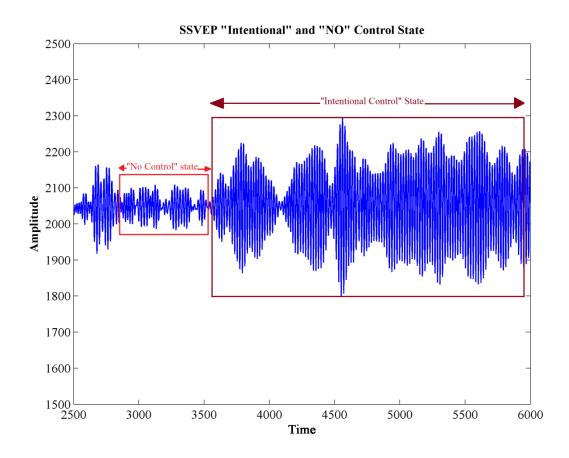

| Fig. 25: Offline analysis of the session based on SSVEP based prediction algorithm79           |

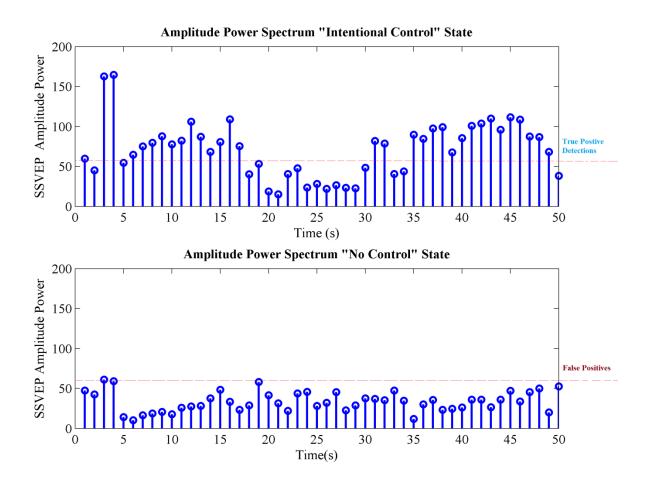

| Fig.26. Offline analysis of the amplitude power spectrum for the "Intentional Control" and "No |

| Control" state based on the SSVEP method                                                       |

#### ABSTRACT

#### **Brain Controlled Switch**

By Dimple Bhuta.

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science at Virginia Commonwealth University, 2009

Major Director: Dr. Ding-Yu Fei

#### Associate Professor, Department of Biomedical Engineering

This study aims at designing and implementing a single channel stand-alone Brain-Controlled Switch (BCS) device, which records the electroencephalography (EEG) signals from the scalp using electrodes, amplifies it, eliminates interferences (associated with the EEG signals) and processes the EEG signals to extract and decode temporal signal features to determine user's intention of regulating an external switch.

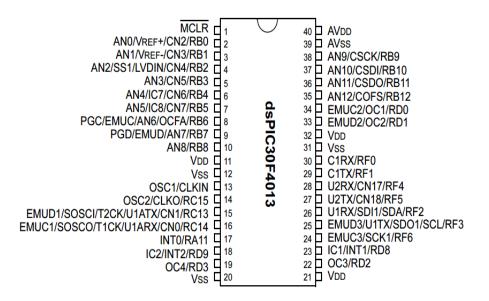

The design of our "brain-controlled switch" device is implemented using a bio-potential amplifier and a microcontroller. The bio-potential amplifier amplifies the EEG signals to a level sufficient for processing, eliminates interferences and ensures patient safety. The microcontroller (dsPIC30F4013) digitizes the amplified and conditioned analog EEG signals from the bio-potential amplifier, extracts the desired signal features for decoding and prediction of user's intention and accordingly operates the external switch.

When the user concentrates on an external visual stimulus or performs externally triggered movement (hand movement or motor imagery movement), a reproducible pattern appears in user's EEG frequency bands. The analysis of these patterns is used to decode and predict user's intention to operate an external switch. To realize our "brain-controlled switch", we explored two EEG sources: steady-state visually evoked potentials (SSVEP) and beta rebounds, which are patterns generated in the EEG frequency bands associated with focusing on an external visual stimulus or performing externally triggered movements.

In case of SSVEP based brain controlled switch, a repetitive visual stimulus (LED flickering at a specified frequency) was used. When the user concentrates on the flickering LED, a dominant fundamental frequency (equivalent to the flickering frequency) appears in the spectral representation of the EEG signals recorded at occipital lobes. Our microcontroller implemented a digital band pass filter to extract the frequency band containing this fundamental frequency and continuously took an average of the amplitude power every predetermined time interval. Whenever the amplitude average power exceeded the preset power threshold the external switch was turned ON. A healthy subject participated in this study, and it took approximately  $3.14 \pm 1.81$  seconds of active concentration for the subject to turn ON the switch in real time with a false positive rate of 1.17%.

In case of beta rebound based brain controlled switch, the subject was instructed to perform a brisk hand movement following an external synchronization signal. Our design focused on the post-movement beta rebound which occurs after the cessation of the movement to operate the external switch. Our microcontroller in this case implemented a digital band pass filter to extract the beta band and continuously took an average of its amplitude power every predetermined time interval. Whenever the amplitude average power exceeded the preset power threshold the

xii

external switch was turned ON. It took approximately  $12.23 \pm 7.39$  seconds of active urging time by the subject to turn ON the switch in real time with a false positive rate of 9.33%. Thus we have designed a novel stand-alone BCS device which operates an external switch by decoding and predicting user's intentions.

#### **CHAPTER 1**

#### INTRODUCTION

#### 1.1 Background

Since the discovery of electroencephalography (EEG) by Hans Berger in 1929 [1], people have speculated that it could be used as muscle-independent communication and control channel (which doesn't use brain's regular pathways of peripheral nerves and muscles) between brain and external devices such as computers, wheelchairs or robotic arms. Hence it is termed as a brain-computer interface (BCI). The target population of the BCI devices is "totally locked-in" patients: their mind is conscious and alert however they lose their ability to move and communicate due to the loss of their motor function. Hemorrhage of brain stem, stroke and tumors, encephalitis, and brain injuries localized in the ventral midbrain causes locked-in syndrome [2]. Also neuromuscular diseases such amyotrophic lateral sclerosis (ALS caused by progressive degeneration of central and peripheral motor neurons), multiple sclerosis and cerebral palsy causes total-locked in syndrome. In "total-locked in" condition, only 10% of the population live more than 10 years following diagnosis and more than 90% of the patients do not choose to prolong life by accepting ventilation due to the anticipated loss of the ability to communicate[3, 4]. In classic "locked-in" syndrome vertical eye movement as well as eye blinks remains intact, which could be used as a basic means of communication to answer questions, give simple commands, or even operate a word processing program. However in total "locked-in syndrome" even the eye muscles are paralyzed, hence an EEG based BCI device can provide basic communication capabilities to these patients with no muscle control, so that they could

express their wishes to caregivers or operate word processing programs and even control a robotic arm [5].

A BCI system mainly consists of four parts: signal recording, processing, predication of the user's intention and controlling the external device. Current BCI researchers record signals for the BCIs from the scalp or utilize signals recorded from inside the brain using implanted electrodes, thus based on the recording site BCI can be divided into non-invasive or invasive BCIs respectively [6]. The signals recorded from non-invasive BCIs generally passes through a bio-potential amplifier which has high amplification ability, high common mode rejection ratio CMRR and circuit protection features; to obtain an appropriate EEG signal for processing. In the signal processing part, signal features in terms of amplitude and/or frequency power are extracted. The prediction part determines user's intention by analyzing the extracted signal features that the user encodes if he/she wants to perform a previously specified task. The extracted signal features are translated into real time commands to operate and control the external device.

Based on the site of acquiring brain signals, the BCI systems can be divided into two types:

(a) Invasive BCI: It provides neuronal signals of best quality as they are recorded from electrodes placed inside the brain. Brain signals can be recorded from small samples of neurons in the single cortical areas, local field potentials (LPF) or large neurons from multiple cortical areas[7]. The signals obtained from the invasive BCI's are very specific to the movement (can produce position and velocity information of the movement), achieve high speed of communication and can be used to control devices with multiple degrees of freedom. The action potentials (neuronal spikes from multiple recording sites) and the LPF (local field potentials) recorded from electrodes inserted into the cortical

tissues were used to operate robotic arms which requires multiple degrees of freedom [8-14]. However these methods are far from practical clinical applications as the electrodes can't be used for a long time, as implantation of the electrodes can further damage the brain tissue by central nervous system infection and also the conductivity of electrodes decreases over time as the body's immune response encapsulates the electrodes. Also most of these experiments have been carried out in non-human primates; hence there is a large gap in applying invasive BCI methods to the target population of "locked-in" patients.

(b) Non-Invasive BCI: It is commonly known as EEG-based BCI system. EEG refers to the mean brain electrical activity arising from billions of neurons recorded non-invasively from the scalp (generally motor cortex or somatosensory cortex) [15]. A composite EEG signal comprises of different rhythms (frequencies bands) produced by distinct cortical areas. They are delta (< 4Hz present frontally in adults and in the posterior lobe in children associated with deep sleep or anesthesia), theta (4-8Hz), alpha (8-12 Hz predominant over occipital, parietal and posterior temporal regions, and are associated with relaxed focus or readiness), beta (13-30 Hz predominant over frontal and central lobes, and are associated with active concentration and alert thinking) and gamma (above 30Hz dealing with mental representations). The EEG based BCI systems tries to decipher its user's intention and decisions through measurements of the combined electrical activity of massive neuronal populations. Hence the quality of the signal recorded from EEG-based BCI system is poor (compared to invasive systems, as the EEG signals are contaminated with neural sources of noise (such as EEG features not used for communication) as well as non-neural artifacts (such as power line noise). It also lacks

specificity (information about the position and velocity information of the movement). However compared to invasive methods, it is robust over time, inexpensive, convenient to use and has low risk in implantation. Several successful EEG based methods have been reported such P300 based letter selection system for 51yr old ALS patient with an accuracy of 83% over 2.5 years [16], mu rhythm based one-dimensional cursor control (up-down of the screen)[17, 18], self-regulated mu rhythm[19], slow cortical potentials based computer-aided spelling system[17, 18], motor imagery based brain controlled switch[20] and visual evoked potential (VEP)[21-24]. EEG based methods appear to be similar to conventional skills which no longer requires intense concentration once learned. Some BCI protocols ask that the user employs very specific motor imagery (e.g., imagery of right or left hand movement) or other mental tasks to produce the EEG features the system uses as control signals. Current EEG-based BCI systems have transfer rates between 5-25 bits/minutes [25, 26]. Although these transfer rates aren't sufficient for controlling neuro-prosthetic devices such as robotic arms, they try to offer some practical solutions (e.g. yes/no answer reply by switch control, one and two dimensional cursor control and wheel chair control) for "locked-in" patients in the near future.

**1.2 Objective:** The objective of this study is to design a real world single channel BCS device. The design is based on the assumption that our target population of "locked-in" patients can still think about moving and the brain areas corresponding to the movement generate patterns that represent the expected value of reward. Our goal is to record these movement intentions, interpret them and use them as control signals to operate a simple ON/OFF switch.

Our device consists of an analog front end circuit (or a bio-potential amplifier) and the digital part. The analog part records the EEG signals from scalp electrodes, amplifies them to a level sufficient for signal processing, reduces the non-neural EEG signal artifacts, filters them to remove the dc offset and perform anti-aliasing. The digital part of our system is designed to convert analog EEG signals into digital signals for processing, extract the features of our interest from the overall available EEG features, eliminate interferences and implement a prediction algorithm to operate an external switch.

To make our design compatible with the real world switch we have tried to implement a design which lets the user decide when to switch ON the external switch by performing a task. A couple of research groups have explored the self-paced or asynchronous EEG based BCI to differentiate between "Intentional Control" state (subject performs a task to indicate movement intention)" and "No Control state" (rest state)[27-29]. We have utilized the principle of "Intentional control" and "No control" state by providing system cues to realize an asynchronous BCS.

We consider the following properties in developing a real world brain-controlled switch:

(a) Self-paced: Incase of the real-world light switch, the switch is turned ON/OFF by the user only when he/she intends to do so by performing a movement task. Similarly in case of BCS, the users would pay attention to the system cues only when they want to turn the switch ON/OFF. Birch's group addressed that the users may perform a certain motor task only when they want to turn ON the switch also called as "Intentional Control state", whereas the users may carry out normal thinking (any task such as relaxing, day dreaming or thinking about a problem) when the users does not wish to operate the switch also called as the "No control" or the rest state[28]. In our experiment, the subject was asked to perform a brisk hand movement in synchronization with an external visual

go-signal as well as asked to concentrate on an external visual stimulus in the "Intentional Control" state. In the "NO control" states, the subject was asked to look away from the visual cue.

- (b) Minimal false positive rate (FPR): In case of the real world light switch, the switch stays OFF in the "No Control" state; our BCS should also avoid false triggering, that is activation of the switch in the "NO control" state. Birch's group suggested that 0% FPR is required in practical applications and they achieved FPR below 1% in their offline or pseudo-online optimization studies [30, 31]. We have also used FPR to evaluate our switch's performance.

- (c) Sensitivity: Real world switch allows its users multiple attempts until the switch is turned ON, since not all switches are sensitive enough that they can be turned ON in the single attempt. Also once activated the switch remains ON until the user intends to turn it OFF. This property is particularly important in case of a BCS as the EEG signal isn't strong enough and the EEG patterns associated with the goal signal (intension of movement) aren't consistent with time. In sensitivity measurement for switch's performance evaluation, switch performance is measured as the average of response time it takes to activate the switch in determined number of trials.

**External stimulus based operation**: BCI technology was proposed to establish a nonmuscular communication and control channel between brain of "totally locked-in" patients and external devices. Two EEG based methods: beta-rebound and steady state visual potentials (SSVEP) were tested to extract the amplitude power feature of the EEG signal from a specific frequency band (beta band for event related potentials and narrow band including the frequency of the SSVEP signal).

- **(i)** Beta rebound based method: Event-related potentials are electrical brain responses whose voltage amplitude increases (event-related synchronization or ERS) or decreases (event-related desynchronization or ERD) in a specific frequency band, in response to an externally triggered movement (hand movement or motor imagery task). These ERD/ERS patters are reproducible and are stable over time. In the beta band, following an ERD that occurs shortly before and during the movement, ERS with very high amplitude oscillations appear within 1 second interval post movement which is also called as beta rebound[32]. A neural network learns to recognize the ERS/ERD patterns associated with specific movements (e.g. right-hand or left hand) and, eventually, the patterns associated with simply thinking about these movements. After the neural network is trained, the system can recognize the EEG patterns associated with specific movements with impressive accuracy and can thereby control movement of a cursor or other external device [33]. In our experiment we have chosen to work with beta rebound patterns generated in-response to cessation of movement after the brisk movement. The beta band rebound is used by our algorithm to control the switch.

- (ii) Steady State Visually Evoked Potentials (SSVEP) based method: They are "frequency coded signals" which can be recorded throughout the visual system. The fundamental frequency of the SSVEP is equal to the flashing or flickering frequency of the visual stimulus, thus the target the subject is gazing at can be identified by frequency analysis. The amplitude increase (associated with concentrating on visual stimuli) in the frequency band of the SSVEP can be used

to control brain-computer interfaces[34]. The frequency bandwidth in which the SSVEP signals are effectively observed is determined empirically to be approximately 6-24Hz[35]. The lower frequencies (6-8Hz) give high accuracy but slower speeds. The stimulus frequency in alpha wave range (8-12Hz) has high background alpha band EEG interference, thus decreasing the accuracy of amplitude measurement. However the beta band (13-28Hz) contains the fundamental frequency component without any interference and has the highest amplitude detection associated with corresponding flickering frequencies; hence the beta band frequency of 13Hz was selected as flickering LED frequency to control the SSVEP based BCS. SSVEP BCIs are considered to be dependent BCI as they depend on muscular control of gaze direction for their operation.

#### **CHAPTER 2**

#### **METHODS**

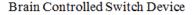

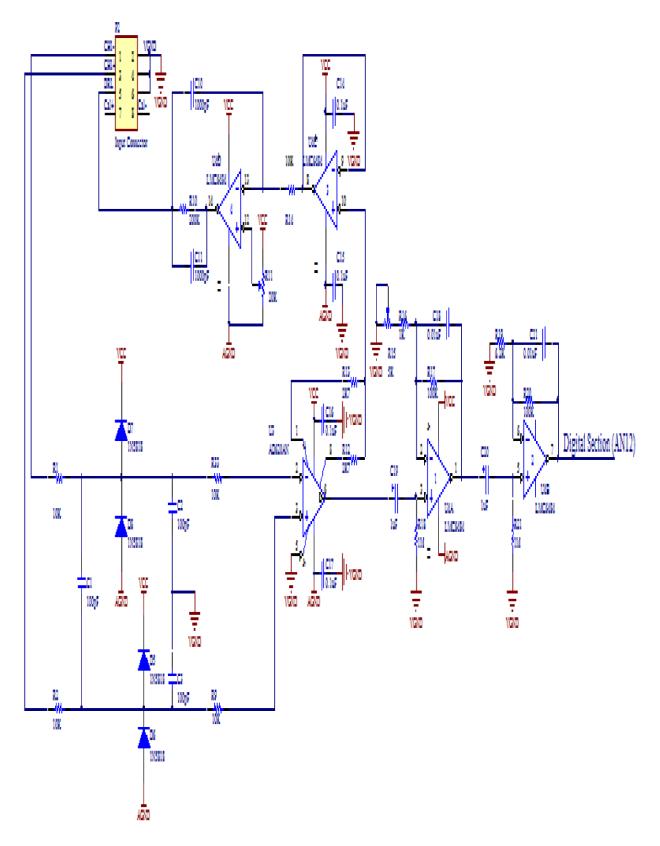

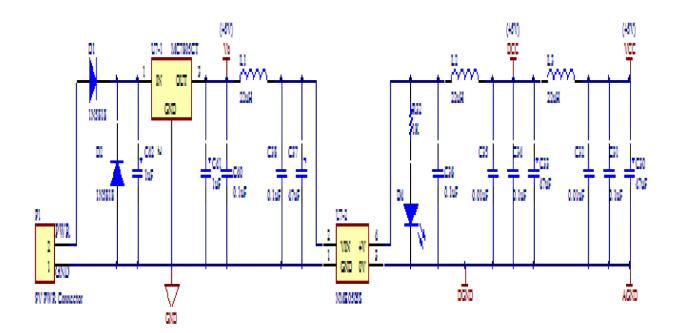

A number of portable, battery operated medical instruments are used in hospitals worldwide due to the recent advances in technology [36]. Also the rapidly expanding field of neuro-prosthetics aims at interfacing artificial devices with the brain [37]. The aim of my project is to develop a one channel portable EEG system to control the light switch. Hence it is termed as a brain-controlled switch. The circuit consists of two parts: an analog front-end circuit (bio-potential amplifier) and a digital circuit [38] show in Fig.1.

Fig.1. Block Diagram of the Brain Controlled Switch Device.

EEG signal amplitude is normally in the range of 0.5 to 100 microvolt's and it contains electrical and physiological artifacts hence it first passes through an analog part (also called the bio-

potential amplifier) which amplifies and conditions the EEG signal to a level sufficient for processing. The analog signal is than converted into digital samples by the microcontroller, features of interest from the EEG signal are extracted using digital filters and a prediction algorithm is implemented in the microcontroller based on external stimulus based operation performed to determine user's intent and accordingly operate the switch.

#### 2.1 Hardware section:

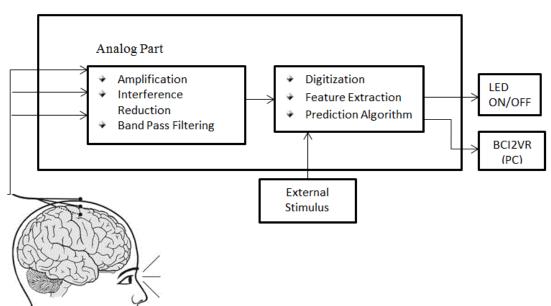

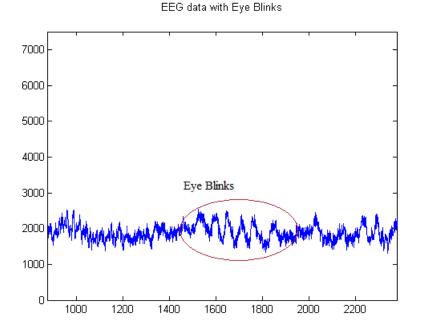

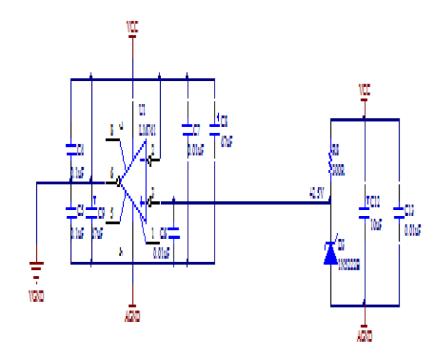

A bio-potential amplifier is used in this section. The EEG signal recorded non-invasively from the scalp is the input to the one channel bio-potential amplifier. The EEG signal obtained from the electrodes is only few microvolts range and it is contaminated with electrical and physiological artifacts (or interferences). The electrical interference arises from electromagnetic interference (EMI), RF (radio frequency interference), cable movements, broken wire contacts, too much electrode gel or dried gel and power line interference (50/60Hz noise) [39, 40]. Physiological sources of interference are motion artifacts, electromyography (EMG) or muscle noise, eye motion or eye blinks, skin-electrode interference and sometimes even the electrocardiography (ECG) or heartbeats. EEG signal acquisition is very important for any BCI system [41]. Thus the bio-potential amplifiers must have high amplification ability (to amplify the microvolt EEG signals for further processing), ability to eliminate electrical interferences, have high input impedance and provide electrical protection to the circuit against high voltage inputs such as defibrillation shocks. To achieve these features, the designed bio-potential amplifier consists of pre-amplifier, main amplifier with filters, driven-right leg circuit (DRL), protection and isolation circuit shown in Fig. 2.

Fig.2. Block Diagram of the Analog Section.

The output signal from the bio-potential amplifier is the conditioned and amplified EEG signal is sent for digital signal processing to the dsPIC30F4013 microcontroller. The parts of the bio-potential amplifier are discussed in detail in this section and the schematic diagram is shown in appendix A.

**2.1.1 Protection Circuit:** Protection circuit protects against high input voltages, from electrostatic discharge, RF signals entering the system through electrode cables and accidental power supply contact. These large voltages can destroy the high impedance instrumentation amplifier, and the EEG circuitry[42].

As shown in the appendix A, a pair of differential signals enters the protection circuit through capacitors (capacitors filters out high frequency input interference and RF interference, if high frequency interference occurs the capacitor shorts) and resistors limit the current. The clamping diodes enables the inputs to the operational amplifier to be limited to the supply voltage plus the diode forward junction voltage (5.7-0.0 volts with reference to AGND or 3.1 (2.5(VGND) + 0.7)

to -3.1 with reference to Virtual ground). When the voltages are above this level, diodes act as open circuits pulling harmful currents to ground potential thus protecting the EEG circuit and the user. The resistors after the diodes limit the current to the Instrumentation amplifier.

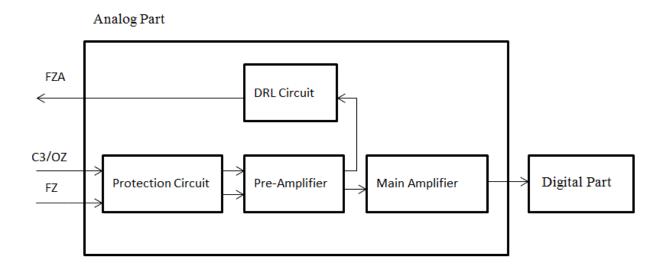

**2.1.2 Pre-amplifier:** An instrumentation amplifier (IA) AD620 is used as the pre-amplifier. It is a low cost, high accuracy instrument with excellent CMRR (AD620 datasheet). The IA is the heart of the bio- potential amplifier as it provides high input impedance, high CMRR and amplification ability which is needed for the accurate measurement of the EEG signals.

The high input impedance is required as it provides minimal loading to the signal being measured thus preventing signal distortion.

Pair of differential signals from the protection circuit is an input to the IA. The IA relates these signals. This relation is performed based on the assumption that both the signals will contain common mode signal (interferences of the EEG signal). When the differential signal is referenced to op-amp output zero voltage, the unknown common-mode signal found in the input signals is eliminated and the output is a pure differential signal. This property of the IA is called as the CMRR. High CMRR is essential for a good quality instrumentation amplifier[43].

IA also amplifies the pure differential voltages (EEG signal) by a factor of 10. This amplification factor (or gain of IA) is calculated as follows.

AND (0V)

Fig.3. Circuit Diagram of the Instrumentation Amplifier.

Gain of the instrumentation amplifier is determined by  $R_{G}$  and is given by

$\label{eq:Gain} \text{Gain}\left(\text{G}_{\text{IA}}\right) = \frac{49.4 \text{K}\Omega}{\text{R}_{\text{G}}} + 1 \text{ ,}$

We selected  $R_G=2^*(2.7k)=5.4\;k\Omega$  and therefore

$$G_{IA} = \frac{49.4K\Omega}{5.4K} + 1,$$

$$G_{IA} = 10.1$$

AD620 also provides low power operation which is beneficial while using multiple independent EEG channels.

**2.1.3 Main amplifier**: It provides the final amplification for the EEG signal and further helps to remove interferences by using a second order band pass filter. We are using two stages of first order band pass filter (passive high pass and active low pass) to realize a second order band pass filter (range 0.2-102.5 Hz), the design of which is shown in schematic A.

A passive high pass filter is used to remove DC voltage offsets and reduce the baseline drift[44]. It is a very essential part of the bio-amplifier as electrodes (made of gold, tin and silver) are polarizable accumulating electric charge on the surface of the electrode hence building up a large DC voltage offset which could saturate the amplifier (limit the voltage value up to 2.5V which doesn't contain any EEG). A second order active low pass filter is used to prevent aliasing that would otherwise occur when the signal is converted to digital samples by the ADC in the digital part. For example according to the sampling theorem our sampling frequency  $f_s$  must be greater than twice of the highest frequency; i.e.  $f_s \ge (2 \times f_{max}) \ge (2 \times 102.5) \ge 205$  Hz. It also attenuates the muscle signal interference (EMG noise (1-5000) range) and the remaining RF interference.

The calculations of cut-off frequencies of the band pass filter and total gain of the pre-amplifier is shown below:

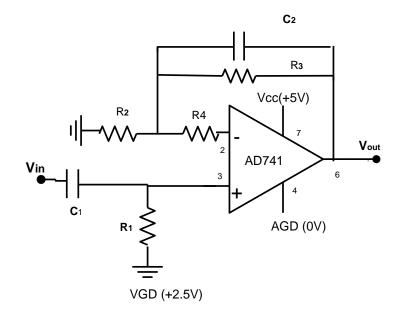

Fig.4. Circuit Diagram of the First-order Band Pass Filter (Active low pass and passive high pass).

Passive high pass filter cut-off frequency:  $f_{c1} = \frac{1}{2\pi \cdot R_1 \cdot C_1}$

Active low pass filter cut-off frequency:  $f_{c2} = \frac{1}{2\pi \cdot R_3 \cdot C_2}$

Gain of the Band pass filter:  $G = \frac{V_0}{V_i} = \frac{R_3}{R_2} + 1$

(i) For the first stage of the first order band pass filter:

We have selected  $R_1 = 1M\Omega$ ,  $R_2 = 1K\Omega + 5K\Omega$  (pot),  $R_3 = 100K\Omega$ ,  $C_1 = 1$  µF, C2= 0.01uF

$$f_{c11} = \frac{1}{2\pi \cdot R_1 \cdot C_1} = \frac{1}{2\pi \cdot 1M\Omega \cdot 1\mu F} = 0.159 = 0.2$$

Hz, where we have selected  $f_{c11}$  as the

cut-off frequency for the first stage high pass filter

$$f_{c12} = \frac{1}{2\pi \cdot R_3 \cdot C_2} = \frac{1}{2\pi \cdot 100 \text{ K}\Omega \cdot 0.01 \mu \text{F}} = 159.2 \text{ Hz}$$

, where we have selected  $f_{c12}$  as the cut-

off frequency for the first stage low pass filter

$$G_1 = \frac{V_0}{V_i} = \frac{R_3}{R_2} + 1$$

, where we have selected

$G_1$  as the gain of the first stage amplifier and  $R_2$  is a variable register (5K $\Omega$  pot and

1K register), we have selected  $R_{21} = 1k$  and  $R_{22} = 5k$  (potentiometer),  $R_2 =$

$R_{21} + R_{22} = 6K\Omega(max)$  and  $1K\Omega(min)$

$$G_1 = \frac{R_3}{R_{21} + R_{22}} + 1 = \frac{100k}{6k} + 1$$

to  $\frac{100k}{1k} + 1$

= 17.7 to 100

Hence  $G_{1\min} = 17.7$  to  $G_{1\max} = 100$

(ii) For the second stage of the first order band pass filter:

We have selected  $R_1 = 1M\Omega$ ,  $R_2 = 6.2K$ ,  $R_3 = 100K\Omega$ ,  $C_1 = 1 \ \mu F$ ,  $C2 = 0.01 \mu F$

$$f_{c21} = \frac{1}{2\pi \cdot R_1 \cdot C_1} = \frac{1}{2\pi \cdot 1M\Omega \cdot 1\mu F} = 0.159 = 0.2$$

Hz, where we have selected  $f_{c21}$  as the

cut-off frequency of the second stage high pass filter

$f_{c22} = \frac{1}{2\pi \cdot R_3 \cdot C_2} = \frac{1}{2\pi \cdot 100 \text{ K} \Omega \cdot 0.01 \mu \text{F}} = 159.2 \text{ Hz}$ , where we have selected  $f_{c22}$  as the cut-

off frequency of the second stage low pass filter

$$G_2 = \frac{V_0}{V_i} = \frac{R_3}{R_2} + 1$$

,

Where we have selected  $G_2$  as the gain of the second stage amplifier

$$=\frac{100k}{6.2k}+1$$

= 17.1

(iii) 2<sup>nd</sup> order band pass filter:

Hence the cut-off frequency  $f_{cH}$  for the passive  $2^{nd}$  order high pass filter, which is composed of two identical  $1^{st}$  order passive high pass filter with cut-off frequency,

$$f_{11} = f_{21} = 0.159 \text{ Hz is}$$

$$f_{cH} = 1.555 \times f_{11} = 1.555 \times 0.159 = 0.247 \cong 0.2 \text{Hz}$$

Hence the cut-off frequency  $f_{cL}$  for the active  $2^{nd}$  order high pass filter with composed of two identical  $2^{nd}$  order passive high pass filter with cut-off frequency  $f_{12} = f_{22} = 159.2$  is

$$f_c = 0.6434 \times f_{12} = 0.6436 \times 159.2 = 102.461 \cong 102.5 \text{ Hz}$$

Total Gain of the pre-amplifier  $G_{TMax} = G_{1max} \times G_2 = 100 \times 17.1290 = 1712.9$

$$G_{TMin} = G_{1min} \times G_2 = 17.6667 \times 17.1290 = 302.6$$

Thus we have designed a pre-amplifier with a variable gain and band pass filter with the cut-off frequencies range from 0.2-102.5Hz.

**2.1.4 Total Gain of the Bio-potential amplifier:** To amplify the EEG signal to the level sufficient for processing first the pre-amplifier with the gain of  $G_{IA}$  is used and then main amplifier which provides variable gain in the range of  $G_{TMin}$  to  $G_{TMax}$  is used.

Total amplification range provided to the EEG signal by the bio-potential amplifier is calculated as follows:

$G_{\min} = G_{IA} \times G_{TMin} = 3070.9$

$G_{max} = G_1 \times G_{TMax} = 17382.7$

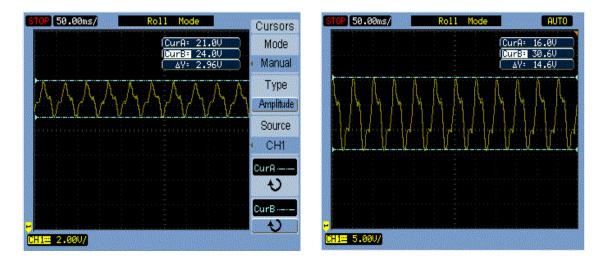

The maximum and minimum amplification provided by the bio-potential amplifier to a  $50\mu V$  sine wave is shown in the figure 5:

Maximum amplitude:

#### Minimum amplitude:

### Fig.5. Minimum and the maximum amplification provided by the bio-potential amplifier to

a 50µV signal generated from the calibrator and displayed on the oscilloscope.

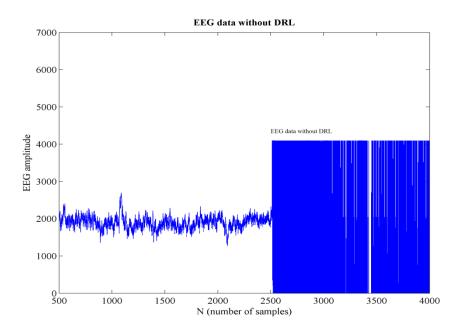

**2.1.5 Driven Right Leg (DRL) circuit:** The common mode voltage is further minimized by the DRL circuit by attaching a third electrode to the patient which provides a low-impedance path between the patient and the instrumentation amplifier (IA). The DRL circuit reduces the effective electrode resistance and it only allows a safe amount of current to flow through the third electrode.

The DRL senses the common mode signals found in the instrumentation amplifier are amplifies, inverts and feeds it back to the body via the third electrode. It greatly reduces common mode interference as the signal when feedback to the instrumentation amplifier will cancel common mode noise between the right leg driver (is also called reference electrode) and the electrodes on the brain thus reducing the common-mode noise at the source[45].

The DRL circuit also works as a good amplifier isolator as it introduces large impedance between body and ground achieved by selecting a large register and a small feedback capacitor thus ensuring patient safety.

Thus we have designed a bio-potential amplifier with good amplification ability and high CMRR to eliminate interferences present with the EEG signal, which is suitable for our BCI system.

**2.1.6 Electrical Isolation:** Optocoupler 6N138/ 6N139is introduced between the Max232 and personal computer (PC) in case of RS232 serial communication. Optocouplers are generally used to transfer data between two devices without making direct electrical connection (electrical isolation). It basically blocks the passage of leakage current from the power line (50-60Hz). If the patient comes in contact with the 120V line, this barrier would prevent dangerous (even fatal) currents from following through the patient by grounding to the ground the microcontroller[46]. It also allows higher transmission rates by reducing the voltage swings.

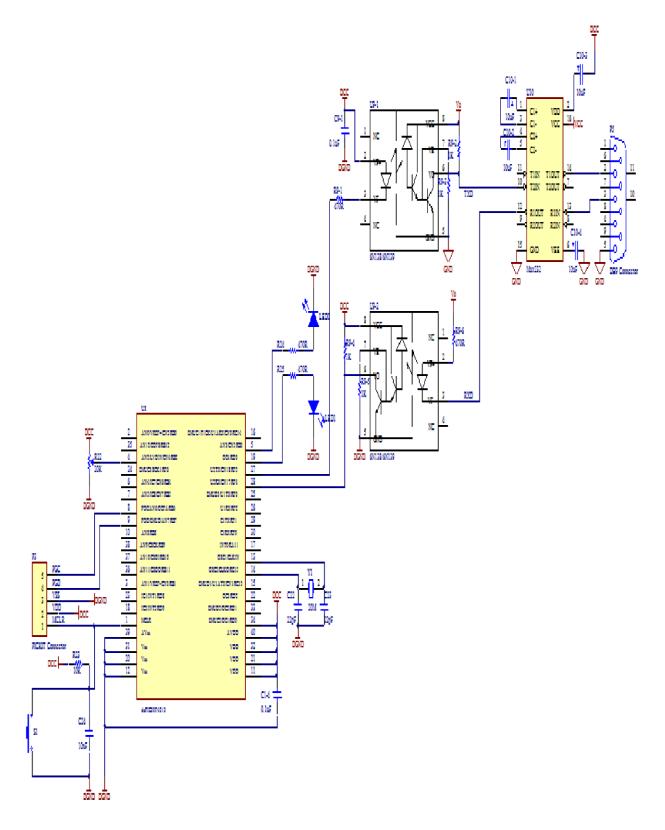

#### **2.2 Digital Section:**

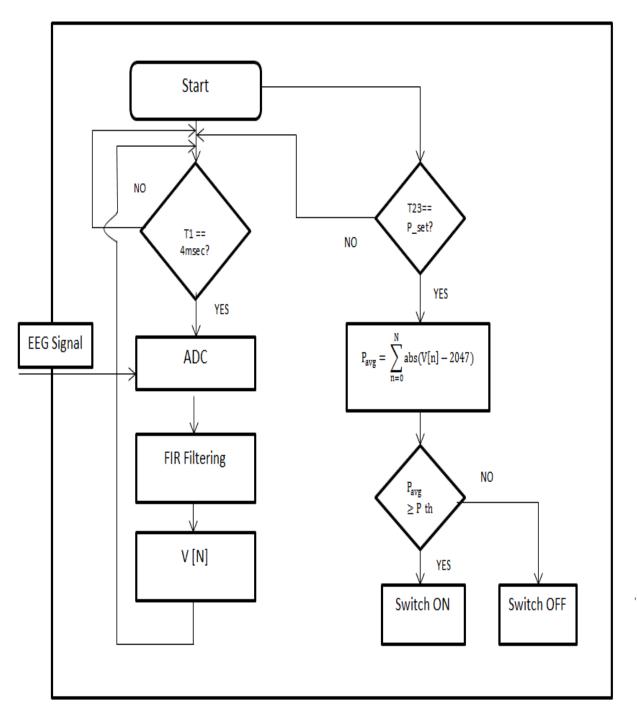

An amplified and conditioned EEG signal enters the digital part which is based on the microcontroller DsPIC30F4013. It consists of analog to digital (A/D) module that converts the EEG signal into a digital signal at the sampling rate of 250Hz. To extract the frequency bands associated with the SSVEP and beta rebound patterns, digital filtering is performed using the DSP engine in the DsPIC30F4013 microcontroller. A prediction algorithm was developed to decode user's intention (amplitude increase in both SSVEP and beta rebound based methods in response to active concentration by the user on an external visual stimulus and performance of a brisk hand movement (or imagination of the movement) respectively) by calculating average amplitude power and comparing it with preset power threshold every predetermined time interval. And if the average calculated power was greater than the power threshold the light switch was turned ON. The algorithm for the digital section is shown in Fig. 6. The digitized and processed EEG signal is relayed to the computer (Dell Vistro desktop), where it is displayed, analyzed and processed continuously using Matlab toolbox called brain computer interface to virtual reality or BCI2VR [47, 48]. To achieve the successful working of the digital part, we need to configure the A/D module, the timer module, the digital filtering module and the (UART) module (to interface the microcontroller with the computer, where the digitized EEG signal is display and analyzed using the BCI2VR software). The following section discusses the in detail configuration of each module and the algorithm to decode and prediction users intention which control an external switch. The schematic diagram of the digital section is shown in Appendix B. All the sections in the digital part are discussed with the aid of dsPIC30F family reference manual, dsPIC30F4013 data sheet and dsPIC Language Tools Libraries[49-51].

## Digital Section

Fig.6. Flow Chart of the Digital Section.

**2.2.1 Interrupts and Timers:** For our project we are using 16-bit Timer1 to generate an interrupt every 4 ms (which corresponds to the sampling rate of 250Hz) and a 32-bit Timer23 to carry out power calculations every preset interval.

A microcontroller can serve several peripheral devices (such as the UART module, analog to digital converter (ADC) modules, external light emitting diodes(LEDs) etc. not all at the same time) without getting tied down, by using interrupts. An interrupt as the name suggests, is an external or internal event that interrupts the normal execution of central processing unit (CPU) and informs that the microcontroller that its device needs immediate service. Every interrupt has a program associated with it called the interrupt service routine (ISR) or interrupt handler.

(a) When an Interrupt Occurs:

Microcontroller finish's the current instruction it's executing and saves the address of the next instruction on the top of stack. It jumps to the interrupt vector table (group of fixed memory locations set aside to hold the addresses of ISRs). The interrupt vector table directs the microcontroller to the address of ISR. Microcontroller executes all the Instructions of the ISR.

After the last instruction is executed, microcontroller returns to the place where it was interrupted and starts execution from that address.

A DsPIC30F4013 microcontroller has up to 41 interrupt sources and 4 processor exceptions (traps). DsPIC30F microcontrollers have seven priority levels which can be assigned to peripheral interrupt source by writing to the control bits in the appropriate interrupt priority Control register (IPCx, where x denotes the register number, x = 1-11). With seven is the highest priority level and one is the lowest level. Assigning a priority level of '0' to an interrupt source is equivalent to disabling that interrupt.

21

(b) Sources/ Types of interrupts

There are 41 sources of interrupts in the dsPIC30F. Following are some of the most widely used sources of interrupts in the dsPIC30F:

- 1. There is an interrupt set aside for each of timers (Timer 1, 2, 3, 4 and 5).

- 2. The ADC interrupts.

- Peripheral interrupts such as UART transmit and receive, serial peripheral interface (SPI), inter integrated circuit (I2C) etc.

- 4. Five interrupts INT0-INT4 are used as external hardware interrupts.

- (c) To control the interrupt operation we need three bits corresponding to each interrupt they are:

- Interrupt Flag Status Registers (IFSx (where x denotes the register number, x = 0, 1, and 2)): When an interrupt is activated, the IFSx (interrupt flag) bit is raised. Thus it indicates that an interrupt event occurred.

- Interrupt Enable Control Registers (IECx (where x denotes the register number, x = 0, 1, and 2)): It allows the programmer to enable (unmask) or disable (mask) corresponding interrupt.

- 3. Interrupt Priority Control Registers (IPCx (where x denotes the register number, x = 0-11)): Each user interrupt source can be assigned to one of eight priority levels. The IPC registers are used to set the interrupt priority level for each source of interrupt. The interrupt priority (IP) bit along with the interrupt flag (IF) and interrupt enable (IE) bits will complete all the flags needed to program the interrupt for the dsPIC30F.

INTCON1, INTCON2 registers control the functions of the global interrupts. INTCON1 register contains control and status flags for the processor trap sources. It also handles the interrupt nesting (for a multi-level priority system, any ISR in progress will be interrupted by another higher user assigned priority level source). Interrupt nesting can be disabled by setting the NSTDIS control bit of the INTCON1 control register. If interrupt nesting is disabled, the user assigned interrupt priority levels are of no use and all the servicing interrupts will be set to the highest priority level(7). User assigned interrupt priority levels will only be used to decide which of the simultaneously pending interrupts will be serviced next. INTCON2 register controls the external interrupts.

**Timer** in simplified terms is a register, whose value keeps on increasing (or decreasing) on every clock pulse, till it reaches its maximum value and rolls over to generate an interrupt. Thus the timer is used to generate time delay independent of the CPU.

For a timer with internal clock source,  $1/4^{th}$  of the frequency of the crystal oscillator on the pins OSC1 and OSC2 of the microcontroller (system clock frequency  $(F_{osc})/4$ ) is fed into the timer, where system clock period  $(T_{osc}) = (4/F_{osc})$ . The internal clock of the CPU can be as fast as 120 MHz which is too fast for the timer to operate; therefore a prescaler (P) could be used to decrease the frequency of the Timer.

For example prescale value =1: P, the Timer increment Frequency =  $(F_{osc}/4) \times (1/P)$ .

DsPIC30F4013 is equipped with five 16-bit timers (Timer1, Timer2, Timer 3, Timer 4 and Timer 5). Each module consists of the three readable/writeable registers:

1. Timer register (TMRx (16-bit timer count registers, where x = 1, 2, 3, 4, and 5)): It is a writable register which holds the start value from which the timer will start counting.

- 2. Period register (PRx, which is a 16-bit period register associated with the timer): It is a writable register which holds the final value of the count. TMRx increments on every instruction cycle until it reaches the value preloaded in the PRx register, and then it resets (starts counting from zero again). This register increases the execution speed of operation since timer value is checked in hardware rather than in software.

- 3. Timer x control register (TxCON where x = 1-5): It is a 16-bit control register associated with the timer.

Timer overflow interrupt: An overflow occurs when a Timer has counted till its maximum value (or final value loaded in the PRx register). For example, when a 16-bit Timer 1 reaches its maximum count of 65535, the next clock cycle cause the timer to rolls over to 0 (or value loaded in the TMRx register) and start counting again, thus generating an overflow. An overflow can trigger an interrupt (set the Interrupt Flag Status bit (TxIF)) if the associating bits such as Interrupt Enable Control bit (TxIE) and Interrupt Priority Control bits (TxIP<2:0>) of the timer module are set.

Steps to design Timer1 to interrupt every 4msec (or at a sampling rate of 250 Hz) are as follows:

1. Configuration of Timer1: The Timer 1 control register (T1CON) is shown in Fig. 7.and the description of T1CON registers bits in discussed in Table 1.

| Upper Byte |         |       | -      |           |     |    |     |       |       |       |

|------------|---------|-------|--------|-----------|-----|----|-----|-------|-------|-------|

| R/W-0      | U-0     | R/W-0 | U-0    | U-0       | U   | -0 | U-0 | U     | 0     |       |

| TON        | _       | TSIDL | _      | _         | -   | -  | _   | -     | -     |       |

| bit 15     |         |       |        | •         |     |    |     | bit 8 |       |       |

|            |         |       |        |           |     |    |     |       |       |       |

|            | Lower I | Byte: |        |           |     |    |     |       |       |       |

|            | U-0     | R/W-  | 0 R/W- | 0 R/V     | V-0 | ι  | J-0 | R/W-0 | R/W-0 | U-0   |

|            | _       | TGAT  | E T    | CKPS<1:0> |     |    | _   | TSYNC | TCS   | _     |

|            | bit 7   |       |        |           |     |    |     |       |       | bit 0 |

# Fig.7. Timer 1 control register.

# Table 1. Timer 1 control (T1CON) register bits description

| T1CON bit | Description                                                                        |

|-----------|------------------------------------------------------------------------------------|

| bit 15    | TON: Timer On Control bit                                                          |

|           | 1 = Starts the timer                                                               |

|           | 0 = Stops the timer                                                                |

| bit 14    | Unimplemented: Read as '0'                                                         |

| bit 13    | TSIDL: Stop in Idle Mode bit (When the processor enters Idle mode, its system      |

|           | clock is functional but the CPU stops code execution)                              |

|           | 1 = Discontinue timer operation when device enters Idle mode                       |

|           | 0 = Continue timer operation in Idle mode                                          |

| bit 12-7  | Unimplemented: Read as '0'                                                         |

| bit 6     | TGATE: Timer Gated Time Accumulation Enable bit, in this mode the internal         |

|           | timer register increments till the state of the T1CK (external clock) pin is high. |

|           | T1IF interrupt flag will be set whenever the timer counts up to value preloaded in |

|           | the PR1 register or the T1CK pin state is changed to low.                          |

|           | 1 = Gated time accumulation enabled                                                |

|           | 0 = Gated time accumulation disabled                                               |

- bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits, Timer1 has the following prescale option

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- bit 3 Unimplemented: Read as '0'

- bit 2 TSYNC: Timer External Clock Input Synchronization Select bit, used specifically for external clock operation as a counter When TCS = 1:

- 1 = Synchronize external clock input

- 0 = Do not synchronize external clock input

When TCS = 0:

This bit is ignored. Read as '0'. Timer 1 uses the internal clock when TCS = 0.

- bit 1 TCS: Timer Clock Source Select bit, selects whether the clock for the instruction cycle will be from internal or external clock

- 1 = External clock from pin TxCK

- 0 =Internal clock (FOSC/4)

- bit 0 Unimplemented: Read as '0'

To Configure Timer1 Module for our application, we load the T1CON register with the following value:

T1CON = 0xA030 or 0b101000000110000; Start timer, use the internal clock ( $F_{osc}/4$ ) and prescale the clock value to 256

Hence the timer increment frequency in our case is:

Crystal oscillator = 10MHz, PLL =8, F<sub>osc</sub> = 10MHz x 8=80MHz

Instruction cycle frequency ( $F_{CY}$ ) = ( $F_{osc}/4$ ) = 20MHz,

million instructions per second (MIPS) = 20;

Timer increment frequency =  $(F_{osc}/4) \times (1/Prescalar) = (20MHz \times 1/256) = 78125Hz$

Or equivalently we can use the dsPIC peripheral library timer functions (with the inclusion of timer.h header) to configure the above register in the following way:

OpenTimer1 (T1\_ON & T1\_GATE\_OFF & T1\_IDLE\_STOP &

T1\_PS\_1\_64 & T1\_SYNC\_EXT\_OFF &

T1\_SOURCE\_INT, match\_value);

- 2. Load the value in the Timer1 period register PR1, if we know the amount of delay required we can calculate the values and load it into the PR1 register as follows:

PR1 = Timer increment frequency x Amount of delay

For example to generate a delay of 4 ms= 78125 x 4 ms= 312.5 = 0x0139

Hence PR1 = 0x0139 or match\_value = 0x0139.

- 3. Load the start value in the TMR1 register. TMR1=0x0000 or WriteTimer1 (0x0000).

- 4. Enable the Timer1 overflow interrupt, set the Interrupt priority and clear Timer1 interrupt flagIEC0bits.T1IE = 1, IFS0bits.T1IF=0, IPC0bits.T1IP<2:0> =110 (6) or we can use timer function ConfigIntTimer1 (T1\_INT\_PRIOR\_6 & T1\_INT\_ON).

5. As soon as the timer counts up to the preloaded value of PR1, Timer1 overflows and the Timer1 interrupt flag bit is set (IFS0bits.T1IF=1). A microcontroller looks up the address in the interrupt vector table and executes the ISR associated with the Timer. Before exiting the ISR the Timer overflow flag bit needs to be cleared (IFS0bits.T1IF=0). Also before exiting the ISR we need to reload the initial count values in the Timer registers (in our case WriteTimer1(0x0000)).

# Steps to design Timer23 to calculate the power value every preset time interval is as follows:

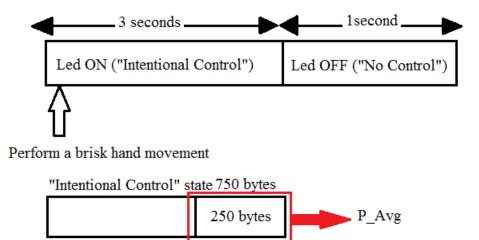

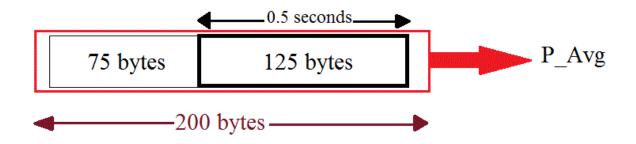

We are using 32-bit timer to provide4 sec synchronization signal (go-signal) via a LED (which remains ON for 3 sec and OFF for 1 sec) and to calculate the average amplitude power every 4 second for beta rebound method. For SSVEP based method we use the 32-bit timer to calculate the average amplitude power used to regulate the switch every 0.5 second. The steps to design the timer to work in 32-bit mode are as follows:

1. Configuration of a 32-bit timer module is formed by combining two 16-bit Timer2 and Timer3modules. When configured for 32-bit operation, control bits of Timer 2 (T2CON control register, PR2 period register and TMR2 register) control the operation of 32-bit timer (where T3CON of timer 3 has no effect). And for interrupt control, control bits of Timer3 register (IFS0bits.T3IF, IEC0bits.T3IE and IPC1bits.T3IP<2:0>) are used. The Timer 2 control register (T2CON) is shown in Fig.8. and the description of T2CON registers bits in discussed in Table 2.

| Upper Byte | a:  |       | -   |     |     |     |       |

|------------|-----|-------|-----|-----|-----|-----|-------|

| R/W-0      | U-0 | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

| TON        | _   | TSIDL | —   | —   | _   | _   | _     |

| bit 15 b   |     |       |     |     |     |     | bit 8 |

| Lower Byte | :     |            |       |       |     |       |       |

|------------|-------|------------|-------|-------|-----|-------|-------|

| U-0        | R/W-0 | R/W-0      | R/W-0 | R/W-0 | U-0 | R/W-0 | U-0   |

| _          | TGATE | TCKPS<1:0> |       | T32   | —   | TCS   | _     |

| bit 7      |       |            |       |       |     |       | bit 0 |

Fig.8. Timer 2 control register.

## Table 2: Timer 2 control (T2CON) register bits description

| T2CON bits | Description                                                      |

|------------|------------------------------------------------------------------|

| bit 15     | TON: Timer On bit                                                |

|            | When $T32 = 1$ (in 32-bit Timer mode):                           |

|            | 1 = Starts 32-bit TMRx:TMRy timer pair                           |

|            | 0 = Stops 32-bit TMRx:TMRy timer pair                            |

|            | When $T32 = 0$ (in 16-bit Timer mode):                           |

|            | 1 = Starts 16-bit timer                                          |

|            | 0 = Stops 16-bit timer                                           |

| bit 14     | Unimplemented: Read as '0'                                       |

| bit 13     | TSIDL: Stop in Idle Mode bit (same as Timer1)                    |

|            | 1 = Discontinue timer operation when device enters Idle mode     |

|            | 0 = Continue timer operation in Idle mode                        |

| bit 12-7   | Unimplemented: Read as '0'                                       |

| bit 6      | TGATE: Timer Gated Time Accumulation Enable bit (same as Timer1) |

|            |                                                                  |

|         | 1 = Timer gated time accumulation enabled                                        |

|---------|----------------------------------------------------------------------------------|

|         | 0 = Timer gated time accumulation disabled                                       |

|         | (TCS must be set to logic '0' when $TGATE = 1$ )                                 |

| bit 5-4 | TCKPS<1:0>: Timer Input Clock Prescale Select bits                               |

|         | 11 = 1:256 prescale value                                                        |

|         | 10 = 1:64 prescale value                                                         |

|         | 01 = 1:8 prescale value                                                          |

|         | 00 = 1:1 prescale value                                                          |

| bit 3   | T32: 32-bit Timer Mode Select bits, determines whether the timer is operating in |

|         | 32-bit mode or 16-bit mode.                                                      |

|         | 1 = TMRx and TMRy form a 32-bit timer                                            |

|         | 0 = TMRx and TMRy form separate 16-bit timer                                     |

| bit 2   | Unimplemented: Read as '0'                                                       |

| bit 1   | TCS: Timer Clock Source Select bit                                               |

|         | 1 = External clock from pin TxCK                                                 |

|         | 0 = Internal clock (FOSC/4)                                                      |

| bit 0   | Unimplemented: Read as '0'                                                       |

To Configure Timer2 Module for our application we have loaded the T2CON register with following value:

T2CON = 0xA02A or 0b101000000101010; Start timer, use the internal clock ( $F_{osc}/4$ ) and prescale the clock value to 64

Hence the timer increment frequency in our case is:

Crystal oscillator = 10MHz, PLL =8, F<sub>osc</sub> = 10MHz x 8=80MHz

$F_{cy} = (F_{osc}/4) = 20MHz, MIPS = 20;$

Timer increment frequency =  $(F_{osc}/4) \times (1/Prescalar) = (20MHz \times 1/64) = 312500Hz$

Or equivalently we can use the dsPIC peripheral library Timer functions (with the inclusion of timer.h header) to configure the above register in the following way:

OpenTimer23(T2\_ON & T2\_GATE\_OFF & T2\_IDLE\_STOP &

T2\_PS\_1\_64 & T2\_32BIT\_MODE\_ON &

T2\_SYNC\_EXT\_OFF &

match value =0xFFFFFFFF)

T2\_SOURCE\_INT, match\_value);

Load the value in the period register of 32-bit timers, PR3 register holds the most significant word (MSWord) and PR2 register holds the least significant word (LSWord). The maximum value that can be loaded into the PR3:PR2 pair is 0xFFFFFFFF or 4294967295. In this case we load in the max value (PR2 = 0xFFFF and PR3 =0xFFFF or

3. Load the start value in the TMR3:TMR2 register (similarly here TMR3 holds the MSWord and TMR2 holds the LSWord). To write, user must first write the MSWord data to the TMR3HLD register (used in the 32-bit operation, which will automatically transfer TMR3HLD contents into the TMR3 register) and then write the LSWord contents into TMR2 register.

If we know the amount of delay required we can calculate the values and load it into the TMR register as follows:

For example to generate a delay = Timer increment frequency x (Amount of delay)

- 3.1. For beta rebound based method:

- i. For the LED to be ON for3 second and to calculate power after every 4 sec, timer increment frequency is 312500 × 3 = 937500

Timer32-bit start value = 4294967296 937500 = 4294029796 = 0xFFF1B1E4, which is loaded in the TMR3:TMR2 register as follows:

TMR3HLD = 0xFFF1;

TMR2 = 0xB1E4;

Or WriteTimer23 (0xFFF8D8F2); using the dsPIC30F libraries

ii. For the LED to be OFF for 1 second, timer increment frequency is  $312500 \times 1 = 312500$

Timer 32-bit start value = 4294967296- 312500 = 4294654796 = 0xFFFB3B4C

Similarly we load timer23 with this value as WriteTimer23 (0xFFFB3B4C)

3.2. For the SSVEP based method:

To calculation power after every 0.5 second we program an interrupt to generate every

0.5 second, timer increment frequency is  $312500 \times 0.5 = 156250$

Timer 32-bit start value = 4294967296-156250 = 4294811046 = 0xFFFD9DA6

Similarly we load timer23 with this value as WriteTimer23 (0xFFFD9DA6);

- Enable the Timer3 overflow interrupt, set the Interrupt priority and clear Timer3 interrupt flagIEC0bits.T3IE = 1, IFS0bits.T3IF =0, IPC1bits.T3IP<2:0> = 111 (priority 7) or we can use Timer function ConfigIntTimer23 (T3\_INT\_PRIOR\_7 & T3\_INT\_ON);

- 5. As soon as the timer counts up to the preloaded value of PR3:PR2 = 0xFFFFFFFF, 32-bit Timer overflows and interrupt flag bit of TMR3 is set (IFS0bits.T3IF=1). A microcontroller looks up the address in the interrupt vector table and executes the ISR associated with the

Timer3. Before exiting the ISR the Timer overflow flag bit needs to be cleared (IFS0bits.T3IF=0). Also before exiting the ISR we need to alternately reload the initial count values WriteTimer23 (0xFFF8D8F2) to get the delay of 1.5 second and WriteTimer23 (0xFFF4143F) to get the delay of 2.5second.

2.2.2 Universal Asynchronous Receiver Transmitter (UART): We are using the UART module to interface our BCS device to the PC for offline processing, steps to interface the UART module with PC are discussed in Appendix F. UART is a full-duplex asynchronous system used for serial communication (data is sent one bit at a time) with peripheral devices (devices with a serial port such as personal computers, RS232 and RS-485 interfaces). DsPIC30F4013 has two UART modules (UxMODE) built-in making data transfers faster and cheaper. The rate of data transfer in serial data communication is stated in bits per second (bps). Another widely used terminology for bps is baud rate. The important features of UART module in dsPIC30F family is it uses standard non-return-to-zero(NZR) format (one start bit, eight or nine data bits, and one or two stop bits), parity options (for 8-bit data), built-in baud rate generator, error detection capabilities, separate transmit and receive interrupts and loopback mode for diagnostic support. RS232: RS232 is most widely used asynchronous serial communication protocol used in computers and digital systems. The DsPIC30F4013 has four pins that are used specifically for transferring and receiving data serially. These four pins are called U1ATX, U1ARX, U2TX and U2RX. These pins use TTL compatible logic levels (High (1) = +5 V and low (0)) = 0V),

however in RS232 High (1) = 12V and LOW=+12V (this is done to increase the range and reliability of the data transfer). To facilitate the interface a line drive (voltage converter) needs to be used. MAX232 is a line drive used for this project.

MAX232: The MAX232 converts RS232 voltage levels to TTL voltage levels, and vice versa. Four capacitors are used for voltage conversions. MAX232 has two sets of line drivers for transferring and receiving data. The line drivers used for transmission (TX) pins are called T1 and T2, while the line drivers for reception (RX) pins are designated as R1 and R2. In many applications only one of each is used. For example, T1 and R1 are used together for TX and RX pins of dsPIC30F4013 and second one is left unused. The circuit connections of the UART module in the dsPIC30F4013 microcontroller to the MAX232 and PC are shown in Appendix B.

In dsPIC30F4013, Each UART module is equipped with a 9-bit wide FIFO transmit data buffer called UARTX transmit register (UxTXREG) which can hold up to 4 words. A UART module (UART1 or UART2) can only be enabled by setting the UART enable bit (UARTEN) and UTXEN bits of the UARTx Mode Register (UxMODE) and UARTX status and control Register (UxSTA, where x = 1 or 2) registers (where x corresponds to UART1 or UART2), along with configuring its TX and RX pins as output and input respectively). However the actual transmission won't occur until the UxTXREG register is loaded with data and baud rate generator produces the baud rate. We are using UART2's transmit mode to display our digitized results on the PC.

#### Steps to design UART2 module as a transmitter are as follows:

1. Configure the UxTX and UxRX pins of the UxMODE (where x is 1 or 2) as inputs and outputs

-UxRX is configured as input (For UART2, its TX and RX pins are multiplexed with port F hence we configure TRISFbits.TRISRF4=1).

-TX is configured as output (For UART2, TRISFbits.TRISRF3 =0).

2. Configuring the Control Registers or setting up the UART

2.1 The configuration of the UART mode control register is shown in figure 9 and the description of the bits are shown in table 3.

| Upper Byte | ):  |       |     |          |       |          |             |

|------------|-----|-------|-----|----------|-------|----------|-------------|

| R/W-0      | U-0 | R/W-0 | U-0 | U-0      | R/W-0 | U-0      | <b>U-</b> 0 |

| UARTEN     | _   | USIDL | _   | reserved | ALTIO | reserved | reserved    |

| bit 15     |     |       |     |          |       |          | bit 8       |

| Lower Byte: |        |       |     |     |            |       |       |  |  |  |

|-------------|--------|-------|-----|-----|------------|-------|-------|--|--|--|

| R/W-0       | R/W-0  | R/W-0 | U-0 | U-0 | R/W-0      | R/W-0 | R/W-0 |  |  |  |

| WAKE        | LPBACK | ABAUD | _   | _   | PDSEL<1:0> |       | STSEL |  |  |  |

| bit 7       |        |       |     |     |            |       | bit 0 |  |  |  |

## Fig.9. UARTx Mode control (UxMode) register.

| UxMODE | Description                                                           |

|--------|-----------------------------------------------------------------------|

| bits   |                                                                       |

| bit 15 | UARTEN: UART Enable bit                                               |

|        | 1 = UART is enabled.                                                  |

|        | 0 = UART is disabled.                                                 |

| bit 14 | Unimplemented: Read as '0'                                            |

| bit 13 | USIDL: bit determines whether the module will stop or continue normal |

|        | operation in Idle mode                                                |

|        | 1 = Discontinue operation when device enters Idle mode                |

|        | 0 = Continue operation in Idle mode                                   |

| bit 12 | Unimplemented: Read as '0'                                            |

| bit 11 | Reserved: Write '0' to this location                                  |

## Table 3: UARTx Mode control register bits description

| bit 10  | ALTIO: UART Alternate I/O Selection bit, the alternate UART pins are     |

|---------|--------------------------------------------------------------------------|

|         | beneficial when the primary UART pins are shared by other peripherals.   |

|         | 1 = UART communicates using UxATX and UxARX I/O pins                     |

|         | 0 = UART communicates using UxTX and UxRX I/O pin                        |

| bit 9-8 | Reserved: Write '0' to these locations                                   |

| bit 7   | WAKE: Enable Wake-up on Start is used to wake the dsPIC from the sleep   |

|         | mode is only beneficial during the reception mode.                       |

|         | 1 = Wake-up enabled                                                      |

|         | 0 = Wake-up disabled                                                     |

| bit 6   | LPBACK: UART Loopback Mode Select bit                                    |

|         | 1 = Enable Loopback mode, In this mode the UxRX pin is disconnected      |

|         | from the UART receive logic and connected internally to the UxTX pin.    |

|         | 0 = Loopback mode is disabled                                            |

| bit 5   | ABAUD: Auto Baud Enable bit is useful in the reception mode to determine |

|         | the baud rates of the received characters                                |

|         | 1 = Input to Capture module from UxRX pin                                |

|         | 0 = Input to Capture module from ICx pin                                 |

| bit 4-3 | Unimplemented: Read as '0'                                               |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits are used to select the data   |

|         | length and parity used in the transmission                               |

|         | 11 = 9-bit data, no parity                                               |

|         | 10 = 8-bit data, odd parity                                              |

|         | 01 = 8-bit data, even parity                                             |

00 = 8-bit data, no parity

bit 0 STSEL: Stop Selection bit determines the number of stop bits used during the data transmission 1 = 2 Stop bits, 0 = 1 Stop bit

2.2 Configuration of the UARTx status and control register (UxSTA) is shown in Fig. 10.and the

description of T1CON registers bits in discussed in Table 4.

| Upper Byte | ):  |     |     |        |       |       |       |

|------------|-----|-----|-----|--------|-------|-------|-------|

| R/W-0      | U-0 | U-0 | U-0 | R/W-0  | R/W-0 | R-0   | R-1   |

| UTXISEL    | _   | —   | —   | UTXBRK | UTXEN | UTXBF | TRMT  |

| bit 15     |     |     |     |        |       |       | bit 8 |

| Lower Byte   | :     |       |       |      |      |       |       |

|--------------|-------|-------|-------|------|------|-------|-------|

| R/W-0        | R/W-0 | R/W-0 | R-1   | R-0  | R-0  | R/C-0 | R-0   |

| URXISEL<1:0> |       | ADDEN | RIDLE | PERR | FERR | OERR  | URXDA |

| bit 7        |       |       |       |      |      |       | bit 0 |

#### Fig.10. UARTx Status and control register.

#### Table 4. UARTx Status and control register (UxSTA, where x=1 or 2) bits description

| UxSTA bits | Description                                                                    |

|------------|--------------------------------------------------------------------------------|

| bit 15     | UTXISEL: Transmission Interrupt Mode Selection bit                             |

|            | 1 = Interrupt is generated when a word is transferred from Transmit buffer to  |

|            | the Transmit Shift register (UxTSR) and as result, the transmit buffer becomes |

|            | empty.                                                                         |

|            | 0 = Interrupt is generated when all four words are transferred from the        |

|            | Transmit buffer to the Transmit Shift register                                 |

| bit 14-12  | Unimplemented: Read as '0'                                                     |

| bit 11  | UTXBRK: Transmit Break bit drives the UxTX line to '0'. This bit is set in        |

|---------|-----------------------------------------------------------------------------------|

|         | software and runs for 13 baud clocks. This needs to be cleared in software        |

|         | where it generates a stop bit after which the transmitter can renew its activity  |

|         | 1 = UxTX pin is driven low, regardless of transmitter state                       |

|         | 0 = UxTX pin operates normally                                                    |

| bit 10  | UTXEN: Transmit Enable bit, This bit finally enables the UART transmission        |

|         | and also sets the UxTXIF flag bit if UTXISEL $= 0$                                |

|         | 1 = UART transmitter enabled.                                                     |

|         | 0 = UART transmitter disabled, any pending transmission is aborted and buffer     |

|         | is reset.                                                                         |

|         | Note: The UTXEN bit should not be set until the UARTEN bit has been set.          |

|         | Otherwise, UART transmissions will not be enabled.                                |

| bit 9   | UTXBF: Transmit Buffer Full Status bit (Read Only), Each UART module is           |

|         | equipped with a 9-bit wide FIFO transmit data buffer which can hold up to 4       |

|         | words. UTXBF status bit is set if the buffer is full                              |

|         | 1 = Transmit buffer is full, no new data will be accepted in the FIFO buffer      |

|         | 0 = Transmit buffer is not full, at least one more data word can be written       |

| bit 8   | TRMT: Transmit Shift Register is Empty bit (Read Only) is used to check           |

|         | whether the last transmission has completed                                       |

|         | 1 = Transmit shift register is empty and transmit buffer is empty                 |

|         | 0 = Transmit shift register is not empty, a transmission is in progress or queued |

|         | in the transmit buffer                                                            |

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit used for UART                  |

|       | Reception hence Don't Care('00')                                           |

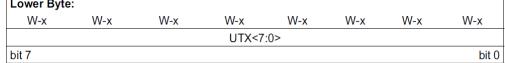

|-------|----------------------------------------------------------------------------|