### Virginia Commonwealth University VCU Scholars Compass

Theses and Dissertations

**Graduate School**

2010

# Digital Implementation of a True Random Number Generator

Sam Mitchum Virginia Commonwealth University

Follow this and additional works at: http://scholarscompass.vcu.edu/etd Part of the <u>Engineering Commons</u>

© The Author

Downloaded from http://scholarscompass.vcu.edu/etd/2327

This Dissertation is brought to you for free and open access by the Graduate School at VCU Scholars Compass. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

## Digital Design and Implementation of True Random Number Generators

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at Virginia Commonwealth University.

by

Samuel Theodore Mitchum, Junior Bachelor of Science in Engineering, University of South Carolina, 1981 Master of Engineering, University of South Carolina, 1986

> Director: Dr. Robert H. Klenke Associate Professor Department of Electrical and Computer Engineering

> > Virginia Commonwealth University Richmond, Virginia December 2010

# TABLE OF CONTENTS

| ACKNOWLEDGEMENT                                                      | 4    |

|----------------------------------------------------------------------|------|

| CHAPTER 1 INTRODUCTION                                               | 5    |

| 1.1 STATEMENT OF PURPOSE                                             | 5    |

| 1.2 Problem Definition                                               | 5    |

| 1.3 Overview                                                         | 8    |

| 1.4 Abbreviations and Acronyms                                       | 8    |

| CHAPTER 2 DEFINING AND MEASURING RANDOMNESS                          | 9    |

| 2.1. Definition                                                      | 9    |

| 2.2. Tests For Randomness                                            |      |

| 2.3 HOW RANDOM IS RANDOM ENOUGH?                                     |      |

| 2.4 Not-So-Random Number Generators                                  |      |

| 2.4.1 Linear Feedback Shift Register                                 |      |

| 2.4.2 Whitening                                                      |      |

| CHAPTER 3 BACKGROUND                                                 | . 19 |

| 3.1 ELECTRONIC RNG HISTORY                                           | . 19 |

| 3.1.1 Analog RNGs                                                    |      |

| 3.1.2 Chaos RNGs                                                     |      |

| 3.1.3 Digital RNGs                                                   | . 23 |

| 3.1.4 RNG's Similar To This Work                                     |      |

| CHAPTER 4 DIGITAL TRNG DESIGNS                                       | . 29 |

| 4.1. Overview                                                        | . 29 |

| 4.2 Randomness                                                       | . 29 |

| 4.2.1 Randomness In The Analog Domain                                |      |

| 4.2.2 Randomness In The Digital Domain                               |      |

| 4.2.3 Distilling Randomness From Clock Jitter                        | . 31 |

| 4.2.4 Range of Numbers and Paths Through The Range                   | . 32 |

| 4.2.5 Capturing Randomness Using Divergent Paths                     | 34   |

| 4.2.6 Simple Divergent Path RNG                                      | 40   |

| 4.2.7 Divergent Path Formulae                                        |      |

| 4.2.8 Differences From Other Architectures                           | 44   |

| CHAPTER 5 DIVERGENT PATH ARCHITECTURES                               | . 46 |

| 5.1 Adder-Shifter Based TRNG Architecture                            | . 46 |

| 5.2 DESIGN OF THE ASTRNG CHIP                                        | . 49 |

| 5.2.1 ASTRNG Design Methodology                                      | 49   |

| 5.2.2 ASTRNG Development                                             |      |

| 5.2.3 ASTRNG IC Fabrication Testing                                  |      |

| 5.2.4 ASTRNG IC Statistical Testing                                  |      |

| 5.2.5 ASTRNG Realization In FPGA                                     |      |

| 5.3 CONCATENATED LFSR BASED ARCHITECTURES                            |      |

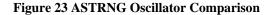

| 5.3.1 CLTRNG Realization With 9, 13 and 16 Bit LFSRs                 |      |

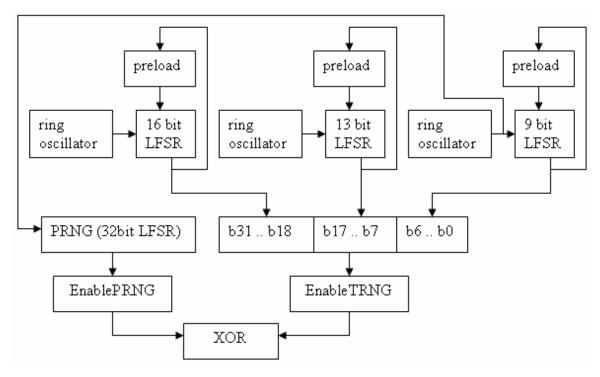

| 5.3.2 LFSR Realization With 11, 11 and 10 Bit LFSR Contributions     |      |

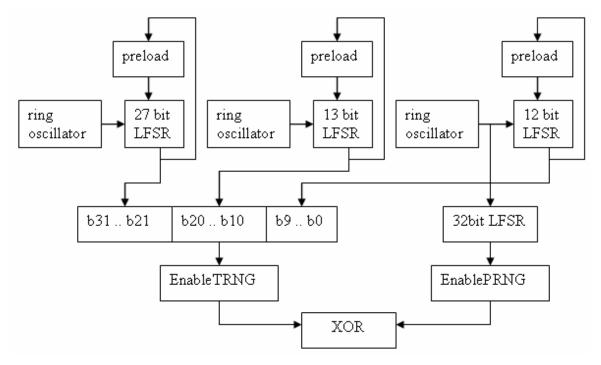

| 5.3.3 CLTRNG Realization With 7, 9, 11 and 13 Bit LFSR Contributions |      |

| 5.3.4 Using a TRNG to Whiten a PRNG                                  |      |

| CHAPTER 6 TEST EQUIPMENT                                             | . 63 |

| 6.1 TRNG TEST EQUIPMENT                                              | . 63 |

| 6.2 RNG TEST EQUIPMENT BUILT IN TESTS                     |    |

|-----------------------------------------------------------|----|

| 6.3 RNG TEST INTERFACE PCBS                               |    |

| 6.3.1 Single RNG IC Interface PCB                         |    |

| 6.3.2 Multiple RNG IC Interface PCB                       |    |

| 6.3.3 Avnet Development Board for Xilinx Spartan2 FPGA    |    |

| CHAPTER 7 TEST RESULTS                                    |    |

| 7.1 RNG IC TEST RESULTS                                   |    |

| 7.1.1 Reset and Read Test Results for RNG ICs             |    |

| 7.1.2 NIST800-22 Results for RNG ICs                      |    |

| 7.1.3 Whitened NIST800-22 Results for RNG ICs             |    |

| 7.2 FPGA RNG TEST RESULTS                                 |    |

| 7.2.1 NIST800-22 Test Results for FPGA ASTRNG             |    |

| 7.3 THREE LFSR BASED FPGA CLTRNG TEST RESULTS             |    |

| 7.3.1 Reset and Read Test Results for 3-LFSR CLTRNG       |    |

| 7.3.2 NIST800-22 Test Results for 3-LFSR CLTRNG           |    |

| 7.4 ANOTHER THREE LFSR BASED FPGA CLTRNG TEST RESULTS     |    |

| 7.4.1 Reset and Run Test Results for Second 3-LFSR CLTRNG |    |

| 7.4.2 NIST800-22 Test Results for Second 3-LFSR CLTRNG    |    |

| 7.4 FOUR LFSR BASED FPGA CLTRNG TEST RESULTS              |    |

| 7.4.1 Reset and Read Test Results for 4-LFSR CLTRNG       |    |

| 7.4.2 NIST800-22 Test Results for 4-LFSR CLTRNG           |    |

| 7.5 USING A TRNG TO WHITEN A PRNG                         |    |

| CHAPTER 8 CONCLUSION                                      |    |

| 8.1 SUMMARY OF WORK                                       |    |

| 8.2 Lessons Learned                                       |    |

| 8.3 FUTURE WORK                                           | 88 |

### ACKNOWLEDGEMENT

This dissertation is a continuation of development begun at Philips Semiconductor. The high cost and long lead times required to obtain analog chip design help on the existing random number generator circuit inspired the System Architect to charge me with developing a truly digital design containing no analog components. The Glen Allen office was shut down before this work was completed. Philips Semiconductor granted me permission to continue this development and to publish my findings. I would like to recognize the contributions of the following people from Philips Semiconductor:

Raj Maini, Director of Strategic Marketing, for giving me permission to continue David Deland, Manager of the Glen Allen office

Dr. Jack Ehrhardt, System Architect and Bill Chauncey, Mathematician

Mark Harrison, Lucien Rainville, Bill Lester, team members

I would also like to thank my advisory committee from VCU:

Dr. Bob Klenke, Department of Electrical and Computer Engineering, Advisor

Dr. Jim Ames, Department of Computer Science

Dr. Jim Deveney, Professor Emeritus, Department of Mathematics

Dr. Alen Docef, Department of Electrical and Computer Engineering

Dr. Mike McCollum, Department of Electrical and Computer Engineering I would like to thank Donovan Davis, Naveen Elangho and Jin Xu for helping with the layout of the RNG chip.

Finally I would like to thank the School of Engineering, Virginia Commonwealth University and especially the Administrative Assistants who have been very helpful.

### **CHAPTER 1 INTRODUCTION**

### **1.1 Statement of Purpose**

The purpose of this research is to develop a digital true random number generator that can be synthesized using standard digital design tools. Random number generators are used in security for generating secrets such as session keys and large primes for key exchange and exponentiation[1]. Random number generators are also used for simulating random events and for professional gaming. The security applications are of primary importance as the number and complexity of networks continues to grow. Random number generators will be required to protect the medical, financial and personal data of entities connected to these networks. A digital true random number generator that can be synthesized using standard digital tools will enable designers to address these privacy concerns more efficiently.

### **1.2 Problem Definition**

Random number generators may be divided into two classes – pseudo random number generators and true random number generators. Pseudo random number generators generate a stream of numbers in a known pattern. The pattern is typically very long and it is hard to recognize the sequence of numbers is ordered. However, perfect knowledge of the generating circuit and the most recently generated number will enable the next generated number to be determined. For this reason pseudo random number generators are often called deterministic random number generators. Pseudo random

number generators are easily built from a Linear Feedback Shift Register (LFSR) assuming judicious selection of the XOR taps[2]. In order to disguise the fact that they are deterministic, PRNGs are often built with many more generated bits than are used per number. For example, a 128 bit LFSR may be used to implement a 32 bit PRNG. Protection comes from the fact that it is more difficult to discover the 96 hidden bits than the 32 bits used for the random number. Hence it is anticipated that the 128 bit implementation would be more secure. As with many real-world aspects of security, it is assumed that simply extending the length of the PRNG would provide acceptable privacy. However the issue of perfect knowledge of the generator determining the next output value is not addressed by this solution.

True random number generators produce a stream of truly random numbers. That is, knowing the generating circuit and the past history of numbers generated is insufficient to determine the next number. True random number generators are often called non-deterministic random number generators since the next number to be generated cannot be determined in advance. For a perfect true random number generator, the probability of the next generated number being any specific value should be equal to the probability of the next generated number being any other specific value. Since a certainty is always a probability of 1 and since some specific value will certainly be generated, the probability of any particular value being generated next should be equal to 1 (certainty) divided by the number of possible values in the range. As a simple illustration, consider a six sided die. The probability of any one of the six sides facing up after rolling the die is 1 (certainty) divided by 6 (the number of possible values). For a digital random number composed of N bits where N is positive definite, the range of values has 2<sup>N</sup> possible values. So the probability of any particular value being generated next by a true N-bit digital random number generator is:

#### **Equation 1**

$$P = \frac{1}{2^N}$$

At the inception of this research, true random number generators always required some analog components be included in ICs (Integrated Circuits). True random number generators were always based on an analog property like junction or thermal noise that was often whitened and scaled to produce a uniformly distributed random number generator. Whenever a SOC (System On a Chip) required random number generation, an analog IC designer was required to complete the design. A digital random number generator that can be designed using standard digital design tools would significantly reduce the cost and complexity of including a true random number generator in a design.

When a true random number generator is implemented in an FPGA (Field Programmable Gate Array), either several additional analog components such as resistors and operational amplifiers must be added to the design, or the designer must measure and match performance of individual logic blocks to achieve acceptable performance[3][4]. Again, a digital random number generator that can be designed and implemented using standard digital design tools would alleviate the need for extra components and/or the tedious hand-matching of logic blocks. This dissertation documents the design and implementation of a true random number generator using standard digital design methodology.

### **1.3 Overview**

The remaining chapters of this dissertation are organized as follows; Chapter 2 covers methods for grading random number generators. Chapter 3 covers existing random number generator designs. Chapter 4 introduces the concept of divergent path RNGs. Chapter 5 covers two architecture proposals for non-deterministic digital random number generators. Chapter 6 presents the hardware and software used to test the generators. Chapter 7 contains the test results from the two proposed architectures. Finally chapter 8 presents possible future work on digital random number generation.

### **1.4 Abbreviations and Acronyms**

| Acronym | Stands For               | Meaning                                       |  |

|---------|--------------------------|-----------------------------------------------|--|

| FPGA    | Field Programmable Gate  | A digital device whose architecture can be    |  |

|         | Array                    | readily reconfigured.                         |  |

| LFSR    | Logical Feedback Shift   | A multibit parallel FIFO whose incoming       |  |

|         | Register                 | bit is a logical combination of current bits. |  |

| NIST    | National Institute of    | The government organization that              |  |

|         | Standards and Technology | promotes and publishes standards.             |  |

| PRNG    | Pseudo (Deterministic)   | A number generator that creates a             |  |

|         | Random Number Generator  | repeatable sequence of numbers that           |  |

|         |                          | appear to be random.                          |  |

| RN      | Random Number            | A number whose value cannot be predicted      |  |

|         |                          | merely by knowing previous numbers in         |  |

|         |                          | the sequence and the generating circuit.      |  |

| RNG     | Random Number Generator  | A circuit for creating a sequence of          |  |

|         |                          | numbers.                                      |  |

| SOC     | System On a Chip         | A complete microprocessor based design        |  |

|         |                          | incorporated on a single semiconductor.       |  |

| TRNG    | True (Non-deterministic) | A number generator that creates a non-        |  |

|         | Random Number Generator  | repeatable, non-predictable sequence of       |  |

|         |                          | numbers.                                      |  |

The following abbreviations and acronyms are used throughout this paper.

### CHAPTER 2 DEFINING AND MEASURING RANDOMNESS

### 2.1. Definition

In order to discuss random number generation, it is necessary to define what random means. Webster's New World College Dictionary gives three definitions for random[5]:

1) lacking aim or method; purposeless; haphazard

2) not uniform; especially of different sizes

3) Statistics of statistical sample selection in which all possible samples have equal probability of selection

No one of these three definitions is sufficient to describe a true random number generator. The first definition, haphazard, implies that the number stream from the RNG is not predictable. But is says nothing about the distribution of numbers generated. This definition would be satisfied with only a small portion of potential numbers actually being produced; for example if a six sided die was cast and always came up either 3 or 6 but never 1, 2, 4 or 5. The second definition, not uniform, adds nothing to the first definition. But the third definition, equal probability of selection, means that over time, the probability of each possible number being produced should be the same. To continue the analogy with a six sided die, this definition means that after rolling the die for a long time, each value in the set  $\{1, 2, 3, 4, 5, 6\}$  should have come up about the same number of times. How many samples constitute a long time and how close to equal constitutes about the same number of times are defined by the statistical tests for randomness. One other characteristic is defined by these tests: how haphazard (or unpredictable) the stream is. For example, a simple counter will produce every value in the count range and with

equal distribution. But a counter is not considered to be a RNG because the output is not haphazard; that is, the output is very predictable.

A random number generator outputs a stream of numbers. If the order of the numbers in the stream is exactly known then the stream is completely determined and there is no randomness in it. If the order of the numbers is not known then the stream has some degree of randomness. For most systems, a random number stream that is uniformly distributed is ideal. For such a system, the probability of any number being generated is equal to the probability of any other number being generated at any time. The tests used to measure the randomness in this paper all assume a uniform distribution. Each test has a unique way to measure the distribution.

### 2.2. Tests For Randomness

There are many ways to test the randomness of a stream of numbers. A few simple ones would be:

- count the number of "1" bits and the number "0" bits and make sure they are approximately the same

- break the stream into groups of say four bits and make sure that each possible fourtuple occurs roughly the same number of times (0000, 0001, 0010, 0011, .... 1111)

- pick a bit size and a particular pattern for that size and count how many bits are produced before that exact pattern is produced again.

There are many published sets of tests for randomness, including FIPS 140-1 and George Masaglia's Diehard Tests. The National Institute for Standards and Technology (NIST) has published a suite of statistical tests for determining the quality of a random number generator in publication 800-22 [6]. These are the tests that have been used to determine

the quality of the RNGs in this paper. This suite contains sixteen different tests which are detailed below.

- Frequency Test: This test compares the proportion of 1's to 0's in the data. The proportion of 1's should be about half the number of bits. The test fails if there are too many or too few 1's in the bit stream.

- 2) Block Frequency Test: This test computes the proportion of 1's to 0's in a specified block size. For random data the frequency should be about half the block size. This test fails if there are too many blocks which have either too many or too few 1's.

- 3) Cumulative Sums Test: This test identifies the maximal excursion from 0 of a random walk using the values [-1, +1]. In other words, start at a point in the bit stream and move forward to the adjacent bit. If it is a "0" then SUM = SUM 1. If it is a "1" then SUM = SUM + 1. If the bits alternated perfectly then the cumulative sum would remain low. If there are too many 1's or 0's in a row, however, the cumulative sum gets large. This test fails if the cumulative sum is either too large or too small.

- 4) Runs Test: This test counts the number of occurrences of runs of 1's. A run is defined as a continuous stream of bits of the same value bounded at the start and the end by bits of the opposite value. The expected results are more runs of shorter numbers of 1's and fewer runs of longer numbers of 1's. The test fails if there is significant deviation from the expected number of runs for any length of consecutive bits.

- Longest Runs Test: This test counts the longest number of consecutive bits in each block of m bits. The test fails if there are too many consecutive 1's in the block.

- 6) Rank Test: This test divides the stream of binary bits into rows and columns of matrices. It then calculates the rank of each resulting matrix as a way of testing for linear dependence hence too many repeated patterns. The test fails if ranks of the resulting matrices are incorrectly distributed.

- 7) Discrete Fourier Transform Test: This test examines the peak heights in the discrete Fourier transform of the sequence. The purpose is to detect repetitive patterns in the sequence. The test fails if the number of peaks exceeding a given threshold is too large.

- 8) Non-overlapping Template Matching Test: This test searches the bit stream for specific, aperiodic patterns. If the pattern is found, the search is started again just beyond the end of the pattern. If the pattern is not found, the search is started again at the next bit position. The test fails if too many occurrences of the pattern are found.

- 9) Overlapping Template Test: This test is similar to the non-overlapping template matching test except if the pattern is found, the search is continued from the next bit following the start of the pattern so that patterns which overlap are detected. Again the test fails if too many occurrences of the pattern are found.

- 10) Maurer's Universal Statistical Test: This test counts the number of bits between matching patterns in the data stream. This measure is related to how well the stream can be compressed. The test fails if the bit stream is compressible.

- 11) Approximate Entropy Test: This test compares the frequency of occurrence of all patterns of a certain bit length with the frequency of occurrence of all patterns that are one bit longer. The test fails if the difference in frequency of occurrence for the two lengths is not as expected for random data.

- 12) Random Excursions Test: This test is similar to the cumulative sum test in that a sum is calculated by taking a random walk from a point considered to be the origin and returning to that point. For each bit traversed, subtract 1 if the bit is a "0" and add 1 if the bit is a "1". The test actually examines eight different measurements how many times each of the sums in the set [-4, -3, -2, -1, +1, +2, +3, +4] are encountered during a random walk. The test fails if the number of times each sum is encountered does not match that predicted for random data.

- 13) Random Excursions Variant Test: This test is a more stringent variation of the random excursions test. The difference is the number of sums. This test uses a total of eighteen sums, [-9, ... -1, +1, ... +9] where the random excursions test only uses eight. The test fails when the number of times each sum occurs does not match that expected for random data.

- 14) Serial Test: This test measures the frequency of occurrence of all possible overlapping patterns of a specified bit size. In a random stream, each pattern should occur approximately the same number of times. The test fails if the number of occurrences of each pattern is not approximately the same. Note for the case of 1 bit patterns, this test degenerates to the frequency test.

- 15) Lempel-Ziv Test: This test counts the number of cumulatively distinct patterns in the sequence. It is a measure of how much the bit stream can be compressed.The test fails if the bit stream can be compressed.

- 16) Linear Complexity Test: This test calculates the size of a LFSR that would be required to produce the bit stream. The test fails if the required LFSR is too small.

These are the sixteen tests that make up the NIST800-22 test suite for randomness. They are quite complete – a fact that may be inferred as NIST has not seen the need to update them. The scoring is somewhat arbitrarily as suggested by NIST at 96%; that is, a score of 95.9% fails while a score of 96.0% passes.

### 2.3 How Random is Random Enough?

Continuing the analogy with a six sided die, the value defined by rolling the die would be random. Assuming the die was well-constructed and balanced, there should be no way to predict what number would come up on any given roll. The probability should be equal that any one of the range of numbers {1, 2, 3, 4, 5, 6} would come up on any given roll. That is, if the die were cast many times, then the number of 1's should match the number of 2's, the number of 3's, the number of 4's, the number of 5's and the number of 6's. If this is true then the die is called "fair" and the probability of being rolled is equally distributed across all six elements of the range. Such a die would be called statistically random.

Suppose an extra dot is added to the 2 face of the die. Now there is no 2 face and there are two 3 faces. Now if the die is rolled there is still a 1 in 6 chance of the other four faces (1, 4, 5, 6) coming up. But there is no chance a 2 face will come up and there

is a 2 in 6 (or 1 in 3) chance of a 3 face coming up. Now, with this change, a haphazard number is still generated by rolling the die because the number that will come up is not perfectly predictable. But the probabilities are no longer evenly distributed. This uneven distribution is one aspect that tests like those in the NIST 800-22 suite are designed to detect.

Suppose another change is made to the die. The extra dot is removed so that all six numbers are present, but we make the entire 1 dot face heavier than the other faces. Now all six values can be rolled but the face across from the 1 dot will come up more often. If the heavy face is 1, the faces adjacent to the heavy face are  $\{2, 3, 4, 5\}$  and the face opposite the heavy face is 6. If the die is rolled many times then 1 will come up the least frequently,  $\{2, 3, 4, 5\}$  will come up with about equal frequency and 6 will come up most frequently. This variation in frequency is another aspect that statistical tests will measure.

Finally, in a perfectly fair die it is not possible to predict which number will be rolled following any other number. If it were possible to predict the order of numbers, for example {1, 4, 3, 6, 2, 5, 1, 4, 3, 6, 2, 5 ...}, then the die would be of little use and that is obvious. But a more basic (and more likely) example of this same aspect would be if every time a 3 was rolled then a 1 would be rolled. The numbers rolled before the 3 and after the 1 could be perfectly haphazard. But every time a 3 was rolled, a 1 would be rolled next. While this would be obvious after a few dozen rolls with a six sided die, it would be much harder to detect with a random number generator having four billion output values. The statistical tests also find and measure these small patterns within the larger output sample.

### 2.4 Not-So-Random Number Generators

### 2.4.1 Linear Feedback Shift Register

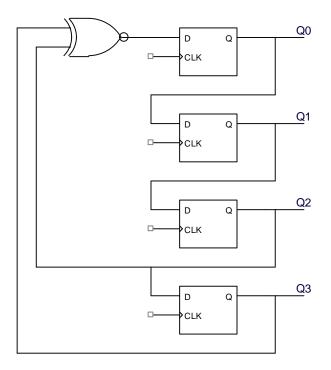

A Linear Feedback Shift Register is a circuit composed of a chain of flip-flops. Each flip-flop output is tied to the next flip-flop input. All are clocked by a common clock. The input to the first flip-flop in the chain is a linear combination of the outputs of one or more of the flip-flops in the chain. See Figure 1 for an example of a LFSR.

#### Figure 1

If the feedback is chosen correctly then a maximal length LFSR is obtained. A maximal length LFSR will cycle through every possible output value over and over – much like a counter except with a scrambled count. The output of a maximal length LFSR appears to be random though it is actually well ordered. The output of a maximal length LFSR will typically pass all statistical tests for randomness. These RNGs are often called PRNGs (pseudo random number generators) or deterministic RNGs because the output stream can be predicted (determined) mathematically.

Xilinx has published an application note that describes maximal length LFSRs and gives topography for up to 168 bits[7]. This application note also contains a bibliography for scholars interested in learning how appropriate feedback taps are chosen.

Unlike security applications and gaming, with simulation it is often more desirable to guarantee a particular distribution of random numbers than to guarantee lack of predictability of random numbers. In these applications a PRNG is an optimal choice. Simulation software frequently implements one or more PRNG distributions in order to model various combinations of timing delays, power fluctuations and other real world phenomena. If the calculation of new random numbers could be accelerated that would improve the speed of simulator and reduce the amount of time needed to run simulations. McCollum and others present a FPGA implementation for accelerating a PRNG and for controlling the distribution of the random number stream in [8].

### 2.4.2 Whitening

According to statistics, the variance of the linear combination of two sets of numbers is equal to the sum of the variances of the individual sets as long as there is no correlation between the two sets[9]. The linear combination can be realized by adding, subtracting or XORing the two sets. Equation 2 illustrates this principle.

## Equation 2 Variance of TRNG XOR PRNG $V(x^{\wedge} y) = V(x) + V(y)$

Since a TRNG is independent of any LFSR based PRNG by virtue of its definition, Equation 2 shows how the output of a TRNG can be statistically improved by XORing it with the output of an LFSR. Combining the output of the TRNG with the output of a LFSR will increase the variance, and hence the randomness of the TRNG. This process is termed whitening and is well known in the practice of cryptology. Cusick and Stanica state "LFSRs can be applied in generating pseudorandom numbers, pseudonoise sequences, fast digital counters, *whitening sequences*, cryptography..."[10].

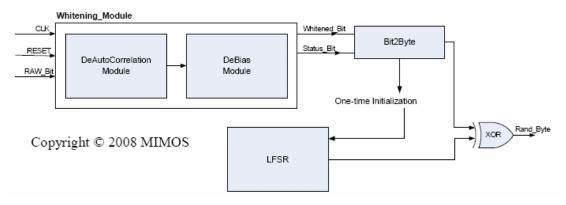

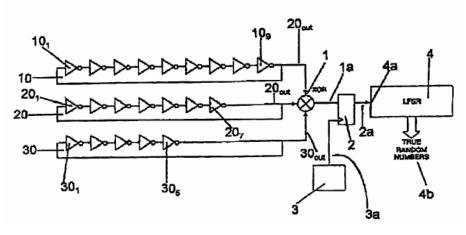

Thamrin, Witjaksono and others describe a RNG whose output is whitened by XORing with a LFSR[11]. Figure 2 below is a reproduction of Figure 7 in this paper for the purpose of illustrating such a circuit.

Figure 2 RNG Using LFSR Whitened By LFSR

Marsaglia presented a paper in 1968 proving that LFSRs do contain some frequency related correlation in the stream of generated numbers[12]. Therefore a TRNG linearly combined with a LFSR would exhibit better statistical properties than either the TRNG or the LFSR alone. Expressed another way, the TRNG could be linearly combined with the PRNG and the resulting combination would be more statistically random than either of the two input streams.

### **CHAPTER 3 BACKGROUND**

### **3.1 Electronic RNG History**

### **3.1.1 Analog RNGs**

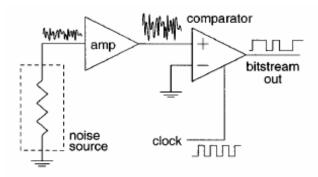

As mentioned before, analog electronic RNGs have been used for some time. Early analog RNG designs are based on amplifying electrical noise then converting the amplified signal to a digital signal. The circuitry for converting to a digital signal can be as simple as a clocked comparator. An example of such a TRNG is given in [13]. The block diagram from this Analog RNG, Figure 1 in [13], is reproduced in Figure 3 for convenient reference.

Figure 3 Simple Analog RNG [9]

If the frequency characteristics of the Analog RNG are inadequate for the application, a whitening filter can be placed either before or after the amplifier. If 32 bit random numbers are required then a 32 bit SIPO (serial in, parallel out) can be used to collect the bits into words. "This is the most popular RNG technique for single-chip or board-level solutions where shielding of the noise source is possible"[13].

Another publication of a similar analog RNG but having digital post processing is given in [14]. The analog noise source for this RNG is not just a resistor; rather it is an

A/D output compared to the reference voltage. Note this analog RNG requires whitening as shown by this quote "The proposed RNG exploits the direct amplification technique, using an accurate offset zeroing system, and, when its output is fed to a XOR-based decorrelating algorithm, the FIPS ... and correlation randomness tests can be easily passed"[14]. This design illustrates an example of whitening RNG output by XORing with a PRNG output.

Each analog RNG starts with an analog noise source and amplifier. This reliance on analog circuitry presents an extra requirement for IC designers – that an analog IC designer be a part of the design team. Two other problems IC designers face with analog RNG designs are: "The lack of adequate shielding from power supply and substrate signals in an IC environment prohibits the exclusive use of this method for IC-based cryptographic systems"[13].

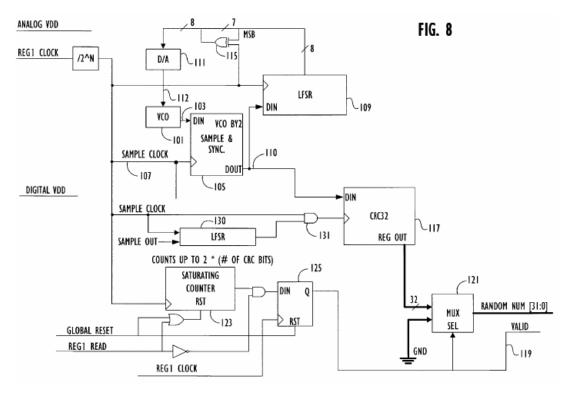

An interesting analog RNG design is given by Walsh and Beisterfeldt in [15]. The block diagram for this RNG is reproduced on the following page. This design utilizes a voltage controlled oscillator (VCO) to generate a waveform with a varying frequency. The control voltage on the VCO is generated by the output of a D/A converter. The input to the D/A converter is generated by a LFSR. The LFSR is clocked by the sample clock and its input bit comes from the VCO output sampled by a D flipflop that shares the same sampling clock as the LFSR. The output of the D flipflop is sent through a CRC32 generator to whiten it. The output of the CRC32 block is multiplexed with ground (0 volts) to form the random number output – 32 bits wide. The multiplexer select is generated by a counter so that 0 is output while the random number is being

formed then the random number is output after it is formed. Variations on this design (fast clock sampled by a much slower clock) have also been published as digital designs.

Figure 4 Oscillator Sampling RNG [15]

#### 3.1.2 Chaos RNGs

RNGs have been designed using chaos theory. An excellent pair of papers on chaos based RNG design has been presented by Stojanovski and Kocarev[16][17]. In the first paper they cover the theory of chaos based RNG design while in the second paper they present an example of a chaos based RNG. The basic theory behind chaos based RNGs is that chaotic circuits tend to operate chaotically when observed at a course grain level, though they are deterministic in microscopic space and by their defining equations. The equation defining a chaos based TRNG appears to be perfectly solvable; however the solution requires infinite calculation resolution and infinite granularity in measurement. Since a digital number is being produced, neither the infinite calculation resolution nor

the infinite measurement granularity is available. Hence the domain must be partitioned into the same number of partitions as the number of digital possibilities. For example, to generate a 32 bit random number it would be necessary to partition the domain into  $2^{32}$ states. Now the generator output will always be in one of the predefined states (it will have one of  $2^{32}$  states which can be conveniently named [0 .. 4,294,967,295]. But since each state represents multiple values, the actual function output may have one of many values. Hence the next state, which can be perfectly calculated using the chaotic equation and the real value, is not visible in the digital world and will appear to be random. A simple example may clarify: Assume a really simple equation,  $X_{n+1} = 2*X_n$ , and a 2 bit RNG. Then we would partition the output domain into the following four states: 0 =[0..0.4999], 1 = [0.5 .. 0.9999], 2=[1.0 .. 1.4999] and 3=[1.5 .. 1.9999]. Table 1 illustrates how the digital output can vary because the actual value varies for this simple equation.

| X <sub>n</sub> | random number | $X_{n+1}=2*X$ | next random number |

|----------------|---------------|---------------|--------------------|

| 0.2499         | 0             | 0.4998        | 0                  |

| 0.2500         | 0             | 0.5000        | 1                  |

| 0.7499         | 1             | 1.4998        | 2                  |

| 0.7500         | 1             | 1.5000        | 3                  |

Table 1 Chaos RNG Example

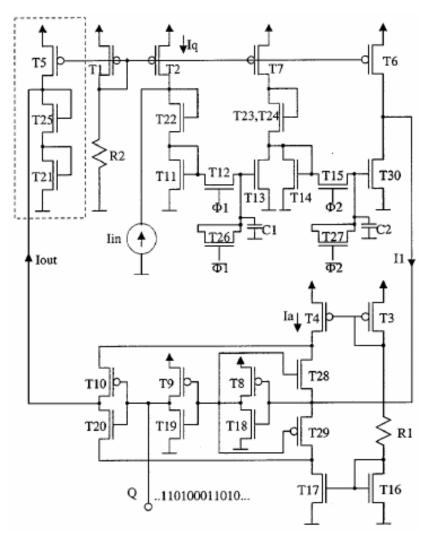

The second paper by these authors presents a RNG based on a single attractor. The structure of this RNG is shown in Figure 4 below. The structure is simple with only 29 MOS transistors and 2 resistors required. However, the presence of the resistors, and of course the balancing of the transistors, will require analog IC design methodology. This RNG cannot be designed using digital methods only.

Figure 5 Chaos Based RNG [17]

### **3.1.3 Digital RNGs**

The first practical digital RNGs were built from LFSRs as covered in Chapter 2. LFSRs produce a deterministic sequence that appears to be random but in fact repeats, at least within the size of the LFSR. For example, a 32 bit LFSR will produce at best a stream of 32 bit numbers that repeat after  $(2^{32} - 1)$  numbers. The exact sequence is controlled by the precise layout of the LFSR; specifically where the taps for feedback are located and whether they represent an XOR or an XNOR. The components of a LFSR are (1) one flipflop per bit and (2) the input to the LSBit is an XOR combination of the

outputs of the LFSR. Chu and Jones have documented not only the LFSR operation but several different architectures in [18].

Predating the formalization of LFSR design, Knuth patented a design for a random number generator. The difference between his design and a traditional LFSR based PRNG is that whether various stages in the shift register are either complemented or not is based on the value being shifted out[19]. Tausworthe[20] and MacLaren and Marsaglia[21] were contemporaries of Knuth who published similar designs. Each of these designs exhibited similar probability distributions.

A variant on a simple LFSR is an LFSR with more bits than are required. One popular choice has been a 128 bit LFSR with only 32 bits of random number used. It is hoped that failure to expose all the bits will keep third parties from predicting the stream of numbers. Nonetheless this design still contains the weakness of a known generating circuit and a pattern that can eventually be traced.

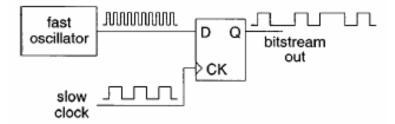

As mentioned before, another popular structure for a digital RNG is a slow clock sampling a fast clock. Some papers refer to this style as oscillator sampling. Figure 2 in [13] shows such a design and is reproduced below in Figure 6.

Figure 6 Oscillator Sampling from Fig2 in [13]

While this design looks deceptively simple, there is often considerable post processing required to whiten the resulting random number stream as it is often impractical to completely isolate the sample clock from the faster oscillator. That is, some common frequency remnants must be whitened out. Some papers refer to this whitening as decorrelating the output.

Another realization of a digital RNG constructed from oscillator sampling is given by [3]. This design features a single D flipflop that handles the sampling. The TRNG output is available but is also used to seed a PRNG. Using a TRNG to seed a PRNG has also become popular because the unpredictability of the TRNG is merged with the statistically desirable qualities of the PRNG. FIPS publication 140-2 specifically recommends using a TRNG to seed a PRNG as the safest way to construct a RNG [22].

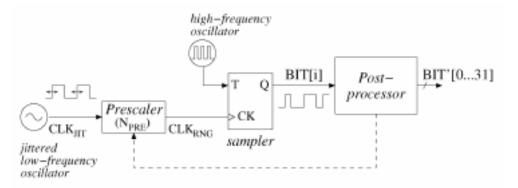

A more complex architecture for an oscillator sampled RNG is given in [23]. Note in this design, illustrated in Figure 7, the low frequency clock is the jittery one while the high frequency oscillator is being sampled. Note also the presence of post processing to whiten the RNG output.

Figure 7 Oscillator Sampled RNG from [23]

### 3.1.4 RNG's Similar To This Work

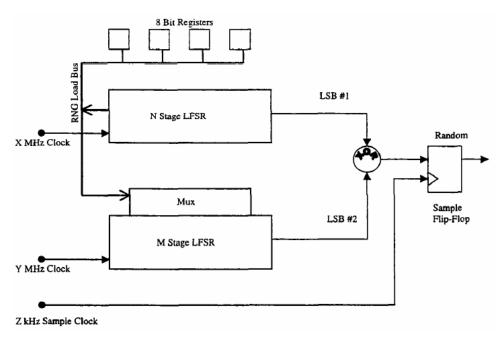

Several designs similar to the one documented herein have been presented. McTaggert and Burson have presented a TRNG based on free running clocks[24]. In this RNG, there are two LFSRs, each clocked by a separate and unrelated free running oscillator. One of the oscillators is crystal based. The other oscillator is not crystal based but its architecture is not disclosed. The LFSRs are of different lengths – one is 39 stages and one is 23 stages. The LSBits of the two LFSRs are XORed together. The output of the XOR is sampled by a flipflop to form the random number. The clock for the flipflop is independent of the two LFSR clocks. Provisions have been made for seeding the random number by preloading parts of the LFSRs. Figure 8 below shows the circuitry for this random number generator.

Figure 8 Multi Clock RNG[24]

A TRNG based on a LFSR clocked by a random clock is presented in [25]. The random clock is composed of the XOR of several unrelated ring oscillators. That signal is then sampled by a flipflop and presented as the clock for a maximal length LFSR. The number of inverters in each of the various ring oscillators is required to be prime relative to the number of inverters in the other ring oscillators in order to lessen the possibility of

the oscillators locking into the same frequency or a related harmonic. The use of at least three oscillators is advised in case one oscillator locks to the bus clock. This concept is interesting because all of the randomness comes from the clock waveform as opposed to any shuffling, scrambling or whitening of the produced bit stream. Figure 9 shows a typical realization of this type of random number generator.

Figure 9 LFSR with random clock[25]

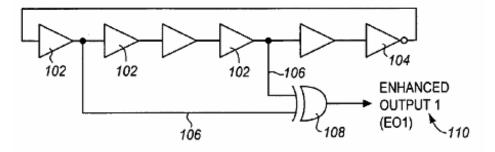

Wilbur has patented another RNG implementation involving multiple ring oscillators[26], Note the presence of two ring oscillators generating randomness. Each ring oscillator has an "enhanced" output which is the XOR of several taps from the ring.

Figure 10 Ring Oscillator With Enhanced Output[26]

Figure 11 illustrates the entire TRNG block diagram as presented in the patent disclosure. The outputs of the ring oscillators drive a delay line. The delay line provides

multiple taps into the Combiner-Sampler. The Combiner-Sampler XORs the taps together. The output of the Combiner-Sampler is XORd with the output of the sample flipflop. The output of the sample flipflop is fed to a second sampling flipflop to produce the random output.

Figure 11 TRNG Based On Scrambled Clocks[26]

### **CHAPTER 4 DIGITAL TRNG DESIGNS**

### 4.1. Overview

The purpose of this research is to develop a digital true random number generator that can be synthesized using standard digital design tools. Developing a digital TRNG composed of standard digital components is important because:

- It alleviates the need for analog circuit design.

- The RNG can be incorporated with other digital cryptographic components.

- No external components are required for FPGA implementations.

A general architecture for digital TRNGs will be developed.

### 4.2 Randomness

### 4.2.1 Randomness In The Analog Domain

Randomness in the analog domain has long been accepted in the form of signal noise. The signal noise is usually present as a small amplitude signal superimposed over the intended signal and may often be seen as tiny vertical perturbations in an oscilloscope trace of the signal. The noise is comprised of several aspects including thermal noise, noise picked up from a power supply and junction noise. Often the frequency characteristic of signal noise is such that a suitable RNG can be obtained by simply subtracting the signal then scaling the noise. Otherwise one or more frequencies may be filtered out of the noise source. At that point the noise can be sampled and converted to digital values as required.

### **4.2.2 Randomness In The Digital Domain**

In the digital domain, every effort is usually made to prevent randomness in amplitude. Each piece of information is represented by a bit which is resolved to a "0" or a "1". The clock rate for a digital circuit is usually chosen so that all transitions from "0" to "1" or from "1" to "0" are allowed to complete between clocks. Hence digital circuits are designed to be immune to amplitude noise. Many digital clock signals are designed to be quite repeatable to enable not only a predictable period for the afore-mentioned transitions but also to enable accurate timing. Often the clock signal is fed back through a crystal to restrict the frequency of operation. Such crystal controlled oscillators can be accurate to 20 ppm (parts per million) depending on how exactly the mechanical crystal properties are controlled when the crystal is cut. There is very little noise in such a crystal controlled clock source and hence little randomness to recover in either the amplitude or the period of oscillation.

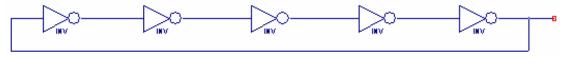

A noisy oscillator may be formed by connecting inverters in series then connecting the last output to the first input to form a ring. Each inverter alters the phase of the signal by 180 degrees so in order for the circuit to oscillate, there must be an odd number of inverters in the ring. Such an oscillator is called a ring oscillator and oscillates with a period equal to twice the total propagation delay around the ring. Figure 12 is an example of a ring oscillator.

Figure 12

These ring oscillators require very little chip area at only two transistors per CMOS inverter stage and are easy to build with either schematics or HDL. Ring

oscillators are also susceptible to substantial perturbations in the oscillation period called jitter which can easily be several percent of the nominal oscillator period[27]. This jitter makes a ring oscillator a reasonable source of randomness. A different method will be needed to capture this randomness since it is in the clock period rather than in the signal amplitude, however. Where the noise source in an analog TRNG would be visible as vertical perturbations on an oscilloscope trace, the noise source in a digital TRNG would be visible as horizontal perturbations on an oscilloscope trace.

#### 4.2.3 Distilling Randomness From Clock Jitter

Distilling randomness from an analog noise source is straightforward. Use a sample and hold to freeze the noisy signal long enough to perform a digital conversion to the required number of bits. Distilling randomness from digital clock jitter is more complex. If a straight conversion, analogous to the noise source conversion, is performed then the converting circuit would need to resolve to  $(2^N)$  values where N is the number of bits required for the random number. The resolution would have to occur in one (maximum period – minimum period) time and that would require a counter with a count interval as shown in equation 3.

# Equation 3 $CountInterval = \frac{(MaxPeriod - MinPeriod)}{2^{N}}$

Therefore if the change in period is 10 nanoseconds and the random number is 32 bits, the counter interval would be  $2.3 \times 10^{-18}$  seconds. Direct conversion to obtain the random number is not possible using current technology. Hence it will be necessary to gather randomness a few bits at a time and build it up into a significant word size.

#### 4.2.4 Range of Numbers and Paths Through The Range

A digital RNG generates numbers which are based on powers of 2. The number of bits in the generated number defines the range of the generated number since each bit can have one of two possible values, 0 or 1. The number of possible values that can be represented is  $2^{N}$  where N is the number of bits. Thus the range of numbers that can be generated by a RNG having N bits is  $[0 ... 2^{N}-1]$ . A digital RNG is constrained to generate a random number within this specified range. For instance, a four bit RNG can only generate numbers from the set [0, 1, 2, 3, 4, 5, 6, 7, 8, 9, 10, 11, 12, 13, 14, 15].

When arithmetic operations result in carries beyond the most significant bit (MSB) position these carries are typically ignored. When a RNG would attempt to generate a number outside of the allowed range, a modulo operation is realized to bring the number back within range. For example, if +1 is added to the maximum count for a four bit RNG, the resulting number would be beyond the range that can be expressed in four bits. So the carry beyond the MSB is ignored and the result of 15 + 1 is 16 MOD 16 or 0.

A generating function traverses a path through the range of numbers generated. A very trivial example is a counter. On each cycle "1" is added to the number. The sequence generated is  $\{0, 1, 2, 3, 4, ..., (2^{N}-1), 0, 1, 2, ...\}$ . Notice the modulo operation returns the generator output back to the allowed range at 0. The particular example of a counter has some interesting properties:

- Each number in the range of numbers is generated no numbers are skipped.

- The frequency of each generated number is the same; that is, a "2" is generated just as often as a "3".

• The pattern or sequence of numbers generated is always the same. Expressed another way, the counting generator traverses the same path through the range of numbers over and over.

Not all functions share these properties. For instance doubling, or multiplying by two, also traverses a path through the range of numbers. But unlike counting, doubling will not generate every value in the range – only the powers of 2. Any function used to construct a RNG should be capable of generating all numbers in the range.

There are many functions that can generate all the numbers in the range. Instead of a counter, adding any constant that is relatively prime with the size of the range (the modulus) will generate every value in the range. The proof is straightforward. Let a be the relatively prime constant used to generate the range and m (the size of the range) be the modulus. Then starting at zero and adding a each time followed by a modulo operation, the results are shown in Equation 4. Note there would be a total of m values generated – one value generated for each value in the range.

Equation 4 Generating Range Using a Relatively Prime Constant  $((0*a) + a) \mod m = a$   $((1*a) + a) \mod m = (2*a) \mod m$   $((i*a) + a) \mod m = ((i+1)*a) \mod m$

Each calculated number must fall in the inclusive range [0 to (m-1)] by definition of the modulus operation. There are as many calculated numbers as there are values in the range. Each calculated number must be unique as stated by the Modified Cancellation Law for Congruences illustrated by Equation 5. Therefore all values in the range are generated by successively adding a constant that is relatively prime with the modulus.

#### **Equation 5 Modified Cancellation Law**

$$((i \bullet a) \mod m) = ((j \bullet a) \mod m)$$

$$\therefore i = j$$

Since i = j then every unique value of  $i \in [0 ... (m-1)]$  must generate a unique number within the range of possible numbers. A simple example is easily computed for the case of a 3 bit range (m = 8) and a relatively prime a = 3 as shown by Equation 6.

#### **Equation 6 Example of Relatively Prime Generation**

$(0*3) \mod 8 = 0$ (1\*3) \mmod 8 = 3 (2\*3) \mmod 8 = 6 (3\*3) \mmod 8 = 1 (4\*3) \mmod 8 = 4 (5\*3) \mmod 8 = 7 (6\*3) \mmod 8 = 2 (7\*3) \mmod 8 = 5

### 4.2.5 Capturing Randomness Using Divergent Paths

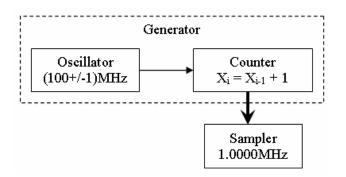

In order to explore the concept of randomness within a generator it is necessary to make an abstraction, separating the generator and the sampler. If the sampling is not at perfectly uniform intervals then it will affect the apparent randomness of the generator. Normally it is expected any randomness within the sampler will increase the apparent randomness of the generator. Therefore this paper postulates a random number generator producing random numbers and a sampler reading random numbers at fixed intervals. If a RNG is constructed from a generating function such as a counter that is clocked by a noisy source such as a ring oscillator then some slight amount of randomness may be observed in the following way. Let the generator be a free running counter clocked by a ring oscillator at an average rate of 100MHz but with a noise of +/- 1MHz and let the sample interval be 1 microsecond (1MHz) as shown in Figure 13.

Figure 13 Simple Generator and Sampler

The counter runs at 100MHz on average. But at any given sample, the generator could have run at 99MHz, 100MHz or 101MHz because of the noisy oscillator driving the counter. Now, ignoring terminal count issues, the value of this generator at any sample time can be predicted within 3 counts by multiplying the number of sample intervals times the average oscillator frequency divided by the sample frequency. Although the count can be predicted within 3 counts, it cannot be predicted exactly – hence there is some randomness in the value. For example, on the fifth sample the value of this generator could be 499, 500 or 501. On the seventh sample the value of this generator would be (n x 100) +  $\{-1, 0, 1\}$ . There is a small amount of uncertainty about the value that is due to the noisy oscillator in the generator. That uncertainty in the generator needs to be collected and preserved. A simple counter cannot preserve it. In fact no generator that

has a single path through the range of generated numbers can preserve this uncertainty. The value at any point in the future may be found be interpreting the generator once for each sample interval and then adding the uncertainty to the final value. In general, the value at the Nth sample from this type of generator is given by Equation 7.

#### **Equation 7 Values From a Single Path**

$R_{0} + R_{1} + R_{2} + R_{3}... = (N \bullet \Delta R_{AVG}) + U$ where  $U \in [-1,0,+1]$

The uncertainty is not preserved across multiple samples as is shown by Equation 7. All of the uncertainty or randomness can be considered independent of how many samples were taken. In order to create a TRNG or True Random Number Generator, a way is needed to capture and store the randomness generated at each sample. Capturing and storing the randomness at each sample can be accomplished by altering the path that the generator traverses through the range of possible values at each sample. If the path is altered at each sample then the state of the generator, including whatever randomness is captured, can be preserved in the output value. Figure 14 is a visualization of how altering the path of the generator at each sample can preserve randomness.

Figure 14 Altering Path to Preserve Randomness

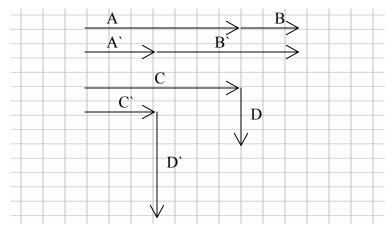

Notice in Figure 14 if the relative lengths of segments A and B are reversed, as shown with segments A' and B', then the end result is the same – that is, the variations in length have no noticeable effect on the final position because there is only a single path. If the path is altered between segments, as shown with segments C and D and the alternate segments C' and D', then the final result is different. The variations in length of the individual segments are preserved by the alternate path. It is necessary to vary the path at each sample in order to preserve the randomness at each sample.

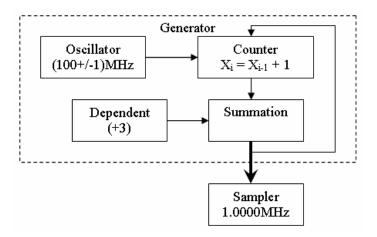

In order to affect a new path at each period, the generator must employ a second function independent of the generation function. In order to illustrate this requirement, consider two cases. The first case will involve a simple generating function, +1 and at every sample a dependent function, +3. The dependent function is derived from the independent function by multiplying the independent function by 3. See Figure 15 for a block diagram of the generator with a dependent function added. Another more subtle change is also required to the generator. The number read by the sampler must be re-introduced to the generator as a counter preload. Randomness is captured by feeding it back into the system so the sampled value is loaded into the counter each time it is read.

**Figure 15 Generator With Dependent Function**

This block diagram is represented by Equation 8 below where  $R_0$  is the first random number,  $R_1$  is the second,  $R_2$  the third, etc. T is the number of sample periods,  $\Delta R_{AVG}$  is the average value of the change in random number (the average number of clocks) per sample period and U is the uncertainty at each sample. The equation says each random number is the product of the average number of clocks per sample times the number of samples plus the uncertainty. The uncertainty term, U, is outside the summation indicating that the uncertainty is not captured at each sample period.

#### **Equation 8 Uncertainty From a Single Path**

$R_{0} + R_{1} + R_{2} + R_{3}... = (T \bullet (\Delta R_{AVG} + 3)) + U$  $R = (\sum_{1}^{T} (100 + 3)) + U$ where  $U \in [-1, 0, +1]$

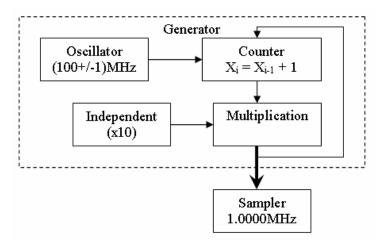

The second case will involve the same simple generating function, +1, but paired with the function x10 as shown in the block diagram in Figure 16. The function x10 is independent of the generating function +1. Independent here is used in the algebraic sense: that is, there is no correlation between  $\{X_2 = X_1 + 1\}$  and  $\{X_2 = X_1 \times 10\}$ .

**Figure 16 Generator with Independend Function**

Equation 9 describes the generator in Figure 16.  $U_T$  is the uncertainty at sample T. Unlike the generator with a dependent second function, the exact value of U at the sample instant is required to compute the next random number.

### **Equation 9 Uncertainty From Multiple Path**

$$R = \sum_{1}^{T} ((100 + U_T) * 10)$$

where  $U_T \in [-1, 0, +1]$

In Equation 9, the uncertainty cannot be factored out of the summation hence the randomness is collected from each sample period. The second function in the second case, times 10, is independent of the first function, +1. The uncertainty cannot be factored out because the final value generated depends on what the uncertainty was at the sample instant as well as how long it has been since the last sample. Hence randomness is captured from each sample. Table 2 shows two iterations of output from the generator and the result of reversing the order of the oscillator fluctuations. Once the independent second function is added, the random number is different based on the order of the oscillator fluctuations. Hence the randomness has been captured by the generator.

| Osc Freq | Counter | RN    | Osc Freq | Counter | RN    |

|----------|---------|-------|----------|---------|-------|

| 101      | 101     | 1010  | 99       | 99      | 990   |

| 99       | 1109    | 11090 | 101      | 1091    | 10910 |

**Table 2 RN Generated Versus Oscillator Frequency**

The independent function in the generator alters the path of the generating function by moving the generated value to a new point in the range. Since the uncertainty is present at each period, it is the uncertainty that is being preserved by relocating the value at each period. Since the value is relocated, a discontinuity is introduced at each period. The path of the generation function is forced to diverge from its normal trajectory through the range of generated values. A simple example will illustrate this process.

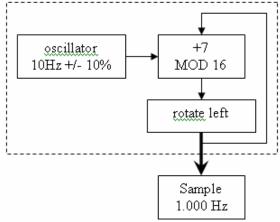

# 4.2.6 Simple Divergent Path RNG

Assume a 4 bit random number, implying a range of [0 ... 15], a generating function of +7, a secondary function of x 2, an oscillator for the generation circuit running at 10 Hz average with +/- 10% noise and a sample frequency of 1 Hz. At this point it is necessary to make a few modifications for the sake of the actual implementation. First, since there are 4 bits holding the value, math will be done Modulo 16 as shown in Equation 10.

# Equation 10 Modulo 16 (15+1)MOD16 = 0

Second, a straight multiply by 2 is problematic for two reasons; (a) it tends to push digits beyond the 4 bit limit and (b) it removes randomness from bit0. Instead the multiply function will be replaced by a rotate left function. This will preserve all the generated bits and has no tendency to push bits beyond the 4 bit limit. With these two concessions to the requirements of digital synthesis, the state machine for the example RNG is shown in Figure 17.

Figure 17

Assuming the reset value is 0, Table 3 shows the first two iterations of this RNG.

| Iteration | (+7 x {9,10,11}) MOD 16      | Rotate Left                  |  |

|-----------|------------------------------|------------------------------|--|

| 0         | 0                            | 0                            |  |

| 1         | (15, 6, 13)                  | (15, 12, 11)                 |  |

| 2         | {(6,12,2),(11,14,1),(2,4,6)} | {(12,9,4),(7,13,2),(4,8,12)} |  |

Table 3

The middle column is calculated by multiplying +7 times the number of oscillations in the sample period (9, 10 or 11) then taking MOD 16 of the resulting number. See Figure 18 for examples of this calculation.

> (9x7)MOD16 = 15(10x7)MOD16 = 6(11x7)MOD16 = 13

#### **Figure 18 Example Calculations**

The right column is just a Left Shift of the middle column with bit3 rotated into bit0. See Figure 19 for examples of this calculation.

15 = %1111RotateLeft = %1111 = 15 6 = %0110RotateLeft = %1100 = 12 13 = %1101RotateLeft = %1011 = 11Figure 19 Example Rotate Left Calculations

Note that if there were no uncertainty, only one value of each three-tuple would be generated. Since the oscillator jitter is assumed to be symmetrically distributed about the average value, the middle value of each three-tuple would be generated in the absence of jitter. The produced sequence would be [0, 12, 13]. Figure 20 illustrates the divergent paths generated by this RNG.

Figure 20

The paths diverge from each point at the rate of 3 paths per point because the clock has an uncertainty of +/- 1 counts per period. Hence there are three possible values for each generated number. The independent function ROTATE-LEFT preserves the randomness from each path.

# 4.2.7 Divergent Path Formulae

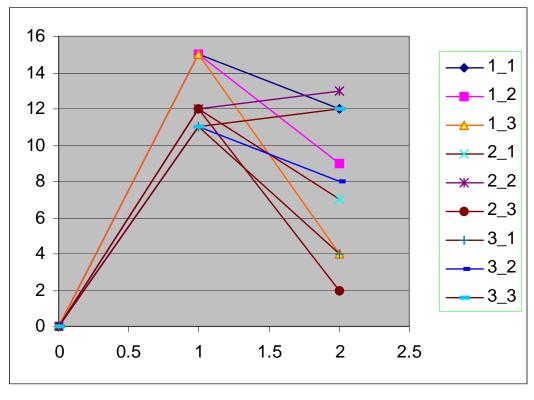

As shown in Figure 20, there are three possible paths at each point of divergence. After the first iteration there are 3 possible values. After the second iteration there are 9 possible values. Should a third iteration be performed there would be 27 different values calculated. At each iteration the number of possible values becomes multiplied by the divergence from each point. By inspection the total number of possible values after some arbitrary number of iterations is given by Equation 11. **Equation 11 Number of Possible Values**

$$N = D^i$$

where N = number of values, D = divergence (number of paths from each point) and i = iterations.

Another observation may be made about this simple generator. By the third iteration, the number of possible values that can be calculated is  $3^3 = 27$ . The range of values for a 4 bit generator is only  $2^4 = 16$ . So the number of values that can be calculated exceeds the range of the generator. That is, any generated value must be in the range [0 .. 15], a total of 16 possible values. But the total number of calculations which must be performed to guarantee that the actual generated number has been calculated on the third iteration away is 27 according to Equation 11. At this point, calculating the expected output of the generator becomes futile as there are more calculations required than simply listing the possible values. Hence by Chaitin's criterion for randomness, that no simpler representation for the set exists other than listing the set, this generator will mimic truly random behavior on the third iteration of values [28]. The number of iterations necessary to mimic true random number generator behavior can be derived from Equation 11 by setting it equal to the range of possible values,  $2^N$ , as shown in Equation 12. That is, after how many iterations does the number of possible values equal the size of the range?

#### **Equation 12 Iterations When RNG Appears Random**

$$2^{N} = D^{i}$$

$$N \log(2) = i \log(D)$$

$$i = \frac{N \log(2)}{\log(D)}$$

where N = number of bits (4) and D = divergence (3) at each point. The term on the top left,  $2^N$ , represents the range of values – or for Chaitin's criterion the size of a list of all the possible values. The term on the right, D<sup>i</sup>, represents the number of values which must be calculated to guarantee prediction of the random number generated with a divergence D on the i<sup>th</sup> iteration. For the simple RNG example with D = 3 and N = 4, this equation yields i = 2.5 in agreement with the empirical measurement of 3 (see the plot in Figure 20). Hence for a divergence of 3, prediction of more than two samples into the future is futile as the list of calculated values is longer than the list of possible values.

#### **4.2.8 Differences From Other Architectures**

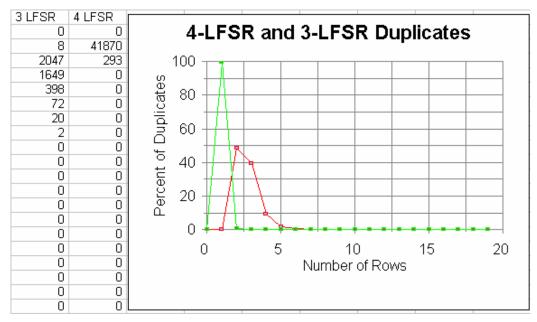

The Multi-Clock Generator presented by McTaggart and Burson[24] is an example of the simplest form of a divergent path RNG. The two LFSRs, clocked by different clocks, represent two functions. The two functions are independent since they are each maximal length and the numbers of bits of the two LFSRs are relatively prime. The divergence for this particular generator would be 2 as there are two independent operations.

The RNG presented by Oerlemans[25] is quite different from a divergent path RNG. Oerlemans has presented a single LFSR clocked by an unpredictable clock so that the stream of numbers is not predictable. But the randomness introduced by the clock uncertainty is not preserved – each sample is only as random as the clock frequency which is derived from the XOR of the oscillators. The average and standard deviation of the clock frequency of this generator could be calculated by observing enough generated numbers. Then the value at any time could be predicted to fall within a subset of the range of numbers. Hence there is not necessarily any point in the future at which prediction of the output value becomes futile. The RNG presented by Oerlemans is not guaranteed to ever meet Chaitin's criterion for randomness. A divergent path generator will capture the randomness from each sample. The farther into the future prediction is attempted, the more randomness the generator has captured. As shown in Equation 12 above, there is a point at which prediction of the output from a divergent path generator becomes futile. Hence a divergent path RNG will always meet Chaitin's criterion for randomness at some future sample. The number of samples at which the RNG becomes random by Chaitin's definition is governed by the number of independent functions comprising the RNG. More independent functions means less samples before the RNG achieves randomness.

# CHAPTER 5 DIVERGENT PATH ARCHITECTURES 5.1 Adder-Shifter Based TRNG Architecture

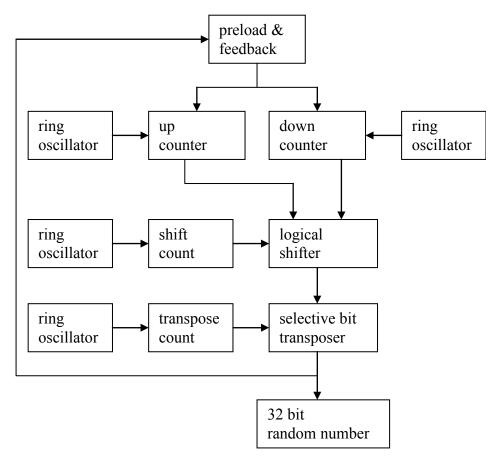

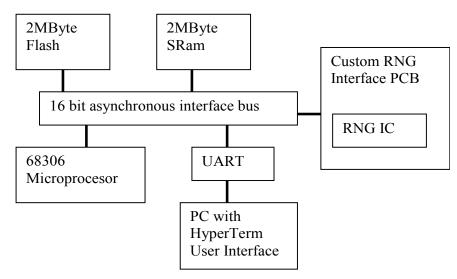

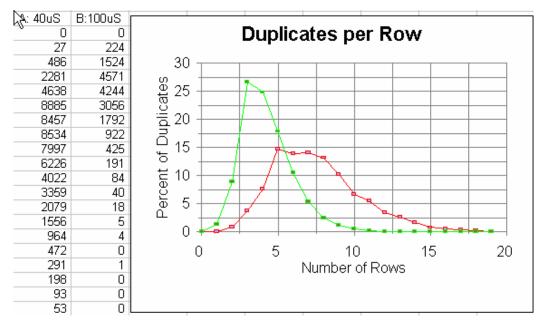

In chapter 4 a simple example for a TRNG was presented. A free-running adder was used to generate bits and a shifter was used at sample intervals to capture and preserve randomness. This type of TRNG can be abstracted to a general architecture consisting of an adder for bit generation followed by a shifter for randomness preservation. A TRNG that has an adder-shifter architecture will be referred to as an ASTRNG in the remainder of this paper. The ASTRNG illustrated in Figure 21 has two additional features: (1) a transposing unit attached after the shifter and (2) the adder is split into two counters.

Figure 21 Block Diagram of ASTRNG

The bit generation for this ASTRNG has been configured as a 16 bit up counter and a 16 bit down counter for two reasons. First, splitting the counter reduced the time required to produce every possible value from  $2^{32}$  clocks to  $2^{16}$  clocks. Second, it helps balance the number of high bits (1's) with the number of low bits (0's). Each counter has its own noisy ring oscillator. Each counter runs all the time. Each counter has an associated latch that is not shown in the block diagram in order to avoid confusion. All four counters are latched when a value is read from the ASTRNG. The counters continue to run and the latched counts are used for creating the value read. This architecture avoids synchronizing the ring oscillators at every read. Whenever a random number is read, the random number is fed back into the counters using the preload function. Following the bit generation stage is the shift stage for preserving randomness. This stage is a 32 bit barrel shifter. The shift count is not fixed; rather a free running 5 bit counter is clocked by a third noisy ring oscillator as shown. Whenever a value is read from the ASTRNG, the shift count is latched and the value from the bit generator is rotated by that count. As discussed earlier, bits are rotated left and the leftmost bit (b31) is rotated back into the rightmost bit (b0) position. The final stage in this ASTRNG transposes the individual bits in the shifted value. There are four transpositions implemented. A free running 2 bit counter, clocked by a fourth noisy ring oscillator, is latched whenever a value is read from the ASTRNG. The latched 2 bit count determines which transposition is applied to the value. Table 4 illustrates how the bits are transformed according to the transpose count. The four different transpositions implemented are: (1) 32 bit, (2) 16 bit, (3) 8 bit and (4) 4 bit.

| output bit  | count=00 | count=01    | count=10    | count=11 |

|-------------|----------|-------------|-------------|----------|

|             | 31       | 15          | 7           |          |

| 0           | 30       | 14          | 6           | 32       |

| 2           | 29       |             | 5           | 1        |

|             | 28       | 13<br>12    | 4           | 0        |

| 3<br>4<br>5 | 27       | 11          | 3           | 7        |

| 5           | 26       | 10          | 3<br>2<br>1 | 6        |

| 6           | 25       | 9           | 1           | 5        |

| 7           | 24       | 8           | 0           | 4        |

| 8           | 23       | 7           | 15          | 11       |

| 9           | 22       | 6           | 14          | 10       |

| 10          | 21       | 5           | 13          | 9        |

| 11          | 20       | 4           | 12          | 8        |

| 12          | 19       | 3           | 11          | 15       |

| 13          | 18       | 3<br>2<br>1 | 10          | 14       |

| 14          | 17       | 1           | 9           | 13       |

| 15          | 16       | 0           | 8           | 12       |

| 16          | 15       | 31          | 23          | 19       |

| 17          | 14       | 30          | 22          | 18       |

| 18          | 13       | 29          | 21          | 17       |

| 19          | 12       | 28          | 20          | 16       |

| 20          | 11       | 27          | 19          | 23       |

| 21          | 10       | 26          | 18          | 22       |

| 22          | 9        | 25          | 17          | 21       |

| 23          | 8        | 24          | 16          | 20       |

| 24          | 7        | 23          | 31          | 27       |

| 25          | 6        | 22          | 30          | 26       |

| 26          | 5        | 21          | 29          | 25       |

| 27          | 4        | 20          | 28          | 24       |

| 28          | 3        | 19          | 27          | 31       |

| 29          | 2        | 18          | 26          | 30       |

| 30          | 1        | 17          | 25          | 29       |

| 31          | 0        | 16          | 24          | 28       |

**Table 4 Transposer Bit Transpositions Per Count**

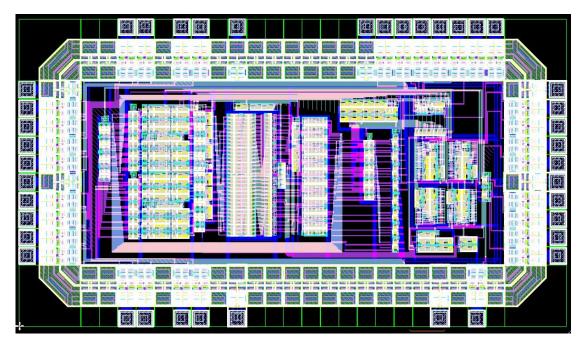

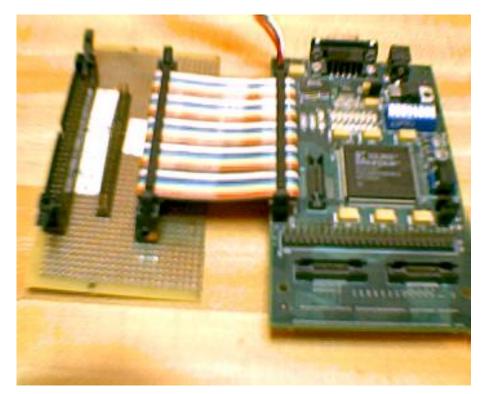

This ASTRNG was constructed using the Mentor Graphics chip design tools. The resulting design was translated to a GDS-II plot file and that file was sent to MOSIS for fabrication in AMI05 technology. Five (5) of the chips were bonded and packaged in the typical MOSIS 40 pin ceramic DIP package and returned from MOSIS. The five chips

were tested for functional operation and current requirements and the results sent back to MOSIS. Then the five TRNG chips were tested for divergence and shown to be truly random. Finally bit streams were gathered from each of the five TRNG chips and tested using the NIST 800-22 tests for randomness.

## **5.2 Design of the ASTRNG Chip**

#### 5.2.1 ASTRNG Design Methodology

The architecture of this TRNG is shown in Figure 21. The ASTRNG design was begun using VHDL. However, when problems were encountered with the synthesis tool, Leonardo Spectrum, the VHDL design was abandoned in favor of a digital schematic design based on Mentor Graphics Design Architect, abbreviated DA. DA comes with a generic AMI05 parts library. The library contains most commonly used gates, latches and flipflops. This library was used in the ASTRNG design to minimize the amount of time spent designing individual gates and allow concentration on the ASTRNG layout and testing.

Fortunately switching to schematic design did not decrease the ability to test individual blocks as they were completed. AccuSim was used to verify operation of each component as it was designed. As each block layout was completed, a spice extraction was performed and the resultant circuit was simulated using MachTA. While this represents a lot of time spent designing and running tests, such attention to detail at the block design level made the final layout much easier to test and gave a high degree of confidence the resulting IC would work.

# **5.2.2 ASTRNG Development**

This ASTRNG architecture required substantial development effort. First a more detailed block diagram was prepared. The transistor count in each of these blocks was estimated using Leonard Spectrum output statistics with no attempts at optimizing. Then each block was constructed using the following methodology:

- a) Draw a schematic using Design Architect

- b) Simulate the schematic using Accusim

- c) Layout the schematic using IC Station

- d) Verify the layout using LVS (Layout Versus Schematic)

- e) Check the layout using DRC (Design Rules Check)

- f) Perform a parasitic extraction to properly model the fabricated part

- g) Verify correct operation using MachTA on the extraction

There were a number of blocks to be designed including those shown in the block diagram as well as some that were required but not shown in the block diagram. The blocks that were designed as a part of this project are tabulated in Table 5.

| Name             | Number | X Size | Y Size |

|------------------|--------|--------|--------|

| Input Mux        | 1      | 200    | 1100   |

| Up Counter       | 1      | 796    | 1080   |

| Down Counter     | 1      | 796    | 1080   |

| Logical Shifter  | 1      | 1000   | 2200   |

| Transposer       | 1      | 600    | 2200   |

| Ouput Mux        | 1      | 160    | 2000   |

| Latch16          | 1      | 193    | 1050   |

| Control Register | 1      | 992    | 360    |

| Ring Oscillator  | 4      | 500    | 600    |

| 5 Bit Counter    | 1      | 631    | 360    |

| 2 Bit Counter    | 1      | 320    | 240    |

| Counter Latch    | 2      | 322    | 970    |

**Table 5 Blocks In ASTRNG**

A down counter bit slice and two versions of an up counter bit slice (one with a preload and one without) were designed using AMI05 standard cells. Sixteen up counter bit slices with preload were combined in the up counter while sixteen down counter slices were combined in the down counter. A small amount of logic was added to each counter to permit synchronous preload.

The logical barrel shifter was prepared in a different manner. Since an instantaneous multiple bit shift was required, a block of five multiplexers implemented each bit. Then a five bit count selected which of the multiplexer inputs were selected. The five bit counter was built from five of the non-preload up counter bit slices mentioned above. The logical shifter posed the greatest routing challenge of any module because of the large number of interconnects.

The transposer was designed as a 32 bit wide four to one multiplexer. As such it could be broken down into bit slices of a 4 to 1 multiplexer. Then thirty-two of the bit slices were combined along with some control logic to create the transposer.

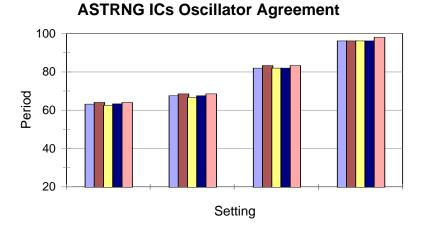

As shown in the block diagram, there were four ring oscillators required for this design. Each ring oscillator had a different number of stages. Each ring oscillator is controllable to some extent so the frequency of oscillation can be altered by switching inverter stages in and out of the design. The fewer the stages, the faster the ring oscillates. More stages cause the ring to oscillate slower. The rings were designed to permit frequency shifting among four different oscillation frequencies. In order to permit changes to the topology during operation, the changes had to be synchronized to the operation of the ring. Digital control of the ring oscillators including frequency shifting is covered in more detail in this paper[29].