### Virginia Commonwealth University VCU Scholars Compass

Theses and Dissertations

Graduate School

2010

# Embedded Processor Selection/Performance Estimation using FPGA-based Profiling

Fadi Obeidat Virginia Commonwealth University

Follow this and additional works at: http://scholarscompass.vcu.edu/etd Part of the <u>Engineering Commons</u>

© The Author

Downloaded from http://scholarscompass.vcu.edu/etd/2232

This Dissertation is brought to you for free and open access by the Graduate School at VCU Scholars Compass. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of VCU Scholars Compass. For more information, please contact libcompass@vcu.edu.

#### School of Engineering

#### Virginia Commonwealth University

This is to certify that the dissertation prepared by Fadi Obeidat entitled EMBEDDED PROCESSOR SELECTION/PERFORMANCE ESTIMATION USING FPGA-BASED PROFILING has been approved by his committee as satisfactory completion of the dissertation requirement for the degree of Doctor of Philosophy

Robert Klenke, Ph.D., Committee Chair, Department of Electrical and Computer Engineering, School of Engineering

Mike McCollum, Ph.D., Dept. Department of Electrical and Computer Engineering, School of Engineering

Afroditi V Filippas, Ph.D., Department of Electrical and Computer Engineering, School of Engineering

Kayvan Najarian, Ph.D., Department of Computer Science, School of Engineering

Vojislav Kecman, Ph.D., Department of Computer Science, School of Engineering

Date

# EMBEDDED PROCESSOR SELECTION/PERFORMANCE ESTIMATION USING FPGA-BASED PROFILING

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy at Virginia Commonwealth University.

by Fadi Obeidat

Director: Robert Klenke ASSOCIATE PROFESSOR, DEPARTMENT OF ELECTRICAL AND COMPUTER ENGINEERING

> Virginia Commonwealth University Richmond, Virginia July, 2010

#### Abstract

In embedded systems, modeling the performance of the candidate processor architectures is very important to enable the designer to estimate the capability of each architecture against the target application. Considering the large number of available embedded processors, the need has increased for building an infrastructure by which it is possible to estimate the performance of a given application on a given processor with a minimum of time and resources. This dissertation presents a framework that employs the softcore MicroBlaze processor as a reference architecture where FPGA-based profiling is implemented to extract the functional statistics that characterize the target application. Linear regression analysis is implemented for mapping the functional statistics of the target application to the performance of the candidate processor architecture. Hence, this approach does not require running the target application on each candidate processor; instead, it is run only on the reference processor which allows testing many processor architectures in very short time. To my wife, my son, and the family

## **Table of Contents**

| CHAPT | TER 1 INTRODUCTION                                           | 1  |

|-------|--------------------------------------------------------------|----|

| 1.1.  | OVERVIEW                                                     | 2  |

| 1.2.  | MOTIVATION                                                   | 3  |

| 1.3.  | CHALLENGES                                                   | 4  |

| 1.4.  | PROBLEM STATEMENT                                            | 10 |

| 1.5.  | CONTRIBUTION                                                 | 11 |

| 1.6.  | DISSERTATION ORGANIZATION                                    | 14 |

| CHAPT | TER 2 PERFORMANCE MODELING                                   | 15 |

| 2.1.  | PERFORMANCE EVALUATION FOR PROCESSOR DESIGN                  | 17 |

| 2.2.  | Performance Evaluation for Embedded Systems Design           | 22 |

| 2.3.  | EMBEDDED PROCESSOR SELECTION BASED ON PERFORMANCE ESTIMATION | 26 |

| 2.2   | 3.1. Traditional Techniques                                  | 27 |

| 2     | 3.2. Analytical Techniques                                   | 29 |

| 2.4.  | SUMMARY                                                      | 34 |

| CHAPT | TER 3 PROBLEM ANALYSIS                                       | 36 |

| 3.1.  | BACKGROUND                                                   | 36 |

| 3.2.  | THEORETICAL ANALYSIS                                         | 40 |

| 3.3.  | APPLICATION FUNCTIONAL STATISTICS                            | 48 |

| 3.4.  | LINEAR REGRESSION                                            | 49 |

| 3.5.  | PREDICTION MODELS, RELATED WORK                              | 52 |

| 3.6.  | SUMMARY                                                      | 54 |

| CHAPT | TER 4 REFERENCE MODEL AND FPGA-BASED PROFILING               | 55 |

| 4.1.  | REFERENCE MODEL SPECIFICATIONS                               | 55 |

| 4.2.  | Profiling                                                    | 57 |

| 4.3.  | FPGA-BASED INSTRUCTION-LEVEL PROFILING                       | 60 |

| 4.4.  | SUMMARY                                                      | 66 |

| CHAPT | TER 5 EXPERIMENTS AND RESULTS                                | 67 |

| 5.1.  | EXPERIMENT SETUP                                             | 67 |

| 5.    | 1.1. Target Platforms                                        | 67 |

| 5.    | 1.2. Algorithms and Benchmarks                               | 71 |

| 5.    | 1.3. Floating-Point Implementation                           | 73 |

| 5.2.  | RESULTS                                                      | 73 |

| 5.                   | 2.1. Ordinary Least Squares vs. Robust Fit                             | 73             |

|----------------------|------------------------------------------------------------------------|----------------|

| 5.                   | 2.2. Absolute Performance Estimation                                   | 75             |

| 5.                   | 2.3. Relative Performance Estimation                                   | 85             |

| 5.                   | 2.4. Discussion                                                        | 90             |

| 5.3.                 | SUMMARY                                                                | 91             |

| CHAP                 | TER 6 CONCLUSIONS                                                      | 92             |

|                      |                                                                        |                |

| CHAP                 | TER 7 FUTURE WORK                                                      | 93             |

| <b>CHAP</b><br>7.1.  | T <b>ER 7 FUTURE WORK</b><br>Different Statistical Analysis Approaches |                |

| 7.1.                 |                                                                        | 93             |

| 7.1.<br>7.2.         | DIFFERENT STATISTICAL ANALYSIS APPROACHES                              | 93<br>94       |

| 7.1.<br>7.2.<br>7.3. | DIFFERENT STATISTICAL ANALYSIS APPROACHES<br>MULTI-CORE PROCESSORS     | 93<br>94<br>94 |

## **List of Figures**

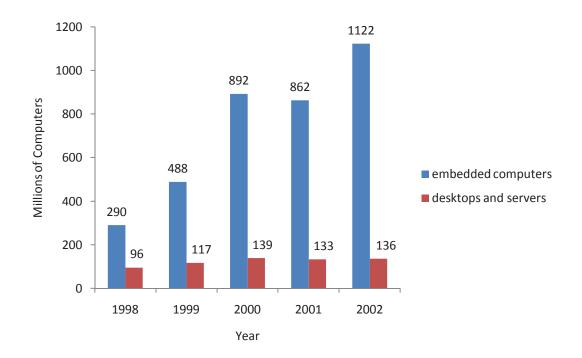

| Figure 1.1. The number of embedded processors sold between 1998 and 2002 comp     | ared |

|-----------------------------------------------------------------------------------|------|

| to desktop and server processors                                                  | 2    |

| Figure 2.1. Performance Modeling Tradeoffs                                        | 15   |

| Figure 2.2. Processor Evaluation Cube                                             | 20   |

| Figure 2.3. Statistical Analysis Techniques (neural network or linear regression) | 34   |

| Figure 3.1. A Layout for Analytical Performance Modeling                          | 43   |

| Figure 3.2. Framework Outline                                                     | 50   |

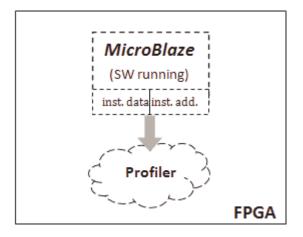

| Figure 4.1. MicroBlaze/FPGA Reference-Model/Profiler Outline                      | 57   |

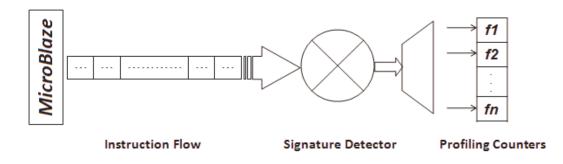

| Figure 4.2. Application-Independent Profiling                                     | 62   |

## **List of Tables**

| <b>Table 4.1.</b> Double-precision floating point div function -first 18 instructions                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 4.2. Numerical C programs used to test the application-independent FPGA-based                                                                                                                                                                                                                                                      |

| profiling mechanism                                                                                                                                                                                                                                                                                                                      |

| Table 5.1. Programs and Benchmarks used for Experimental Validation         72                                                                                                                                                                                                                                                           |

| Table 5.2. Error analysis summary using software implementation of floating point                                                                                                                                                                                                                                                        |

| operations (SW FP)74                                                                                                                                                                                                                                                                                                                     |

| Table 5.3. Error analysis summary using hardware implementation of floating point                                                                                                                                                                                                                                                        |

| operations (HW FP)75                                                                                                                                                                                                                                                                                                                     |

| Table 5.4. Performance Measurements/Estimations (in cycles) of the Target Programs on                                                                                                                                                                                                                                                    |

| the MicroBlsze Architecture (SW FP)77                                                                                                                                                                                                                                                                                                    |

| Table 5.5. Performance Measurements/Estimations (in cycles) of the Target Programs on                                                                                                                                                                                                                                                    |

| the PPC and GS Architectures (SW FP)                                                                                                                                                                                                                                                                                                     |

| Table 5.6. Performance Measurements/Estimations (in cycles) of the Target Programs on                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                          |

| the AVR and PIC Architectures (SW FP)                                                                                                                                                                                                                                                                                                    |

| the AVR and PIC Architectures (SW FP)                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                          |

| Table 5.7. Performance Measurements/Estimations (in cycles) of the Target Programs on                                                                                                                                                                                                                                                    |

| <b>Table 5.7.</b> Performance Measurements/Estimations (in cycles) of the Target Programs onthe MicroBlaze Architecture (HW FP)82                                                                                                                                                                                                        |

| Table 5.7. Performance Measurements/Estimations (in cycles) of the Target Programs onthe MicroBlaze Architecture (HW FP)Table 5.8. Performance Measurements/Estimations (in cycles) of the Target Programs on                                                                                                                            |

| <b>Table 5.7.</b> Performance Measurements/Estimations (in cycles) of the Target Programs on         the MicroBlaze Architecture (HW FP) <b>Table 5.8.</b> Performance Measurements/Estimations (in cycles) of the Target Programs on         the PPC and GS Architectures (HW FP)         83                                            |

| Table 5.7. Performance Measurements/Estimations (in cycles) of the Target Programs onthe MicroBlaze Architecture (HW FP)Table 5.8. Performance Measurements/Estimations (in cycles) of the Target Programs onthe PPC and GS Architectures (HW FP)83Table 5.9. Performance Measurements/Estimations (in cycles) of the Target Programs on |

#### Acknowledgments

Since I started my Ph.D., I have had the chance to work on several projects which all added a great experience to me. I am blessed to have been guided and supervised by Dr. Robert Klenke who has offered me challenge and great support. I also want to thank Dr. Mike McCollum, Dr. Afroditi Filippas, Dr. Kayvan Najarian and Dr. Vojislav Kecman for their valuable feedback on my work. I am greatly thankful for Dr. Jerry Tucker and Dr. Rosalyn Hobson for their boundless support. My gratitude goes for my colleagues Jose Ortiz, Jeremy Cooper, Robert DeMott II, Abed Al-Raoof Bsoul, Jacob Berlier, and Brad Geltz who lent me their experiences and provided me with assistance repeatedly.

## **Chapter 1 Introduction**

An embedded system is a special purpose computer working within a device to control/manage its functionality. For example, processors found in cell phones, digital cameras, medical equipments, cars and modern airplanes are all considered embedded systems. Because of the dramatic grown in embedded system applications, embedded processors have formed the largest class of computers. Figure 1.1 shows the market volume of the embedded processors compared to the other types of processors [1]. While they cover a wide range of applications, ranging from very simple applications such as monitoring the temperature for an air condition to very complex applications such as flight control systems, embedded processors vary in their characteristics, from 8-bit simple-pipeline architectures to 64-bit super-pipeline architectures. Consequently, and because of the very special functionalities embedded systems concerned with, it is very hard, or even impossible, to find an embedded processor that can be considered as the absolute best choice for all embedded applications. Hence, a careful trade-off should be considered when selecting an embedded processor.

Figure 1.1. The number of embedded processors sold between 1998 and 2002 compared to desktop and server processors [1]

#### 1.1. Overview

In embedded systems, selection of an appropriate processor to execute a given application is considered as a crucial decision. The processor must have enough processing power to meet the time constraints for executing the algorithms necessary to operate and control the system. However, the characteristics of the selected processor should not be significantly more powerful than required as this increases its cost, power consumption, heat production and other physical characteristics that must be kept to a minimum in most embedded systems [2]. Furthermore, adopting the most efficient and effective algorithm for a given system and application is also at high level of importance. The algorithm should achieve the desired functionality, meeting the time and accuracy constraints of the embedded application, with a minimum of hardware resources. Accordingly, matching several algorithms demands with different processor architectures for modeling the performance of pairs of algorithms/processors is considered as very challenging task [3]. This is especially true at early stages of the design process where: "there's no magic box into which you place the system requirements that spits out which processor to use" *S. Rosenthal* [4].

#### **1.2. Motivation**

Embedded applications involve computations that are subject to real-time physical constraints. The response of an embedded system is determined by its reaction to the physical environment, specified by deadlines, throughputs ...etc, and the execution on the physical platform, specified by processor speed, power ...etc [5-6]. While the application's algorithm governs the reaction constraints of the system, it is the designer's responsibility to select the execution platform to achieve highest degrees of performance and efficiency. Hence, a key to embedded systems design is the ability to accurately predict the system's execution time for a given algorithm and set of inputs.

Selecting an appropriate processor for implementing the target algorithm should be compatible not only with the other hardware components such as sensors and actuators, but also with the algorithm functional behavior and timing constraints. Degradation in any of these parts affects the performance of the whole system and may lead to undesired performance characteristics [7-8]. So, it is very important to build an infrastructure by which it is possible to extract the dominant operations and required resources that characterize the system behavior.

#### **1.3.** Challenges

Although embedded processors are generally considered less complex than desktop processors, most modern embedded processors implement common principles in computer architecture in order to gain the highest possible performance. Thus, most embedded processors include one or more of the following features: pipelining, branch prediction, cache ...etc. These advanced architectural features introduce difficulties in evaluating the performance of not only desktop processors but also embedded processors. Moreover, factors like time-to-market, and the critical timing and functionality of embedded applications make evaluation of embedded processors more challenging.

Ideally, the time needed by a CPU to execute a program is given by the following equation:

CPU time =

$$\sum_{i=1}^{n} (CPI_i \times C_i) \times C_i$$

(1.1)

Where:

$CPI_i = cycles per instruction-type_i$   $C_i = count of instructions of type_i executed$  n = number of instructions in the corresponding ISAclock cycle = 1/(CPU clock rate)

However, this equation does not account for the clock cycle overhead coming from other aspects in the design, since it assumes that no pipeline stalls occur (no structural, data, or control hazards), and all instructions are available in the cache or first-level memory (all hits) [1].

Nowadays, most processor architectures adopt pipelining to enhance processor performance which in turn allows multiple instructions to run concurrently in the processor, one instruction per stage/functional unit. A simple pipeline is divided into three stages: instruction fetch, instruction decode, and instruction execution. This technique has been evolved continuously to achieve better performance. For example, the execution stage can be divided further into execution, memory access, and write back. Increasing the number of stages does not actually decrease the execution time for instructions; instead, it increases the number of overlapped instructions which in turn increases the processor throughput. However, increasing number of pipeline stages, or implementing parallel functional units that can work simultaneously in the same stage, means increasing the architecture complexity for handling the control between stages/units. Theoretically, after filling the pipeline stages, the processor is supposed to finish one instruction every execution cycle. However, in practice, the implementation of the pipeline results in some constraints that limit achieving the maximum desired performance. Such constraints are called pipeline hazards where the flow of the instructions is halted for one or more execution cycles.

Pipeline hazards are divided into three types: structural hazards, data hazards, and control hazards. In structural hazards, instructions that are overlapping in different pipeline stages try to access the same architecture resource. For example, in a single memory processor architecture, both instructions and data are stored in the same memory. Thus, fetching an instruction and accessing the memory for loading or storing data cannot occur at the same time, which means that one instruction should wait until the other finishes accessing the corresponding stage. Data hazards occur when an instruction cannot be executed as scheduled because there is missing (dependent) data that is a result from a previous instruction. For example, if a load instruction is followed by an another instruction, then the following instruction should wait until the load instruction finishes loading the required data from the memory. In control hazards, the instruction that has just been fetched is not the one that needs to be executed due to some change in the instruction flow such as a branch misprediction.

Different software techniques (static: at compile time) and hardware techniques (dynamic: at run time) have been developed to reduce or eliminate pipeline hazards. For example, splitting the memory architecture into an instruction memory and a data memory solves the corresponding structural hazard. Forwarding results before finishing an instruction's execution helps to reduce the impact of data dependencies. Also, reordering the instructions at compile time can minimize data dependencies and reduce the penalty of branch mispredictions. Another technique to assist making correct branch decisions is to implement branch perdition units at hardware level, e.g. the simplest version is to assume branches always taken.

Implementing a cache as a first-level of the memory hierarchy includes many challenges regarding decisions such as cache size, block size, and level of the associativity. For example, increasing the cache size decreases the miss rate but may tend to increase the access time, i.e., increasing the block size decreases the miss rate (due to spatial locality<sup>1</sup>) but the miss rate tends to go up as the block size becomes too large relative to the cache size (this also tends to increase miss penalty). Also, increasing the level of cache associativity decreases the miss rate, however, the larger cache size, the less relative reduction on the miss rate (this also may tend to increase the access time).

<sup>&</sup>lt;sup>1</sup> Spatial locality: the locality principle stating that "if a data location is referenced, data location with nearby address will tend to be referenced soon", while, *temporal locality* states that "if a data location is referenced then it tend to be referenced again soon" *D. Patterson* [1].

All of the mentioned techniques, whether used to enhance the performance or to reduce the trade-offs in performance impacts, hold a lot of challenges when considering the performance evaluation of an architecture for several algorithms. For example, increasing the depth of the pipeline generally tends to achieve better performance, however, if the running algorithm behaves in such a way to produce large numbers of branch mispredictions, then, the penalty of the branch mispredictions on performance may dominate the performance of the system. On the cache side, different algorithms have different functional behaviors (instruction/data flow) that vary in the level of spatial and temporal locality, hence, the benefits of a given cache implementation are algorithmdependent (as in pipeline architecture). In fact, other microarchitectural details (such as number of internal registers, etc) tend to have different performance impacts with different functional behaviors.

While the above discussion points to the difficulty of performance evaluation at the instruction-level, estimating the performance at source code-level (e.g., the C-level) holds more challenges. For example, the impacts of other tools involved in the system development (such as compilers) are hard to predict in the absence of the assembly code. In addition to the role of compilation in rearranging the code to eliminate data and control hazards, other issues such as predicting the final version of the code produced from different levels of optimization is hard to predict. Moreover, the hidden functional behavior of the library functions, which are sometimes only provided as binary files, also make detailed performance analysis a very challenging task [9]. Furthermore, some

operations at source code-level can be implemented using different functionalities. For example, multiplying or dividing an integer by a number to the power of two  $(2^n)$  is normally handled by shifting that number n-digits to the left or right, respectively.

Considering the obstacles in evaluating the performance of a single architecture for a wide spectrum of algorithms, things become more challenging when evaluating multiple different processor architectures with different instruction set architectures (ISAs), or even the same ISA with different microarchitectural details. Amdahl's law states that "the performance enhancement possible with a given improvement is limited by the amount that the improved feature is used" [1]. This factor points to the difficulty in evaluating different processor architectures as each architecture tends to react differently to algorithm's demands, based on its ISA, available resources and processor organization. For example, if processor A includes a built-in floating point functional unit while processor B implements floating point operations using library functions (not supported by its ISA), it will not be a straightforward conclusion that processor A will be faster than processor B to execute a certain application, even if that application includes floating point computations in its code. This is because other factors such as memory architecture and the real time functional behavior of the target algorithm may dominate the performance. For example, the cache architecture of the processor B may, significantly, perform better behavior to exploit the spatial/temporal locality characteristics of the target algorithm, on the other hand, the algorithm run-time functional behavior may access the portions of the code that include floating point operation infrequently (nonintensively).

#### **1.4. Problem Statement**

At the early design stages of an embedded system, exploring the performance characteristics of the target application by executing it on different hardware platforms is considered a very costly approach in terms of time and money. Such an approach requires acquiring the software development tools for each processor and the corresponding skills to use them, integrating the processor with other system components such as sensors/actuators and analog/digital convertors (or modeling their equivalent behavior), and possibly testing the system in the field or on a hardware in a loop simulation environment. Hence, a main concern for embedded system designers is to reduce the set of algorithm/processor candidates by eliminating unacceptable alternatives, or better yet, to have a systematic approach by which they are able to perform a fair performance comparison based on the main parameters and characteristics of the given application and the candidate processor's architectures. Furthermore, this comparison needs to be done efficiently, with minimum of resources: time, tools and cost, especially since often the software development tools and microarchitectural specifications of the candidate architectures are not readily available to the **designer.** In this research, the efforts are constrained to model the performance of single-threaded algorithms which would constitute the main loop of the target

application. At this point, the effects of multiple threads and interrupts on the performance of the main loop algorithm are not considered. Furthermore, the performance metric considered is limited to the execution time of the algorithm on the target processor – expressed as either processor clock cycles or actual processor execution time.

#### **1.5.** Contribution

A key question is whether, in order to make a correct design decision, the designer needs performance estimation with absolute accuracy<sup>2</sup>, or a relative accuracy<sup>3</sup> amongst design alternatives. At the early stages of the design process, factors like the estimation speed, which can influence how many alternatives can be considered in the design process, are also very important. Hence, a tradeoff to minimize such important factors with an acceptable decrease in the level of accuracy is considered to be very helpful, as long as it is possible to accurately classify the relative performance of the candidate architectures. Later in the design process modeling at a more detailed level of abstraction can be done on a minimized list of processors to gain better accuracy in performance estimation.

<sup>&</sup>lt;sup>2</sup> In this dissertation, the term absolute accuracy (or absolute performance estimation) is used to describe the performance of an application on certain processor architecture in terms of number of cycles (or units of time), regardless the performance of other processor architecture.

<sup>&</sup>lt;sup>3</sup> In this dissertation, the term relative accuracy (or relative performance estimation) is used to describe the performance of an application on certain processor architectures in terms of better-worse (slower/faster) where the estimated time is used only for comparison purposes rather than an absolute estimation.

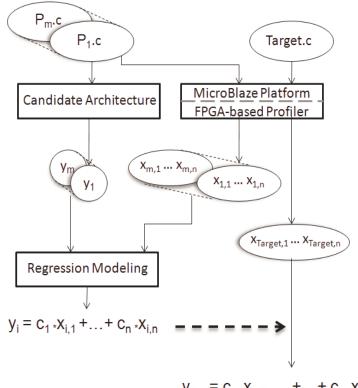

This research describes a method for analyzing the performance of a given application on different architectures based on running/profiling the application on a reference model (processor). Hence, the performance statistics resulted from this analysis can be used to assist in determining the functional behavior of the target application. This approach is unique in that there have been no efforts, tools or frameworks, up to this point in time, that use a reference processor in a similar way to predict the performance of other (foreign) architectures. The observed statistics produced by the reference model can be used to determine the application's dominant operations (such as integers, floating point, etc.), which in turn allows exploring the hardware resources needed to be embodied in the system platform. Using analytical modeling techniques such as regression analysis, these statistics can be used (bound), along with a set of reference performance measurements of a domain of algorithms on the candidate architectures, for estimating the performance of these architectures against new algorithms/applications.

This research also introduces a novel FPGA-based instruction profiling technique. While FPGA-based profiling is a relatively new technique in the field and has been adopted recently in certain FPGA and software/hardware codesign approaches [10-14], the technique described herein relies on tracing the unique instruction flow of the functions-of-interest (considered as a function's footprint) rather than tracing the program counter (PC) value. This is a very important distinction which allows framework developed for

this dissertation to be applied against new algorithms with minimal efforts, and without the need for time-consuming reconfiguration of the FPGA.

A basic assumption in this research is that the reference performance measurements for a domain of algorithms on the candidate architectures have been previously extracted and published by the processor's vendor/manufacturer, so customers (embedded system designers) can access both the performance records, and the source code of these algorithms. For the purpose of producing results to evaluate the framework, these reference performance measurements were obtained by the author by running benchmark programs on the example processors that were evaluated. However, in the future, it is proposed that vendors/manufactures will extract and publish these results for the benchmark programs for use by designers in evaluating the processor for their specific application. Moreover, performance measurements reported by other users (on candidate processor architectures) for specific programs/benchmarks can be used for training purposes as long as the embedded system designer has an access to these programs/benchmarks so they can be run and profiled on the reference model.

It should be pointed out that the method described herein does not produce a 100% cycleaccurate estimation; however, this approach provides the embedded system designer with a high-level, very fast, performance modeling technique that can be used for initial processor selection and that requires minimal resources/knowledge of the application functional behavior and processor architecture.

### **1.6.** Dissertation Organization

This dissertation is organized as follows: Chapter 2 discusses/surveys the performance modeling techniques in the areas of processor design, selection and embedded systems. Chapter 3 shows a problem analysis and discusses the theoretical background of the proposed framework. Then, reference model specifications and FPGA-based profiling are discussed in Chapter number 4. Chapter 5 illustrates experiments and results. Chapter 6 concludes, and Chapter 7 describes future work.

### **Chapter 2 Performance Modeling**

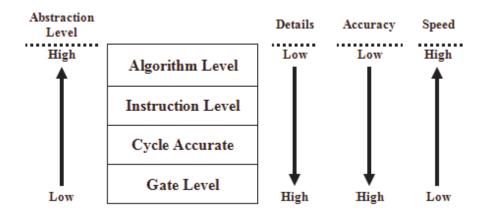

Whether targeting desktop processors or embedded processors, performance modeling faces a set of common challenges (tradeoffs) and trends. Figure 2.1 summarizes the tradeoffs in the field of performance modeling. In general, as the level of the abstraction increases, more details are omitted/or more assumptions are made, hence, the accuracy of the model decreases. However, the lower the level of details employed to build a performance model, the more accuracy achieved, but, with a significant decrease in the estimation speed. This is true whether considering simulation-based modeling or analytical-based modeling.

Figure 2.1. Performance Modeling Tradeoffs

Considering that, generally, each level of abstraction cannot achieve better accuracy than its adjacent lower level of abstraction, or faster estimation speed than its adjacent higher level of abstraction, efforts in performance modeling have concentrated on minimizing the tradeoffs by either 1) modifying higher level of abstraction techniques to employ more details to achieve more accuracy than what they traditionally achieve to be as close as possible to the accuracy of the adjacent lower level of abstraction, (e.g. time annotation), or 2) simplifying the lower level of abstraction techniques to achieve faster estimation than what they traditionally achieve, to be as close as possible to the speed of the adjacent higher level of abstraction, (e.g. parallelism in cycle accurate simulation).

In addition to the accuracy and speed factors, it is desirable for performance modeling techniques to posses features such as structural simplicity, user friendliness, lower development cost, lower setup time, and flexibility to target new systems and applications. Such factors add still more tradeoffs in performance modeling techniques.

The first section in this chapter presents an overview of performance evaluation techniques used in processor design. The following section discusses general hardware and software performance evaluation techniques used in embedded system design. The third section discusses existing performance modeling techniques developed to assist in the processor selection decisions at early stages of an embedded system design – similar to the framework developed for this research. The final section presents a summary.

#### 2.1. Performance Evaluation for Processor Design

In the development of new microprocessors, it is very important to validate the functionality and the performance of processors-under-development before proceeding in the design process or releasing the products into the market. Hence, performance evaluation is involved in several stages of the design, where going backward in the design process is very costly. A major challenge in processor performance evaluation is that "one second of program execution on these processors involves several billion instructions and analyzing one second of execution may involve dealing with tens of billions pieces of information" *L. John* [15].

Based on the classification shown in [15], performance evaluation can be classified into two main categories: performance measurements, and performance modeling. Performance measurement aims to emulate/verify the architectural functional and timing behaviors under a set of benchmark programs that characterize the target application domains at run-time. This technique is only possible if either actual system or its prototype, where the RTL design of the architecture-under-development is ported into FPGAs [14, 16], are available. By stressing the architecture with intensive workloads, different events/signals can be monitored to explore the bottlenecks in the design. In case of running workloads on a prototype, tools like Xilinx-ChipScope [17] can be used to trace the status of the processor [16], or alternately, the signals-of-interest can be routed externally for monitoring [14]. In case of using an actual architecture, performance

17

measurements can be implemented either at the hardware-level by accessing the on-chip counters (if equipped/available) or using logic analyzer to trace the machine status at the events-of-interest, captured via interrupts, or at the software-level using code instrumentation or software drivers. While using on-chip performance counters is considered very fast, it is limited to certain events that are actually accessible by such counters. Interrupts and code instrumentation can be implemented to measure a number of different events but they add a significant performance overhead – as they interfere intensively with program execution [11, 13, 15].

The second class of performance evaluation, that of performance modeling, is concerned with evaluating the performance of architectures-under-development. Performance modeling can be employed at the early stages of the design process where the actual architecture is not available and it is expensive to prototype all possible design choices, or if the signals-of-interest are hard measure on the actual hardware. Performance modeling can be further classified into analytical-based and simulation-based. Analytical modeling [18-19] has rarely been used due to the accuracy requirements and the level of implementation details needed for it to be employed [15, 20]. However, at the earliest stages of development, analytical modeling can be used as a decision support technique [20].

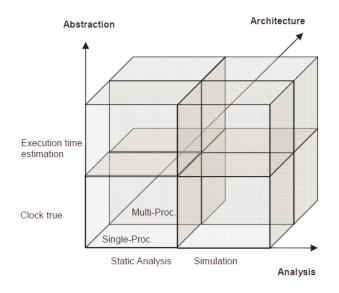

A framework dubbed the Processor Evaluation Cube (PEC) which helps in classification and comparison of a range of processor evaluation techniques is proposed in [21]. The

three axes of the PEC are: analysis, architecture and abstraction where each axis consists of two distinct points (see Figure 2.2). The analysis axis distinguishes methods employing static analysis or simulation; the architecture axis distinguishes methods evaluating single processor or multiprocessor target architectures; the abstraction axis distinguishes methods employing cycle-true evaluation or higher level execution time estimation techniques. The authors observed that in most cases modeling the performance of single processors falls in the performance evaluation context and in few cases the selection is mentioned as an explicit goal of the performance estimation techniques - in contrast with multiprocessor performance modeling which focuses in the selection process considering the performance of each single core has been implicitly modeled. In the research efforts surveyed in [21], it is shown that most (about two thirds) of the efforts targeting single processor performance estimation fall in the non-cycle-true static analysis category while, on the other hand, around half of the surveyed efforts targeting the performance estimation of multiprocessor architectures fall in the non-cycle true static analysis category. The remainder of the efforts fall on the (non or) cycle-true simulation categories. The survey argues that many different evaluation techniques may fall in the same category in PEC classification, though significant differences in performance analysis can be found to distinguish between them. The study also remarks that some techniques may fall in more than one category because they actually include the two options in an axis, nevertheless; based on the interpretation of these techniques, these could be classified into a single category. Finally, the authors point to the ability of adding more points to the existing axes (or adding more axes) for tightening category boundaries, or expanding the classification paradigm to include new criteria.

Figure 2.2. Processor Evaluation Cube [21]

In the area of simulation-based performance modeling of processors, cycle accurate simulation is considered the dominant technique used for hardware design space exploration [15, 20, 22-23]. Unlike functional simulators which are used to simulate only the functional behavior of an application on a certain processor, cycle accurate simulators [24] are concerned with handling both functional and timing behaviors of the target architecture, which in turn requires representing the impact of the micro-architectural details into the simulator structure, adding more complexity and slowing the simulation speed. Methodologies and techniques for cycle accurate simulation have been surveyed in [22]. The study argues that simulation speed and the level of accuracy are the most

important factors in the development of cycle accurate simulators where the more architectural details represented in the model and the larger benchmark set used for validation, the more accurate the results achieved. However the greater the level of detail, the slower simulation speed. Hence, such tradeoffs limit the efforts for developing cycle accurate simulators [15, 20, 22-23]. Techniques such as reducing the input set and using the sampling approach have been adopted to reduce the simulation workload [25-26], thus increasing the simulation speed, however, such techniques have direct impacts on the simulation accuracy. Recently, there have been interests in employing different parallelism (and partitioning) techniques for cycle accurate simulators to enhance the simulation speed by using multicore processors [27-31], or by using FPGAs to accelerate the time intensive portions of the cycle-accurate simulation [32-34]. However, such techniques face difficulties such as: 1) how to partition the jobs for maximum parallelism, 2) how to minimize the communications overhead, and 3) how to avoid deadlocks among shared resources [35-36].

The objective of the modeling techniques described above is to model/measure the performance of architectures-under-development at several stages of the development process for use by the processor developers themselves. On the other hand, this research aims to model the performance of an existing architecture that is already built, for the end user running an actual application. Hence, no direct comparison can be made between the framework developed in this research and the previously discussed modeling techniques. However, determining an application's

dominant operations using the techniques used this framework could be very valuable in determining the processing bottlenecks for the development of an application-specific instruction-set processor (ASIP).

#### 2.2. Performance Evaluation for Embedded Systems Design

While desktop processors are generally very complex and hence need complex performance modeling techniques, factors like time-to-market, time critical/complex functionalities, and heterogeneous application domains have made estimating the execution time of software applications on embedded systems a crucial issue. To overcome the issues regarding traditional cycle accurate modeling techniques such as speed and complexity, new software performance analysis have been developed embedded systems design. Some of these methods are described in the following sections.

#### 2.2.1. Open-Source Cycle Accurate Simulation for Embedded Processors

SimpleScalar [24] is an open source cycle accurate simulator which is widely used in academia. While it supports Alpha, PowerPC, and ARM instruction set architectures, it assumes a fixed pipeline structure and timing delays. Since it is implemented using very low level C-code with many macros, an extensive validation is needed whenever it is

modified with different parameters [37], which in turn makes it hard to retarget to a new processor architecture.

#### 2.2.2. Time Annotation Techniques

In [38], timing delays for instructions are annotated from low level models (cycle-level models) back to the application source code. Hence, the original application can be simulated without the underlying architecture details with orders of magnitude faster run times and good level of accuracy. Another timing annotation technique called compilation-based simulation is shown in [39], where the assembler code is annotated with the timing delay (execution cost) of instructions that can be obtained from the datasheet or benchmarking. This allows obtaining timing information by running the application code on the host machine and simply adding up the number of cycles for each instruction instead of using cycle accurate simulation. Of course both of these techniques have reduced accuracy because the effects such as the interaction between instructions due to micro-architecture details are not accounted for.

#### 2.2.3. Statistical Analysis Techniques

In [40], a non-linear Lazy statistical method is employed to predict the performance of embedded software running on the SPARC architecture. The performance model is defined as a set of functional models mapped into a set of possible architectures with different memory latency and CPU speed parameters. A program's main parameters are extracted using an instruction-level profiler (SPARC-IPROF), and then a cycle-accurate simulator (TSS, built in C) is used to obtain the performance of each application/architecture pair. The model is then able to estimate the performance of an application on a certain trained processor configuration. Another statistical approach is shown in [41] where the source code is translated into simplified virtual instruction set, allowing program parameters can be extracted by running the application on a virtual instruction set simulator while performance estimates can be obtained using cycle accurate simulation. Linear regression is then used for building the prediction model.

Modeling the performance of an application on a specific processor whose cycle accurate and functional simulators have been tested using a set of benchmark programs is proposed in [42]. In this technique, linear regression is used to model the impacts of the application's parameters on the system performance. A total of 183 benchmark applications, most of them are DSP applications, have been used to train the model. The functional simulator has been enhanced to allow counting various events (e.g. counting different types of instructions and possibly also cache and memory accesses). The study shows a number of experiments on each one of which new parameters have been used to study how accurate the model is when employing such parameters. For different parameters sets, mean absolute errors ranging from 5.44% to 38.8%, (std. deviation = 7.12 to 57.7), with a maximum errors ranging from 26.31% to 518%, have been reported when testing DSP applications on ARM v5 implementation. This work shows that increasing the number of parameters does not always lead to an increase in the performance modeling accuracy, hence, the efficiency of the selected parameters for modeling an application has to be considered for more accurate results and a more efficient regression model. Moreover, programs that had small size reported larger errors because their behavior can be far away from the general observed statistics that govern the performance prediction model.

#### 2.2.4. Static Analysis of Embedded Software

In some real-time embedded systems applications, static timing analysis is mainly used to explore the worst case execution time (WCET) by detecting all possible scenarios for a program execution which in turn allows predicting the time cost for the worst case flow of the target program (or tasks). This is important for schedulability analysis, and to check the safety of the system to be certain that some circumstances cannot cause a system timing failure. Typically, WCET depends on analyzing the disassembled binary executable code to determine the structure of the program and to determine how each basic block of the program interacts with the hardware resources [8, 43-46]. A major issue in WCET analysis is that loops and conditional statements must be pre-determined, i.e. any dependency of the program's execution on real-time inputs/conditions should be pre-solved [8, 46]. Furthermore, as the design architecture and constraints become more complex, the number of the states increases quickly which in turn makes the analysis more difficult and time consuming.

25

Processor selection is not a goal of the performance modeling techniques discussed up to this point, instead, these techniques aim to replace the traditional cycle accurate simulation techniques used in the hardware design space exploration with new high-level, faster modeling approaches. However, techniques mentioned in [40-42] are among the techniques which have inspired this research's efforts.

#### 2.3. Embedded Processor Selection based on Performance Estimation

A processor's performance, typically, can be characterized by a set of features like: clock rate, built-in functionalities (supported assembly instructions), level of pipelining, cache architecture, etc. Maximizing such features is considered to be one of the options to obtain more performance. However, unlike a desktop processor where "faster is better", in embedded systems, the design philosophy states that "**fast enough is good enough**" *T. Conte* [2], where, factors like cost, size, power consumption, heat production, limited memory resources and other physical characteristics constrain the designer's processor choices. In addition, in selecting a processor for a certain application, the non-functional requirements of the processor such as the portability and the user's familiarity with its development tools may dominate the processor selection decision [47-49]. An example of non-functional requirements affecting the processor selection decision can be found in [50].

#### 2.3.1. Traditional Techniques

A study of the methods and guidelines for embedded processor selection is shown in [47]. The study found that the largest factor influencing an off-the-shelf processor selection decision is the performance, followed by other factors such as cost, and product time-to-market. The consideration of these factors, as the study shows, are typically based on a set of criteria such as benchmarking results, system requirements and resources, and the designer's familiarity with the development tools. In [2, 4, 47, 51], a set of tips based on the authors' experiences in embedded systems design are listed. These tips concentrate on key features of processor architectures that have a direct impact on the performance of the systems, such as the processor word size and the memory architecture. Such tips are very helpful when the embedded system designer has a deep knowledge of the application functional behavior/demands and processor architecture.

In [49, 52], a database of microprocessors is created to help in selecting an appropriate processor based on general specifications such as clock rate, memory resources, power consumption and price. Using this database, the designer can trade between the different features and narrow down the search space for the desired architecture.

While execution time cannot be indicated using only the clock rate of the system, it is important to know how many operations the CPU is capable of accomplishing per unit of time (or how many cycles each instruction needs to execute), measurements like MIPS (millions of instructions per second) and MFLOPS (millions of floating point operations per second) have been introduced to help in evaluating the performance of processors. Such criteria indicate a processor's general performance. However, for different types of processors and different types of applications, MIPS/FLOPS may mislead the performance evaluation due to the different amount of work accomplished by different instruction set architectures (ISAs) for applications with characteristics [15, 53].

Reviewing the recorded performance measurements of different benchmark programs published by a processor's manufacturer can indicate the performance of the candidate processor in the same domain of applications. The accuracy of the performance estimation depends on the level of the representation (i.e. instruction distribution, branchs, cache behavior ...etc) of the target application in the benchmark suite. However, designing a benchmark suite for embedded applications, is itself a very challenging task because benchmark programs should be non-redundant and comprehensive while at the same time, covering a wide domain of embedded applications which are very diverse [15, 20, 22-23, 54]. Currently, few benchmark programs are available for targeting embedded systems. The most popular embedded benchmark suites are the free open source MiBench [54], and the EDN Embedded Microprocessor Benchmark Consortium (EEMBC) [55].

Using Rate Monotonic Analysis (RMA) to evaluate processors for use in real-time embedded applications is shown in [48]. This technique depends on high-level analysis of the target architecture and the pseudo code of the target algorithm. Hence, a background in how compilers generate code is necessary to obtain a better evaluation. In this approach, the target algorithm is assumed to be divided into a set of tasks, where each task is assigned a run time value (duration) and frequency value (period). Based on analyzing the total utilization of the processor for all tasks, a decision can be made to accept or reject the candidate architecture. The pessimistic maximum allowed load is suggested to be 70% of the total processor load; however, to account for forgotten tasks and ones that are added at design time based on new requirements, the author suggests that a load of as low as 35% can be considered a fairly reasonable initial value. This technique needs the designer to have deep knowledge in both the functional behavior and time constraints of the target application and the microarchitectural details of the execution platform, which, at the early stages of the design process are hard to extract without having the software development tools of the candidate architectures (compilers, simulators, etc.).

# 2.3.2. Analytical Techniques

Techniques for performance estimation by evaluating the degree of matching between algorithm requirements and the processor architecture resources, is shown in [3, 56-57]. For example, in [3], a requirements matching technique was shown predicting the most suitable architectures, in terms of general performance (goodness), for three out of four MiBench algorithms. In this technique, a set of correlation functions are applied to the algorithm/processor requirements/characteristics to estimate the utilization of the architecture resources, where, typical algorithm properties are extracted using platformindependent intermediate representation (SUIF), and the corresponding architecture is characterized using features such as the instruction set, pipelining, branch support, etc, where, due to the complexity, the cache factor is ignored.

In [58], the objective is to select the best architecture among a set of possible candidate processors (microcontrollers, DSPs and RISC microprocessors). The target application is modeled in an object oriented environment, where intermediate descriptions of the code are generated for three virtual machine types; microcontrollers, DSPs and RISC microprocessors. Next, by analyzing the application's characteristics such as the number of jumps, arithmetic and memory access operations, etc., the application behavior is classified into one of the following domains: 1- control intensive: many control instructions like a finite state machine (FSM), 2- data intensive: computations accomplished on internal registers like digital filters, or 3- memory intensive: such as list processing. Depending on this classification, a microcontroller, a DSP or a RISC architecture is selected for the implementation. The study does not show an estimation of the execution time but gives relative match of an application among a set of architectures.

In [9, 59], a performance analysis technique using an intermediate representation called Low Level Virtual Machine (LLVM) is proposed where the performance is indicated as an estimation to the number of executed instructions. In this technique, each LLVM intermediate instruction and library function is correlated to the number of executed instructions on the target architecture that can be obtained by running executable code on an instruction set simulator for the target architecture. A mathematical model to estimate the performance of standard library functions is proposed by relating the number of the executed instructions for each library function to the size/number of parameters passed. By analyzing the functional behavior of the library functions, the study classifies them into two groups, input independent, where the performance is the same regardless to the input value, and input dependent, where the performance changes, linearly or nonlinearly, based on the input nature. The proposed mathematical model has been verified by running the library functions a large number of times on a functional simulator and plotting the number of the executed instructions for each function against the input argument size/numbers. Although this approach is not shown to give very accurate results, it allows analyzing the performance of new applications at high-level without compilation and simulation tools.

In [60], a technique for embedded system performance estimation to assist in selecting a suitable processor for a given application is proposed based on application/processor architecture analysis. The evaluation is accomplished through two steps: 1- eliminating the unsuitable processors among a large set of processor candidates based on the application's and the processor's key features, 2- estimating the number of cycles needed to implement the target application on the rest of processor candidates. In this technique, the application (written in C) is profiled to determine the number of iterations for each

block of the source code. Then, the target application is translated into an intermediate format using SUIF (Stanford University Intermediate Format) to extract the main parameters characterizing the application (e.g. number of concurrent load/store operations). Using simple processor description format, each processor architecture is characterized through a set of specifications such as type/number of functional units and number of registers. Finally, analytically, the application code size and execution time are estimated based on the extracted profiling results, application parameters, and hardware characteristics. The authors reported estimates within 30% of the results obtained from lower level tools.

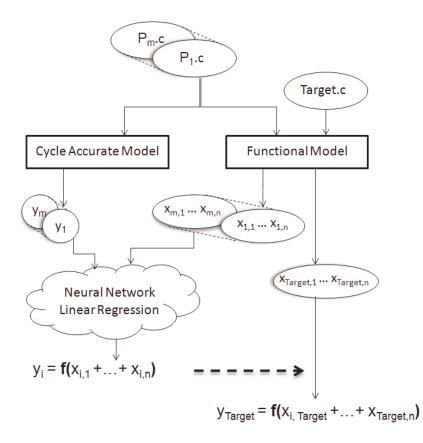

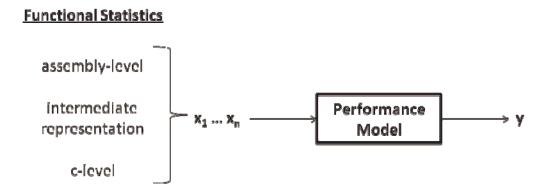

A neural network-based performance estimation technique is proposed in [61-63], similar to the concept in [42]. Figure 2.3 is a general outline of this approach, which eliminates the need to execute a specific target application on a cycle-accurate model of the processor in order to generate a performance estimate. However, a cycle-accurate model of the processor is still needed to determine the performance estimate for the set of benchmark applications used to train the regression model or the neural network. Because of the non-linear impacts of the hardware architectural details (such as pipeline, cache, and branch prediction units) on the system performance, the authors have proposed estimating such relationships using a neural network. The neural network is trained using the results of running a set of programs on a cycle accurate simulator (measuring the time) and a functional simulator with profiling capability (measuring the number of load/store, branch, integer and floating point operations). To estimate the performance of

a new application, the application needs to be run only on the functional simulator. Then, the extracted dynamic numbers of instructions for the target application are fed into the trained neural network for performance estimation. An application domain classification technique, by which applications are classified as control-flow or data-flow applications, has been used to enhance the estimation accuracy. Using 41 benchmark programs, this approach shows some level of estimation speed-up (resulting from the need to only execute the target application on the faster, functional processor model), with a moderate accuracy level [61]. For example, a speed-up up to 190 times in comparison with cycle accurate simulator has been achieved for the superscalar PowerPC-750 architecture where the estimation mean error was 6.41% with a maximum error ranges from -32.41%to 25.87% for the data flow domain (std. deviation = 9.54), and a mean error of 7.62 with a maximum error ranges from -49.37% to 24.96% for the control flow domain (std. deviation = 12.46). A higher level of accuracy has been achieved when testing the ADSP 218x processor, where for generic domain the results were 2.42% (avg), 4.89 (std. dev.), -18.1 to 18.88 (max error). The accuracy of the estimation results depends not only on the strength of the neural network structure but also on the size of the data set used to train the neural network and the selection of the parameters that govern the system and the processor architecture complexity. Moreover, the need for a cycle accurate simulator (and the software development tool for each platform) to train the neural network is considered a main obstacle of using this technique for algorithm/processor selection purposes.

Figure 2.3 Statistical Analysis Techniques (neural network [61] or linear regression [42])

# 2.4. Summary

While the traditional techniques described in Section 2.3.1 above are generally simple, they do not give any statistical information that explains quantitatively how the presence or absence of certain features in the processor or requirements in the application affect the performance of the system. This lack of information, in turn, makes evaluating system alternatives a very hard task. On other words, such techniques can be used for decision support but cannot be used for detailed performance estimation purposes.

On the other hand, the analytical techniques described in Section 2.3.2 require running the target algorithms in a simulation environment, which inherently requires using the compilation tool of each candidate architecture. Furthermore, problems like integrating the simulation tool with other system components constraint such techniques to off-line analysis. It is clear that the neural network technique has been able to predict the performance of the target architecture with an acceptable level of accuracy using the functional parameters of the target algorithms. However, the need for the software development tools (compiler, functional simulator) for each target architecture significantly increases the cost and the setup time.

The approach developed in this research is similar to the neural network approach, however, linear regression for building the prediction model is used here in lieu of neural networks. However, the most important distinction is that in the technique developed in this research, no software development tools for target architectures are needed. Instead, the MicroBlaze platform is used as a reference processor, through which it is possible to predict the performance of foreign architectures. The use of the MicroBlaze as a reference processor also allows evaluating the performance of the application at the source code level with only the MicroBlaze software development tools being required.

# **Chapter 3 Problem Analysis**

This chapter is organized as follows; section 3.1 provides a general background on the problem, section 3.2 discusses the theoretical analysis of the framework developed in this research, section 3.3 compares the developed framework directly to the most closely related existing methods, and section 3.4 gives a summery.

# 3.1. Background

In embedded systems, software has become a dominant design factor. As a result, modeling the performance of running software is one of the main design challenges, especially at a high-level of abstraction [64]. Moreover, considering the enormous number of ISAs and microarchitectures available for embedded systems makes this modeling a very challenging task. In [65-69], system-level design tools are provided which support a number of ISAs and microarchitectures. However, such tools are hard to extend or retarget [38]. Simulation tools such as [24] offer cycle accurate measurements, but they target specific ISAs and require avery low level hardware details, hence, they are hard to modify, even for the same ISA. Augmenting ISSs with timing information [38-39] requires compiling the target algorithm with the corresponding architecture's compiler, and analyzing the binary code and the hardware architecture, which in turn, requires disassembling the executable code and validating the ISS against cycle accurate models. Modeling new (or existing) ISAs or microarchitectures using architecture

description languages (ADLs) such as [70-74] is not within the scope of this research. Although such languages allow automatic generation of software development tools, such techniques are very time consuming since they require a complete specification of the target architecture.

As mentioned in Chapter 1, the fundamental question is whether absolute accuracy or relative accuracy is needed? While absolute accuracy has been always the ultimate goal for performance modeling, factors like time, cost, complexity, and the limited resources at the early stages of an embedded system design lead to the conclusion that an analytical framework that is able to achieve a relative accuracy to be a very useful resource. A challenging problem is how to collect quantitative statistics for the target algorithm to determine the dominant operations and the demanded resources that can assist in evaluating the performance characteristics of the system. The framework developed for this work and described herein, works at high-level of abstraction (C-level) where no ISA or microarchitectural details are required to model the performance of the candidate architectures, i.e., an algorithm written in C can run on a reference model, and quantitative statistics regarding system functional behavior can be collected using the developed profiling technique to assist in evaluating the performance of the target algorithm/architecture.

Implementing different ISAs and/or different microarchitectures in order to attempt to exploit their advantages for a certain class of applications has led to the development of an enormous number of embedded processors. Despite of their differences, however, similar design concepts can be found in most processor's implementations due to key design principles that considered as a rule of thumb in processor architectures. A survey of embedded RISC processors [75], which considered a subset of five types of processors, has shown that in most cases 1) the instruction size can is either 16 or 32 bits, 2) the address space is 32 bits, 3) the integer registers are 32 bits, 4) the I/Os are memory mapped, and 5) integer instruction sets are very similar. Moreover, when analyzing the operation of embedded applications, it can be stated that a small portion of code consumes a large portion of the execution time which is compatible with the *Pareto* principle. By their nature, embedded applications tend to spend 90% of the execution time in 10% of the code, dubbed "90-10 rule" [76-77]. While different ISAs/microarchitectures produce different performance characteristics, similar hardware design principles tend to have analogous impacts on performance.

Regardless the processor's ISA and microarchitectural details, when running software, processors tend to implement the same functionality, with different timing behaviors (and perhaps different precision). Considering the performance represented by the number of consumed units of time to execute a certain program, it is difficult, or even impossible, to map processor performance to another processor performance that has different ISA or/and different microarchitecture, based only on the performance measurements (as a

single number). For example, assume that processor **A** consumes  $\mathbf{y}_{A1}$  units of time to execute program **1**, and processor **B** consumes  $\mathbf{y}_{B1}$  units of time to execute the same program, then, it is possible to find another program (or a sequence of instructions) that consumes  $\mathbf{y}_{A2}$  where  $\mathbf{y}_{A2} = \mathbf{y}_{A1}$ , while it is not mandatory that the new program will consume  $\mathbf{y}_{B1}$  where  $\mathbf{y}_{B2} = \mathbf{y}_{B1}$ . Hence, the relationship between  $\mathbf{y}_{A1}$  and  $\mathbf{y}_{B1}$  that holds for the first program does not hold for the second program. However, if we analyze the logical execution of the running program at high-level (source code), both processors tend to follow the same logical execution flow to implement the same functionality for a given algorithm.

Since the performance of running software is a reflection of its functional behavior on a certain architecture, then, it is possible to evaluate the performance of an application by analyzing its functional behavior. The problem here is that although programs may follow the same functional behavior at a high-level, the real execution of programs is at a low-level in which different ISAs/microarchitectures have different specifications that lead to different execution paths, instruction flows, and timing constraints. The following section discusses the approach developed in this research to handle this issue.

#### **3.2. Theoretical Analysis**

The performance of an application on a certain processor is a result of the timing constraints of the algorithm's execution on the processor's microarchitecture, i.e., the timing behavior is characterized by the instruction flow through the hardware resources, which is subject to both logical and physical constraints. Hence:

$$Performance = f (Functional Behavior, Microarchitecture)$$

(3.1)

where performance is represented by a single number that represents a timing measurement (number of cycles or units of time), the functional behavior is the instruction flow of the target algorithm (at assembly-level), and the microarchitecture is the hardware (physical) implementation such as pipeline architecture, memory elements (including registers, cache and memory), system clock, ...etc.

At the assembly level, a single program, before execution can be thought of as a set of N instructions, where the ordering between instructions represents the logical structure of the program. If the instruction  $I_i$  is the i-th instruction in the program structure, considering the address of instructions as a part of the instruction signature, then, for  $k \neq j$ ,  $I_k = I_j$  is not a valid expression, although they may have the same instruction type and the same operands, the address cannot be identical. On the other hand, a single program running on a processor can be thought of as an ordered trace of **M** instructions, where the

ordering between instructions represents their logical execution order (**M** could be less than, equal to, or greater than **N**). If the instruction  $I_i$  is the i-th instruction in the trace, considering the address of instructions as a part of the instruction signature, then, for  $k \neq$ j,  $I_k = I_j$  is a possible option, i.e., an instruction can be called more than one time in the same program. However, for different ISAs, the quantities **N**, **M**, the type of instructions, and instruction flow are different since they are ISA-dependent.

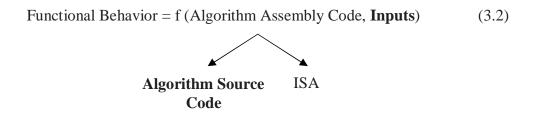

The functional behavior (as expressed in 3.1) of executing an algorithm on an ISA can be represented by the following expression:

The algorithm assembly code is the translated version of the source code based on the target ISA, which is platform-dependent, where the source code is the program written at high-level language (such as C) that decides the logical execution of the program (platform-independent). The inputs are the incoming data in through input ports. Inputs and Algorithm Source Code are bolded in the above expression because they can be considered common factors in our analysis.

At the level of source code, a single program before execution can be thought of as a set of **N** statements, where the ordering between statements represents the logical structure of the program. If statement  $S_i$  is the i-th statement in the trace, considering the logical order of the C statements, then, for  $k \neq j$ ,  $S_k = S_j$  is not valid for any j-k. On the other hand, a single program running on a processor can be thought of as an ordered trace of **M** statements, where the ordering between statements represents their logical execution order. If statement  $S_i$  is the i-th statement in the trace, considering the logical order of the C (i.e., the source code) statements, then, for  $k \neq j$ ,  $S_k=S_j$  is a possible option. Unlike assembly-level analysis, at the C-level, the quantites **N**, **M**, the statements, and the possible paths of program execution tend to be identical regardless the ISA of the target platform (ISA/platform-independent).

Although the real execution of a programs is at assembly level (binary executable code), analyzing a program at high level (or using an intermediate representation) to determine the logical functional behavior can assist in evaluating its performance [3, 9, 41, 56-57, 59-60]. As mentioned previously, in this research, the goal is not to build a cycle accurate model, since this requires, at least, having the target algorithm compiled into the target ISA, disassembling the binary code, and building a detailed microarchitecture model, instead, rather, analytical modeling is used to discover the relationship between the application's functional behavior and the processor's performance in executing it.

Figure 3.1 shows a general layout of analytical-based performance modeling. A performance relation can be defined as:

$$\mathbf{X} \times \mathbf{P} \mathbf{M} \rightarrow \mathbf{y} \tag{3.3}$$