# Real-time display of a multiprocessor Spiking Neural Network

Master Thesis

submitted to the Faculty of the

Escola Tècnica d'Enginyeria de Telecomunicació de Barcelona

Universitat Politècnica de Catalunya

by

Clément Nader

In partial fulfillment of the requirements for the master in **ELECTRONICS ENGINEERING**

Advisor: Bernardo Vallejo Co-advisor: Dr. Jordi Madrenas Boadas Barcelona, September 2021 - February 2022

# Contents

| A            | ckno  | wledgments                              | V      |

|--------------|-------|-----------------------------------------|--------|

| $\mathbf{A}$ | bstra | $\operatorname{\mathbf{ct}}$            | vi     |

| Li           | st of | Figures                                 | vii    |

| Li           | st of | Tables                                  | X      |

| $\mathbf{A}$ | crony | vms                                     | xi     |

| 1            | Intr  | oduction                                | 1      |

| <b>2</b>     | Stat  | te of the art                           | 2      |

|              | 2.1   | Biological neurons                      | <br>2  |

|              | 2.2   | Artificial Neural Networks              | <br>2  |

|              | 2.3   | Spiking Neural Networks                 | <br>3  |

|              | 2.4   | HEENS architecture                      | <br>4  |

| 3            | Pro   | ject development                        | 9      |

|              | 3.1   | Current state of the project            | <br>9  |

|              | 3.2   | Vivado software and VHDL language       | <br>11 |

| 4            | Scre  | een display via HDMI                    | 12     |

|              | 4.1   | Principle                               | <br>12 |

|              |       | 4.1.1 Introduction                      | <br>12 |

|              |       | 4.1.2 Aspect ratio and video resolution | <br>13 |

|              |       | 4.1.3 Video timings                     | <br>14 |

|              |       | 4.1.4 Color format                      | <br>16 |

|              | 4.2   | Hardware specification                  | <br>17 |

|              |       | 4.2.1 HDMI transmitter: ADV7511         | <br>17 |

|   |     | 4.2.2   | I2C bus switch on ZC706                      | 24 |

|---|-----|---------|----------------------------------------------|----|

|   | 4.3 | Progra  | amming                                       | 25 |

|   |     | 4.3.1   | Introduction                                 | 25 |

|   |     | 4.3.2   | Clock generation                             | 26 |

|   |     | 4.3.3   | Screen resolution                            | 26 |

|   |     | 4.3.4   | HDMI transmitter configuration via I2C       | 27 |

|   |     | 4.3.5   | Conversion from RGB to YCbCr                 | 34 |

|   |     | 4.3.6   | Generation of the screen                     | 36 |

|   | 4.4 | Result  | 58                                           | 39 |

| 5 | Ras | ter plo | ot                                           | 41 |

|   | 5.1 | Comm    | nunication with HEENS                        | 41 |

|   |     | 5.1.1   | Principle                                    | 41 |

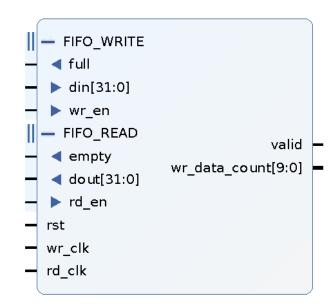

|   |     | 5.1.2   | FIFO signals                                 | 43 |

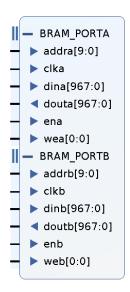

|   |     | 5.1.3   | Block memory signals                         | 44 |

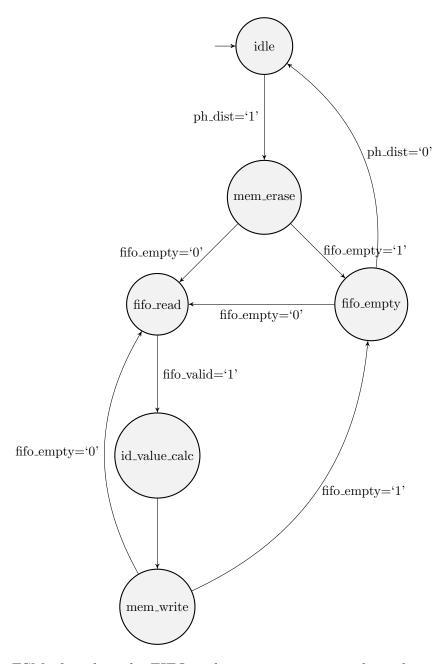

|   |     | 5.1.4   | Reading the FIFO and storing the information | 46 |

|   |     | 5.1.5   | Implementation of the buffer                 | 49 |

|   | 5.2 | Creati  | ing the plot                                 | 50 |

|   |     | 5.2.1   | Information to show                          | 50 |

|   |     | 5.2.2   | Reading the memory and creating the plot     | 54 |

|   |     | 5.2.3   | Extended plot                                | 55 |

|   |     | 5.2.4   | Created packages                             | 57 |

|   | 5.3 | Result  | s with emulated neural network               | 58 |

| 6 | Plo | t of ne | eural parameters                             | 64 |

|   | 6.1 | Comm    | nunication with HEENS                        | 64 |

|   |     | 6.1.1   | Principle                                    | 64 |

|   |     | 6.1.2   | Reading the FIFO and storing the information | 66 |

|   | 6.2 | Creati  | ing the plots                                | 68 |

| 6.3   | Results with emulated neural network                                  | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Exp   | perimental results                                                    | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.1   | Principle                                                             | 71                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.2   | Ring oscillator                                                       | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7.3   | Delay lines                                                           | 74                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Cor   | nclusion and future development                                       | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.1   | Summary                                                               | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 8.2   | Future work                                                           | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| efere | nces                                                                  | 80                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ppen  | $\operatorname{dix}$                                                  | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ADV   | √7511 registers map                                                   | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Fixed registers that must be set                                      | 84                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Main Power Up                                                         | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | HDMI or DVI mode                                                      | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Input Formatting Related Registers                                    | 86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | CSC related registers                                                 | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ZC7   | 06 I2C bus switch                                                     | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Rast  | ter plot results for 2x2 and 6x6 configurations                       | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 6x6 configuration                                                     | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | 2x2 configuration                                                     | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| HEI   | ENS Control Interface registers                                       | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | HEENS Control Interface register map                                  | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | HEENS Transfer Register write operation                               | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | HEENS Monitored Neurons Register write operation                      | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|       | Exp<br>7.1<br>7.2<br>7.3<br>Cor<br>8.1<br>8.2<br>efere<br>ppen<br>ADV | Experimental results 7.1 Principle 7.2 Ring oscillator 7.3 Delay lines  Conclusion and future development 8.1 Summary 8.2 Future work  Seferences  Pependix  ADV7511 registers map Fixed registers that must be set Main Power Up HDMI or DVI mode Input Formatting Related Registers CSC related registers  ZC706 12C bus switch  Raster plot results for 2x2 and 6x6 configurations 6x6 configuration 2x2 configuration HEENS Control Interface register map HEENS Control Interface register map HEENS Control Interface register map HEENS Transfer Register write operation |

# Acknowledgments

I would like to thank all the people who helped me and contributed to my work:

- Bernardo Vallejo for his daily advice, support and help during this thesis. Thank you for your time and the knowledge that you shared,

- Dr. Jordi Madrenas for his great supervision and proofreading of the thesis.

- Sasan Nikseresht and Diana Mata Hernández my other coworkers at the laboratory, thank you for the good working atmosphere you created and support you provided me,

- my flatmates Lydia Iracheta, Andrei Platonov and Rebecca Künnis for their daily psychological support,

- my previous coworkers and great friends Antoine Colson and Salvador Poveda for their help and conscientiousness during all these works,

- Mariline and Rémy Nader for their precious proofreading,

- and finally, my whole family and friends for their love and support.

# Abstract

Artificial Neural Networks (ANNs) are powerful computational tools that are used to solve complex pattern recognition, function estimation and classification problems not manageable by other analytical tools. They are inspired by the structure and function of the human brain and throughout their development, they have been evolving towards more powerful and more biologically realistic models.

A new generation of ANNs: Spiking Neural Networks (SNNs) have been developed. These networks emulate the neurobiological processing of information with temporal dynamics and precise timing. They are energy efficient and amenable to hardware application development. Such hardware SNNs work in real time and thus, having a real-time display makes full sense.

This current thesis presents the realization of a real-time display using High-Definition Multimedia Interface (HDMI) connected to an ongoing project. This project uses HEENS (Hardware Emulator of Evolved Neural System) architecture to implement hardware SNNs on Zyng FPGAs (Field Programmable Gate Arrays).

First of all, the communication to HDMI has been established, on two boards ZedBoard and Zynq ZC706. Screen resolution, video timings and color format have been studied. I2C (Inter-Integrated Circuit) communication has been examined and especially with the slave ADV7511, the HDMI transmitter, whose documentation has been also studied thoroughly. This transmitter has to be configured via I2C to be able to receive the HDMI signals and transmit them to the connector. Finally, all this acquired knowledge has enabled the actual implementation on the boards using VHDL (VHSIC (Very High Speed Integrated Circuit) Hardware Description Language) of the HDMI connection. As a result, bands of colors can be shown on monitor displays.

Then, the representation of the Spiking Neural Network behavior has been made on screen, with plots to display the evolution in real time of the network. Communication has been established between the actual project architecture and the real-time display in order to receive the neural information and store it in a form which will allow their plot. At the same time, text generation has been implemented to be able to write text on screen. VHDL code has been developed to generate the plots with contours, ticks and labels as any standard chart.

The first plot that has been made is the raster plot of the neuron spikes over time. Next, in order to monitor furthermore the Spiking Neural Network, another plot has been implemented to display internal neural parameters. Among these analog parameters, one of the most important is the membrane potential, whose plot has been studied more specifically. In the end, both plots: the raster plot and the membrane potential plot (for four chosen neurons to monitor), are displayed at the same time on the screen.

To conclude, HDMI communication has been established on FPGA in order to monitor a Spiking Neural Network in real time. Two plots are displayed on the screen: the spikes over time and neural parameters for a few selected neurons of the network.

# List of Figures

| 1  | Neuron structure. [5]                                                                                  | 2  |

|----|--------------------------------------------------------------------------------------------------------|----|

| 2  | Spiking neurons and their membrane potential. [3]                                                      | 3  |

| 3  | HEENS architecture with one Master Chip (MC) and $n$ Neuromorphic Chips (NCs) connected as a ring. [3] | 4  |

| 4  | HEENS Finite State Machine. [3]                                                                        | 5  |

| 5  | Block diagram of HEENS Multi-Processor. [3]                                                            | 7  |

| 6  | Virtualization of Processing Element arrays. [3]                                                       | 8  |

| 7  | Picture of ZedBoard                                                                                    | 9  |

| 8  | Picture of Zynq ZC706                                                                                  | 10 |

| 9  | HDMI Block Diagram. [15]                                                                               | 12 |

| 10 | Screen areas (drawing pixels and blank interval). [18]                                                 | 14 |

| 11 | Chroma subsampling 4:4:4 vs 4:2:2 vs 4:2:0. [23]                                                       | 16 |

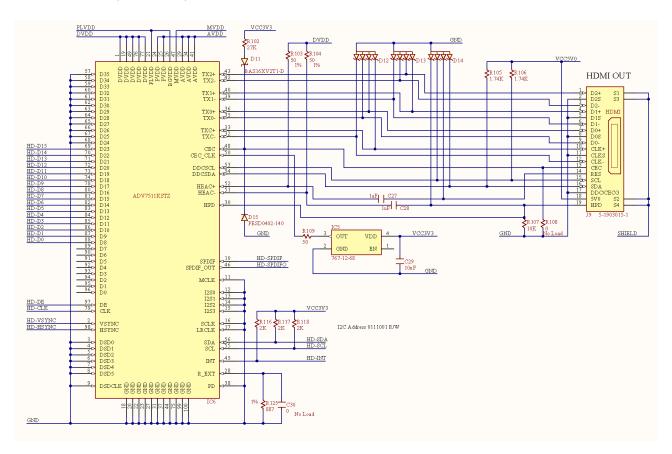

| 12 | Schematic of the ADV7511 chip connections on ZedBoard. [26]                                            | 17 |

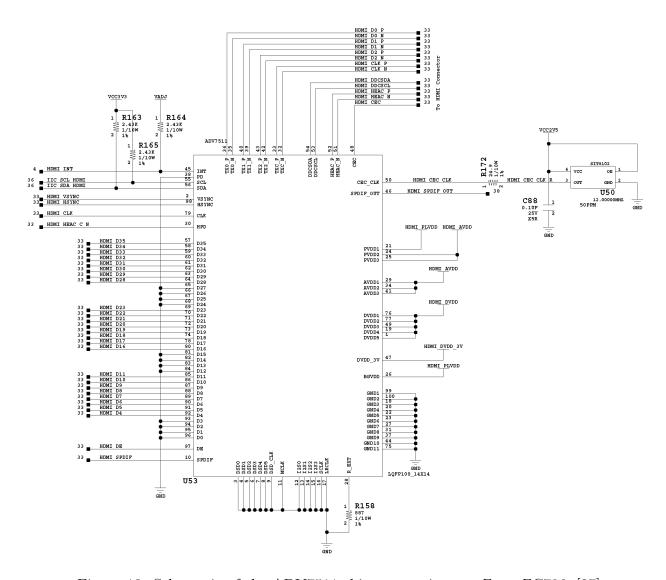

| 13 | Schematic of the ADV7511 chip connections on Zynq ZC706. [27]                                          | 18 |

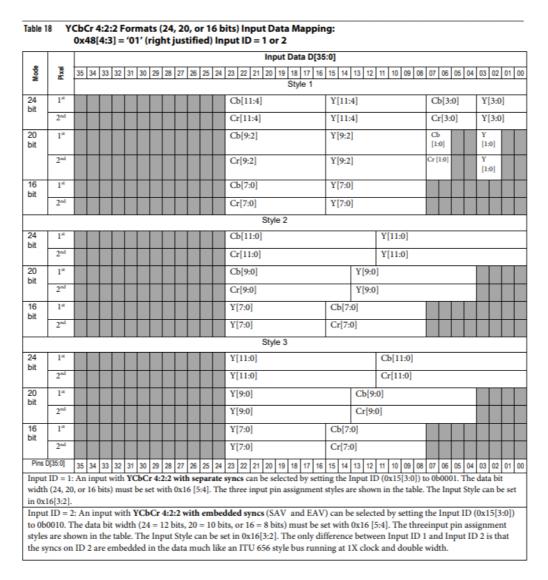

| 14 | Table of color data pins corresponding to input ID 1 and 2 on ADV7511. [28]                            | 19 |

| 15 | Table of color data pins corresponding to input ID 0 on ADV7511. [28]                                  | 20 |

| 16 | I2C bus topology on ZC706. [29]                                                                        | 24 |

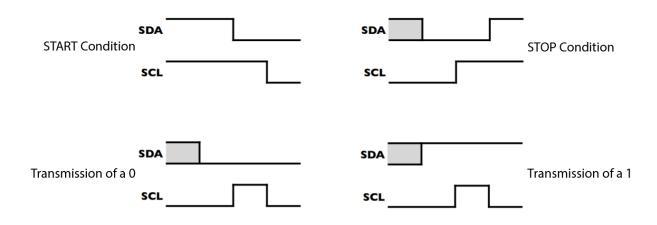

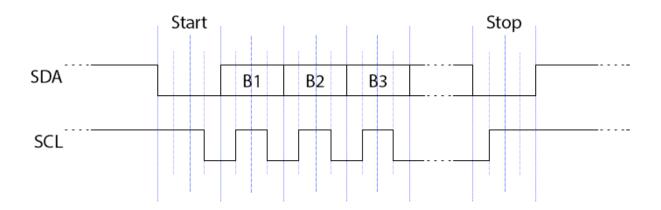

| 17 | I2C events. [32]                                                                                       | 27 |

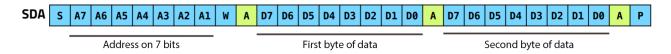

| 18 | I2C writing frame with two bytes of data. [32]                                                         | 28 |

| 19 | I2C reading frame with two bytes of data. [32]                                                         | 28 |

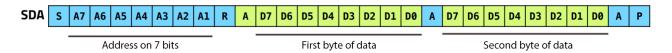

| 20 | FSM of the I2C sending process                                                                         | 29 |

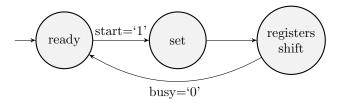

| 21 | I2C clocks                                                                                             | 30 |

| 22 | SDA and SCL signals during an I2C frame example                                                        | 31 |

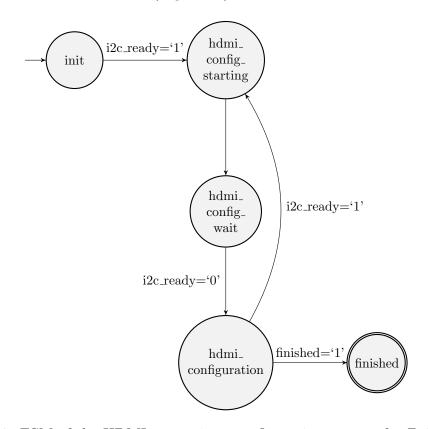

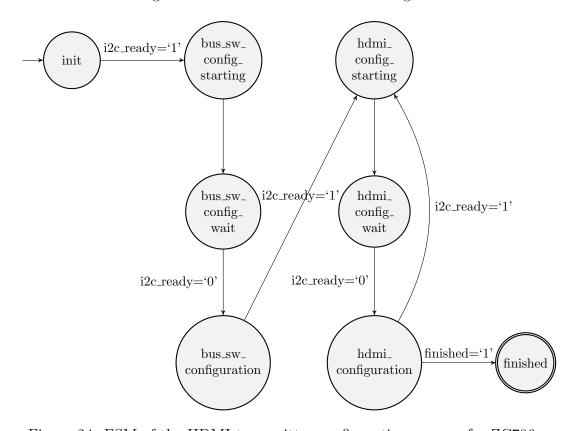

| 23 | FSM of the HDMI transmitter configuration process for ZedBoard                                         | 32 |

| 24 | FSM of the HDMI transmitter configuration process for ZC706                                            | 33 |

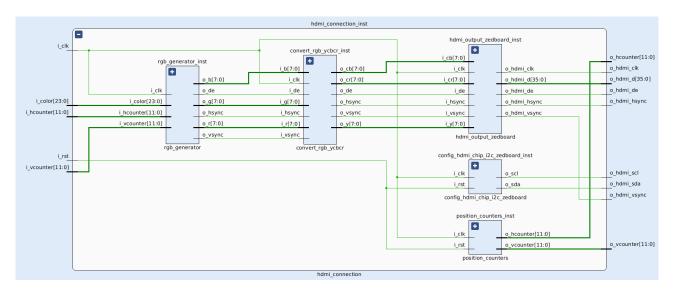

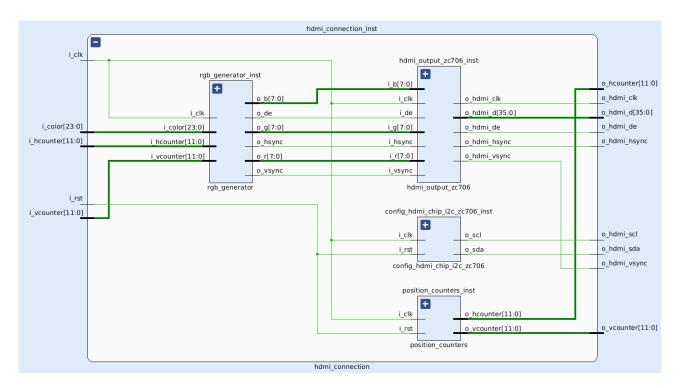

| 25 | Schematics of the hdmi_connection component on ZedBoard                                                | 36 |

| 26 | Schematics of the hdmi_connection component on ZC706                                                   | 36 |

| 27  | Result screen of the HDMI test                                                                                            | 39 |

|-----|---------------------------------------------------------------------------------------------------------------------------|----|

| 28  | FIFO input/output ports of the spikes                                                                                     | 43 |

| 29  | Block memory input/output ports of the spikes information                                                                 | 44 |

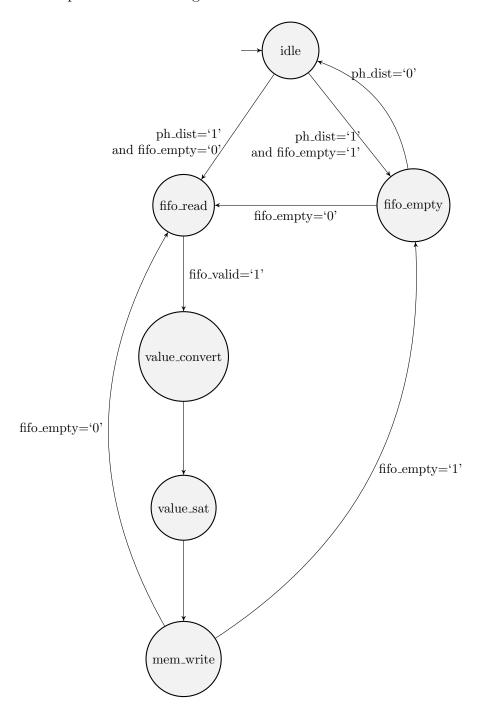

| 30  | FSM of reading the FIFO and writing in memory the spikes information                                                      | 46 |

| 31  | Example of character representation: the 'A' character                                                                    | 50 |

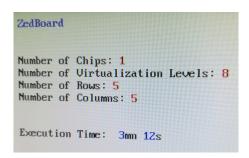

| 32  | Result screen of the raster plot implementation for ZedBoard with $5\mathrm{x}5$ array                                    | 59 |

| 33  | Result screen of the raster plot implementation for ZedBoard with 5x5 array (zoomed on the top left information)          | 59 |

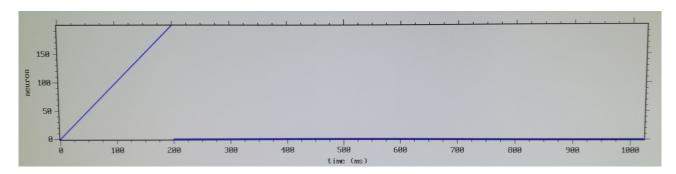

| 34  | Result screen of the raster plot implementation for ZedBoard with 5x5 array (zoomed on the plot)                          | 60 |

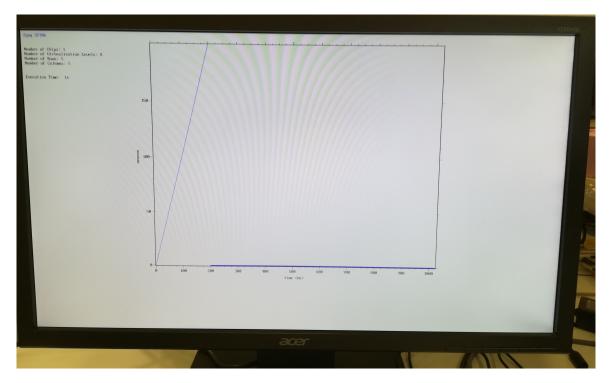

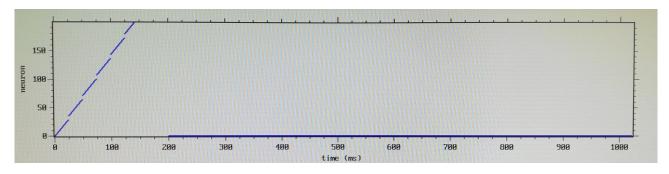

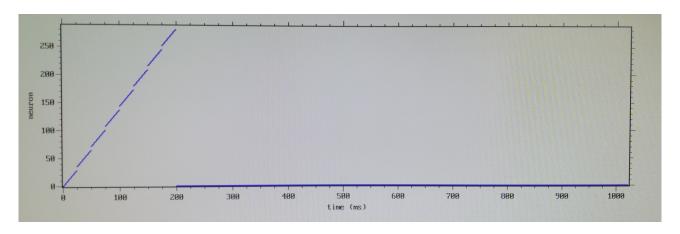

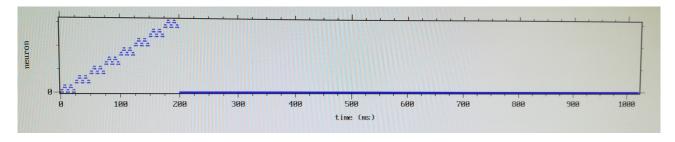

| 35  | Result screen of the raster plot implementation for ZedBoard with 5x5 array with the extended plot                        | 61 |

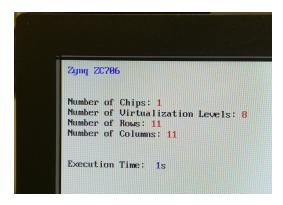

| 36  | Result screen of the raster plot implementation for ZC706 with 11x11 array (zoomed on the top left information)           | 62 |

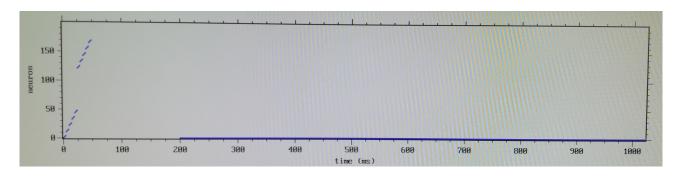

| 37  | Result screen of the raster plot implementation for ZC706 with 11x11 array (zoomed on the plot)                           | 62 |

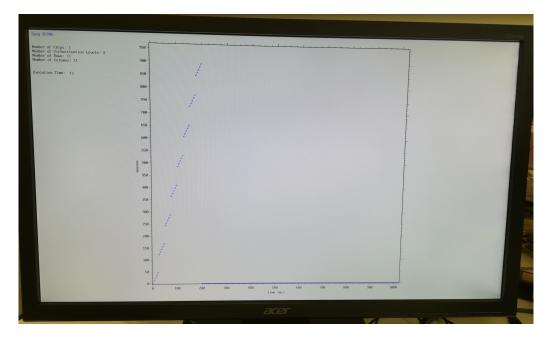

| 38  | Result screen of the raster plot implementation for ZC706 with 11x11 array with the extended plot                         | 63 |

| 39  | FSM of reading the FIFO and writing in memory the potential information                                                   | 66 |

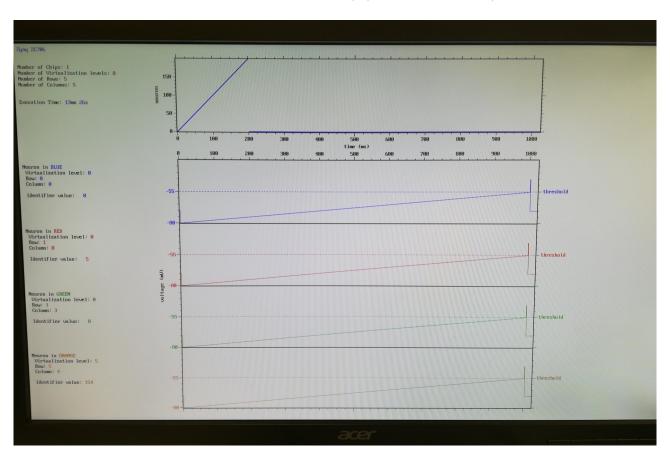

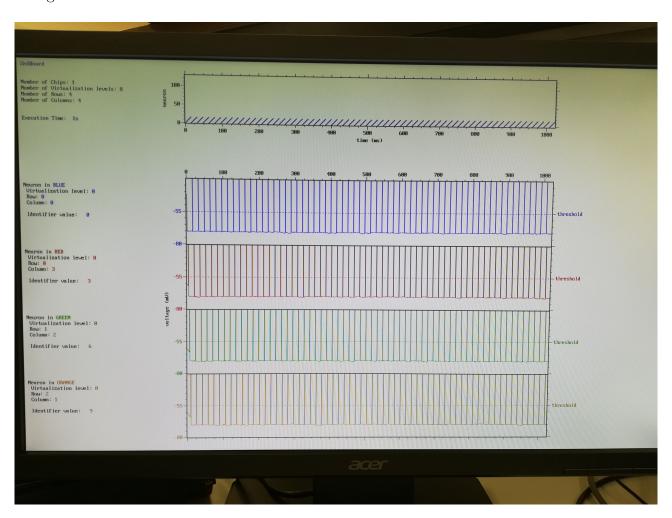

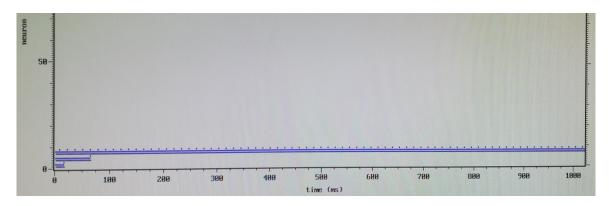

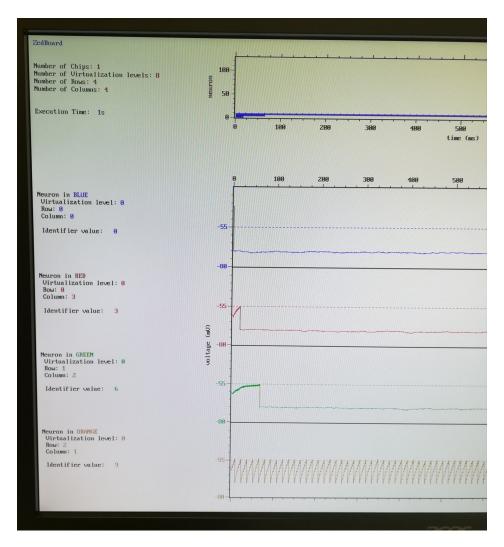

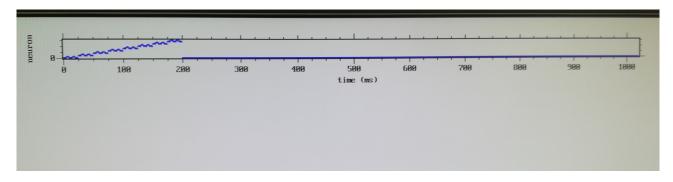

| 40  | Result screen of the membrane potential plot implementation for ZedBoard with 5x5 array                                   | 69 |

| 41  | Result screen of the membrane potential plot implementation for ZedBoard with 5x5 array (zoomed at the left of the plots) | 70 |

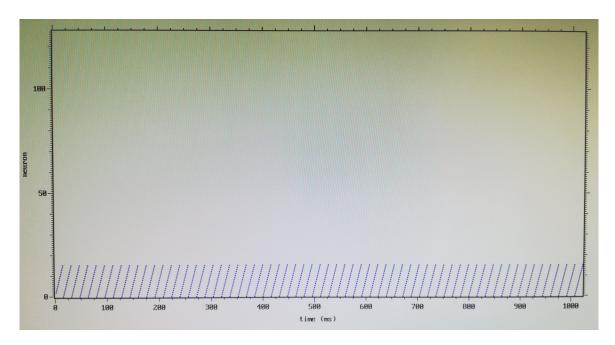

| 42  | Result screen of the ring oscillator example on ZedBoard with 4x4 array                                                   | 72 |

| 43  | Result screen of the ring oscillator example on ZedBoard with 4x4 array, in the extended configuration of the raster plot | 73 |

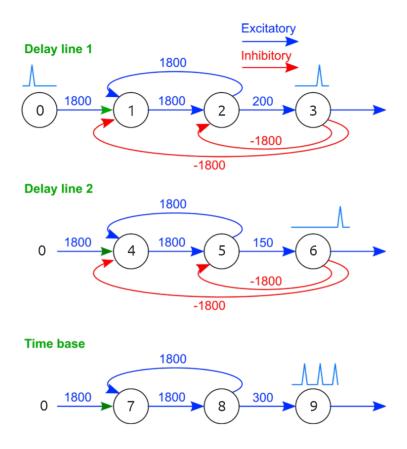

| 44  | Example of two delay lines with short and longer delays, and time base. [40]                                              | 74 |

| 45  | Result screen of the delay lines example on ZedBoard with 4x4 array, in the extended configuration of the raster plot     | 75 |

| 46  | Result screen of the delay lines example on ZedBoard with 4x4 array, zoomed on the left of the screen                     | 75 |

| A.1 | Table of fixed registers that must be set. [28]                                                                           | 84 |

| A.2  | Register map of 0x9D. [28]                                                                      | 84 |

|------|-------------------------------------------------------------------------------------------------|----|

| A.3  | Register map of 0x41. [28]                                                                      | 85 |

| A.4  | Table of HDMI or DVI mode. [28]                                                                 | 85 |

| A.5  | Register map of 0xAF. [28]                                                                      | 85 |

| A.6  | Register map of 0x15. [28]                                                                      | 86 |

| A.7  | Register map of 0x16. [28]                                                                      | 86 |

| A.8  | Register map of 0x17. [28]                                                                      | 87 |

| A.9  | Register map of 0x48. [28]                                                                      | 87 |

| A.10 | Table of CSC - HDTV YCbCr (Limited Range) to RGB (Full Range). [28] $\ .$                       | 88 |

| A.11 | Table of CSC - Identity Matrix (Input = Output). [28] $\dots \dots \dots \dots$                 | 88 |

| A.12 | I2C slaves address on ZC706. [29]                                                               | 89 |

| A.13 | Result screen of the raster plot implementation for ZC706 with 6x6 array (zoomed on the plot)   | 90 |

| A.14 | Result screen of the raster plot implementation for ZC706 with 6x6 array with the extended plot | 90 |

| A.15 | Result screen of the raster plot implementation for ZC706 with 2x2 array (zoomed on the plot)   | 92 |

| A.16 | Result screen of the raster plot implementation for ZC706 with 2x2 array with the extended plot | 92 |

# List of Tables

| 1   | Screen areas size for 3 different resolutions. [18, 19]                  | 14 |

|-----|--------------------------------------------------------------------------|----|

| 2   | Pixel clock for 3 different resolutions                                  | 15 |

| 3   | Register map for ADV7511 for both ZedBoard and ZC706 boards              | 22 |

| 4   | Register map (CSC) for ADV7511 for both ZedBoard and ZC706 boards        | 23 |

| 5   | Factors decomposition in powers of two, for RGB to HDTV YCbCr conversion | 35 |

| A.1 | HCI Registers map. [42]                                                  | 93 |

| A.2 | HTR register (write operation). [42]                                     | 93 |

| A.3 | HMNR register (write operation). [42]                                    | 95 |

# Acronyms

**AER-SRT** Address Event Representation over Synchronous Serial Ring.

AI Artificial Intelligence.

**ANN** Artificial Neural Network.

**ASCII** American Standard Code for Information Interchange.

**BRAM** Block RAM (Random-Access Memory).

CDC Clock Domain Crossing.

**CEC** Consumer Electronics Control.

**CSC** Color Space Conversion.

**DDC** Display Data Channel.

**DDR** Double Data Rate.

**DMA** Direct Memory Access.

**DSP** Digital Signal Processor.

**DVI** Digital Visual Interface.

FIFO First In/First Out.

**FPGA** Field Programmable Gate Array.

FSM Finite State Machine.

**HCI** HEENS Control Interface.

**HDMI** High-Definition Multimedia Interface.

**HDTV** High Definition Television.

**HEENS** Hardware Emulator of Evolved Neural System.

**HEENS-MP** HEENS Multi-Processor.

HMNR HEENS Monitored Neurons Register.

**HSR** HEENS Status Register.

HTR HEENS Transfer Register.

HTS HEENS Toolchain Suite.

I2C Inter-Integrated Circuit.

**ID** Identifier.

IO Input/Output.

**IP** Intellectual Property.

LCM Least Common Multiple.

LIF Leaky Integrate-and-Fire.

LSB Least Significant Bit.

MC Master Chip.

MIF Memory Initialization File.

MSB Most Significant Bit.

**NC** Neuromorphic Chip.

PC Personal Computer.

**PE** Processing Element.

**PL** Programmable Logic.

**PLL** Phase-Locked Loop.

**PS** Processing System.

**RAM** Random-Access Memory.

**RGB** Red, Green and Blue.

**ROM** Read-Only Memory.

RTL Register Transfer Level.

SCL Serial Clock.

SDA Serial Data.

**SDK** Software Development Kit.

**SDTV** Standard Definition Television.

**SIMD** Single Instruction Multiple Data.

**SNAVA** Spiking Neural Architecture for Versatile Applications.

**SNN** Spiking Neural Network.

TMDS Transition Minimized Differential Signaling.

**VESA** Video Electronics Standards Association.

VGA Video Graphics Array.

VHDL VHSIC (Very High Speed Integrated Circuit) Hardware Description Language.

VHSIC Very High Speed Integrated Circuit.

WNS Worst Negative Slack.

YCbCr Luma (Y), Blue-difference Chroma (Cb) and Red-difference Chroma (Cr).

# 1 Introduction

Artificial Neural Networks (ANNs) are powerful computational tools that allow solving complex pattern recognition, function estimation and classification problems that are not easily manageable by analytical tools outside of Artificial Intelligence (AI). They are inspired by the structure and function of the human brain and throughout their development, they have been evolving towards more powerful and more biologically realistic models. [1]

The third generation Spiking Neural Network (SNN) has been developed, which emulates the neurobiological processing of information with temporal dynamics and precise timing. In addition, with their digital signaling and sparse coding, SNNs are energy efficient and amenable to hardware application development. [1, 2]

Hardware SNNs can work in real time and thus having a real-time display of their operation makes full sense.

This current thesis presents the realization of a real-time display of SNN using High-Definition Multimedia Interface (HDMI), connected to an ongoing project.

This project is an implementation of a hardware architecture for general-purpose Spiking Neural Network. It is designed with a large scalability, reconfigurability and programmability to display the operation of neuronal models. [3]

It uses a new version of SNAVA (Spiking Neural Architecture for Versatile Applications) [4] called HEENS (Hardware Emulator of Evolved Neural System), which saves significant amount of control resources, compared to the other architectures and provides programmable connectivity. [5]

The HEENS architecture has been implemented on Zynq FPGAs (Field Programmable Gate Arrays) containing both an integrated Processing System (PS) and Programmable Logic (PL). In addition, a toolchain HTS (HEENS Toolchain Suite) has been developed and used to prototype, configure and execute the SNNs on the hardware. [5]

The goal of this thesis is to establish the HDMI communication between the PL of the FPGA and a monitor screen in order to display in real time the SNN operation.

In order to see and understand the behavior of the Spiking Neural Network with real-time display, a raster plot of the neuron spikes over time will be made, as well as the monitoring of some neurons through a plot of analog values such as their membrane potential.

# 2 State of the art

# 2.1 Biological neurons

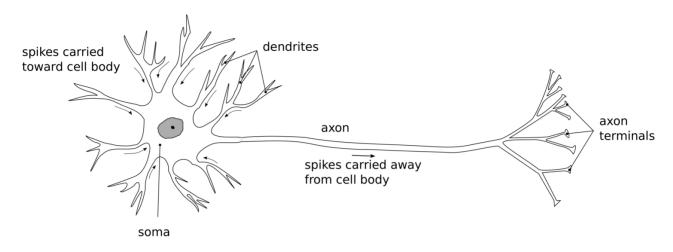

Human brain is composed of billions of interconnected neurons that communicate via electrical spikes transmitted through synapses. Neurons are composed by three parts: dendrites, soma and axon (Figure 1). [3]

Figure 1: Neuron structure. [3]

Dendrites behave as input points which receive and collect electrical signals from other neurons through synapses, and transmit them to the soma. The soma acts as the process unit of the neuron which manages the whole cell. The axon is the output canal which transmits generated spikes to its axon terminals, to connect through synapses to the next neurons. [3]

# 2.2 Artificial Neural Networks

Artificial Neural Networks (ANNs) are biologically inspired computational networks. They simulate the electrical activity of the biological brain. Processing Elements (PEs) are connected to each other by weighted links to inhibit or amplify the connection. It is through the adjustment of these connection weights that learning is emulated in ANNs. [6, 7, 8]

ANNs are used in a wide range of scientific fields such as finance, hydrology, or image and voice recognition. These applications can be regrouped into three categories of Artificial Intelligence: pattern classification, prediction, and control and optimization. [9]

# 2.3 Spiking Neural Networks

New models of Artificial Neural Networks have appeared that try to get closer and closer to the biological nervous system. During last years, a model has been the topic of much research: Spiking Neural Networks (SNNs), which is considered as the third generation of ANNs. These networks have a behavior closer to biological neurons by utilizing spikes, which enables to integrate the concepts of space and time. Their implementation is also easier than standard ANNs and can be made on fast and reliable hardware platforms. Indeed, they do not use multiplications, and the connection with spikes means only to send a single bit and not real number as other ANNs. [3, 10]

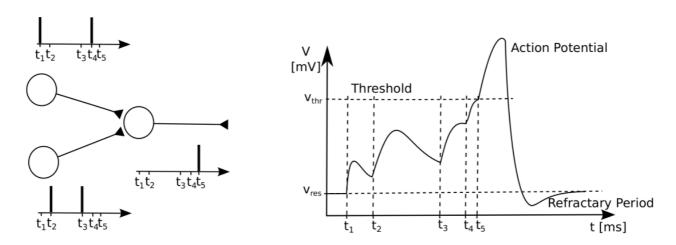

Each time a neuron receives a spike, its membrane potential increases as a function of the weight of the link (Figure 2). When it reaches the threshold  $(V_{thr})$ , it increases by an action potential (it fires) before decreasing below the resting potential  $(V_{res})$ . At the threshold potential, the neuron produces a spike. Membrane potential decays with time to converge to the resting potential.

Figure 2: Spiking neurons and their membrane potential. [3]

Different neuron models exist to integrate this behavior into hardware, such as Leaky Integrate-and-Fire (LIF) model, Hodgkin–Huxley model or Izhikevich model. [10]

## 2.4 HEENS architecture

Hardware Emulator of Evolved Neural System (HEENS) is a hardware implementation of Spiking Neural Networks. The current project implements this HEENS architecture.

#### Description of the HEENS architecture

HEENS is an evolution of the SNAVA architecture [4]. It is characterized by a better resource utilization and by an enhanced programmability and scalability capabilities. Indeed, it allows the user to decide the number of Processing Elements (PEs) in the two-dimension array (rows and columns) and the number of virtual layers as a third spatial dimension. It supports also an online dynamic evolution and reconfiguration of the synapses interconnections. [3, 11]

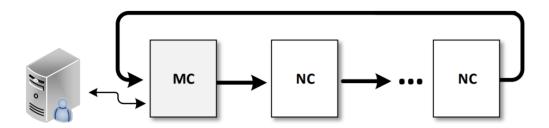

This architecture can interconnect multiple chips in a ring topology (Figure 3). The Master Chip (MC) manages the network to configure and reconfigure the other nodes. It communicates with the general purpose processor and receives the instructions for the initialization and configurations.

Figure 3: HEENS architecture with one Master Chip (MC) and n Neuromorphic Chips (NCs) connected as a ring. [3]

During the neural application, the MC behaves like any other chip. These other chips, called Neuromorphic Chips (NCs), process the neural algorithm. The MC collects the spikes from the other chips as well as from its own PEs. It then updates the neural and synaptic parameters such as the membrane potential. Finally, it distributes to the network the post-synaptic spikes.

### **HEENS** process phases

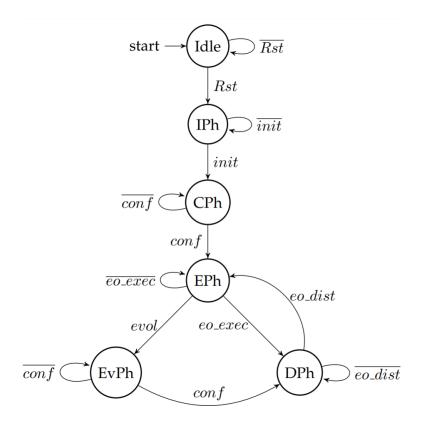

The process is split in five phases (Figure 4): the initialization (IPh), the configuration (CPh), the execution (EPh), the evolution (EvPh) and the distribution (DPh).

Figure 4: HEENS Finite State Machine. [3]

The process remains in the idle phase as long as the reset has not occurred. The registers are set to their default value.

- The initialization is made at a reset. The MC assigns the chip Identifier (ID) relative to each node, and transmits the ring size to the network.

- The configuration occurs after the initialization. The MC sends to the PEs their neural algorithm, their synaptic and neural parameters, as well as the map of the synaptic connections to the other PEs. Once all chips are configured, the configuration phase ends.

- In the execution phase, the neural algorithms are computed in a parallel way by each PE. Their states variables are updated. Once finished, the flag *eo\_exec* is raised and the process can go to the next state.

- In the distribution phase, the spikes that have occurred are collected by the MC and broadcast to the network. Additionally, data will be sent to the PC (Personal Computer) in this state, and the communication with the real-time display that we will see in this thesis will also be made.

- Actually, the data is not sent to the PC at each distribution phase. It is stored in a FIFO (First In/First Out) memory and when the FIFO is half-full, the data is sent via Ethernet to the PC, while the other half starts to get filled in. This feature has been created instead of sending each time the data to increase the velocity, as the application development with Ethernet is slow. Thus, this thesis work is important to display the real-time behavior of the SNN, which cannot be done otherwise.

- At the end of each execution phase, the system checks if it has received an evolution command from the user. If it is the case, the system goes to the evolution phase instead of the distribution phase. The MC will send the newly received information to the selected PEs. They will then reconfigure themselves accordingly by adjusting their neural and synaptic parameters. Once all selected chips are re-configured, the evolution phase ends, and the system goes to the distribution phase.

The time unit is defined as the number of emulation cycles. These cycles include the execution and distribution phases (as well as the evolution phase if it appears), once the initialization and configuration have been realized.

#### **HEENS Multi-Processor**

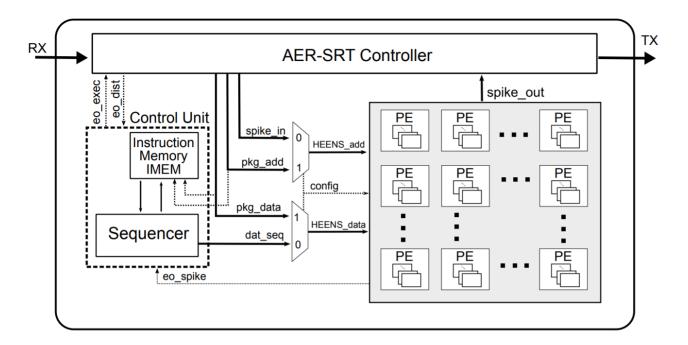

The HEENS Multi-Processor (HEENS-MP) that can be seen in Figure 5 corresponds to a Neuromorphic Chip. It uses a SIMD (Single Instruction Multiple Data) computation scheme with a single control unit to achieve parallelism at data level in the PE array. This reduces area and gives a better computing efficiency. [3]

Figure 5: Block diagram of HEENS Multi-Processor. [3]

The chip is composed mainly by:

- communication buses: they permit information flow;

- the Processing Element array: each PE is a unit of SIMD-type execution, which processes the instructions of the neural algorithm;

- the control unit: it is in charge of managing the whole flow of data and instructions of the PE array, thanks to its sequencer. In addition, it generates the control signals to synchronize operations with the AER-SRT controller;

- the Address Event Representation over Synchronous Serial Ring (AER-SRT) controller: once PEs have processed their neural algorithm, a swept is made to get all the post-synaptic spikes. The spikes generated in each execution phase are encoded and gathered into a FIFO. This FIFO is read during the distribution phase and the post-synaptic spikes are transmitted to the network.

#### Address format of the Processing Elements

Each neuron (or PE) possesses an ID (Identifier) defined on 18 bits: 7 for the chip ID, 3 for the virtualization level, 4 for the row and 4 for the column.

The chip ID enables to know on which chip of the ring architecture the neuron is.

PEs can multiplex their behavior in time to emulate more than one neuron in an execution cycle. These additional neurons are said to be on virtualisation levels. Level 0 represents the physical layer (the HUB neurons). In addition, HEENS architecture accepts 7 other levels of virtualization (for a total of 8 levels) (Figure 6). [3, 11]

Each of these levels of virtualization has a PE array of a certain number of rows and columns.

Figure 6: Virtualization of Processing Element arrays. [3]

# 3 Project development

# 3.1 Current state of the project

The project implements HEENS architecture on FPGAs and uses a toolchain (HTS) developed in Python in order to configure the Spiking Neural Network. This toolchain also provides a plot of the spiking neurons over time, but it is not in real time because of bandwidth and communication limitations, so it is necessary to wait to receive the information on the PC before displaying them.

For now, the project has been defined for two different types of boards: ZedBoard (Figure 7) and Zynq ZC706, a more complex board (Figure 8).

Figure 7: Picture of ZedBoard.

Figure 8: Picture of Zynq ZC706.

The neurons possess IDs defined on 18 bits: 4 for the column, 4 for the row, 3 for the virtualization level and 7 for the chip ID.

The project has not yet developed the virtualization levels, nor the connection to other boards. Thus, the number of neurons is only defined by the size of the Processing Element array on the Master Chip. Due to physical limits, on ZedBoard, arrays up to 5x5 can be defined, and on ZC706, up to 13x13.

The emulation time slot (the duration of the execution and distribution phases) in real time is set to 1 ms. This value has been chosen in order to have an onscreen display that is not too fast.

The data arising from the neurons is composed by the information that the neurons have produced a spike or not during the last execution phase, as well as internal neural parameters such as their membrane potential.

These spikes can be represented over time with as vertical axis the number of the neuron that has produced them. This is called a raster plot. Its display onscreen will be seen later in this document, along with the plot of neural parameters.

# 3.2 Vivado software and VHDL language

The thesis development has been made on the PL (Programmable Logic) in VHDL (VHSIC (Very High Speed Integrated Circuit) Hardware Description Language). The software used is Vivado from Xilinx.

Verilog can also be used on Vivado in addition to VHDL. Besides, Xilinx provides a Software Development Kit (SDK) to create embedded applications on FPGA microprocessors (in C or C++ languages). The Processing System (PS) of both boards is a Zynq 7.

However, since in this thesis we are only working on the Programmable Logic (PL), the SDK is not necessary and all the current work can be done with Vivado.

In addition to the VHDL code, a constraint file is required (of extension .xdc for Xilinx Design Constraints). It contains the design constraints and in particular the definition of the physical pins of the board, their association to signals to be used in the code, as well as the voltage of the corresponding IO (Input/Output) pin banks. This file also contains the creation of the clock to specify to the software the clock constraints so that it is able to create timing reports and gives the slack values especially the Worst Negative Slack (WNS).

Once the Register Transfer Level (RTL) design is done (the VHDL code) and the constraints file is written, synthesis is realized to transform the RTL-specified design into a gate-level representation. Then, the implementation is performed to optimize the logic design, to place the logic cells of the design and to route the connection between the cells. Finally, a bitstream is generated to configure the device. [12, 13]

For the system verification and debugging, simulations can be done in order to check the behavior of any component with a plot of the signals against time. This helps understand precisely what happens to each signal. For example, it helps to understand the behavior of IPs (Intellectual Properties) [14] and their signals timings. Indeed, they are not defined by the user, so it can be hard to understand them fully. Simulations also helps to check that the components behave as expected and their interconnections.

To keep track of the advancement of the whole HEENS project, a Git repository was created. It contains the two different Vivado projects for the two boards, the Verilog and VHDL files for the PL, the C and C++ files for the PS, as well as the Python files of the toolchain. Git makes easier to have different people working on a single project, as each one can work on their own separated branches. And also, it allows to return to previous states, to check what changes have been made since then, and to incorporate some of these changes into the current state.

# 4 Screen display via HDMI

# 4.1 Principle

#### 4.1.1 Introduction

The High-Definition Multimedia Interface (HDMI) is provided for transmitting digital television audiovisual signals from DVD players, set-top boxes and other audiovisual sources to television sets, projectors and other video displays. [15]

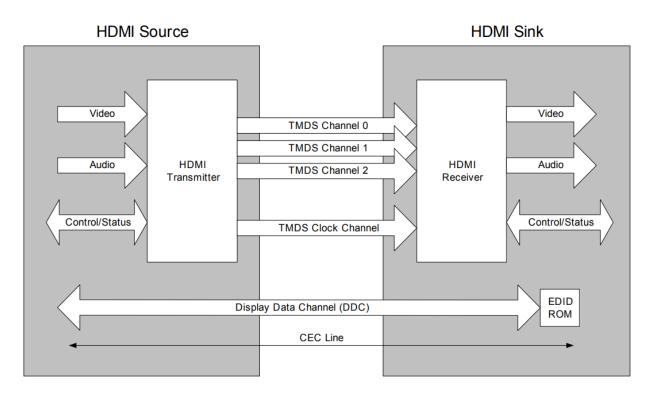

The HDMI cable and connectors carry four differential pairs that make up the TMDS (Transition Minimized Differential Signaling) data and clock channels (Figure 9). These channels are used to carry video, audio and auxiliary data.

In addition, there is a VESA (Video Electronics Standards Association) Display Data Channel (DDC) used for configuration and status exchange between a source and a sink; and there is a CEC (Consumer Electronics Control) line that is optional and provides high-level control functions.

Figure 9: HDMI Block Diagram. [15]

The 3 TMDS data channels contain the audio, video and auxiliary data. The TMDS clock channel is typically at the video pixel rate, and is used as a frequency reference for the receiver to read the data channels.

In the project, audio is not used.

Video data can have a pixel size of 24, 30, 36 or 48 bits. The default 24-bits color depth requires a TMDS clock equal to the pixel clock rate, and higher color depths require faster TMDS clocks. The video pixels can be encoded in the color formats RGB, YCbCr 4:4:4 or YCbCr 4:2:2.

### 4.1.2 Aspect ratio and video resolution

The video resolution is the size in pixels of the height and the width of an image, video or screen. The aspect ratio corresponds to the ratio between the width and the height pixel sizes.

Monitors screen have had different aspect ratios. During 1990s, the most common one was 4:3, which corresponded also to the television and cinema formats (even though cinema would soon use 16:9). Then, in 2004, 16:10 resolution appears for computer monitors, it enables the display of two full pages of text side-by-side on one screen. [16] Finally, in 2008, television adopted the standard 16:9, followed by the computer monitors. [17]

The studied resolutions are:

- HD, High Definition (720p), 1280x720, aspect ratio 16:9;

- FHD, Full High Definition (1080p), 1920x1080, aspect ratio 16:9;

- WSXGA+, Widescreen Super Extended Graphics Array Plus, 1680x1050, aspect ratio 16:10.

The first two resolutions are the classical ones for HDMI (without going to very high definition), with 1080p being the default resolution of the project. The last one corresponds to the first screen that was used, which was older.

### 4.1.3 Video timings

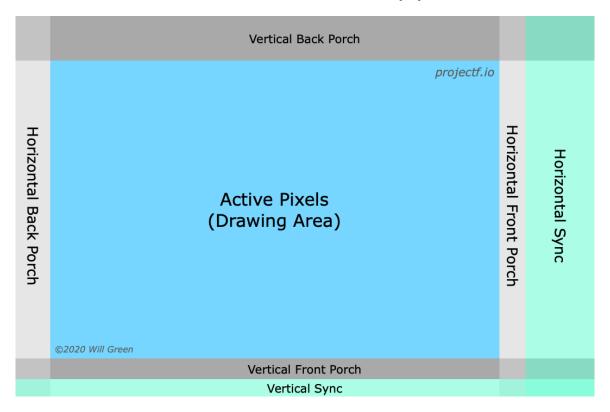

In order to work with screens using FPGAs with either VGA (Video Graphics Array), DVI (Digital Visual Interface) or HDMI (High-Definition Multimedia Interface) protocols, video timings need to be respected. The transmission of a frame is separated in two phases: drawing pixels and blank interval. This blank interval is split, for both horizontal and vertical directions, between the back porch before the visible screen, the front porch after and finally the synchronization area (Figure 10). The horizontal synchronization signal separates two vertical lines, while the vertical signal separates two frames. [18]

Figure 10: Screen areas (drawing pixels and blank interval). [18]

These area sizes are defined as a convention for the different resolutions (Table 1). Another important parameter is the polarity of the synchronization signals, whether they need to be high during the synchronization pulse and low the rest of time, or the contrary.

| Screen     | Aspect              |       | Hor   | rizontal |          |       | Ve    | rtical |          |

|------------|---------------------|-------|-------|----------|----------|-------|-------|--------|----------|

| resolution | Aspect  <br>  ratio | Back  | Front | Sync     | Sync     | Back  | Front | Sync   |          |

| resolution | 14010               | porch | porch | width    | polarity | porch | porch | width  | polarity |

| 1280x720   | 16/9                | 220   | 110   | 40       | positive | 20    | 5     | 5      | positive |

| 1920x1080  | 16/9                | 148   | 88    | 44       | positive | 36    | 4     | 5      | positive |

| 1680x1050  | 16/10               | 288   | 104   | 184      | negative | 33    | 1     | 3      | positive |

Table 1: Screen areas size for 3 different resolutions. [18, 19]

The specifications of the sizes of these areas define the total number of pixels to be drawn for one frame. Then, the refresh rate of the screen defines the pixel clock at which the FPGA has to work in order to communicate with the screen (Table 2). The studied monitors work with a refresh rate of 60 frames per second.

| Screen     | Total           | Total         | Total number | Pixel clock          | Typical           |

|------------|-----------------|---------------|--------------|----------------------|-------------------|

| resolution | horizontal size | vertical size | of pixels    | 1 IXEI CIOCK         | pixel clock       |

| 1280x720   | 1650            | 750           | 1237500      | $74.25\mathrm{MHz}$  | 75 MHz            |

| 1920x1080  | 2200            | 1125          | 2475000      | $148.50\mathrm{MHz}$ | $150\mathrm{MHz}$ |

| 1680x1050  | 2256            | 1087          | 2452272      | $147.13\mathrm{MHz}$ | $150\mathrm{MHz}$ |

Table 2: Pixel clock for 3 different resolutions.

For practical reasons and because HDMI communication still works fine, rounded pixel clocks have been selected for the project. In order to work for screen resolution of 1920x1080 which is the default one, and at 1680x1050 which is the first one used with the old screen, the pixel clock was fixed at 150 MHz.

### 4.1.4 Color format

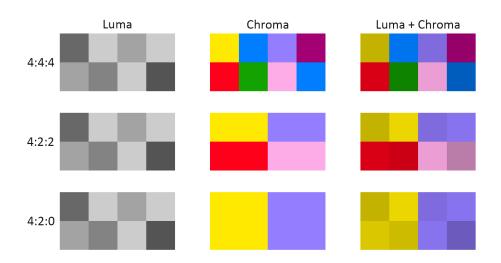

To communicate via HDMI, different color formats can be used. The simplest one is RGB which uses the classical separation of the color between red, green and blue, and each of these components is defined on 8, 10 or 12 bits. Another format is YCbCr which uses also three signals on 8, 10 or 12 bits: Y is the luminance component (the brightness), and Cb and Cr are the color difference signals respectively for blue and red. [20, 21]

This second color format YCbCr is often used when noises are a prevalent problem, or simply when we want to reduce the size of color data. Indeed, human eye is very sensitive to luminance (or luma) which corresponds to Y signal, but less to chrominance (or chroma) which corresponds to Cb and Cr signals. Thus, we can dedicate more bits for Y and fewer bits for Cb and Cr, whereas with RGB we need many bits for each of the three colors to maintain a good image quality. [22]

YCbCr format enables the use of chroma subsampling. It is a compression that keeps a good luminance signal but reduces its color information. [23] As seen before, this does not affect much the quality of the image.

To talk about this compression, the terms 4:4:4, 4:2:2 and 4:2:0 are often used. The first number corresponds to the horizontal sampling reference (usually 4), the second one to the number of chroma samples in the first row, and the third one to the number of new chroma samples in the second row (usually it is either equal to the second number or zero). [23, 24, 25]

4:4:4 has no compression, 4:2:2 has a horizontal resolution halved and a full vertical resolution, and 4:2:0 has a horizontal and vertical resolution halved (Figure 11).

Figure 11: Chroma subsampling 4:4:4 vs 4:2:2 vs 4:2:0. [23]

In addition to subsampling considerations, there are two formats for YCbCr: SDTV (Standard Definition Television) and HDTV (High Definition Television). Since the screen resolutions for the project correspond to high definition, the format will be HDTV YCbCr.

# 4.2 Hardware specification

### 4.2.1 HDMI transmitter: ADV7511

Our FPGA cards (ZedBoard and Zynq ZC706) provide both a HDMI transmitter integrated circuit called ADV7511, for the HDMI output. This chip has first to be programmed via I2C (Inter-Integrated Circuit). Then, it will receive the pixel clock signal ( $hdmi\_clk$ ), the synchronization signals ( $hdmi\_hsync$  and  $hdmi\_vsync$ ), the data enable signal ( $hdmi\_de$ ) and the data color signals ( $hdmi\_d$  vector). In return, it will create the 3 TMDS data channels and the TMDS clock channel, as well as the auxiliary data channels, which will then be sent and carried by the HDMI connector.

### Color signals configuration

These data color signals correspond to 36 pins on the chip. However, on the Zedboard, only 18 pins are connected (Figure 12), which correspond to pins 8 to 23, and on the ZC706, 24 pins are connected (Figure 13), which correspond to pins 4 to 11, 16 to 23 and 28 to 35.

Figure 12: Schematic of the ADV7511 chip connections on ZedBoard. [26]

Figure 13: Schematic of the ADV7511 chip connections on Zynq ZC706. [27]

Now that we are aware of the connection available with the chip ADV7511 for both boards, we can study the manual of this HDMI transmitter [28] in order to configure it.

The ZedBoard that uses the data pins from 8 to 23 corresponds to Table 18 of the datasheet [28] (Figure 14).

Figure 14: Table of color data pins corresponding to input ID 1 and 2 on ADV7511. [28]

We need a color format YCbCr 4:2:2 with 16 bits. I have decided to use style 3, with Y being sent on bits 16 to 23, and on bits 8 to 15: Cb for the first pixel and Cr for the second. The chroma signals have half horizontal resolution.

ZC706 with its 24 pins corresponds to Table 16 of the datasheet [28] (Figure 15).

| o o                                           | Input Data D[35:0] |               |           |        |    |       |    |    |        |       |    |                 |        |    |    |    |         |    |       |    |      |     |      |      |     |      |    |   |  |  |  |  |  |  |

|-----------------------------------------------|--------------------|---------------|-----------|--------|----|-------|----|----|--------|-------|----|-----------------|--------|----|----|----|---------|----|-------|----|------|-----|------|------|-----|------|----|---|--|--|--|--|--|--|

| Mode                                          | Format             | 35 34 33 32 3 | 1 30 29 2 | 3 27   | 26 | 25    | 24 | 23 | 22 21  | 20    | 19 | 18              | 17 16  | 15 | 14 | 13 | 12      | 11 | 10    | 09 | 08   | 07  | 06   | 05 0 | 4 0 | 3 02 | 01 | ( |  |  |  |  |  |  |

| 36                                            | RGB                | R[11:0]       | R[11:0]   |        |    |       |    |    |        |       |    | G[11:0] B[11:0] |        |    |    |    |         |    |       |    |      |     |      |      |     |      |    |   |  |  |  |  |  |  |

| bit                                           | YCrCb              | Cr[11:0]      |           |        |    |       |    | Y[ | [11:0] |       |    |                 |        |    |    |    |         |    | 5[11: | 0] |      |     |      |      |     |      |    |   |  |  |  |  |  |  |

| 30                                            | RGB                | R[9:0]        |           | G[9:0] |    |       |    |    |        |       |    |                 | B[9:0] |    |    |    |         |    |       |    |      |     |      |      |     |      |    |   |  |  |  |  |  |  |

| bit                                           | YCrCb              | Cr[9:0]       |           |        |    |       |    |    | Y[9:0] |       |    |                 |        |    |    |    | Cb[9:0] |    |       |    |      |     |      |      |     |      |    |   |  |  |  |  |  |  |

| 24                                            | RGB                | R[7:0]        |           |        |    |       |    | G  | 7:0]   |       |    |                 |        |    |    |    |         | B  | 7:0]  |    |      |     |      |      |     |      | Г  | Ī |  |  |  |  |  |  |

| bit                                           | YCrCb              | Cr[7:0]       |           |        |    |       |    | Y[ | 7:0]   |       |    |                 |        |    |    |    |         | Cl | 7:0   | ]  |      |     |      |      | T   | T    | T  | Ī |  |  |  |  |  |  |

| Pins D[35:0] 35 34 33 32 31 30 29 28 27 26 25 |                    |               |           | 24     | 23 | 22 21 | 20 | 19 | 18     | 17 16 | 15 | 14              | 13     | 12 | 11 | 10 | 09      | 08 | 07    | 06 | 05 0 | 4 0 | 3 02 | 01   | 1   |      |    |   |  |  |  |  |  |  |

Figure 15: Table of color data pins corresponding to input ID 0 on ADV7511. [28]

For this board, either RGB format or YCbCr 4:4:4 (with no subsampling) can be chosen. I have decided to use RGB because it is the easiest one, as the generated colors data will be directly in this format, therefore no color conversion will be required.

As separate syncs are used for ZC706, I have chosen input ID 1 (and not 2) for ZedBoard in order to use also separate syncs, and have a more similar behavior.

The colors for each board have to be defined with each component on 8 bits.

#### Registers map

For the ADV7511 to work as a HDMI transmitter, some of its registers have to be set. When using I2C to set them, the whole 8 bits that compose the register must be sent. So even though only few bits of a register must be set to a value different from the default one, the whole byte information must be provided.

#### Fixed registers that must be set

There are some registers that have to be set to defined value for the chip to work properly (Figure A.1). When the whole 8 bits are not specified in the table from the documentation [28], these unspecified bits may have to be set to their default value that may be different from zero, and so they need to remain at this value. Actually, it is the case for one of these fixed registers: 0x9D (Figure A.2).

#### Main Power Up

In order to power up the transmitter, register 0x41(6) needs to be set to zero (Figure A.3).

#### HDMI or DVI mode

For the output mode of the chip, there is a choice between HDMI and DVI modes (Figure A.4). I have chosen DVI mode. And then 0xAF(1) has to be set to 0. However, the rest of this register 0xAF cannot be simply set to zero (Figure A.5).

HDMI is backward compatible with Digital Visual Interface (DVI), without any signal conversion or loss of video quality. It just necessitates that the video pixel encoding is RGB because DVI only supports this color format. [15]

Thus, video data needs to be converted to RGB color format, which can be done directly by the transmitter using Color Space Conversion (CSC).

#### Input Formatting Related Registers

For the input mode, there will be two different configurations for ZedBoard or ZC706. Besides, both use separate syncs. And the data length of each color component is of 8 bits.

For ZedBoard, as seen in figure 14, input ID is 1, data is right justified, and input style 3 has been chosen.

For ZC706, as seen in figure 15, input ID is 0, there is no data alignment and no input style to be set.

Then, the input formatting related registers can be mapped following the documentation [28] (Figures A.6 to A.9).

### CSC related registers

Finally, registers have to be mapped for the Color Space Conversion (CSC).

For ZedBoard, colors data need to be converted from HDTV YCbCr to RGB (Figure A.10).

For ZC706, colors data is already in format RGB, so the identity matrix needs to be used (Figure A.11).

## Summary registers map tables

Finally, all the registers to be set are summarized in Tables 3 and 4.

| Register address | Register<br>ZedBoard | value<br>ZC706 |                                                                                                                                                                                        |

|------------------|----------------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fixed regis      | sters to be se       |                |                                                                                                                                                                                        |

| 0x98             | 0x0                  |                |                                                                                                                                                                                        |

| 0x9A             | 0xE                  | 0              |                                                                                                                                                                                        |

| 0x9C             | 0x30                 | 0              |                                                                                                                                                                                        |

| 0x9D             | 0x6                  | 1              |                                                                                                                                                                                        |

| 0xA2             | 0xA                  | 4              |                                                                                                                                                                                        |

| 0xA3             | 0xA                  | 4              |                                                                                                                                                                                        |

| 0xE0             | 0xD                  | 0              |                                                                                                                                                                                        |

| 0xF9             | 0x0                  | 0              | $\rightarrow$ Fixed I2C Address                                                                                                                                                        |

| Main I           | Power Up             |                |                                                                                                                                                                                        |

| 0x41             | 0x10                 | 0              | $\rightarrow$ Main Power Up                                                                                                                                                            |

| Inpu             | t Mode               |                |                                                                                                                                                                                        |

| 0x15             | 0x01                 | 0x00           | Input ID:     for ZedBoard: 1:     16, 20, 24 bit YCbCr 4:2:2     (separate syncs)     for ZC706: 0:     24 bit RGB 4:4:4 or YCbCr 4:4:4     (separate syncs)                          |

| 0x16             | 0x3C                 | 0x30           | Output Format: 4:4:4, Input Color Depth: 8 bit, Input Style: for ZedBoard: 3, for ZC706: not defined                                                                                   |

| 0x17             | 0x0                  | 0              | $ \rightarrow \begin{cases} \text{Vsync and Hsync Polarities: pass through,} \\ 4:2:2 \text{ to } 4:4:4 \text{ Up Conversion Method:} \\ \text{zero order interpolation} \end{cases} $ |

| 0x48             | 0x08                 | 0x00           | →<br>Normal Video Input Bus Order,<br>Video Input Justification:<br>for ZedBoard: right justified,<br>for ZC706: not defined                                                           |

|                  | ut Mode              |                |                                                                                                                                                                                        |

| 0xAF             | 0x $0$ 4             | 4              | $\rightarrow$ DVI mode                                                                                                                                                                 |

Table 3: Register map for ADV7511 for both ZedBoard and ZC706 boards.

| D : 4 11         | Register     | value | ]                |

|------------------|--------------|-------|------------------|

| Register address | ZedBoard     | ZC706 |                  |

| Color Space      | e Conversion | n     |                  |

| 0x18             | 0xE7         | 0xA8  | $\rightarrow A1$ |

| 0x19             | 0x34         | 0x00  | $\rightarrow$ A1 |

| 0x1A             | 0x04         | 0x00  | $\rightarrow$ A2 |

| 0x1B             | 0xAD         | 0x00  | $\rightarrow A2$ |

| 0x1C             | 0x00         | 0x00  | $\rightarrow A3$ |

| 0x1D             | 0x00         | 0x00  | $\rightarrow$ A3 |

| 0x1E             | 0x1C         | 0x00  | $\rightarrow A4$ |

| 0x1F             | 0x1B         | 0x00  | $\rightarrow A4$ |

| 0x20             | 0x1D         | 0x00  | $\rightarrow B1$ |

| 0x21             | 0xDC         | 0x00  | $\rightarrow B1$ |

| 0x22             | 0x04         | 0x08  | $\rightarrow B2$ |

| 0x23             | 0x1D         | 0x00  | $\rightarrow B2$ |

| 0x24             | 0x1F         | 0x00  | $\rightarrow B3$ |

| 0x25             | 0x24         | 0x00  | $\rightarrow B3$ |

| 0x26             | 0x01         | 0x00  | $\rightarrow B3$ |

| 0x27             | 0x35         | 0x00  | $\rightarrow B4$ |

| 0x28             | 0x00         | 0x00  | $\rightarrow$ C1 |

| 0x29             | 0x00         | 0x00  | $\rightarrow$ C1 |

| 0x2A             | 0x04         | 0x00  | $\rightarrow C2$ |

| 0x2B             | 0xAD         | 0x00  | $\rightarrow$ C2 |

| 0x2C             | 0x08         | 0x08  | $\rightarrow C3$ |

| 0x2D             | 0x7C         | 0x00  | $\rightarrow$ C3 |

| 0x2E             | 0x1B         | 0x00  | $\rightarrow C4$ |

| 0x2F             | 0x77         | 0x00  | $\rightarrow C4$ |

Table 4: Register map (CSC) for ADV7511 for both ZedBoard and ZC706 boards.

### 4.2.2 I2C bus switch on ZC706

On Zynq ZC706, an I2C bus switch exists and it needs to be configured first before communicating with ADV7511. 8 different slaves are connected to this bus switch.

I2C communication can be made via the PS (Processing System) or the PL (Programmable Logic) (Figure 16). However, I wanted to try to have everything directly on the PL, so the I2C has been programmed on it.

Figure 16: I2C bus topology on ZC706. [29]

The I2C address of the bus switch is 0b1110\_100 [29]. A first I2C message has to be sent to the bus switch on 8 bits with a '1' at the position that corresponds to the channel(s) to be enabled. For example, in the case where HDMI transmitter ADV7511 (which corresponds to channel 1) is the only slave to be enabled, the I2C message 0b0000\_0010 has to be sent. [29, 30]

Then, the communication can be made with the enabled slaves at their corresponding address (Figure A.12).

Actually, the address of ADV7511 on the I2C bus 0b0111\_001 is the same as on the ZedBoard, which on its side does not possess an I2C bus switch, and the communication can directly be made to the HDMI transmitter using the corresponding address. [26]

# 4.3 Programming

### 4.3.1 Introduction

As an example to understand HDMI and its connection from ZedBoard, the work of Mike Field [31] was very helpful.

He was actually using only 8 pins on the ZedBoard: pins 8 to 15 with the same color format YCbCr 4:2:2, with each data on 8 bits. In order to send both luma (Y) and chroma (Cb or Cr) information in one clock period, he used DDR (Double Data Rate). This corresponds to the input ID 7 (Table 21 of the datasheet [28]), with style 1 (actually style 2 could also have been used but with pins 0 to 7).

In order to test the HDMI connection, an example was made only to show on the screen vertical bands of color. Two projects for this HDMI connection test have been created: for ZedBoard and Zynq ZC706. The sources used by the projects are located outside of the projects and are split between the common files used by both platforms, and specific files for each of the two platforms.

A Git repository has been created, different from the HEENS project one, for this HDMI test including both projects. It helped me while coding to easily check the differences made between the current code and a previous state, as well as to return to a previous state if necessary.

In order to find the pins of the different HDMI IOs, the schematics of both boards have been studied [26, 27] to create the two constraints files (.xdc).

# 4.3.2 Clock generation

The general clock on ZedBoard is single-ended and has a frequency of 100 MHz. On ZC706, it is differential and has a frequency of 200 MHz.

To generate a single-ended clock from a differential one, I have used an IP (Intellectual Property) from Xilinx library: a Differential Input Buffer.

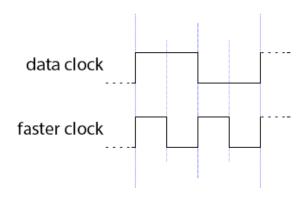

To generate the pixel clock at  $150\,\mathrm{MHz}$ , a Base PLL (Phase-Locked Loop) is used, with a first clock division by 2 for ZC706, to go to the frequency of  $100\,\mathrm{MHz}$  that corresponds to the one of ZedBoard. Then, the clock is multiplied by 15, and the divider is 10 for the pixel clock. Actually, the PLL was also used to generate the  $125\,\mathrm{MHz}$  HEENS clock using a 12 divider in the simpler project that was created to simulate the behavior of HEENS, before the incorporation to the actual code where HEENS clock is generated by the PS. This explains the value of 15 as the LCM (Least Common Multiple) between 3 and 5 corresponding to the numerator of the fractions 3/2 (= 150/100) and 5/4 (= 125/100).

#### 4.3.3 Screen resolution