# Low hardware consumption, resolutionconfigurable gray code oscillator time-todigital converters implemented in 16nm, 20nm and 28nm FPGAs

Yu Wang, Wujun Xie, Haochang Chen, and David Day-Uei Li

Abstract—This paper presents low-hardware consumption, resolution-configurable, automatically calibrating gray code oscillator time-to-digital converter (GCO-TDC) in Xilinx 16nm UltraScale+, 20nm UltraScale and 28nm Virtex-7 field-programmable gate arrays (FPGAs). The proposed TDC utilizes LUTs as delay elements and has several innovations: 1) a sampling matrix structure to improve the resolution. 2) a virtual bin calibration method (VBCM) to achieve configurable resolutions and automatic calibration. 3) hardware implementation of the VBCM in standard FPGA devices. We implemented and evaluated a 16-channel TDC system in all three FPGAs. The UltraScale+ version achieved the best resolution (least significant bit, LSB) of 20.97 ps with 0.09 LSB averaged peak-to-peak differential nonlinearity (DNLpk-pk). The UltraScale and Virtex-7 versions achieved the best resolutions of 36.01 ps with 0.10 LSB averaged DNL<sub>pk-pk</sub> and 34.84 ps with 0.08 LSB averaged DNLpk-pk, respectively.

Index Terms—Gray code oscillator (GCO), field-programmable gate array (FPGA), low hardware consumption, automatic calibration, resolution-adjustable, time-to-digital converter (TDC).

# I. INTRODUCTION

Time-to-digital converters (TDCs) are simply high-precision time-interval meters, converting a time interval (TI) into a digital code. (R2, comment 1) They are widely used in industrial and scientific applications, including light detection and ranging (LiDAR) for automatic vehicles and robotics [1]–[3], 3-D imaging [4]–[6], surveying [7], Raman spectroscopy [8], [9], hardware trojan detection [10], temperature sensing [11], [12], random number generation [13], [14], particle physics [15]–[17], positron emission tomography (PET) [18], fluorescence lifetime imaging microscopy (FLIM) [19] and space sciences [20].

The primary metric of a TDC is the resolution (the minimum TI that can be measured, also called the least significant bit, LSB). Ideally, all bins in a TDC should have the same width. The ideal bin width can be defined as Q = T/n, where T is the period of the sampling clock and n is the number of bins, respectively. However, bin widths are not uniform. The variations of bin widths caused by uneven delay elements [21]

The research has been supported by the Engineering and Physical Sciences Research Council under EPSRC Grant: EP/L01596X/1, the Royal Society of Edinburgh, and the China Scholarship Council. We would also like acknowledge the support from the Xilinx for donating FPGA develop kits to the research group.

are usually characterized by differential nonlinearity (DNL) and integrated nonlinearity (INL). They are respectively defined as DNL[k] = (W[k]-Q)/Q and  $INL[k] = \sum_{n=0}^{k} DNL[j]$ , where W[k] is the k-th bin's width, and it can be evaluated by code density tests [22]. With recent advances in CMOS manufacturing technologies, FPGA-TDCs and ASIC-TDCs can achieve picosecond-level resolutions. However, FPGA-TDCs are cheaper and have shorter developing cycles. These characteristics make FPGA-TDCs popular in prototype designs.

Industrial applications utilizing time-of-flight (TOF) information (such as LiDAR) concern not only the resolution but also linearity. In time-resolved LiDAR systems, a resolution of 66.6 ps corresponds to a distance of 1 cm [23]. Therefore, LiDAR systems for automatic vehicles and robotics require TDCs with a 35-500 ps resolution and high linearity [24]. Besides, PET and Raman spectroscopy also require TDCs with an acceptable resolution of 50 ps [8], [9], [25], [26]. Similar requirements make it possible to design general-purpose TDCs for these applications.

Interpolations in TDCs use the elements' delay to obtain a higher resolution. The tapped delay line TDC (TDL-TDC) is the mainstream for FPGA-TDCs because cascaded carry-chains are available in modern FPGAs, for example, CARRY4 modules in Xilinx 6-series and 7-series FPGAs [27] and CARRY8 modules in UltraScale and UltraScale+ FPGAs [28]. The TDL-TDC's resolution is determined by the carry module's propagation delay and can achieve 10 ps or better [29], [30] in 7-series FPGAs and 5 ps or better [31], [32] in UltraScale FPGAs. Due to the small propagation delay of carry modules, a TDL often requires more than 200 carry modules to

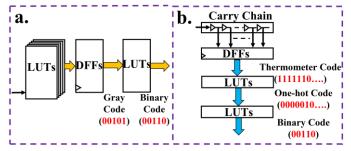

Fig.1. The coding comparison between the (a) GCO-TDC and (b) TDL-TDC.

Y. Wang, W. Xie and D. D.-U. Li are with the Faculty of Engineering, University of Strathclyde, Glasgow, G4 0RE, U.K., (e-mail: y.wang.100@strath.ac.uk; wujun.xie@strath.ac.uk; David.li@strath.ac.uk). H. Chen is with the Fraunhofer UK Research Ltd (e-mail: Haochang.Chen@fraunhofer.co.uk).

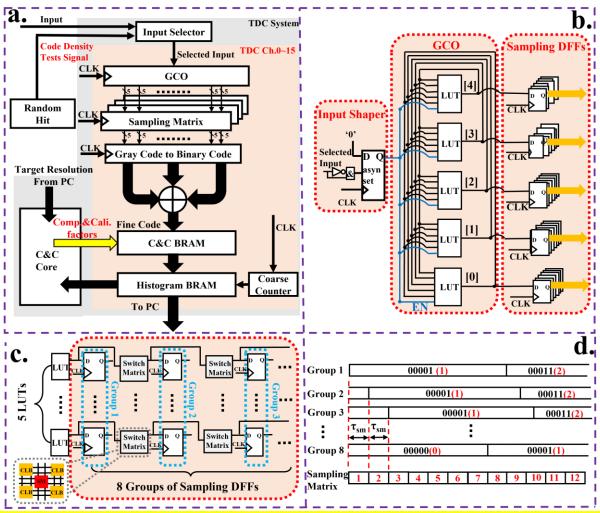

Fig.2. (a) The block diagram of the proposed TDC system. (b) The block diagram of the GCO-TDC (c) The block diagram of the sampling matrix. (d) The concept of the sampling matrix (R2 comment 2 and comment 3; R3, comment 9).

cover a sampling period. For example, it requires 50 CARRY4s (200 carry modules) in the 7-series FPGA (with a 710MHz sampling clock) [33] and 74 CARRY8s (592 carry modules) in the UltraScale FPGA (with a 500MHz sampling clock) [23]. When implementing multichannel designs, the consumption of carry modules would be significant (31.26% of CARRY8s are used for 128 channels in Ref. [23]). Besides, in highly-integrated systems, for example, in LiDAR applications [34], [35], multichannel TDCs are integrated with processing modules in FPGAs. Hence, as a basic unit for arithmetic operations, carry modules should be utilized efficiently rather than being largely utilized as delay elements. (R2, comment 6; R3, comment 1)

Recently, Wu and Xu [36] proposed a gray code oscillator (GCO)-TDC. Compared with TDL-TDCs, this design uses look-up tables (LUTs) rather than carry modules as delay elements. Through outputting gray codes directly, the GCO-TDC avoid tedious coding that uses many logic resources in TDL-TDCs (the comparison is shown in Fig.1). Hence, the GCO-TDC have high efficiency in hardware utilization and uses only eight LUTs and eight D-type flip-flops (DFFs) to build one TDC [36]. (R2, comment 6; R3, comment 1) However, the GCO-TDC's resolution (256 ps) is to be further improved, and it has a 1.25 LSB peak-to-peak differential nonlinearity

(DNL<sub>pk-pk</sub>). (R3, comment 6) For better linearity, Machado *et al.* [37] adopted manual routing for the GCO-TDC and improved DNL<sub>pk-pk</sub> to 0.76 LSB, but the resolution (380.9 ps) significantly increased. To enhance the resolution, Araújo *et al.* [38] proposed a double-sampling GCO-TDC. This work utilized the double-sampling method to improve the resolution to 69 ps. However, the linearity deteriorates to 1.76 LSB DNL<sub>pk-pk</sub>.(R3, comment 7)

Besides, aforementioned GCO-TDCs [36], [38], [39] and most previously reported FPGA-TDCs [29], [30], [40] are designed with fixed resolutions. It is not friendly if application requirements change. For broader applications, TDCs in Ref. [23], [36] and [37] offer flexible resolutions. However, they all need manual configuration channel-by-channel and chip-by-chip when resolution requirements change. This process is time-consumption and difficult for users unfamiliar with FPGA-TDCs. TDCs in Ref. [38] and [39] achieve automatic calibration. But their resolutions are fixed. Hence, an automatic calibration TDC with flexible resolutions is desirable for general applications.

Based on the GCO structure, we proposed a high linearity multichannel TDC with configurable resolutions and automatic calibration. Although we aim for a resolution of 20~100 ps in this paper, it can be extended if needed. The main contributions

of this work are:

- 1) We propose a new sampling matrix structure and dramatically improve the GCO-TDC's resolution.

- We propose a virtual bin calibration method (VBCM) for online resolution configuration and automatic calibration.

- 3) We implemented the VBCM by the hardware description language (HDL). Through multiplexing critical components, this core is hardware-efficient.

- To show our methods, we developed and evaluated 16channel TDCs in 16nm UltraScale+ XCZU7EV, 20nm UltraScale XCKU040 and 28nm Virtex-7 XC7V690T FPGAs.

This article is structured as follows: Section II describes the architecture and design of the proposed TDC. Section III presents the experimental results, Section IV compares with other designs, and Section V summarizes our TDC.

#### II. ARCHITECTURE AND DESIGN

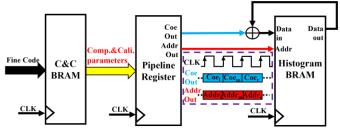

The architecture of the proposed TDC is shown in Fig. 2a. The GCO is the cornerstone of the proposed TDC, and it is responsible for measuring TIs with a coarse counter. For each channel, it also contains a sampling matrix, a gray-code-tobinary-code converter, a compensation&calibration BRAM (C&C BRAM in Fig. 2a), and a histogram BRAM. Besides, the proposed TDC system contains a compensation&calibration (C&C Core in Fig. 2a) for compensation&calibration factors (comp.&cali. factors in Fig. 2a) for all 16 channels. The C&C core only works after system launching and configuring the resolution. After calculating, the C&C core loads comp.&cali. factors into the C&C BRAM. With the C&C core and the C&C BRAM, the proposed TDC achieves multi-resolution and high linearity without manual intervention.

### A. GCO-TDC

The GCO is shown in Fig. 2b. Unlike the binary code, only one bit experiences transition between two contiguous states in the gray code. So, the GCO is robust against the "race and competition" phenomenon and can be structured with combinational logic resources only [36]. In our design, the GCO is implemented with LUTs. In 7-series and more advanced Xilinx FPGAs, each LUT has up to 6 inputs[28], [45]. One of these inputs is connected to "EN" (highlighted in blue

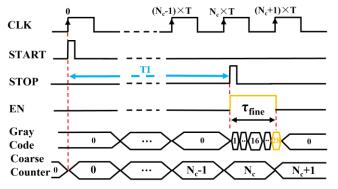

Fig. 3. The timing diagram of the GCO-TDC

in Fig. 2b) to start/reset the GCO, and the other five inputs are used to get feedback from LUTs' outputs. By instantiating LUTs and DFFs with Vivado primitives [28], [45], five-bit gray code can be output from five LUTs and then sampled by DFFs.(R4, comment 2-ii) According to the sampled gray code, TI between the GCO launching and DFFs sampling can be evaluated. Hence, the GCO can be used to measure TI even it is less one clock period.

To reset the GCO after sampling and work with a coarse counter, as shown in Fig. 2b, an "Input Shaper" is designed to generate the control signal for the GCO. (R3, comment 2) The timing diagram of the proposed GCO-TDC is shown in Fig. 3. In the proposed system, the "START" is synchronous with the sampling clock (CLK in Fig. 3), and the "STOP" is asynchronous with it. When a rising edge of "STOP" comes ("STOP" is the input signal for the "Input Shaper"), the signal "EN" changes to "1" (high-logic level) and keeps this state until the rising edge of the sampling clock. Meanwhile, the GCO launches, and then it resets after being sampled by DFFs. With every rising edge of "STOP", a fine code from the GCO and a coarse code from the coarse counter can be latched. (R3, comment 8) By combining the fine code and coarse code, the proposed GCO-TDC can easily extend the measurement range without increasing gray code bits.(R3, comment 2) The TI (highlighted in blue in Fig. 3) can be calculated as TI = $(Nc+1)\times T - \tau_{fine}$ , where  $N_C$  is the coarse code and  $\tau_{fine}$  is the time interval corresponding to the fine code.

## B. Sampling Matrix

In the plain GCO-TDC [36], each LUT is sampled by a single DFF. Although this structure is hardware-efficient, it can only deliver a lower resolution. Therefore, a sampling matrix structure (shown in Fig. 2c) is proposed to improve the resolution.

In Fig. 2c, each LUT is sampled by eight DFFs. With eight

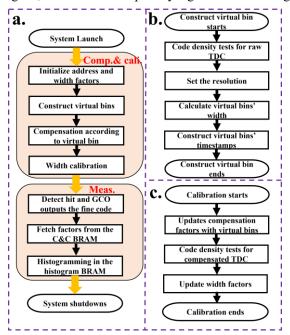

Fig. 4. (a) The workflow the proposed TDC system. (b) The workflow of the virtual bin construction. (c) The workflow of calibration.

Fig. 5. Hardware implementation of the real-time histogram with the VBCM.

groups of DFFs, the TDC conducts eight measurements for the same TI in one clock period. Fig. 2d shows this method's concept, where  $\tau_{sm}$  is the delay of the switch matrix. In plain GCO-TDCs, the resolution is defined as Q = T/n. For the GCO-TDC with a sampling matrix, each plain bin is sub-divided with  $\tau_{sm}$ . (R2, comment 4) Hence, the resolution with a sampling matrix is defined as:

$$LSB_{sm} = \frac{T}{r} \times \frac{1}{M} = \frac{Q}{M}$$

, (R2, comment 4)

where M is the amount of DFF groups.

TABLE I compares raw TDCs' resolutions and hardware consumption (without the C&C core) with different sampling factors (M) in all three FPGAs. According to the utilization percentage, LUTs are mainly consumed in our design. So, we use the consumption of LUTs to evaluate hardware consumption in Eq (2). To find a balance between the resolution and hardware consumption when we increase M, the normalized efficiency of resolution improvement is proposed and calculated as:

$$E_{M} = \frac{LSB_{M[i-1]} - LSB_{M[i]}}{LSB_{plain}} / \frac{LUT_{M[i]} - LUT_{M[i-1]}}{LUT_{plain}}, M = 2^{i}$$

(2)

Fig. 6. Compensation in (a) the mixed calibration, (b) the weighted histogram calibration and (c) the virtual bin calibration methods.

| TABLE I                                                   |                                                                                          |        |             |             |  |  |  |  |  |  |  |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------|--------|-------------|-------------|--|--|--|--|--|--|--|

| COMPARISONS OF PERFORMANCES AND HARDWARE UTILIZATION WITH |                                                                                          |        |             |             |  |  |  |  |  |  |  |

| DIFFERENT SAMPLING FACTORS (M) (R3, comment 3)            |                                                                                          |        |             |             |  |  |  |  |  |  |  |

| М                                                         | $M \qquad E_{M} \qquad \frac{LSB}{(ps)} \qquad Used \ LUTs \ (\%)^{I} \qquad Used \ DFF$ |        |             |             |  |  |  |  |  |  |  |

| UltraScale+                                               |                                                                                          |        |             |             |  |  |  |  |  |  |  |

| 1                                                         | N/A <sup>3</sup>                                                                         | 158.03 | 117 (0.05%) | 177 (0.04%) |  |  |  |  |  |  |  |

| 2                                                         | 2.56                                                                                     | 79.01  | 139 (0.06%) | 194 (0.04%) |  |  |  |  |  |  |  |

| 4                                                         | 0.96                                                                                     | 40.23  | 170 (0.07%) | 221 (0.05%) |  |  |  |  |  |  |  |

| 8                                                         | 0.31                                                                                     | 19.41  | 222 (0.10%) | 268 (0.06%) |  |  |  |  |  |  |  |

| 16                                                        | 0.08                                                                                     | 10.51  | 295 (0.13%) | 354 (0.08%) |  |  |  |  |  |  |  |

|                                                           |                                                                                          |        | UltraScale  |             |  |  |  |  |  |  |  |

| 1                                                         | N/A <sup>3</sup>                                                                         | 267.09 | 146 (0.06%) | 233 (0.05%) |  |  |  |  |  |  |  |

| 2                                                         | 6.50                                                                                     | 136.39 | 157 (0.06%) | 238 (0.05%) |  |  |  |  |  |  |  |

| 4                                                         | 1.76                                                                                     | 68.93  | 178 (0.07%) | 248 (0.05%) |  |  |  |  |  |  |  |

| 8                                                         | 0.44                                                                                     | 35.42  | 220 (0.09%) | 268 (0.06%) |  |  |  |  |  |  |  |

| 16                                                        | 0.15                                                                                     | 19.02  | 279 (0.12%) | 380 (0.08%) |  |  |  |  |  |  |  |

|                                                           |                                                                                          |        | Virtex-7    |             |  |  |  |  |  |  |  |

| 1                                                         | N/A <sup>3</sup>                                                                         | 256.41 | 146 (0.03%) | 233 (0.03%) |  |  |  |  |  |  |  |

| 2                                                         | 5.73                                                                                     | 125.69 | 159 (0.04%) | 238 (0.03%) |  |  |  |  |  |  |  |

| 4                                                         | 11.69                                                                                    | 64.10  | 162 (0.04%) | 248 (0.03%) |  |  |  |  |  |  |  |

| 8                                                         | 0.43                                                                                     | 32.54  | 204 (0.05%) | 268 (0.03%) |  |  |  |  |  |  |  |

| 16                                                        | 0.11                                                                                     | 17.05  | 281 (0.06%) | 380 (0.04%) |  |  |  |  |  |  |  |

<sup>1</sup> Percentage of LUTs' utilization; <sup>2</sup> Percentage of DFFs' utilization;

<sup>3</sup> Not available.

where  $LSB_M$  and  $LUT_M$  are, respectively the TDC's resolution and consumption of LUTs with an M-order sampling matrix, and  $LSB_{plain}$  and  $LUT_{plain}$  are the resolution and LUTs' consumption of the plain GCO-TDC (M = 1). When M increases,  $E_M$  decreases in UltraScale and UltraScale+ FPGAs. However, it shows a different trend in the Virtex-7 FPGA.  $E_M$  in the Virtex-7 FPGA reaches its peak value when M = 4 due to a different FPGA architecture. Overall,  $E_M$  is close to 0 when M = 16 in all three FPGAs, meaning the efficiency of resolution improvement is low when M increases from 8 to 16. Hence, we choose M = 8, considering the trade-off between performances and hardware consumption. (R3, comment 3)

#### C. Virtual Bin Calibration Method

Our previous work [44] presented a PS-based architecture to achieve automatic calibration. However, this design is device-dependent and its resolution is fixed. Here we propose a virtual bin calibration method for automatic calibration and online resolution configuration in common FPGA devices. For this work, we will demonstrate the proposed method in three different FPGA devices manufactured in 16nm, 20nm, and 28nm CMOS processes.

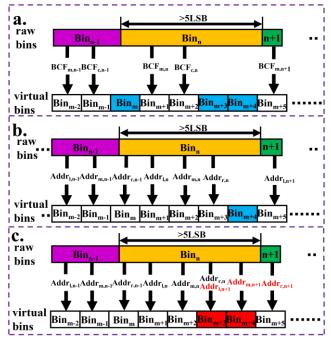

The workflow of the VBCM is shown in Fig. 4a. After launching the system and configuring the resolution, the C&C core calculates compensation factors (Addr<sub>l</sub>, Addr<sub>m</sub> and Addr<sub>r</sub>) and width calibration factors (Coe<sub>l</sub>, Coe<sub>m</sub> and Coe<sub>r</sub>), then loads them to the C&C BRAM in the compensation/calibration stage (Comp.&cali. in Fig. 4a). In the measurement stage (Meas. in Fig. 4a), indexed by a fine code, factors are delivered from the C&C BRAM to the histogram BRAM. During this procedure, width calibration factors (Coe<sub>l</sub>, Coe<sub>m</sub> and Coe<sub>r</sub>) are seriatim added to corresponding bins of the histogram BRAM indexed by compensation factors (Addr<sub>l</sub>, Addr<sub>m</sub> and Addr<sub>r</sub>) shown in Fig.5. Through this, real-time calibration and resolution configuration can be achieved.

Calculations of compensation and width calibration factors contains: 1) construction of virtual bins and 2) calculations according to virtual bins. These two steps are both based on code density tests. Figure 4b shows the workflow of virtual bins

```

\begin{split} start\_point=max[Addr_{l}[k-1],Addr_{m}[k-1],Addr_{r}[k-1]];\\ if (T_{raw}[k] \leq T_{vir}[start\_point])\\ &Addr_{l}[k]= start\_point;\\ elseif (T_{raw}[k] \leq T_{vir}[start\_point+1])\\ &Addr_{l}[k]= start\_point+1;\\ elseif (T_{raw}[k] \leq T_{vir}[start\_point+2])\\ &Addr_{l}[k]= start\_point;\\ &Addr_{l}[k]= start\_point+1;\\ &Addr_{m}[k]= start\_point+2;\\ &Addr_{r}[k]= start\_point+2;\\ else\\ &Addr_{l}[k]= start\_point+1;\\ &Addr_{m}[k]= start\_point+1;\\ &Addr_{m}[k]= start\_point+2;\\ &Addr_{r}[k]= start\_point+3;\\ \end{split}

```

Fig. 7. The pseudo-codes of compensation in virtual bins calibration.

construction. With the target resolution  $R_{conf}$ , the number of hits collected at a virtual bin should be:

$$hit_{vir} = \frac{R_{conf}}{T} \times \tilde{N} = \frac{\tilde{N}}{n_{vir}},$$

(3)

where  $n_{vir}$  ( $n_{vir} \le n$ ) is the number of virtual bins in a sampling period and  $\tilde{N}$  is the number of random hits for code density tests. Hence, the "timestamp" of the m-th virtual bin (number of hits collected until the m-th virtual bin) and the "timestamp" of the k-th raw bin can be defined, respectively, as:

$$T_{vir}[m] = hit_{vir} \times m, \quad m \in [1, n_{vir}],$$

(4)

$T_{raw}[k] = \sum_{1}^{k} hit_{raw}[j], \ k \in [1, n],$  (5)

where  $hit_{raw}[j]$  is the number of hits at the *j*-th raw bin.

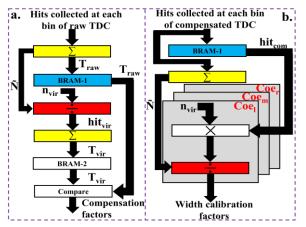

With  $T_{vir}$  and  $T_{raw}$ , like the mixed calibration [32] and weighted calibration methods [44], the compensation factors can be calculated. However, both the mixed calibration method [32] and weighted calibration methods [44] have a limited compensation range, causing "missing bins" (highlighted in blue in Fig. 6a and Fig. 6b). Hence, this work proposes a new compensation missing-bin-free strategy. With compensation factors (Addr<sub>l</sub>, Addr<sub>m</sub> and Addr<sub>r</sub>), the concept of the proposed compensation strategy is shown in Fig. 6c. In most cases, ultra-narrow bins (< 1 LSB, highlighted in green in Fig. 6c) and regular bins (1  $\sim$  2 LSB, highlighted in purple in Fig. 6c) could neighbor ultra-wide bins (highlighted in yellow in Fig. 6c). However, earlier studies [32], [44] did not utilize all compensation factors of ultra-narrow bins (only BCF<sub>m,n+1</sub> is used in Fig. 6a and only Addr<sub>l,n+1</sub> is used in Fig. 6b). To utilize "idle" compensation factors, in Fig. 6c, Addr<sub>l,n+1</sub> and Addr<sub>m,n+1</sub> are used to remap to virtual bins covered by Bin<sub>n</sub> (Bin<sub>m+3</sub> and Bin<sub>m+4</sub>, highlighted in red in Fig. 6c). The pseudo-codes for compensation factor calculations are shown in Fig. 7. After updating compensation factors according to virtual bins, the width calibrations factors can be calculated as shown in Fig. 4c. Code density tests are conducted again for the compensated TDC. (R3, comment 10) Then, with the number of hits collected at each bin, width calibration factors can be calculated as:

$$Coe_{l,m,r}[k] = \frac{\tilde{N}}{n_{vir}} \times \frac{1}{hit_{com}[i]} i = Addr_{l,m,r}[k], (R3, comment 11)$$

Fig. 8. Hardware implementation of (a) compensation factor calculations, and (b) width calibration factor calculations.

where  $hit_{com}[i]$  is the number of hits collected at the *i*-th bin of the compensated TDC.

### D. Hardware implementation of the VBCM

The hardware implementation of the VBCM contains: 1) the implementation of the real-time histogram and 2) the implementation of the C&C core. The implementation of the real-time histogram is shown in Fig. 5. For low BRAM-consumption, a pipeline structure is utilized. In the C&C BRAM, three groups of factors are merged and stored in an address to reduce hardware consumption. With pipeline registers, merged factors are separated and delivered to the histogram BRAM within three system clock periods.(R3, comment 12) Compared with consuming two histogram BRAMs in the mixed calibration method [32] and three histogram BRAMs in our previous work [44], only one histogram BRAM is required in this design.

The C&C core is responsible for calculating compensation and width calibration factors. It is composed of two modules: 1) a compensation factor calculation (CFC) module, and 2) a width calibration factor calculation (WCFC) module. The WCFC module works after the CFC module. Hence, we multiplex some components in these two modules to achieve low resource-consumption. The hardware implementation of the CFC module is shown in Fig. 8a. After code density tests,  $T_{vir}$  and  $T_{raw}$  are calculated according to Eqs (4) and (5) and stored in BRAM-2 and BRAM-1, respectively. When all  $T_{vir}$  and  $T_{raw}$  are calculated, they are output from respective BRAMs and compared following pseudo-codes shown in Fig.7 to calculate compensation factors (Addr<sub>1</sub>, Addr<sub>m</sub> and Addr<sub>r</sub>). After

TABLE II

SIMULATION RESULTS WITH DIFFERENT  $\overline{M}$  (Reviewer 4, comment 2 i)

| 16nm UltraScale+           |      |        |           |      |      |      |  |  |  |  |

|----------------------------|------|--------|-----------|------|------|------|--|--|--|--|

| $\overline{M}$             | 1    | 2      | 3         | 4    | 5    | 6    |  |  |  |  |

| $DNL_{pk-pk}(LSB)$         | 0.68 | 0.39   | 0.20      | 0.12 | 0.10 | 0.08 |  |  |  |  |

| INL <sub>pk-pk</sub> (LSB) | 3.21 | 1.39   | 1.39 0.50 |      | 0.49 | 0.31 |  |  |  |  |

| 20nm UltraScale            |      |        |           |      |      |      |  |  |  |  |

| $\overline{M}$             | 1    | 2      | 3         | 4    | 5    | 6    |  |  |  |  |

| $DNL_{pk-pk}(LSB)$         | 0.68 | 0.38   | 0.20      | 0.16 | 0.12 | 0.12 |  |  |  |  |

| INL <sub>pk-pk</sub> (LSB) | 2.56 | 0.95   | 0.77      | 0.48 | 0.36 | 0.35 |  |  |  |  |

|                            |      | 28nm V | irtex-7   |      |      |      |  |  |  |  |

| $\overline{M}$             | 1    | 2      | 3         | 4    | 5    | 6    |  |  |  |  |

| $DNL_{pk-pk}(LSB)$         | 0.65 | 0.36   | 0.20      | 0.16 | 0.09 | 0.10 |  |  |  |  |

| INL <sub>pk-pk</sub> (LSB) | 3.11 | 1.35   | 0.73      | 0.62 | 0.26 | 0.34 |  |  |  |  |

|                            |      |        |           |      |      |      |  |  |  |  |

| LINEARITY OF THE FROPOSED TIDO WITH DIFFERENT TRESOLUTIONS |          |                           |                     |                      |                     |                      |                      |                     |  |  |

|------------------------------------------------------------|----------|---------------------------|---------------------|----------------------|---------------------|----------------------|----------------------|---------------------|--|--|

|                                                            |          | LSB (ps)                  | $DNL_{pk-pk}$ (LSB) | $\sigma_{DNL}$ (LSB) | $INL_{pk-pk}$ (LSB) | $\sigma_{INL}$ (LSB) | ω <sub>eq</sub> (ps) | $\sigma_{eq}$ (LSB) |  |  |

| UltraScale+<br>I 6nm                                       | Raw-TDC  | 19.41 (n = 228)           | 3.98                | 0.96                 | 7.17                | 1.39                 | 43.11                | 0.64                |  |  |

|                                                            |          | $20.97 (n_{vir} = 211)$   | 0.09                | 0.01                 | 0.20                | 0.04                 | 20.98                | 0.29                |  |  |

|                                                            |          | 29.90 ( $n_{vir} = 148$ ) | 0.05                | 0.01                 | 0.12                | 0.02                 | 29.91                | 0.29                |  |  |

|                                                            | VBCM-TDC | 39.86 ( $n_{vir} = 111$ ) | 0.05                | 0.01                 | 0.12                | 0.03                 | 39.86                | 0.29                |  |  |

|                                                            |          | $50.28 (n_{vir} = 88)$    | 0.05                | 0.01                 | 0.11                | 0.02                 | 50.29                | 0.29                |  |  |

|                                                            |          | $80.45 (n_{vir} = 55)$    | 0.03                | 0.01                 | 0.09                | 0.02                 | 80.46                | 0.29                |  |  |

| UltraScale<br>20nm                                         | Raw-TDC  | 35.42 (n = 181)           | 4.76                | 0.93                 | 12.38               | 2.92                 | 76.94                | 4.72                |  |  |

|                                                            |          | $36.01 (n_{vir} = 178)$   | 0.08                | 0.01                 | 0.14                | 0.03                 | 36.02                | 0.29                |  |  |

|                                                            | VBCM-TDC | $40.06 (n_{vir} = 160)$   | 0.07                | 0.01                 | 0.12                | 0.03                 | 40.07                | 0.29                |  |  |

|                                                            |          | $50.08 (n_{vir} = 128)$   | 0.05                | 0.01                 | 0.13                | 0.03                 | 50.09                | 1.00                |  |  |

|                                                            |          | $80.13 \ (n_{vir} = 80)$  | 0.05                | 0.01                 | 0.08                | 0.02                 | 80.15                | 0.29                |  |  |

|                                                            |          | $100.16 (n_{vir} = 64)$   | 0.04                | 0.01                 | 0.11                | 0.03                 | 100.18               | 0.29                |  |  |

|                                                            | Raw-TDC  | 32.54 (n = 197)           | 5.48                | 0.95                 | 11.23               | 2.35                 | 72.96                | 0.65                |  |  |

| _                                                          |          | $34.84 \ (n_{vir} = 184)$ | 0.07                | 0.02                 | 0.29                | 0.08                 | 34.85                | 0.29                |  |  |

| Virtex-7<br>28nm                                           |          | $40.06 (n_{vir} = 160)$   | 0.07                | 0.01                 | 0.18                | 0.04                 | 40.07                | 0.29                |  |  |

|                                                            | VBCM-TDC | $50.08 \ (n_{vir} = 128)$ | 0.07                | 0.01                 | 0.16                | 0.04                 | 50.09                | 0.29                |  |  |

|                                                            |          | $80.13 \ (n_{vir} = 80)$  | 0.04                | 0.01                 | 0.15                | 0.03                 | 80.15                | 0.29                |  |  |

|                                                            |          | $100.16 (n_{vir} = 64)$   | 0.05                | 0.01                 | 0.11                | 0.03                 | 100.18               | 0.29                |  |  |

TABLE III

LINEARITY OF THE PROPOSED TDC WITH DIFFERENT RESOLUTIONS

compensation is complete, compensation factors are updated into the C&C BRAM. Then code density tests are conducted again for the compensated TDC, and results are stored in BRAM-1 as shown in Fig.8b. With bin-widths of the compensated TDC, width calibration factors (Coe<sub>I</sub>, Coe<sub>m</sub> and Coe<sub>r</sub>) can be calculated according to Eq (6). In the WCFC module, we reuse the BRAM-1, the accumulator and the divider (highlighted in bule, yellow and red in Fig.7) previously used in the CFC module. Moreover, three width calibration factors are calculated similarly. Therefore, the multiplier-divider component (highlighted in gray) is also multiplexed in the WCFC module.

In our design, all data is presented and calculated in the fixed-point format to reduce hardware consumption. Considering errors when the decimal parts are discarded, we use the last  $\overline{M}$  bits of Coe to present decimals. Then, calibration factors can be calculated as:

$$\overline{Coe_{l,m,r}[k]} = Coe_{l,m,r}[k] \times 2^{\overline{M}} = \frac{\tilde{N}}{n_{vir}} \times \frac{2^{\overline{M}}}{hit_{com}[i]}, i = \frac{1}{N} \frac$$

For selecting an appropriate  $\overline{M}$ , we used MATLAB to simulate the VBCM with a different  $\overline{M}$  (setting  $n_{vir} = n$ ). Results in TABLE II indicate that when  $\overline{M}$  increases from 5 to 6, linearity cannot be further improved in UltraScale and Virtex-7 FPGAs, but only peak-to-peak INL (INL<sub>pk-pk</sub>) is enhanced in the

UltraScale+ FPGA. Hence, we choose  $\overline{M} = 5$  for all three FPGAs for an optimized design. (Reviewer 4, comment 2 i)

### III. EXPERIMENTAL RESULTS

We implemented the proposed TDC in ZCU104 [46] (16nm UltraScale+), KCU105 [47] (20nm UltraScale) and NetFPGA SUME [48] (28nm Virtex-7) evaluation boards, respectively. Random hits for code density tests were generated by an SRS CG-635 (Stanford Research Systems), and TDCs' clocks are from low-jitter crystal oscillators on the boards (IDT-8T49 in ZCU104, SI-570 in KCU105 and DSC-1103 in NetFPGA SUME). The frequencies of TDCs' clocks are 226MHz (ZCU104), 156MHz (KCU105) and 156MHz (NetFPGA SUME) respectively, due to different GCOs' oscillation frequencies in three FPGAs. The temperature and voltage were maintained in experiments.

### A. Resolution configuration and linearity

We evaluated our configurable TDCs with different resolution options. The linearity is characterized by DNL, INL and their standard deviations ( $\sigma_{DNL}$  and  $\sigma_{INL}$ ). Besides, Wu [49] also proposed the equivalent bin-width ( $\omega_{eq}$ ) and its deviation ( $\sigma_{eq}$ ) to evaluate the TDC's linearity. They are:

$$\sigma_{eq}^2 = \sum_{i=1}^n \left( \frac{W[i]^2}{12} \times \frac{W[i]}{W_{total}} \right), \tag{8}$$

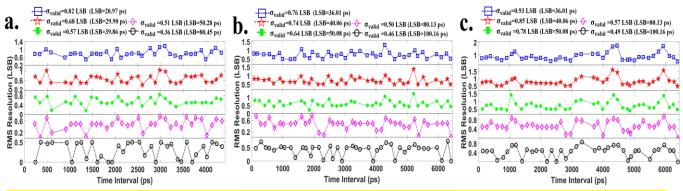

Fig.9. RMS resolutions with different resolution configurations in (a) 16nm UltraScale+, (b) 20nm UltraScale, and (c) 28nm Virtex-7 FPGAs.(R3, comment 13)

$$\omega_{eq} = \sigma_{eq} \times \sqrt{12} = \sqrt{\sum_{i=1}^{n} \frac{W[i]^3}{W_{total}}}, \tag{9}$$

where  $W_{total} = \sum_{i=1}^{n} W[i]$ . The experimental results are summarized in TABLE III. With the VBCM, the proposed TDC's linearity is improved significantly. The 16nm UltraScale+ TDC has DNL<sub>pk-pk</sub> enhanced by more than 44-fold (from 3.98LSB to less than 0.09 LSB), and INL<sub>pk-pk</sub> enhanced by more than 35-fold (from 7.17 LSB to less than 0.20 LSB). Besides, we have also achieved significant improvements in 20nm UltraScale and 28nm Virtex-7 FPGAs, with DNL<sub>pk-pk</sub> respectively improved by more than 59-fold (from 4.76 LSB to less than 0.08 LSB) and 78-fold (from 5.48 LSB to less than 0.07 LSB), and INL<sub>pk-pk</sub> respectively improved by more than 88-fold (from 12.38 LSB to less than 0.14 LSB) and 38-fold (from 11.23 LSB to less than 0.29 LSB). Results indicate the proposed TDC has high linearity in different resolutions.

#### B. Time Interval Tests

The RMS resolution can be evaluated by the standard deviation of measurements for the same TI. It is defined as  $\sigma^2 = \sum_{i=1}^{N_T} \frac{(x_i - \mu)}{N_T}$ , where  $x_i$  is the *i*-th output and  $\mu$  is the averaged value for  $N_T$  measurements when TI is fixed.

To avoid jitter introduced by input signals, we utilized programmable input delay elements inside FPGAs (IDELAY3

Table IV

HARDWARE RESOURCES UTILIZATION(R2, COMMENT 5)

|                 |           | LUT    | DFF    | CARRY <sup>1</sup> | BRAM <sup>2</sup> |

|-----------------|-----------|--------|--------|--------------------|-------------------|

| I 714 C         | Available | 230400 | 460800 | 28800              | 312               |

| UltraS<br>cale+ | 1-ch.     | 222    | 268    | 9                  | 1.5               |

| caie+<br>16 nm  | 16-ch.    | 3548   | 4288   | 144                | 24                |

| 10 nm           | C&C core  | 3719   | 1596   | 310                | 1                 |

| I 714 C         | Available | 242400 | 484800 | 30300              | 600               |

| UltraS<br>cale  | 1-ch.     | 220    | 268    | 9                  | 1.5               |

| cate<br>20 nm   | 16-ch.    | 3518   | 4288   | 144                | 24                |

| 20 nm           | C&C core  | 3725   | 1569   | 310                | 1                 |

| 1/24            | Available | 433200 | 866400 | 108300             | 1470              |

| Virtex-         | 1-ch.     | 204    | 268    | 18                 | 1.5               |

| 28 nm           | 16-ch.    | 3263   | 4288   | 288                | 24                |

| 20 nm           | C&C core  | 3753   | 1597   | <mark>574</mark>   | 1                 |

<sup>1</sup> CARRY8s in UltraScale+ and UltraScale FPGAs, and CARRY4s in Virtex-7 FPGA; <sup>2</sup> 36K-BRAM.

in UltraScale+ and UltraScale FPGAs, and IDELAY2 in the Virtex-7 FPGA) to generate controllable delays.

The RMS resolutions for different resolution configurations are shown in Fig. 9. We conducted time interval tests with different intervals (less than one system clock period). However, for each resolution option with different intervals, the averaged RMS resolution or the maximum RMS resolution cannot represent the RMS resolution because they overestimate or underestimate it [23]. Hence, the valid RMS resolution ( $\sigma_{valid}$ ) is used, and it is defined as  $\sigma_{valid}^2 = \sum_{i=1}^{H} \frac{\sigma_i^2}{H} [23]$ , where  $\sigma_i$  is the standard deviation of measurements for the i-th fixed time interval and H is the number of different time intervals. With the resolution improved, the valid RMS resolution deteriorates in all three FPGAs. The UltraScale+ version achieves the best valid RMS resolution of 0.36 LSB when LSB=80.45 ps. The UltraScale and Virtex-7 versions, respectively, can achieve valid RMS resolutions of 0.46 LSB and 0.49 LSB when LSB=100.16 ps.(R3, comment 13)

# C. Multichannel Design

We implemented the proposed TDCs in all three FPGAs. In each channel, an 18k-BRAM is used as the histogram BRAM, and a 36k-BRAM is used as the C&C BRAM. Besides, less than 230 LUTs and 270 DFFs are required to build the GCO-TDC with a sampling matrix. For the C&C core, two 18k-BRAMs, no more than 3800 LUTs and 1600 DFFs are used to calculate

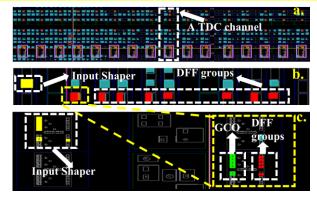

Fig. 10. Implementation layouts of (a) 16 channels, (b) a single channel, and (c) an input shaper and a GCO.

TABLE V DNLPK-PK OF 16-CHANNEL TDCS IN 16NM, 20NM, AND 28NM FPGAS

|        | DNEFR-FR OF TO-CHANNEL TDGS IN TONIN, ZONIN, AND ZONINTT GAS |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |      |

|--------|--------------------------------------------------------------|------|------|------|------|------|------|-------|------|------|------|------|------|------|------|------|------|

| LSB    | 0                                                            | 1    | 2    | 3    | 4    | 5    | 6    | 7     | 8    | 9    | 10   | 11   | 12   | 13   | 14   | 15   | Ave. |

| (ps)   |                                                              |      |      |      |      |      |      | LSB   |      |      |      |      |      |      |      |      |      |

|        | UltraScale+                                                  |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |      |

| 20.97  | 0.09                                                         | 0.07 | 0.10 | 0.08 | 0.07 | 0.18 | 0.08 | 0.07  | 0.11 | 0.06 | 0.07 | 0.07 | 0.07 | 0.13 | 0.07 | 0.08 | 0.09 |

| 29.90  | 0.05                                                         | 0.06 | 0.06 | 0.06 | 0.05 | 0.08 | 0.06 | 0.07  | 0.06 | 0.06 | 0.06 | 0.07 | 0.06 | 0.06 | 0.06 | 0.05 | 0.06 |

| 39.86  | 0.05                                                         | 0.04 | 0.05 | 0.04 | 0.05 | 0.05 | 0.06 | 0.05  | 0.05 | 0.06 | 0.05 | 0.05 | 0.04 | 0.05 | 0.05 | 0.06 | 0.05 |

| 50.28  | 0.05                                                         | 0.04 | 0.04 | 0.04 | 0.05 | 0.05 | 0.04 | 0.04  | 0.04 | 0.04 | 0.04 | 0.05 | 0.05 | 0.05 | 0.04 | 0.05 | 0.04 |

| 80.45  | 0.03                                                         | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 | 0.04  | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 | 0.04 |

|        | UltraScale                                                   |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |      |

| 36.01  | 0.08                                                         | 0.16 | 0.08 | 0.13 | 0.08 | 0.08 | 0.08 | 0.09  | 0.07 | 0.18 | 0.09 | 0.07 | 0.08 | 0.08 | 0.21 | 0.09 | 0.10 |

| 40.06  | 0.07                                                         | 0.11 | 0.10 | 0.20 | 0.10 | 0.02 | 0.06 | 0.12  | 0.09 | 0.10 | 0.07 | 0.09 | 0.09 | 0.10 | 0.25 | 0.16 | 0.11 |

| 50.08  | 0.05                                                         | 0.15 | 0.14 | 0.05 | 0.17 | 0.07 | 0.06 | 0.05  | 0.07 | 0.06 | 0.07 | 0.09 | 0.06 | 0.09 | 0.06 | 0.05 | 0.08 |

| 80.13  | 0.05                                                         | 0.06 | 0.05 | 0.08 | 0.05 | 0.15 | 0.05 | 0.05  | 0.05 | 0.05 | 0.05 | 0.05 | 0.09 | 0.06 | 0.05 | 0.06 | 0.06 |

| 100.16 | 0.04                                                         | 0.18 | 0.05 | 0.06 | 0.04 | 0.16 | 0.05 | 0.04  | 0.05 | 0.05 | 0.05 | 0.04 | 0.06 | 0.04 | 0.05 | 0.05 | 0.06 |

|        |                                                              |      |      |      |      |      |      | Virte | x-7  |      |      |      |      |      |      |      |      |

| 34.84  | 0.07                                                         | 0.07 | 0.06 | 0.06 | 0.10 | 0.07 | 0.07 | 0.06  | 0.05 | 0.11 | 0.06 | 0.15 | 0.09 | 0.07 | 0.07 | 0.10 | 0.08 |

| 40.06  | 0.07                                                         | 0.11 | 0.09 | 0.07 | 0.09 | 0.08 | 0.08 | 0.08  | 0.09 | 0.15 | 0.08 | 0.08 | 0.07 | 0.09 | 0.06 | 0.09 | 0.09 |

| 50.08  | 0.07                                                         | 0.07 | 0.06 | 0.06 | 0.05 | 0.06 | 0.06 | 0.07  | 0.05 | 0.06 | 0.06 | 0.07 | 0.06 | 0.06 | 0.06 | 0.07 | 0.06 |

| 80.13  | 0.04                                                         | 0.04 | 0.05 | 0.05 | 0.05 | 0.05 | 0.04 | 0.05  | 0.05 | 0.05 | 0.05 | 0.05 | 0.05 | 0.05 | 0.05 | 0.05 | 0.05 |

| 100.16 | 0.05                                                         | 0.04 | 0.05 | 0.04 | 0.05 | 0.05 | 0.05 | 0.04  | 0.04 | 0.04 | 0.04 | 0.04 | 0.05 | 0.04 | 0.04 | 0.05 | 0.04 |

|        |                                                              |      |      |      |      |      |      |       |      |      |      |      |      |      |      |      |      |

Table VI

Comparison of Recently Publicated FPGA-TDCs (R3, comment 14)

|               | COMPARISON OF RECENTLY PUBLICATED FPGA-TDCS (R3, COMMENT 14) |                        |                          |                                                          |                                                                              |                                                       |                                                    |                                                          |                                                          |                                                          |                                                          |                          |

|---------------|--------------------------------------------------------------|------------------------|--------------------------|----------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------------|--------------------------|

| Ref-<br>year  | Methods                                                      | Devi.<br>Proc.<br>(nm) | LSB (ps)                 | ω <sub>eq</sub><br>(ps)                                  | RMS<br>Resol.<br>(ps)                                                        | DNL(LSB)                                              | INL(LSB)                                           | LUT (%)1                                                 | DFF<br>(%) <sup>1</sup>                                  | Carry<br>(%) <sup>1</sup>                                | 36K-<br>BRA<br>M                                         | Auto/<br>manual<br>Cali. |

|               |                                                              |                        |                          |                                                          |                                                                              | TDL-TDCs                                              |                                                    |                                                          |                                                          |                                                          |                                                          |                          |

| [29]-<br>17   | Tuned-TDL,<br>Direct Histogram,<br>Bin-width Cali.           | 28                     | 10.50                    | 10.55                                                    | 4.42                                                                         | [-0.04,0.04]                                          | [-0.09,0.04]                                       | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | Manual                   |

| [32]-<br>19   | Tuned-TDL,<br>Sub-TDL,<br>Mixed Calibration                  | 28<br>20               | 10.54<br>5.02            | 10.55<br>5.03                                            | 14.59<br>7.80                                                                | [-0.05, 0.08]<br>[-0.12, 0.11]                        | [-0.09, 0.11]<br>[-0.18, 0.46]                     | 1145<br>0.26<br>703<br>0.29                              | 1916<br>0.22<br>1195<br>0.24                             | N/S <sup>2</sup><br>80 <sup>10</sup><br>0.26             | 1.5                                                      | Manual                   |

| [43]-<br>21   | Slide Scale,<br>Gain & Error cal.,<br>Moving Ave.            | 28                     | 4.88                     | N/S <sup>2</sup>                                         | 2.90~<br>8.03                                                                | [-0.10, 0.15]                                         | [-0.23, 0.28]                                      | 2962<br>N/S <sup>2</sup>                                 | 4157<br>N/S <sup>2</sup>                                 | N/S <sup>1</sup>                                         | N/S¹                                                     | Auto                     |

| [23]-<br>21   | Mixed-binning                                                | 20                     | 51.28<br>83.33<br>105.26 | 51.29<br>83.34<br>105.26                                 | 15.89<br>21.67<br>26.32                                                      | [-0.018, 0.021]<br>[-0.017, 0.016]<br>[-0.008, 0.008] | [-0.019,0.035]<br>[-0.028,0.003]<br>[-0.009,0.007] | 663<br>0.27                                              | 1124<br>0.23                                             | 74 <sup>10</sup><br>0.24                                 | 2.5                                                      | Manual                   |

| [44]-<br>21   | Sub-TDL,<br>AC-WU                                            | 28                     | 9.83                     | 9.85                                                     | 13.86                                                                        | [-0.14, 0.16]                                         | [-0.25, 0.42]                                      | 764<br>1.44                                              | 1095<br>1.02                                             | 50 <sup>11</sup><br>0.38                                 | 2                                                        | Auto                     |

| [42]-<br>21   | Half single-chain,<br>real States-based<br>Coding            | 16                     | 5<br>21.56<br>87.74      | N/S <sup>2</sup><br>N/S <sup>2</sup><br>N/S <sup>2</sup> | $   \begin{array}{c}     19^3 \\     30.18^3 \\     105.29^3   \end{array} $ | [-0.99, 1.44]<br>[-0.16, 0.19]<br>[-0.07, 0.05]       | [-2.84, 1.62]<br>[-0.50, 0.33]<br>[0.00, 0.11]     | N/S <sup>2</sup><br>N/S <sup>2</sup><br>N/S <sup>2</sup> | N/S <sup>2</sup>         |

|               |                                                              |                        |                          |                                                          |                                                                              | Other TDCs                                            |                                                    |                                                          |                                                          |                                                          |                                                          |                          |

| [40]-<br>20   | Bidirectional,<br>RO Vernier                                 | 65                     | 24.50                    | N/S <sup>2</sup>                                         | 28.00                                                                        | [-0.20,0.25]                                          | [0.03,0.82]                                        | 172<br>N/S <sup>2</sup>                                  | 986<br>N/S <sup>2</sup>                                  | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | N/S <sup>2</sup>         |

|               | NITIMAND                                                     |                        | 1.87                     | N/S <sup>2</sup>                                         | 2.79                                                                         | [-0.54,1.30]                                          | [-2.21,3.51]                                       | 1679<br>0.82                                             | 1103<br>0.27                                             | N/S <sup>2</sup>                                         | 12                                                       |                          |

| [41]-<br>21   | NUMMP,<br>Timing Scale<br>Marking                            | 28                     | 11.24                    | N/S <sup>2</sup>                                         | 8.07                                                                         | [-0.43,0.26]                                          | [-0.55,0.30]                                       | 1328<br>0.65                                             | 857<br>0.2                                               | N/S <sup>2</sup>                                         | 12                                                       | N/S <sup>2</sup>         |

|               | Marking                                                      |                        | 20.00                    | N/S <sup>2</sup>                                         | 12.81                                                                        | [-0.05,0.06]                                          | [-0.15,0.08]                                       | 634<br>0.41                                              | 828<br>0.16                                              | N/S <sup>2</sup>                                         | 12                                                       |                          |

|               |                                                              |                        |                          |                                                          |                                                                              | GCO-TDCs                                              |                                                    |                                                          |                                                          |                                                          |                                                          |                          |

| [36]-<br>2019 | GCO,<br>Bin-by-bin Cali.                                     | 28                     | 256                      | N/S <sup>2</sup>                                         | 155                                                                          | [-0.53,0.72] <sup>6</sup>                             | N/S <sup>2</sup>                                   | 8<br>N/S <sup>2</sup>                                    | 8<br>N/S <sup>2</sup>                                    | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | Manual                   |

| [39]-<br>2020 | GCO,<br>Manual Routing                                       | 28                     | 380.9                    | N/S <sup>2</sup>                                         | 290                                                                          | [-0.38,0.38]                                          | [0.01,0.70]                                        | 6<br>N/S <sup>2</sup>                                    | 10<br>N/S <sup>2</sup>                                   | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | Manual                   |

| [38]-<br>2021 | GCO,<br>Double Sampling                                      | 16                     | 69                       | N/S <sup>2</sup>                                         | 54.99                                                                        | [-0.95,0.81]                                          | [-1.01,0.49]                                       | 5<br>N/S <sup>2</sup>                                    | 19<br>N/S <sup>2</sup>                                   | N/S <sup>2</sup>                                         | N/S <sup>2</sup>                                         | Manual                   |

|               |                                                              | 16                     | 20.974                   | 20.98                                                    | 17.11 <sup>5</sup>                                                           | [-0.055, 0.034]<br>0.087 <sup>7</sup>                 | [-0.196, 0.000]<br>0.224 <sup>7</sup>              | 222 <sup>8</sup> 0.10 455 <sup>9</sup> 0.20              | 268 <sup>8</sup><br>0.06<br>368 <sup>9</sup><br>0.08     | 9 <sup>10</sup><br>0.03                                  | 1.512                                                    |                          |

| This<br>TDC   | GCO,<br>Sampling<br>Matrix,<br>VBCM                          | 20                     | 36.014                   | 36.02                                                    | 27.37 <sup>5</sup>                                                           | [-0.036, 0.046]<br>0.102 <sup>7</sup>                 | [-0.057, 0.081]<br>0.262 <sup>7</sup>              | 220 <sup>8</sup><br>0.09<br>453 <sup>9</sup><br>0.19     | 268 <sup>8</sup><br>0.06<br>367 <sup>9</sup><br>0.08     | 9 <sup>10</sup><br>0.03                                  | 1.512                                                    | Auto                     |

|               |                                                              | 28                     | 34.844                   | 34.85                                                    | 32.335                                                                       | [-0.033, 0.034]<br>0.078 <sup>7</sup>                 | [-0.016, 0.277]<br>0.203 <sup>7</sup>              | 204 <sup>8</sup><br>0.05<br>437 <sup>9</sup><br>0.10     | 268 <sup>8</sup><br>0.03<br>368 <sup>9</sup><br>0.04     | 18 <sup>11</sup><br>0.02                                 | 1.512                                                    |                          |

<sup>&</sup>lt;sup>1</sup> Percentage of resource utilization for target device; <sup>2</sup> N/S=not specified; <sup>3</sup> FWHM of the residual; <sup>4</sup> Proposed TDCs' best resolution in this device; <sup>5</sup> Valid RMS resolution; <sup>6</sup> Approximate values from figures presented in literature; <sup>7</sup> Averaged peak-to-peak DNL or INL of multichannel TDCs. <sup>8</sup> Logic resource consumption without the C&C core; <sup>10</sup> CARRY8s; <sup>11</sup> CARRY4s; <sup>12</sup> BRAM consumption per channel.

comp.&cali. factors.(R2, comment 5) The resources required for the proposed TDCs are summarized in TABLE IV. It indicates our design is more hardware-effective compared with TDL-TDCs presented in Ref. [23], [39] and [42], and has similar logic resource consumption compared with the RO-TDC presented in Ref. [40] (a comparison shown in Table VI).

Implementation layouts in the UltraScale+ FPGA are shown in Fig. 10. Each "Input Shaper" is constrained near the corresponding GCO to minimize jitters introduced by routing resources. Moreover, DFFs are manually placed to enhance linearity. In the UltraScale+ FPGA, DFF groups are placed contiguously (SLICE XnYm and SLICE X(n+1)Ym) in a row.

In UltraScale and Virtex-7 FPGAs, DFF groups are placed at a fixed distance (SLICE XnYm and SLICE X(n+2)Ym).

Code density tests were conducted for 16-channel TDCs in three FPGAs. The linearity with different resolutions is summarized in TABLE V, showing the proposed TDC has high linearity and good uniformity.

# IV. COMPARISONS AND DISCUSSIONS

TABLE VI summarizes recently published FPGA-TDCs and the proposed TDC. As shown in Table VI, the TDL-TDC is the mainstream design. Other advanced architectures like the ring-oscillator-based (RO-based) Vernier [40] and the nonuniform monotonic multiphase (NUMMP) architectures [41] were also

well-developed. However, we have further developed the new GCO-TDC architecture (firstly published in Ref. [36] by Xu and Wu).

Unlike high resolution (<10 ps) TDCs aimed for scientific applications, our design aims for multichannel industrial LiDAR applications with variable resolutions and high linearity. Compared with TDL-based and NUMMP-based TDCs for similar specifications (for example, a 20 ps resolution or high linearity), the proposed TDC is more efficient in hardware consumption. Our design uses only one-third LUTs and one-fifth DFFs compared with Ref. [23], and one-third LUTs and one-third DFFs compared with Ref. [41]. Although the ROTDC in Ref. [40] has similar hardware consumption, its dead time is significant (maximum 602 ns). Although our GCO-TDC consumes slightly more logic resources than previously published GCO-TDCs [36], [38], [39], it is acceptable since the proposed TDC significantly improves both the resolution and linearity.

Although calibration methods like bin-by-bin calibration [50], bin-width calibration [29] and mixed calibration methods [32] can improve linearity and precision, they all need manual calibration. To achieve automatic calibration, gain and error calibration [43] and weighted calibration [44] methods are proposed. However, these designs only offer fixed resolutions. TDCs in Ref. [23], [41] and [42] provide flexible resolutions, but they all need manual configuration when resolution requirements change. To our knowledge, the VBCM is the first to achieve online resolution configuration and automatic calibration simultaneously in FPGA-TDCs. The C&C core serves 16 channels in this report but can serve more channels if required. Hence, the number of channels can be easily extended, and each channel's averaged logic resource consumption (with the C&C core) can be reduced. (R2, comment 6)

We use Verilog to implement the proposed TDC. As the GCO-TDC's resolution and linearity are sensitive to placing and routing strategies, it requires a few constraints to guarantee that GCO's placements and routes are immobile. Firstly, we used Vivado Tcl commands "set property BEL" "set property LOC" to place LUTs and DFFs [51] manually and then used commands "set\_property LOCK\_PINS" and "set property FIXED ROUTE" to lock LUTs' input pins and fix routing resources, respectively [51]. We can verify the "Input Shaper", GCO and sampling matrix by postimplementation simulations and the C&C core by behavior simulations. Although the design of the proposed TDC is slightly more complex than TDL-TDCs, it is acceptable since our TDC with automatic calibration is hardware cost-effective, highly linear and resolution-configurable. (R1, comment 1; R4, comment 2-ii)

### V. CONCLUSION

We proposed a new sampling structure, the sampling matrix, to enhance resolutions of GCO-TDCs. With this new structure, GCO-TDCs achieve excellent performances and low hardware consumption simultaneously. We also proposed the VBCM to achieve automatic calibration and online resolution configuration. Besides, the hardware implementation of this method is detailed in this paper, and it is hardware-efficient through multiplexing critical components.

To evaluate our design, we implemented the proposed 16-channel TDC in UltraScale+, UltraScale and Virtex-7 FPGAs, respectively. Experimental results indicate that the proposed TDCs have competitive linearity and excellent uniformity. Due to online resolution configuration, they can have broader applications in TOF-LiDAR, PET-CT, or time-resolved spectroscopy (such as Raman spectroscopy). It can also be utilized as a TDC-core in prototype designs or commercial products, benefiting from automatic calibration and low resource consumption.

#### REFERENCES

- [1]D. Morrison, S. Kennedy, D. Delic, M. R. Yuce, and J.-M. Redoute, 'A 64 × 64 SPAD Flash LIDAR Sensor Using a Triple Integration Timing Technique With 1.95 mm Depth Resolution', *IEEE Sensors J.*, vol. 21, no. 10, pp. 11361–11373, May 2021, doi: 10.1109/JSEN.2020.3030788.

- [2]S. Kurtti, A. Baharmast, J.-P. Jansson, and J. Kostamovaara, 'A Low-Noise and Wide Dynamic Range 15 MHz CMOS Receiver for Pulsed Time-of-Flight Laser Ranging', *IEEE Sensors J.*, vol. 21, no. 20, pp. 22944–22955, Oct. 2021, doi: 10.1109/JSEN.2021.3105447.

- [3]H. Seo *et al.*, 'Direct TOF Scanning LiDAR Sensor With Two-Step Multievent Histogramming TDC and Embedded Interference Filter', *IEEE J. Solid-State Circuits*, vol. 56, no. 4, pp. 1022–1035, Apr. 2021, doi: 10.1109/JSSC.2020.3048074.

- [4] Z. Zang, D. Xiao, and D. Day-Uei Li, 'Non-fusion time-resolved depth image reconstruction using a highly efficient neural network architecture', *Opt. Express*, vol. 29, no. 13, p. 19278, Jun. 2021, doi: 10.1364/OE.425917.

- [5]S. Jahromi, J.-P. Jansson, P. Keranen, and J. Kostamovaara, 'A 32 × 128 SPAD-257 TDC Receiver IC for Pulsed TOF Solid-State 3-D Imaging', *IEEE J. Solid-State Circuits*, vol. 55, no. 7, pp. 1960–1970, Jul. 2020, doi: 10.1109/JSSC.2020.2970704.

- [6]H. Ruokamo, L. W. Hallman, and J. Kostamovaara, 'An \$80\times25\$ Pixel CMOS Single-Photon Sensor With Flexible On-Chip Time Gating of 40 Subarrays for Solid-State 3-D Range Imaging', *IEEE J. Solid-State Circuits*, vol. 54, no. 2, pp. 501–510, Feb. 2019, doi: 10.1109/JSSC.2018.2878816.

- [7] 'Recovery of logged forest fragments in a humanmodified tropical landscape during the 2015-16 El Niño.pdf'.

- [8] J. Holma, I. Nissinen, J. Nissinen, and J. Kostamovaara, 'Characterization of the Timing Homogeneity in a CMOS SPAD Array Designed for Time-Gated Raman Spectroscopy', *IEEE Trans. Instrum. Meas.*, vol. 66, no. 7, pp. 1837–1844, Jul. 2017, doi: 10.1109/TIM.2017.2673002.

- [9]I. Nissinen, J. Nissinen, P. Keranen, D. Stoppa, and J. Kostamovaara, 'A \$16\times256\$ SPAD Line Detector With a 50-ps, 3-bit, 256-Channel Time-to-Digital Converter for Raman Spectroscopy', *IEEE Sensors J.*, vol. 18, no. 9, pp. 3789–3798, May 2018, doi: 10.1109/JSEN.2018.2813531.

- [10] H. Ma *et al.*, 'On-Chip Trust Evaluation Utilizing TDC-Based Parameter-Adjustable Security Primitive', *IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst.*, vol. 40, no. 10, pp. 1985–1994, Oct. 2021, doi: 10.1109/TCAD.2020.3035346.

- [11] G. Begin, K. M. Al-Tamimi, H. H. Alamdari, D. C. Roach, M. Schmidt, and K. El-Sankary, 'Respiratory Bidirectional Ultrasonic TOF Flow Sensor Resilience to Ambient Temperature Fluctuations', *IEEE Sensors J.*, vol. 21, no. 17, pp. 18920–18931, Sep. 2021, doi: 10.1109/JSEN.2021.3088713.

- [12] C.-C. Chen, C.-L. Chen, W. Fang, and Y.-C. Chu, 'All-Digital CMOS Time-to-Digital Converter With Temperature-Measuring Capability', *IEEE Trans. VLSI Syst.*, vol. 28, no. 9, pp. 2079–2083, Sep. 2020, doi: 10.1109/TVLSI.2020.3007587.

- [13] J. Lin, Y. Wang, Q. Cao, J. Kuang, and L. Wang, 'True random number generation based on arrival time and position of dark counts in a multichannel silicon photomultiplier', *Review of Scientific Instruments*, vol. 90, no. 11, p. 114704, Nov. 2019, doi: 10.1063/1.5109034.

- [14] Q. Yan, B. Zhao, Z. Hua, Q. Liao, and H. Yang, 'High-speed quantum-random number generation by continuous measurement of arrival time of photons', *Review of Scientific Instruments*, vol. 86, no. 7, p. 073113, Jul. 2015, doi: 10.1063/1.4927320.

- [15] K. Boretzky et al., 'NeuLAND: The high-resolution neutron time-of-flight spectrometer for R3B at FAIR', Nuclear Instruments and Methods in Physics Research Section A: Accelerators, Spectrometers, Detectors and Associated Equipment, vol. 1014, p. 165701, Oct. 2021, doi: 10.1016/j.nima.2021.165701.

- [16] K. Heijhoff *et al.*, 'Timing measurements with a 3D silicon sensor on Timepix3 in a 180 GeV/c hadron beam', *J. Inst.*, vol. 16, no. 08, p. P08009, Aug. 2021, doi: 10.1088/1748-0221/16/08/P08009.

- [17] J. Lu *et al.*, 'Readout Electronics Prototype of TOF Detectors in CEE of HIRFL', *IEEE Trans. Nucl. Sci.*, vol. 68, no. 8, pp. 1976–1983, Aug. 2021, doi: 10.1109/TNS.2021.3093544.

- [18] A. LaBella, S. Tavernier, C. Woody, M. Purschke, W. Zhao, and A. H. Goldan, 'Toward 100 ps Coincidence Time Resolution Using Multiple Timestamps in Depth-Encoding PET Modules: A Monte Carlo Simulation Study', *IEEE Trans. Radiat. Plasma Med. Sci.*, vol. 5, no. 5, pp. 679–686, Sep. 2021, doi: 10.1109/TRPMS.2020.3043691.

- [19] D. Xiao *et al.*, 'Dynamic fluorescence lifetime sensing with CMOS single-photon avalanche diode arrays and deep learning processors', *Biomed. Opt. Express*, vol. 12, no. 6, p. 3450, Jun. 2021, doi: 10.1364/BOE.425663.

- [20] M. Perenzoni, D. Perenzoni, and D. Stoppa, 'A 64 \$\times\$ 64-Pixels Digital Silicon Photomultiplier Direct TOF Sensor With 100-MPhotons/s/pixel Background Rejection and Imaging/Altimeter Mode With 0.14% Precision Up To 6 km for Spacecraft Navigation and Landing', *IEEE J. Solid-State Circuits*, vol. 52, no. 1, pp. 151–160, Jan. 2017, doi: 10.1109/JSSC.2016.2623635.

- [21] R. Machado, J. Cabral, and F. S. Alves, 'Recent Developments and Challenges in FPGA-Based Time-to-Digital Converters', *IEEE Trans. Instrum. Meas.*, vol. 68, no. 11, pp. 4205–4221, Nov. 2019, doi: 10.1109/TIM.2019.2938436.

- [22] J. Kalisz, 'Review of methods for time interval measurements with picosecond resolution', *Metrologia*, vol. 41, no. 1, pp. 17–32, Feb. 2004, doi: 10.1088/0026-1394/41/1/004.

- [23] W. Xie, Y. Wang, H. Chen, and D. D.-U. Li, '128-channel high-linearity resolution-adjustable time-to-digital converters for LiDAR applications: software predictions and hardware implementations', *IEEE Trans. Ind. Electron.*, pp. 1–1, 2021, doi: 10.1109/TIE.2021.3076708.

- [24] S. W. Hutchings *et al.*, 'A Reconfigurable 3-D-Stacked SPAD Imager With In-Pixel Histogramming for Flash LIDAR or High-Speed Time-of-Flight Imaging', *IEEE J. Solid-State Circuits*, vol. 54, no. 11, pp. 2947–2956, Nov. 2019, doi: 10.1109/JSSC.2019.2939083.

- [25] A. Carimatto *et al.*, '11.4 A 67,392-SPAD PVTB-compensated multichannel digital SiPM with 432 column-parallel 48ps 17b TDCs for endoscopic time-of-flight PET', in *2015 IEEE International Solid-State Circuits Conference (ISSCC) Digest of Technical Papers*, San Francisco, CA, USA, Feb. 2015, pp. 1–3. doi: 10.1109/ISSCC.2015.7062996.

- [26] L. H. C. Braga *et al.*, 'A Fully Digital 8\$\\times\,\$16 SiPM Array for PET Applications With Per-Pixel TDCs and Real-Time Energy Output', *IEEE J. Solid-State Circuits*, vol. 49, no. 1, pp. 301–314, Jan. 2014, doi: 10.1109/JSSC.2013.2284351.

- $[27] \quad `xst\_v6s6.pdf`.$

- [28] 'UltraScale Architecture Libraries Guide (UG974)', p. 661, 2018.

- [29] H. Chen, Y. Zhang, and D. D.-U. Li, 'A Low Nonlinearity, Missing-Code Free Time-to-Digital Converter Based on 28-nm FPGAs With Embedded Bin-Width Calibrations', *IEEE Trans. Instrum. Meas.*, vol. 66, no. 7, pp. 1912–1921, Jul. 2017, doi: 10.1109/TIM.2017.2663498.

- [30] Y. Wang, X. Zhou, Z. Song, J. Kuang, and Q. Cao, 'A 3.0-ps rms Precision 277-MSamples/s Throughput Time-to-Digital Converter Using Multi-Edge Encoding Scheme in a Kintex-7 FPGA', *IEEE Trans. Nucl. Sci.*, vol. 66, no. 10, pp. 2275–2281, Oct. 2019, doi: 10.1109/TNS.2019.2938571.

- [31] W. Xie, H. Chen, and D. D.-U. Li, 'Efficient time-to-digital converters in 20 nm FPGAs with wave union methods (the title was suggested by Reviewer 4, different from the original one 'Are wave union methods suitable for 20 nm FPGA-based time-to-digital converters')', *IEEE Trans. Ind. Electron.*, pp. 1–1, 2021, doi: 10.1109/TIE.2021.3053905.

- [32] H. Chen and D. D.-U. Li, 'Multichannel, Low Nonlinearity Time-to-Digital Converters Based on 20 and 28 nm FPGAs', *IEEE Trans. Ind. Electron.*, vol. 66, no. 4, pp. 3265–3274, Apr. 2019, doi: 10.1109/TIE.2018.2842787.

- [33] C. Liu and Y. Wang, 'A 128-Channel, 710 M Samples/Second, and Less Than 10 ps RMS Resolution Time-to-Digital Converter Implemented in a Kintex-7 FPGA', *IEEE Trans. Nucl. Sci.*, vol. 62, no. 3, pp. 773–783, Jun. 2015, doi: 10.1109/TNS.2015.2421319.

- [34] D. Li, R. Ma, X. Wang, J. Hu, M. Liu, and Z. Zhu, 'DTOF Image LiDAR With Stray Light Suppression and Equivalent Sampling Technology', *IEEE Sensors J.*, vol. 22, no. 3, pp. 2358–2369, Feb. 2022, doi: 10.1109/JSEN.2021.3136931.

- [35] D. Li, M. Liu, R. Ma, and Z. Zhu, 'An 8-ch LIDAR Receiver Based on TDC With Multi-Interval Detection and Real-Time \$In~Situ\$ Calibration', *IEEE Trans. Instrum. Meas.*, vol. 69, no. 7, pp. 5081–5090, Jul. 2020, doi: 10.1109/TIM.2019.2954173.

- [36] J. Wu and J. Xu, 'A Novel TDC Scheme: Combinatorial Gray Code Oscillator Based TDC for Low Power and Low Resource Usage Applications', in 2019 5th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Vienna, Austria, May 2019, pp. 1–7. doi: 10.1109/EBCCSP.2019.8836892.

- [37] R. Machado, F. S. Alves, and J. Cabral, 'Gray-Code TDC with Improved Linearity and Scalability for LiDAR applications', in 2020 6th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, Sep. 2020, pp. 1–8. doi: 10.1109/EBCCSP51266.2020.9291359.

- [38] S. Araujo, R. Machado, and J. Cabral, 'Double-sampling Gray TDC with a ROS Interface for a LiDAR System', in 2021 7th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, Jun. 2021, pp. 1–8. doi: 10.1109/EBCCSP53293.2021.9502403.

- [39] R. Machado, F. S. Alves, and J. Cabral, 'Gray-Code TDC with Improved Linearity and Scalability for LiDAR applications', in 2020 6th International Conference on Event-Based Control, Communication, and Signal Processing (EBCCSP), Krakow, Poland, Sep. 2020, pp. 1–8. doi: 10.1109/EBCCSP51266.2020.9291359.

- [40] K. Cui and X. Li, 'A High-Linearity Vernier Time-to-Digital Converter on FPGAs With Improved Resolution Using Bidirectional-Operating Vernier Delay Lines', *IEEE Trans. Instrum. Meas.*, vol. 69, no. 8, pp. 5941–5949, Aug. 2020, doi: 10.1109/TIM.2019.2959423.

- [41] J. Deng, P. Yin, X. Lei, Z. Shu, M. Tang, and F. Tang, 'A Tunable Parameter, High Linearity Time-to-Digital Converter Implemented in 28-nm FPGA', *IEEE Trans. Instrum. Meas.*, pp. 1–1, 2021, doi: 10.1109/TIM.2021.3117373.

- [42] Y. Hua and D. Chitnis, 'A Highly Linear and Flexible FPGA-Based Time-to-Digital Converter', *IEEE Trans. Ind. Electron.*, pp. 1–1, 2021, doi: 10.1109/TIE.2021.3128912.

- [43] K.-J. Choi and D.-W. Jee, 'Design and Calibration Techniques for a Multichannel FPGA-Based Time-to-Digital Converter in an Object Positioning System', *IEEE Trans. Instrum. Meas.*, vol. 70, pp. 1–9, 2021, doi: 10.1109/TIM.2020.3011490.

- [44] Y. Wang, W. Xie, H. Chen, and D. D.-U. Li, 'Multichannel time-to-digital converters with automatic calibration in Xilinx Zynq-7000 FPGA devices', *IEEE Trans. Ind. Electron.*, pp. 1–1, 2021, doi: 10.1109/TIE.2021.3111563.

- [45] Xilinx, 'Xilinx 7 Series FPGA and Zynq-7000 All Programmable SoC Libraries Guide for HDL Designs (UG768)', 2013. https://www.xilinx.com/support/documentation/ip\_documentation/mig\_7serie s/v4\_2/ug586\_7Series\_MIS.pdf (accessed Mar. 23, 2021).

- [46] 'ZCU104 Evaluation Board User Guide (UG1267)', p. 92, 2018.

- [47] 'KCU105 Board User Guide', p. 128, 2019.

- [48] 'NetFPGA-SUME Reference Manual'. 2016.

- [49] J. Wu, 'Uneven bin width digitization and a timing calibration method using cascaded PLL', in 2014 19th IEEE-NPSS Real Time Conference, Nara, Japan, May 2014, pp. 1–4. doi: 10.1109/RTC.2014.7097534.

- [50] J. Wu, 'Several Key Issues on Implementing Delay Line Based TDCs Using FPGAs', *IEEE Trans. Nucl. Sci.*, vol. 57, no. 3, pp. 1543–1548, Jun. 2010, doi: 10.1109/TNS.2010.2045901.

- [51] 'Vivado Design Suite Tcl Command Reference Guide', p. 1872, 2019.

Low hardware consumption, resolution-configurable gray code oscillator time-to- digital converters implemented in 16nm, 20nm and 28nm FPGAs

Yu Wang was born in Chongqing, China in 1995. He received the B.Eng. degree in measurement and control from the Harbin University of Science and Technology, in 2017, and the M.Eng. degree in electronics and communication engineering from Harbin Engineering University, in 2020. Since 2020, he has been working toward the Ph.D. degree founded by China Scholarship Council at the University of Strathclyde, Glasgow, U.K.

His current research interests include FPGA-based mixed signal circuits.

Wujun Xie was born in Hunan, China, in 1996. He received the B.Eng. degree in electronic and information engineering from the Hangzhou Dianzi University, Hangzhou, China, in 2017, and the M.S. degree in embedded systems from the University of Southampton, Southampton, U.K., in 2018. He has been working toward the Ph.D. degree at the University of Strathclyde, Glasgow, U.K since 2018.

Haochang Chen was born in Xian China, in 1990. He received the M.S. degree in embedded digital systems from the University of Sussex, Brighton, U.K., in 2013, and the PhD degree from the University of Strathclyde, Glasgow, U.K., in 2020, funded by EPSRC, and then he joined the Fraunhofer UK Research Ltd as a researcher. His current research interests include FPGA-based high-precision time metrology systems for ranging and

biomedical imaging applications.

David Day-Uei Li received the Ph.D. degree in electrical engineering from the National Taiwan University, Taipei, Taiwan, in 2001. He then joined the Industrial Technology Research Institute, Taiwan, working on fast wireless and wireless communication chipsets. From 2007 to 2011, he worked at the University of Edinburgh on two European projects focusing on CMOS single-photon avalanche diode sensors and systems. He then

took the lectureship in biomedical engineering at the University of Sussex, Brighton, in mid-2011, and in 2014 he joined the University of Strathclyde, Glasgow, as a Senior Lecturer. He has authored more than 90 journal and conference papers and holds 12 patents. His research exploits advanced sensor technologies to reveal low-light but fast biological phenomena.