Supporting model based safety and security assessment of high assurance systems

by

Hariharan Thiagarajan

B.Tech, Anna University, 2009

M.S., Kansas State University, 2012

### AN ABSTRACT OF A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

### DOCTOR OF PHILOSOPHY

Department of Computer Science Carl R. Ice College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2022

# Abstract

Modern embedded systems are more complex than ever due to intricate interaction with the physical world in a system environment and sophisticated software in a resourceconstrained context. Cyber attacks in software-reliant and networked safety-critical systems lead to consideration of security aspects from the system's inception. Model-Based Development (MBD) is one approach that has been an effective development practice because of the abstraction mechanism that hides the complicated lower-level details of software and hardware components. Standards play an essential role in embedded development to ensure the safety of the users and environment. In safety-critical domains like avionics, automotive, and medical devices, standards provide best practices and consistent approaches across the community.

The Analysis and Design Language (AADL) is a standardized modeling language that includes patterns that reflect best architectural practices inspired by multiple safety-critical domains. The work described in this dissertation comprises numerous contributions that support a model analysis framework for AADL that aims to help developers design and assure safety and security requirements and demonstrate system conformance to specific categories of standards.

This first contribution is Awas - an open-source framework for performing reachability analysis on AADL models annotated with information flow annotations at varying degrees of detail. The framework provides highly scalable interactive visualizations of flows with dynamic querying capabilities. Awas provide a simple domain-specific language to ease posing various queries to check information flow properties in the model.

The second contribution is a process for integrating risk management tasks of ISO 14971 - the primary risk management standard in the medical device domain — with AADL modeling, specifically with AADL's error modeling (EM) of fault and error propagations. This work uses an open-source patient-controlled analgesic (PCA) pump - the largest open-source AADL model to illustrate the integration of risk management process with AADL and provides the first mapping of AADL EM to ISO 14971 concepts. It also provides industry engineers, academic researchers, and regulators with a complex example that can be used to investigate methodologies and methods of integrating MBD and risk management.

The third contribution is a technique to model and analyze security properties such as confidentiality, authentication, and resource partitioning within AADL models. This effort comprises an AADL annex language to model multi-level security domains along with classification of system elements and data using those domains and a tool to infer security levels and check information leaks. The annex language and the tools are evaluated and integrated into the AADL development environment for a seamless workflow.

# Supporting model based safety and security assessment of high assurance systems

by

Hariharan Thiagarajan

B.Tech, Anna University, 2009

M.S., Kansas State University, 2012

### A DISSERTATION

submitted in partial fulfillment of the requirements for the degree

### DOCTOR OF PHILOSOPHY

Department of Computer Science Carl R. Ice College of Engineering

KANSAS STATE UNIVERSITY Manhattan, Kansas

2022

Approved by:

Major Professor John Hatcliff

# Copyright

© Hariharan Thiagarajan 2022.

# Abstract

Modern embedded systems are more complex than ever due to intricate interaction with the physical world in a system environment and sophisticated software in a resourceconstrained context. Cyber attacks in software-reliant and networked safety-critical systems lead to consideration of security aspects from the system's inception. Model-Based Development (MBD) is one approach that has been an effective development practice because of the abstraction mechanism that hides the complicated lower-level details of software and hardware components. Standards play an essential role in embedded development to ensure the safety of the users and environment. In safety-critical domains like avionics, automotive, and medical devices, standards provide best practices and consistent approaches across the community.

The Analysis and Design Language (AADL) is a standardized modeling language that includes patterns that reflect best architectural practices inspired by multiple safety-critical domains. The work described in this dissertation comprises numerous contributions that support a model analysis framework for AADL that aims to help developers design and assure safety and security requirements and demonstrate system conformance to specific categories of standards.

This first contribution is Awas - an open-source framework for performing reachability analysis on AADL models annotated with information flow annotations at varying degrees of detail. The framework provides highly scalable interactive visualizations of flows with dynamic querying capabilities. Awas provide a simple domain-specific language to ease posing various queries to check information flow properties in the model.

The second contribution is a process for integrating risk management tasks of ISO 14971 - the primary risk management standard in the medical device domain — with AADL modeling, specifically with AADL's error modeling (EM) of fault and error propagations. This work uses an open-source patient-controlled analgesic (PCA) pump - the largest open-source AADL model to illustrate the integration of risk management process with AADL and provides the first mapping of AADL EM to ISO 14971 concepts. It also provides industry engineers, academic researchers, and regulators with a complex example that can be used to investigate methodologies and methods of integrating MBD and risk management.

The third contribution is a technique to model and analyze security properties such as confidentiality, authentication, and resource partitioning within AADL models. This effort comprises an AADL annex language to model multi-level security domains along with classification of system elements and data using those domains and a tool to infer security levels and check information leaks. The annex language and the tools are evaluated and integrated into the AADL development environment for a seamless workflow.

# Contents

| Li | st of l | Figures  | x                                                                    | iii |

|----|---------|----------|----------------------------------------------------------------------|-----|

| Li | st of ' | Tables   |                                                                      | vii |

| Ac | know    | ledgem   | ents                                                                 | iii |

| De | edicat  | ion      |                                                                      | ix  |

| 1  | Intro   | oduction | n                                                                    | 1   |

| 2  | Lite    | rature I | Review                                                               | 8   |

|    | 2.1     | System   | n                                                                    | 8   |

|    | 2.2     | System   | n Engineering                                                        | 10  |

|    |         | 2.2.1    | Challenges                                                           | 12  |

|    | 2.3     | Model    | Based System Engineering (MBSE)                                      | 14  |

|    |         | 2.3.1    | Document-Centric System Engineering                                  | 14  |

|    |         | 2.3.2    | Model-Centric System Engineering                                     | 15  |

|    | 2.4     | Safety   | -Critical System                                                     | 16  |

|    |         | 2.4.1    | Interoperable Medical Devices                                        | 16  |

|    |         | 2.4.2    | Stakeholders                                                         | 17  |

|    |         | 2.4.3    | Medical Device: PCA Pump                                             | 18  |

|    |         | 2.4.4    | PCA Pump Interlock Scenario                                          | 20  |

|    |         | 2.4.5    | Challenges                                                           | 22  |

|    | 2.5     | Model    | ing Languages and Tools                                              | 23  |

|    |         | 2.5.1    | OMG SysML (Object Management Group System Modeling Language) $^{32}$ | 23  |

|   |      | 2.5.2   | $Simulink^{33}$                                                         | 23 |

|---|------|---------|-------------------------------------------------------------------------|----|

|   |      | 2.5.3   | Architecture Analysis & Design Language (AADL)                          | 24 |

|   | 2.6  | Risk N  | lanagement                                                              | 28 |

|   |      | 2.6.1   | Challenges of Using $ISO\ 14971$ In Distributed Risk Management $~$ .   | 30 |

|   | 2.7  | Error 1 | Modeling                                                                | 32 |

|   |      | 2.7.1   | Terms and Definitions                                                   | 32 |

|   |      | 2.7.2   | Faults, Failures, and Errors                                            | 35 |

|   |      | 2.7.3   | EMv2                                                                    | 37 |

|   | 2.8  | Hazaro  | l Analysis                                                              | 38 |

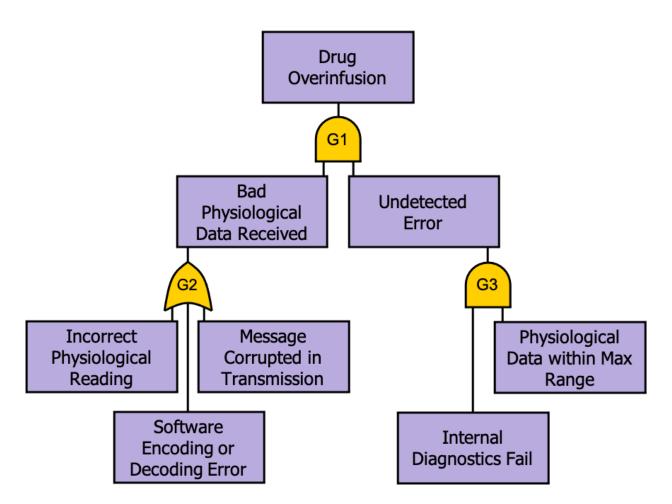

|   |      | 2.8.1   | Fault Tree Analysis (FTA)                                               | 39 |

|   |      | 2.8.2   | Failure Mode Effect Analysis (FMEA)                                     | 41 |

|   |      | 2.8.3   | System Theoretic Process Analysis (STPA)                                | 44 |

|   | 2.9  | Interco | onnected Systems                                                        | 48 |

|   |      | 2.9.1   | Communication Paradigms                                                 | 48 |

|   |      | 2.9.2   | AAMI/ANSI/IEC TIR80001                                                  | 49 |

|   | 2.10 | Securit | ty                                                                      | 50 |

|   |      | 2.10.1  | Dolev-Yao Network Adversary Model                                       | 50 |

|   |      | 2.10.2  | MILS                                                                    | 51 |

|   |      | 2.10.3  | AADL Security Annex                                                     | 52 |

| 3 | Mod  | eling C | ritical Systems                                                         | 54 |

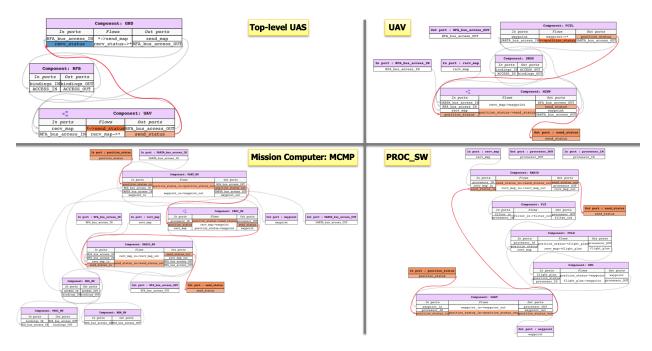

|   | 3.1  | Unmai   | nned Aerial System                                                      | 54 |

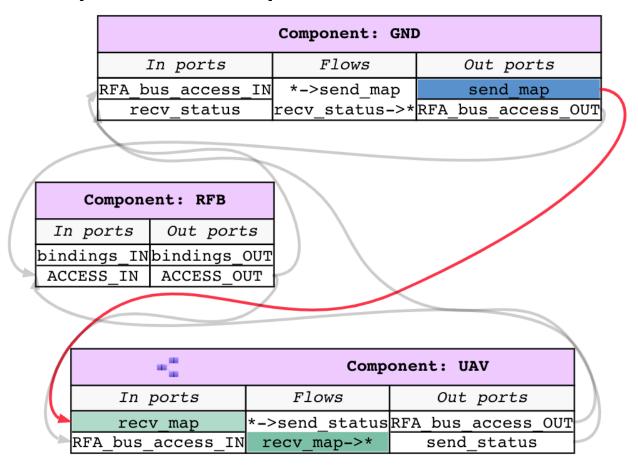

|   |      | 3.1.1   | UAS: The top level system with ground station and UAV                   | 56 |

|   |      | 3.1.2   | Security Requirments                                                    | 58 |

|   | 3.2  | Modeli  | ing Error Library                                                       | 62 |

|   |      | 3.2.1   | Error Library                                                           | 63 |

|   |      | 3.2.2   | Guidelines for developing device specific error library                 | 65 |

|   |      | 3.2.3   | Effect of violation of communication properties mapped to error library | 66 |

|   |      | 3.2.4    | Effect of violation of security properties mapped to error Library | 67  |

|---|------|----------|--------------------------------------------------------------------|-----|

|   | 3.3  | Applic   | eation                                                             | 68  |

|   |      | 3.3.1    | Pulse Oximeter (PulseOX) - Sensor                                  | 69  |

|   | 3.4  | AAMI     | /ANSI/IEC TIR80001                                                 | 71  |

|   |      | 3.4.1    | Performing AAMI/ANSI/IEC TIR80001 on PulseOX                       | 77  |

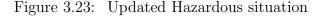

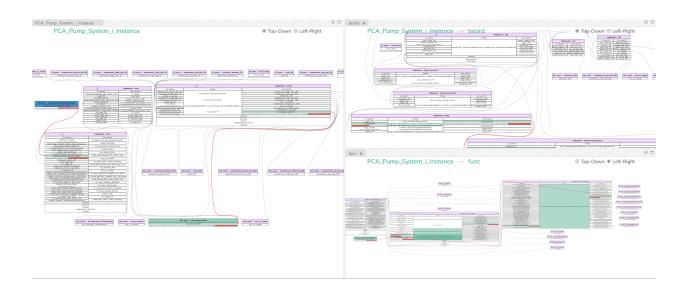

|   | 3.5  | Open     | PCA Pump - Actuator                                                | 85  |

|   |      | 3.5.1    | Safety Subsystem                                                   | 89  |

|   |      | 3.5.2    | Fluid Subsystem                                                    | 91  |

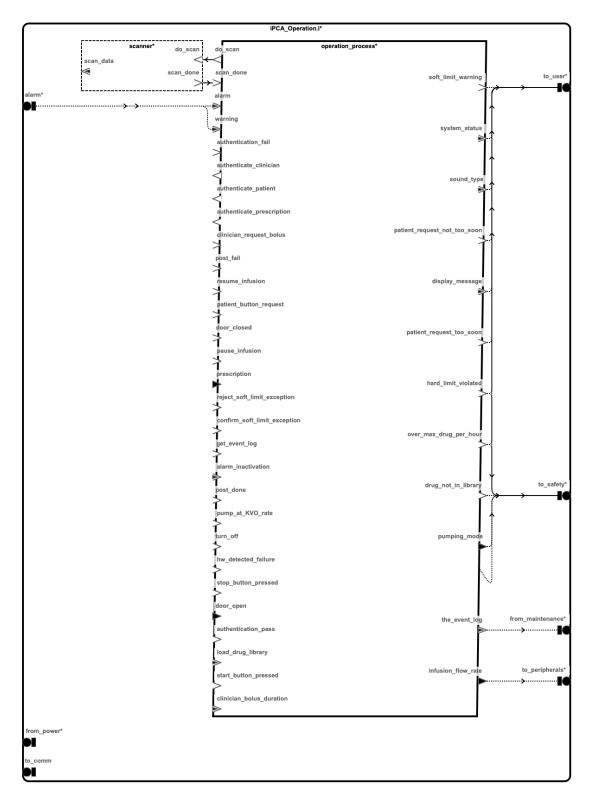

|   |      | 3.5.3    | Operation Subsystem                                                | 91  |

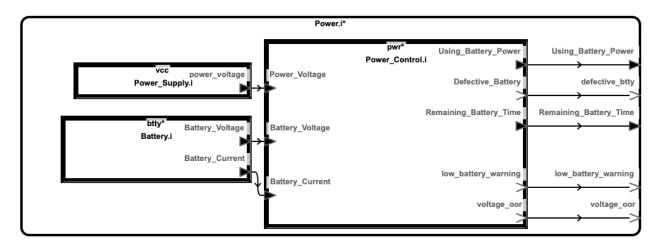

|   |      | 3.5.4    | Power Subsystem                                                    | 92  |

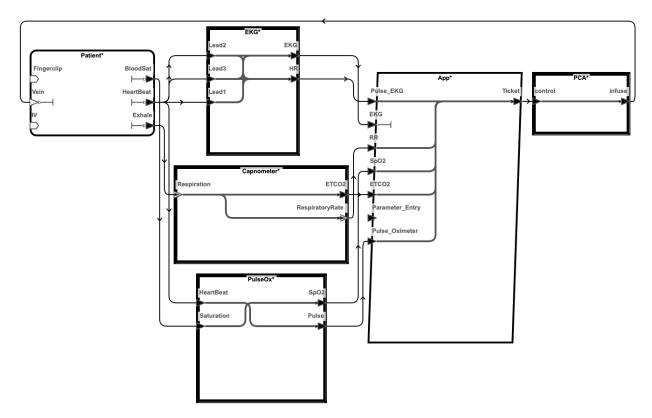

|   | 3.6  | App -    | Controller                                                         | 92  |

|   |      | 3.6.1    | Version II                                                         | 94  |

|   |      | 3.6.2    | Version III                                                        | 95  |

| 4 | The  | ories an | d Tools                                                            | 98  |

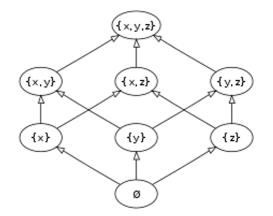

|   | 4.1  | Lattic   | e Theory                                                           | 98  |

|   |      | 4.1.1    | Error Domains                                                      | 102 |

|   |      | 4.1.2    | Security Domains                                                   | 102 |

|   | 4.2  | Failure  | e Propagation and Transformation Calculus (FPTC)                   | 103 |

|   | 4.3  | Model    | Checking                                                           | 104 |

|   |      | 4.3.1    | Agree                                                              | 105 |

|   |      | 4.3.2    | Resolute                                                           | 106 |

|   |      | 4.3.3    | AltaRica                                                           | 107 |

|   |      | 4.3.4    | xSAP                                                               | 107 |

| 5 | Info | rmation  | Flow Framework                                                     | 109 |

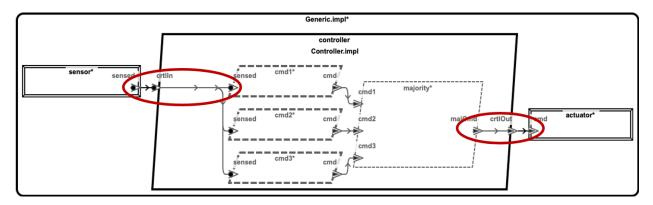

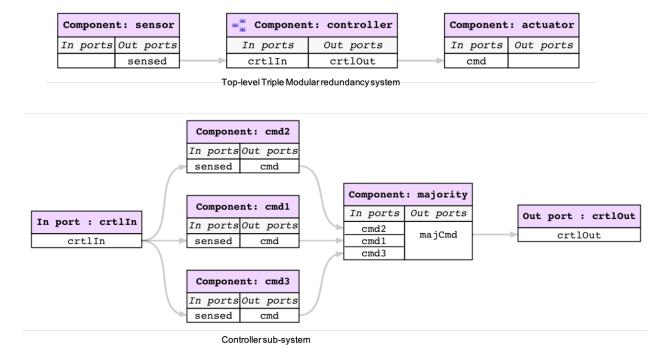

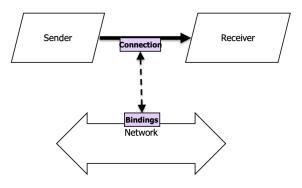

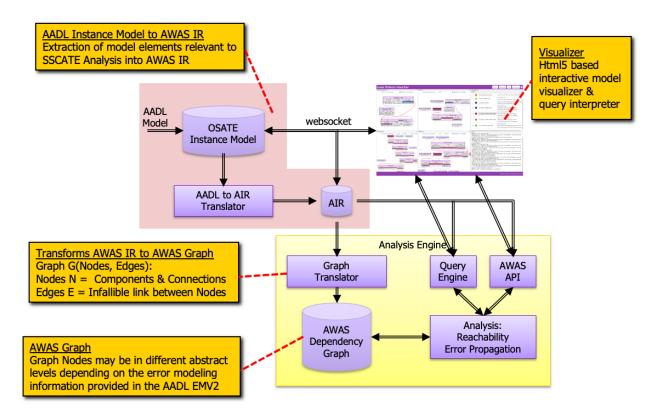

|   | 5.1  | AADL     | to Awas Graph                                                      | 109 |

|   |      | 5.1.1    | Connection Instance                                                | 110 |

|   |       | 5.1.2    | Feature Groups                        | 111 |

|---|-------|----------|---------------------------------------|-----|

|   |       | 5.1.3    | Bindings                              | 113 |

|   | 5.2   | Awas     | Graph Definitions                     | 114 |

|   | 5.3   | Depen    | dence Analysis                        | 115 |

|   |       | 5.3.1    | Node-level Analysis                   | 116 |

|   |       | 5.3.2    | Port-level Analysis                   | 119 |

|   |       | 5.3.3    | Error Propagation Analysis            | 123 |

|   |       | 5.3.4    | State Reachability                    | 124 |

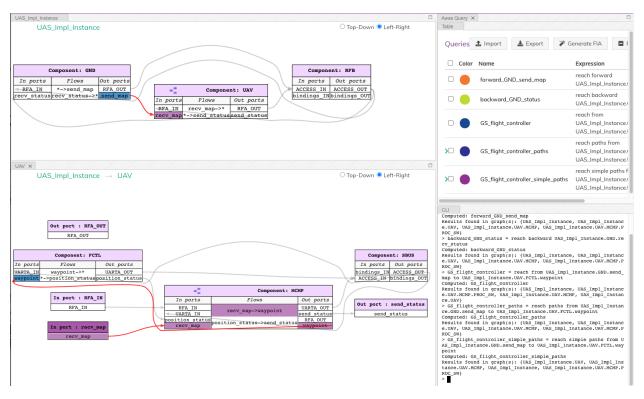

| 6 | Awa   | s Visua  | lization and Querying                 | 131 |

|   | 6.1   | Tool A   | Architecture                          | 131 |

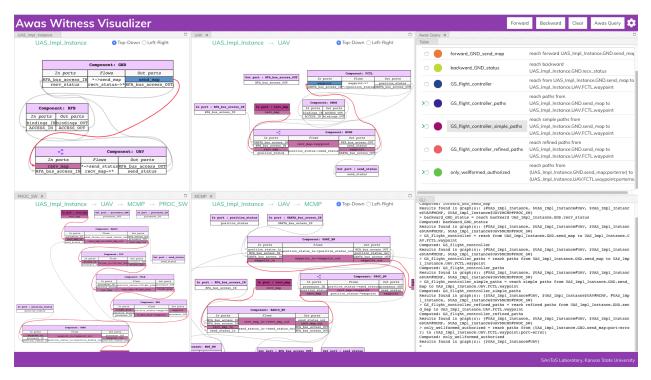

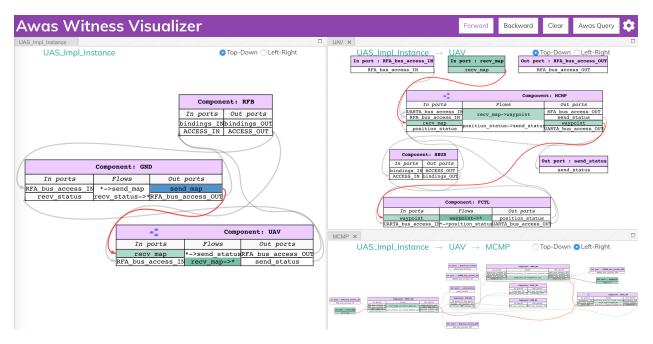

|   | 6.2   | Visual   | izer                                  | 132 |

|   |       | 6.2.1    | Base Awas Dependence Graph            | 134 |

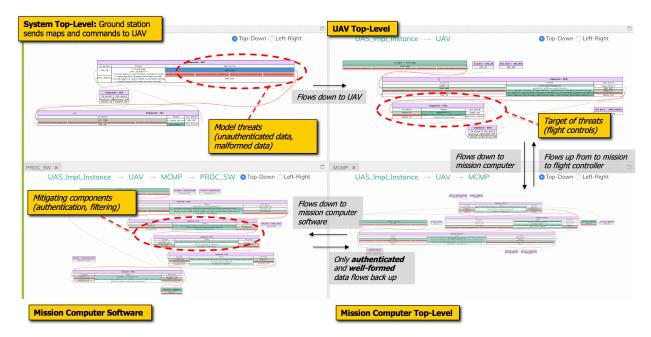

|   |       | 6.2.2    | Property Propagation Graph            | 135 |

|   | 6.3   | Query    | Language                              | 137 |

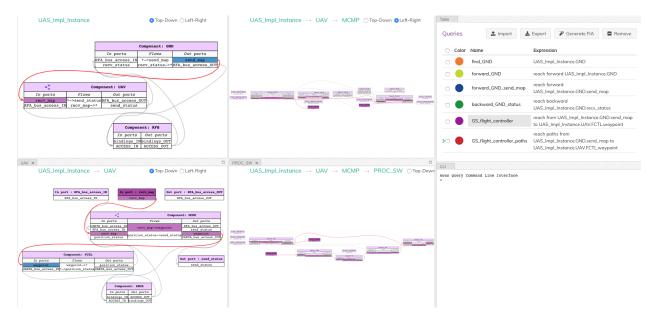

|   |       | 6.3.1    | Forward Reachability                  | 138 |

|   |       | 6.3.2    | Backward Reachability                 | 139 |

|   |       | 6.3.3    | Source and Target Reachability        | 141 |

|   |       | 6.3.4    | Path Reachability                     | 141 |

|   |       | 6.3.5    | Error Reachability                    | 143 |

| 7 | App   | lication | of Awas                               | 145 |

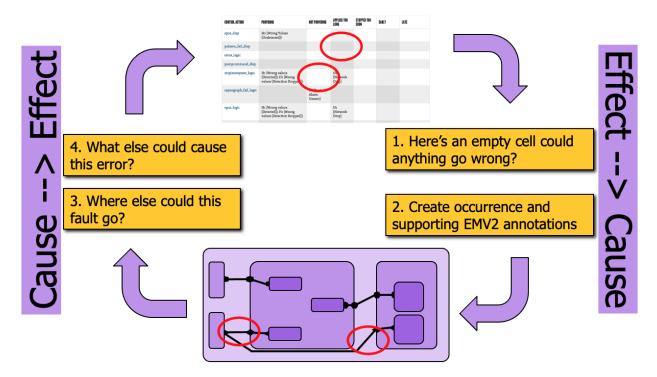

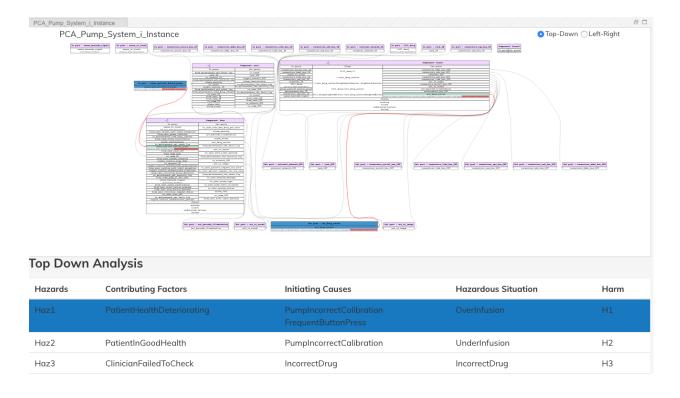

|   | 7.1   | Autom    | nating risk analysis of ISO 14971     | 145 |

|   | 7.2   | AADL     | Error Modeling for the OpenPCA System | 147 |

|   | 7.3   | AADL     | Error Modeling Analysis Support       | 154 |

|   | 7.4   | Securit  | ty Modeling Framework                 | 157 |

|   |       | 7.4.1    | Analysis                              | 163 |

| 8 | Integ | gration  | and Evaluation                        | 166 |

|     | 8.1    | Integra | ation                                                                                          | 166 |

|-----|--------|---------|------------------------------------------------------------------------------------------------|-----|

|     |        | 8.1.1   | Visualizer Integration                                                                         | 168 |

|     |        | 8.1.2   | Alisa Integration                                                                              | 169 |

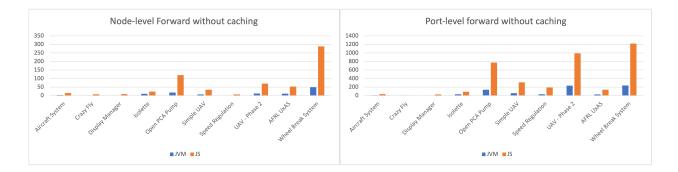

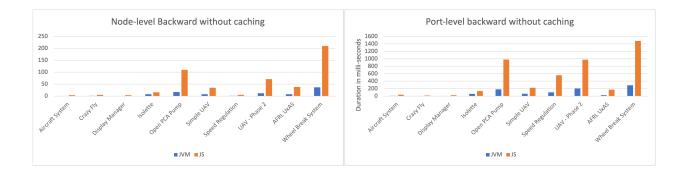

|     | 8.2    | Evalua  | tion $\ldots$ | 170 |

| 9   | Futu   | re Worl | k and Conclusions                                                                              | 176 |

|     | 9.1    | Extens  | sions                                                                                          | 177 |

|     | 9.2    | Discus  | sions                                                                                          | 177 |

|     |        | 9.2.1   | Is MBSE entirely model based?                                                                  | 177 |

|     |        | 9.2.2   | Can automated risk analysis tool be trusted?                                                   | 179 |

| Bil | oliogr | aphy .  |                                                                                                | 180 |

| А   | Quer   | ry Lang | uage Grammar                                                                                   | 191 |

| В   | ISO    | 14971 . |                                                                                                | 193 |

| С   | Secu   | rity Mo | odeling Framework Annex Grammar                                                                | 197 |

# List of Figures

| 2.1  | Cyber-Physical System - Control Structure                                                                    | 9  |

|------|--------------------------------------------------------------------------------------------------------------|----|

| 2.2  | V-Model System Development Process                                                                           | 11 |

| 2.3  | Example PCA Pump                                                                                             | 19 |

| 2.4  | ICE Instantiation of PCA Safety Interlock                                                                    | 20 |

| 2.5  | Simple PCA Interlock with PulseOx                                                                            | 21 |

| 2.6  | SysML block definition diagram for PCA interlock system                                                      | 24 |

| 2.7  | SysML internal block diagram for PCA interlock system                                                        | 25 |

| 2.8  | Patient model in Simulink developed by Arney <i>et al.</i> <sup>30</sup> $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 26 |

| 2.9  | AADL Graphical and Textual view                                                                              | 26 |

| 2.10 |                                                                                                              | 27 |

| 2.11 | ISO 14971 Risk Management Process                                                                            | 29 |

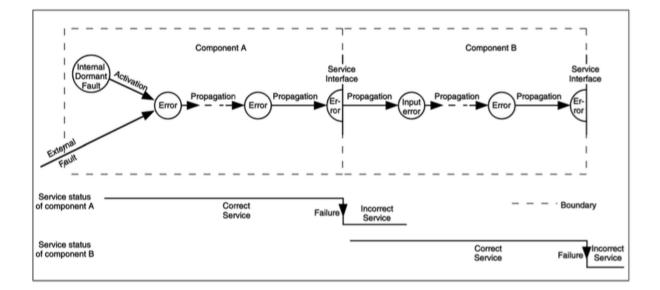

| 2.12 | Fault, Error, and Failure relation                                                                           | 36 |

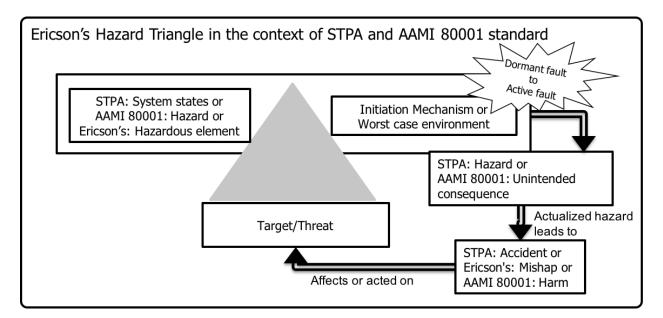

| 2.13 | Hazard relationship in different terminology                                                                 | 39 |

| 2.14 | FTA analysis of PCA interlock system as demonstrated by Procter $et~al.^{40}$ .                              | 40 |

| 2.15 | PCA Pump Interlock control structure                                                                         | 45 |

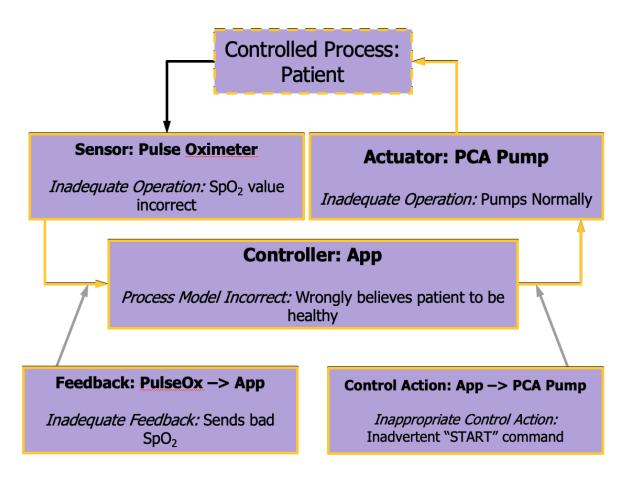

| 2.16 | STPA Step 2 causality guidwords                                                                              | 46 |

| 2.17 | Causal scenario for inadvertently providing $START$ command $\ldots$                                         | 47 |

| 2.18 | AADL security annex classification levels                                                                    | 52 |

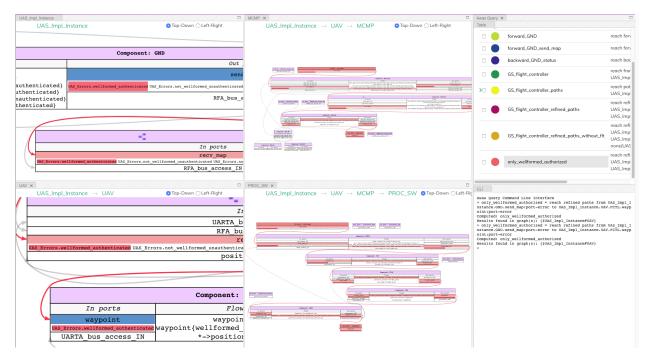

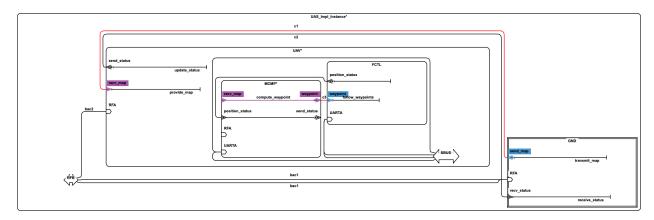

| 3.1  | A Simple UAS Example with AADL Modeling Artifacts                                                            | 55 |

| 3.2  | Simple UAV system top level model – illustrating inter-component dependences                                 |    |

| 3.3  | Instance diagram of top level system and the UAV subsystem                                                   | 57 |

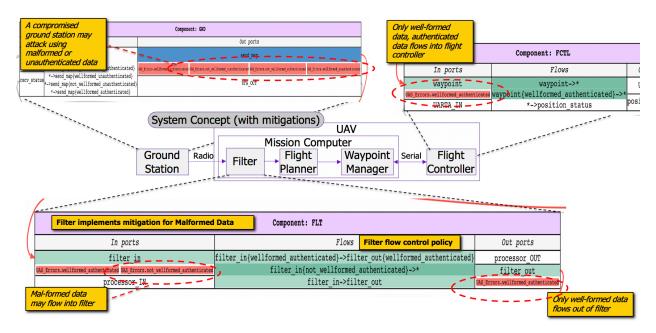

| 3.4  | Mitigation concept to satisfy Req-1 and Req-2                                                                | 59 |

|      |                                                                                                              |    |

| 3.5  | Software Sub-system                                                         | 60 |

|------|-----------------------------------------------------------------------------|----|

| 3.6  | AADL Flow and Error Propagations Annotations in Mission Computer            | 62 |

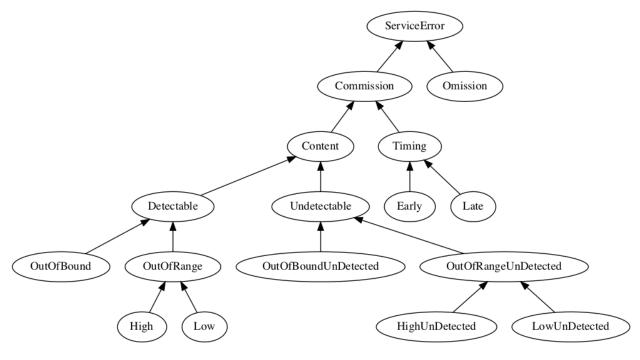

| 3.7  | Error Library                                                               | 63 |

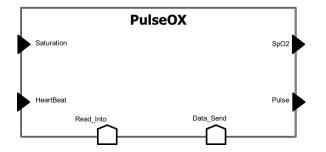

| 3.8  | Pulse Oximeter Specification                                                | 69 |

| 3.9  | EBL error types adapted to the PulseOX                                      | 71 |

| 3.10 | Hazard Property Set                                                         | 72 |

| 3.11 | Hazardous Situation Property Set                                            | 73 |

| 3.12 | Cause Property Set                                                          | 73 |

| 3.13 | Unintended Consequence Property Set                                         | 74 |

| 3.14 | Risk control Property Set                                                   | 76 |

| 3.15 | Pulse Oximeter Subsystem                                                    | 78 |

| 3.16 | Haz01 definition                                                            | 79 |

| 3.17 | Haz01 application on the controller component                               | 79 |

| 3.18 | Definition of Hazard HS01                                                   | 79 |

| 3.19 | Application of Hazardous situation HS01 on EMV2's propagation $\ . \ . \ .$ | 80 |

| 3.20 | Definition of a cause                                                       | 80 |

| 3.21 | Application of cause C01 and the association of the flow                    | 81 |

| 3.22 | Definition of Unintended Consequence UC01                                   | 82 |

| 3.23 | Updated Hazardous situation                                                 | 83 |

| 3.24 | Open PCA Pump Containment Hierarchy                                         | 86 |

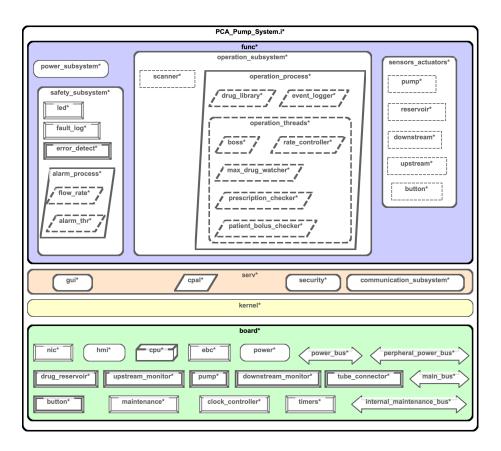

| 3.25 | Context for Open PCA Pump                                                   | 87 |

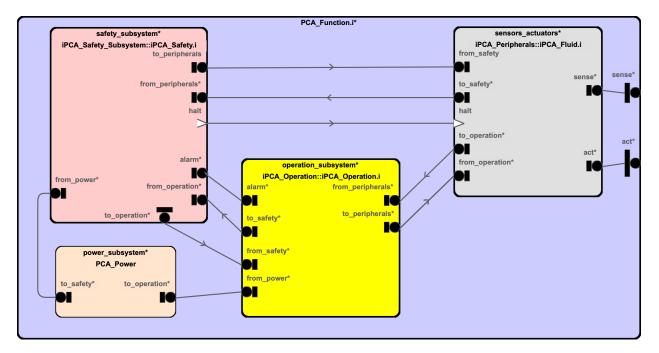

| 3.26 | PCA Pump Functional Architecture                                            | 88 |

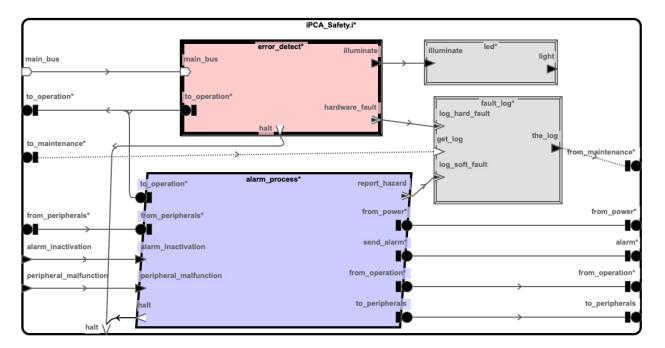

| 3.27 | Safety Subsystem                                                            | 89 |

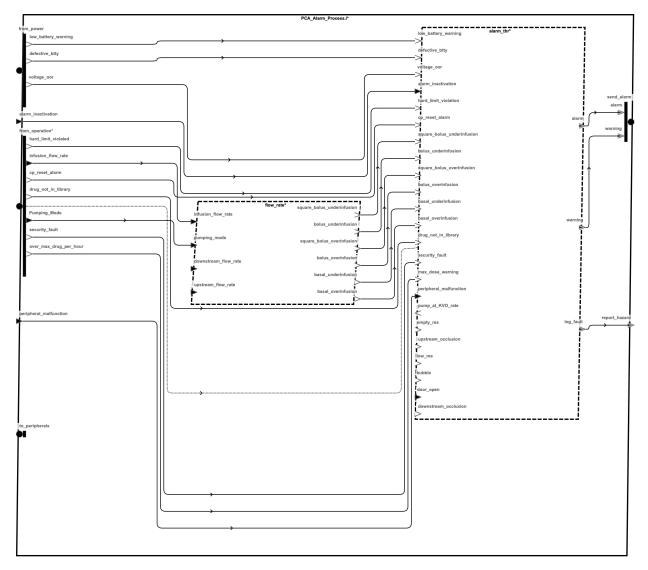

| 3.28 | Safety Process                                                              | 90 |

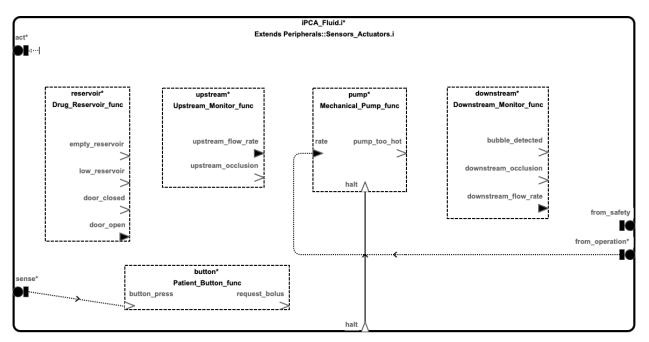

| 3.29 | Fluid Subsystem                                                             | 91 |

| 3.30 | Operation Subsystem                                                         | 93 |

| 3.31 | Power Subsystem                                                             | 94 |

| 3.32 | Interaction between Report and Model                                          | 95  |

|------|-------------------------------------------------------------------------------|-----|

| 3.33 | Interlock Algorithm                                                           | 96  |

| 3.34 | PCA interlock with redundant sensors                                          | 97  |

| 3.35 | Augmented error behavior                                                      | 97  |

| 4.1  | Hass diagram for power set of $\{x,y,z\}$                                     | 99  |

| 5.1  | Generic triple modular redundancy system                                      | 110 |

| 5.2  | Awas graphs of triple modular redundancy system                               | 111 |

| 5.3  | Feature groups and bi-directional connection                                  | 112 |

| 5.4  | Network bus realizing a connection between a Sender and a Receiver $\ldots$   | 113 |

| 5.5  | Error condition                                                               | 126 |

| 5.6  | Error behavior of PCA interlock app                                           | 127 |

| 6.1  | AADL reachability analysis tool architecture                                  | 132 |

| 6.2  | Awas reachability visualizer and query interpreter                            | 133 |

| 6.3  | Awas Visualization of a Forward Slice (interactive forward dependence query)  | 134 |

| 6.4  | Awas Visualization of AADL EMv2-based Security Properties (Overview)          | 135 |

| 6.5  | Awas Visualization of AADL EMv2-based Security Properties (Details) $\ . \ .$ | 136 |

| 6.6  | Forward reachability query and its result projected on the dependence graph   | 139 |

| 6.7  | Backward reachability query and its result projected on the multiple graphs   | 140 |

| 6.8  | Query with both source and target                                             | 141 |

| 6.9  | Result of query concept 3 6.8                                                 | 142 |

| 6.10 | Query with both source and target and path filters                            | 142 |

| 6.11 | Reachability query with EMV2 errors                                           | 143 |

| 6.12 | Result of query 6.11                                                          | 144 |

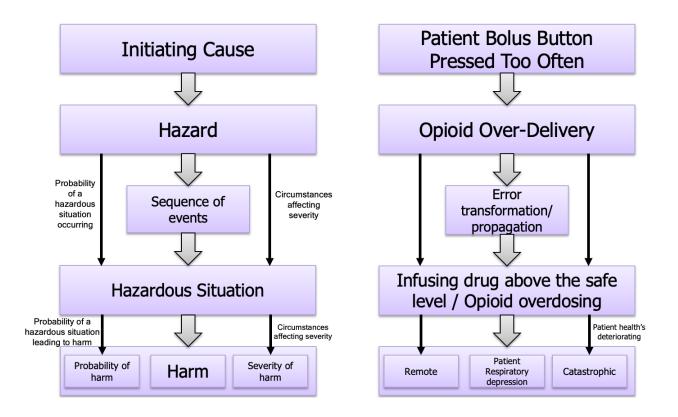

| 7.1  | ISO 14971 Key Risk Analysis Terms and Relationships                           | 146 |

| 7.2  | Awas AADL Intra-component Error Flows Visualization                           | 154 |

| 7.3  | Awas AADL System-wide Error Flow Visualization (selected sub-systems) $$ .  | 156 |

|------|-----------------------------------------------------------------------------|-----|

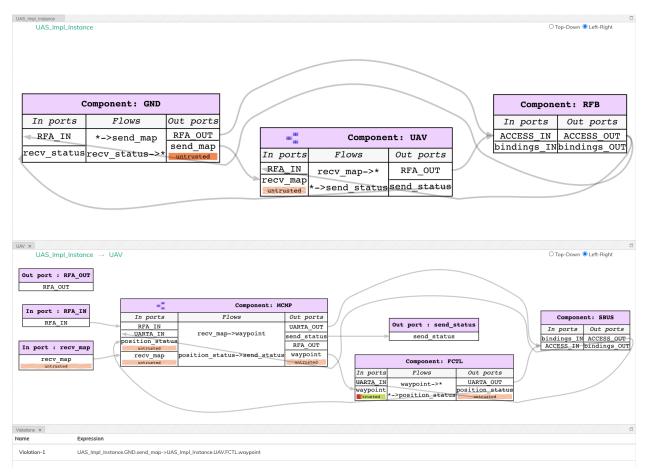

| 7.4  | Awas ISO 14971 Report (excerpts) illustrating Sequence of Events Leading to |     |

|      | Hazardous Situation                                                         | 157 |

| 7.5  | SMF Library example                                                         | 158 |

| 7.6  | Generated Hass diagram of security type lattice                             | 159 |

| 7.7  | Security lattice with disjoint domains                                      | 160 |

| 7.8  | Association of security types                                               | 160 |

| 7.9  | Result of SMF analysis on UAV system                                        | 161 |

| 7.10 | De-classification of security types                                         | 162 |

| 7.11 | Filter component with declassification policy                               | 162 |

| 8.1  | Forward Slice (interactive forward dependence query) on AADI Graphical view | 167 |

| 8.2  | Forward Slice (interactive forward dependence query) on AADI Graphical view | 167 |

| 8.3  | Result of Query Concept 4 in Awas Visualizer                                | 168 |

| 8.4  | Result of Query Concept 4 in AADL graphical view                            | 169 |

| 8.5  | ReqSpec requirement specification for the UAV model                         | 170 |

| 8.6  | Verification plan for the UAV model                                         | 170 |

| 8.7  | ALISA Assurance view                                                        | 171 |

| 8.8  | Forward Analysis                                                            | 171 |

| 8.9  | Backward Analysis                                                           | 172 |

| 8.10 | Source to Target Analysis                                                   | 172 |

| 8.11 | Source to Target With Paths Analysis                                        | 172 |

| 8.12 | Performance Improvement in both JVM and JavaScript Platform $\ . \ . \ .$ . | 174 |

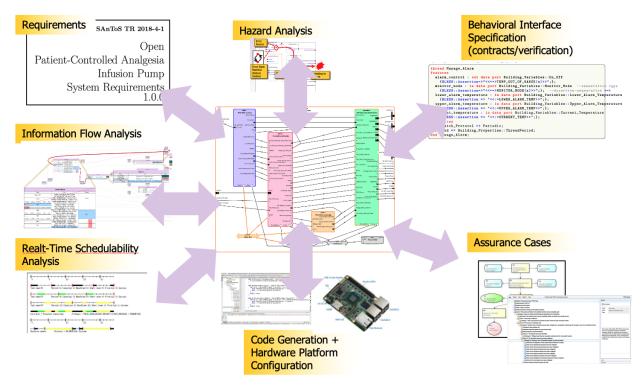

| 9.1  | Model centric system engineering                                            | 178 |

# List of Tables

| 2.1  | Generated FMEA report for the PCA model                                                             | 43  |

|------|-----------------------------------------------------------------------------------------------------|-----|

| 2.2  | PCA Pump Interlock STPA Step 1                                                                      | 45  |

| 3.1  | Communication Errors                                                                                | 67  |

| 3.2  | Violation of security property captured as basic error types $^{50}$                                | 68  |

| 3.3  | Definition of $\bigoplus$ operator used for combining likelihoods of different branches             |     |

|      | in the sequence of events leading to <i>Hazardous Situation</i>                                     | 74  |

| 3.4  | Definition of $\bigotimes$ operator used for combining likelihoods in sequence in the               |     |

|      | sequence of events                                                                                  | 74  |

| 3.5  | Risk Level Matrix <sup>43</sup>                                                                     | 75  |

| 3.6  | IEC 80001 Risk analysis report format                                                               | 77  |

| 3.7  | Causal path between internal causes and <i>Hazardous Situation</i>                                  | 81  |

| 3.8  | Causal path between external causes and <i>Hazardous Situation</i>                                  | 81  |

| 3.9  | Risk analysis report at the end of Step 5                                                           | 83  |

| 3.10 | Risk analysis report at the end of step $6 \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 84  |

| 3.11 | PulseOX redacted risk analysis report                                                               | 85  |

| 5.1  | Insight into state reachability analysis                                                            | 130 |

| 7.1  | ISO 14971 Risk Analysis Concepts Applied to the PCA Pump (excerpts)                                 | 147 |

| 8.1  | Features of sample AADL models                                                                      | 171 |

### Acknowledgments

First and foremost, I thank my major professor, Dr. John Hatcliff, for his consistent support, guidance, patience and kindness throughout my graduate studies. His insightful comments and constructive criticisms shaped my problem-solving and technical communication skills. I would also like to thank Dr. Robby for grooming my software engineering skills and for the opportunity to work on cutting-edge industrial technologies. I immensely enjoyed working with Dr. Eugene Vasserman in developing the security aspects of a safety-critical system.

I am thankful to Dr. David Schmidt and Dr. Torben Amtoft for the engaging lectures and discussions that encouraged me to work on static analysis. I am grateful to Jason Belt and Dr. Sam Procter for all the feedback and collaboration through the years. Thanks to all students and other members of SAnToS Laboratory for the exciting discussions and lively workspace.

I want to thank Rand Whillock, Dr. Robert Edman, Todd Carpenter from Adventium Labs, and Dr. Peter H. Feiler and Lutz Wrage from Software Engineering Institute for their collaboration on several projects.

I am grateful to my wife, I could not have completed this dissertation without her love and support. Finally, my sincere gratitude goes to my mother, father, sisters, and both my brothers-in-law for their patience and belief during my long pursuit of Ph.D.

# Dedication

This dissertation is dedicated to my family, without whom this endeavor would not be possible.

# Chapter 1

# Introduction

"There is a race between the increasing complexity of the systems we build and our ability to develop intellectual tools for understanding their complexity. If the race is won by our tools, then systems will eventually become easier to use and more reliable. If not, they will continue to become harder to use and less reliable for all but a relatively small set of common tasks. Given how hard thinking is, if those intellectual tools are to succeed, they will have to substitute calculation for thought."

#### - Leslie Lamport

In recent times, critical systems are larger and more complex than ever due to sophisticated needs from the market. An important factor in the growing complexity of systems is the increased use of software to implement system's behaviors. Moreover, critical software components and the computing platform execute in a resource-constrained environment.

A common approach to tackle large systems is to decompose systems into sub-systems and utilize off-the-shelf components where ever possible. In this approach, multiple organizations can concurrently develop sub-systems independently and thus significantly reduce time-tomarket. This contrasts with the development of many legacy systems, in which a single organization developed the entire system as a monolithic unit. An ideal goal is to develop interoperable and reusable sub-systems that are usable in varying contexts. Aerospace, military, and medical are some of the major industries that develop critical systems. Failures in these systems can result in huge losses. Therefore hazard analysis, risk assessment, and reliability estimates are vital activities performed in developing these systems to avoid accidents and improve trust.

One approach to developing systems of systems is to use a model-based system engineering (MBSE) methodology. Developing a system model captures of the overall architecture and assigns responsibilities among stakeholders. In a distributed development with multiple stakeholders, integration failure is a common concern. Identification and rectification of integration failures are expensive due to encountering integration failures late in the system integration process, typically after developing individual components. Architecture and Analysis Definition Language (AADL) is a standardized architecture description language<sup>1</sup> enabling: (a) engineers to define a vocabulary and modeling elements for common architecture and coding patterns used in real-time embedded systems and, (b) modeling, analysis, and code generation tools to help engineers design and implement a system. These capabilities enable developers to design and address important engineering challenges before considerable monetary investments are associated with implementing and testing the system.

In the medical device domain, risk management is a crucial activity in the development and certification. The international standard ISO 14971 describes the risk management process for medical devices. The 14971 process includes identifying hazards (things associated with the device and its use that might cause harm), performing risk analysis (including hazard analysis) to identify hazardous situations (causal chains leading from root causes to device-user / device-patient interactions that might cause harm), developing risk controls (mitigations of hazard situations), verifying risk controls, and determining if residual risks are acceptable.

A vital element of the interoperability vision is that reuse is not just limited to subsystem implementations — the component's risk management and assurance results should also be reusable when sub-systems are integrated into a new system context. The interoperability goal also introduces network capability to devices that are traditionally independent and monolithic. In interconnected systems, safety concerns resulting from security issues can often be overlooked as traditional risk management processes were developed when safety critical systems were not networked and thus not as susceptible to security problems. However, more recent standards and guidance documents such as AAMI TIR57 suggest an interleaved safety and security risk management process<sup>2</sup> for monolithic medical systems.

In modern military systems, manufacturers need to consider security aspects from the early design of the system. The MILS approach to designing secure systems decomposes the system to identify security critical parts and develop them as formally verified trusted components/processes in a separation kernel. A verified security kernel offers isolation of resources, faults and provides communication with other components through specialized trusted components. In distributed systems, the trusted components are physically isolated in single-user machines and share resources through trusted mediation components. MBSE provides a robust structure to model and analyzes security aspects much earlier in the system development.

Although distributed development copes up with the growing scale of the system. In practice, it poses the following challenges:

- In a distributed development context, safety and security aspects of the system often span multiple organizations and many sub-systems. Thus, it is essential to have a common understanding of various dependencies in the system and the respective responsibilities of the involved vendors.

- In a multi-vendor development context, various notions of dependence analysis are key to gaining system understanding and supporting safety and security audits and assurance cases. In hazard analysis, understanding how faults propagate through the system due to dependencies helps develop better hazard mitigation strategies. Analyzing security aspects of the system requires comprehending the flow of information through data and control channels. Additionally, over the system's life cycle, upgrading and re-integrating components require an understanding of the impact of the changes.

- The risk management standards such as ISO 14971 are developed for medical systems developed by a single vendor. With the advent of distributed development, adapting

existing risk management standards to distributed context is complicated. The Medical device plug-and-play (MD PnP) and Integrated Clinical Environment (ICE) standard for developing interoperable systems provide a wealth of resources on compositional risk management, security concerns, and providing safety arguments derived from multiple stakeholders. However, applying them to a novel device is not a straightforward task.

We address these challenges by providing a general dependence analysis framework that can be used in a model-based development to support system understanding, security analyses, and analyses used in risk management activities. While the proposed approach is not restricted to a particular modeling language, we use the industry-standard AADL modeling language to illustrate and evaluate the proposed approach. The specific contributions of this dissertation are as follows:

- A general-purpose dependence analysis infrastructure, called Awas<sup>1</sup>, supports modelbased specification of dependencies, automatic derivation of dependencies from system architecture models, and analyses of these different types of dependence information.

- Tool for creating interactive visualizations of Awas dependence information and analysis results. The tools create projections of dependence information from models, enabling developers and auditors to better focus on dependence-related concerns without being overwhelmed by the scale of the model or the details in the model that are not relevant to the task at hand. The generated visualizations are independent of the platform and modeling tools, enabling both technical and non-technical staff to understand and communicate aspects of the model.

- A query language for interrogating information flows and causal relations in systems at varying stages of modeling. This query language and supporting analysis can help developers explore and understand causality relations and "what if" scenarios in Awassupport security and safety analysis activities and help design and verify security and risk controls.

<sup>&</sup>lt;sup>1</sup>Awas means "caution" in Indonesian

• A validation and assessment of Awas using one of the largest and most complex medical device examples considered in the academic/industry literature to date. This work includes an approach for (a) developing model annotation libraries that instantiate the AADL EMv2 framework to support ISO 14971 medical device risk management and (b) auto-generating risk management reports that relate sub-system failures to system-level hazards.

This work developed/applied in the following projects:

#### • Security & Safety Co-Analysis Tool Environment (SSCATE):

This project focused on incorporating hazard analysis into AADL system models. We developed the initial version of the Awas analysis and visualization tool to query and identify hazardous paths in a system model.

#### • Cyber Assured Systems Engineering (CASE):

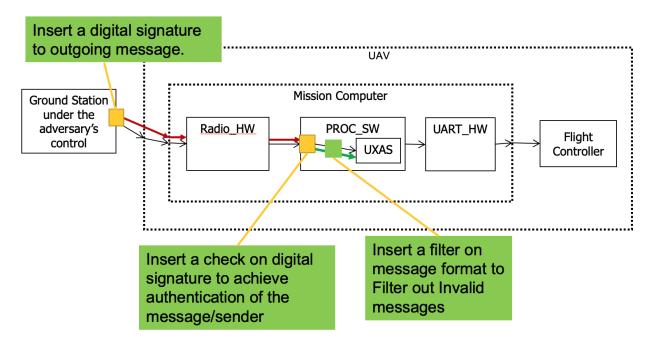

This program's objective was to develop the design, analysis, and verification tools for engineering cyber resilient embedded computing systems. We applied Awas to visualize and support assurance arguments concerning Unmanned Aerial Vehicle's (UAV) security properties.

- Microkernel Application Information fLow with Logic-based Enforcement: This project aims to provide an integrated model and code-level information flow analysis tools to increase aircraft survivability. We developed a secure modeling annex for AADL and extended Awas to infer security types and check the system's security information flow policies.

- Integrating Safety and Security Engineering for Mission-Critical Systems: With the maturity of Awas tools, Software Engineering Institute (SEI) applied Awas in their safety and security hazard analysis and report generation platform for modern mission critical embedded systems.

The primary contribution of this work is the open-source implementation of the dependency analysis framework for AADL available under an open license<sup>3</sup>. Additionally, we provide models, tutorial materials, and user documents for all the tools.

The rest of this dissertation is organized as follows:

Chapter 2 provides the context of system engineering and some of the aspects of developing safety critical system using MBSE. The following section describes popular modeling languages, risk management standards for medical devices, and existing hazard analysis techniques.

Chapter 3 describes the AADL modeling language and its information flow aspects with the help of a security critical system. *AAMI/ANSI/IEC TIR80001* risk management standard, an extension of *ISO 14971* to support networked systems and demonstrate the process using interoperable medical devices. Subsequently, demonstrated iterative development of a safety critical system.

Chapter 4 reviews the formal theories behind the analysis and modeling of the systems and describing some of the existing tools designed to perform model-level safety and security analysis.

Chapter 5 presents Awas - a tool for transforming of AADL EMv2 models into dependency graphs and performing reachability analysis on varying levels of model details. The content of this chapter have been published in the journal – *Innovations in System and Software Engineering*<sup>4</sup>.

Chapter 6 describes the Awas tool architecture, visualization of AADL models and dynamic interaction, and querying capability. The content of this chapter have been presented in the conference – moDeling, vErification and Testing of dEpendable CriTical systems<sup>5</sup>.

Chapter 7 demonstrates applications of the information flow analysis specifically, automating parts of *ISO 14971* medical device risk management process presented in the conference – *International Symposium on Model-Based Safety and Assessment*<sup>6</sup>. The second application is developing an AADL annex and analysis for modeling and analyzing MILS-based security critical systems.

Chapter 8 provides a performance evaluation of Awas using a collection of publicly available AADL models and, based on the feedback from the industrial partners, various integration of Awas with OSATE - an Eclipse-based AADL development environment. Chapter 9 conclude by summarizing the work and providing direction to extend this work to develop distributed critical systems.

# Chapter 2

# Literature Review

To provide a concrete illustration of risk management standards for critical systems, this chapter summarizes some key medical device risk management standards, specifically ISO14971, and focus on risk analysis. Since hazard analysis is a key component of risk analysis, a survey of hazard analysis techniques is provided that includes Fault Tree Analysis (FTA), Failure Mode Effect Analysis (FMEA), and System Theoretic Process Analysis (STPA). Finally, challenges are identified related to critical system communication and security as well as the overall development process.

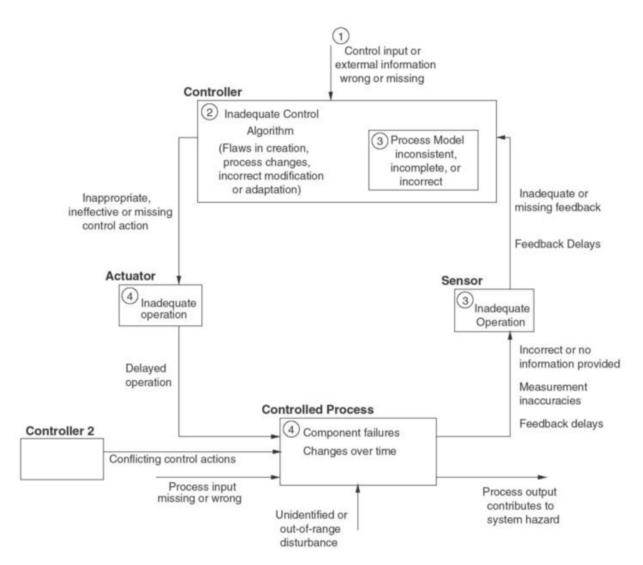

### 2.1 System

With the miniaturization of the computer processor, computing became *anytime* and *any-where*. This was predicted by Mark Weiser who coined the term "ubiquitous computing"<sup>7</sup>. Embedded systems are an important class of computers that control the physical environment in a feedback loop. A device senses a certain aspect of its environment, a controller performs a series of calculations to determine if the environment should be acted on. Based on the result the controller sends commands to actuators to modify the environment<sup>8</sup>.

Embedded systems such as modern cars, smart toasters, washers, even mobile devices share common characteristics, for example, real-time constraints, safe operation, reliability,

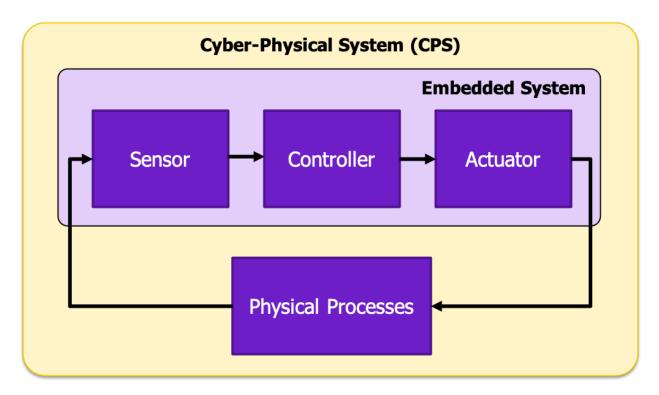

Figure 2.1: Cyber-Physical System - Control Structure

and efficiency requirements. Along with these common properties, they also share a strong link to their physical environment. This common attribute of manipulating the environment led to the introduction of the term "cyber-physical systems" (CPS), defined as the integration of computation and physical processes<sup>9</sup>. In such systems, the physical processes affect computations and vice versa. Figure 2.1 captures the relation between the computer controller and the physical process in a feedback loop.

In practice, a system consists of multiple sensors, controllers, and actuators. Furthermore, each can be atomic (not further decomposed) or a system (with subordinate system elements) working together to achieve a common purpose. The term *controlled process* is used to address both physical processes or a sub-system that the controller controls. In this way, a hierarchy among the system elements is established along with the system boundary at each level. If each system element can also be deployed as an independent system, then such a composition of system elements is termed as a 'system of systems'.

"Internet of Things (IoT)" refers to the pervasive presence of system elements (*things*) such as sensors and actuators, and are connected to the controller through the internet with

unique addressing schemes<sup>10</sup>. Most often, IoT systems employ heterogeneous sensors/actuators and varying connectivity. A key characteristic is interoperability, enabling heterogeneous devices to communicate and collaborate to achieve the system's intended purpose.

In recent times, automobiles, aircraft, nuclear power plants, medical devices, financial systems, manufacturing and industrial automation systems, and home automation rely on software to provide improved and sophisticated services. Complex software components in critical systems pose unique challenges in system engineering, risk management, hazard analysis, and certification of embedded systems.

### 2.2 System Engineering

System engineering is an iterative process of design, develop and operation of a system that satisfies the requirements in an efficient manner<sup>11</sup>. Irrespective of the system domain and its use-case, engineering an embedded system is challenging due to the myriad design choices, specialized development process, and higher degree of assurance requirements to ensure the system's dependability.

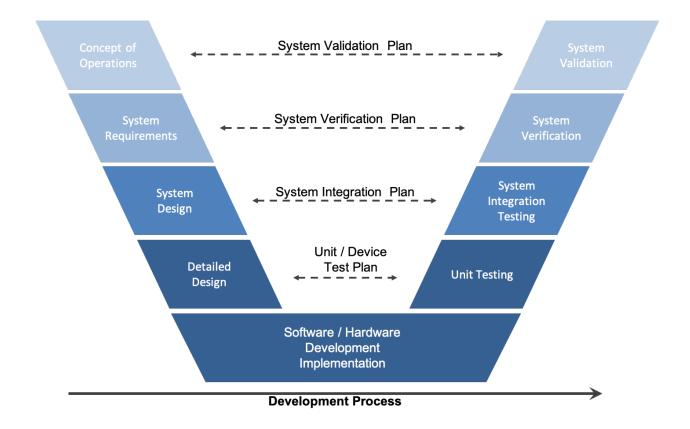

Traditionally, system engineers followed the software development life cycle (SDLC) model such as the waterfall model. However, over the years, the V-model<sup>12</sup> of system development became the de facto process for developing embedded systems and systems of systems. Figure 2.2 shows the various stages of the engineering process, where the left-wing is the project definition, the bottom of the "V" consists of implementation, and the right-wing is the verification process.

As shown in Figure 2.2, this approach defies the project requirements before technology choices and implementation. In the left-wing, the understanding of the system progresses from the high-level concept of operation to a well-defined set of system requirements. In the subsequent stages, a system design is developed to meet the requirements and further decomposed into sub-systems and sub-systems into components. A large system is decomposed into several layers until the system's design consists only of atomic components or third-party components (Commercially of the shelf (COTS) components).

Figure 2.2: V-Model System Development Process

At the end of each stage, the outcome of the stage is discussed with the customer, and an agreement is reached before proceeding to the next stage. The documents generated at the end of each stage guide the development of the following stage. The bottom of the "V" consists of the implementation of hardware and software components. In the right-wing, the system components are then integrated as per the system design and verified against the system requirements. Finally, the validation process ensures that the system satisfies the user's needs and system goals.

The linear waterfall model is bent to form the "V-model" to establish the correlation between the system definition (left-wing) and the assurance (right-wing) stages. The final system is validated against the concept of operation developed as the first stage. Similarly, the system is verified against requirements. The arrows connecting the left and right-wings of the "V" shows the relationship between the stages and ensures that the focus of the development is always within the goals of the system.

### 2.2.1 Challenges

Over the years engineering embedded system evolved and engineers learned from experience. However, the demand for novel and complex systems is ever growing. Here are some of the challenges faced by engineers in developing embedded systems.

#### Safety

One definition of safety used by many experts is "freedom from harm"<sup>13;14</sup>. At the boundary of the embedded system, it interacts with its environment. If there is a system failure, the system often performs an adverse action on its environment, including humans, expensive equipment, nature, or intellectual property. Due to the magnitude of the loss stemming from an accident, system safety is factored in from the first principles of system engineering. However, it is not possible to identify and eliminate all possible failure scenarios efficiently.

#### Security

Security is becoming an increasingly important topic in the field of system engineering. For successful operation, it is important to address security issues comprehensively. Networked systems and IoT devices should account for outside attacks and failures. Anytime a device is connected to the internet, the system engineer has to take into account unauthorized personal accessing sensitive information. A system engineer should consider the flow of information through various system parts, specifically between secure and public domains. Through out the life of a system, a system engineer should consider who gets to access the system based on the following properties.

- Confidentiality: Only authorized users can gain information

- Integrity: Authorized users access accurate and complete information

- Availability: Authorized personals can access information provided by the system

Safety of the critical system may be compromised when the system fails to provide its service to its authorized users. For example, a networked medical device fails to alert its authorized users when a patient's vitals are deteriorating due to Denial of Service(DOS) attack on its network. On the other hand, when an unauthenticated user with malicious intent gains access to the system, then they may add or block sensed information, block or modify commands to the actuator to cause damage to the users and environment or disable the system to deliver services.

#### Reliability

Reliability is the probability of lack of failure that deviates a system from its goals. The reliability of a system is only based on the durability of components and lack of internal failures during regular operation. Various factors affect the system's reliability, including its operating environment, component choices, redundancy, and design. Engineers make a careful trade-off between cost and reliability.

There is subtle difference between safety and reliability of the system. In reliability engineering, engineers tries to reduce the failure rate. On the other hand, safety engineers tries to avoid hazards. Failures and hazards themselves corresponds to the violation of functional requirements and safety requirements. For example, an aircraft that fails to airborne is safe yet it is unreliable. Similarly, in laser tonsillectomy, if the system is not designed to avoid oxygen tube, it can cause fire accident in patient's windpipe. Such a system is reliable to deliver its service but the service is not evaluated for safety.

#### Efficiency

Efficient use of resources is paramount in embedded systems. Often it dictates the design choices and the success of a product. The following are some of the areas where the efficiency is focused.

- Energy: With the widespread use of portable embedded devices, choosing energyefficient hardware and software components is crucial for performing its task.

- Cost: Consumer electronics are mass-produced, and the cost-effective device always edges out in the competitive market.

• Weight: Low weight is essential for portable devices and devices used in avionics and space exploration, and striking a balance among the three is a challenge in developing an embedded system.

#### Heterogeneity

Sifakis *et al.* describes heterogeneity as the property of the embedded system to be built from components with different characteristics<sup>15</sup>. Two challenges come with heterogeneity: a) Modeling systems with a composition of heterogeneous components without the loss of interoperability, and: b) Designing and integrating heterogeneous components that are compatible and safe.

#### Technical

With the rapid improvement in technology, keeping pace in other areas such as adaption rate, standardization, development throughput, and testing needs is difficult. Embedded system hardware consists of limited resource availability and developing software that avoids inefficient hardware resource use is challenging.

### 2.3 Model Based System Engineering (MBSE)

MBSE is a methodology for developing complex and large systems that emphasizes system model as central engineering artifact. In MBSE, a system model acts as the center point where the other phases of system development, such as requirements engineering, the concept of operation, design, analysis, verification, and validation, are captured in it. MBSE reduces cost by early detection of design issues and maintaining a consistent structure.

#### 2.3.1 Document-Centric System Engineering

Prior to MBSE, engineers emphasized text-based documents to capture key aspects of system development. Each stage in the "V-model" and the tractability between stages are docu-

mented. Different teams/stakeholders developing components use documents to capture the interface specifications called Interface Control Documents (ICDs). In a large system with hundreds of components, engineers spend considerable amount of time in developing and maintaining ICDs for each component. However, there is some clear advantage to this engineering approach.

- Both technical and non-technical personal can author and consume these documents

- Sharing documents between teams and stakeholders do not require any additional steps

- Documents are written in natural language and provide greater flexibility to support any situations

### 2.3.2 Model-Centric System Engineering

In a model-centric approach, developing models is the focus of the engineering effort. A model is a simplified version of something–a graphical, mathematical, or physical representation that abstracts reality to eliminate some complexity<sup>16</sup>. Engineers Contribute to a common model or set of models to capture information about the system. These model artifacts are progressively refined and analyzed until the models represents a system.

Although the document-centric approach is simpler, there are some apparent downsides to it. The top on the list is the sheer number of ICDs generated and the lack of linkage between them. Additionally, artifacts in the documents, such as system architecture diagrams are static. If a component's interfaces are updated, engineers have to manually perform the change impact analysis *i.e.* finding the impact of the change throughout other documents and their changes. This process can quickly become very time-consuming with the growing system's size. Finally, manually checking for integration issues in a critical system can lead to inadequate detection and investigation of hazards.

The model-centric approach is a product of the digital world. A model captures several important system engineering functions. However, engineers document the summary report at the end of each stage and the communication artifacts outside the engineering team. The key advantage of the model-centric approach is the consistency of the model throughout the engineering process. A model captures dependencies across teams, and the effect of a change made in one part of the model is immediately reflected in the rest. Additionally, a system can be hierarchically refined and decomposed into sub-systems, and a model consistently translates the structure and behavior to the sub-system. Overall, in a model-centric approach, integration failures are detected and mitigated at the design stage in the "V-model" rather than at the integration testing phase, thus eliminating the cost of redevelopment and testing the failed component.

A system engineered using MBSE suffers from higher initial cost due to the cost associated with defining the process, developing infrastructure, training engineers, and modeling<sup>17</sup>. Systems with a longer operational lifespan benefit from adopting the MBSE approach. Industries such as transportation, aerospace, defense, medical device, energy, and industrial equipment see a higher return on investment using MBSE. On the other hand, finance, business services, retail, and high-tech sectors do not seem to benefit as much from MBSE.

### 2.4 Safety-Critical System

Embedded systems, by definition, interact with their environment, and if a failure could lead to an unacceptable consequence, then such a system is called safety critical system. John Knight defined safety critical systems as those systems whose failure could result in loss of life, significant property damage, or damage to the environment<sup>18</sup>. The distinguishing factor in safety-critical system engineering is the additional effort to ensure the system's safe operation. Risk management effort, strict adherence to safety standards, and certification are key aspects of the safety-critical systems development process.

### 2.4.1 Interoperable Medical Devices

Modern medical devices are typically specialized computers. For example, a pacemaker can be understood as a computer that controls the pacing pulse, timing, and intensity. Many surgeries such as hip replacement, spinal surgery, and ophthalmic surgery are assisted by computerized equipment. In recent times, with the increasing sophistication of medical devices, the manufacturers are incentivized to develop devices with interoperability and platform support.

Medical Application Platform (MAP) is an emerging research focus for developing the system of systems medical devices, and its associated standards and risk management <sup>19;20</sup>. A MAP is a safety and security critical real-time computing platform for (a) integrating heterogeneous devices, medical IT systems, and information displays via a communication infrastructure and (b) hosting application programs ("apps") that provide medical utility via the ability to both acquire information from and update/control inte- grated devices, IT systems, and displays<sup>21</sup>. Developing devices for a platform can lead to an ecosystem of manufacturers that collaborate to develop reusable components encouraging device manufacturers to develop interoperable ecosystem-based plug-and-play medical devices. Integrated Clinical Environment (ICE)<sup>22</sup> is a ASTM F2761-2009 standardized architecture realization of MAP. The CIMIT<sup>23</sup> Medical Device Plug-and-Play program (MD PnP)<sup>24</sup> at Massachusetts General Hospital is one research group that made a significant effort to use the ICE architecture to showcase the benefits of interoperable and interconnected medical devices.

#### 2.4.2 Stakeholders

Kim *et al.*<sup>25</sup> identified the following list of stakeholders in developing interoperable medical devices based in the context of ICE platform.

#### Consortium

The consortium is a central organizational authority that provides architecture standards, interface requirements, and compliance processes. Consortium also provides reference devices and modeling vocabulary that other device manufacturers can use to communicate with stakeholders. Finally, the consortium provides risk management guidelines and processes for component compliance evaluation<sup>24;25</sup>.

#### **Component Vendors**

Component vendors include device manufacturers, interoperable apps authors, and platform providers. Irrespective of their role, all component vendors must provide interface specifications of their component according to the guidelines provided by the consortium, submit their component for compliance testing, and submit for regulatory review.

#### Third-Party Certification Authority

Certification authorities ensure that the component complies with the consortium's architecture standards. Certification authorities perform interface testing, ICE complainant testing, and issue certificates to components based on the results. A system integrator can compose certified components with confidence.

#### **Regulatory Authority**

Authorities ensure safe and effective use of the interoperable components. The safety of each component is evaluated in a broad set of contexts instead of a system instance. Regulatory authorities make sure that the certification authorities are competent and produce enough evidence to substantiate their certificate.

#### Health-care Delivery Organizations (HDO)

HDO comprises hospitals and other health care providers. HDOs procure and deploy ICE systems to improve the quality and effectiveness of the health care provided to the patients. HDOs compose the system based on the clinical needs from the collection of compatible components.

#### 2.4.3 Medical Device: PCA Pump

A PCA infusion pump is a medical device intended to administer intravenous (IV) infusion of pain medication to the patient in various clinical settings. During clinical use, a caregiver (typically nurse) first prepares the PCA pump by loading a vial of medication, priming the pump's infusion set (tubing and needle), and connecting the pump to the patient via the infusion set. The caregiver then configures infusion parameters (e.g., infusion volume, rate, and duration) on the pump's operator interface and initiates the infusion.

Pain medication (opioid) is prescribed by a licensed physician and dispensed by the hospital pharmacy. A clinician loads the vial into the pump, and attaches the pump's drug dispensing tube to the patient's IV line.

A PCA pump can deliver medication in either a basal or bolus mode, where the former continuously delivers medication at a low rate, and the latter delivers a bulk of medication in a short period of time. The patient can request additional boluses for further pain relief by pressing a hand-held button provided by the pump. Too many bolus request can pose severe overdosing risks to the patient.

Figure 2.3: Example PCA Pump

While PCA pumps (and infusion pumps in general) have allowed for a greater level of control and accuracy in drug delivery, they have been associated with persistent safety problems<sup>26</sup>. Through a study of adverse events and device recalls related to infusion pumps, the US Food and Drug Administration (FDA) concluded that many of these problems appear

to be related to deficiencies in device design and engineering<sup>27</sup>. The increased safety concern led FDA to develop *infusion pump improvement initiative* to enhance infusion pump safety<sup>27</sup>, including additional scrutiny of risk controls and supplementary documents such as assurance cases over infusion pumps coming to the market<sup>28</sup>.

# 2.4.4 PCA Pump Interlock Scenario

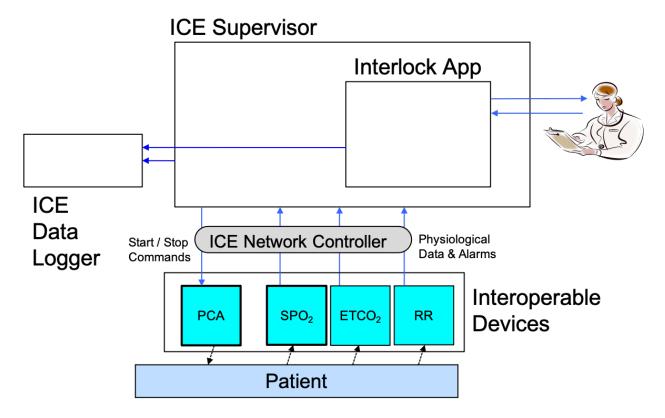

Figure 2.4: ICE Instantiation of PCA Safety Interlock

The most common adverse event in a PCA Pump therapy is drug overdose<sup>29</sup>. Over infusion of opioids may lead to respiratory depression and eventually respiratory distress, which may cause death. May different scenarios can cause over-infusions such as visitors pressing the bolus(PCA-by-proxy), incorrect drug, incorrect dosage, drug interaction, and device malfunction. Patients receiving pain medication are usually also connected to patient monitoring devices. In case of respiratory depression, these monitoring devices sound an alarm and summons a caregiver. However, diagnosis and adequate action may time a while steamin which damage may have already been done.

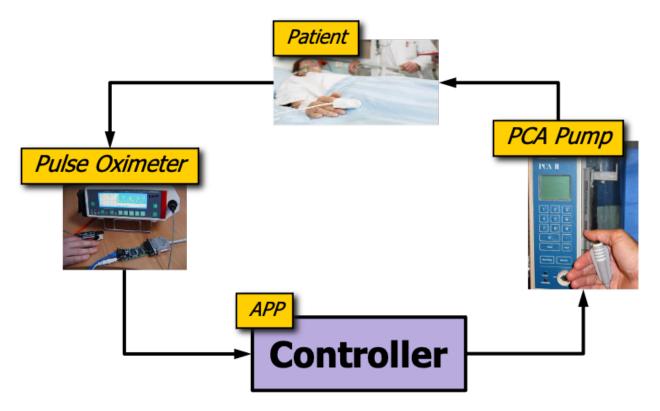

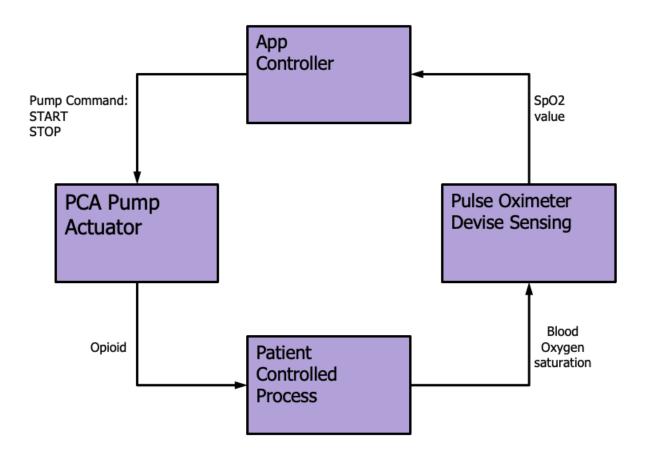

Figure 2.5: Simple PCA Interlock with PulseOx

Researchers proposed the PCA pump interlock scenario to improve the safety of the PCA pumps<sup>21;30;31</sup>. Figure 2.4 illustrates an ICE-based MAP implementation of PCA interlock scenario with interoperable patient monitoring devices, interlock app, PCA pump, and the network controller. In this scenario, different manufacturers develop the components of the PCA interlock system, and the system integrator composes the components as per the model architecture.

Figure 2.5 illustrates a simplified version of the PCA interlock scenario, where a pulse oximeter connected to a patient monitors the patient's current health status. Based on the patient's health condition, an interlock app as described Hatcliff *et al.*<sup>21</sup> halts the infusion when halting conditions (*e.g.* when the patient's respiratory health is deteriorating) are satisfied. Subsequently, if the App determines the patient's vitals to be healthy, it may allow the pump to resume respecting the bolus commands. The interlock App accomplishes this by issuing *START* and *STOP* commands to the PCA Pump. For example, if the last

received command is *STOP*, the bolus activation command is ignored. Similarly, when the PCA Pump receives *START* command, the bolus requests are respected.

#### 2.4.5 Challenges

MAPs are distinct from existing medical systems and safety critical systems due to their unique way of interacting with humans and the environment, assurance requirements, and the involvement of varying stakeholders presents several challenges.

- Communication process and responsibilities among stakeholders: With multiple organizations involved, there is a need for a contract to establish communication and trust among the stakeholders. Additionally, a methodology for assigning responsibilities among the stakeholders.

- *Distribution of development process:* With multiple stakeholders, it is efficient for each organization to work in parallel. However, techniques to identify the dependencies and the temporal order of required artifacts are insufficient.

- *Reuse existing components:* It is inefficient for a device vendor or an app developer to rebuild a component for a different platform or a different system. Currently, there is a lack of appropriate guidelines for adapting and reusing existing components without compromising the system's safety.

- *Risk management for interoperable devices:* It is efficient to perform risk management for a broader class of devices from a system integrator point of view. Therefore, the App can be compatible with a wide range of devices. However, who defines the device class? How to reach consensus on the device requirements? Who evaluates for the conforment?

- Development and automation tools: To meet the market demands and to incorporate rapid development cycle with higher safety standards, a lot of the development process must be automated. Currently, there is a lack of a unified development environment where the system can be designed and analyzed for safety.

# 2.5 Modeling Languages and Tools

Engineers develop models to understand better and test a certain aspect of the system. They develop physical models, mock-ups, and abstract models. This work focus on abstract models developed using modeling tools typically running on a computer providing a modeling language to express modeling constructs. The tool checks the model and ensures the construction of a well-formed model. The following sections provide a brief overview of popular modeling languages in industry and academia.

# 2.5.1 OMG SysML (Object Management Group System Modeling Language)<sup>32</sup>

SysML is a graphical modeling language supporting system engineering phases such as specification, design, analysis, verification, and validation. SysML is a modified version of the Unified Modeling Language (UML) by removing some software-centric diagrams and adding diagrams related to the system engineering lifecycle. SysML consists of nine different diagrams to capture information regarding a system. Among them, the requirement diagram and the parametric diagram are not part of the UML profile. The activity diagram and the block definition diagram are modified from UML to support system engineering tasks. All the other diagrams are the same as the UML diagrams.

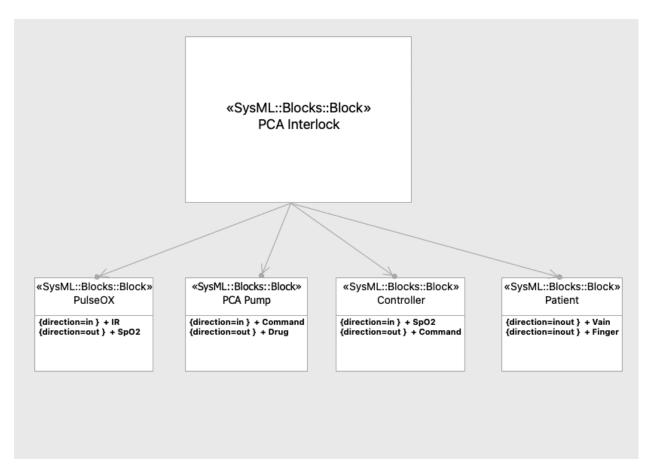

Figure 2.6 is the block definition diagram for the PCA interlock system. A block is a fundamental unit for describing the system structure. A block can be a hardware, software, person, or abstract entity. A block diagram defines the structural relation with other blocks.

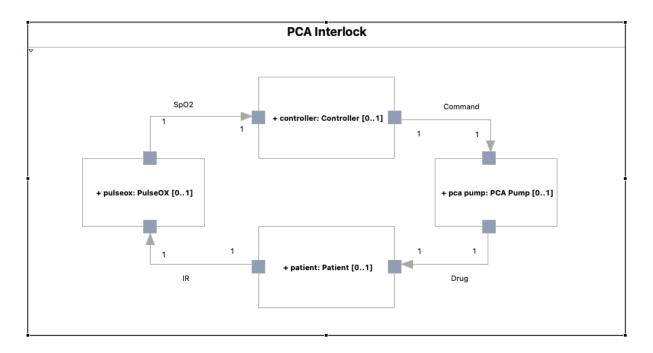

Figure 2.7 is the internal block diagram for the PCA interlock system. This diagram shows the connections between the ports of a block.

# 2.5.2 Simulink<sup>33</sup>

Simulink is a commercial toolbox for Matlab<sup>34</sup> from Mathworks. It is a high-fidelity graphical modeling language excelling at modeling, simulation, and analysis of dynamic systems.

Figure 2.6: SysML block definition diagram for PCA interlock system

Simulink provides a graphical user interface for building block diagrams, and it also provides a library of predefined blocks representing both hardware and software entities. With this collection of blocks, an engineer can build a rapid prototype of a system and analyze the merits of the model design.

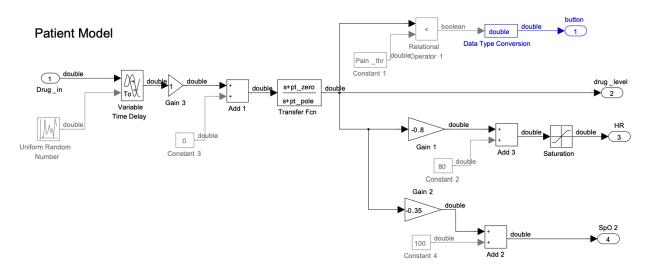

Figure 2.8 presents the patient's drug absorption function. Simulink is capable of providing a graphical view to a mathematical function with input and output ports. The patient can be wrapped by a subsystem and used in the PCA interlock system.

# 2.5.3 Architecture Analysis & Design Language (AADL)

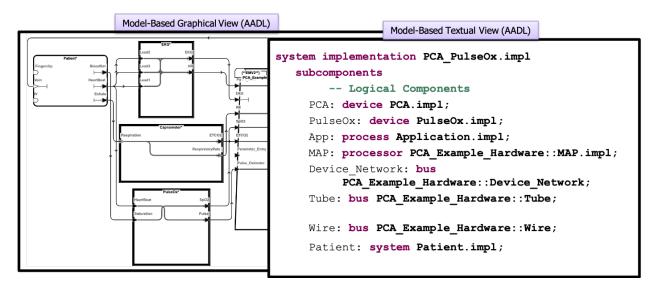

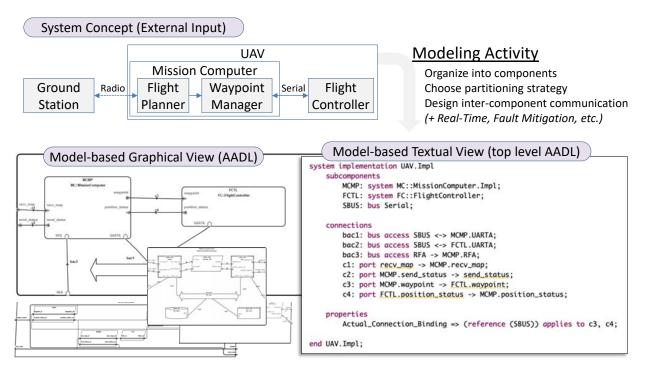

AADL is a SAE standardized architecture description language for modeling real-time embedded systems. AADL has both textual and graphical representations/views as illustrated in Figure 3.1. AADL modeling elements include software, middleware, and hardware compo-

Figure 2.7: SysML internal block diagram for PCA interlock system

nents along with various types of dependency relationships *between* them (inter-component dependencies) and *within* them (intra-component dependencies). Each modeling element can have a variety of *properties* for modeling attributes that specify important characteristics of the elements that may subsequently be leveraged for model analysis or code generation. AADL is an extensible language with an *annex* mechanism to support additional modeling and tool capabilities such as runtime behavior analysis, code generation, error modeling, and user-defined annex.

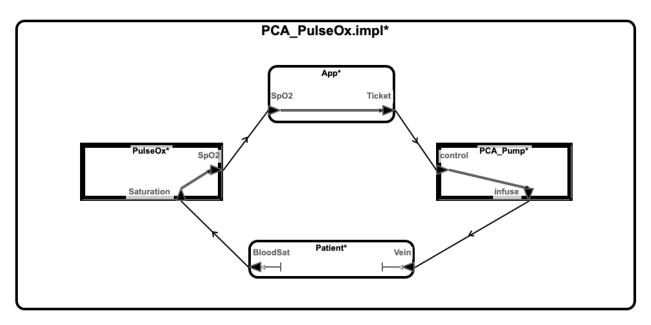

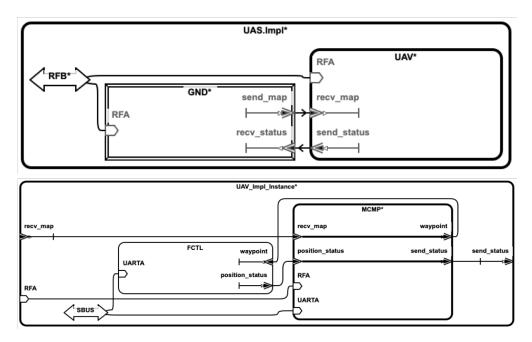

Figure 2.10 illustrates the instance model generated through the instantiation process. This model captures the simple PCA interlock scenario with components PulseOx, App,  $PCA\_Pump$  and Patient represented as a block. The edges between them represent the logical connection in the system. Each component block captures the component's ports and the flow of information within the component between the input and output ports.

Figure 2.8: Patient model in Simulink developed by Arney et al.<sup>30</sup>

Figure 2.9: AADL Graphical and Textual view

#### Inter-component dependencies

The most prominent inter-component relationships are *connections*, which capture data and control flows between software components such as threads and processes (e.g., the flow of SpO2 data between the PulseOx and App). Connections associate *ports* on sending and receiving components. AADL includes different port categories to specify communication patterns between components (e.g., asynchronous message passing, synchronous shared memory). Relationships between middleware components can be captured by specifying

Figure 2.10

connections via *bus accesses* (intuitively, bus access is a feature on a software component indicating that it utilizes a communication substrate). Finally, software elements such as threads/processes and connections can be allocated to middleware and hardware resources such as processors and buses using *bindings*. These dependencies can have multiple layers. For example, a process can first be bound to a *virtual processor* used to model a partition in a hypervisor, and then the hypervisor partitions can be bound to a *processor*. Similarly, a communication *connection* can be bound (transitively) through *virtual buses* representing layers of abstraction and associated protocols in a protocol stack.

#### Intra-component dependencies

AADL also provides multiple notions of intra-component dependencies. The most basic of these are *flow specifications*, which model data and control flow relationships between a component's input and output ports. AADL does not define precise semantics for flows nor explicitly distinguish between data and control flows. Different analysis tools may give flow annotations different interpretations. For example, a latency analysis tool may consider a flow to model a single or a collection of execution paths through the component source code, with an associated worst-case execution time for the path. A security analysis tool may interpret the flow as a specification of information flow (e.g., a combination of data and control flow).

# 2.6 Risk Management

In this section, I will discuss the overall risk management process as per the *ISO 14971*. However, *ISO 14971* does not address interoperability or platform based system. In the work presented in section 3.4 I will present the *ISO 14971* concepts in the context of MAP apps.

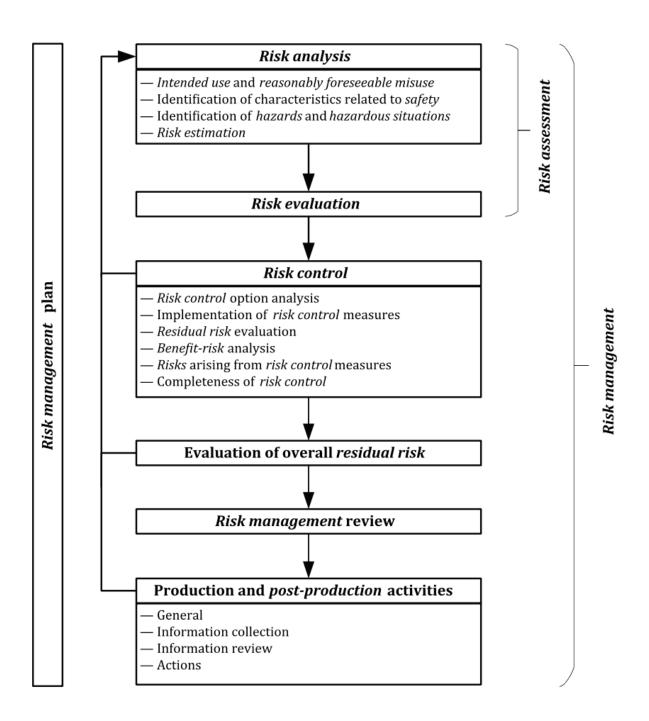

To following steps capture the progression of  $ISO \ 14971$  risk management process as show in figure 2.11.

#### **Risk Analysis**

- 1. Identify the intended use of a medical device and the possible incorrect or improper use. This is also a good place to identify the safety properties

- 2. Identify the hazards associated with the medical device in both normal and fault conditions when operated according to its intended use

- 3. Identify cause and resulting hazardous situation for each hazard identified in the previous step

- 4. Calculate the associated risk(s) for each of the identified hazardous situations. If the probability of occurrence of harm cannot be estimated with the available information, document the consequence and its severity

#### **Risk Evaluation**

1. For each of the identified hazardous situations, determine the foreseeable sequence of events from the root cause and compute the probability along the sequence of events that leads to the hazardous situation

Figure 2.11: ISO 14971 Risk Management Process

2. Check if the level of risk associated with the hazardous situation is acceptable. If it is not acceptable then risk controls must be introduced for the hazardous situation

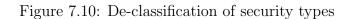

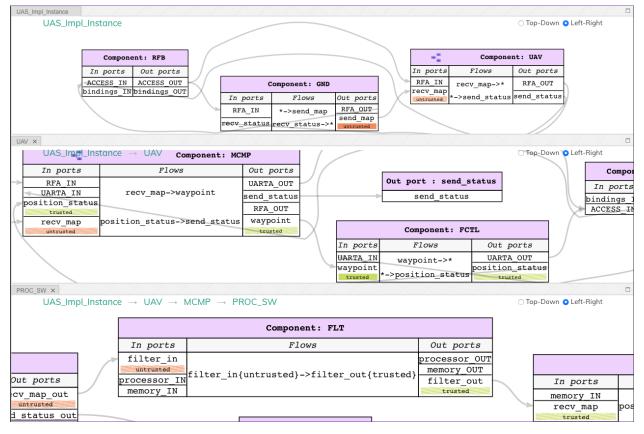

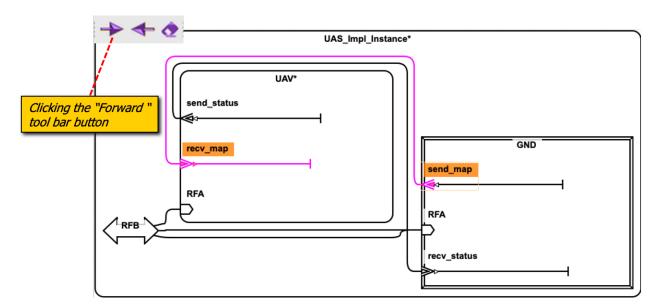

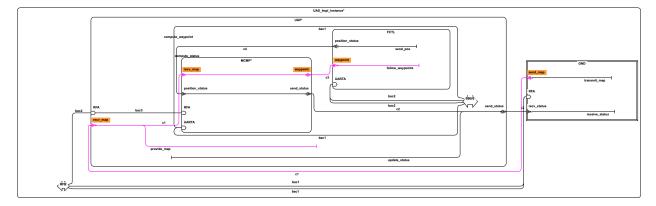

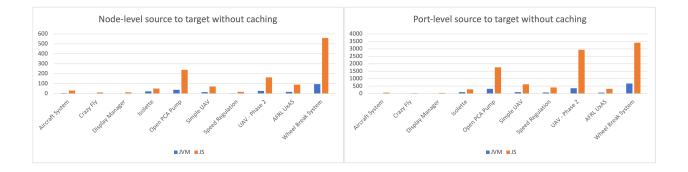

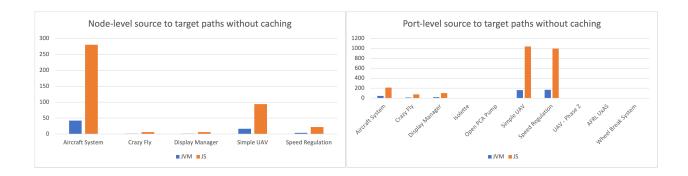

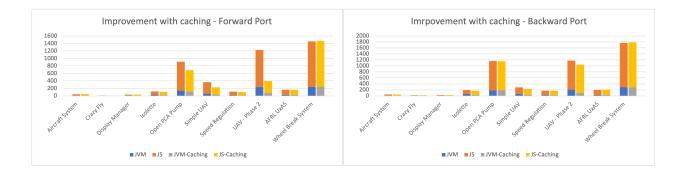

#### **Risk Control**