Purdue University

Purdue e-Pubs

**Open Access Dissertations**

Theses and Dissertations

5-2018

# Characterization of Manifold Microchannel Heat Sinks During Two-Phase Operation

Kevin P. Drummond Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_dissertations

#### **Recommended Citation**

Drummond, Kevin P., "Characterization of Manifold Microchannel Heat Sinks During Two-Phase Operation" (2018). *Open Access Dissertations*. 1865. https://docs.lib.purdue.edu/open\_access\_dissertations/1865

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# CHARACTERIZATION OF MANIFOLD MICROCHANNEL HEAT SINKS DURING TWO-PHASE OPERATION

by

Kevin P. Drummond

### **A Dissertation**

Submitted to the Faculty of Purdue University In Partial Fulfillment of the Requirements for the degree of

**Doctor of Philosophy**

School of Mechanical Engineering West Lafayette, Indiana May 2018

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF COMMITTEE APPROVAL

Dr. Suresh V. Garimella, Co-Chair School of Mechanical Engineering Dr. Justin A. Weibel, Co-Chair School of Mechanical Engineering Dr. Eckhard Groll School of Mechanical Engineering Dr. Dimitrios Peroulis School of Electrical and Computer Engineering

### Approved by:

Dr. Jay P. Gore Head of the Graduate Program For Kathy, Tom, Brian, and Lauren

### ACKNOWLEDGMENTS

First and foremost, I would like to thank both of my advisors, Dr. Suresh V. Garimella and Dr. Justin Weibel, for their support and direction throughout my Ph.D. Their guidance has been invaluable to my personal and professional development and I am grateful for the opportunity that they have afforded me.

I would also like to thank the members of my advisory committee, Dr. Eckhard Groll and Dr. Dimitrios Peroulis, for the guidance that they have provided during my research. Their comments and suggestions have helped shape this work into what it is today.

Thank you to Dr. David Janes, Mr. Doosan Back, Mr. Michael D. Sinanis, and the rest of the DARPA MicroICE team, without which this research would not have been possible. Each team members' knowledge, expertise, and hard work were critical to the success of the project.

I am deeply indebted to many of my lab mates who helped me get acclimated at Purdue and in the lab and provided feedback on my research. Dr. Matt Rau, Dr. Ravi Patel, Dr. S. Niki Ritchey, and Mr. Todd Kingston deserve special recognition for the positive effect they have had on my work.

Finally, thank you to my family. Thank you for always encouraging me to pursue my dreams and providing me with the tools necessary to succeed from a young age. Thank you for guiding and supporting me throughout my life, which has helped shape me into the person I am today and for that I am truly grateful.

# TABLE OF CONTENTS

| LIST  | OF TABLES                                              | ix    |

|-------|--------------------------------------------------------|-------|

| LIST  | OF FIGURES                                             | X     |

| NOM   | ENCLATURE                                              | cviii |

| ABST  | RACT                                                   | XX    |

| 1. IN | NTRODUCTION                                            | 1     |

| 1.1   | Background                                             | 1     |

| 1.2   | Objectives and Major Contributions                     | 2     |

| 1.3   | Organization of the Document                           | 3     |

| 2. L  | ITERATURE REVIEW                                       | 5     |

| 2.1   | Single-Phase Microchannel Heat Sinks                   | 5     |

| 2.2   | Two-Phase Microchannel Heat Sinks                      | 5     |

| 2.3   | High-Heat Flux Cooling Technologies                    | 6     |

| 2.4   | Single-Phase Manifold Microchannel Heat Sinks          | 7     |

| 2.5   | Two-Phase Manifold Microchannel Heat Sinks             | 8     |

| 2.6   | Hotspot and Non-Uniform Heat Flux Dissipation          | 9     |

| 2.7   | Flow Visualization                                     | 10    |

| 3. A  | HIERARCHICAL MANIFOLD MICROCHANNEL HEAT SINK ARRAY FOR |       |

| Н     | IIGH-HEAT-FLUX TWO-PHASE COOLING OF ELECTRONICS        | 12    |

| 3.1   | Test Vehicle Design and Fabrication                    | 13    |

| 3.    | 1.1 Hierarchical Manifold Microchannel Concept         | 13    |

| 3.    | 1.2 Test Vehicle Design                                | 13    |

| 3.    | 1.3 Test Vehicle Fabrication                           | 14    |

|       | 3.1.3.1 Microchannel Plate Fabrication                 | 14    |

|       | 3.1.3.2 Plenum Plate Fabrication                       | 15    |

| ,     | 3.1.3.3 Microchannel-Plenum Plates Bonding             | 16    |

|       | 3.1.3.4 Test Chip Assembly                             | 16    |

|       | 3.1.3.5 Manifold Fabrication                           | 16    |

|       | 3.1.3.6 Test Vehicle Assembly                          | 17    |

| 3.2   | Experimental Methods                                   | 17    |

| 3.2.1 Test Chip Calibration                                     | 17   |

|-----------------------------------------------------------------|------|

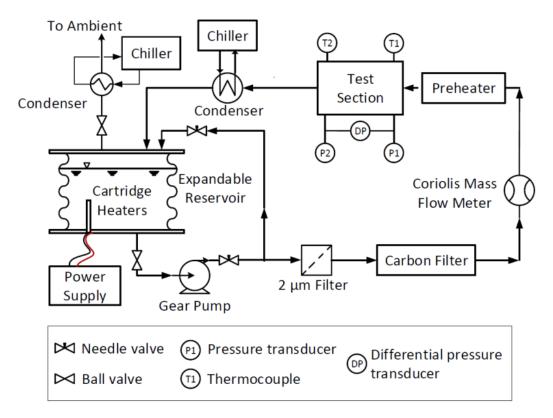

| 3.2.2 Flow Loop                                                 | 18   |

| 3.2.3 Test Procedure                                            | 18   |

| 3.2.4 Data Reduction                                            | 19   |

| 3.2.5 Uncertainty                                               | 21   |

| 3.3 Results and Discussion                                      | 21   |

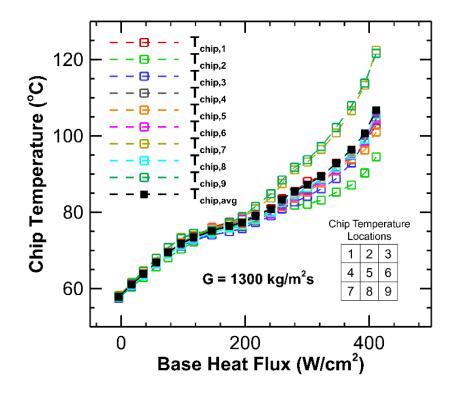

| 3.3.1 Temperature Distribution Across the Test Chip             | 21   |

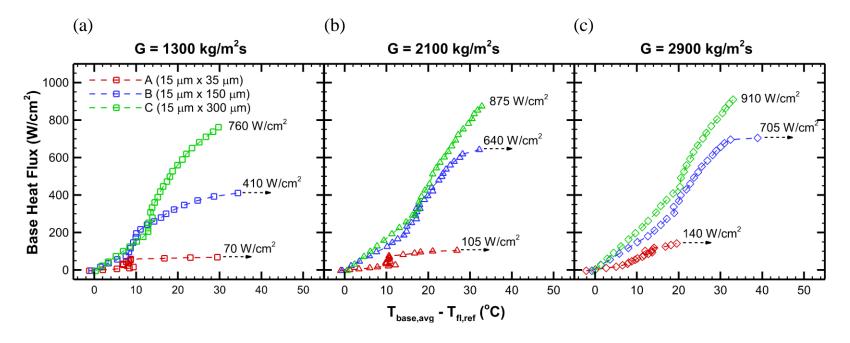

| 3.3.2 Boiling Curves                                            | 22   |

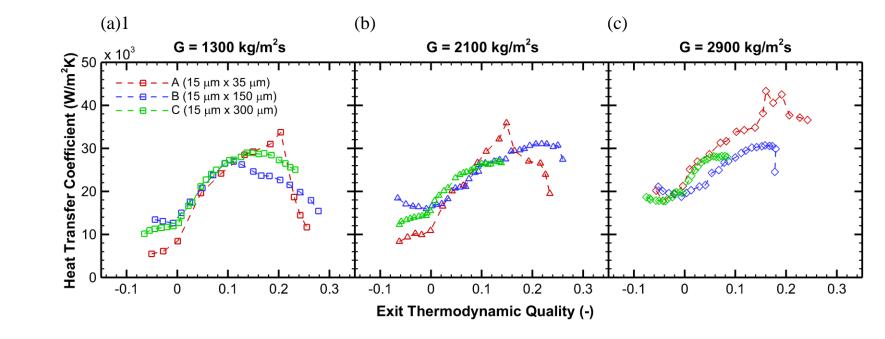

| 3.3.3 Heat Transfer Coefficient                                 | 24   |

| 3.3.4 Effective Thermal Resistance                              | 25   |

| 3.3.5 Pressure Drop                                             | 26   |

| 3.3.6 Conclusions                                               | 27   |

| 4. CHARACTERIZATION OF HIERARCHICAL MANIFOLD MICROCHA           | NNEL |

| HEAT SINK ARRAYS UNDER SIMULTANEOUS BACKGROUND                  | AND  |

| HOTSPOT HEATING CONDITIONS                                      | 43   |

| 4.1 Experimental Setup                                          | 43   |

| 4.1.1 Test Chip Fabrication and Assembly                        | 44   |

| 4.1.2 Manifold Fabrication                                      | 46   |

| 4.1.3 Test Vehicle Assembly                                     | 46   |

| 4.2 Experimental Methods                                        | 47   |

| 4.2.1 Test Procedure                                            | 47   |

| 4.2.2 Data Reduction                                            | 47   |

| 4.2.3 Uncertainty                                               | 50   |

| 4.3 Results and Discussion                                      | 50   |

| 4.3.1 Uniform Background Heat Flux                              | 50   |

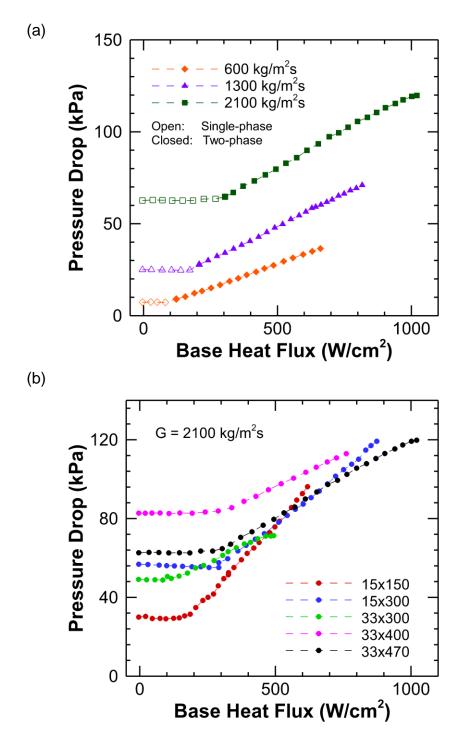

| 4.3.1.1 Effect of Channel Mass Flux                             | 50   |

| 4.3.1.2 Effect of Channel Geometry                              | 52   |

| 4.3.1.3 Pressure Drop                                           | 54   |

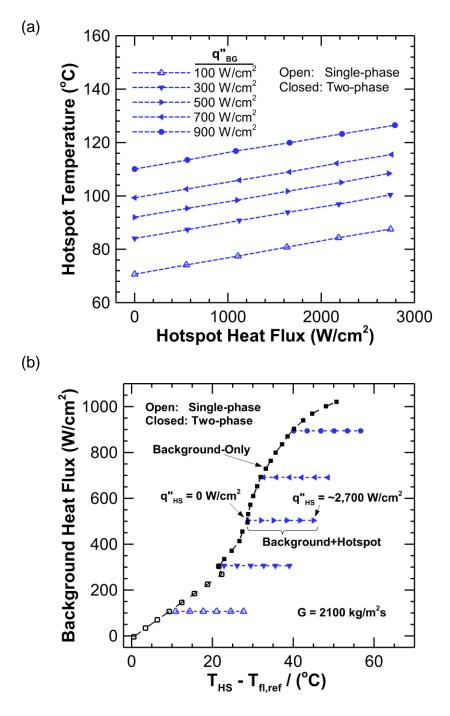

| 4.3.2 Simultaneous Background and Hotspot Heat Flux Dissipation | 55   |

| 4.4 Conclusions                                                 | 57   |

| 5. | DESIC  | GN, FABRICATION, AND CHARACTERIZATION OF A COMPACT,      |      |

|----|--------|----------------------------------------------------------|------|

|    | MUL    | ΓΙ-LEVEL HIERARCHICAL MANIFOLD MICROCHANNEL HEAT SINK    | 72   |

| 5. | 1 Exp  | perimental Setup                                         | 72   |

|    | 5.1.1  | Hierarchical Manifold and Microchannels                  | 72   |

|    | 5.1.2  | Heater/Sensor Layout                                     | 73   |

| 5. | 2 Fab  | prication of Microchannel Plate and Manifolds Plate      | 74   |

| 5. | 3 Inte | egration                                                 | 76   |

| 5. | 4 Exp  | perimental Methods                                       | 77   |

|    | 5.4.1  | Measurement Details                                      | 77   |

|    | 5.4.2  | Testing Procedure                                        | 78   |

|    | 5.4.3  | Data Reduction                                           | 78   |

| 5. | 5 Res  | sults                                                    | 78   |

|    | 5.5.1  | Boiling Curves                                           | 79   |

|    | 5.5.2  | Pressure Drop                                            | 79   |

|    | 5.5.3  | Comparison to $3 \times 3$ Array                         | 80   |

| 5. | 6 Co   | nclusions                                                | 80   |

| 6. | THE    | EFFECTS OF TWO-PHASE FLOW MORPHOLOGY ON LOCAL WALL       |      |

|    | TEMF   | PERATURES IN HIGH-ASPECT-RATIO MANIFOLD MICROCHANNELS    | 93   |

| 6. | 1 Exp  | perimental Test Apparatus                                | 93   |

|    | 6.1.1  | Test Device Design                                       | 93   |

|    | 6.1.2  | Test Device Fabrication                                  | 94   |

|    | 6.1.3  | Assembly of the Test Apparatus                           | 95   |

| 6. | 2 Exp  | perimental Testing Procedure                             | 96   |

|    | 6.2.1  | Experimental Test Facility                               | 96   |

|    | 6.2.2  | Infrared Camera Calibration                              | 97   |

|    | 6.2.3  | Data Reduction                                           | 97   |

|    | 6.2.4  | Uncertainty                                              | 98   |

|    | 6.2.5  | Testing Conditions                                       | 98   |

| 6. | 3 Res  | sults and Discussion                                     | 99   |

|    | 6.3.1  | Steady-State, Time-Averaged Experimental Results         | 99   |

|    | 6.3.2  | Flow Morphology and Spatially Resolved Wall Temperatures | .100 |

| 6.3.2.1 Low-Aspect-Ratio Microchannel (Sample 1)    |                 |

|-----------------------------------------------------|-----------------|

| 6.3.2.2 Medium-Aspect-Ratio Microchannel (Sample 2) |                 |

| 6.3.2.3 High-aspect-Ratio Microchannel (Sample 3)   |                 |

| 6.3.3 Discussion                                    |                 |

| 6.4 Conclusions                                     |                 |

| 7. CONCLUSIONS AND FUTURE WORK                      |                 |

| 7.1 Conclusions                                     |                 |

| 7.2 Suggested Future Work                           |                 |

| REFERENCES                                          |                 |

| APPENDIX A. LIST OF EXPERIMENTAL EQUIPMENT          |                 |

| APPENDIX B. TECHNICAL DRAWINGS OF FABRICATED        | COMPONENTS129   |

| APPENDIX C. MATLAB SCRIPTS FOR DATA REDUCTION       |                 |

| C.1 Script_Reduction_H1.m                           |                 |

| C.2 Function_Reduction_H1.m                         |                 |

| C.3 Function_Error_H1.m                             |                 |

| APPENDIX D. SIMULTANEOUS HOTSPOT AND BACKG          | ROUND HEAT FLUX |

| DISSIPATION RESULTS                                 |                 |

| APPENDIX E. EXPERIMENTAL UNCERTAINTY ANALYSI        | S166            |

| APPENDIX F. SINGLE-PHASE MODELING                   |                 |

| VITA                                                |                 |

| PUBLICATIONS                                        |                 |

# LIST OF TABLES

| Table 3.1. | Summary of microchannel test sample dimensions.                            | 29  |

|------------|----------------------------------------------------------------------------|-----|

| Table 3.2. | Experimental operating conditions                                          | 29  |

| Table 3.3. | Uncertainty in measured and calculated values                              | 29  |

| Table 3.4. | Summary of thermal performance metrics for the three channel geometries at |     |

|            | each mass flux tested (*experiment stopped due to high steady-state        |     |

|            | temperature rather than CHF)                                               | 30  |

| Table 4.1. | Summary of microchannel dimensions.                                        | 59  |

| Table 4.2. | Summary of experimental operating conditions                               | 59  |

| Table 5.1. | Summary of manifold and microchannel dimensions.                           | 82  |

| Table 5.2. | Electrical parameters of platinum heaters.                                 | 82  |

| Table 5.3. | Key parameters for deep reactive ion etching (DRIE) of high aspect ratio   |     |

|            | microchannels                                                              | 82  |

| Table 6.1. | Uncertainty in measured and calculated data                                | 104 |

| Table 6.2. | Summary of microchannel dimensions and operating conditions. The           |     |

|            | embedded figures show a view of the channel from the front and a cross     |     |

|            | sectional view when cut through the inlet plenum.                          | 104 |

| Table A.1. | Equipment used in the two-phase manifold microchannel heat sink facility   | 125 |

| Table B.1. | Custom-fabricated equipment used in the $3 \times 3$ two-phase manifold    |     |

|            | microchannel heat sink test vehicle.                                       | 130 |

| Table C.1. | A list of codes for post-processing data.                                  | 154 |

# LIST OF FIGURES

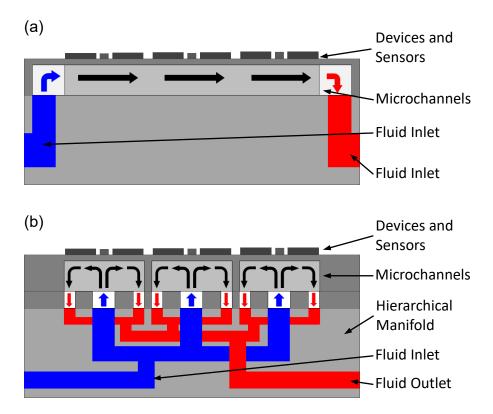

| Figure 1.1. | Cross-sectional schematic diagrams of direct cooling using (a) a traditional                   |

|-------------|------------------------------------------------------------------------------------------------|

|             | microchannel heat sink and (b) a intrachip hierarchical manifold microchannel                  |

|             | heat sink design                                                                               |

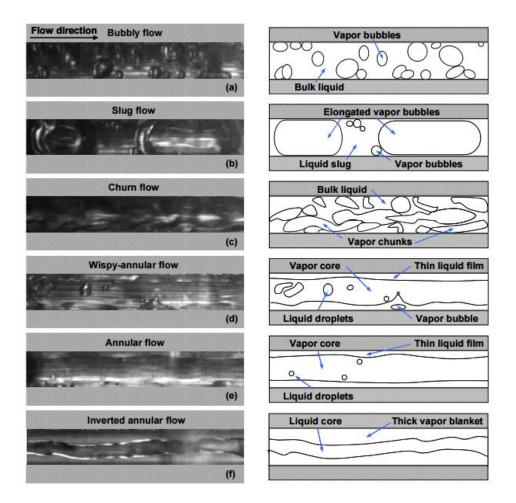

| Figure 2.1. | Description of boiling flow regimes [3]11                                                      |

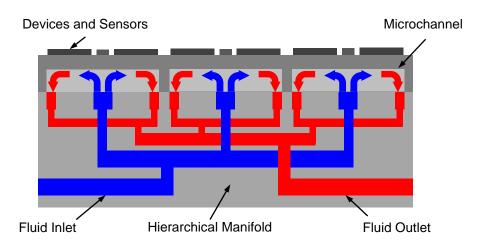

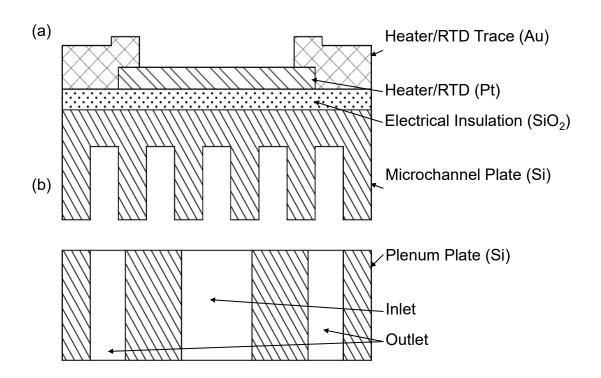

| Figure 3.1. | Cross-sectional schematic diagram of the hierarchical manifold microchannel                    |

|             | heat sink array design concept                                                                 |

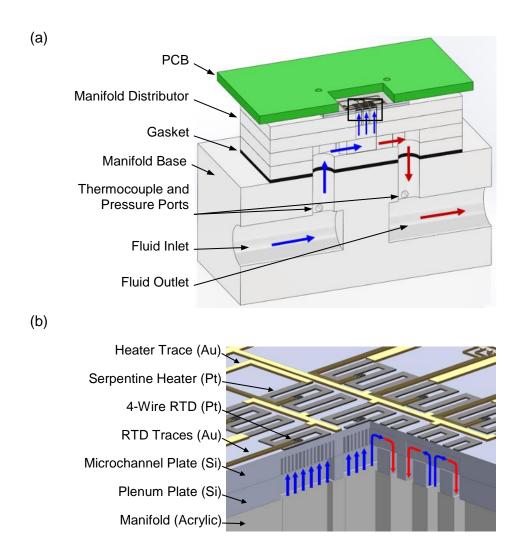

| Figure 3.2. | (a) Drawing of the thermal test vehicle with half-symmetry section removed to                  |

|             | show the fluid flow paths; (b) the inset shows a zoomed in view of the test chip               |

|             | and the fluid flow paths through the microchannels (quarter-symmetry section                   |

|             | removed; channels and heater/sensor thicknesses are not to scale)                              |

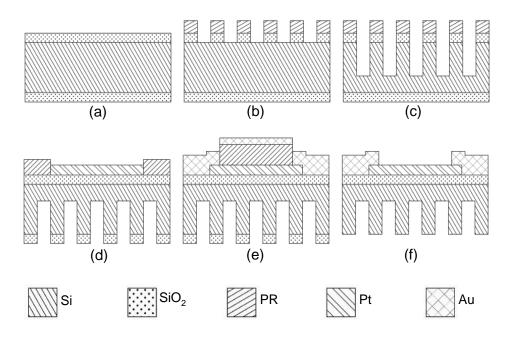

| Figure 3.3. | Schematic diagram of microchannel plate fabrication: (a) silicon wafer with                    |

|             | oxide; (b) exposed and developed PR (Mask #1, channels) and oxide dry-                         |

|             | etched; (c) silicon dry-etched; (d) PR stripped from channel side, PR spun,                    |

|             | exposed, and developed on heater-side (Mask #2, heaters/sensors) and                           |

|             | sputtered Ti-Pt; (e) exposed and developed PR (Mask #3, lead wire traces)                      |

|             | and deposited Ti-Au; and (f) final microchannel plate after lift-off, PR                       |

|             | stripped, and channel-side oxide layer removed. (Drawings are not to                           |

|             | scale.)                                                                                        |

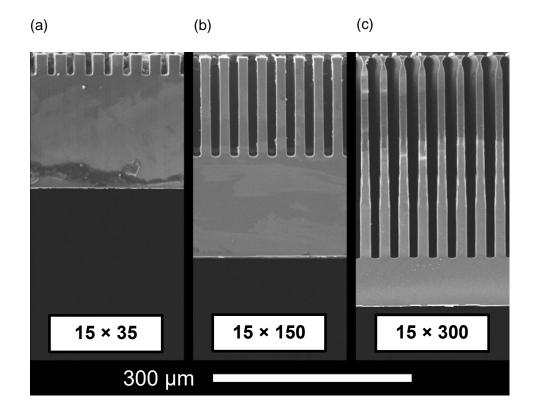

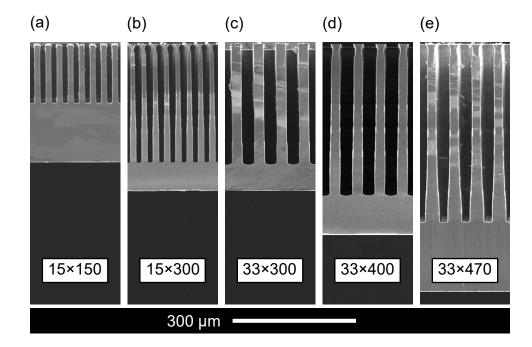

| Figure 3.4. | SEM images of channel cross-sections for (a) Sample A (15 $\mu$ m × 35 $\mu$ m), (b)           |

|             | Sample B (15 $\mu m \times 150 \ \mu m$ ), and (c) Sample C (15 $\mu m \times 300 \ \mu m$ )34 |

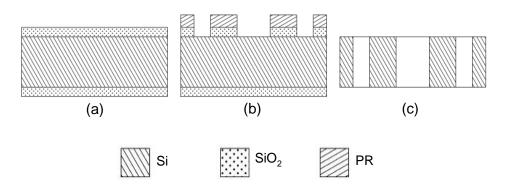

| Figure 3.5. | Schematic diagram of plenum plate fabrication process: (a) silicon wafer with                  |

|             | oxide; (b) exposed, developed PR (Mask #4, plenum), and oxide dry-etch;                        |

|             | and (c) final plenum plate after silicon dry-etched through wafer, PR stripped,                |

|             | and oxide removed. (Drawings are not to scale.)                                                |

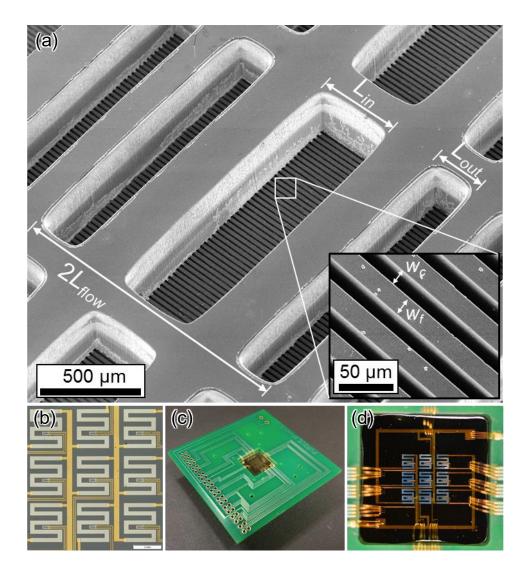

| Figure 3.6.  | (a) SEM image of plenum plate (with bonded microchannel plate underneath)                                        |

|--------------|------------------------------------------------------------------------------------------------------------------|

|              | and inset showing zoomed-in view of the exposed top surface of the                                               |

|              | microchannel plate; (b) microscope image of the serpentine heaters, RTDs,                                        |

|              | and lead-wire traces on the test chip; (c) photograph of the test chip mounted                                   |

|              | to the PCB with the heater-side surface face up; and (d) zoomed-in view of                                       |

|              | the heaters and sensors wire-bonded to the PCB contact pads                                                      |

| Figure 3.7.  | Schematic diagram of the flow loop                                                                               |

| Figure 3.8.  | Individual temperatures across chip surface as a function of base heat flux for                                  |

|              | Sample B (15 $\mu$ m × 150 $\mu$ m) at G = 1300 kg/m <sup>2</sup> s                                              |

| Figure 3.9.  | Base heat flux as a function of chip temperature rise for all three heat                                         |

|              | sink arrays at mass fluxes, G, of (a) 1300 kg/m <sup>2</sup> s, (b) 2100 kg/m <sup>2</sup> s, and                |

|              | (c) 2900 kg/m <sup>2</sup> s                                                                                     |

| Figure 3.10. | Heat transfer coefficient as a function of exit thermodynamic quality at mass                                    |

|              | fluxes, G, of (a) 1300 kg/m <sup>2</sup> s, (b) 2100 kg/m <sup>2</sup> s, and (c) 2900 kg/m <sup>2</sup> s40     |

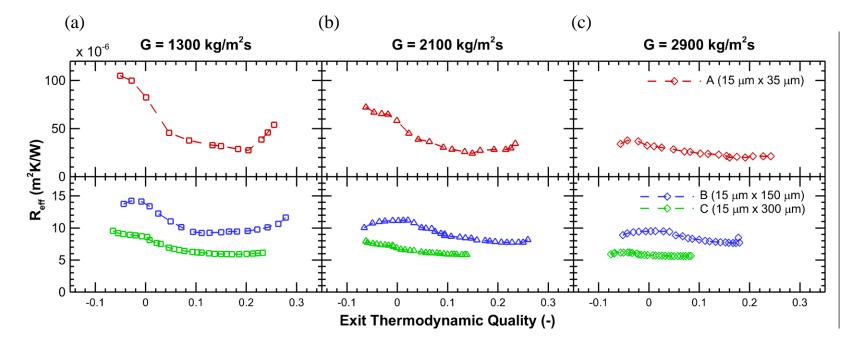

| Figure 3.11. | Effective thermal resistance as a function of exit thermodynamic quality for                                     |

|              | mass fluxes, G, of (a) 1300 kg/m <sup>2</sup> s, (b) 2100 kg/m <sup>2</sup> s, and (c) 2900 kg/m <sup>2</sup> s; |

|              | note that the ordinate scale is different for the top and bottom rows of plots41                                 |

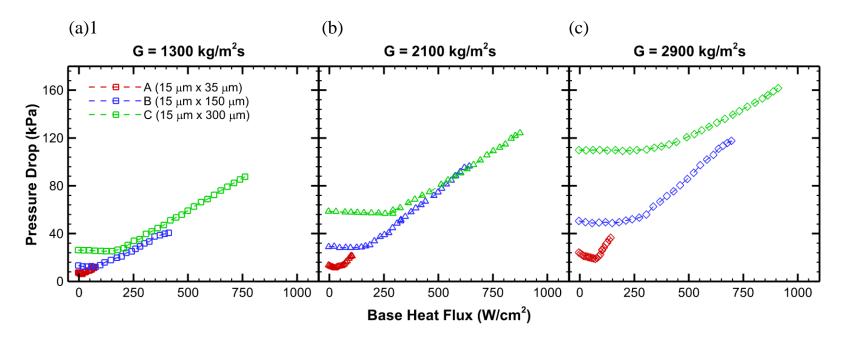

| Figure 3.12. | Pressure drop as a function of base heat flux for mass fluxes, G, of (a) 1300                                    |

|              | kg/m <sup>2</sup> s, (b) 2100 kg/m <sup>2</sup> s, and (c) 2900 kg/m <sup>2</sup> s42                            |

| Figure 4.1.  | Schematic diagram of the heat sink unit cell showing the fluid flow paths and                                    |

|              | relevant dimensions60                                                                                            |

| Figure 4.2.  | (a) CAD image of the test vehicle with a half-symmetry section removed and                                       |

|              | fluid inlets (blue) and outlets (red) shown; (b) zoomed-in view of the test                                      |

|              | vehicle with a quarter-symmetry section removed showing the fluid flow paths                                     |

|              | in the test chip; and (c-f) each plate level of the manifold distributor used to                                 |

|              | deliver fluid to individual heat sinks61                                                                         |

| Figure 4.3.  | Schematic diagram of (a) the microchannel plate and (b) the plenum plate62                                       |

| Figure 4.4.  | SEM images of the five microchannel cross-sections tested: (a) 15×150, (b)                                       |

|              | 15×300, (c) 33×300, (d) 33×400, (e) 33×470                                                                       |

xi

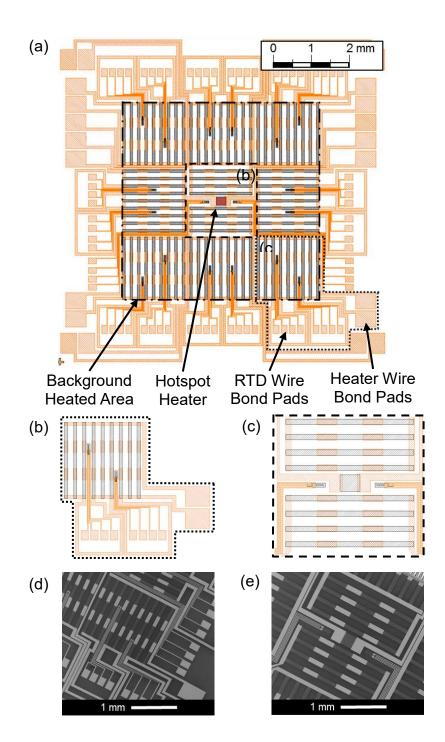

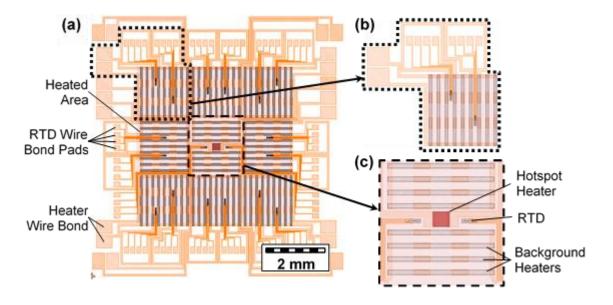

| Figure 4.5.  | CAD drawing of (a) entire heater and RTD layout, (b) a background-only             |

|--------------|------------------------------------------------------------------------------------|

|              | heater zone, and (c) the center zone with background and hotspot heaters.          |

|              | SEM images are shown for these same two heater zones consisting of (d) only        |

|              | background heaters and (e) background and hotspot heaters                          |

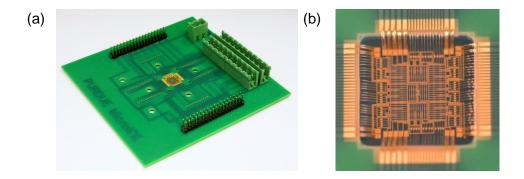

| Figure 4.6.  | (a) Photograph of the test chip mounted to the PCB with heaters and sensors        |

|              | face up and (b) zoomed-in view of the heaters and sensors wire-bonded to           |

|              | PCB contact pads65                                                                 |

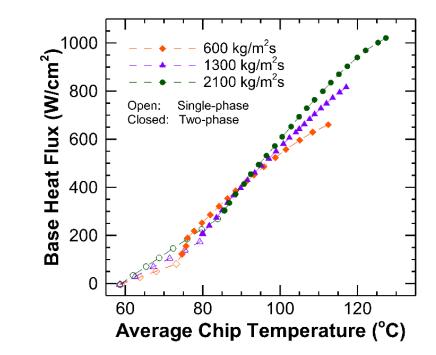

| Figure 4.7.  | Base heat flux as a function of average chip temperature for Sample 33×47066       |

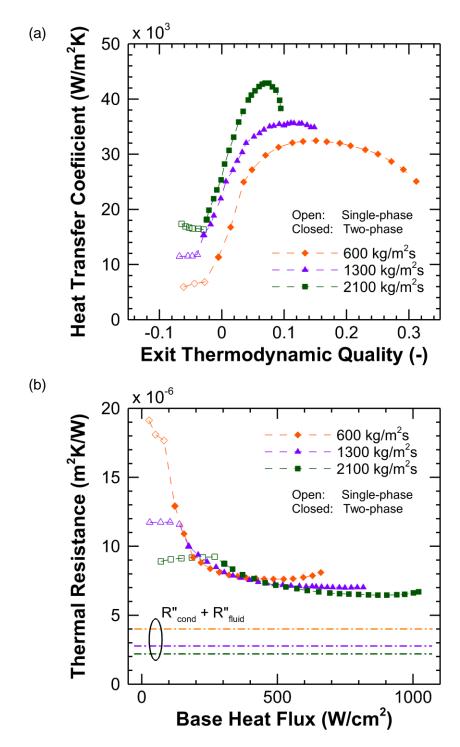

| Figure 4.8.  | (a) Heat transfer coefficient as a function of exit thermodynamic quality and      |

|              | (b) effective thermal resistance as a function of base heat flux for Sample        |

|              | 33×470 with data points showing total resistance and dashed lines showing          |

|              | sum of conduction and caloric resistances67                                        |

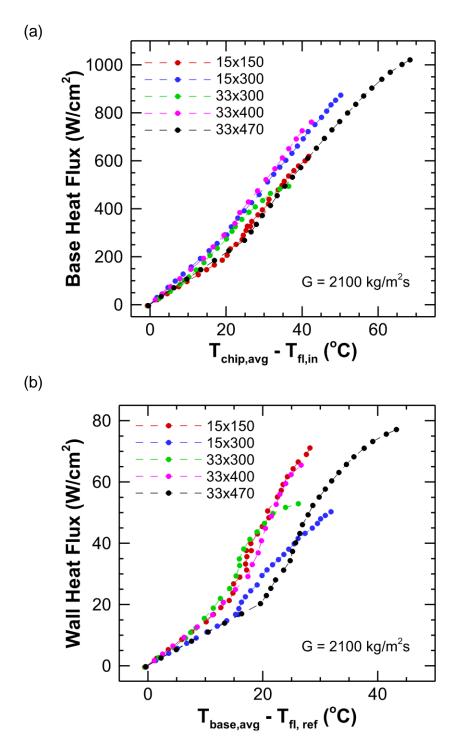

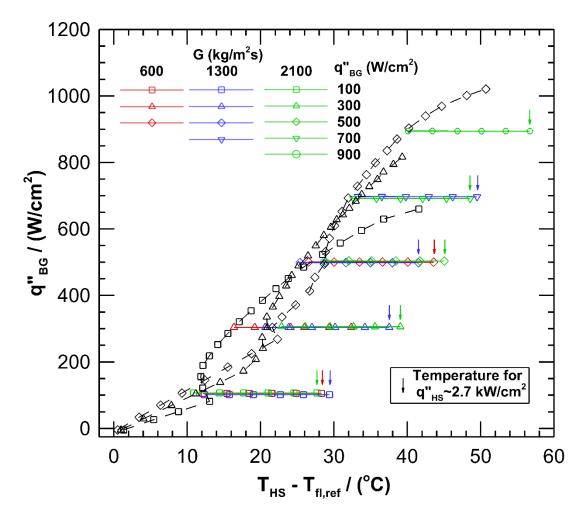

| Figure 4.9.  | (a) Base heat flux as a function of chip temperature rise above the fluid inlet    |

|              | temperature and (b) wall heat flux as a function of chip temperature rise above    |

|              | the fluid reference temperature, at a mass flux of 2100 kg/m <sup>2</sup> s68      |

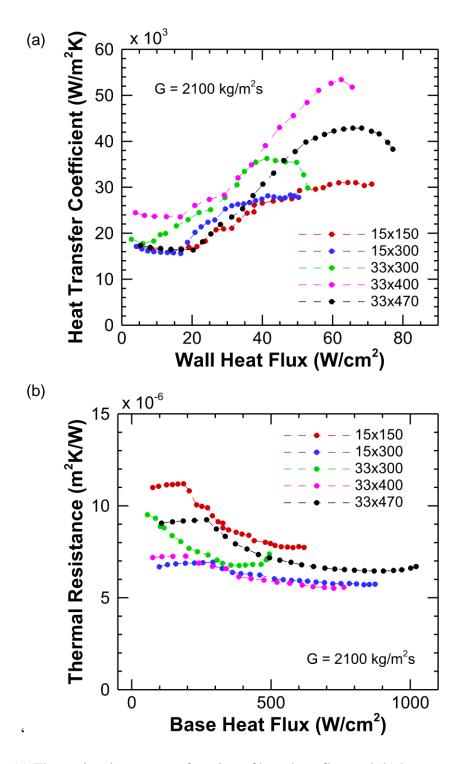

| Figure 4.10. | (a) Thermal resistance as a function of base heat flux and (b) heat transfer       |

|              | coefficient as a function of fluid exit thermodynamic quality at a mass flux of    |

|              | 2100 kg/m²s                                                                        |

| Figure 4.11. | (a) Pressure drop as a function of base heat flux and mass flux for Sample         |

|              | 33×470 and (b) pressure drop as a function of base heat flux and channel           |

|              | geometry at a mass flux of 2100 kg/m <sup>2</sup> s70                              |

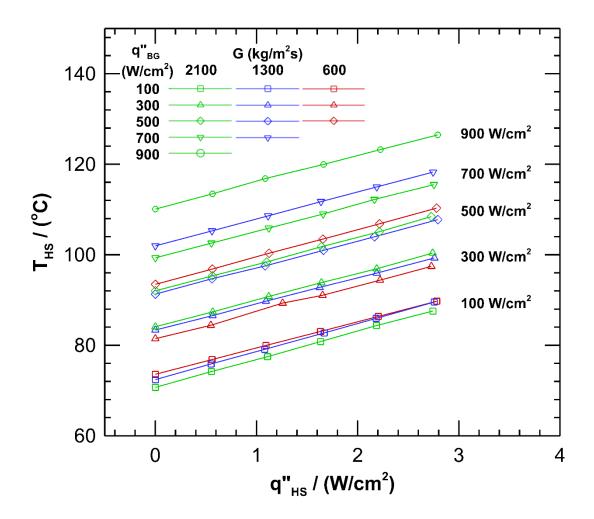

| Figure 4.12. | (a) Hotspot temperatures as a function of hotspot heat flux for a variety of fluid |

|              | mass fluxes and background heat fluxes. (b) Hotspot temperature rise above         |

|              | fluid reference temperature; boiling curves with black data points show            |

|              | hotspot temperature at zero hotspot heat flux and colored data points show         |

|              | hotspot temperature during hotspot testing (arrow pointing to hotspot              |

|              | temperature at the maximum hotspot heat flux of ~2,700 W/cm <sup>2</sup> )71       |

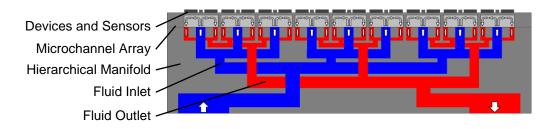

| Figure 5.1.  | Schematic diagram showing a hierarchical manifold microchannel heat sink           |

|              | array                                                                              |

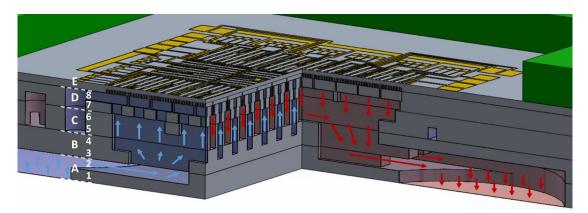

| Figure 5.2.  | CAD model of the hierarchical manifold microchannel heat sink used in this         |

|              | work with sections removed to show internal flow features                          |

| Figure 5.3.  | Heater/RTD layout                                                                     |

|--------------|---------------------------------------------------------------------------------------|

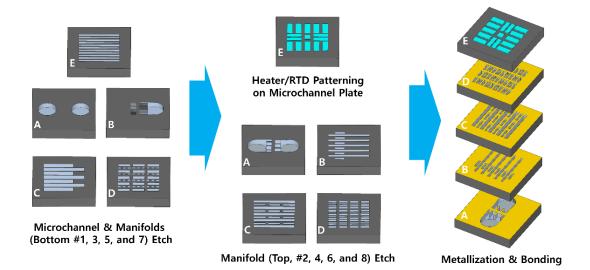

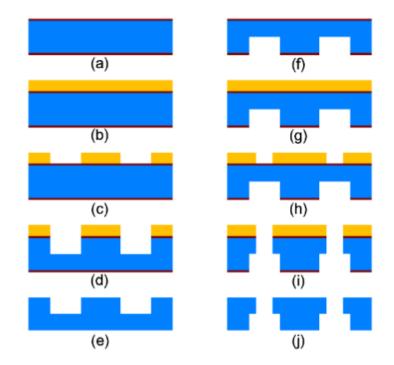

| Figure 5.4.  | Overall fabrication flow (Refer to Figure 5.1 for wafer letters and level             |

|              | numbers)                                                                              |

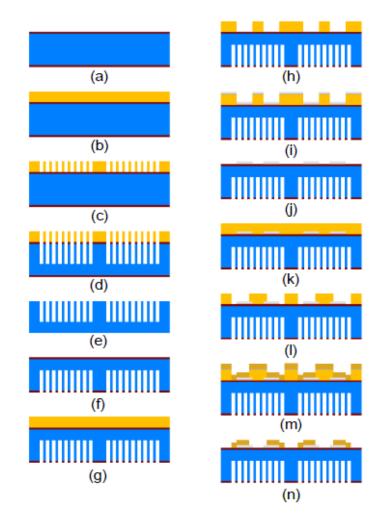

| Figure 5.5.  | Cross-section of microchannel and heater/RTD fabrication process. (a)                 |

|              | Piranha clean & oxidation (b) HMDS & PR coating (c) microchannel                      |

|              | lithography (d) SiO <sub>2</sub> & Si etch (e) PR removal and BOE (f) piranha clean & |

|              | oxidation (g) HMDS & PR coating (h) heater/RTD backside lithography (i)               |

|              | Ti and Pt deposition (j) lift-off (k) HMDS & PR coating (l) lead wire                 |

|              | lithography (m) Ti and Au deposition and (n) lift-off                                 |

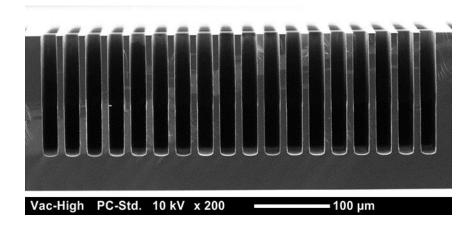

| Figure 5.6.  | SEM image of microchannel cross-section                                               |

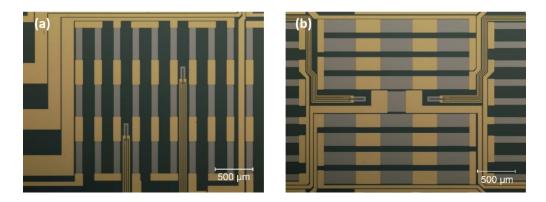

| Figure 5.7.  | Optical images of fabricated heater/RTD. (a) background heater array and (b)          |

|              | center hotspot heater with background heaters                                         |

| Figure 5.8.  | Cross-section of manifold fabrication process (a) piranha clean & oxidation           |

|              | (b) HMDS & PR coating (c) bottom-side lithography (d) $SiO_2$ & Si etch (e)           |

|              | PR removal and BOE (f) piranha clean & oxidation (g) PR coating (h) top-              |

|              | side lithography (i) SiO <sub>2</sub> & Si etch (j) PR removal and BOE87              |

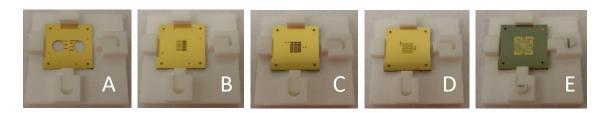

| Figure 5.9.  | Top view of fabricated manifolds (metallized with Ti/Au). Plate labels                |

|              | correspond the labels in Figure 2 and plates are stacked in alphabetical              |

|              | order                                                                                 |

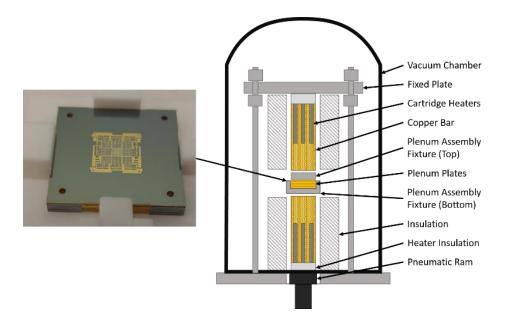

| Figure 5.10. | Schematic of bonding facility and a bonded chip after thermocompression               |

|              | bonding                                                                               |

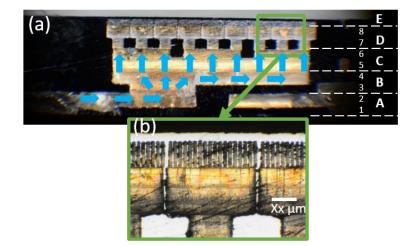

| Figure 5.11. | (a) Cross-section images of bonded microchannel array test vehicle. Arrows            |

|              | indicate inlet flow direction. (b) Magnified image of top microchannel plate88        |

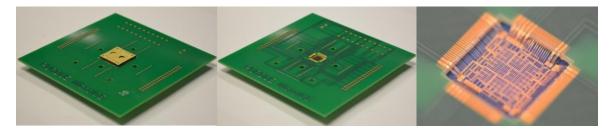

| Figure 5.12. | Fully assembled microchannel array test vehicle                                       |

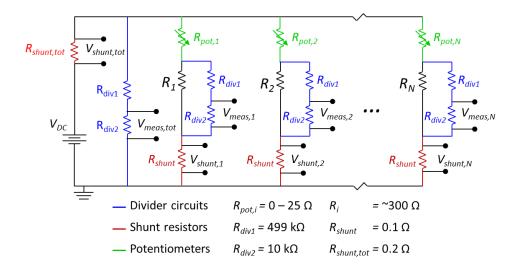

| Figure 5.13. | Electrical circuit showing the components used to measure heater power to             |

|              | the test vehicle                                                                      |

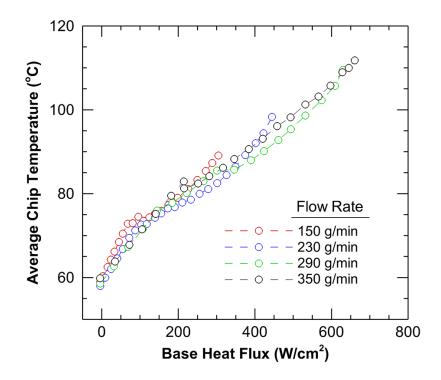

| Figure 5.14. | Average chip temperature as a function of base heat flux at flow rates of 150,        |

|              | 230, 290, and 350 g/min90                                                             |

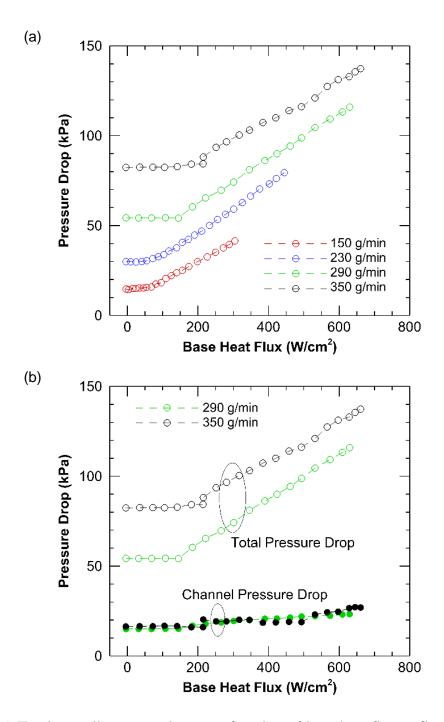

| Figure 5.15. | (a) Total overall pressure drop as a function of base heat flux at flow rates of  |

|--------------|-----------------------------------------------------------------------------------|

|              | 150, 230, 290, and 350 g/min and (b) and the total pressure drop across the       |

|              | test section compared to the channel pressure drops at flow rates of 290 and      |

|              | 350 g/min91                                                                       |

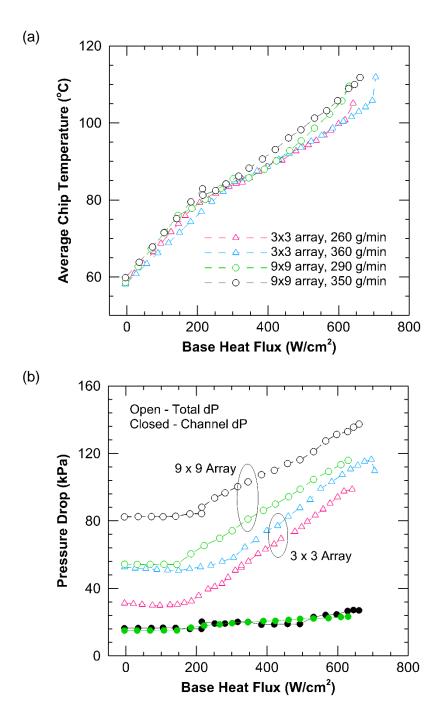

| Figure 5.16. | (a) Average chip temperature as a function of base heat flux at flow rates of     |

|              | 150, 230, 290, and 350 g/min92                                                    |

| Figure 6.1.  | Schematic diagram of a manifold microchannel heat sink                            |

| Figure 6.2.  | (a) Exploded view of a manifold microchannel (MMC) heat sink with a               |

|              | quarter-section removed, (b) the same MMC heat sink with the critical             |

|              | channel dimensions labeled, and (c) the MMC unit cell with the flow inlet and     |

|              | outlet paths shown105                                                             |

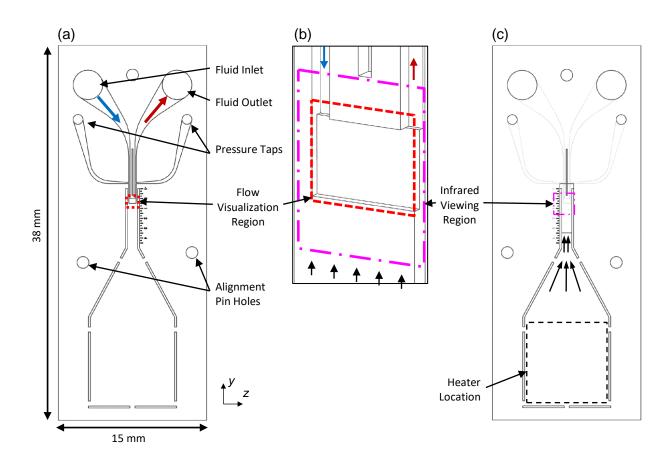

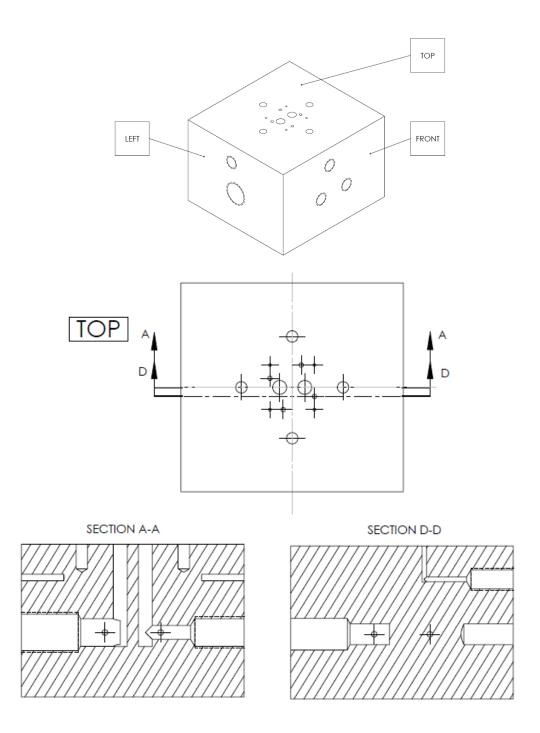

| Figure 6.3.  | CAD drawings of the test device: (a) front side with arrows showing the heat      |

|              | flow path to the channel (black) and the fluid inlet (blue) and outlet (red), (b) |

|              | inset of the channel region viewed at an angle with a section removed to view     |

|              | the channel cross-section, and (c) back side of the test device106                |

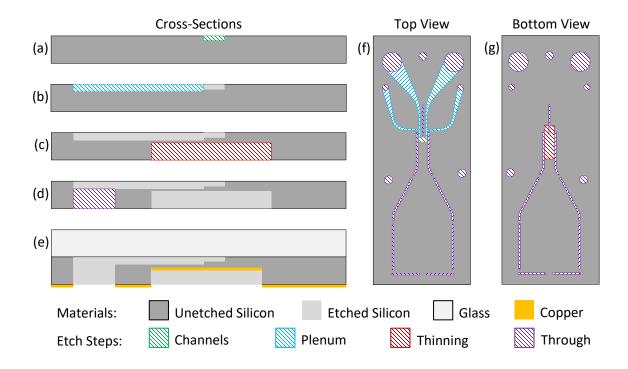

| Figure 6.4.  | (a-e) Schematic diagrams showing the test device cross-sections throughout        |

|              | the fabrication procedure and (f) top and (g) bottom schematic diagrams after     |

|              | fabrication. Dimensions are not to scale107                                       |

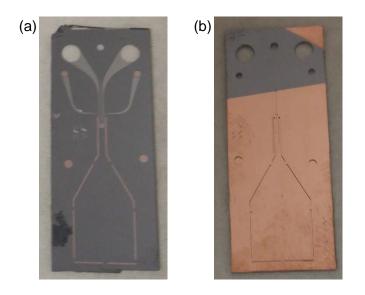

| Figure 6.5.  | Photographs of a test apparatus from the (a) front side and (b) back side107      |

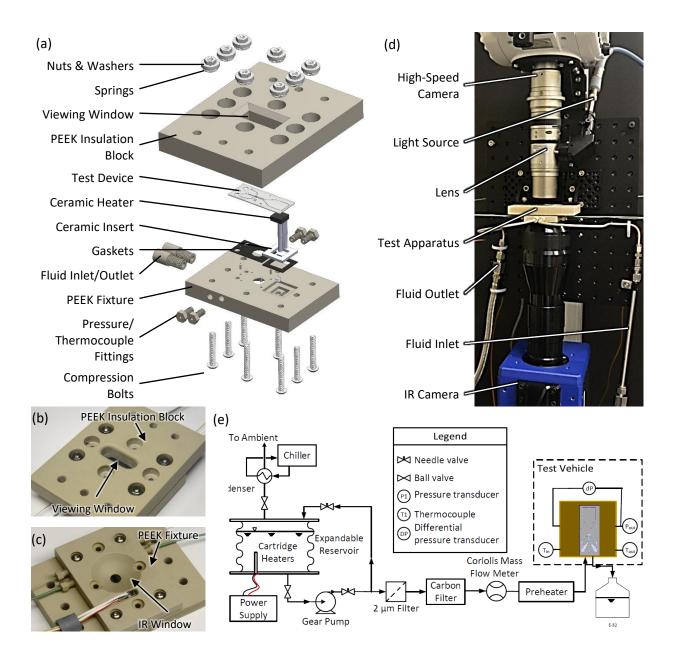

| Figure 6.6.  | (a) Exploded view of the test section assembly, and photographs of the test       |

|              | vehicle from the (b) top side, which contains a viewing window for high-          |

|              | speed visualizations and (c) bottom side, showing the pressure taps,              |

|              | thermocouples, heater leads, and IR viewing window, (d) photograph of the         |

|              | test vehicle assembled in the flow loop with the IR camera and high-speed         |

|              | camera mounted, and (e) a schematic diagram of the experimental flow              |

|              | loop                                                                              |

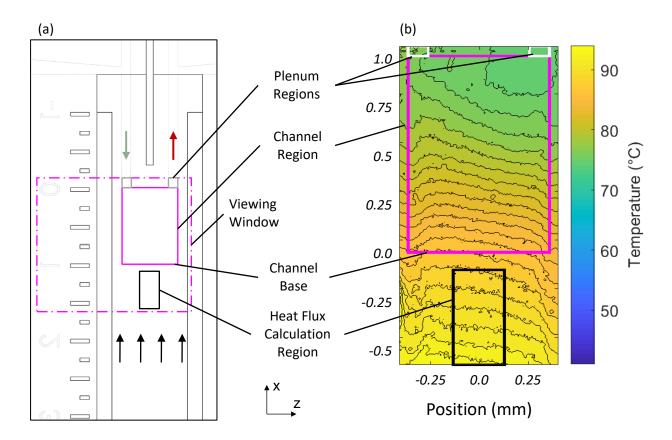

| Figure 6.7.  | (a) CAD model of the test device (Sample 3, 750 $\times$ 1000 µm) viewed from     |

|              | the back side showing the position of the uncropped IR viewing region and         |

|              | (b) a sample temperature map showing the region used to calculate heat flux       |

|              | into the channel and the channel region109                                        |

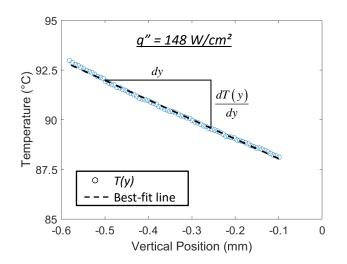

| Figure 6.8.  | A representative set of z-averaged temperature measurements as a function of                             |    |

|--------------|----------------------------------------------------------------------------------------------------------|----|

|              | vertical position for Sample 3 at a heat flux of 148 W/cm <sup>2</sup> along with the best-              |    |

|              | fit line for these data1                                                                                 | 09 |

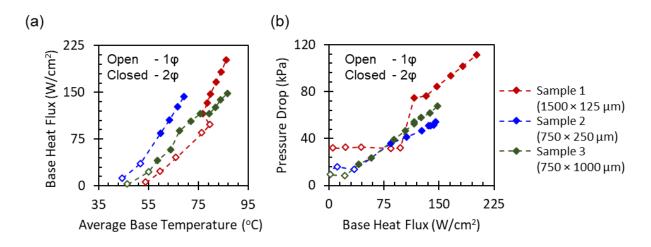

| Figure 6.9.  | (a) Base heat flux as a function of base temperature and (b) pressure drop as                            |    |

|              | a function of base heat flux for each channel geometry1                                                  | 10 |

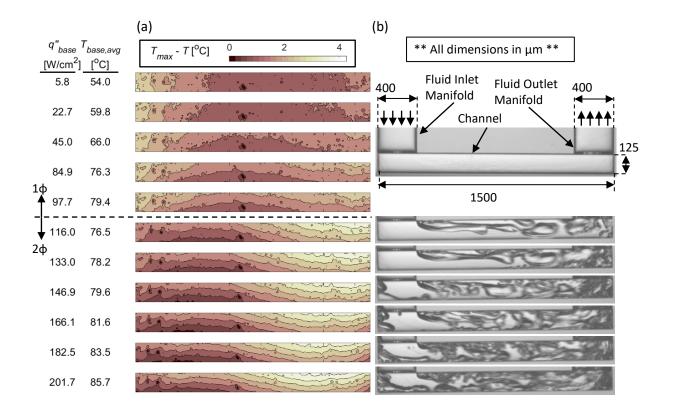

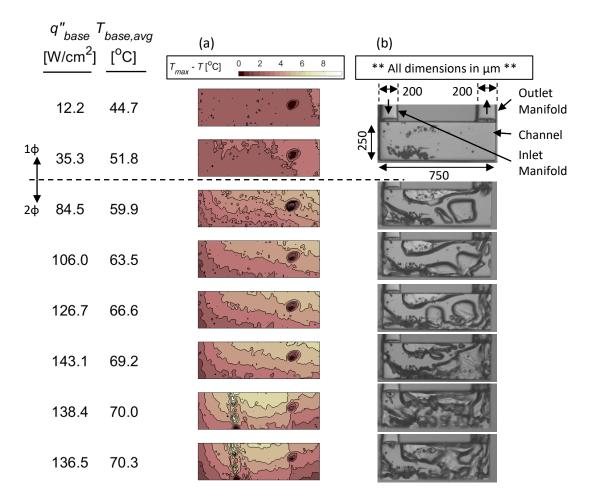

| Figure 6.10. | (a) Wall temperature maps for Sample 1 (1500 $\times$ 125 $\mu m$ ) over the range of                    |    |

|              | heat flux inputs shown in Figure 6.9. The relative temperature range remains                             |    |

|              | constant while the absolute temperature scales change for each plot. (b) Flow                            |    |

|              | visualization images are shown during two-phase operation1                                               | 10 |

| Figure 6.11. | (a) Wall temperature maps for Sample 2 (750 $\times$ 250 $\mu m$ ) over the range of                     |    |

|              | heat flux inputs shown in Figure 6.9. The relative temperature range remains                             |    |

|              | constant while the absolute temperature scales change for each plot. (b) Flow                            |    |

|              | visualization images are shown during two-phase operation1                                               | 11 |

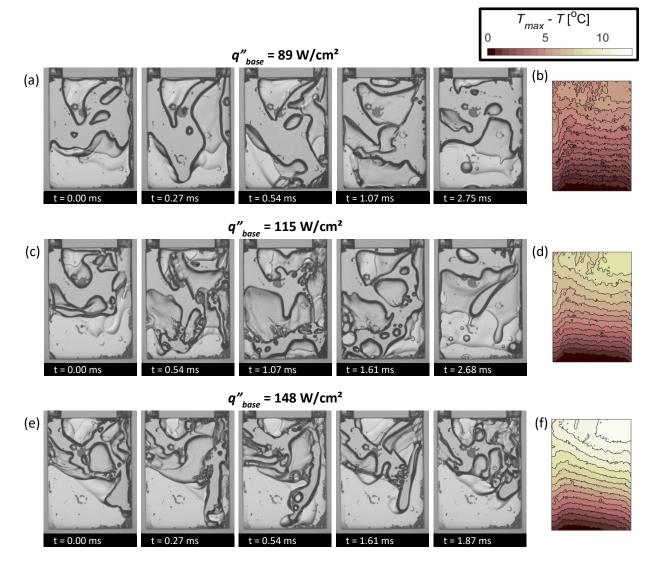

| Figure 6.12. | High-speed images showing the two-phase flow inside the channel of Sample                                |    |

|              | 3 along with the corresponding time-averaged wall temperature map for each                               |    |

|              | heat flux. Data for base heat fluxes of (a,b) 89 W/cm <sup>2</sup> , (c,d) 115 W/cm <sup>2</sup> , (e,f) |    |

|              | 148 W/cm <sup>2</sup> are shown1                                                                         | 12 |

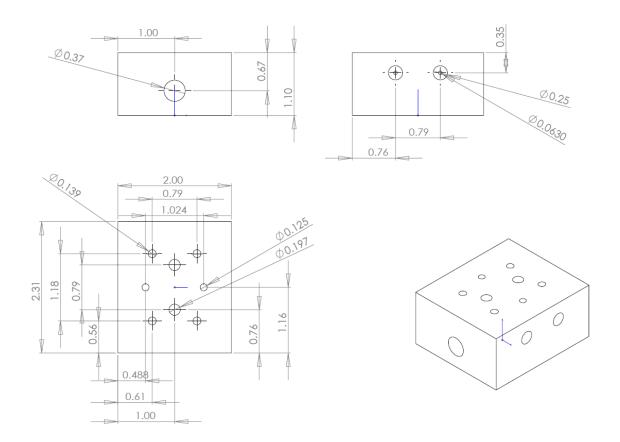

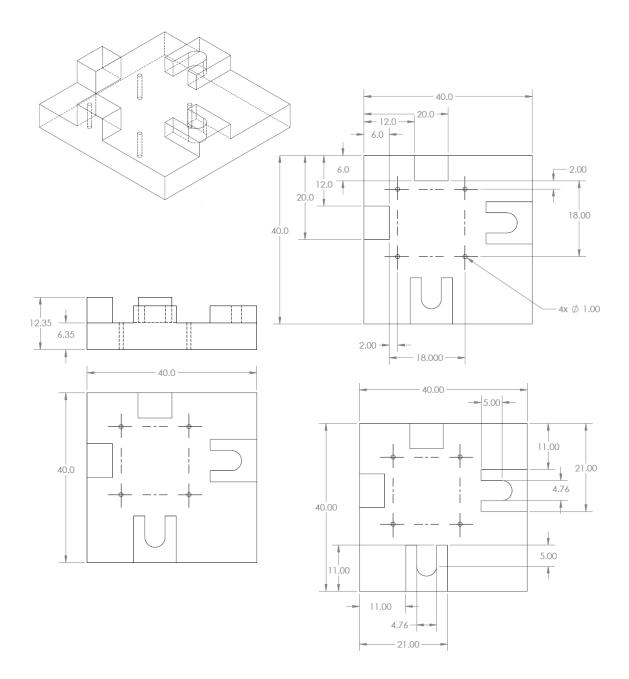

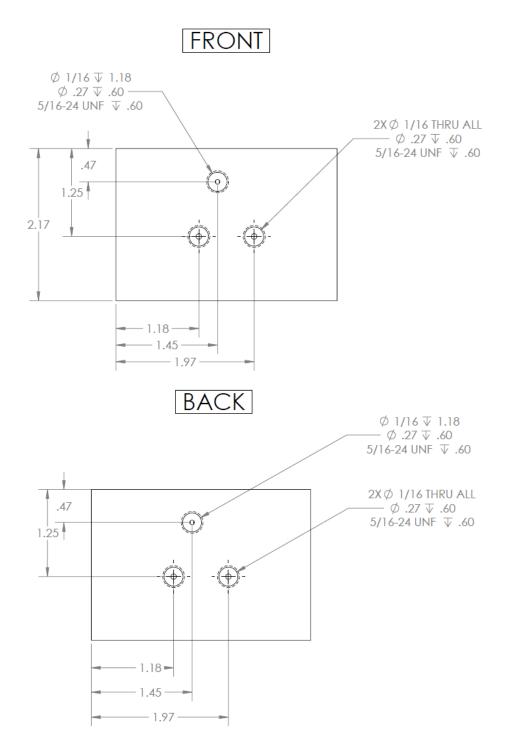

| Figure B.1.  | Photograph of the test vehicle installed in the flow loop                                                | 29 |

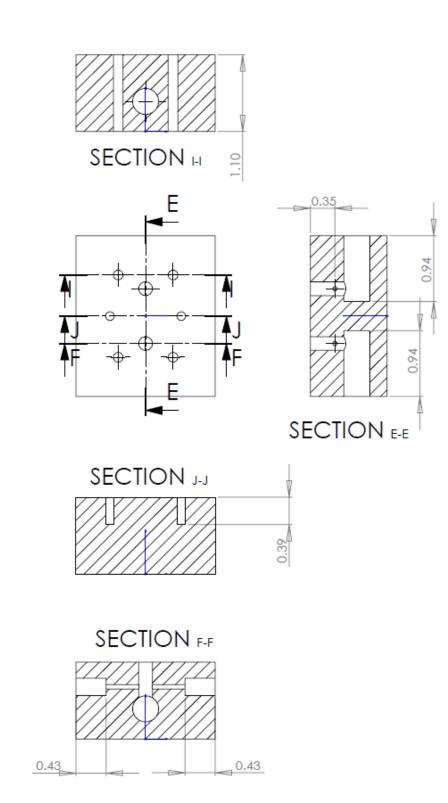

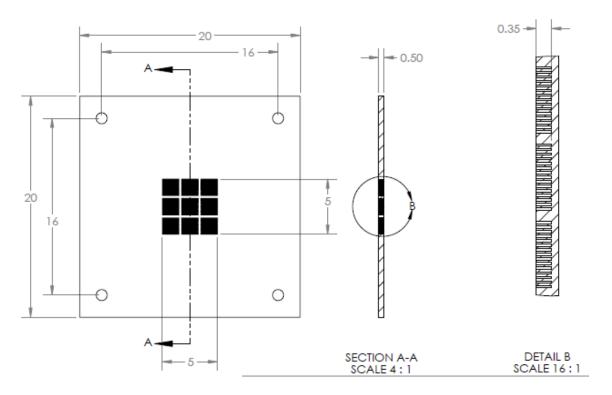

| Figure B.2.  | Technical drawings of the manifold base; all dimensions in inches unless                                 |    |

|              | otherwise specified1                                                                                     | 32 |

| Figure B.3.  | Technical drawings of the manifold base; all dimensions in inches unless                                 |    |

|              | otherwise specified1                                                                                     | 33 |

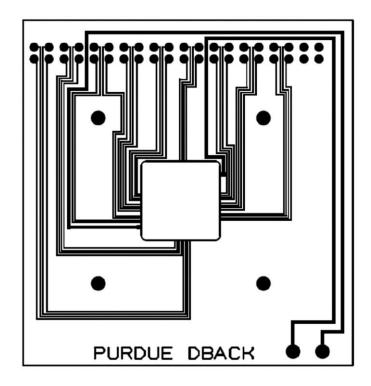

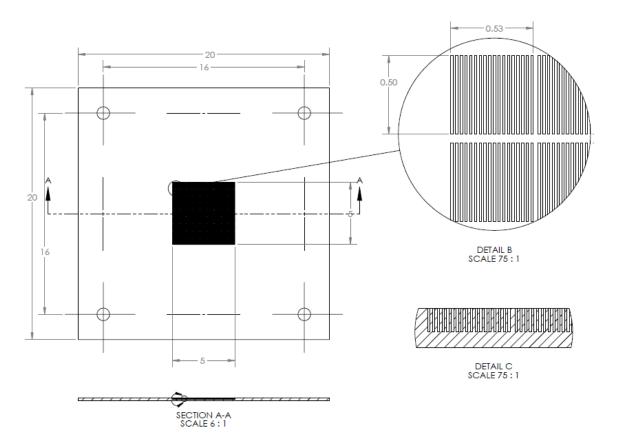

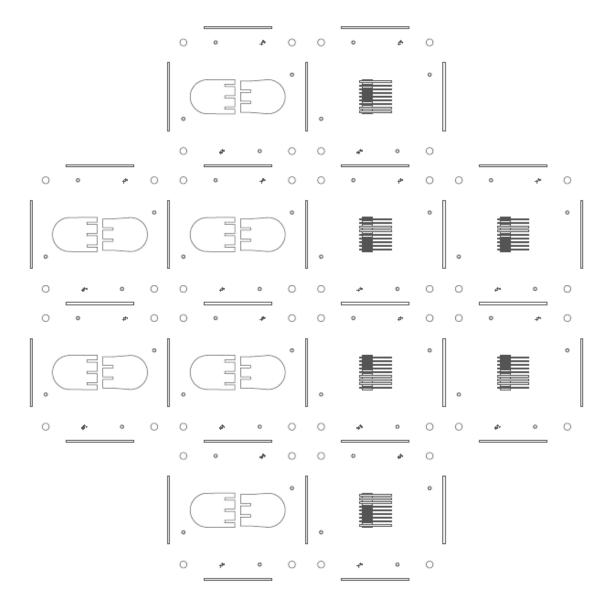

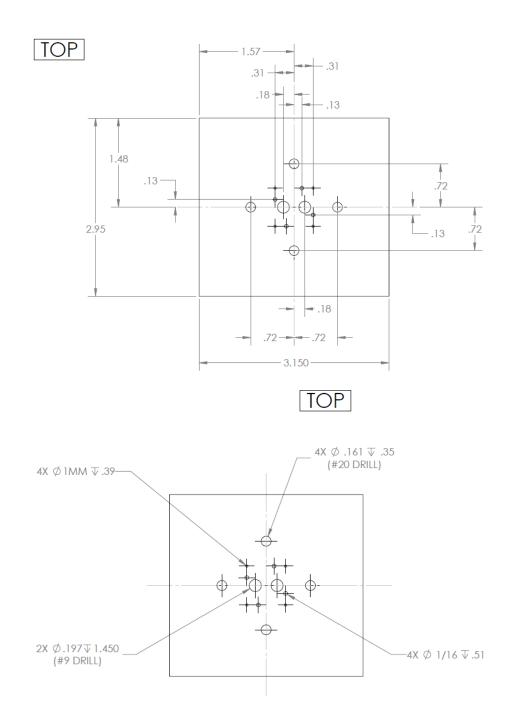

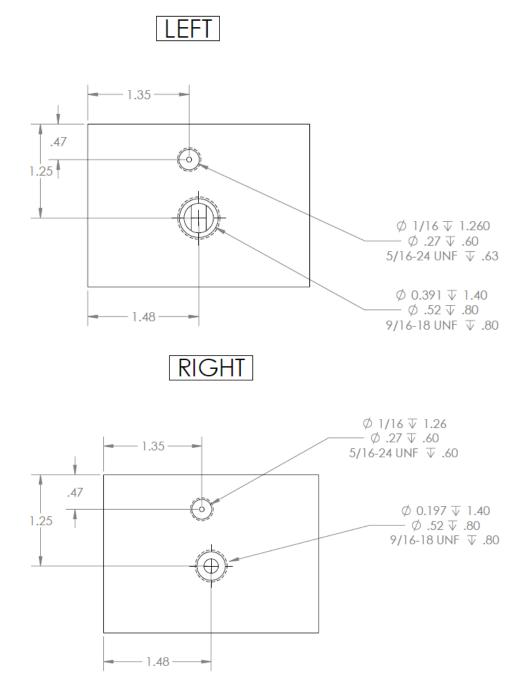

| Figure B.4.  | Technical drawing for a $3 \times 3$ microchannel plate. Note that the channel                           |    |

|              | dimensions change depending on the sample1                                                               | 34 |

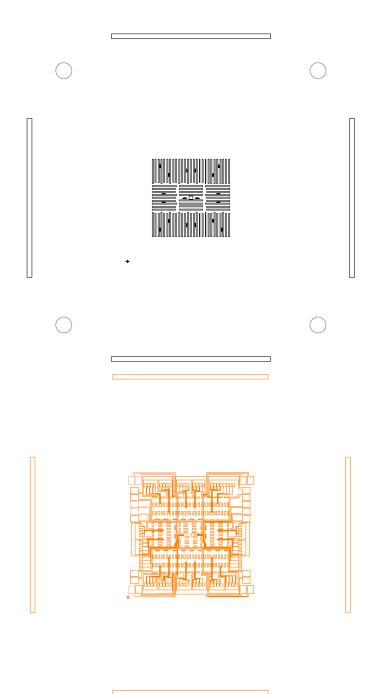

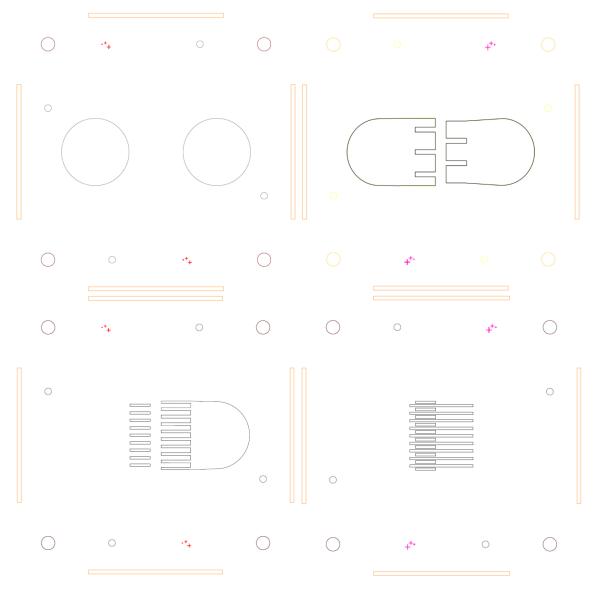

| Figure B.5.  | Mask design for the Pt heaters and temperature sensors and Au traces                                     | 35 |

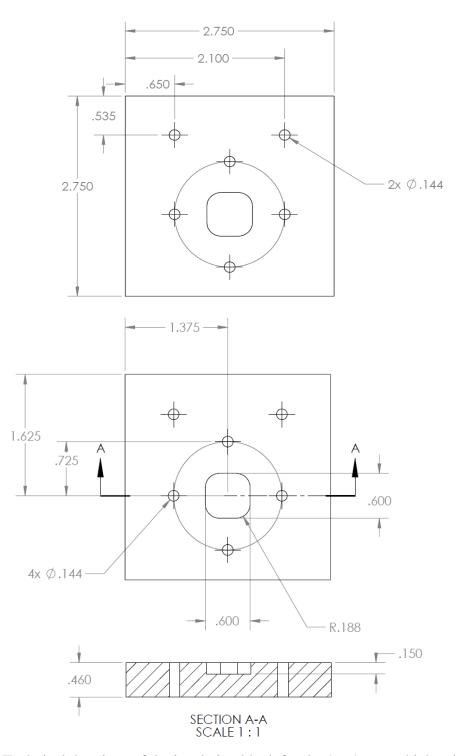

| Figure B.6.  | Technical drawings of the manifold; all dimensions in inches unless otherwise                            |    |

|              | specified1                                                                                               | 36 |

| Figure B.7.  | Technical drawing of the plenum plate mask for a single die. All dimensions                              |    |

|              | in millimeters1                                                                                          | 37 |

| Figure B.8.  | Mask design for the heater deign containing the hotspot heater. (a) Pt heaters                           |    |

|              | and RTDs and (b) Au traces                                                                               | 38 |

| Figure B.9.  | Mask design of the printed circuit board used for the background-only heater           |

|--------------|----------------------------------------------------------------------------------------|

|              | design                                                                                 |

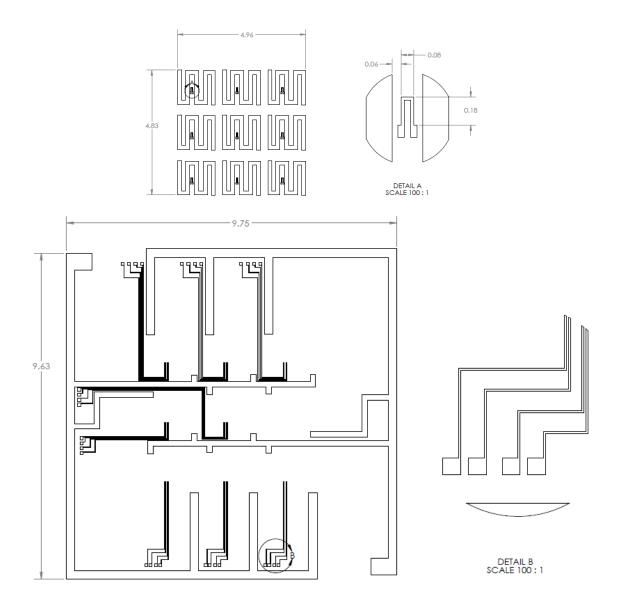

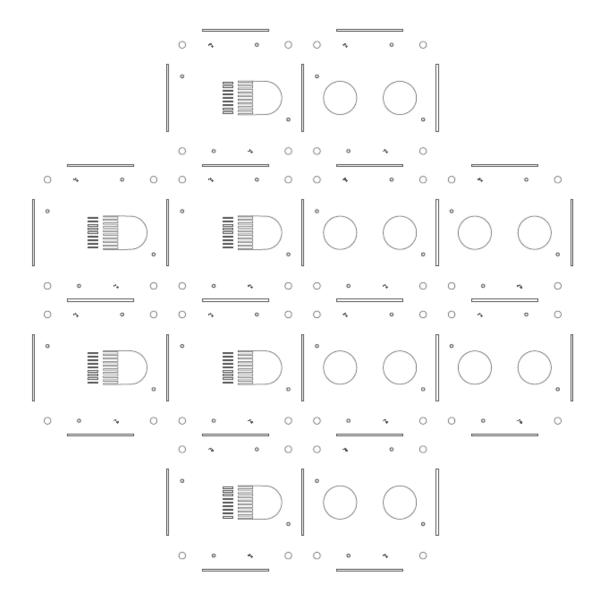

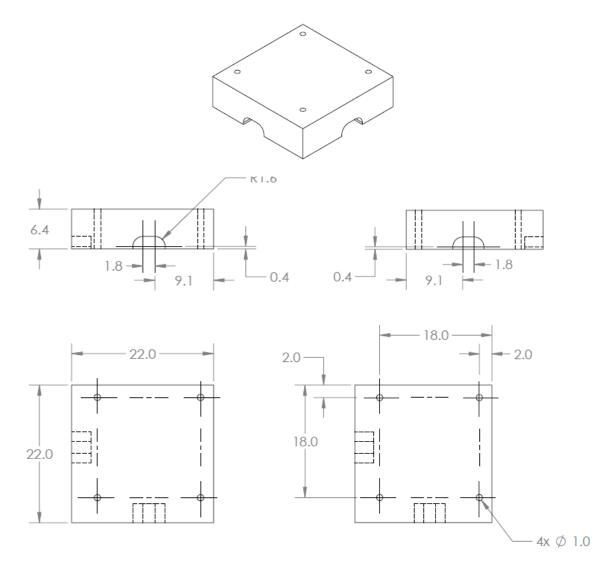

| Figure B.10. | Technical drawing for the $9 \times 9$ array of microchannel heat sinks. All           |

|              | dimensions in millimeters                                                              |

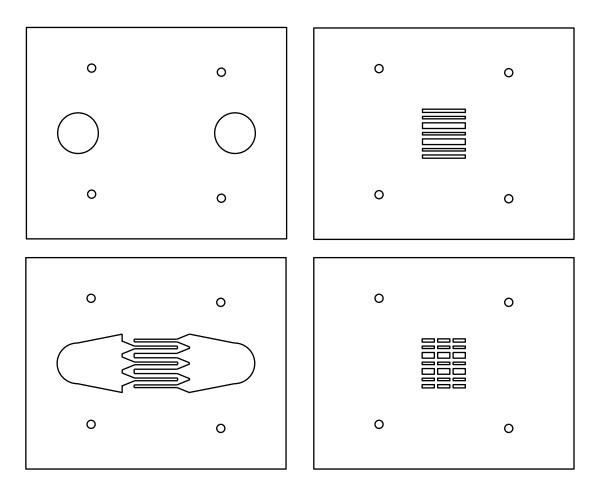

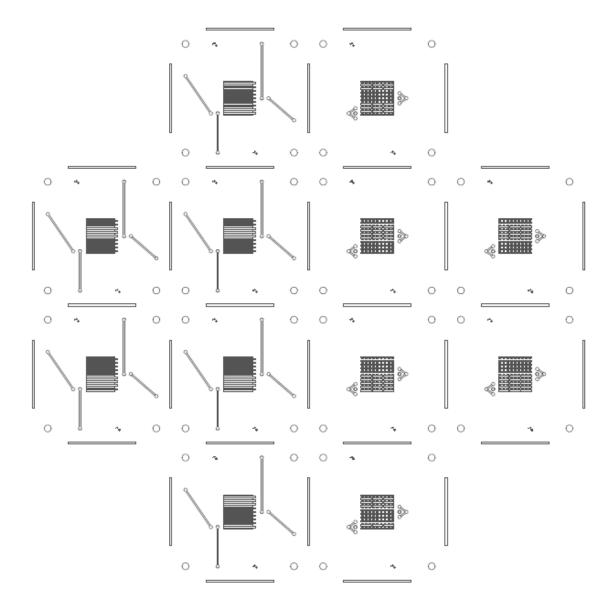

| Figure B.11. | Mask layout for 4-inch wafer for compact manifold used to feed $9 \times 9$ array      |

|              | of heat sinks141                                                                       |

| Figure B.12. | Mask layout for 4-inch wafer for compact manifold used to feed $9 \times 9$ array      |

|              | of heat sinks142                                                                       |

| Figure B.13. | Mask layout for 4-inch wafer for compact manifold used to feed $9 \times 9$ array      |

|              | of heat sinks                                                                          |

| Figure B.14. | Mask layout for 4-inch wafer for compact manifold used to feed $9 \times 9$ array      |

|              | of heat sinks                                                                          |

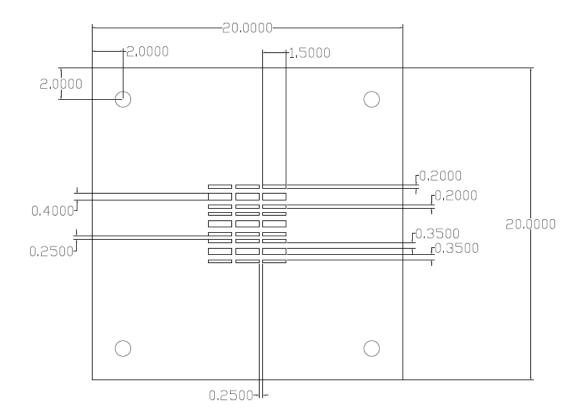

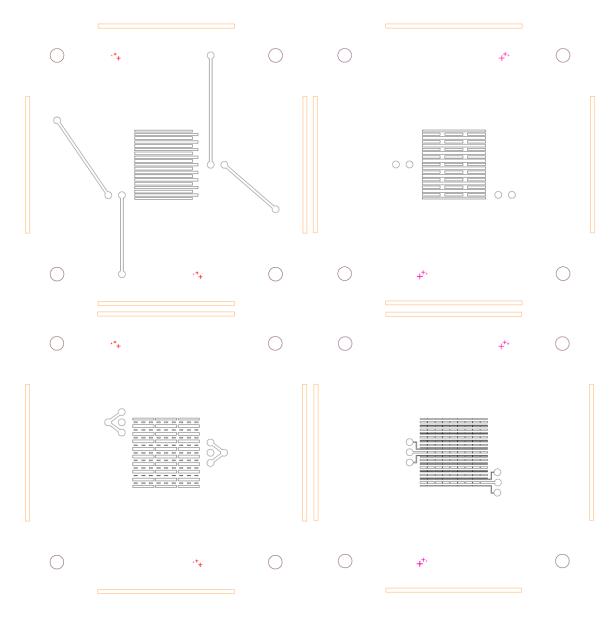

| Figure B.15. | CAD drawings of the photomasks for levels 1-4 of the hierarchical                      |

|              | manifold145                                                                            |

| Figure B.16. | CAD drawings of the photomasks for levels 5-8 of the hierarchical                      |

|              | manifold146                                                                            |

| Figure B.17. | Technical drawings of the manifold assembly fixture; all dimensions in                 |

|              | millimeters unless otherwise specified                                                 |

| Figure B.18. | Technical drawings of the manifold assembly fixture (bottom); all dimensions           |

|              | in millimeters unless otherwise specified                                              |

| Figure B.19. | Technical drawings of the manifold base for the test vehicle with a $9 \times 9$ array |

|              | of heat sinks; all dimensions in inches unless otherwise specified149                  |

| Figure B.20. | Technical drawings of the manifold base for the $9 \times 9$ test vehicle; all         |

|              | dimensions in inches unless otherwise specified150                                     |

| Figure B.21. | Technical drawings of the manifold base for the $9 \times 9$ test vehicle; all         |

|              | dimensions in inches unless otherwise specified151                                     |

| Figure B.22. | Technical drawings of the manifold base for the $9 \times 9$ test vehicle; all         |

|              | dimensions in inches unless otherwise specified152                                     |

| Figure B.23. | Technical drawings of the insulation block for the $9 \times 9$ test vehicle; all      |

|              | dimensions in inches unless otherwise specified153                                     |

| Figure D.1. | Hotspot temperatures as a function of hotspot heat flux for a variety of fluid                    |   |

|-------------|---------------------------------------------------------------------------------------------------|---|

|             | mass fluxes and background heat fluxes164                                                         | 4 |

| Figure D.2. | Hotspot temperature rise above fluid reference temperature; boiling curves                        |   |

|             | with black data points show hotspot temperature at zero hotspot heat flux and                     |   |

|             | colored data points show hotspot temperature during hotspot testing (arrow                        |   |

|             | pointing to hotspot temperature at the maximum hotspot heat flux of                               |   |

|             | ~2,700 W/cm <sup>2</sup> )165                                                                     | 5 |

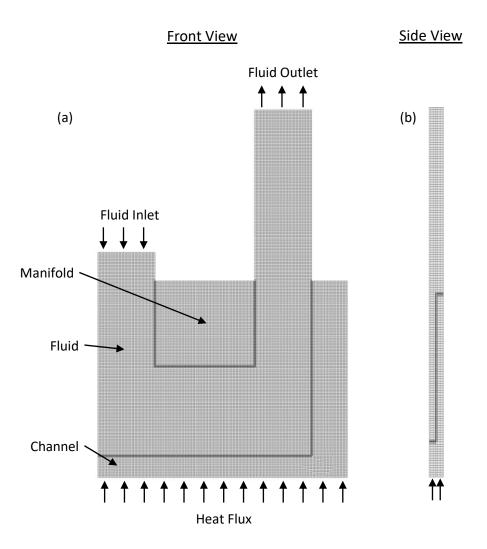

| Figure F.1. | Images of the meshed model domain for the CFD simulations from the (a)                            |   |

|             | front and (b) side17                                                                              | 5 |

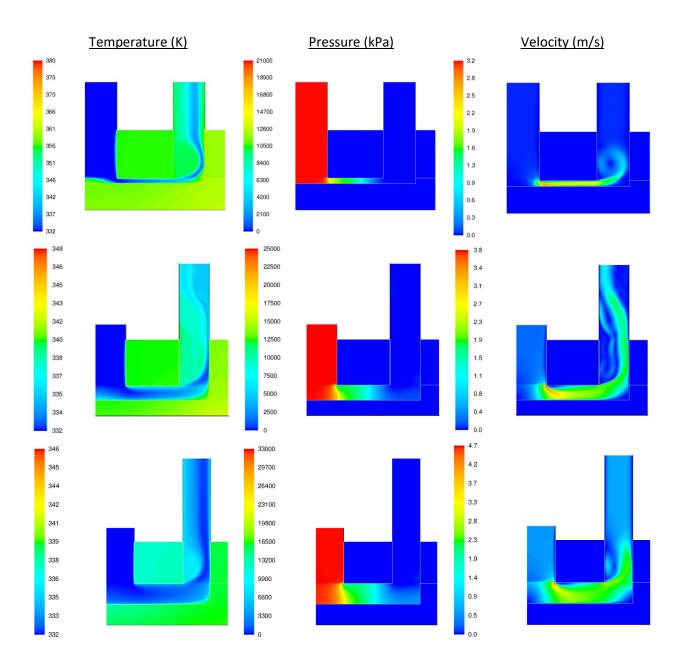

| Figure F.2. | Temperature, pressure and velocity profiles in MMCs of (a) Sample A, (b)                          |   |

|             | Sample B, and (c) Sample C (from Section 3.3) for a channel mass flux of                          |   |

|             | 2900 kg/m <sup>2</sup> s and a heat flux of 75 W/cm <sup>2</sup> during single-phase operation176 | 6 |

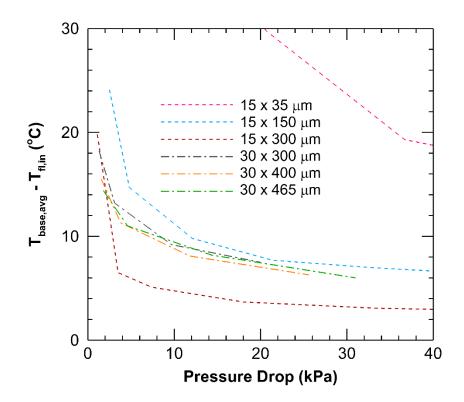

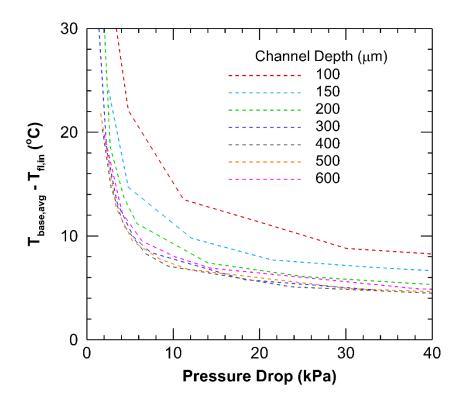

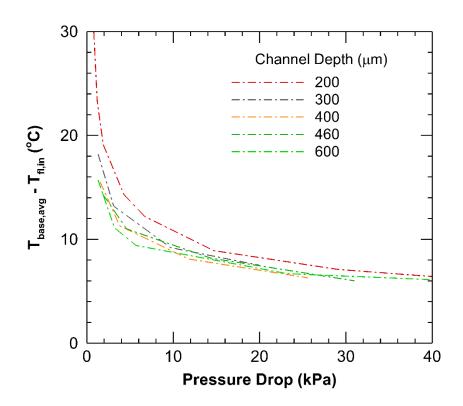

| Figure F.3. | Average base temperature above the fluid inlet temperature as a function of                       |   |

|             | pressure drop for the channel geometries tested in Chapters 3 and 417                             | 7 |

| Figure F.4. | Average base temperature above the fluid inlet temperature as a function of                       |   |

|             | pressure drop for a fixed channel width of 15 $\mu m$ and various channel                         |   |

|             | depths178                                                                                         | 8 |

| Figure F.5. | Average base temperature above the fluid inlet temperature as a function of                       |   |

|             | pressure drop for a fixed channel width of 30 $\mu$ m and various channel                         |   |

|             | depths179                                                                                         | 9 |

## NOMENCLATURE

| A                   | area                                                        |

|---------------------|-------------------------------------------------------------|

| AR                  | aspect ratio                                                |

| d                   | depth                                                       |

| $d_{wafer}$         | wafer thickness                                             |

| $C_p$               | specific heat                                               |

| G                   | mass flux                                                   |

| $h_{wall}$          | heat transfer coefficient                                   |

| $h_{LV}$            | latent heat of vaporization                                 |

| Ι                   | electrical current                                          |

| k                   | thermal conductivity                                        |

| L                   | length                                                      |

| $L_{nd}$            | nondimensional length                                       |

| $N_c$               | number of channels per heat sink                            |

| $N_{sink}$          | number of heat sinks                                        |

| $P_{el}$            | electrical power                                            |

| $P_c$               | channel perimeter                                           |

| Q                   | heat                                                        |

| $R_{HS,heater}$     | hotspot heater electrical resistance                        |

| $R_{HS,tot}$        | combined electrical resistance of hotspot heater and traces |

| R" <sub>th</sub>    | overall thermal resistance                                  |

| R" cond             | conduction thermal resistance                               |

| R" <sub>fluid</sub> | caloric thermal resistance                                  |

| Т                   | temperature                                                 |

| T <sub>fl,ref</sub> | fluid reference temperature                                 |

| V                   | voltage                                                     |

| W                   | width                                                       |

| x                   | thermodynamic quality                                       |

| Z.                  | location along channel                                      |

## GREEK SYMBOLS

| ρ         | mass density               |

|-----------|----------------------------|

| $\eta_f$  | fin efficiency             |

| $\eta_0$  | overall surface efficiency |

| $\varphi$ | phase                      |

### SUBSCRIPTS

| avg              | average          |

|------------------|------------------|

| b                | base             |

| base             | base of channels |

| BG               | background       |

| С                | channel          |

| chip             | chip surface     |

| el               | electrical       |

| f                | fin              |

| fl               | fluid            |

| HS               | hotspot          |

| i                | individual zone  |

| in               | inlet            |

| loss             | loss             |

| out              | outlet           |

| sat              | saturation       |

| sens             | sensible         |

| Si               | silicon          |

| sink             | heat sink        |

| SiO <sub>2</sub> | silicon dioxide  |

| tot              | total            |

| wet              | wetted area      |

### ABSTRACT

Author: Drummond, Kevin P.. PhD Institution: Purdue University Degree Received: May 2018 Title: Characterization of Manifold Microchannel Heat Sinks During Two-Phase Operation Major Professors: Suresh V. Garimella, Justin A. Weibel

High-heat-flux removal is necessary for next-generation microelectronic systems to operate more reliably and efficiently. The direct embedding of microchannel heat sinks into the heated substrate serves to reduce the parasitic thermal resistances due to contact and conduction resistances typically associated with the attachment of a separate heat sink. Manifold microchannel (MMC) heat sinks can dissipate high heat fluxes at moderate pressure drops, especially during two-phase operation. High-aspect-ratio microchannels allow for a large enhancement in heat transfer area. This work focuses on designing intrachip MMC heat sinks for high-heat-flux dissipation and to characterize the flow morphology present in the MMCs during two-phase operation.

A  $3 \times 3$  array of heat sinks is fabricated into a heated silicon substrate for direct intrachip cooling. The heat sinks are fed in parallel using a hierarchical manifold distributor that is designed to deliver equal flow to each of the heat sinks. Each heat sink contains a bank of high-aspect-ratio microchannels; channels with nominal widths of 15 µm and 33 µm and nominal depths between 150 µm and 470 µm are tested. Discretizing the chip footprint area into multiple smaller heat sink elements with high-aspect-ratio microchannels ensures shortened effective fluid flow lengths. High two-phase fluid mass fluxes can thus be accommodated in micron-scale channels while keeping pressure drops low compared to traditional, microchannel heat sinks.

The thermal and hydraulic performance of each heat sink array geometry is evaluated using the engineered dielectric liquid HFE-7100 as the working fluid and for mass fluxes ranging from 600 kg/m<sup>2</sup>s to 2100 kg/m<sup>2</sup>s at a constant inlet temperature of 59 °C. To simulate heat generation from electronics devices, a uniform background heat flux is generated with thin-film serpentine heaters fabricated on the silicon substrate opposite the channels; temperature sensors placed across the substrate provide spatially resolved surface temperature measurements. Experiments are also conducted with simultaneous background and hotspot heat generation; the hotspot heat flux is produced by an individual 200  $\mu$ m × 200  $\mu$ m hotspot heater.

During uniform heating conditions, heat fluxes up to 1020 W/cm<sup>2</sup> are dissipated at chip temperatures less than 69 °C above the fluid inlet and at pressure drops less than 120 kPa. Heat sinks with wider channels yield higher wetted-area heat transfer coefficients, but not necessarily the lowest thermal resistance; for a fixed channel depth, samples with thinner channels can have increased total wetted areas owing to the smaller fin pitches. During simultaneous background and hotspot heating conditions, background heat fluxes up to 900 W/cm<sup>2</sup> and hotspot fluxes up to 2,700 W/cm<sup>2</sup> are dissipated. The hotspot temperature increases linearly with hotspot heat flux and is independent of background heat flux and mass flux. At hotspot heat fluxes of 2,700 W/cm<sup>2</sup>, the hotspot experiences a temperature rise of 16 °C above the average chip temperature.

The ability to fabricate and assemble a chip-integrated, compact hierarchical manifold used to deliver fluid to a  $9 \times 9$  array of heat sinks has been demonstrated, with feature sizes significantly reduced compared to the  $3 \times 3$  array of heat sinks. The integrated manifold provides ports to measure the pressure drop across the channel; combining these data with the overall pressure drop, the contributions of both components to the hydraulic performance is determined. The hierarchical manifold consists of eight feature layers that have a minimum feature size of 50 µm. The manifold is fabricated by etching one feature layer into each side of four silicon wafers and then thermocompression bonding the wafers together. The resulting manifold is a compact, leak-free device that is used to deliver fluid to the array of heat sinks and recollect the outlet flow from the heat sinks. A sample manifold was diced, revealing a manifold that was aligned with the channels within 5 µm. Heat fluxes up to 630 W/cm<sup>2</sup> are tested with temperatures and pressures reaching 110 °C and 135 kPa, respectively.

An experiment is designed to provide simultaneous high-speed flow visualization and spatially-resolved wall temperature measurements on a single manifold microchannel. Visualizing the flow morphology inside the channel during two-phase operation is critical to being able to understand the performance MMCs. This work provides an understanding of the two-phase flow structure and wall temperature profiles in high-aspect-ratio microchannels, which cannot be extracted from the area- and time-averaged data obtained using the heat sinks containing many parallel channels. In high-aspect-ratio channels, vapor blanketing at the bottom of the channel is observed, which leads to significantly diminished thermal performance. The vapor formation

characteristics in high-aspect-ratio microchannels also lead to time-periodic fluctuations that are not observed in low and intermediate aspect ratios. Opportunities for future experimental and model work to further understand flow boiling in MMCs are identified based on the work completed in this dissertation and the open literature.

### **1. INTRODUCTION**

#### 1.1 Background

The continuing miniaturization of electronics components of ever greater performance and functionality has led to severely increased thermal management challenges. For example, heat fluxes in excess of 1000 W/cm<sup>2</sup> must be dissipated in next-generation radar, power electronics, and high-performance computing systems [1,2]. Electronic devices have traditionally been cooled through the attachment of standalone heat sinks. In this 'remote cooling' architecture, the total temperature rise across the thermal management solution is governed by parasitic interfacial, conduction, and spreading resistances between the device and heat sink. The deterioration of electrical performance characteristics and thermomechanical reliability at high device temperatures calls for the development of transformative 'intrachip cooling' strategies, with coolant channels deployed directly in the electronic device, to enable improved functionality of electronic systems. While direct, intrachip cooling allows for reduced conduction resistances and altogether eliminates contact resistances, heat spreading is drastically reduced, necessitating high heat transfer coefficients in the heat sink. Local hotspots in the die also can lead to high local chip temperatures and large temperature gradients across the die. Dielectric working fluids are preferred for such systems because they minimize the threat for electrical shorting, do not interfere with RF signals, are non-corrosive, and are available at a variety of saturation temperatures.

High heat fluxes can be dissipated using heat sinks utilizing straight, parallel microchannels [3]. In general, increasing channel depth, decreasing channel width, and increasing fluid flow rate all allow for larger heat dissipation at a given chip temperature. However, there are practical limits to how deep and thin these channels can be made. Additionally, pressure drop along the length of the channels leads to intractably large pumping power requirements at the extremely small channel widths and high flow rates necessary to dissipate extreme heat fluxes on the order of 1000 W/cm<sup>2</sup>. Transitioning to two-phase evaporative cooling in microchannel heat sinks can provide improved surface temperature uniformity and increased heat dissipation compared to single-phase heat sinks [4–6].

In addition to traditional microchannels, a variety of heat sink designs have been implemented to dissipate high heat fluxes at reduced pressure drop. One such design is manifold microchannel (MMCs) heat sinks, which distribute the flow through the microchannel heat sink in multiple parallel flow paths of decreased effective flow length. Figure 1.1 shows the fluid flow paths in a manifold microchannel heat sink; fluid from the manifold (not shown) arrives normal to the microchannels through a plenum plate, which defines the inlets and outlets to the channels. The flow impinges on the channel base, splits and travels along the channel in both directions, and exits the channels through the plenum plate. The decreased flow length in MMC heat sinks can lead to significantly higher heat flux dissipation compared to conventional microchannel heat sinks at the same allowable pressure drop [7]. Significant effort has gone into predicting the optimal geometric and operational parameters for MMC heat sinks during single-phase operation; a range of experiments have also been conducted for single-phase flows in MMC heat sinks. The few studies that have focused on the two-phase operation of MMC heat sinks [8–10] have shown their viability as high-heat-flux removal devices.

#### **1.2** Objectives and Major Contributions

The main goals of the present work are to: (1) design and fabricate hierarchical MMC heat sinks with thin, high-aspect-ratio microchannels in a monolithic substrate along with the simulated heat source, (2) experimentally characterize the thermal and hydraulic performance of the MMC heat sinks during two-phase operation using a dielectric working fluid, (3) design and characterize a compact, highly discretized MMC heat sink, and (4) to investigate the two-phase flow morphology and local wall temperature measurements for high-aspect-ratio microchannels.

A  $3 \times 3$  array of heat sinks—each containing a bank of parallel, high-aspect-ratio (AR = 2.7 to 19.1), small hydraulic diameter (~20 to 60 µm) microchannels—are fabricated in a silicon chip over a 5 mm × 5 mm area. The intrachip microchannels are etched directly into the substrate of the heat source (also 5 mm × 5 mm) to limit conduction and contact resistances, allowing for higher heat flux removal. Fluid is delivered to the microchannels through a hierarchical manifold designed to provide uniform flow to each heat sink in the array throughout two-phase operation. Heat flux in excess of 1 kW/cm<sup>2</sup> are dissipated, demonstrating the ability of two-phase MMC heat sinks to dissipate high heat fluxes. The effects of fluid mass flux, channel depth, channel width, and aspect ratio are studied. Results are presented for the cooling of a uniform background heat flux and with simultaneous hotspot heating. A compact hierarchical manifold is designed and fabricated to deliver fluid to a  $9 \times 9$  array of heat sinks over a 5 mm × 5 mm area. The overall size

of the test device, including the manifold, is  $20 \times 20 \times 3 \text{ mm}^3$ . The device shows reliable performance and was tested up to 660 W/cm<sup>2</sup>. An experiment is designed to obtain simultaneous flow visualization and spatially resolved wall temperature measurements in a single manifold microchannel. These experiments provide valuable insights into the flow morphology in high-aspect-ratio MMCs during two-phase operation heat sinks and its effect on thermal performance.

#### **1.3** Organization of the Document

Chapter 1 contained background information pertaining to MMC heat sinks and provided the objectives and major contributions of the present work. Chapter 2 provides a review of the literature containing heat sink designs focused on high heat flux removal with an emphasis on MMC heat sink design and optimization and evaporative cooling strategies. Chapter 3 presents the fabrication of a novel manifold microchannel heat sink design and experimental characterization of the thermal and hydraulic performance during two-phase operation. Chapter 4 describes the testing of manifold microchannel heat sinks with different channel geometries during simultaneous uniform and hotspot heat flux dissipation. Chapter 5 presents the design and testing of a compact, highly discretized manifold microchannel array and compares the results to select data from Chapter 3. Chapter 6 presents a novel single-channel test facility used to visualize the two-phase flow morphology in the manifold microchannel and simultaneously measure local fin temperatures. Chapter 7 provides a summary of the conclusions from this work and the suggestions for future research.

Figure 1.1. Cross-sectional schematic diagrams of direct cooling using (a) a traditional microchannel heat sink and (b) a intrachip hierarchical manifold microchannel heat sink design.

### 2. LITERATURE REVIEW

#### 2.1 Single-Phase Microchannel Heat Sinks

Heat sinks containing deep, high-aspect-ratio microchannels provide high heat transfer coefficients and large area enhancement, which make them a candidate for high-heat-flux applications. In a pioneering study by Tuckerman and Pease [1], a 10 mm  $\times$  10 mm silicon microchannel heat sink with 50 µm wide and 300 µm deep channels was shown to dissipate 790 W/cm<sup>2</sup> at chip temperature rises of less than 71 °C above the fluid inlet temperature and pressure drops less than 186 kPa, using single-phase water as the working fluid. Single-phase microchannel heat sinks have been widely studied for electronics cooling applications [1], [2]. In general, increasing channel depth, decreasing channel width, and increasing fluid flow rate all allow for larger heat dissipation at a given chip temperature. However, there are practical limits to how deep and thin these channels can be made. Additionally, pressure drop along the length of the channels leads to intractably large pumping power requirements at the extremely small channel widths and high flow rates necessary to dissipate extreme heat fluxes on the order of 1000 W/cm<sup>2</sup>. Before you convert to PDF, carefully review our Formatting Checklist, then double check the

formatting of your entire document, page-by-page.

#### 2.2 **Two-Phase Microchannel Heat Sinks**

Two-phase evaporative cooling occurs when the fluid flowing through a heated channel reaches a temperature that causes bubble incipience to occur at the heated surface. Figure 2.1 shows the progression of boiling regimes at a given location along a microchannel as heat flux is increased [3]. At low heat fluxes, small bubbles nucleate at the walls and detach as the fluid moves past the wall; the bubbles remain isolated and are smaller than the width of the channel. As heat flux is increased, the bubble nucleation rate increases and the bubbles grow, resulting in coalescence; in microchannels, where the flow is confined in the transverse direction, the bubble grows preferentially along the channel length, producing vapor slugs that occupy nearly the entire channel cross-section. With a further increase in heat flux, the vapor slugs merge, causing a continuous vapor core surrounded by a liquid annulus to form. At high heat fluxes, the liquid film becomes thinner and the vapor core velocity increases as more liquid evaporates. Eventually, there

is not enough fluid to keep the wall wetted, resulting in dryout. Sudden temperature rises usually accompany dryout due to the relatively ineffective heat transfer performance of the vapor at the wall compared to the thin, liquid film in the other flow regimes.

Two-phase evaporative cooling in traditional microchannel heat sinks has been widely explored to improve surface temperature uniformity and heat dissipation efficiency relative to single-phase cooling [4]–[7]. Two-phase operation can also enable reductions in size, weight, and overall power consumption when compared to single-phase systems, which can lead to lower overall system costs.

#### 2.3 High-Heat Flux Cooling Technologies

For most working fluids, the latent heat of vaporization is orders of magnitude larger than the specific heat capacity; hence, evaporative cooling systems can operate at lower chip temperature rises and at reduced flow rates to dissipate the same amount of heat as single-phase systems. However, a significant fraction of the liquid must be evaporated before exiting the channel to realize the full potential of evaporative cooling. In most microchannel systems, intermittent dryout of the liquid film or flow instabilities causing premature critical heat flux (CHF) can lead to reduced performance well before a high exit quality can be reached. For flow boiling in microchannels, CHF has been found to increase with increasing channel wetted area, mass flux, and channel hydraulic diameter, as well as decreasing channel length [8]. Channel wetted area can be increased by decreasing channel pitch (*i.e.*, decreasing channel and fin widths to increase the number of channels) or increasing channel depth. Because pressure drop scales with  $L/d_{H^2}$  [9], decreasing the channel width while holding flow length constant results in prohibitive increases in pressure drop.

A variety of heat sink designs have been employed to dissipate larger heat fluxes by delaying CHF or reducing the pressure drop in two-phase operation compared to a conventional design with straight, parallel channels fed by a single header. These designs have implemented one or more of features such as vapor venting [10], pin-fins and interrupted channels of various shapes and configurations [10]–[12], wick structures to aid in thin film evaporation [13]–[15], microchannels with reentrant cavities and/or inlet restrictors [16], microgaps [17], arrays of jets [18]–[21], diverging channels [22], [23], microchannels fed with tapered manifolds [24], and stacked heat sinks [25]. Heat fluxes as high as 1127 W/cm<sup>2</sup> have been dissipated with dielectric

fluids [26] using a 10 mm  $\times$  20 mm copper heat sink that incorporated both flow boiling in microchannels and jet impingement. In this demonstration, the surface temperature at the highest heat flux exceeded 200 °C for a refrigerated fluid inlet temperature of -20 °C, which would present significant implementation challenges in electronics cooling applications.

#### 2.4 Single-Phase Manifold Microchannel Heat Sinks

Manifold microchannel heat sinks aim to increase maximum heat dissipation and decrease pressure drops at high flow rates and vapor fractions by distributing the flow through the microchannel heat sink in multiple parallel flow paths of decreased effective flow length. While channel length in traditional microchannel heat sinks is set by the length of the device being cooled, manifold microchannel heat sinks decouple flow length from the device size by delivering the fluid intermittently along the channel length, creating multiple parallel flow paths of decreased effective flow length. Figure 1.1(a) shows a traditional microchannel heat sink which contains a single inlet, a bank of microchannel heat sink design where the heated area is discretized into an array of multiple heat sinks, each with separate inlets and outlets that are fed in parallel.

Harpole and Eninger [27] developed a thermal model for single-phase flow in manifold microchannel heat sinks to optimize geometric parameters of a silicon heat exchanger using a water-methanol mixture as the working fluid. Their models predicted that steady-state heat fluxes greater than 1000 W/cm<sup>2</sup> were achievable with a fluid-to-chip temperature rise of less than 30 °C and a pressure drop of 101 kPa using high-aspect-ratio microchannels (channel widths from 7  $\mu$ m to 14  $\mu$ m and heights of 167  $\mu$ m). Most research on manifold microchannel heat sinks for electronics cooling has continued to focus on single-phase operation. A variety of researchers have conducted numerical studies to identify optimized geometries and operating conditions for both the fluid distribution manifold and microchannel heat sink [28]–[36]. These studies concluded that (1) at a fixed pumping power, there is an optimal channel height, channel width, and flow length for which thermal resistance is minimized, (2) the flow length should be minimized to minimize pressure drop for a fixed heat flux until manifold pressure drop governs the overall pressure drop at extremely short flow lengths, and (3) decreasing the channel width and increasing the flow rate both increase the heat transfer rate at the cost of increased pressure drop. While the

optimal geometric and operational parameters depend on the working fluid, desired heat flux, and allowable pumping power, these studies have shown that manifold microchannel heat sinks can increase heat dissipation without significantly increasing pressure drop when compared to traditional microchannels. For example, Ryu *et al.* [28] found that single-phase manifold microchannel heat sinks can dissipate >50% higher heat fluxes than a conventional microchannel heat sink at the same allowable pressure drop. Several experimental studies have confirmed that, in single-phase operation, manifold microchannel heat sinks can dissipate at sinks can dissipate heat fluxes at sinks can dissipate heat fluxes that sinks can dissipate heat fluxes that sinks can dissipate that,

Experimental studies have also shown that manifold microchannel heat sinks can dissipate high heat fluxes at moderate pressure drops [35], [40], [41]. The increased number of parallel flow paths in manifold microchannel heat sinks can lead to flow maldistribution between channels caused by uneven pressure drops in the manifold; this can cause significant performance reduction if not properly accounted for. Manifolds with constant cross-sectional area flow channels result in channels at the end of the manifold receiving a disproportionately large portion of the total flow [30], [42]. For the geometry and flow rates studied, Tang *et al.* [42] showed that the final four channels (out of 10 total) received 85 % of the total flow, with the final channel receiving over 35 %. Similarly, Escher *et al.* [30] showed that there is a 70 % difference in mass flow rate between the channel at the beginning of the manifold and the last channel. This amount of flow maldistribution can lead to significant chip temperature gradients and hotspots across the chip surface. Both studies found that flow maldistribution can be drastically reduced, but not eliminated, during single-phase operation by using tapered manifold flow channels.

#### 2.5 Two-Phase Manifold Microchannel Heat Sinks

moderate pressure drops [37]–[39].

Few studies have considered two-phase operation of manifold microchannel heat sinks. In one study, Baummer *et al.* [40] demonstrated dissipation of a heat flux of 300 W/cm<sup>2</sup> over a 1 cm<sup>2</sup> area with a chip temperature rise less than 50 °C using a manifold microchannel heat sink having 42  $\mu$ m wide and 483  $\mu$ m deep channels using HFE-7100 as the working fluid.

Cetegen [43] characterized high-aspect-ratio manifold microchannel heat sinks during twophase operation. Channel widths between 22  $\mu$ m and 60  $\mu$ m and heights between 406  $\mu$ m and 483  $\mu$ m (aspect ratios from 6.8 – 18.7) were fabricated in copper using Micro Deformation Technology. The heat sink covered a 1 cm<sup>2</sup> are and the manifold consisted of five rectangular fluid inlets; the flow length (dictated by the wall thickness of the manifold walls, was 450  $\mu$ m. Using R-245fa as the working fluid, heat fluxes up to 1.23 kW/cm<sup>2</sup> were dissipated over a 1 cm<sup>2</sup> area at a temperature rise of ~56 °C and pressure drop of 60 kPa.

#### 2.6 Hotspot and Non-Uniform Heat Flux Dissipation

In many practical electronics cooling applications, non-uniform heat flux generation is common, and must be accommodated by the heat sink design to limit temperature gradients in the chip. For example, Sharma *et al.* [32], [44] tested a manifold microchannel heat sink designed to dissipate non-uniform heat fluxes more effectively by utilizing varying channel geometries depending on spatial location on the chip. Background heat fluxes of 20 W/cm<sup>2</sup> with periodic 300 W/cm<sup>2</sup> hotspots evenly distributed across the chip surface were tested; chip temperature uniformity was maintained within a 15 °C spread using single-phase water as the working fluid. Lorenzi *et al.* [45] modelled and experimentally-tested pin fin heat sinks with variable pin sizes and pitches to dissipate a hotspot heat flux superimposed on a background heat fluxes, with the local substrate temperature at the hotspot remaining below the maximum substrate temperature, which occurred near the fluid outlet. Abdoli *et al.* [46] modelled a pin-fin heat sink with a hotspot heat flux of 2 kW/cm<sup>2</sup> superposed on a background heat flux of 1 kW/cm<sup>2</sup>. Using single-phase water as the working fluid, they predicted that an array of pin fins would yield spatial temperature uniformity with a maximum variation of less than 10 °C.

Recent heat sink designs have targeted simultaneous dissipation of a high, uniform die-level heat flux (>1,000 W/cm<sup>2</sup>) with significantly higher heat flux hotspots, representative of RF electronic devices. Technologies that have been evaluated include a GaN-on-diamond manifold microchannel heat sink [47], an embedded pin-fin heat sink with a manifold fluid distributor [48], a manifold microchannel heat sink with non-uniform channel height and shape [49], and a heat sink employing fluid impingement onto diamond-lined, silicon-carbide microchannels [50] Additional complexities arise in evaporative heat sink systems during non-uniform heating. For example, Ritchey *et al.* [13-14] found that non-uniform heating can lead to flow instabilities and flow maldistribution that induce premature critical heat flux during two-phase operation of microchannel heat sinks.

#### 2.7 Flow Visualization

Flow visualizations in traditional microchannels have provided key insights into the morphological changes that occur with different channel geometries, fluids and flow rates, and heat fluxes [53]. Due to drastic changes in the flow morphology with each of these variables, it is difficult to generally correlated performance in two-phase microchannel heat sinks with high accuracy. Rather, flow regime maps categorize discrete regions of similar flow morphology. For example, depending on the channel geometry and flow characteristics, flow regimes present in microchannel systems include bubbly, slug, and annular flows. Inside each regime, mechanistic models specific to the flow morphology yield improved predictive capabilities [54].

Flow visualizations of two-phase flows in manifold microchannels have not been widely reported. Cetegen [43] provided flow visualizations in a single manifold microchannel unit cell with a channel length of 3.875 mm and a channel height of 2.42 mm and channel widths of 70 µm and 225 µm using HFE-7100 as the working fluid. A heated copper block is used to provide a uniform wall heat flux boundary condition at the channel wall and a glass plate provides optical access from the other side. For the range of mass fluxes and heat fluxes tested, they observed flow regimes similar to traditional microchannels of the same dimensions; however, transitions between regimes occur radially from the inlet and vapor can be trapped in the stagnation regions for some operating conditions. Flow instabilities were also observed, which were attributed to nucleation suppression in the impingement region and vapor blockage at the outlet.

Figure 2.1. Description of boiling flow regimes [3].

## 3. A HIERARCHICAL MANIFOLD MICROCHANNEL HEAT SINK ARRAY FOR HIGH-HEAT-FLUX TWO-PHASE COOLING OF ELECTRONICS

This chapter focuses on designing, fabricating, and characterizing a hierarchical manifold microchannel array for intrachip evaporative cooling with a dielectric fluid. Extreme heat flux dissipation from electronic devices at low pressure drops and low chip temperatures has not been previously demonstrated using dielectric fluids. A  $3 \times 3$  array of heat sinks—each containing 50 parallel, high-aspect-ratio (AR = 2.7 to 19.1), small hydraulic diameter (~20 to 30 µm) microchannels—are fabricated in a single silicon chip over a 5 mm × 5 mm area. The intrachip microchannels are etched directly into the substrate of the heat source (also 5 mm × 5 mm) to limit conduction and contact resistances, allowing for higher heat flux removal. Fluid is delivered to the microchannels through a hierarchical manifold designed to provide uniform flow to each heat sink in the array throughout two-phase operation. The material in this chapter was presented at the Government Microcircuit Applications and Critical Technology Conference in 2015 and published in the proceedings [57]. It was later refined and published in the International Journal of Heat and Mass Transfer [58].

The work in Chapters 3, 4, and 5 are the result of collaboration with Doosan Back and Michael D. Sinanis, Ph.D. students in the School of Electrical and Computer Engineering at Purdue University. Mr. Sinanis designed the etching recipes, etched two of the channel wafers and plenum wafers, and diced the wafers. Mr. Back designed the heater/sensor masks, performed all of the fabrication steps for the heater/sensors, and wire-bonded the samples. Mr. Drummond designed the channels and manifolds, fabricated the remaining channels and manifold layers (lithography and etching), calibrated the device heaters and sensors, fabricated and assembled all thermal/hydraulic characterization facilities, ran the thermal-hydraulic experiments, and processed the data. The text sections 5.1.2 and 5.3 were written Mr. Back but are included in this thesis for continuity.

#### **3.1** Test Vehicle Design and Fabrication

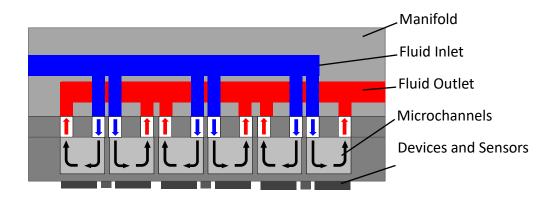

#### 3.1.1 Hierarchical Manifold Microchannel Concept

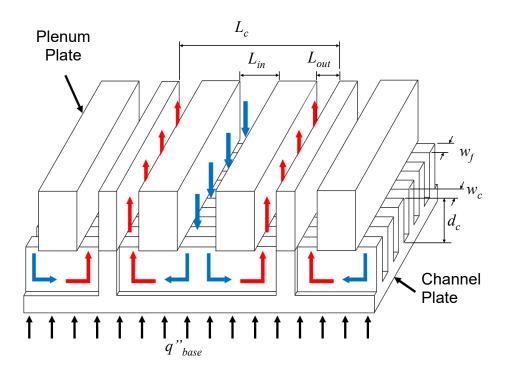

Manifold microchannel heat sinks are designed to distribute fluid through multiple inlets and outlets along the heat sink so that the flow length through any single set of microchannels is significantly reduced. This concept is extended to achieve greatly improved performance in the current work by using a hierarchical manifold to feed an array of intrachip microchannel heat sinks featuring high-aspect-ratio channels. Direct liquid cooling minimizes conduction resistances and eliminates contact resistances that result from approaches relying on separately attached heat sinks. Figure 3.1 shows a schematic diagram of the hierarchical manifold microchannel heat sink array concept used in the current work. The silicon microchannel plate contains a 2D array of microchannel heat sinks, with each heat sink containing 50 microchannels in parallel, as well as resistance heaters and thermometers, as discussed later. The manifold routes a single flow inlet into the individual inlets to the microchannel heat sinks (blue regions in Figure 3.1). Fluid from the manifold arrives normal to each heat sink through a rectangular inlet centered along the length of each microchannel. Within each microchannel, the flow impinges on the channel base, splits in two directions, travels along the remaining channel flow length and exits into the manifold. Within the manifold, the flow from the array of microchannel heatsinks is combined into a single outlet stream (red regions in Figure 3.1).

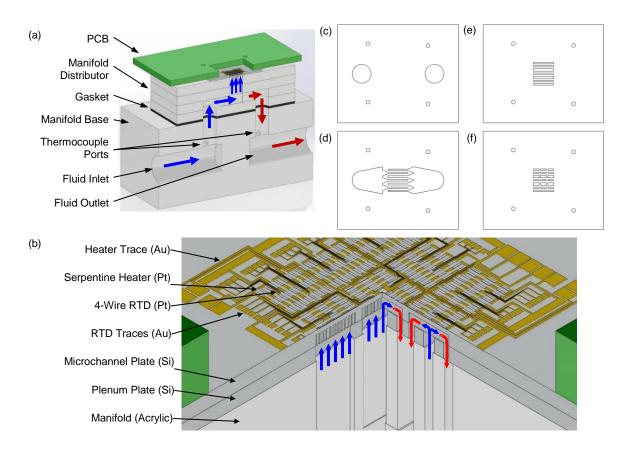

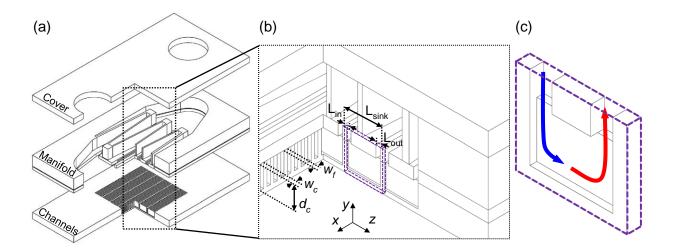

#### 3.1.2 Test Vehicle Design

A thermal test vehicle, with all coolant distribution components heterogeneously integrated, is fabricated to demonstrate the thermal and hydraulic performance of the microchannel cooling approach (Figure 3.2(a)). The system consists of a manifold base, manifold distributor, plenum interface plate, microchannel plate, and printed circuit board (PCB). The base serves as an interface between the flow loop and the hierarchical manifold distributor and contains ports for inlet and outlet pressure and temperature measurements. The manifold distributor splits the single coolant inlet into 9 parallel flow streams that enter a  $3 \times 3$  array of microchannel heat sinks into a single coolant outlet (Figure 3.2(b)). Each heat sink cools a footprint area of 1667  $\mu$ m × 1667  $\mu$ m, with 50 parallel channels occupying a central area of 1500  $\mu$ m × 1500  $\mu$ m; the flow