Purdue University

Purdue e-Pubs

**Open Access Theses**

Theses and Dissertations

12-2017

# Analysis and Mitigation of Common-mode Behavior in Hybrid Vehicle Applications

Michael R. Hayashi Purdue University

Follow this and additional works at: https://docs.lib.purdue.edu/open\_access\_theses

## **Recommended Citation**

Hayashi, Michael R., "Analysis and Mitigation of Common-mode Behavior in Hybrid Vehicle Applications" (2017). *Open Access Theses*. 1284. https://docs.lib.purdue.edu/open\_access\_theses/1284

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

# ANALYSIS AND MITIGATION OF COMMON-MODE BEHAVIOR IN HYBRID VEHICLE APPLICATIONS

A Thesis

Submitted to the Faculty

of

Purdue University

by

Michael R. Hayashi

In Partial Fulfillment of the

Requirements for the Degree

of

Master of Science in Electrical and Computer Engineering

December 2017

Purdue University

West Lafayette, Indiana

# THE PURDUE UNIVERSITY GRADUATE SCHOOL STATEMENT OF THESIS APPROVAL

Dr. Steven Pekarek, Chair School of Electrical and Computer Engineering Dr. Oleg Wasynczuk School of Electrical and Computer Engineering Dr. Scott Sudhoff School of Electrical and Computer Engineering Dr. Saeed Mohammadi School of Electrical and Computer Engineering

# Approved by:

Dr. Michael Capano

Head of the School Graduate Program

To my parents, Bruce and Lorena, whose encouragement gave rise to this thesis

## ACKNOWLEDGMENTS

The author expressed his gratitude towards Prof. Steven Pekarek for his continued guidance in this thesis and all supporting work. Prof. Oleg Wasynczuk, Prof. Scott Sudhoff, and Prof. Saeed Mohammadi are also recognized for their service as part of the author's graduate committee.

This research has been supported by John Deere Electronic Solutions through the Hoosier Heavy Hybrid Center of Excellence by the United States Department of Energy Graduate Automotive Technology Education program. Dr. Long Wu, Dr. Sumit Dutta, and Mr. Guozhen Zhou at John Deere merit additional recognition for their extended technical discussions of this work.

# TABLE OF CONTENTS

|    |                                           |         |                                      | Page |

|----|-------------------------------------------|---------|--------------------------------------|------|

| LI | ST O                                      | F TAB   | LES                                  | vii  |

| LI | ST O                                      | F FIGU  | JRES                                 | viii |

| SY | YMB(                                      | DLS .   |                                      | xi   |

| AI | BBRE                                      | EVIATI  | ONS                                  | xiii |

| Gl | LOSS                                      | ARY .   |                                      | XV   |

| AI | BSTR                                      | ACT     |                                      | xvii |

| 1  | INT                                       | RODU    | CTION                                | 1    |

|    | 1.1                                       | Litera  | ture Review                          | 2    |

|    | 1.2                                       | Basis   | of Modeling Approach                 | 4    |

| 2  | SYS                                       | TEM C   | DF INTEREST                          | 6    |

|    | 2.1                                       | Hybrid  | d Vehicle Drive Architecture         | 6    |

|    | 2.2                                       | System  | n Components                         | 6    |

|    |                                           | 2.2.1   | Three-phase Machine Model            | 8    |

|    |                                           | 2.2.2   | Three-phase Cable Model              | 16   |

|    |                                           | 2.2.3   | DC Bus Model                         | 21   |

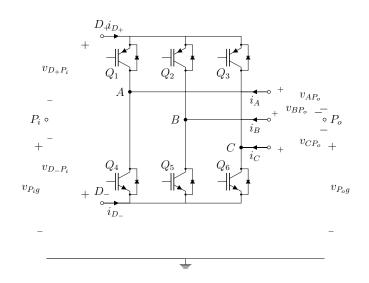

|    |                                           | 2.2.4   | Active Rectifier and Inverter Model  | 25   |

|    |                                           | 2.2.5   | Buck Converter Model                 | 26   |

|    |                                           | 2.2.6   | Electronic Brake Model               | 29   |

|    | 2.3                                       | Circui  | t Block Interconnection              | 34   |

| 3  | CON                                       | /IPARIS | SON OF MODELS                        | 40   |

|    | 3.1 Source-fed Inverter and Brake Chopper |         |                                      | 40   |

|    |                                           | 3.1.1   | Mixed-mode Model                     | 40   |

|    |                                           | 3.1.2   | Common-mode Equivalent Circuit Model | 41   |

|    |                                           | 3.1.3   | Findings from Simulation             | 41   |

# Page

vi

|    | 3.2                                                  | Hybri                              | vbrid Drive Architecture                                                                                                      |    |  |

|----|------------------------------------------------------|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|----|--|

|    |                                                      | 3.2.1                              | Mixed-mode Model                                                                                                              | 46 |  |

|    |                                                      | 3.2.2                              | Common-mode Equivalent Circuit Model                                                                                          | 47 |  |

|    |                                                      | 3.2.3                              | Findings from Simulation                                                                                                      | 48 |  |

| 4  | MIT                                                  | IGATI                              | ON OF COMMON-MODE VOLTAGES                                                                                                    | 55 |  |

|    | 4.1                                                  | Altern                             | native Switching Strategies                                                                                                   | 55 |  |

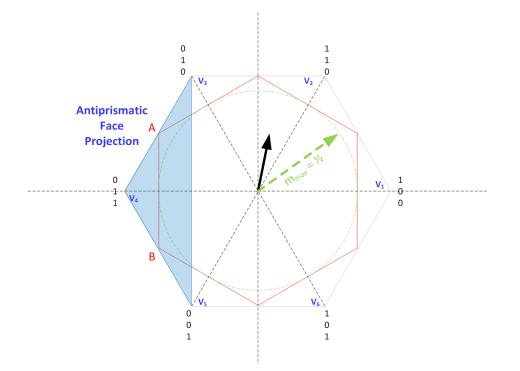

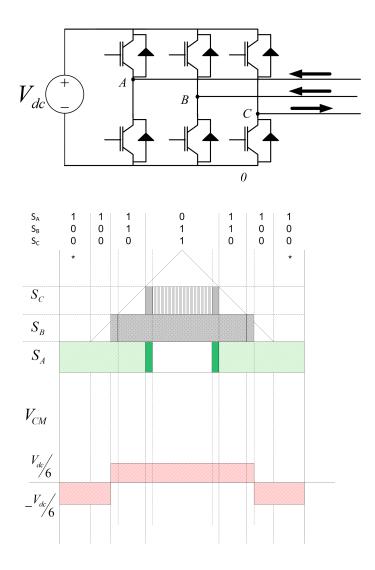

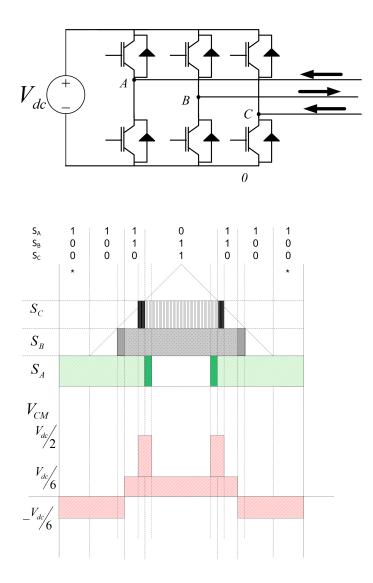

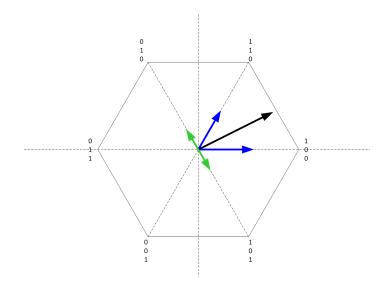

|    |                                                      | 4.1.1                              | First Space Vector Modulation (1SVPWM) and Other Switching Strategies using Active Switching Vectors                          | 56 |  |

|    |                                                      | 4.1.2                              | Three-dimensional Space Vector Modulation (3DSVPWM) $% \mathcal{A} = \mathcal{A} = \mathcal{A} + \mathcal{A} + \mathcal{A}$ . | 63 |  |

|    |                                                      | 4.1.3                              | Interleaved Sine-Triangle Modulation with Third Harmonic In-<br>jection (IST3PWM)                                             | 69 |  |

|    | 4.2 Switching Patterns to Address Non-ideal Behavior |                                    |                                                                                                                               | 70 |  |

|    | 4.2.1 Dead Time Considerations                       |                                    |                                                                                                                               |    |  |

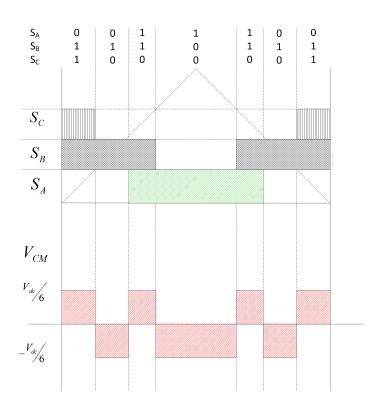

|    |                                                      | 4.2.2                              | Proper Switching Period Sequence                                                                                              | 76 |  |

|    |                                                      | 4.2.3                              | Sector Transitions                                                                                                            | 80 |  |

|    | 4.3                                                  | 4.3 Implementing Switching Changes |                                                                                                                               |    |  |

|    | 4.4                                                  | Hardw                              | vare Changes                                                                                                                  | 84 |  |

| 5  | CONCLUSION                                           |                                    |                                                                                                                               |    |  |

| RI | EFEF                                                 | RENCE                              | S                                                                                                                             | 86 |  |

## LIST OF TABLES

| Tabl | le                                                                 | Page |

|------|--------------------------------------------------------------------|------|

| 4.1  | Modulation Index Components of Three-dimensional Switching Vectors | 64   |

| 4.2  | Summary of Alternative Space Vector Modulation Performance         | 65   |

## LIST OF FIGURES

| Figu | re                                                                                          | Page |

|------|---------------------------------------------------------------------------------------------|------|

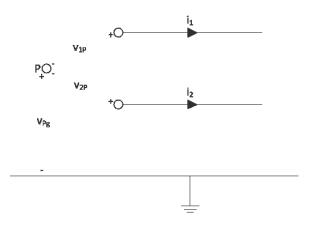

| 1.1  | Diagram for Common-mode and Differential-Mode Definitions                                   | 4    |

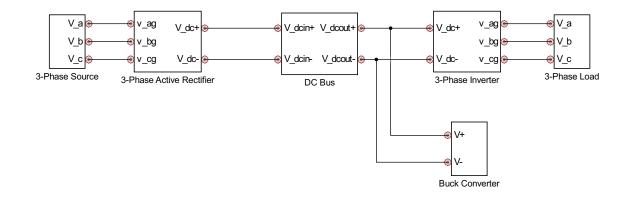

| 2.1  | Block Diagram of Prototypical Hybrid Vehicle Drive Architecture $\ . \ .$                   | 6    |

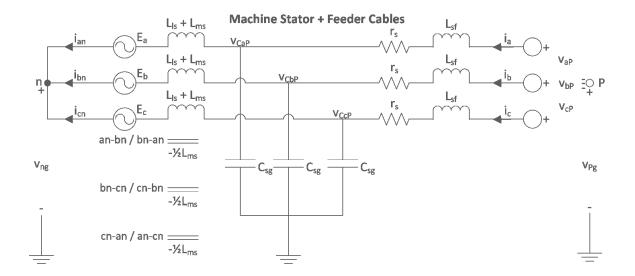

| 2.2  | Akagi Model of Three-phase Machine Stator and Attached Feeder Cables                        | 8    |

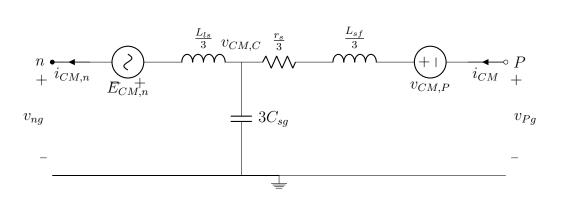

| 2.3  | CM Equivalent Circuit of Akagi's 3-phase Machine Stator and Feeder Ca-<br>bles              | 10   |

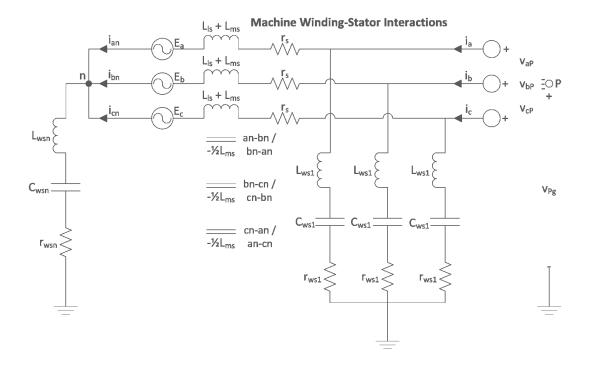

| 2.4  | Chen and Lipo Model of Three-phase Machine Winding-Stator Interactions                      | 11   |

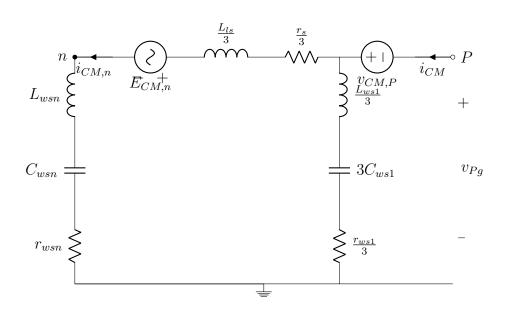

| 2.5  | CM Equivalent Circuit of Chen and Lipo's 3-phase Machine Winding-<br>Stator Interactions    | 13   |

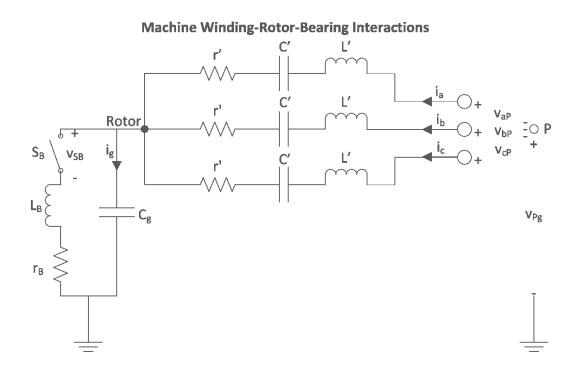

| 2.6  | Chen and Lipo Model of Three-phase Machine Winding-Rotor-Bearing<br>Interactions            | 14   |

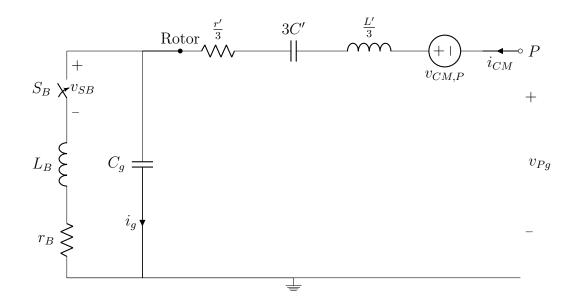

| 2.7  | CM Equivalent Circuit of Chen and Lipo's 3-phase Machine Winding-Rotor-Bearing Interactions | 16   |

| 2.8  | Series Impedance Model of Three-phase Cables                                                | 17   |

| 2.9  | CM Equivalent Circuit for Series Impedance Model of Three-phase Cables                      | 18   |

| 2.10 | Series Impedance and Shunt Admittance Model of Three-phase Cables                           | 19   |

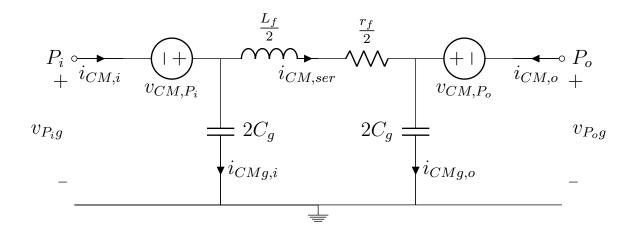

| 2.11 | CM Equivalent Circuit for $Z_{ser}$ and $Y_{shu}$ Model of Three-phase Cables .             | 21   |

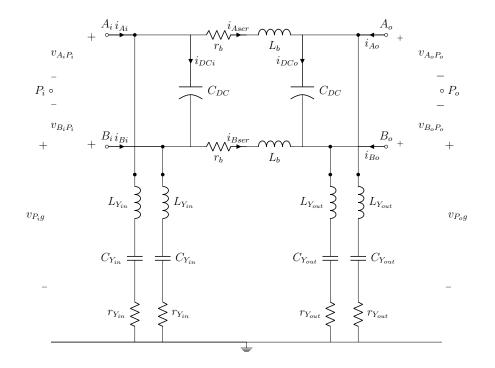

| 2.12 | Mixed-mode Model of DC Bus                                                                  | 22   |

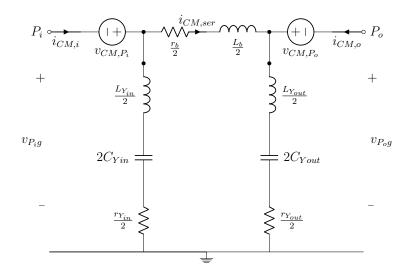

| 2.13 | Common-mode Equivalent Circuit of DC Bus                                                    | 24   |

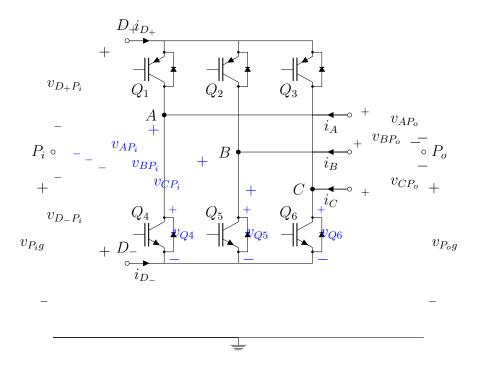

| 2.14 | Determining Common-mode Voltage Sources from Power Electronics .                            | 25   |

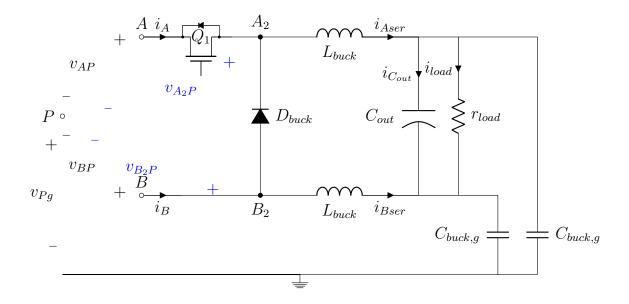

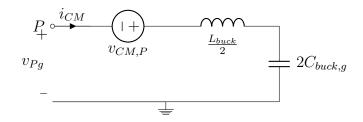

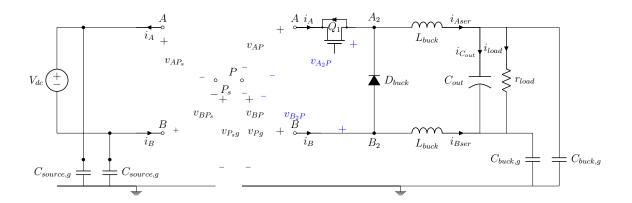

| 2.15 | Mixed-mode Model of Balanced Buck Converter                                                 | 27   |

| 2.16 | Common-mode Equivalent Circuit of Balanced Buck Converter                                   | 29   |

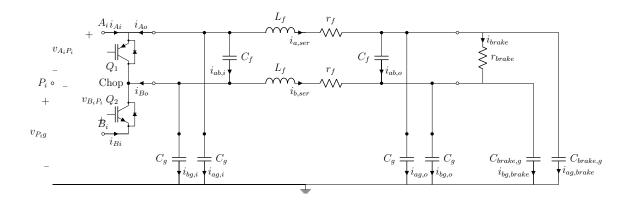

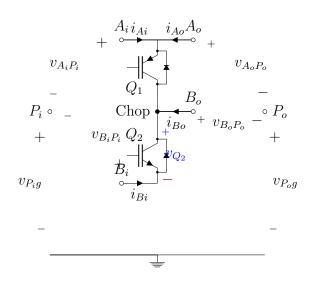

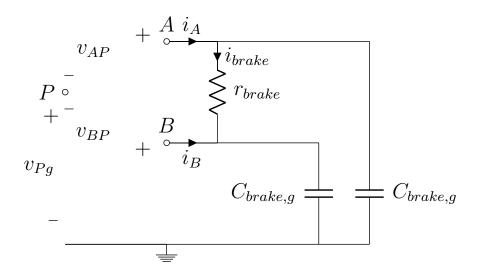

| 2.17 | Electronic Brake Model Consisting of Brake Chopper, Single-phase Cable, and Brake Resistor  | 29   |

| 2.18 | Voltage Determination from Mixed-mode Model of a Brake Chopper .                            | 30   |

| 2.19 | Series Impedance and Shunt Capacitance Model of Single-phase Cables                         | 31   |

| Figu | re                                                                                                 | Page |

|------|----------------------------------------------------------------------------------------------------|------|

| 2.20 | CM Equivalent Circuit for $Z_{ser}$ and $C_g$ Model of Single-phase Cables $% \mathcal{L}_{ser}$ . | 33   |

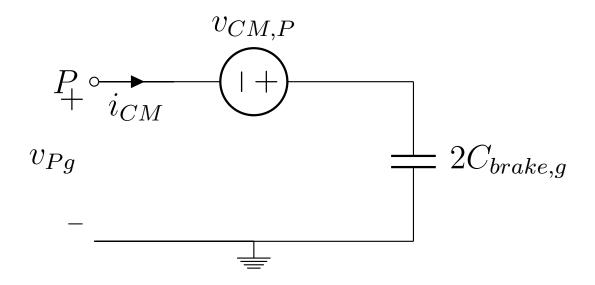

| 2.21 | Mixed-mode Model of a Brake Resistor                                                               | 34   |

| 2.22 | Common-mode Equivalent Circuit of a Brake Resistor                                                 | 35   |

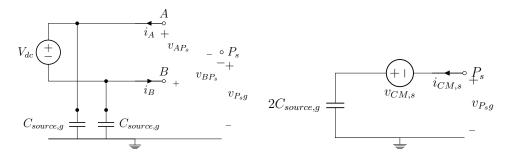

| 2.23 | Common-mode Equivalent Circuit Transformation for Simple DC Source                                 | 35   |

| 2.24 | Mixed-mode Model of DC Source Feeding a Balanced Buck Converter .                                  | 36   |

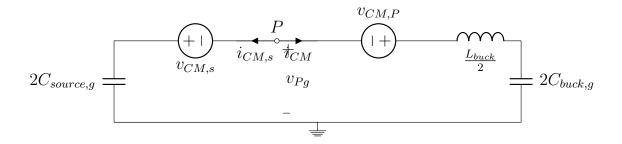

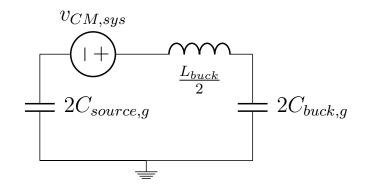

| 2.25 | CM Equivalent Circuit of DC Source Block and Buck Converter Block                                  | 37   |

| 2.26 | CM Equivalent Circuit of DC-DC Converter System                                                    | 37   |

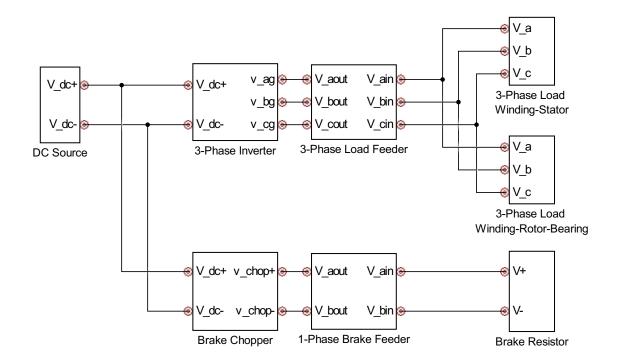

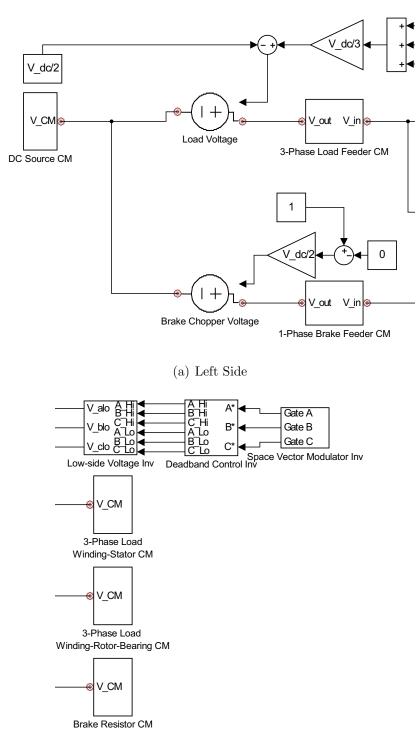

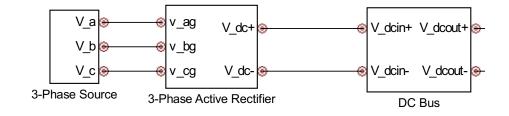

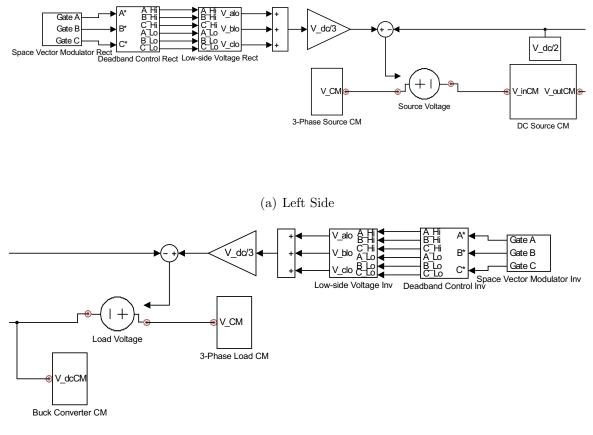

| 3.1  | Top-level Mixed-mode Model in ASMG                                                                 | 40   |

| 3.2  | Top-level Common-mode Equivalent Model in ASMG                                                     | 42   |

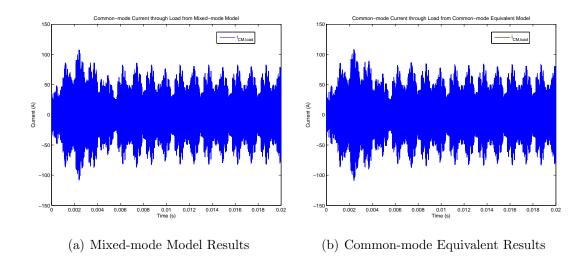

| 3.3  | Load Machine CM Current of System without Rectifier                                                | 43   |

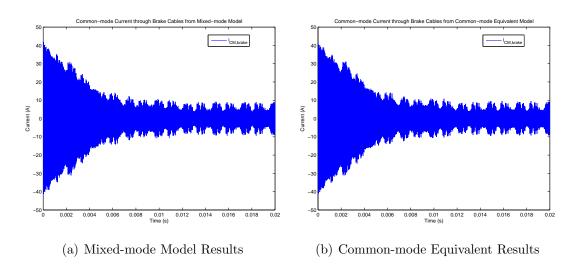

| 3.4  | Brake Cables CM Current of System without Rectifier                                                | 43   |

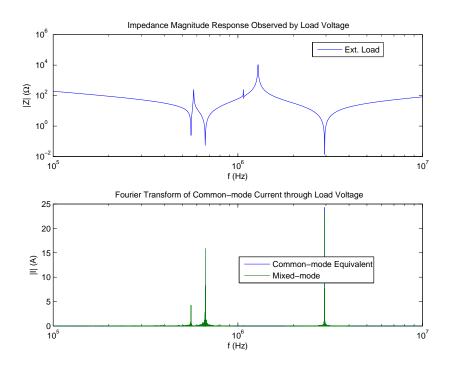

| 3.5  | CM Load Current in Frequency Domain for System without Rectifier .                                 | 44   |

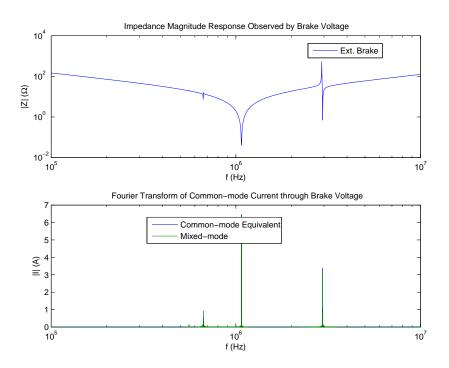

| 3.6  | CM Brake Current in Frequency Domain for System without Rectifier .                                | 45   |

| 3.7  | Top-level Mixed-mode Model in ASMG                                                                 | 46   |

| 3.8  | Top-level Common-mode Equivalent Model in ASMG                                                     | 47   |

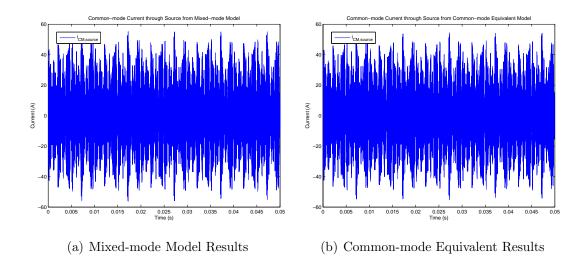

| 3.9  | Source Machine Common-mode Current of Drive System                                                 | 49   |

| 3.10 | Load Machine Common-mode Current of Drive System                                                   | 49   |

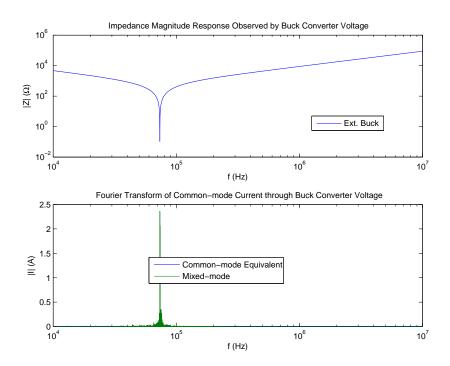

| 3.11 | Buck Converter Common-mode Current of Drive System                                                 | 50   |

| 3.12 | CM Source Current in Frequency Domain for Drive System                                             | 51   |

| 3.13 | CM Load Current in Frequency Domain for Drive System                                               | 52   |

| 3.14 | CM Buck Converter Current in Frequency Domain for Drive System                                     | 53   |

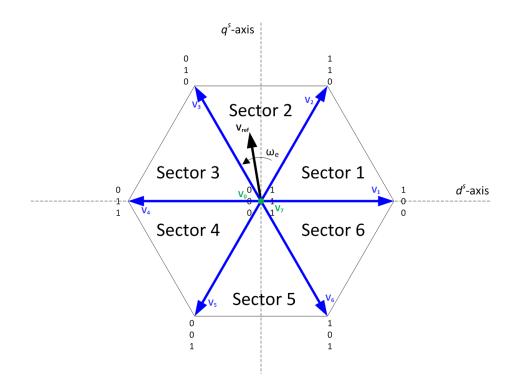

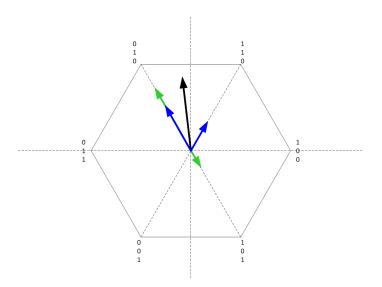

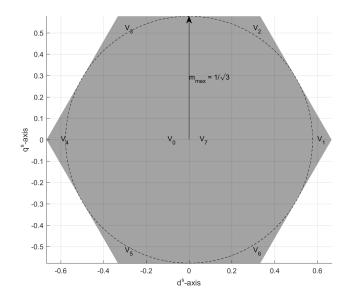

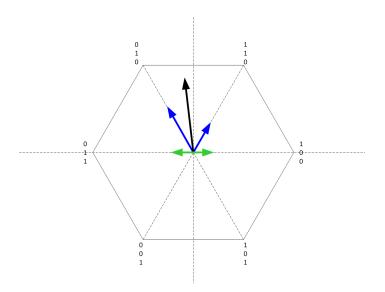

| 4.1  | Switching Vector and Hexagonal Sector Definitions in Traditional SVPWM                             | 57   |

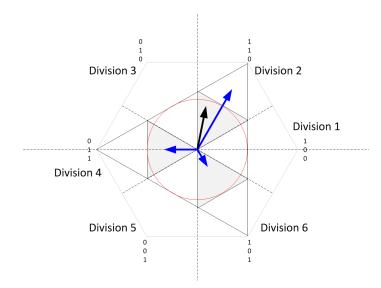

| 4.2  | Synthesizing a Voltage Vector in Division 2 with 3<br>AVM                                          | 58   |

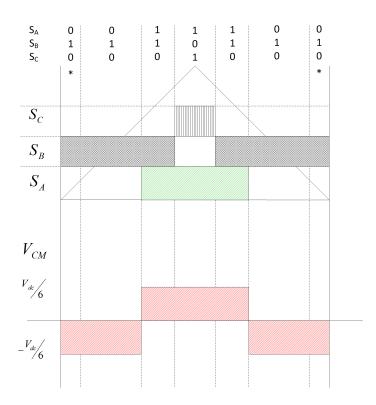

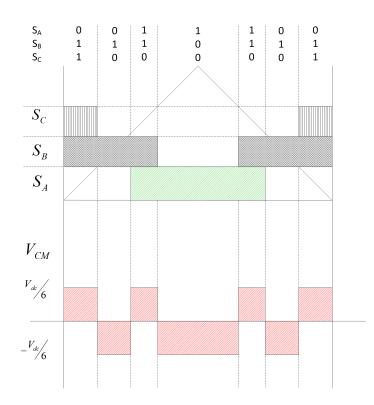

| 4.3  | Switch Timing in Division 2 with 3AVM                                                              | 58   |

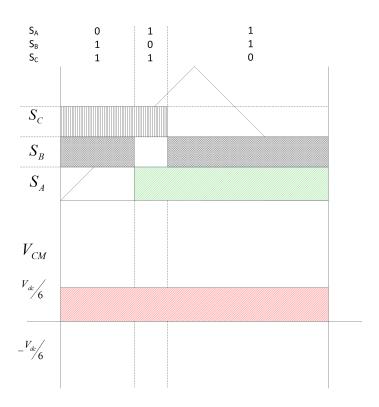

| 4.4  | Synthesizing a Voltage Vector in Sector 2 with AZVC-1                                              | 59   |

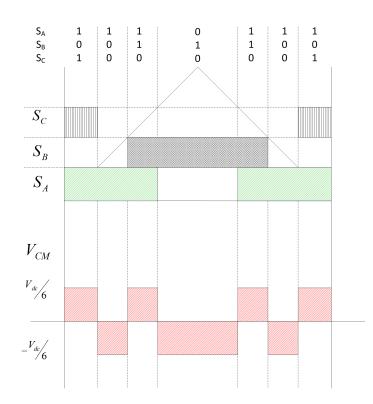

| 4.5  | Switch Timing in Sector 2 with AZVC-1                                                              | 59   |

| 4.6  | Switch Timing in Sector 2 with 1SVPWM (AZVC-2)                                                     | 60   |

| Figu | re                                                                                   | Page |

|------|--------------------------------------------------------------------------------------|------|

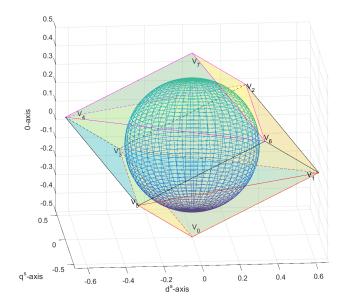

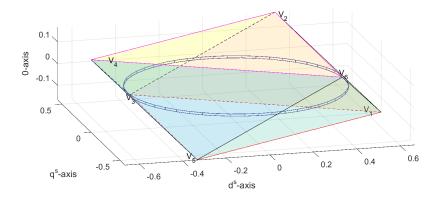

| 4.7  | Gyroelongated Triangular Bipyramid Region of Space Vector Modulation<br>in QD0-Space | 66   |

| 4.8  | Projection of Three-dimensional Space Vector Modulation onto QD-plane                | 66   |

| 4.9  | Active Vectors in Three-dimensional Space Vector Modulation                          | 67   |

| 4.10 | QD-plane Slice of Three-dimensional Space Vector Modulation                          | 68   |

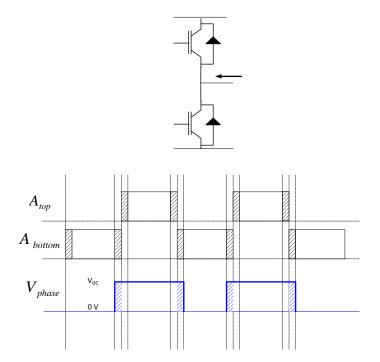

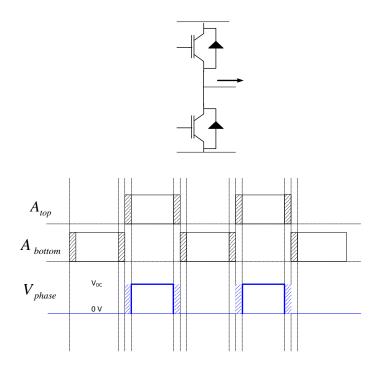

| 4.11 | Switching Waveforms with Current Out of the Phase Terminal                           | 71   |

| 4.12 | Switching Waveforms with Current Into the Phase Terminal                             | 72   |

| 4.13 | Dead Time Problem Avoided for AZVC-1 Sector 2 Case                                   | 73   |

| 4.14 | Dead Time Problem Encountered for AZVC-1 Sector 2 Case                               | 74   |

| 4.15 | Synthesizing a Voltage Vector in Sector 1 with 1SVPWM                                | 76   |

| 4.16 | Switch Timing in Sector 1 with 1SVPWM                                                | 77   |

| 4.17 | Synthesizing a Voltage Vector in Sector 2 with 1SVPWM                                | 79   |

| 4.18 | Switch Timing in Sector 2 with 1SVPWM                                                | 79   |

| 4.19 | Standard Three-leg Inverter                                                          | 83   |

## SYMBOLS

- P geometric point

- K number of lines

- r radius

- S switch state

- p Heaviside operator

- v voltage

- i current

- $\lambda$  flux linkage

- q charge

- E back electromotive force

- k coupling coefficient

- Z impedance

- *r* resistance

- L inductance

- X reactance

- Y admittance

- g conductance

- C capacitance

- B susceptance

- T period or temporal duration

- d duty cycle

- m modulation index

- f ordinary frequency

- $\omega$  angular frequency or angular speed

- $T_e$  electromagnetic torque

## ABBREVIATIONS

| 1SVPWM                    | first space vector modulation                                   |

|---------------------------|-----------------------------------------------------------------|

| 3AVM                      | three active vector modulation                                  |

| 3DSVPWM                   | three-dimensional space vector modulation                       |

| AC                        | alternating current                                             |

| ASMG                      | Automated State Model Generator                                 |

| AZVC                      | active zero vector control                                      |

| CM                        | common mode                                                     |

| CMEC                      | common-mode equivalent circuit                                  |

| DC                        | direct current                                                  |

| DM                        | differential mode                                               |

| $\mathrm{DM}/\mathrm{CM}$ | mixed mode                                                      |

| EMF                       | electromotive force                                             |

| EMTP                      | electromagnetic transients program                              |

| ESR                       | equivalent series resistance                                    |

| ESL                       | equivalent series inductance                                    |

| FB10                      | Full-bridge converter with ten switches                         |

| H6                        | H-bridge converter with six switches                            |

| HERIC                     | Highly Efficient and Reliable Inverter Concept                  |

| IST3PWM                   | interleaved sine-triangle modulation with third-harmonic injec- |

|                           | tion                                                            |

| KCL                       | Kirchhoff's Current Law                                         |

| KVL                       | Kirchhoff's Voltage Law                                         |

| MATLAB                    | Matrix laboratory                                               |

| PCKA                      | PC Krause & Associates                                          |

|                           |                                                                 |

| PWM    | pulse width modulation                                 |

|--------|--------------------------------------------------------|

| RMS    | root-mean-square                                       |

| ST3PWM | sine-triangle modulation with third harmonic injection |

| STPWM  | sine-triangle modulation                               |

| SVPWM  | space vector modulation                                |

| WBG    | wide bandgap                                           |

# GLOSSARY

| Admittance          | reciprocal of impedance with real part conductance and imaginary $% \left( {{{\left[ {{\left[ {{\left[ {\left[ {\left[ {\left[ {\left[ {\left[ {\left[$ |  |  |  |  |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                     | part susceptance, SI unit of siemans (S)                                                                                                                |  |  |  |  |

| Alternating Current | periodically varying circuit quantities associated with symmetric                                                                                       |  |  |  |  |

|                     | flow in both directions; in regards to a system, one intended to                                                                                        |  |  |  |  |

|                     | carry power through AC quantities in the differential mode                                                                                              |  |  |  |  |

| Antiprism           | a polyhedron composed of two parallel, identical polygons rotated                                                                                       |  |  |  |  |

|                     | with respect with one another such that the vertices of each poly-                                                                                      |  |  |  |  |

|                     | gon are connected by triangular faces                                                                                                                   |  |  |  |  |

| Bipyramid           | a polyhedron formed by joining two, identical pyramids at their                                                                                         |  |  |  |  |

|                     | bases                                                                                                                                                   |  |  |  |  |

| Common Mode         | circuit mode associated with effort across and flow between a set                                                                                       |  |  |  |  |

|                     | of conductors and an arbitrary return path usually including some                                                                                       |  |  |  |  |

|                     | part of the system identified as ground                                                                                                                 |  |  |  |  |

| Current             | flow of electric charge past a cross-sectional area, SI unit of am-                                                                                     |  |  |  |  |

|                     | peres $(A)$                                                                                                                                             |  |  |  |  |

| Differential Mode   | circuit mode associated with effort across and flow between each                                                                                        |  |  |  |  |

|                     | conductor in a pair usually comprising the typical operation of                                                                                         |  |  |  |  |

|                     | the system                                                                                                                                              |  |  |  |  |

| Direct Current      | constant circuit quantities associated with flow in one direction;                                                                                      |  |  |  |  |

|                     | in regards to a system or bus, one intended to carry DC power in                                                                                        |  |  |  |  |

|                     | the differential mode                                                                                                                                   |  |  |  |  |

| Gyroelongated       | describing a polyhedron that has added axial height by the inser-                                                                                       |  |  |  |  |

|                     | tion of an antiprism into the middle                                                                                                                    |  |  |  |  |

H-bridge a common type of full-wave, single-phase active rectifier and topology typically drawn such that there are four electronic switches, one on each of the vertical segments of a capital letter "H", with the AC source or load drawn on the horizontal segment

| Impedance | complex ratio of AC voltage to AC current $\left(Z = \frac{\tilde{V}}{\tilde{I}}\right)$ that includes |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | amplitude and phase information; the real part is resistance, and                                      |

|           | the imaginary part is reactance, SI unit of ohms $(\Omega)$                                            |

- Mixed Mode also called fully detailed in regards to models or phase quantity in regards to circuit quantities, a combination of the differential mode and common mode

- Root-mean-square an operation associated with the effective value of a sinusoidal quantity that squares all values over a period, averages them together, and takes the square root of the result

- Voltage electrical potential difference between two points that gives electric potential energy per unit charge, SI unit of volts (V)

### ABSTRACT

Hayashi, Michael R. MSECE, Purdue University, December 2017. Analysis and Mitigation of Common-mode Behavior in Hybrid Vehicle Applications. Major Professor: Steven D. Pekarek.

Modeling techniques to predict common-mode (CM) current in an electric drive intended for a hybrid vehicle are examined. A particular focus is on the derivation of a common-mode equivalent circuit (CMEC) in which machines, cables, and passives are represented by their passive coupling paths to ground and power electronic devices are replaced by equivalent voltage sources. The interconnection of components is accomplished using a judicious selection of a reference point used to define CM voltage.

Circuit-based simulation results are presented for a system consisting of a permanent magnet generator coupled to an active rectifier that is providing power to an inverter/permanent magnet motor. The simulation results are compared to those obtained from a detailed system model in which the switching behavior of all semiconductor devices is represented. It is shown that the CM current predicted using the CM equivalent circuit closely matches that obtained using the detailed system model.

Finally, several switching strategies are presented for three-phase, three-leg converters with the intent of reducing the CM voltage at a single or multitude of frequencies. The CM equivalent circuit is used to explore the impact that these strategies have on CM current in modern power electronics systems as well as future systems that will be dominated by wide-bandgap semiconductor devices.

## 1. INTRODUCTION

The advent of fast-switching power electronic devices has led to unintended voltages and currents that are often referred to as common-mode (CM) issues. Large commonmode voltages can lead to insulation breakdown and drive large common-mode currents. Common-mode currents flow through parasitic paths in the electrical system and often negatively affect electromagnetic compatibility, i.e., false triggering of fault detection systems, and motor bearing wear-out. [1] [2] With these considerations in mind, more powerful modeling approaches are sought to predict and eventually mitigate common-mode behavior.

The modeling of common-mode systems to date has mostly been confined to two approaches. The first involves adding parasitic elements to the differential-mode (DM) circuit used for intended operation. [3] [4] By simulating the circuit with parasitics included, mixed-mode (DM/CM) behavior may be predicted, including inter-mode coupling effects. This approach has the disadvantage of needing significant computing power in order to simulate the stiff system dynamics. The second is the establishment of common-mode equivalent circuits by characterizing paths through which common-mode current flows and establishing sources that represent power electronics or imbalance. [5] [6] [7] While the computing power required to model this smaller linear circuit is reduced, there had been few attempts to create a process to form, connect, and apply these CM equivalent circuits until recently. In the writings of Brovont and Pekarek [8] [9], an approach was derived to transform the mixed-mode circuits into common-mode circuits. In this thesis, this approach is applied to a drive system that includes two machines and their drive circuits.

### 1.1 Literature Review

Currents flowing through the shafts of machines were first identified in the 1920's, and the modern rise of power electronics in inverters has led to heightened scrutiny of their effects on bearings. [10] Methods to predict and measure shaft currents have been presented by several researchers. [11] [3] [4] In general, the modeling approach used to study shaft currents in this thesis is based on the work of Chen, Lipo, and Fitzgerald. [11]

The CM equivalent circuit approach presented follows the work of Brovont and Pekarek. [8] [9] Previous attempts to create common-mode equivalent circuits involved fitting empirical impedance data to equivalent resistances, inductances, and capacitances as presented by Naik, Nondahl, Melfi, Schiferl, and Wang. [3] While such efforts may produce accurate models, they are not readily adaptable as modifications are made to the system nor do they give intuition based on machine physics. In order to construct common-mode equivalent circuits for the variety of circuit blocks that might be encountered in a hybrid vehicle drive system, the Brovont and Pekarek modeling method is detailed after this literature review.

Hardware solutions to common-mode effects include filters such as the one designed by Rendusara and Enjeti made to handle the effects of long motor cables. [12] More comprehensive solutions include modifying the inverter topology and accepting additional computational complexity and switching losses. One example uses a four-leg inverter for active CM voltage control and incorporating a second-order filter as presented by Julian, Oriti, and Lipo [13]. Another uses an active common-noise canceler (ACC) in which a fourth phase leg responds to noise on three-phase cables by injecting a signal into a four-winding transformer as Ogasawara, Ayano, and Akagi detailed. [6] By combining multi-level converters with many filtering stages, Parreiras, Prado, and Filho produced a mining pump drive that severely curtails common-mode effects at the cost of many added components. [7] One of the most drastic solutions proposed involved constructing open-end machines, connecting a second three-leg drive, and using clamp-on ferrites as Narasimhan, Tewari, Severson, Baranwal, and Mohan suggested. [14]

As might be anticipated, common-mode behavior can also affect DC systems that are supplied by power electronics converters attached to the DC bus. Common-mode chokes and multi-stage filters remain an option for handling common-mode behavior. Buck converters can introduce a complementary switch and balance inductance to make the circuit block symmetric and reduce the transmission of common-mode current. [15] Virtually every other form of switched mode power supply admits a balanced counterpart that prevents the generation of large common-mode voltages. [16] Numerous other DC-DC converter topologies such as H6 (H-bridge with six switches) and the Highly Efficient and Reliable Inverter Concept (HERIC) are used to construct singlephase inverters and active rectifiers that minimize common-mode behavior compared to the conventional H-bridge with four switches. [17] While the space of single-phase power electronic converters may seem distinct from three-phase converters, novel ideas such as the Full-bridge with ten switches (FB10) topology can result from the hybridization of single-phase and three-phase topologies meant to reduce common-mode behavior. [18] Despite the advantages of modified power converter topologies, they tend to be rather scarce outside of academic settings due to their novelty and small selection of commercial options available. For these reasons, no further attention is paid to this area of research.

When addressing common-mode behavior in existing products, modifications to software are generally preferred to hardware changes due to the relative simplicity of implementation without affecting the supply chain or manufacturing processes. To that end, alterations are made to simple switching strategies such as sine-triangle modulation (STPWM) or space vector modulation (SVPWM) to minimize the commonmode voltage generated. A survey of published techniques is included in the final chapter of this thesis.

#### **1.2** Basis of Modeling Approach

The common-mode equivalent circuit derivations utilized in this research will take a mixed-mode circuit and algorithmically produce a common-mode equivalent circuit. The judicious use of definitions of CM voltage and CM current will enable this process. One may predict common-mode behavior and evaluate the type and placement of mitigation measures to use using standard elementary circuit theory. [8]

Recall that the differential mode represents the desired operation of a circuit. DM voltages are conceptualized as existing between pairs of terminals, and DM currents are assumed to travel down one conductor and back through the second. In contrast, the common mode represents the unintended operation of a circuit due to parasitic couplings, asymmetric design, or the environmental influence of a power system. CM voltages are conceptualized as existing between all terminals in a set and an arbitrary point, and CM currents are thought to travel down the set of all conductors simultaneously and back through a ground path.

Fig. 1.1. Diagram for Common-mode and Differential-Mode Definitions

For the pair of wires in Figure 1.1, the convention is that current is considered positive going into the system. DM voltage, DM current, CM voltage, and CM current may be defined for use in this thesis using Figure 1.1 as a basis [8]:

$$v_{DM} \triangleq v_{1P} - v_{2P} \tag{1.1}$$

$$i_{DM} \triangleq \frac{1}{2}(i_1 - i_2)$$

(1.2)

$$v_{CM} \triangleq \frac{1}{2}(v_{1P} + v_{2P})$$

(1.3)

$$i_{CM} \triangleq i_1 + i_2 \tag{1.4}$$

While the form of the DM voltage in (1.1) may be familiar, DM current (1.2) might seem a little strange. Suppose that current I flows down from terminal 1 and returns through terminal 2 ( $i_2 = -i_1$ ). In this situation,  $i_{DM} = \frac{1}{2}[(I) - (-I)] = \frac{1}{2}[2I] =$ I with zero CM current. Similarly, the CM voltage in (1.3) may be verified by supposing that the voltages are balanced with respect to arbitrary reference point P ( $v_{1P} = +\frac{V}{2}, v_{2P} = -\frac{V}{2}$ ). In this situation where P is the differential voltage midpoint,  $v_{CM} = \frac{1}{2}(\frac{+V}{2} + \frac{-V}{2}) = 0$  and  $v_{DM} = V$ .

Care must be taken when generalizing these definitions to  $K \ge 2$  lines.

$$v_{CM} \triangleq \frac{1}{K} \sum_{k=1}^{K} v_{kP}$$

, (single voltage of this form) (1.5)

$$i_{CM} \triangleq \sum_{k=1}^{K} i_k$$

, (single current of this form) (1.6)

The equation (1.6) reveals that the CM current is defined as the sum of currents. The CM voltage equation (1.5), the arithmetic mean of voltages, retains the arbitrary point P as a reference.

## 2. SYSTEM OF INTEREST

## 2.1 Hybrid Vehicle Drive Architecture

Fig. 2.1. Block Diagram of Prototypical Hybrid Vehicle Drive Architecture

The system under consideration in this research is a hybrid vehicle drive architecture intended for a heavy-duty, off-road vehicle. The primary components in the architecture are a source machine acting as a generator, a load machine acting as a motor, and a DC bus between them. There may be DC-DC converters attached to the DC bus to perform voltage conversion or provide electronic braking. Cables attach the major system components to the DC bus, and common-mode suppression devices may be introduced at various locations in the architecture. The block diagram of a prototypical system is shown in Figure 2.1.

## 2.2 System Components

The process of taking an existing electrical system and finding the common-mode equivalent system can be divided into four steps.

- 1. Add parasitic elements to each DM circuit block, including coupling paths to ground

- 2. Use Kirchhoff's Laws and the CM definitions to derive CM equivalent circuit blocks

- 3. Combine CM equivalent circuit blocks to achieve a system-level CM equivalent circuit

- 4. Characterize CM sources (typically voltage sources)

The dominant parasitic pathways that are added to form a DM/CM (mixed-mode or fully detailed) circuit vary from situation to situation. The recommended number varies depending on the CM problems encountered, the desired fidelity of the model, or the available bandwidth of impedance analyzers and other measurement equipment. Complicated models exist in the literature, but it may be difficult to capture their effects with an impedance analyzer or network analyzer and more difficult still to represent the results with lumped circuit elements. In this chapter, the components of the system in Figure 2.1 are analyzed and a common-mode equivalent circuit is formed.

There are two possible tripping points with the arbitrary reference point CM equivalent circuit formation. The first is that it presupposes that there is no DM-CM coupling in the circuit. Both circuit designs and circuit models should intentionally be made as symmetrically as possible. A symmetrical system will lack a DM-CM coupling that allows DM voltage to drive CM current. The second is that the circuit remains in the mode of operation used to derive the circuits. This usually means that the electronic switches in the circuit must remain in continuous mode (current greater than zero) and not go discontinuous at any point in time, which may be difficult to predict and subsequently enforce because of mixed-mode effects. While the CM equivalent circuit may be modified to support continuous and discontinuous modes, it may be difficult to identify the timing when the zero-current threshold is reached due to the superposition of DM current and CM current. When these two conditions are met, the information in the CM equivalent circuit will be absolutely identical to the CM information in the mixed-mode model.

### 2.2.1 Three-phase Machine Model

#### Akagi Machine Model

Fig. 2.2. Akagi Model of Three-phase Machine Stator and Attached Feeder Cables

Figure 2.2 shows a simple model of a three-phase machine and feeder cables developed by Hirofumi Akagi. [5]  $L_{sf}$  represents the inductance of the feeder cables.  $r_s$ is the sum of the feeder cable resistance and the machine stator resistance.  $L_{ls} + L_{ms}$ represents the stator winding self-inductance, and the mutual inductance between any two phases is  $-\frac{L_{ms}}{2}$ .  $E_x$ ,  $x \in \{a, b, c\}$  represents the back-emf of the machine. This machine is assumed to be wye-connected to the neutral, denoted n with a voltage with respect to ground of  $V_{ng}$ . Three parasitic capacitances  $C_{sg}$  join the nodes between  $r_s$ and  $L_s$  in each phase to ground. These represent winding-to-stator parasitic coupling paths. The feeder cables have terminals that are at potentials  $v_{aP}$ ,  $v_{bP}$ , and  $v_{cP}$  with respect to arbitrary point P. The arbitrary point is at a potential  $v_{Pg}$  above ground. Currents  $i_a$ ,  $i_b$ , and  $i_c$  are defined as positive into the cable terminals. The currents flowing through the machine phases towards the neutral are  $i_{an}$ ,  $i_{bn}$ , and  $i_{cn}$ . With all of these circuit elements and quantities defined, one can start using circuit laws to start the derivation of the CM equivalent circuit.

The first set of loops are through the cable terminals through the parasitic capacitances to ground using KVL. One can express this set of loops using p as the Heaviside operator  $(p = \frac{d}{dt})$ :

$$\begin{array}{rcrcrcrcrcrcrc}

0 = v_{Pg} + & v_{aP} & - & L_{sf}p(i_{a}) & - & r_{s}(i_{a}) & - & \frac{1}{C_{sgp}}(i_{a} - i_{an}) \\

0 = v_{Pg} + & v_{bP} & - & L_{sf}p(i_{b}) & - & r_{s}(i_{b}) & - & \frac{1}{C_{sgp}}(i_{b} - i_{bn}) \\

+ & 0 = v_{Pg} + & v_{cP} & - & L_{sf}p(i_{c}) & - & r_{s}(i_{c}) & - & \frac{1}{C_{sgp}}(i_{c} - i_{cn}) \\

\hline

0 = & 3v_{Pg} + v_{aP} + v_{bP} + v_{cP} - L_{sf}p(i_{a} + i_{b} + i_{c}) - r_{s}(i_{a} + i_{b} + i_{c}) - \frac{1}{C_{sgp}}(i_{a} + i_{b} + i_{c} - i_{an} - i_{bn} - i_{cn}) \\

0 = & 3v_{Pg} + & 3v_{CM,P} & - & L_{sf}p(i_{CM}) & - & r_{s}(i_{CM}) & - & \frac{1}{C_{sgp}}(i_{CM} - i_{CM,n}) \\

0 = & v_{Pg} + & v_{CM,P} & - & \frac{L_{sf}}{3}p(i_{CM}) & - & \frac{r_{s}}{3}(i_{CM}) & - & \frac{1}{3C_{sgp}}(i_{CM} - i_{CM,n}) \\

\end{array}$$

$$(2.1)$$

The loops for each phase are added to produce the fourth line in (2.1). Using the definitions of common-mode current (1.6) and K = 3 lines times common-mode voltage (1.5), the simplification in the fifth line follows from the fourth. The sixth line divides the fifth line through by 3 in order to aid in the reconstruction of a circuit from this equation.

The second set of loops are through the machine neutral point through the parasitic capacitances to ground using KVL:

$$0 = v_{ng} + E_a + (L_{ls} + L_{ms})p(i_{an}) - \frac{L_{ms}}{2}p(i_{bn}) - \frac{L_{ms}}{2}p(i_{cn}) - \frac{1}{C_{sgp}}(i_a - i_{an})$$

$$0 = v_{ng} + E_b + (L_{ls} + L_{ms})p(i_{bn}) - \frac{L_{ms}}{2}p(i_{cn}) - \frac{L_{ms}}{2}p(i_{an}) - \frac{1}{C_{sgp}}(i_b - i_{bn})$$

$$0 = v_{ng} + E_c + (L_{ls} + L_{ms})p(i_{cn}) - \frac{L_{ms}}{2}p(i_{an}) - \frac{L_{ms}}{2}p(i_{bn}) - \frac{1}{C_{sgp}}(i_c - i_{cn})$$

(2.2)

The loops for each phase in (2.2) are summed before applying common-mode definitions and dividing by 3.  $E_{CM,n} = \frac{1}{3}(E_a + E_b + E_c)$  is treated as a CM voltage source that represents the imbalance in the machine back-emf.  $L_{ms}p$  components cancel, which yields:

$$0 = v_{ng} + E_{CM,n} + \frac{L_{ls}}{3}p(i_{CM,n}) - \frac{1}{3C_{sg}p}(i_{CM} - i_{CM,n})$$

(2.3)

Fig. 2.3. CM Equivalent Circuit of Akagi's 3-phase Machine Stator and Feeder Cables

Taking (2.1) and (2.3), a circuit shown in Figure 2.3.  $v_{CM,P}$  will be represented as an independent voltage source. Note that there is no path in the model for CM current to flow through the wye connection: [5]

$$i_{CM,n} = i_{an} + i_{bn} + i_{cn} = 0 (2.4)$$

When a common-mode current is equal to zero, then that means there is an opencircuit in the CM equivalent circuit. In this case,  $v_{ng}$  represents an open-circuit voltage. The elements  $E_{CM,n}$  and  $\frac{L_{ls}}{3}$  have no effect in this circuit. The caution is that experimental results are needed to validate whether further parasitic elements in the stator can be neglected. If not, a more complicated model is needed.

## Chen and Lipo Machine Model

Shaotang Chen and Thomas A. Lipo developed a more complicated model of a three-phase machine based on  $\Pi$ -models from transmission line theory. [11] Standard

Fig. 2.4. Chen and Lipo Model of Three-phase Machine Winding-Stator Interactions

machine parameters such as winding resistance  $r_s$ , stator self-inductance  $L_{ls} + L_{ms}$ , stator mutual inductance  $-\frac{1}{2}L_{ms}$ , and back-emf  $E_x$ ,  $x \in \{a, b, c\}$  appear. This model is able to approximate several distributed parasitic paths rather than just a single path of the common-mode cable and terminal effects shown in the Akagi model. The feeder cables are modeled separately. One half of the circuit model represents winding-stator interactions, shown in Figure 2.4. The "ws1" subscript refers to a lumped element path to ground at the terminals of the machine. The "wsn" subscript refers to a lumped element path to ground at the neutral point of the windings. If the stator core is separated from the grounded chassis, then the capacitances to ground  $C_{ws1}$ and  $C_{wsn}$  are the effective capacitances from the windings to the stator core and from the stator core to the chassis at the machine terminals and neutral point, respectively.

The machine terminals are at potentials  $v_{aP}$ ,  $v_{bP}$ , and  $v_{cP}$  from an arbitrary point P. The arbitrary point is at a potential  $v_{Pg}$  above ground. Currents  $i_a$ ,  $i_b$ , and  $i_c$  are

defined positive into the cable terminals. The currents flowing through the machine phases towards the parasitically-grounded neutral are  $i_{an}$ ,  $i_{bn}$ , and  $i_{cn}$ . With all of these circuit elements and quantities defined, one can start using circuit laws to start the derivation of the CM equivalent circuit.

The first set of loops are through the machine terminals through the parasitic impedances "ws1" to ground using KVL:

$$0 = v_{Pg} + v_{aP} - \left(L_{ws1}p + \frac{1}{C_{ws1}p} + r_{ws1}\right)(i_a - i_{an})$$

$$0 = v_{Pg} + v_{bP} - \left(L_{ws1}p + \frac{1}{C_{ws1}p} + r_{ws1}\right)(i_b - i_{bn})$$

$$+ 0 = v_{Pg} + v_{cP} - \left(L_{ws1}p + \frac{1}{C_{ws1}p} + r_{ws1}\right)(i_c - i_{cn})$$

$$0 = 3v_{Pg} + (v_{aP} + v_{bP} + v_{cP}) - \left(L_{ws1}p + \frac{1}{C_{ws1}p} + r_{ws1}\right)(i_a + i_b + i_c - i_{an} - i_{bn} - i_{cn})$$

$$0 = 3v_{Pg} + 3v_{CM,P} - \left(L_{ws1}p + \frac{1}{C_{ws1}p} + r_{ws1}\right)(i_{CM} - i_{CM,n})$$

$$0 = v_{Pg} + v_{CM,P} - \left(\frac{L_{ws1}p}{3}p + \frac{1}{3C_{ws1}p} + \frac{r_{ws1}}{3}\right)(i_{CM} - i_{CM,n})$$

$$(2.5)$$

The loops for each phase are added together to produce the fourth line in (2.5). Using the definitions of common-mode current (1.6) and K = 3 lines times common-mode voltage (1.5), the simplification in the fifth line follows from the fourth. The sixth line divides the fifth line through by 3 in order to aid in the reconstruction of a circuit from this equation.

The second set of loops are through the machine terminals, through the neutral point, and through the parasitic impedances "wsn" to ground using KVL:

$$0 = v_{Pg} + v_{aP} - (r_s + L_{ls}p + L_{ms}p)(i_{an}) + \frac{L_{ms}}{2}p(i_{bn}) + \frac{L_{ms}}{2}p(i_{cn}) - E_a - \frac{\left(L_{wsn}p + \frac{1}{C_{wsn}p} + r_{wsn}\right)}{(i_{an} + i_{bn} + i_{cn})}$$

$$0 = v_{Pg} + v_{bP} - (r_s + L_{ls}p + L_{ms}p)(i_{bn}) + \frac{L_{ms}}{2}p(i_{cn}) + \frac{L_{ms}}{2}p(i_{an}) - E_b - \frac{\left(L_{wsn}p + \frac{1}{C_{wsn}p} + r_{wsn}\right)}{(i_{an} + i_{bn} + i_{cn})}$$

$$0 = v_{Pg} + v_{cP} - (r_s + L_{ls}p + L_{ms}p)(i_{cn}) + \frac{L_{ms}}{2}p(i_{an}) + \frac{L_{ms}}{2}p(i_{bn}) - E_c - \frac{\left(L_{wsn}p + \frac{1}{C_{wsn}p} + r_{wsn}\right)}{(i_{an} + i_{bn} + i_{cn})}$$

$$(2.6)$$

The loops for each phase are added together before applying common-mode definitions and dividing by 3.  $E_{CM,n} = \frac{1}{3}(E_a + E_b + E_c)$  is treated as a CM voltage source that represents the imbalance in the machine back-emf. It is noted that the  $L_{ms}p$  terms cancel, yielding:

$$0 = v_{Pg} + v_{CM,P} - \left(\frac{r_s}{3} + \frac{L_{ls}}{3}p\right)(i_{CM,n}) - E_{CM,n} - \left(L_{wsn}p + \frac{1}{C_{wsn}p} + r_{wsn}\right)(i_{CM,n})$$

(2.7)

Fig. 2.5. CM Equivalent Circuit of Chen and Lipo's 3-phase Machine Winding-Stator Interactions

Taking (2.5) and (2.7), a circuit can be constructed as shown in Figure 2.5. Note that this model has a path for CM current to flow through the neutral point of the wye connection.

$$i_{CM,n} = i_{an} + i_{bn} + i_{cn} \neq 0 \tag{2.8}$$

The CM voltage source  $E_{CM,n}$  (if the back-emf is unbalanced or has harmonics of the electrical rotor frequency  $f_r$  present) and stator resistance and leakage inductance have an effect on the common-mode behavior of the system.

The Shaotang Chen and Thomas A. Lipo model of a three-phase machine is only halfway complete. A winding-rotor-bearing interactions model also based on Π-models from transmission line theory needs to be added. [11] This model shares

Fig. 2.6. Chen and Lipo Model of Three-phase Machine Winding-Rotor-Bearing Interactions

the same arbitrary point P and the terminal voltages  $v_{aP}$ ,  $v_{bP}$ , and  $v_{cP}$  with the winding-stator model. The lumped circuit approximation may be seen in Figure 2.6. The primed impedances r', C', and L' are the result of a circuit reduction when the transmission line modeling the distributed impedance of the winding with respect to the rotor steel can be reduced to a single RLC circuit. The capacitance  $C_g$  models both the airgap capacitance between the rotor to ground (the dominant component) and the capacitance across the bearing itself (a smaller component). This capacitance has a current  $i_g$  flowing through it. The resistance  $r_B$  and inductance  $L_B$ comes from the path that current would take when the steel bearings conduct from the rotor through the inner raceway and to the grounded chassis. The switch  $S_B$ represents the stochastic behavior of the bearing which will randomly conduct based on lubrication chemistry, age, and electric potential difference. Normally, scheduled switching events are coalesced into CM voltage sources as described at the start of Section 2.2, but the random switching behavior representing the bearing will prompt the inclusion of a discrete switch in the common-mode equivalent circuit. The net effect of this switch in the model is to discharge the airgap capacitance through the bearing resistance and inductance, corresponding to a life-draining electric discharge machining event.

The first set of loops are through the machine terminals through the primed coupling impedances to ground through the airgap capacitance using KVL:

$$0 = v_{Pg} + v_{aP} - \left(L'p + \frac{1}{C'p} + r'\right)(i_{a}) - \frac{1}{C_{gp}}(i_{g})$$

$$0 = v_{Pg} + v_{bP} - \left(L'p + \frac{1}{C'p} + r'\right)(i_{b}) - \frac{1}{C_{gp}}(i_{g})$$

$$+ 0 = v_{Pg} + v_{cP} - \left(L'p + \frac{1}{C'p} + r'\right)(i_{c}) - \frac{1}{C_{gp}}(i_{g})$$

$$0 = 3v_{Pg} + (v_{aP} + v_{bP} + v_{cP}) - \left(L'p + \frac{1}{C'p} + r'\right)(i_{a} + i_{b} + i_{c}) - \frac{1}{C_{gp}}(3i_{g})$$

$$0 = 3v_{Pg} + 3v_{CM,P} - \left(L'p + \frac{1}{C'p} + r'\right)(i_{CM}) - \frac{1}{C_{gp}}(3i_{g})$$

$$0 = v_{Pg} + v_{CM,P} - \left(\frac{L'}{3}p + \frac{1}{3C'p} + \frac{r'}{3}\right)(i_{CM}) - \frac{1}{C_{gp}}(i_{g})$$

$$(2.9)$$

The loops for each phase are added together to produce the fourth line in (2.9). Using the definitions of common-mode current (1.6) and K = 3 lines times common-mode voltage (1.5), the simplification in the fifth line follows from the fourth. The sixth line divides the fifth line through by 3 in order to aid in the reconstruction of a circuit from this equation.

This set of loops is sufficient to describe operation when the bearing is not conducting. However, a single loop will concisely show how the randomly conducting bearing fits into the common-mode equivalent circuit. Let  $v_{S_B} = 0$  be the voltage across the ideal switch  $S_B$  when the bearing is conducting.

Rotor and Bearing:

$$0 = \frac{1}{C_g p} (i_g) - v_{S_B} - (L_B p + r_B)(i_{CM} - i_g)$$

(2.10)

Fig. 2.7. CM Equivalent Circuit of Chen and Lipo's 3-phase Machine Winding-Rotor-Bearing Interactions

Taking (2.9) and (2.10), a circuit is constructed from those equations and is shown in Figure 2.7. Depending on how the engineer chooses to model the random conduction of the bearing, the CM equivalent circuit has one of two possible topologies.

$$\begin{cases} i_{CM} - i_g = 0, \ S_B = 0\\ i_{CM} - i_g \neq 0, \ S_B = 1 \end{cases}$$

(2.11)

The motor model gains a fourth parasitic connection to ground when the bearing conducts in addition to the permanent "ws1" branch of the stator, the permanent "wsn" branch of the stator, and the permanent  $C_g$  path of the rotor.

### 2.2.2 Three-phase Cable Model

## Short Transmission Line

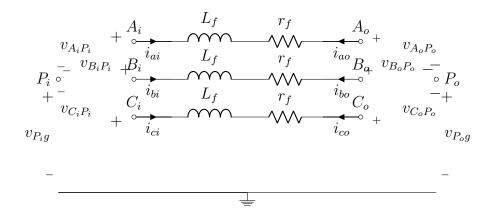

The Chen and Lipo model requires an external model of the phase cables. When dealing with electrically short cables, a simple model of a three-phase transmission

Fig. 2.8. Series Impedance Model of Three-phase Cables

line as uncoupled series impedances may be used. The circuit model is seen in Figure 2.8. Each phase cable has a resistance  $r_f$  and a self-inductance  $L_f$ . The input side refers the three terminals  $A_i$ ,  $B_i$ , and  $C_i$  to the arbitrary point on the input side  $P_i$ . Currents  $i_{ai}$ ,  $i_{bi}$ , and  $i_{ci}$  flow into the input terminals. The output side refers the three terminals  $A_o$ ,  $B_o$ , and  $C_o$  to a different arbitrary point on the output side,  $P_o$ . Currents  $i_{ao}$ ,  $i_{bo}$ , and  $i_{co}$  are defined positive into the terminals on the output side. Note that for this simple model,  $i_{xi} = -i_{xo}$ ,  $x \in \{a, b, c\}$ .

A single set of loops describes this circuit block:

| $0 = v_{P_ig} +$           | $v_{A_iP_i}$              | —              | $\left(L_f p + r_f\right)\left(i_{ai}\right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | —                    | $v_{A_oP_o}$                    | $- v_{P_og}$         |

|----------------------------|---------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|---------------------------------|----------------------|

| $0 = v_{P_ig} +$           | $v_{B_iP_i}$              | _              | $\left(L_f p + r_f\right)\left(i_{bi}\right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                    | $v_{B_oP_o}$                    | $-v_{P_og}$          |

| $+ 0 = v_{P_ig} +$         | $v_{C_iP_i}$              | _              | $\left(L_f p + r_f\right)\left(i_{ci}\right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | _                    | $v_{C_oP_o}$                    | $-v_{P_og}$          |

| $0 = 3v_{P_ig} + (v_{A_i}$ | $P_i + v_{B_i P_i} + v_0$ | $C_i P_i - (L$ | $_{f}p+r_{f}\left( i_{ai}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+i_{bi}+$ | $i_{ci}$ ) – ( $v_A$ | $v_{B_oP_o} + v_{B_oP_o} + v_C$ | $_{oPo}) - 3v_{Pog}$ |

| $0 = 3v_{P_ig} +$          | $3v_{CM,P_i}$             | _              | $\left(L_f p + r_f\right)\left(i_{CM,i}\right)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                    | $3v_{CM,Po}$                    | $-3v_{P_og}$         |

| $0 = v_{P_ig} +$           | $v_{CM,P_i}$              | _              | $\left(\frac{L_f}{3}p + \frac{r_f}{3}\right)(i_{CM,i})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _                    | $v_{CM,P_o}$                    | $-v_{P_og}$          |

|                            |                           |                | · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |                                 | (2.12)               |

The sum of the loops in (2.12) produces the fourth line. Simplification results by using CM voltage definitions  $3v_{CM,P_i} = v_{A_iP_i} + v_{B_iP_i} + v_{C_iP_i}$  and  $3v_{CM,P_o} = v_{A_oP_o} + v_{B_oP_o} + v_{C_oP_o}$  and the CM current definition  $i_{CM,i} = i_{ai} + i_{bi} + i_{ci}$ . Dividing the resulting equation by 3 produces the equation of a loop that gives rise to the CM equivalent circuit.

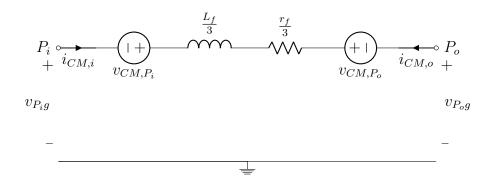

Fig. 2.9. CM Equivalent Circuit for Series Impedance Model of Threephase Cables

The CM equivalent circuit of the cables is shown in Figure 2.9. The input reference point  $P_i$  and the output reference point  $P_o$  appear with independent voltage sources  $v_{CM,P_i}$  and  $v_{CM,P_o}$  next to them. The impedances have been cut by three, the number of wires. If shunt admittances are significant, then a medium-length cable model should be used.

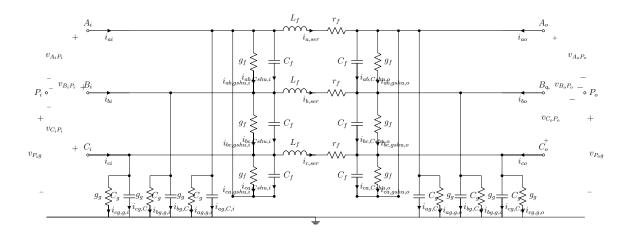

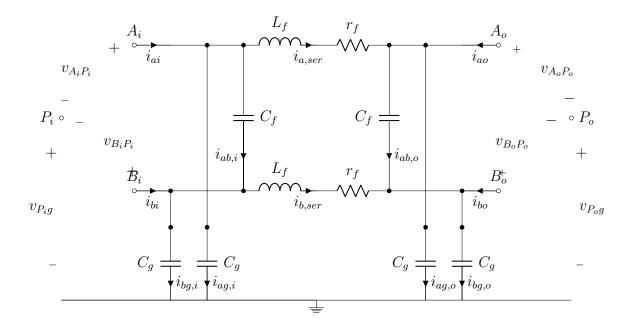

### Medium Transmission Line

Cables that are of a medium length electrically require a shunt admittance to be included in addition to the uncoupled series impedances. This model is seen in Figure 2.10. Each phase cable has a resistance  $r_f$  and a self-inductance  $L_f$ . There are a capacitance  $C_f$  and a conductance  $g_f$  that appear in a line-to-line (DM) fashion. Additionally, a capacitance  $C_g$  and a conductance  $g_g$  placed in a phase-to-ground fashion grow with length and must be addressed. The input side refers the three terminals  $A_i$ ,  $B_i$ , and  $C_i$  to the arbitrary point on the input side  $P_i$ . Currents  $i_{xi}$  are defined positive into the input terminals. The output side refers the three terminals  $A_o$ ,  $B_o$ , and  $C_o$  to a different arbitrary point on the output side,  $P_o$ . Currents  $i_{xo}$

Fig. 2.10. Series Impedance and Shunt Admittance Model of Three-phase Cables

are defined positive into the terminals on the output side and are generally distinct from the current on the input side. A current  $i_{x,ser}$  is defined through the lumped series elements. Let  $i_{x_1x_2,y_{shu,z}}$  represent the current in the phase-to-phase lumped elements. Let  $i_{xg,y,z}$  represent the current in the phase-to-ground lumped elements. The sets are as follows:  $x, x_1, x_2 \in \{a, b, c\}, x_1 \neq x_2$  for the phases,  $y \in \{C, g\}$  for the type of admittance, and  $z \in \{i, o\}$  for the side.

The first set of loops constructed is through  $P_i$ , both shunt elements to the phase behind and back, both shunt elements to the phase ahead and back, the series elements, and the output capacitances to ground:

$$0 = v_{P_{i}g} + v_{A_{i}P_{i}} - \frac{1}{g_{f}}(i_{ab,gshu,i}) + \frac{1}{C_{f}p}i_{ab,Cshu,i} + \frac{1}{g_{f}}(i_{ca,gshu,i}) - \frac{1}{C_{f}p}i_{ca,Cshu,i} - (r_{f} + L_{f}p)(i_{a,ser}) - \frac{1}{C_{gp}}(i_{ag,C,o})$$

$$0 = v_{P_{i}g} + v_{B_{i}P_{i}} - \frac{1}{g_{f}}(i_{bc,gshu,i}) + \frac{1}{C_{f}p}i_{bc,Cshu,i} + \frac{1}{g_{f}}(i_{ab,gshu,i}) - \frac{1}{C_{f}p}i_{ab,Cshu,i} - (r_{f} + L_{f}p)(i_{b,ser}) - \frac{1}{C_{gp}}(i_{bg,C,o})$$

$$0 = v_{P_{i}g} + v_{C_{i}P_{i}} - \frac{1}{g_{f}}(i_{ca,gshu,i}) + \frac{1}{C_{f}p}i_{ca,Cshu,i} + \frac{1}{g_{f}}(i_{bc,gshu,i}) - \frac{1}{C_{f}p}i_{bc,Cshu,i} - (r_{f} + L_{f}p)(i_{c,ser}) - \frac{1}{C_{gp}}(i_{cg,C,o})$$

$$(2.13)$$

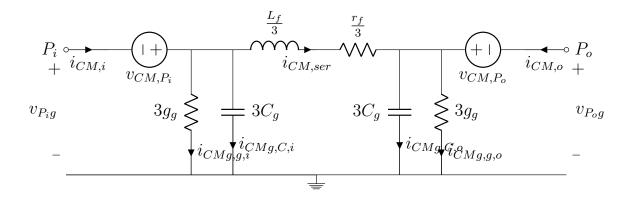

The sum of the three loops in (2.13) begins the process of forming the loop equation for the CM equivalent circuit. Simplification results by using CM voltage definition  $3v_{CM,P_i} = v_{A_iP_i} + v_{B_iP_i} + v_{C_iP_i}$  and the CM current definitions  $i_{CM,ser} = i_{a,ser} + i_{b,ser} + i_{c,ser}$  and  $i_{CMg,C,o} = i_{ag,C,o} + i_{bg,C,o} + i_{cg,C,o}$ . Noticing the cancellation of  $g_f$  and  $C_f$  terms and dividing the resulting equation by 3 produces the equation of a loop that helps give rise to the CM equivalent circuit:

$$0 = v_{P_{ig}} + v_{CM,P_i} - \left(\frac{r_f}{3} + \frac{L_f}{3}p\right)(i_{CM,ser}) - \frac{1}{3C_g p}(i_{CMg,C,o})$$

(2.14)

The second set of loops constructed is through  $P_o$ , both shunt elements to the phase behind and back, both shunt elements to the phase ahead and back, the series elements, and the input capacitances to ground:

$$0 = v_{P_{o}g} + v_{A_{o}P_{o}} - \frac{1}{g_{f}}(i_{ab,gshu,o}) + \frac{1}{C_{f}p}i_{ab,Cshu,o} + \frac{1}{g_{f}}(i_{ca,gshu,o}) - \frac{1}{C_{f}p}i_{ca,Cshu,o} + (r_{f} + L_{f}p)(i_{a,ser}) - \frac{1}{C_{g}p}(i_{ag,C,i})$$

$$0 = v_{P_{o}g} + v_{B_{o}P_{o}} - \frac{1}{g_{f}}(i_{bc,gshu,o}) + \frac{1}{C_{f}p}i_{bc,Cshu,o} + \frac{1}{g_{f}}(i_{ab,gshu,o}) - \frac{1}{C_{f}p}i_{ab,Cshu,o} + (r_{f} + L_{f}p)(i_{b,ser}) - \frac{1}{C_{g}p}(i_{bg,C,i})$$

$$0 = v_{P_{o}g} + v_{C_{o}P_{o}} - \frac{1}{g_{f}}(i_{ca,gshu,o}) + \frac{1}{C_{f}p}i_{ca,Cshu,o} + \frac{1}{g_{f}}(i_{bc,gshu,o}) - \frac{1}{C_{f}p}i_{bc,Cshu,o} + (r_{f} + L_{f}p)(i_{c,ser}) - \frac{1}{C_{g}p}(i_{cg,C,i})$$

$$(2.15)$$

The sum of the three loops in (2.15) is simplified by using the CM voltage definition  $3v_{CM,P_o} = v_{A_oP_o} + v_{B_oP_o} + v_{C_oP_o}$  and the CM current definitions  $i_{CM,ser} = i_{a,ser} + i_{b,ser} + i_{c,ser}$  and  $i_{CMg,C,i} = i_{ag,C,i} + i_{bg,C,i} + i_{cg,C,i}$ . Noticing the cancellation of  $g_f$  and  $C_f$  terms and dividing the resulting equation by 3 produces the equation of a loop that helps give rise to the CM equivalent circuit:

$$0 = v_{P_{og}} + v_{CM,P_{o}} + \left(\frac{r_{f}}{3} + \frac{L_{f}}{3}p\right)(i_{CM,ser}) - \frac{1}{3C_{g}p}(i_{CMg,C,i})$$

(2.16)

A third set of loops is through the shunt conductances to ground. The loops are through  $g_g$  on the input side, the series elements, and  $g_g$  on the output side:

$$\begin{array}{rcl}

0 &=& \frac{1}{g_g}(i_{ag,g,i}) &-& (r_f + L_f p)(i_{a,ser}) &-& \frac{1}{g_g}(i_{ag,g,o}) \\

0 &=& \frac{1}{g_g}(i_{bg,g,i}) &-& (r_f + L_f p)(i_{b,ser}) &-& \frac{1}{g_g}(i_{bg,g,o}) \\

+& 0 &=& \frac{1}{g_g}(i_{cg,g,i}) &-& (r_f + L_f p)(i_{c,ser}) &-& \frac{1}{g_g}(i_{cg,g,o}) \\

\hline

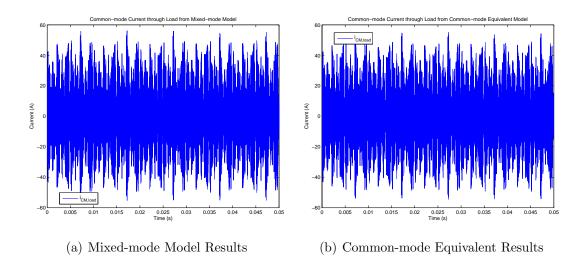

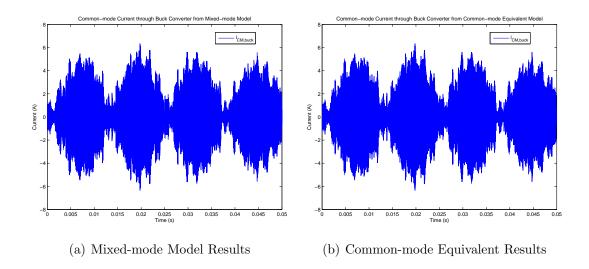

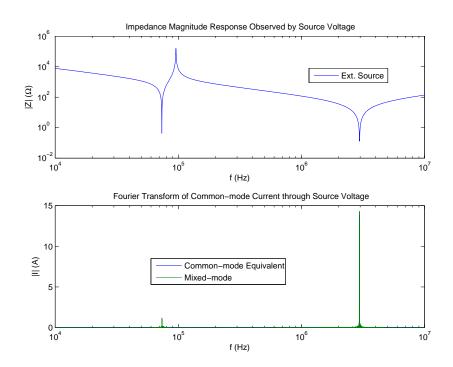

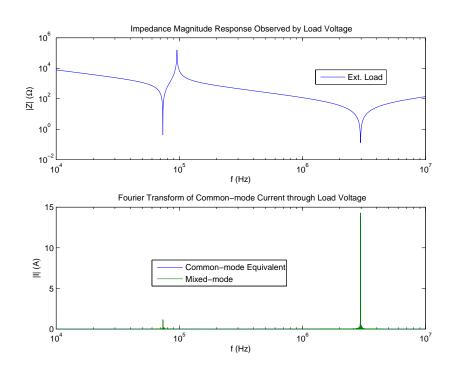

0 &=& \frac{1}{g_g}(i_{ag,g,i} + i_{bg,g,i} + i_{cg,g,i}) - (r_f + L_f p)(i_{a,ser} + i_{b,ser} + i_{c,ser}) - \frac{1}{g_g}(i_{ag,g,o} + i_{bg,g,o} + i_{cg,g,o}) \\