© 2021 Ameya D. Patil

#### HARNESSING NOISE TO ENHANCE ROBUSTNESS VS. EFFICIENCY TRADE-OFF IN MACHINE LEARNING

BY

AMEYA D. PATIL

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois Urbana-Champaign, 2021

Urbana, Illinois

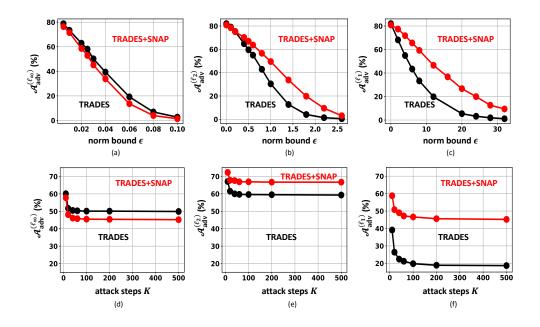

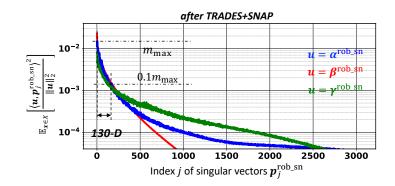

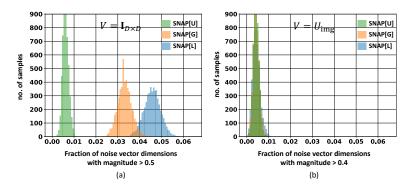

Doctoral Committee:

Professor Naresh R. Shanbhag, Chair Assistant Professor Alexander Schwing Professor Pavan Kumar Hanumolu Professor Romit Roy Choudhury

## ABSTRACT

While deep nets have achieved human-comparable accuracy in various classification tasks, they fall short significantly in terms of the robustness and cost metrics. For example, tiny engineered corruptions in deep net inputs can reduce their accuracy to zero. Furthermore, deep nets also require millions of trainable parameters, resulting in significant training and inference costs. These robustness and cost challenges are well recognized today. In response, there have been a plethora of works focusing on improving either the accuracy vs. robustness trade-off, or the accuracy vs. cost trade-off. However, simultaneous consideration of accuracy, robustness, and cost metrics is largely absent today, in part, because far fewer works have explored the robustness vs. cost trade-off. This dissertation aims to fill this gap by focusing explicitly on the robustness vs. cost trade-off in the presence of data noise, as well as hardware noise. Specifically, we explore how to harness the noise in order to enhance this trade-off. We characterize and improve robustness vs. cost trade-offs across diverse problem settings, ranging from beyond-CMOS hardware implementations of machine learning (ML) classifiers to efficient training of deep nets that are robust to multiple types of corruptions in their inputs. This dissertation can be roughly divided into two part, one focusing on hardware noise and the other on data noise.

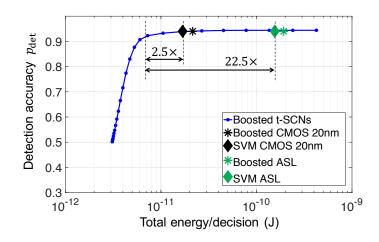

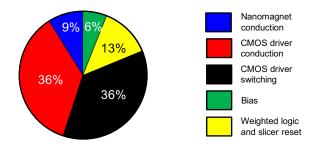

In the first part, we start by focusing on harnessing noise in spintronic hardware implementations, where the logic gates become error prone when operated at lower switching energy/delay. We propose techniques to shape the resulting hardware noise distribution and to efficiently compensate it at the system-level output. As a result, we observe  $1000 \times$  improvement in tolerance to gate-level switching error rates, while keeping the area/energy overhead of compensation circuits to as low as 15%. These robustness enhancements further enable  $3 \times$  reduction in iso-throughput energy consumption of a binary ML classifier employed for EEG-based seizure detection. Building on this work, we propose spintronic channel networks, exponential decay of spin current to efficiently realize multi-bit dot product computation. We employ error-prone nanomagnets as efficient stochastic slicers biased by spin currents proportional to the likelihood of the classification decision. We achieve  $112\times$ -to- $22.5\times$  and  $14\times$ -to- $2.5\times$  higher energy-efficiency over conventional spin-based and 20 nm CMOS designs, respectively, when realizing 10-to-100-dimensional binary classifiers. Furthermore, we also consider the impact of hardware noise originated from process variations and readout circuits in in-memory computing implementations employing non-volatile resistive crossbar arrays. Based on our analysis, we identify design configurations achieving the highest signal-to-noise ratio (SNR), and further estimate how such robustness trades off with the array energy consumption.

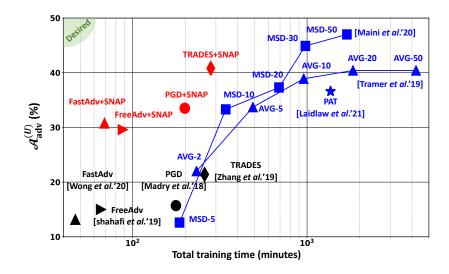

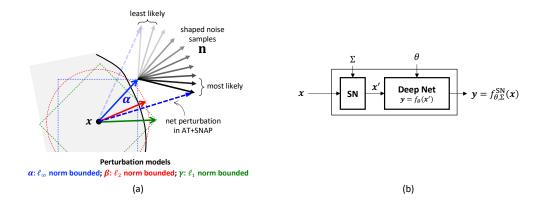

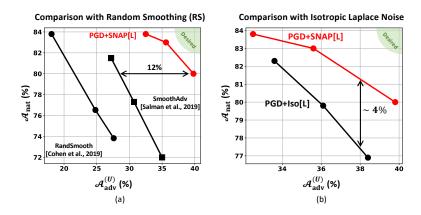

In the second part, we switch gears to improve the robustness vs. cost trade-off for deep nets in the presence of data noise. Specifically, we focus on the impact of adversarial perturbations in the deep nets inputs. We propose and validate the hypotheses about orientations of dominant subspaces of adversarial perturbations. We demonstrate how changes in the curvature of decision boundary of the deep nets affects the orientations of the adversarial perturbations. Based on these insights we demonstrate how shaped noise can be introduced as a feature to enhance robustness vs. cost trade-off in deep nets. Specifically, we propose shaped noise augmented processing (SNAP), a method to efficiently train deep nets that are robust to multiple types of adversarial perturbations, simultaneously. SNAP prepends a deep net with a shaped noise augmentation layer whose distribution is learned along with the network parameters using any established robust training framework. Based on extensive comparisons with nine state-of-the-art (SOTA) robust training frameworks, we show that SNAP achieves the best robustness vs. training cost trade-off. In particular, it enables  $4 \times$  reduction in the training cost compared to the SOTA approach published just this last year. Furthermore, thanks to the computational simplicity of SNAP, it is the first technique of its kind that is scalable to large datasets, such as ImageNet.

We conclude by identifying potential directions for future research.

To my parents, for all their love and support.

## ACKNOWLEDGMENTS

First and foremost, I would like to thank my advisor, Prof. Naresh Shanbhag. He gave me immense freedom to work on a diverse set of problems, was always available for discussions, and provided unwavering support when our ideas didn't work out as expected. I really appreciate his strategic mentorship in helping us make better research and career decisions. I am grateful for his guidance in making me a better researcher and teaching me to accept rejections in stride as a natural part of the process. I would also like to thank my dissertation committee members, Prof. Alex Schwing, Prof. Pavan Hanumolu, and Prof. Romit Roy Choudhury for providing helpful feedback for my research and dissertations. Prof. Schwing's passion and commitment for deep learning research was very inspiring, and I am grateful for all his help and support in our collaborative work in the field of adversarial robustness of deep nets. I also enjoyed interacting with Prof. Hanumolu regarding different aspects of circuit design for in-memory computing and I learned a lot from those. Finally, I really appreciated insightful discussions with Prof. Roy Choudhury about different aspects of our work.

I was fortunate to get a chance to collaborate with Sasi Manipatruni, Dmitri Nikonov, and Ian Young from Component Research group in Intel for our spintronic work and wish to sincerely thank them for their help. I also want to thank Ram Krishnamurthy, Greg Chen, Phil Knag, Huseyin Ekin Sumbul, and Raghavan Kumar for hosting me as an intern in Summer 2018 at Intel Labs, which was a wonderful experience. Being a part of Prof. Shanbhag's research group, it was great to know and collaborate with its excellent members over the years: Sujan Gonugondla, Charbel Sakr, Mingu Kang, Michael Tuttle, Hassan Dbouk, Saion Roy, Kuk-Hwan Kim, Yingyan Lin, Sai Zhang, Sungmin Lim, Yongjune Kim, Han-Mo Ou, and Hanfei Geng. I appreciate all our interactions which have shaped both my research, career, and personality. The research in this dissertation was funded in part by SONIC, C-BRIC, AIHW programs supported by SRC and DARPA, as well as DARPA's FRANC program. I feel lucky to have been a part of the SRC community as a graduate student and interacting with other faculties and students from different universities that are part of these programs was a formative experience. Thank you to the ECE Illinois Department for providing me with this opportunity to pursue a PhD degree and recognizing my work through multiple fellowships and awards.

I am lucky to have met an amazing set of friends over the past decade of staying away from home. Thanks to Zaid Ahsan, Navjot Singh, Krishan Swaminathan-Gopalan, Mubin Khan, Shripad Gade, Anadi Chaman, Kushagra Singhal, and Anurup Ganguly for making my stay in Urbana-Champaign enjoyable. All our fun activities together – long discussions, soccer games, IPL, and cooking – helped me deal with the stress and grind of the graduate school. Pranav Madadi has been an amazing friend and a source of constant support over both IIT and UIUC years. Thank you Nachiket Dongre, Sumit Jadhav, Onkar Deshpande, Abhishek Gune, Niranjan Natekar, Piyush Kulkarni, Rutuparna Karandikar, Rohan Dutte, Omkar Waikar, Vibhav Bhave, Anad Bhattad, and Jayesh Tandale for making a point to stay in touch despite being scattered all over the world. I cherished our regular calls as well as Pune meet-ups, which I always found extremely rejuvenating.

Finally, and most importantly, I would like to thank my parents, Dhananjay and Madhura Patil for all their efforts and sacrifices in helping me to get where I am today. I cannot find words to describe their love for me. I feel devastated that my mother didn't make it to see me reaching this milestone, having lost her battle to cancer just over three months ago. I wish that her soul may rest in peace and thank her from the bottom of my heart in all my prayers.

# TABLE OF CONTENTS

| CHAP | TER 1INTRODUCTIONINTRODUCTION                                 | 1  |

|------|---------------------------------------------------------------|----|

| 1.1  | Accuracy vs. Robustness Trade-off                             | 4  |

| 1.2  | Accuracy vs. Cost Trade-off                                   | 6  |

| 1.3  | Dissertation Contribution: Improving Robustness vs. Cost      |    |

|      | Trade-off                                                     | 8  |

| 1.4  | Dissertation Organization                                     | 10 |

|      |                                                               |    |

|      | TER 2ROBUST SPINTRONICS VIA SHANNON-INSPIRED                  |    |

| API  | PROACH                                                        | 13 |

| 2.1  | Overview                                                      | 13 |

| 2.2  | Background                                                    | 14 |

| 2.3  | Modeling Stochasticity of ASL Devices                         | 18 |

| 2.4  | Shannon-inspired ASL Architecture                             | 21 |

| 2.5  | Simulation Results                                            | 29 |

| 2.6  | Discussion                                                    | 31 |

| ·    |                                                               |    |

|      | TER 3 EFFICIENT INFERENCE VIA SPIN CHANNEL                    |    |

|      | TWORKS                                                        | 32 |

| 3.1  | Overview                                                      | 32 |

| 3.2  | Background                                                    | 33 |

| 3.3  | Spin Channel Networks                                         | 35 |

| 3.4  | Design of SCN-based Classifiers                               | 41 |

| 3.5  | Simulation Results                                            | 46 |

| 3.6  | Related Works                                                 | 51 |

| 3.7  | Discussion                                                    | 51 |

| ·    |                                                               |    |

| CHAP |                                                               |    |

|      | EP IN-MEMORY ARCHITECTURE                                     | 53 |

| 4.1  | Overview                                                      | 53 |

| 4.2  | Preliminaries                                                 | 55 |

| 4.3  | Voltage Driven MRAM-based Deep In-memory Architecture .       | 57 |

| 4.4  | Simulation Results for Voltage Driven MRAM-DIMA $\ . \ . \ .$ | 61 |

| 4.5  | Current Driven MRAM-DIMA                                      | 64 |

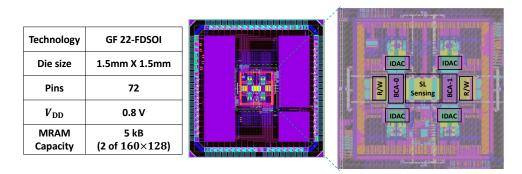

| 4.6  | Prototype Chip Tape-out                                       | 68 |

| 4.7  | Discussion                                                    | 69 |

| CHAPTER 5 SNR ANALYSIS OF IN-MEMORY COMPUTING                                                                                                          |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EMPLOYING RESISTIVE CROSSBAR ARRAYS                                                                                                                    |  |

| 5.1 Overview                                                                                                                                           |  |

| 5.2 Analysis Setup $\ldots$ 71                                                                                                                         |  |

| 5.3 Voltage Driven Crossbars                                                                                                                           |  |

| 5.4 Current Driven Crossbars                                                                                                                           |  |

| 5.5 Discussion $\ldots$ 88                                                                                                                             |  |

| CHAPTER 6 SUBSPACE ANALYSIS OF ADVERSARIAL PER-                                                                                                        |  |

| TURBATIONS                                                                                                                                             |  |

| 6.1 Overview $\ldots \ldots 91$                                    |  |

| 6.2 $$ Orthogonality between Images and Adversarial Perturbations . $$ 92 $$                                                                           |  |

| 6.3 Distinction between Different Perturbation Models $\dots \dots \dots 95$                                                                           |  |

| $6.4  \text{Discussion}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                              |  |

| CHAPTER 7 EFFICIENT AND ROBUST DEEP NET TRAIN-                                                                                                         |  |

| ING VIA NOISE SHAPING                                                                                                                                  |  |

| 7.1 Overview                                                                                                                                           |  |

| 7.2 Shaped Noise Augmented Processing (SNAP)                                                                                                           |  |

| 7.3 Experimental Results                                                                                                                               |  |

| 7.4 Robustness Stress Tests                                                                                                                            |  |

| 7.5 Additional Investigations                                                                                                                          |  |

| 7.6 Relationship between SNAP and Randomized Smoothing 121                                                                                             |  |

| 7.7 Related Works                                                                                                                                      |  |

| 7.8 Discussion $\ldots \ldots \ldots$  |  |

| CHAPTER 8 CONCLUSION AND FUTURE WORK                                                                                                                   |  |

| 8.1 Summary of Contributions                                                                                                                           |  |

| 8.2 Future Prospects                                                                                                                                   |  |

| APPENDIX A DERIVATION OF EQ. (5.4)                                                                                                                     |  |

| $AITENDIX A DEIGVATION OF EQ. (0.4) \dots \dots$ |  |

| APPENDIX B DERIVATION OF EQ. (5.12)                                                                                                                    |  |

| APPENDIX C PROOF OF THEOREM 7.1                                                                                                                        |  |

| C.1 Preliminary Lemmas                                                                                                                                 |  |

| C.2 Theorem Proof                                                                                                                                      |  |

| REFERENCES                                                                                                                                             |  |

# CHAPTER 1 INTRODUCTION

Machine learning (ML) systems strive to perform recognition, synthesis and policy-making tasks on the given input data. The examples of such systems include, robots using cameras to learn navigation in unseen environments, voice/chat assistants, and others. Such systems, when perfected and deployed, have potential to revolutionize multiple industries. The last five years have seen a huge surge of interest in the research and development of ML systems. It stems from the recent success of deep nets (see Fig. 1.1) in achieving human-comparable accuracy across diverse well-defined tasks, such as image recognition [1], speech recognition [2], and strategy games including Chess and Go [3].

The above accuracy metric measures the probability of given ML systems making correct decisions on unseen inputs, under idealistic conditions, *i.e.* the training data distribution is the same as that of the test data and the underlying hardware provides high precision deterministic implementation. Achieving high accuracy is necessary, but not sufficient to enable wide-scale deployment of ML systems in the real world. This is because the real world, as we all are aware, is often messy, noisy, non-ideal, and at times, even adversarial. For example, the underlying hardware itself could be erroneous due to device/circuit-level variations and noise [4, 5, 6, 7, 8]. Similarly, the inputs to ML systems could be corrupted via natural or engineered perturbations [9, 10]. Hence, it is necessary for ML systems to preserve their accuracy in the presence of noisy/non-ideal conditions. In adversarial ML research area, the term *robust accuracy* is defined as the accuracy of the classifier in the presence of engineered perturbations in its inputs. Hence, in this dissertation, we extend it to define *robustness* of a given ML system as a measure of the probability of correct decisions under *non-ideal* and *noisy* conditions. While noise is omnipresent, it can be broadly classified into two categories based on its sources:

Figure 1.1: Recent success of deep nets: They have achieved state-of-the-art, human-comparable accuracy across diverse set of tasks, such as (a) image recognition [1], (b) speech recognition [2], and (c) strategy games [3].

- Data noise: this category includes natural weather-like corruptions, engineered adversarial transformations, and/or the noise in front-end sensing circuits of the ML systems.

- Hardware noise: this category includes switching errors in hardware logic gates, noise due to reduced precision and analog computation, and/or impact of process and voltage variations.

Unfortunately, human-comparable accuracy of state-of-the-art (SOTA) ML algorithms does not translate to equivalently high robustness. For example, the image recognition accuracy of deep nets gets severely lowered in the presence of common corruptions [10] (*e.g.* snow, fog, and others). Furthermore, even tiny, imperceptible perturbations in their inputs can fool deep nets to make decision errors on *every* single input in the test dataset [9, 11, 12, 13,

14]. Similarly, emerging beyond-CMOS devices suffer from increased vulnerability to hardware noise and variations [4, 8, 15, 16], causing significant drop in the inference accuracy. Hence, it is important to develop techniques that enhance robustness of ML systems, while preserving their accuracy.

The discussion of accuracy and robustness of ML systems is incomplete without the consideration of their efficiency. In this dissertation, we capture it via the cost metrics, which include both the time required to train the model (training cost), as well as energy and latency associated with producing single decision in deployment (inference cost per decision). Deep nets today require millions of trainable parameters to achieve their state-of-theart accuracy [1, 17], resulting in significant training and inference costs. This challenge is further exacerbated due to current hardware limitations such as expensive memory accesses [18], slowing down of CMOS scaling [19, 20], and increased vulnerability to process variations in both CMOS [5] and beyond-CMOS [4, 21, 8] devices.

Today both robustness and cost challenges are well-recognized. In response, a large number of works have focused on improving either accuracy vs. robustness trade-off (see Sec. 1.1), or accuracy vs. cost trade-off (see Sec. 1.2). However, simultaneous consideration of accuracy, robustness, and cost metrics is largely absent today, in part, because far fewer works have explored robustness vs. cost trade-off. This dissertation aims to fill this gap by focusing explicitly on robustness vs. cost trade-off in the presence of data noise, as well as hardware noise (see Sec. 1.3). We outline dissertation organization in Sec. 1.4.

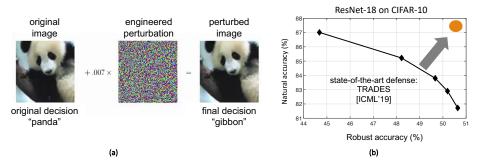

Figure 1.2: Adversarial vulnerability of deep nets: (a) example of imperceptible adversarial perturbation resulting in incorrect decision [9], and (b) trade-off between natural accuracy and robust accuracy observed for the state-of-the-art defense TRADES [22].

## 1.1 Accuracy vs. Robustness Trade-off

In spite of the high classification accuracy of deep nets [1], they are surprisingly easily fooled by corruptions in their inputs. For example, their accuracy reduces significantly in the presence of common weather-like corruptions [10], strange poses of familiar objects [23], and image rotations [24]. Furthermore, even tiny imperceptible changes in their inputs, *i.e. adversarial perturbations* [9], are sufficient to cause incorrect classification. Figure 1.2(a) shows an example of such perturbation, where despite being imperceptible, it changes the classification decision of a deep network AlexNet [9]. Similar perturbations can be found for any given deep net and any given input of that network. Furthermore, such a phenomenon has been observed across domains, *i.e.*, in image [9], speech [25], text [26], as well as, video games [27].

Multiple approaches to construct adversarial examples (attack methods) have been proposed [28, 11, 29, 12, 30, 31, 32, 33, 34]. While the basic idea is to move the input in the direction of increasing loss, stronger attacks [13, 12, 34, 30, 31] operate iteratively by perturbing the input in small increments. Almost all of these attacks succeed *deterministically*, *i.e.*, they cause classification errors for all inputs in the test dataset, against a naturally trained deep net. On the defense side, early attempts to provide adversarial defenses employed techniques such as introducing non-differentiable and/or randomized operations in the forward pass, ensemble of multiple networks [35, 36, 37, 38, 39, 40, 41]. However, such defenses were shown to be ineffective [42, 14], especially when the attacker takes explicit measures to evade that particular defense, *i.e.*, *adaptive* attacks. One example of adaptive attack is when an attacker employs expectation over transformation (EOT) to eliminate the impact of randomization in defense technique [42]. Thus, defending DNNs against adversarial attacks remains a formidable challenge partly due to a lack of in-depth understanding of the underlying cause of its vulnerability to adversarial perturbations.

Today *adversarial training* (AT) provides state-of-the-art (SOTA) empirical defense against adversarial perturbations. In AT, adversarial perturbations are computed during training to optimize a *robust* loss function [13]. After its initial success, multiple extensions and improvements in AT have been proposed [22, 43, 44, 45, 46, 47, 48, 49, 50, 51, 52, 53, 54]. In all these works, an improvement in robustness was always accompanied with some reduction in natural accuracy, *i.e.*, all of them observe a trade-off between accuracy vs. robustness [55, 56]. For example, Fig. 1.2(b) shows such a tradeoff for one of the SOTA AT framework called TRADES [22] on CIFAR-10 dataset. Notice that robust accuracy increases only at an expense of reduction in natural accuracy. Furthermore, robust accuracy is significantly (by  $\sim 40\%$ ) lower than natural accuracy even for the state-of-the-art defense. We will discuss in Sec. 1.3 how any efforts in further improving the robustness requires one to start considering robustness vs. cost trade-off.

The second source of noise is the device/circuit-level non-determinism in hardware implementations. Today, all digital CMOS implementations require deterministic switching of their component switches and gates. The problem of robustifying computation in the presence of unreliable/noisy components was posed, as early as, in 1956 by John von Neumann in [57]. He defined robust logic network as one whose output exhibits a probability of error  $p_e < 0.5$  when designed using  $\epsilon$ -noisy logic gates, *i.e.*, gates whose outputs are in error with probability  $\epsilon$ . It was further demonstrated that a robust logic network can be designed for any logic function provided  $\epsilon \leq 0.0073$ and that it is impossible to do so if  $\epsilon > \frac{1}{6}$ . Later tighter upper bounds on  $\epsilon$ were obtained in a series of papers [58, 59] culminating with those of Evans and Schulman [60]. In all these works, the overhead of additional gates required to achieve robustness was found to be impractically high, *i.e.* the cost associated with improving accuracy vs. robustness trade-off was too large.

More recently, a class of statistical error compensation (SEC) techniques was proposed to achieve robust computation in the presence of process/voltage induced delay variations in CMOS digital implementations of signal processing/ML applications [7, 61, 62]. In SEC, the hardware errors due to delay variations were compensated at the final system-level output to maintain the complexity of compensation circuits within 15%-to-20% of the main block computation [63]. As a result, up to  $16 \times$  increase in error tolerance was achieved at a marginal drop in accuracy [7]. Such robustness gains were traded-off with up to  $4 \times$  improvement in the energy-efficiency.

Finally, researchers explored modifying ML classifier training flow to enhance its robustness to hardware noise during inference. The examples include hardware-in-a-loop training of classifiers [64, 65] and hardware-aware noise injection during training [8, 16, 66, 15]. For emerging non-volatile memories, such approaches can also be combined with adaptive program-verify

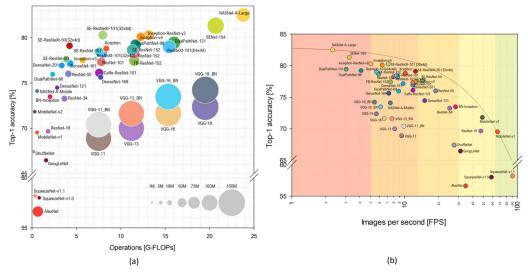

Figure 1.3: Accuracy vs. cost trade-off in deep nets [67]: classification accuracy vs. (a) number of floating-point operations and (b) images per second on NVIDIA Jetson TX1 GPU of the deep nets classifying Imagenet [68] 2012 ILSVRC dataset. The size of each ball in Fig. (a) denotes the number of parameters in the network. Millions of parameters and floating-point operations are required to achieve the SOTA accuracy.

write techniques employed to minimize the impact of write variations [21]. All these methods achieve certain improvements in the robustness to hardware noise and variations at a cost of small reduction in the accuracy.

## 1.2 Accuracy vs. Cost Trade-off

As shown in Fig. 1.1(a), deep nets achieved human-comparable accuracy in image classification tasks in 2014-15. Early proposals, such as VGGNet, were very expensive in terms of the number of network parameters and floatingpoint operations (FLOPs) required to produce a single decision. Since then, plethora of efforts have focused on improving accuracy vs. cost trade-off in deep nets as observed in Fig. 1.3(a). The proposals included both improved network architectures (*e.g.* [1, 17, 69, 70, 71, 72, 73, 74, 75]), as well as better training techniques (*e.g.* [76, 77, 78]) to achieve significant gains in accuracy vs. cost (FLOPs per inference) trade-off. The reduction in the parameter count and FLOPs also translates in improved throughput in hardware for image classification. For example, Fig. 1.3(b) shows corresponding accuracy vs. images classified per second for recently proposed deep nets running on

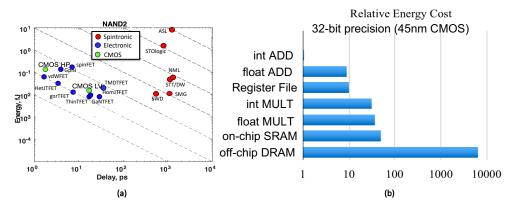

Figure 1.4: Hardware Challenges: (a) NAND2 gate switching energy vs. switching delay comparisons of the multiple beyond-CMOS devices under exploration, and their comparison with 14 nm CMOS [97, 98], (b) relative energy costs of different 32 bit operations for 45 nm CMOS implementations [18]. None of the beyond-CMOS devices on horizon significantly outperform CMOS and both on-chip and off-chip memory accesses are significantly costlier than compute operations in CMOS.

NVIDIA Jetson TX1 GPU. Researchers have also explored strategies, such as pruning [79, 80, 81, 82, 83, 84, 53, 85], aggressive quantization [86, 87, 88, 89], and neural architecture search (NAS) [90, 91, 92, 93, 94, 95, 54], to push the envelop of accuracy vs. robustness trade-off. Thanks to all these efforts, bringing the power of deep nets to the cost-constrained microcontroller-based edge devices is now a real possibility [96]. However, almost all these works do not focus on the robustness aspects discussed in Sec. 1.1. Only recently early exploration in this direction was started by combining adversarial training with pruning/NAS techniques [53, 85, 54].

All of the works discussed above improve accuracy vs. cost trade-off within the constraints of the current hardware. In order to push their envelope further, one needs to address today's hardware limitations. For instance, as the channel lengths continue to reduce beyond a few tens of nanometers, the energy and delay reductions due to CMOS scaling have stagnated. Furthermore, while multiple beyond-CMOS devices are under exploration, none of them significantly outperform CMOS in terms of gate-level switching energy and delay [97, 98], as evident in Fig. 1.4(a). Even in CMOS implementations, accessing data from memory is more expensive than doing computations on that data [18], as shown in Fig. 1.4(b). For example, fetching 32 bit word from register file or on-chip SRAM is almost  $10 \times$  more energy-expensive

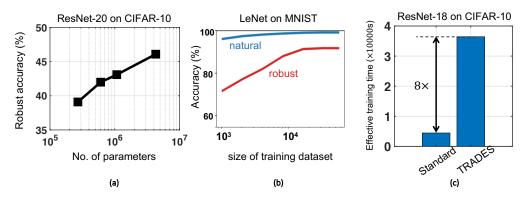

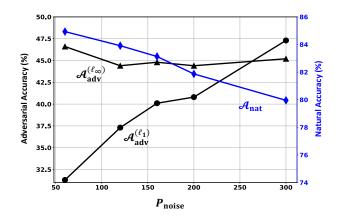

Figure 1.5: Interwoven robustness and cost challenges: Robust accuracy vs. (a) no. of model parameters [99] for ResNet-20 network trained on CIFAR-10 dataset, (b) natural and robust accuracy vs. size of training dataset for MNIST dataset [100], and (c) comparison of effective training time for standard training and TRADES adversarial training [22].

than 32 bit int ADD operation. Furthermore, off-chip DRAM accesses are almost  $10 \times$  more energy-expensive than even iso-precision int MULT. This challenge is particularly exacerbated for deep net implementations due to their large parameter requirements. In the Sec. 1.3, we will discuss how the current approaches addressing these challenges, in fact, requires one to focus on robustness vs. cost trade-off due to hardware noise.

## 1.3 Dissertation Contribution: Improving Robustness vs. Cost Trade-off

As discussed in Sec. 1.1 and Sec. 1.2 the accuracy vs. robustness trade-off and accuracy vs. cost trade-off are primarily explored independently today. However, they start getting interwoven as one attempts to design ML implementations at the limits of accuracy, robustness, and efficiency. For instance, while pushing the envelop of accuracy vs. robustness trade-off via AT, one begins to run into prohibitive increase in training and inference costs as shown in Fig. 1.5, *i.e.* one needs bigger models [99, 104] (Fig. 1.5(a)), larger training dataset [100, 105] (Fig. 1.5(a)), and at times, even  $8 \times$ -to- $10 \times$  more complex training algorithms [22, 106, 107]. On the other hand, quest for achieving leaps of energy-efficiency in hardware requires addressing the robustness challenge in the presence of hardware noise [108, 65, 5]. For instance, prominent beyond-CMOS devices, such as RRAM and spin-based devices,

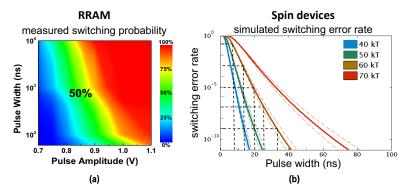

Figure 1.6: Intrinsically non-deterministic nature of emerging beyond CMOS devices: (a) measured switching probability vs. pulse width vs. pulse amplitude trade-off for RRAM devices [101], (b) simulated switching error rate vs. pulse width trade-off for spin-based devices with different energy barriers [102, 103].

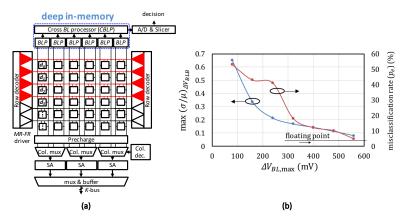

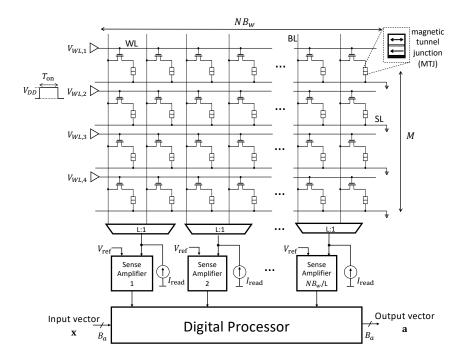

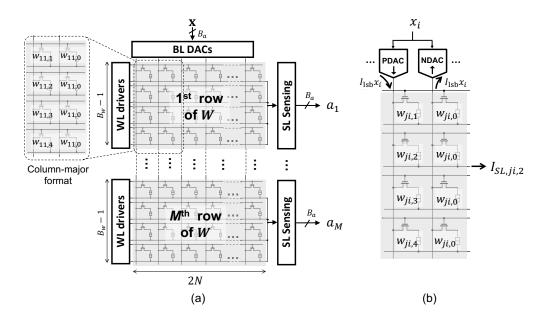

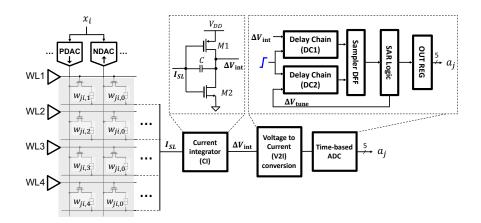

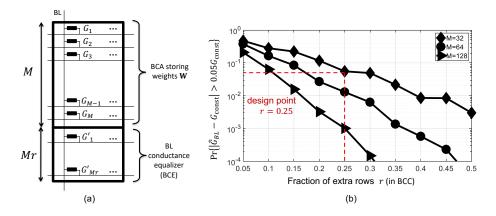

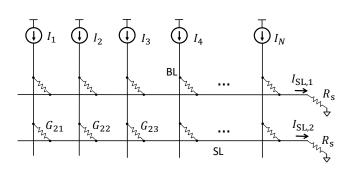

are inherently non-deterministic in nature [102, 101, 103]. Their switching error rates increase with the reduction in their switching energy/delay as shown in Fig. 1.6. Similar trends are also observed in one of the promising approach called *in-memory computing* (IMC), where one strives to embed computation within the bitcell array (BCA) and its peripherals in order reduce the memory access costs. Due to severe area constraints in the BCA, such in-memory computation often needs to happen in the analog domain along bitlines (BLs) by using change in BL voltage  $\Delta V_{BLB}$  to represent multibit information (see *e.g.* Fig. 1.7(a)). With decreasing BL discharge, a key knob for reducing energy cost of SRAM read, the variations in  $\Delta V_{BLB}$  increase as shown in Fig. 1.7(b) [65]. It adversely affects the classifier accuracy (also shown in Fig. 1.7(b) [65]) indicating the need for improving robustness against hardware noise to achieve maximum energy benefits.

In summary, improving the accuracy vs. robustness trade-off in the presence of data noise exacerbates the need for cost-efficiency, while one needs to achieve robustness against hardware noise to further enhance the accuracy vs. cost trade-off. To address this predicament, we believe that one needs to focus explicitly on improving the robustness vs. cost trade-off. Specifically, we ask following fundamental questions:

How should the noise be managed in order to enhance robustness vs. cost trade-off in ML systems? Is noise always a problem that should be mitigated? Can it be exploited as a feature?

Figure 1.7: Need for robustness against hardware noise in in-memory computing: (a) deep in-memory architecture (DIMA), and (b) variations in  $\Delta V_{BLB}$ and their impact on classifier accuracy as a function of maximum BL discharge, a key knob controlling energy consumption.

This dissertation attempts to address these questions in diverse problem settings across the design stack. Based on our work, we find that noise need not always be mitigated, but the robustness vs. cost trade-off in the presence of both hardware noise and data noise can be enhanced via *noise shaping*. For example, in Chapter 2, we show how hardware noise distribution in spintronic digital implementations can be shaped to achieve robust computation even in the presence of error-prone logic gates. As an another example, in Chapter 7, we demonstrate how *shaped noise* can be specifically introduced in the deep nets to achieve high adversarial robustness at significantly lower training cost.

## 1.4 Dissertation Organization

Our contributions in this dissertation are organized as follows:

Chapter 2 explores how the noise distribution in spin-based digital implementations can be shaped by exploiting inherent trade-off between error rate, energy, and delay for spin-based logic gates. Such noise shaping enabled efficient error compensation via a Shannon-inspired model of computation. Resulting classifier implementation is  $1000 \times$  more tolerant to gate-level switching error rate compared to the conventional implementation. These robustness improvements are translated into energy-efficiency gains.

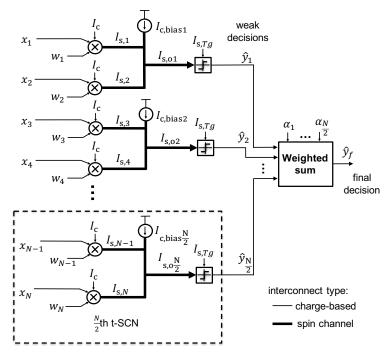

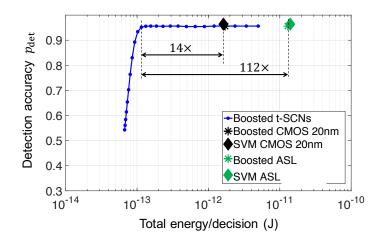

**Chapter 3** demonstrates how the impact of spin device noise is fundamentally changed via novel circuit design and algorithmic techniques to achieve energy-efficient inference implementations. In particular, this chapter presents *spin channel networks (SCN)* – a novel spin-based circuit design approach that exploit exponential decay of spin current to efficiently realize multi-bit dot product computation. Furthermore, Adaptive Boosting (AdaBoost) framework is employed to design multiple isolated tiny spin channel networks (t-SCNs) that work in unison to solve an arbitrary binary classification task. Such boosted t-SCNs achieve  $112 \times -to-22.5 \times$  and  $14 \times -to-2.5 \times$ higher energy-efficiency over conventional spin-based and 20 nm CMOS designs, respectively, when realizing 10-to-100-dimensional binary classifiers.

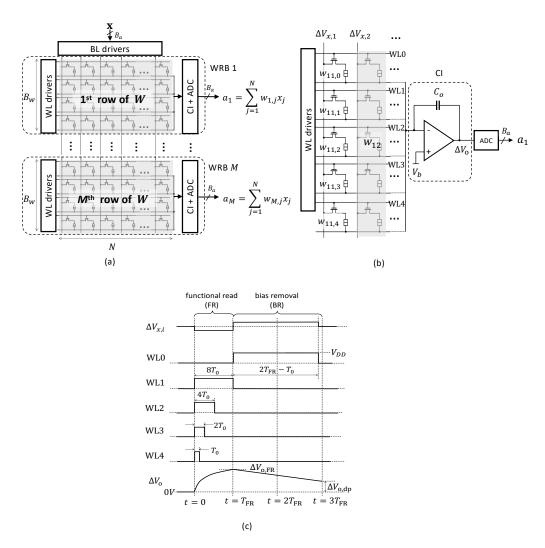

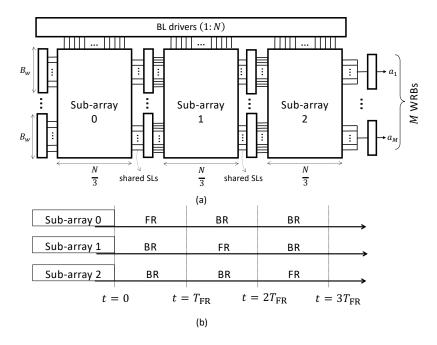

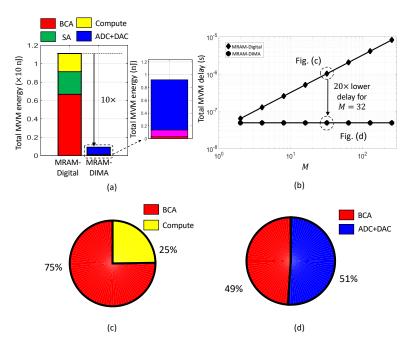

Chapter 4 proposes an MRAM-based deep in-memory architecture to achieve multi-bit matrix-vector multiplication (MVM) within a single read operation of MRAM bitcell array (MRAM-BCA). The MRAM-BCA peripheral circuits are modified to potentially achieve such multi-bit computation at  $20 \times$  and  $10 \times$  lower energy and delay, respectively, compared to digital MRAM implementation. The robustness challenges that emerge as a byproduct of achieved energy benefits are further characterized, and techniques to address them are discussed.

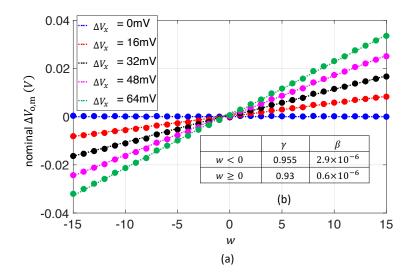

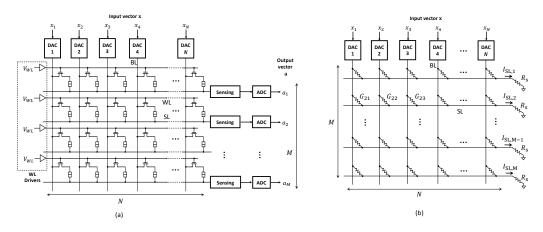

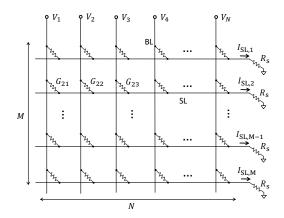

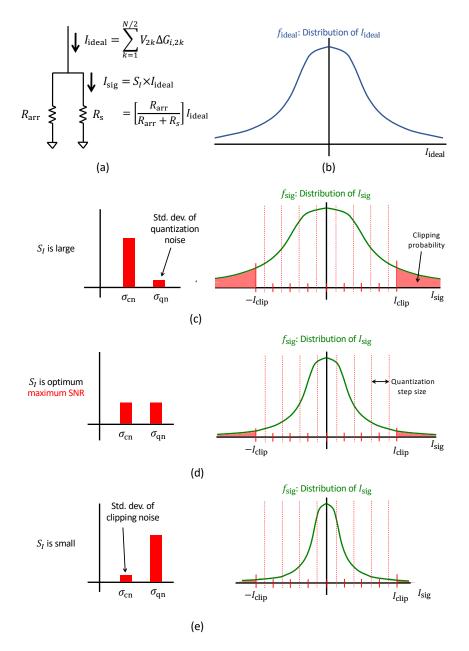

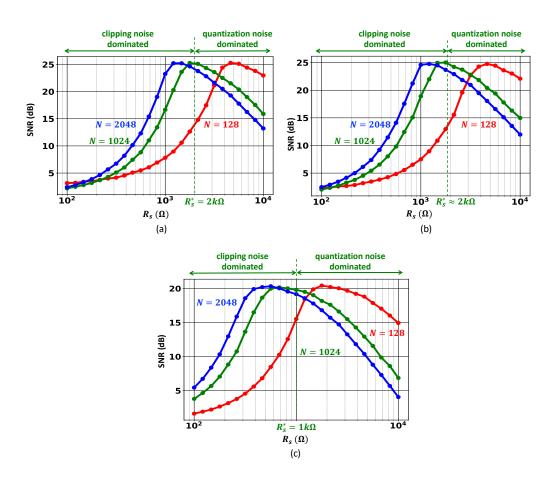

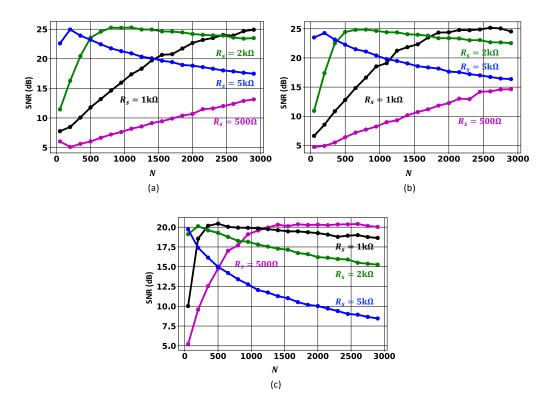

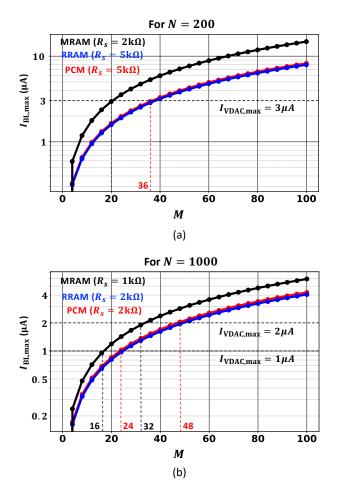

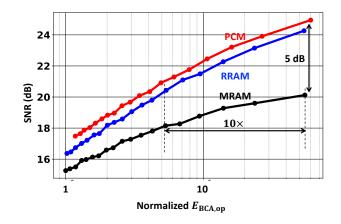

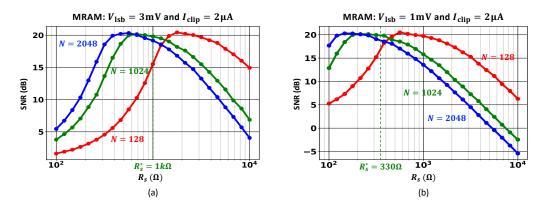

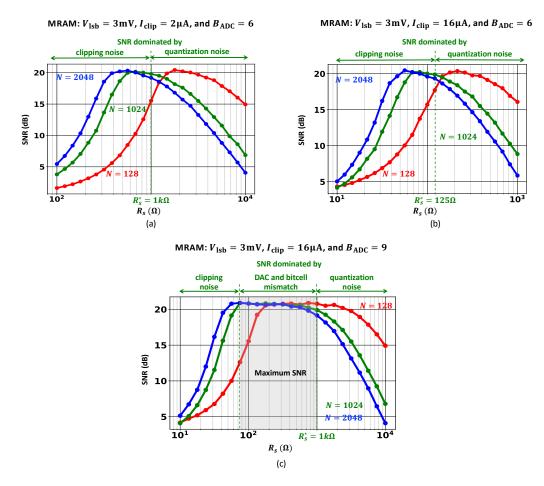

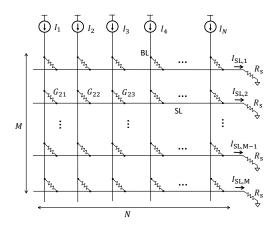

**Chapter 5** presents signal-to-noise ratio (SNR) analysis for in-memory computing in resistive crossbar arrays. Specifically, we show how the circuitlevel specifications of peripherals affect SNR as a function of array size, sensing circuit impedance, as well as energy per operation for PCM, MRAM, and RRAM. The noise sources considered are mismatch in the conductance and input digital-to-analog converters (DACs), as well as, clipping and quantization noise in the readout circuits. We conclude by proving some design guidelines for appropriate noise budgeting in order to achieve accurate inmemory matrix vector multiplication in the in-memory crossbar arrays.

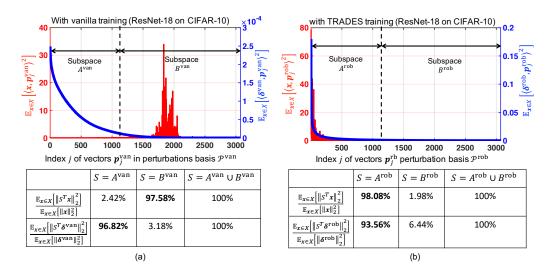

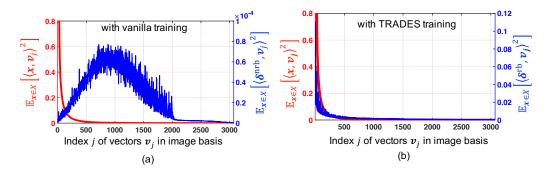

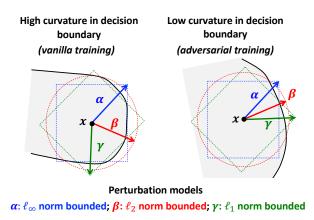

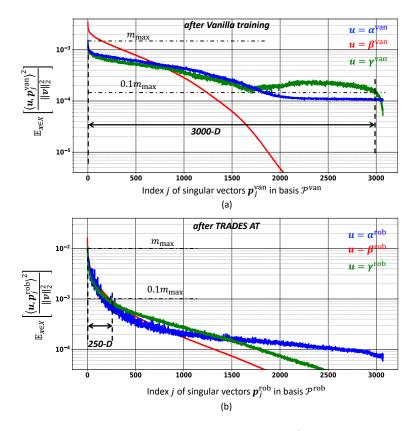

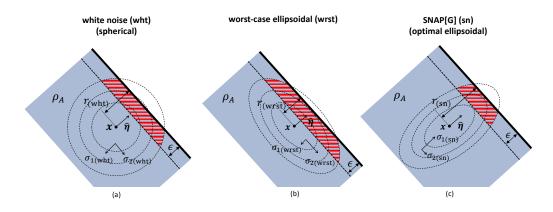

**Chapter 6** aims to develop deeper understanding of geometric orientations of adversarial perturbations of deep nets via subspace analysis for image classification tasks. Specifically, we propose and validate the hypotheses about orientations of dominant subspaces of adversarial perturbations. We demonstrate how changes in the curvature of decision boundary of the deep nets affects the orientations of the adversarial perturbations. The hypotheses and insights developed in this chapter lead to noise shaping and augmentation techniques proposed in Chapter 7.

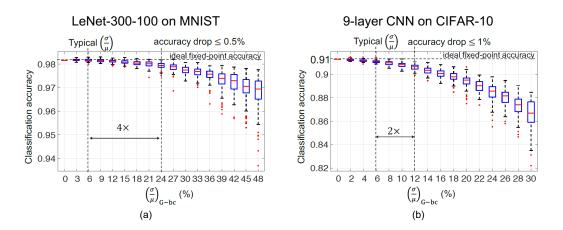

**Chapter 7** explores how shaped noise can be employed as to enhance adversarial robustness vs. cost trade-off in deep nets based on the insights from Chapter 6. Specifically, we propose shaped noise augmented processing (SNAP), a method to efficiently train deep nets that are robust to multiple types of adversarial perturbations, simultaneously. SNAP prepends a deep net with a shaped noise augmentation layer whose distribution is learned along with the network parameters using any established robust training framework. Based on extensive comparisons with nine state-of-theart (SOTA) robust training frameworks, we show that SNAP achieves the best robustness vs. training cost trade-off. Furthermore, thanks to the computational efficiency of our approach, we report for the first time ResNet-50 (ResNet-101) networks on ImageNet that achieve > 30% robust accuracy against the union of  $(\ell_{\infty}, \ell_2, \ell_1)$  adversarial perturbations.

**Chapter 8** outlines a few potential extensions and future research directions.

## CHAPTER 2

## ROBUST SPINTRONICS VIA SHANNON-INSPIRED APPROACH

## 2.1 Overview

As we discussed in Chapter 1, CMOS scaling is slowing down and none of the beyond-CMOS devices are yet able to significantly outperform CMOS [97, 98]. Spin-based computational devices built with nanomagnets and spinpolarized transport have emerged as a viable beyond CMOS option, due to their following favorable attributes: (i) non-volatility, (ii) higher logical efficiency, and (iii) high integration density and compatibility with the state-ofart back-end electronics manufacturing processes. These devices are a subset of the beyond-CMOS devices which include devices based on electron spin [109, 103] and magneto-electric [110, 111] phenomena. However, spin-based devices are not competitive to CMOS [98], in terms of switching energy and delay, due to their high energy-delay requirements to achieve deterministic switching [102, 112, 113, 114]. As switching energy or delay is reduced, their switching error probability increases, rendering them incompatible with the required determinism of the digital logic.

In this chapter, we demonstrate how spin-based digital implementations of ML classifiers can be made robust to a significant increase in the switching error probability of their component logic gates. We employ the Shannon-inspired model of computation [5] to enhance such gate-level switching error tolerance. In the Shannon-inspired framework, hardware errors are engineered and then efficiently compensated via the introduction of tailored redundancy, in the spirit of Shannon's theory for communications [115]. The detailed contributions of this chapter are as follows:

• We characterize the  $\epsilon$ -energy-delay trade-off for ASL gates to enable non-uniform  $\epsilon$  assignments across logic gates.

- We propose logic-level path delay reallocation techniques to assign appropriate error rates to individual gates such that the resulting output error distributions are shaped to facilitate error compensation.

- We propose a novel maximum likelihood (ML) error compensation scheme that exploits these shaped output error statistics to compensate the errors efficiently.

- We demonstrate a 1000× higher average error rate tolerance and a 3× lower energy-per-decision for an ASL-based digital support vector machine (SVM) implementation, while maintaining its system-level classification accuracy.

## 2.2 Background

#### 2.2.1 All Spin Logic Device

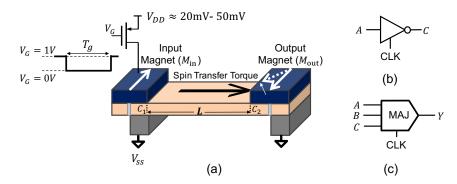

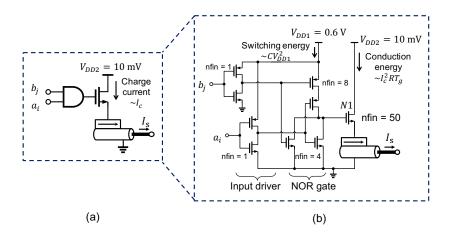

Figure 2.1(a) shows a diagram of an ASL inverter. It consists of two nanomagnets separated by a conducting channel of length L. The input magnet  $(M_{\rm in})$  polarizes the supply current passing through it. This creates a spin concentration gradient and propagates a spin current in the channel of length L. This spin current, in turn, exerts a torque on the magnetization of the output magnet  $(M_{\rm out})$  forcing it to switch. Since the magnets are non-volatile, they retain the magnetization vector state when the supply current is switched off.

Electrical current in the order of  $10 \,\mu A$ -to- $100 \,\mu A$  is required to generate sufficient spin current to switch the output magnet. Since the nanomagnets and the spin channel are metallic, the equivalent electrical resistance across the nanomagnet-channel stack is small (few  $\Omega$ s), enabling these devices to operate at ultra-low supply voltages. However, the electrical current through the input nanomagnet flows irrespective of output activity, causing high static energy consumption. The nanomagnets, being non-volatile, retain the magnetization vector state even when the supply current is switched off. Hence, researchers propose to clock these devices via a MOSFET [116, 117], operating in the linear region, which acts as a switch turning ON the ASL device only when it needs to compute as shown in Fig. 2.1(a). The ON

Figure 2.1: All Spin Logic (ASL) (a) diagram of clocked ASL inverter gate [118, 117], (b) clocked ASL inverter symbol, and (c) clocked ASL 3-majority gate symbol.

duration  $T_g$  of clock can be externally controlled for each gate. Thus, the energy consumption of the clocked ASL gates is completely determined by  $T_g$  and the ON current of the gating MOSFET. Figure 2.1(b) and 2.1(c) show the logical symbols for clocked ASL inverter and 3-majority gate, respectively. Pajouhi *et al.* [116] proposed to share a single MOSFET across multiple nanomagnets by electrically stacking their supply terminals in series to significantly amortize the clock pulse generation and MOSFET switching overheads. In this work, we assume such amortization described in [116] and focus on the impact of gate-level switching errors on the final output.

#### 2.2.2 Support Vector Machine

Linear SVM [119] is a simple and popular machine learning algorithm for binary classification. The SVM learns a hyperplane to separate the training feature vectors into two regions, each corresponding to one class, as shown below:  $\hat{z}=1$

$$\mathbf{w}^T \mathbf{x} + b \underset{\hat{z}=-1}{\overset{z=-1}{\gtrless}} 0$$

where  $\mathbf{w}$  and b denote the trained weight vector and bias representing the separating hyperplane, respectively,  $\mathbf{x}$  denotes the *N*-dimensional input feature vector, and  $\hat{z}$  denotes the predicted label. If the true label is denoted by z, the accuracy of SVM is given by the probability of classification error  $p_e = \Pr{\{\hat{z} \neq z\}}$ , which can be empirically estimated for a given dataset.

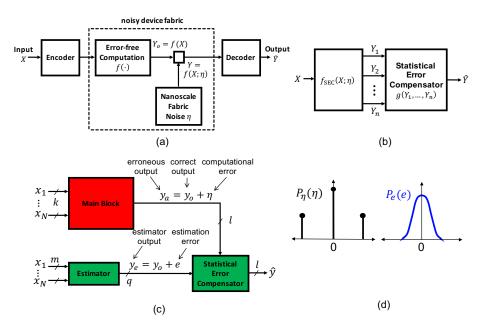

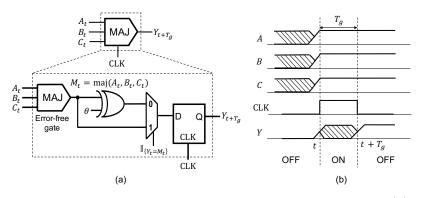

Figure 2.2: The Shannon-inspired model of computation: (a) model, (b) statistical error compensation (SEC), (c) algorithmic noise tolerance (ANT), a special case of SEC, where the error compensator combines two unreliable outputs  $y_a$  and  $y_e$ , (d) illustrative distributions of computational error  $\eta$ , estimation error e that lead to a low-complexity and accurate error compensator.

#### 2.2.3 Shannon-inspired Model of Computation

The Shannon-inspired model of computation [5] (Fig. 2.2(a)) comprises an encoder, a noise-free computation of the desired correct output  $Y_o = f(X)$  being corrupted by noise in nanoscale fabrics parametrized by variable  $\eta$  to generate the observed output  $Y = f(X; \eta)$  of the error-prone device fabric (the channel), followed by the decoder that recovers the corrected output  $\hat{Y}$ . In Fig. 2.2(a), all variables  $(X, Y_o, \eta, Y, \hat{Y})$  are random variables. In this chapter, we use capitals to denote random variables and small letters to denote their particular instance. For example, Y denotes a random variable, while y denotes a specific value of Y.

Statistical error compensation (SEC) (Fig. 2.2(b)), one class of the design techniques within the Shannon-inspired framework [5, 120], introduces a statistical error compensator block as a decoder, which combines multiple unreliable outputs  $Y_1, \ldots, Y_n$  to compute corrected output  $\hat{Y}$ . Algorithmic noise tolerance (ANT) (Fig. 2.2(c)) is a special case of SEC where the error compensator combines two unreliable outputs  $y_a$  and  $y_e$ . ANT consists of a main block designed using unreliable/noisy device fabric accounts for 85%- 90% of total gate count complexity. It strives to compute correct output  $y_o$ , but ends up computing  $y_a$  due to the unreliability of the underlying device fabric. ANT augments the main block with a low complexity estimator that computes an estimate  $y_e$  of the correct output  $y_o$ . Under the assumption of additive noise model, the main block and estimator outputs are described as follows:

$$y_a = y_o + \eta \tag{2.1}$$

$$y_e = y_o + e \tag{2.2}$$

where  $\eta$  is a system-level hardware error observed at the main block output, and e is the estimation error incurred due to inherent lower complexity of the estimator.

The estimator and the error compensator are designed using reliable, and hence energy-inefficient, circuits, constituting the error compensation overhead in ANT. Hence, their combined complexity (in terms of gate count) needs to be significantly ( $\approx$  5-to-10×) smaller than the main block. Previously, it has been shown that [7, 121, 122] the complexity of the error compensator can be reduced by shaping the distributions of  $\eta$  and e,  $P_{\eta}(\eta)$ and  $P_e(e)$ , respectively, to be disparate from each other as shown in Fig. 2.2(b) and 2.2(c). In particular, a dense  $P_e(e)$  is realized by introducing a reduced-precision estimator, while a sparse  $P_{\eta}(\eta)$  is realized by permitting MSB errors in the LSB-first architectures [121, 123, 63, 122]. Various design techniques to reduce the overhead of the estimator and the error compensator have been proposed [63, 124, 125, 123].

#### 2.2.4 Mutual Information (MI)

The mutual information (MI) I(X;Y) between two random variables X and Y quantifies the amount of information conveyed about X by knowing the value of Y, and vice versa. The MI I(X;Y) is defined as:

$$I(X;Y) = H(X) - H(X|Y) = H(Y) - H(Y|X)$$

(2.3)

where H(X) and H(X|Y) denote the entropy of X and conditional entropy of X given Y, respectively. The entropy H(X) of a random vari-

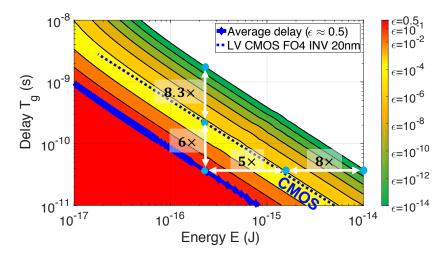

Figure 2.3: Trade-off between switching error rate  $\epsilon$ , switching energy  $E_g$ , and switching delay  $T_g$  for a clocked ASL inverter gate.

able X quantifies the uncertainty about the value of X, and is a function of its probability distribution. In this chapter, we use MI metric to show that the Shannon-inspired model of computation (Fig. 2.2) enhances the MI  $I(Y_o; Y_a, Y_e)$ , thereby enabling an accurate recovery of  $y_o$  from  $y_a$  and  $y_e$ .

## 2.3 Modeling Stochasticity of ASL Devices

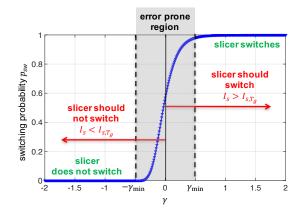

In this section, we develop a gate-level model to capture the inherent devicelevel stochasticity of ASL at the circuit and architecture level. Even after receiving supply current  $I_{\rm on}$  (>  $I_{\rm crit}$ ) at the input nanomagnet, the output nanomagnet of the ASL gate may not switch due to the presence of Langevin thermal noise [102, 112, 113, 114], where  $I_{\rm crit}$  denotes the minimum current required for nanomagnetic switching. In this chapter, we refer to this probabilistic event as *switching error*, and its probability  $\epsilon$  as the *switching error rate*. In [102], an analytical expression for  $\epsilon$  was derived by employing the Fokker-Planck equation for magnetization vector switching dynamics governed by the fundamental LLG equation and was validated against Landau-Lifshitz simulations of a macrospin including appropriate thermal field. This analysis indicates a gate-level trade-off between switching error rate  $\epsilon$ , the switching energy  $E_g$ , and the switching delay  $T_g$  of ASL gates.

Figure 2.3 shows the iso-error rate delay vs. energy contours of an ASL inverter at various error rates. As expected, the error rate decreases with

Figure 2.4: The modified  $\epsilon$ -noisy gate model for clocked ASL: (a) a gatelevel schematic emulating the stochastic behavior of a non-volatile, clocked ASL 3-majority gate, and (b) timing diagram illustrating the phase where the gate is ON and OFF.

Figure 2.5: RCA with gate-level uniform error rate  $\epsilon$  assignment operating at total delay of 1.24 ns: (a) schematic of 8 bit RCA showing all gates operating at  $\epsilon = \epsilon_{\rm cp-avg} = 10^{-2}$ , and error distribution  $P_{\eta}(\eta)$  for a 15 bit RCA (b) when  $\epsilon = \epsilon_{\rm cp-avg} = 10^{-2}$ ,  $E_{\rm RCA15} = 90$  fJ, and (c) when  $\epsilon_{\rm cp-avg} = 10^{-1}$ ,  $E_{\rm RCA15} = 60$  fJ, where  $E_{\rm RCA15}$  denotes total switching energy of 15 bit RCA.

Figure 2.6: RCA with shaped error statistics operating at total delay of 1.24 ns: (a) schematic of an 8 bit RCA illustrating spatial distribution of gatelevel  $\epsilon$  after applying PDB and PDR, and error distribution  $P_{\eta}(\eta)$  for a 15 bit RCA (b) when  $\epsilon_{\text{cp-avg}} = 10^{-2}$ ,  $E_{\text{RCA15}} = 90$  fJ, and (c) when  $\epsilon_{\text{cp-avg}} = 10^{-1}$ ,  $E_{\text{RCA15}} = 60$  fJ. The colors in (a) approximately convey the error rates of the gates as per the color code in Fig. 2.3.

increasing energy or delay. In fact, when  $I_{\rm on} \gg I_{\rm crit}$ , the expression for  $\epsilon$  [102] can be simplified via Taylor series approximation to:

$$\epsilon(E_g, T_g) = \beta \exp(-\zeta \sqrt{E_g T_g}) \tag{2.4}$$

where  $\beta$  and  $\zeta$  are device-dependent constants A 3-majority ASL gate operates with error rate of  $\epsilon(E_g, T_g)$  if all its inputs are equal, and with higher error rate of  $\epsilon(\frac{E_g}{3}, T_g)$  otherwise. In this work, we conservatively upper-bound the error rate of 3-majority gate to  $\epsilon(\frac{E_g}{3}, T_g)$ . Equation (2.4) explains the observed linearity of the contours at higher values of  $E_g$  or  $T_g$  in Fig. 2.3. We further note that ASL inverter consumes  $8 \times$  more energy compared to 20 nm CMOS FO4 inverter [103] at  $\epsilon = 10^{-14}$  and at identical switching delays. Hence, ASL-based conventional digital architectures remain non-competitive with respect to present day CMOS. As  $\epsilon$  is increased beyond 1%, the ASL inverter becomes more energy-efficient than CMOS, demonstrating the potential for achieving energy-efficiency, if one can tolerate such high gate-level error rates while maintaining final system-level accuracy. We develop a modified  $\epsilon$ -noisy gate model (Fig. 2.4(a)) to describe a clocked ASL gate, which comprehends its underlying stochastic behavior, while being sufficiently abstract to permit the design and analysis of complex ASL networks. The modified  $\epsilon$ -noisy gate model captures: (a) the logic-level manifestation of device-level stochasticity, (b) the input dependence of ASL errors due to the non-volatility of the nanomagnets, i.e., the ASL gate makes an error only when the output nanomagnet fails to switch when it should, implying a dependence of the error event on the input data, and (c) the role of the CLK terminal in the gate operation.

Figure 2.4(b) shows the timing diagram for the modified  $\epsilon$ -noisy model. The Boolean inputs A, B, and C are applied at time t. The ASL gate generates its output Y at time  $t + T_g$  where  $T_g$  is the switching delay assigned to the ASL gate. The model comprises of an ideal noise-free Boolean gate whose output  $M_t = \text{maj}\{A_t, B_t, C_t\}$  is EXORed with a Bernoulli random variable  $\theta$  with parameter  $\epsilon$ , i.e.,  $\Pr\{\theta = 1\} = \epsilon$ . The output selector (implemented using a multiplexer in Fig. 2.4(b)) computes the final output  $Y_{t+T_g}$  by choosing either the output of the EXOR gate  $M_t \oplus \theta$  or the error-free output  $M_t$ . The D flip-flop models the non-volatility, i.e., the ability to retain the output when CLK = 0. The EXOR gate output is chosen only if  $Y_t \neq M_t$ , capturing the fact that the switching error can occur only if the output nanomagnet is required to switch.

## 2.4 Shannon-inspired ASL Architecture

In this section, we describe how the Shannon-inspired approach can be applied to clocked ASL networks to increase their tolerance to switching errors. In Sec. 2.4.1, we propose path delay reallocation techniques that exploit the gate-level trade-off between  $\epsilon$ ,  $E_g$ , and  $T_g$  to shape the output error statistics and thereby ease error recovery. In Sec. 2.4.2, we propose a novel fusion block architecture to compensate for the switching errors.

#### 2.4.1 Shaping Error Statistics

In clocked digital ASL networks, the random switching errors occur at the output of every logic gate as modeled in Sec. 2.3. The impact of such gate-

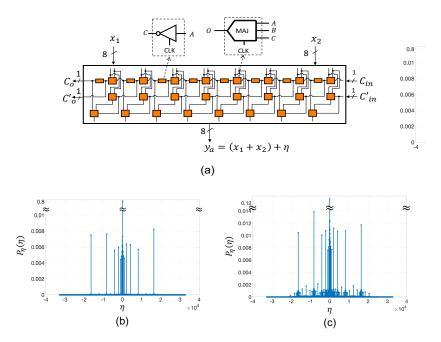

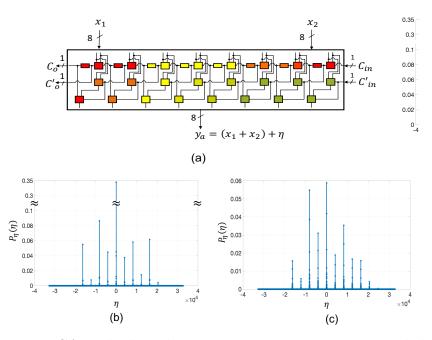

level errors accumulates as the input propagates to the final output. For example, consider a clocked ASL-based 8 bit ripple carry adder (RCA) consisting of all ASL gates operating at identical switching delay  $T_g$ , switching energy per nanomagnet  $E_g$ , and hence, identical  $\epsilon(E_g, T_g)$  as shown in Fig. 2.5(a). The resulting distribution  $P_\eta(\eta)$  of output error  $\eta$  for a 15 bit RCA is dense as shown in Fig. 2.5(b) and 2.5(c) for  $\epsilon(E_g, T_g) = 10^{-2}$ and  $\epsilon(E_g, T_g) = 10^{-1}$ , respectively. Brute force compensation of the errors having such distributions can be computationally expensive as discussed in Sec. 2.4.2. We propose error statistics shaping techniques to impose a structure on  $P_\eta(\eta)$  to reduce the complexity of error compensation.

We exploit the error rate, energy, and delay trade-off of the clocked ASL gates (shown in Fig. 2.3) to shape the distribution of error  $\eta$ . In particular, we control the gate-level switching delay via clock pulse width modulation as described in Sec. 2.2.1 [117, 116]. Exploiting this degree-of-freedom, we propose two logic-level delay assignment steps, namely path delay balancing (PDB) and path delay redistribution (PDR). We begin with a logic gate network with all gate delays equal to  $T_g$ . Thus, the critical paths are those with the maximum number of gates  $N_{\rm cp}$  and therefore have the path delay  $T_{\rm cp} = T_g N_{\rm cp}$ . In PDB and PDR steps, the gate delays are reassigned at a constant switching energy (per nanomagnet) of  $E_g$  (moving vertically in Fig. 2.3) and at a constant throughput (identical critical path delay  $T_{\rm cp}$ ) as follows.

#### PDB

In PDB, delays of gates lying on the shorter paths are increased, at a constant energy  $E_g$ , making every gate to lie on one or more critical paths. Thus, PDB reduces error rate of gates on shorter paths, while leaving the original critical path unaltered, now containing gates with highest error rates.

#### PDR

In PDR, the gates delays along all critical paths are further redistributed to further enhance the sparsity of  $P_{\eta}(\eta)$ , while keeping their path delay constant. In particular, the delays of the few gates in the middle of the critical path are increased (lowering  $\epsilon$ ) at the expense of the reduction in the delays (increasing

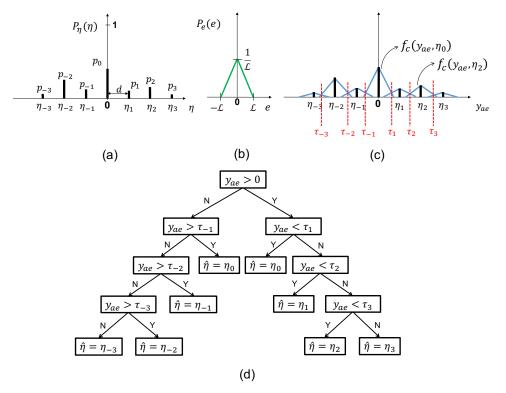

Figure 2.7: Maximum likelihood (ML) error compensation: (a) illustrative  $P_{\eta}(\eta)$  consisting of seven distinct peaks, (b) illustrative  $P_e(e)$ , (c) corresponding  $f_c(y_{ae}, \eta_i)$  defined in (2.8), and (d) TreeCompensator, the resulting ML error compensator having a decision-tree structure.

$\epsilon$ ) of the gates lying at the beginning and at the end of the critical path. Such delay redistribution increases the error rates of the top few MSBs and bottom few LSBs, while reducing the error rates of the other bits in the middle. Doing so results in increased probability of errors having extreme magnitudes (both very high and very low), leading to a highly sparse  $P_{\eta}(\eta)$ .

We define the average device error rate of the clocked ASL network as  $\epsilon_{cp-avg} = \epsilon(E_g, T_{cp-avg})$ , where  $T_{cp-avg} = \frac{T_{cp}}{N_{cp}}$ . Note:  $T_{cp-avg} = T_g$ , when all gates on the critical path have equal delay. Figure 2.6(a) illustrates the spatial distribution in gate-level switching error rates (employing the color code from Fig. 2.3) for an 8 bit clocked ASL-based RCA after applying both PDB and PDR. The resulting  $P_{\eta}(\eta)$  for a 15 bit RCA subject to PDB and PDR is shown in Fig. 2.6(b) and (c) for  $\epsilon_{cp-avg} = 10^{-2}$  and  $\epsilon_{cp-avg} = 10^{-1}$ , respectively. Compared to the distributions in 2.5(b) and (c), the distributions in 2.6(b) and (c) are sparse, i.e., they have distinct well-separated peaks with relatively smaller spread around them.

Next, we show that error statistics shaping via PDB and PDR preserves the information in the erroneous output  $y_a$  about the correct output  $y_o$ , which can be quantified via the MI  $I(Y_a; Y_o)$ . We empirically estimate  $I(Y_a; Y_o)$  for the 15 bit RCA example in Fig. 2.5 and Fig. 2.6. For an error-free RCA,  $I(Y_a; Y_o) = 13.98$  bits, which drops to 6.18 bits, with all gates are operating at an identical error rate of  $\epsilon_{cp-avg} = 10^{-1}$ . The resulting  $P_{\eta}(\eta)$  in Fig. 2.5(c) is dense. The shaped error statistics in Fig. 2.6(c) enhances MI  $I(Y_a; Y_o)$ to 11.15 bits. Noted that there exist multiple methods of shaping  $P_{\eta}(\eta)$  to increase the MI. Furthermore, a high value of  $I(Y_a; Y_o)$  only guarantees the existence of an error compensation scheme to reliably recover  $y_o$  from  $y_a$ . However, such scheme need not be efficient. In Sec. 2.4.2, we derive a nearoptimal low-complexity error compensation scheme that exploits the sparsity of  $P_{\eta}(\eta)$ .

#### 2.4.2 Maximum Likelihood (ML) Error Compensator

The role of the fusion block in SEC is to compute the estimate  $\hat{y}$  of the correct output  $y_o$ , as a function of two error-prone observations  $y_a$  and  $y_e$  (see Fig. 2.2(a)). One approach to make  $\hat{y}$  a good estimate of  $y_o$  is to choose  $\hat{y}$  such

Figure 2.8: Digital clocked ASL-based 120-dimensional SVM classifiers: (a) conventional serial architecture with uniform delay assignments, (b) Shannon-inspired architecture.

Figure 2.9: Accuracy vs. energy, error rate trade-off for different digital clocked ASL-based 120-dimensional SVM classifier implementations operating at a fixed decision delay and  $p_{FA}$  of 1%: (a) True positive rate  $p_{TP}$  vs. average device error rate  $\epsilon_{cp-avg}$ , (b)  $p_{TP}$  vs. total classifier energy per decision, (c) mutual information (MI)  $I(Y_o; Y)$  and corresponding classification error rate  $(1 - p_{TP})$  vs.  $\epsilon_{cp-avg}$  curves for serial architecture (black), and after shaping its error  $\eta$  statistics (blue), and Shannon-inspired architecture (red).

that it maximizes the likelihood of the observations  $y_a$  and  $y_e$  as follows:

$$\hat{y} = \arg\max_{y} P_{Y_a, Y_e|Y_o} \left\{ Y_a = y_a, Y_e = y_e \middle| Y_o = y \right\}$$

(2.5)

where  $P_{Y_a,Y_e|Y_o}$  denotes the likelihood of  $Y_a$  and  $Y_e$  given  $Y_o$  and y denotes a free variable in the maximization that is swept over the range of possible values of correct output  $y_o$ . Thus,  $\hat{y}$  is a maximum likelihood (ML) estimate of  $y_o$ . In general, it can be computationally expensive to compute and maximize  $P_{Y_a,Y_e|Y_o}$ . However, the error statistics shaping described in Sec. 2.4.1 significantly reduces the computation of the ML estimate  $\hat{y}$  as shown next.

Noting the independence of  $\eta$  and e conditioned on  $Y_o$  in (2.5), we get,

$$\hat{y} = \arg\max_{y} P_{\eta}(y_a - y) P_e(y_e - y)$$

(2.6)

We employ parametric models for  $P_{\eta}(\eta)$  and  $P_{e}(e)$  [123] as shown in Fig.

2.7(a) and 2.7(b), respectively, to simplify (2.6) to:

$$\hat{y} = y_a - \hat{\eta} \tag{2.7}$$

with  $\hat{\eta}$  given as:

$$\hat{\eta} = \arg \max_{\eta_i} \left[ \underbrace{p_i \mathbb{1}_{\{\eta_i - \mathcal{L} < y_{ae} < \eta_i + \mathcal{L}\}} f_e(-y_{ae} + \eta_i)}_{f_c(y_{ae}, \eta_i)} \right]$$

(2.8)

where  $y_{ae} = y_a - y_e = \eta - e$ ,  $\Pr\{\eta = \eta_i\} = p_i$ ,  $\min_{i,j} |\eta_i - \eta_j| = d$ ,  $\Pr\{|e| < \mathcal{L}\} = 1$ , and  $f_e$  denotes a functional description of  $P_e$  when  $|e| < \mathcal{L}$ .

Given  $y_a$ ,  $y_e$ , a brute-force computation of the ML estimate  $\hat{y}$  requires evaluating (2.7) by calculating RHS of (2.8) for every  $\eta_i$ , and selecting  $\eta_i = \hat{\eta}$ that maximizes it. Figure 2.7(c) illustrates plots of  $f_c(y_{ae}, \eta)$  as a function of  $y_{ae}$  for all values of  $\eta$ . It can be observed that  $\hat{\eta}$  can be approximately computed via comparisons of  $y_{ae}$  with thresholds  $\tau_i$ s. Thus, the ML error compensator has a decision tree structure as shown in Fig. 2.7(d), and is henceforth referred to as a TreeCompensator. The thresholds  $\tau_i$ s in the TreeCompensator are a function of error distributions  $P_{\eta}$  and  $P_e$ . For a given implementation, these distributions can be characterized once during simulations, or one-time calibration phase of the prototype chip. Once the thresholds are computed offline and stored, the TreeCompensator can be implemented efficiently using only a few subtracters.

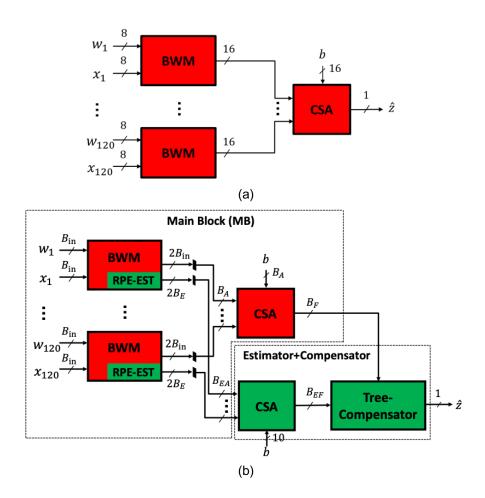

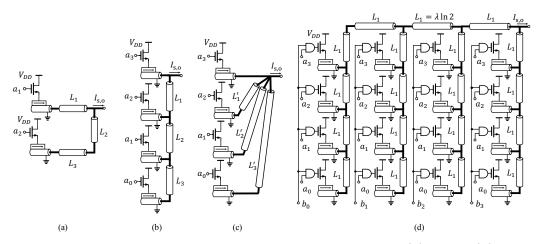

## 2.4.3 Digital Clocked ASL-based Dot Product Implementations

Figure 2.8(a) shows the conventional serial architecture of a 120-dimensional SVM classifier. It employs 8 bit signed Baugh Wooley multipliers (BWM) and a carry save adder (CSA). All gates in this architecture operate at identical error rates. The Shannon-inspired architecture in Fig. 2.8(b) employs the conventional serial architecture as the main block (MB), and applies PDB and PDR to shape its output error distribution. Since PDB and PDR techniques make some gates operate at a lower error rate, few reliable intermediate signals in BWMs can be employed as the estimates of the BWM outputs indicated via green reduced-precision embedded estimator (RPE-EST)

Figure 2.10: Impact of non-idealities and process variations on the Shannoninspired implementation: (a)  $p_{\rm TP}$  vs  $\epsilon_{\rm cp-avg}$  trade-off for Shannon-inspired implementation having 46 distinct clock pulse widths, (b)  $p_{\rm TP}$  box plot for different levels of static within-die process variations measured in terms of  $\frac{\sigma}{\mu}$  $E_b$ ,  $\alpha$ , and  $I_{\rm on}$  for Shannon-inspired implementation having 46 distinct clock pulse widths, and (c)  $p_{\rm TP}$  box plot as a function of extent of dynamic clock network variations  $\frac{\beta}{T_{\rm g,min}}$  for the Shannon-inspired implementation having 46 distinct clock pulse widths, and  $\frac{\sigma}{\mu}$  of  $E_b$ ,  $\alpha$ , and  $I_{\rm on}$  set at 4%, 5%, and 7%, respectively.

blocks in BWMs, similar to techniques discussed in [63] to reduce estimator overhead. The additional overhead consists of a CSA and a digital clocked ASL implementation of the TreeCompensator derived in Sec. 2.4.2 to compute error compensated output  $\hat{y}$ . The bit precisions in the estimator and the compensator blocks are primarily dictated by the number of dominant peaks in the sparse shape of the  $\eta$  distribution of the main block. The CSA and the compensator overhead amounts to 11% of the gate complexity of the MB. We assume a low error rate  $\epsilon = 10^{-4} \epsilon_{cp-avg}$  for all the gates in the CSA and TreeCompensator (marked green in Fig. 2.8(b)). We assume that the TreeCompensator computation can be pipelined since it operates only on the final outputs of the MB and the estimator. This allows the gates in the TreeCompensator to operate at a lower energy since its critical path is shorter than that of the MB.

## 2.5 Simulation Results

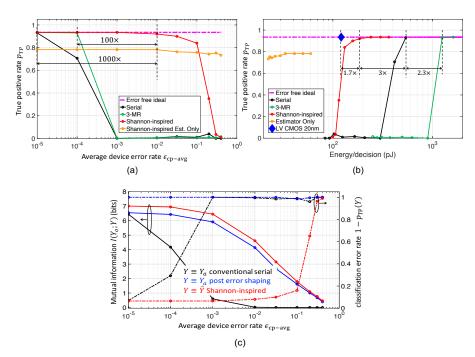

We demonstrate the benefits of the Shannon-inspired model of computation for a digital clocked ASL architecture of SVM classifier used for electroencephalogram (EEG) based seizure detection. The accuracy of the classifier is captured in terms of true positive (TP) rate  $p_{TP}$  and false alarm (FA) rate  $p_{FA}$ , where  $p_{TP} = \Pr\{\hat{z} = 1 | z = 1\}$  and  $p_{FA} = \Pr\{\hat{z} = 1 | z = 0\}$ , and the probabilities are estimated empirically (via leave-one-out cross-validation) [126] for the MIT-CHB EEG dataset [127] by running extensive Monte Carlo simulations. We compare the Shannon-inspired architecture (Fig. 2.8(b)) with (i) clocked ASL-based conventional serial architecture (Fig. 2.8(a)) consisting of 54,332 gates, (ii) clocked ASL-based 3-MR architecture, which replicates the conventional serial architecture thrice and takes a bitwise majority vote on their outputs, and (iii) 20 nm LV CMOS architecture, which consists of the exact same full adder-level logic network as that of the serial architecture. We compare  $p_{TP}$  vs. energy per decision and  $\epsilon_{cp-avg}$  trade-offs at a fixed decision delay of 9.7 ns and  $p_{FA} = 1\%$ .

## 2.5.1 Accuracy vs. $\epsilon_{cp-avg}$ and Energy Trade-off

We observe in Fig. 2.9(a) that Shannon-inspired architecture (Fig. 2.8(b)) can tolerate 1000× higher  $\epsilon_{cp-avg}$  compared to the conventional serial architecture (Fig. 2.8(a)) while maintaining the  $p_{TP}$  close to that of the fixed-point ideal error-free architecture. In particular, the  $p_{TP}$  for Shannon-inspired architecture is close to 93% even though  $\epsilon_{cp-avg}$  is as high as 1%. The 3-MR architecture tolerates an  $\epsilon_{cp-avg}$  up to 0.01%. It is greater than that of the serial architecture but worse by 100× when compared to the Shannon-inspired architecture. Furthermore, we show that intermediate estimator-only output ( $y_e$  in Fig. 2.8(b)) achieves lower accuracy, emphasizing the requirement to combine the two erroneous outputs ( $y_a, y_e$  in Fig. 2.8(b)) to achieve close-to-ideal accuracy.

The Shannon-inspired architecture achieves a  $3 \times$  lower energy compared to the conventional serial architecture (Fig. 2.9(b)) while maintaining  $p_{TP} =$ 93%. The 3-MR architecture, however, consumes  $2.3 \times$  more energy than the serial architecture even though it operates at a higher device error rate. This is because the energy overhead of replication offsets the energy reduction achieved by operating at higher device error rate. However, despite its high error tolerance, the Shannon-inspired architecture still requires  $1.7 \times$  more energy compared to the 20 nm LV CMOS architecture, indicating the need to explore devices with improved energy vs. error rate trade-offs and/or the use of increasingly powerful SEC techniques [128, 129, 61]. We also note in Fig. 2.9(b) that the estimator block (consisting only of the green CSA block in Fig. 2.8(b)) consumes 20% of the total energy ("Estimator Only" curve in Fig. 2.9(b)).

The reason for the effectiveness of the Shannon-inspired model in compensating for errors is the enhancement in MI  $I(Y_o; Y_a)$  due to error statistics shaping via PDB and PDR as shown Fig. 2.9(c). Despite error statistics shaping,  $y_a$  remains a poor estimate of  $y_o$ , as evident from its high classification error rate  $(1 - p_{TP})$ . Since  $I(Y_o; Y_a)$  is high, it implies that  $Y_o$  can be estimated accurately from  $Y_a$ . However, such an error compensator need not be efficient. Hence, in the Shannon-inspired model, we rely on two errorprone observations  $y_a$  and  $y_e$  to estimate  $y_o$  both efficiently and accurately. The MI  $I(Y_o; \hat{Y})$  is even higher than  $I(Y_o; Y_a)$  due to additional information about  $y_o$  contributed by  $y_e$ .

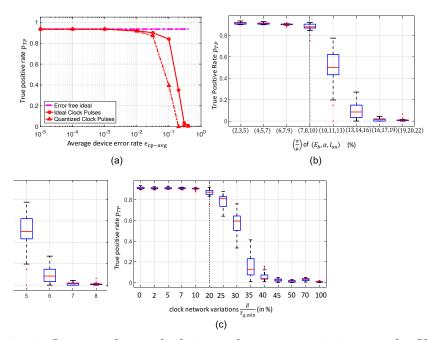

#### 2.5.2 Impact of Non-idealities and Process Variations

Next, we evaluate the tolerance of the proposed Shannon-inspired architecture to various practical non-idealities, such as, finite number of distinct clock pulse widths, process variations, and clock pulse width variations. While PDB and PDR can potentially assign a unique delay to each gate, in practice, those delays need to be further quantized to take one value out of the finite set of available distinct clock pulse widths. Figure 2.10(a) shows the  $p_{TP}$  vs.  $\epsilon_{cp-avg}$  curves for the Shannon-inspired architecture after quantizing the ideal clock pulse widths to 46 distinct pulse widths for the SVM implementation (Fig. 2.8(b)) consisting of 54,332 gates. The number of distinct clock pulse widths is of the same order as the number of gating domains explored in [116]. We observe negligible deterioration in the accuracy of Shannon-inspired architecture (in  $\epsilon_{cp-avg} < 1\%$  regime). Such gate clock pulse width quantization enables amortization of the clock pulse generation circuitry, including the sharing of the clocking transistors across different nanomagnets [116]. The clock network design is further simplified since the quantized clock pulse widths are integer multiples of the shortest reference clock, and multiple parallel dot products (in applications such as filter banks, neural networks) can share a single clock generation circuitry.

Process variations present an additional challenge in beyond-CMOS systems. We evaluate the tolerance of the Shannon-inspired approach to static within-die variations in three device parameters, namely, energy barrier  $E_b$ and damping coefficient  $\alpha$  of the nanomagnets, and clocking transistor ON current  $I_{\rm on}$ . We observe in Fig. 2.10(b) that the Shannon-inspired architecture with quantized clock pulse widths can tolerate a  $3(\frac{\sigma}{\mu})$  variations of up to 24% in each of the three device parameters. When dynamic variations in the clock pulse widths are included in addition to their quantization and process variations, we find in Fig. 2.10(c) that the Shannon-inspired architecture can tolerate a maximum deviation ( $\beta$ ) of 20% of the minimum clock pulse width  $(T_{\rm g,min})$ .

## 2.6 Discussion

In this chapter, we demonstrated how the Shannon-inspired model of computation can be employed to make digital clocked ASL implementations robust to random gate-level switching errors. Such an approach can be extended to many other spintronic devices, such as MESO [110], CoMET [111], as long as they use nanomagnet switching for information processing. Shannon-inspired techniques have previously been applied to CMOS implementations to further reduce their energy consumption via voltage overscaling [7, 129]. In contrast, ASL/spintronics provides a new way to trade off stochasticity with energy by realizing this energy-accuracy trade-off at the device level.

This chapter also showed how the hardware noise distribution in digital clocked ASL-based implementations can be shaped to enhance the robustness vs. cost trade-off discussed in Chapter 1. Such trade-off enhancements enable the use of a highly error prone but scalable physical devices (*e.g.* ASL, MESO, CoMET, MRAM, RRAM, and others) in ML inference implementations by meeting the system-level accuracy requirements despite the device-level unreliability.

# CHAPTER 3

# EFFICIENT INFERENCE VIA SPIN CHANNEL NETWORKS

## 3.1 Overview

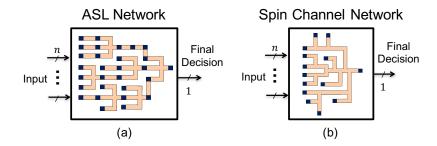

In Chapter 2, we demonstrated how the robustness enhancement can be exploited to improve energy-efficiency of spin-based digital implementations. However, despite 1000× improvement in the robustness to gate-level switching errors, the energy-efficiency improvements fell short of outperforming CMOS implementations. Recently, Ganguly *et al.* [130] took a physicsbased approach for examining the power dissipation in spintronic switches. They identified that nanomagnetic switching consumes  $10^3 \times -to-10^4 \times$  higher switching charge ( $Q_{sw}$ ) compared to the CMOS inverter of comparable size. Such a large gap in the switching charge requirements underscores the fundamentally expensive nature of the nanomagnetic switching. ASL networks (Fig. 3.1(a)) use nanomagnetic switching at the output of every gate to implement digital logic. Hence, they require switching of a large number intermediate nanomagnets leading to a high energy consumption.

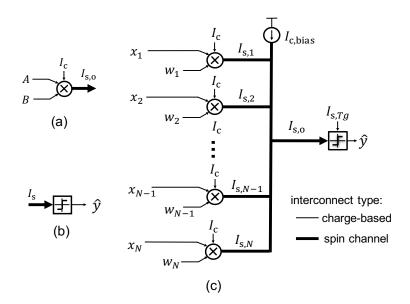

In this chapter, we propose *spin channel networks* (SCN) (Fig. 3.1(b)), where all intermediate nanomagnets are eliminated and all input nanomag-

Figure 3.1: Illustration of (a) an all spin logic (ASL) network, and (b) a spin channel network (SCN) implementing an inference kernel by mapping a large n bit input vector to 1 bit decision.

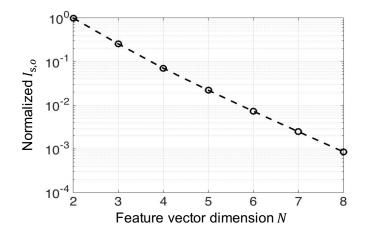

nets contribute to the charge required to switch a single output nanomagnet to represent a final decision, thereby amortizing the energy consumed in switching it. It is particularly suited for inference implementations. While elimination of intermediate nanomagnetic switching is expected to enhance the energy-efficiency, it also presents following two key challenges:

(1) how does one realize arbitrary computation while accumulating analog spin currents from multiple nanomagnets?

(2) will this approach scale with the input vector dimensionality (complexity) of the inference kernel?

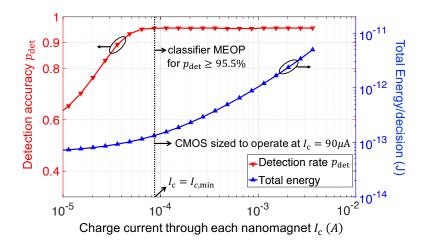

To address challenge (1), we show that the exponential decay property of spin current along the spin channel, a disadvantage in digital ASL networks, can be exploited to achieve energy-efficient analog dot product implementation. To circumvent the challenge (2) we employ Adaptive Boosting (AdaBoost) [131] framework to design multiple isolated tiny spin channel networks (t-SCNs) that work in unison to solve an arbitrary binary classification task. Such boosted t-SCNs achieve  $112 \times -to-22.5 \times$  and  $14 \times -to-2.5 \times$ higher energy-efficiency over conventional ASL-based and 20 nm CMOS designs, respectively, when realizing 10-to-100-dimensional binary classifiers.

## 3.2 Background

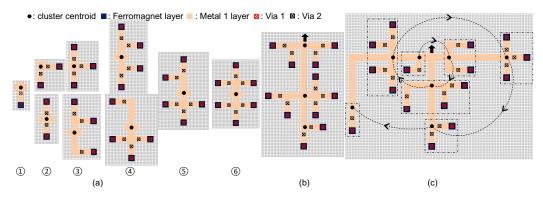

## 3.2.1 ASL Device Primitives

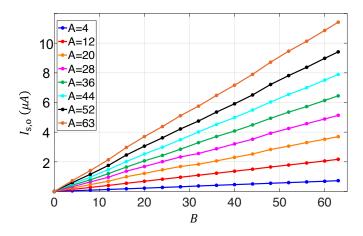

Figure 3.2 identifies two ASL primitives and their functionalities, that will be used to design SCNs in Sec. 3.3. The primitives are nanomagnet with a spin channel and a spin channel. In particular, nanomagnet takes input charge current  $I_c$  and injects proportional spin current  $I_{s,o}$  in the channel, where  $\beta_m$  is a proportionality constant that depends upon the device material and geometry, including the channel length  $L_c$ . The input spin current  $I_{s,in}$  into a spin channel is reduced by a factor of  $e^{\frac{L}{\lambda}}$  to generate an output spin current  $I_{s,o}$ , where L denotes channel length, and  $\lambda$  is the spin flip length [132, 133]. The layouts are obtained by following the  $\lambda$ -rules in [98].