| Imperial College of Science, Technology and Med  | licine |

|--------------------------------------------------|--------|

| Department of Electrical and Electronic Engineer | ering  |

# Resource-Constrained Acquisition Circuits for Next Generation Neural Interfaces

Michal Maslik

## **Declaration of Originality**

I hereby certify that this thesis and all presented material is my own original work except where the use of work of others is acknowledged and appropriately referenced.

## Copyright Declaration

The copyright of this thesis rests with the author. Unless otherwise indicated, its contents are licensed under a Creative Commons Attribution-Non Commercial 4.0 International Licence (CC BY-NC).

Under this licence, you may copy and redistribute the material in any medium or format. You may also create and distribute modified versions of the work. This is on the condition that: you credit the author and do not use it, or any derivative works, for a commercial purpose.

When reusing or sharing this work, ensure you make the licence terms clear to others by naming the licence and linking to the licence text. Where a work has been adapted, you should indicate that the work has been changed and describe those changes.

Please seek permission from the copyright holder for uses of this work that are not included in this licence or permitted under UK Copyright Law

#### Abstract

The development of neural interfaces allowing the acquisition of signals from the cortex of the brain has seen an increasing amount of interest both in academic research as well as in the commercial space due to their ability to aid people with various medical conditions, such as spinal cord injuries, as well as their potential to allow more seamless interactions between people and machines. While it has already been demonstrated that neural implants can allow tetraplegic patients to control robotic arms, thus to an extent returning some motoric function, the current state of the art often involves the use of heavy table-top instruments connected by wires passing through the patient's skull, thus making the applications impractical and chronically infeasible.

Those limitations are leading to the development of the next generation of neural interfaces that will overcome those issues by being minimal in size and completely wireless, thus paving a way to the possibility of their chronic application. Their development however faces several challenges in numerous aspects of engineering due to constraints presented by their minimal size, amount of power available as well as the materials that can be utilised.

The aim of this work is to explore some of those challenges and investigate novel circuit techniques that would allow the implementation of acquisition analogue front-ends under the presented constraints. This is facilitated by first giving an overview of the problematic of recording electrodes and their electrical characterisation in terms of their impedance profile and added noise that can be used to guide the design of analogue front-ends.

Continuous time (CT) acquisition is then investigated as a promising signal digitisation technique alternative to more conventional methods in terms of its suitability. This is complemented by a description of practical implementations of a CT analogue-to-digital converter (ADC) including a novel technique of clockless stochastic chopping aimed at the suppression of flicker noise that commonly affects the acquisition of low-frequency signals. A compact design is presented, implementing a 450 nW, 5.5 bit ENOB CT ADC, occupying an area of 0.0288 mm<sup>2</sup> in a 0.18 µm CMOS technology, making this the smallest presented design in literature to the best of our knowledge.

As completely wireless neural implants rely on power delivered through wireless links, their supply voltage is often subject to large high frequency variations as well voltage uncertainty

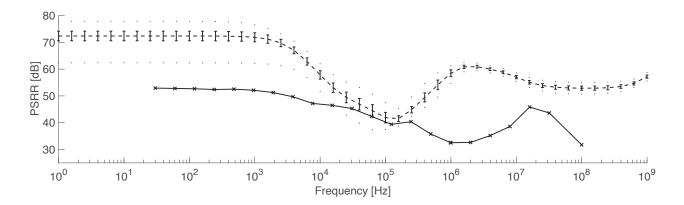

making it necessary to design reference circuits and voltage regulators providing stable reference voltage and supply in the constrained space afforded to them. This results in numerous challenges that are explored and a design of a practical implementation of a reference circuit and voltage regulator is presented. Two designs in a 0.35 µm CMOS technology are presented, showing respectively a measured PSRR of  $\approx$ 60 dB and  $\approx$ 53 dB at DC and a worst-case PSRR of  $\approx$ 42 dB and  $\approx$ 33 dB with a less than 1% standard deviation in the output reference voltage of 1.2 V while consuming a power of  $\approx$ 7 µW.

Finally,  $\Sigma\Delta$  modulators are investigated for their suitability in neural signal acquisition chains, their properties explained and a practical implementation of a  $\Sigma\Delta$  DC-coupled neural acquisition circuit presented. This implements a 10-kHz, 40 dB SNDR  $\Sigma\Delta$  analogue front-end implemented in a 0.18 µm CMOS technology occupying a compact area of 0.044 µm<sup>2</sup> per channel while consuming 31.1 µW per channel.

#### Acknowledgements

First and foremost, I would like to thank Dr Timothy Constandinou for supervising me and always having supported me during my studies at Imperial College, not only as a PhD student but ever since I first set my foot at Imperial in September 2012 as an undergraduate student when Tim became my personal tutor. If it was not for Tim, I would have, similarly to a lot of my fellow students, very likely taken up a career in one of London's banking institutions and ended up on a path that would not allow me to pursue what has always been my passion - technology and electronics. I am forever going to be grateful for the opportunity I have received in being able to continue my studies and for the freedom I have been given to work on and research electronic circuits during my PhD studies.

I am extremely grateful to have been a part of CBIT for the last 5 years, it has been an absolute honour and a privilege to be surrounded by so many bright and talented people every day. I believe that the community that has grown in B422 is very special and the atmosphere of support and friendship that surrounds it has led and is going to lead to more and more outstanding work and research. My special thanks goes to Lieuwe for teaching me a lot about integrated circuits and for all the interesting discussions we have had on just about every possible topic.

Finally, I would like to thank my family for all their love and support and for giving me the means and possibility allowing me to come to London and pursue my studies at Imperial and for always being there for me no matter how difficult the times and for always hearing me out when I needed it the most.

# Contents

| $\mathbf{A}$ | bstra                       | ıct   |                                 | ii |  |

|--------------|-----------------------------|-------|---------------------------------|----|--|

| A            | Acknowledgements            |       |                                 |    |  |

| 1            | Introduction and Motivation |       |                                 | 2  |  |

|              | 1.1                         | Motiv | ation                           | 3  |  |

|              |                             | 1.1.1 | Cochlear Implants               | 4  |  |

|              |                             | 1.1.2 | Retinal Implants                | 5  |  |

|              |                             | 1.1.3 | Recording Implants              | 6  |  |

|              | 1.2                         | Neura | l Signals                       | 8  |  |

|              |                             | 1.2.1 | Extracellular Action Potentials | 8  |  |

|              |                             | 1.2.2 | Local Field Potentials          | 9  |  |

|              |                             | 1.2.3 | Non-Invasive Recordings         | 10 |  |

|              | 1.3                         | Recor | ding Neural Implants            | 11 |  |

|              | 1.4                         | Brain | Machine Interfaces              | 13 |  |

|              |                             | 1.4.1 | Data Transmission               | 14 |  |

|              |                             | 1.4.2 | Power Delivery                  | 14 |  |

viii CONTENTS

|   |     | 1.4.3   | Chronicity and Failures                                           | 16 |

|---|-----|---------|-------------------------------------------------------------------|----|

|   |     | 1.4.4   | Local Field Potentials                                            | 20 |

|   |     | 1.4.5   | Next Generation of Neural Interfaces                              | 22 |

|   |     | 1.4.6   | Project ENGINI                                                    | 23 |

|   | 1.5 | Object  | tives                                                             | 26 |

|   | 1.6 | Thesis  | Outline                                                           | 29 |

| 2 | Ove | erview  | of Analogue Front-Ends and Electrodes for Neural Implants         | 32 |

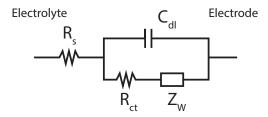

|   | 2.1 | Electro | ode Model                                                         | 33 |

|   |     | 2.1.1   | Capacitive Conduction                                             | 35 |

|   |     | 2.1.2   | Faradaic Current                                                  | 37 |

|   |     | 2.1.3   | Spreading Resistance                                              | 38 |

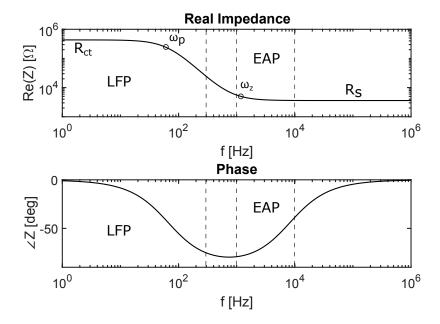

|   | 2.2 | Analys  | sis of Electrode Model                                            | 39 |

|   |     | 2.2.1   | Effects of Increasing Electrode Geometric Area on Recording Noise | 41 |

|   |     | 2.2.2   | Effects of Increasing Electrode Surface Area on Recording Noise   | 43 |

|   |     | 2.2.3   | Effects of Electrode Materials on Recording Noise                 | 45 |

|   | 2.3 | Niobiu  | ım as a Potential Novel Electrode Material                        | 48 |

|   |     | 2.3.1   | Verification of Suitability of Nb as an Electrode material        | 49 |

|   |     | 2.3.2   | Conclusion                                                        | 52 |

|   | 2.4 | Introd  | uction to Analogue Front-Ends                                     | 53 |

|   |     | 2.4.1   | Harrison's Amplifier                                              | 55 |

|   |     | 2.4.2   | DC-Coupled Amplifiers                                             | 57 |

<u>CONTENTS</u> ix

|   |     | 2.4.3 Digitisation                                          | 59  |

|---|-----|-------------------------------------------------------------|-----|

|   | 2.5 | Summary                                                     | 61  |

| 3 | Con | ntinuous Time Acquisition of Neural Signals                 | 63  |

|   | 3.1 | Introduction                                                | 63  |

|   |     | 3.1.1 Non-Uniform Sampling                                  | 64  |

|   |     | 3.1.2 Introduction to Continuous-Time Sampling              | 67  |

|   | 3.2 | Aliasing in Continuous-Time Sampling                        | 69  |

|   | 3.3 | Continuous-Time Sampling for Biological Signals             | 72  |

|   | 3.4 | CT ADC Implementation                                       | 76  |

|   |     | 3.4.1 Charge-Based Topology Implementation                  | 77  |

|   |     | 3.4.2 Implemented Circuit Testing                           | 80  |

|   | 3.5 | Comparison to Other Designs in Literature and Conclusion    | 85  |

| 4 | Clo | ckless Chopping Scheme for CT Acquisition of Neural Signals | 87  |

|   | 4.1 | Chopping in CT Acquisition                                  | 92  |

|   |     | 4.1.1 Stochastic Chopping                                   | 94  |

|   | 4.2 | Circuit Implementation                                      | 97  |

|   |     | 4.2.1 Threshold Crossing Detector                           | 99  |

|   |     | 4.2.2 Chopping                                              | 100 |

|   |     | 4.2.3 Input Comparator                                      | 101 |

|   |     | 4.2.4 Charge Injection                                      | 104 |

X CONTENTS

|   | 4.3 | Result | 5s                                                  | 104 |

|---|-----|--------|-----------------------------------------------------|-----|

|   |     | 4.3.1  | Flicker Noise Removal Method                        | 104 |

|   |     | 4.3.2  | Circuit Implementation                              | 105 |

|   |     | 4.3.3  | Measured Results                                    | 110 |

|   |     | 4.3.4  | Conclusion                                          | 114 |

| 5 | Ref | erence | Circuits and Voltage Regulators for Neural Implants | 117 |

|   | 5.1 | Refere | ence Circuits                                       | 118 |

|   |     | 5.1.1  | Bandgap Reference                                   | 119 |

|   |     | 5.1.2  | Beta-Multiplier Reference                           | 120 |

|   |     | 5.1.3  | Reference Voltage Generation                        | 121 |

|   | 5.2 | Voltag | ge Regulators                                       | 122 |

|   |     | 5.2.1  | NMOS and PMOS Regulators                            | 123 |

|   |     | 5.2.2  | Feedback Loop Compensation                          | 123 |

|   |     | 5.2.3  | Solutions Presented in Literature                   | 126 |

|   | 5.3 | Imple  | mentation of Version 1                              | 127 |

|   |     | 5.3.1  | Beta Multiplier Analysis                            | 128 |

|   |     | 5.3.2  | V <sub>be</sub> Reference Analysis                  | 129 |

|   |     | 5.3.3  | Voltage Regulator                                   | 131 |

|   |     | 5.3.4  | Power Supply Indicators                             | 131 |

|   | 5.4 | Result | s of Version 1                                      | 132 |

|   | 5.5 | Imple  | mentation of Version 2                              | 136 |

<u>CONTENTS</u> xi

|   |      | 5.5.1  | Output Amplifier Implementation                  | 37 |

|---|------|--------|--------------------------------------------------|----|

|   |      | 5.5.2  | Load Capacitor                                   | 38 |

|   | 5.6  | Result | s of Version 2                                   | 39 |

|   |      | 5.6.1  | Voltage Reference Measurements                   | 11 |

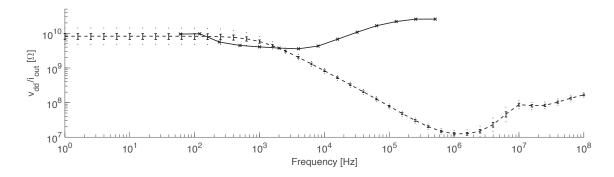

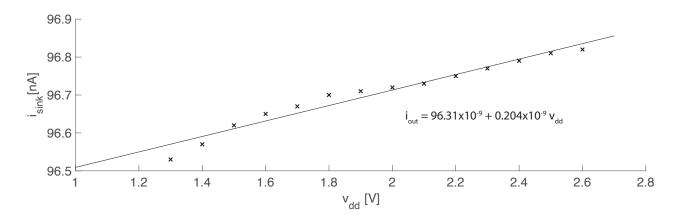

|   |      | 5.6.2  | Current Source Measurements                      | 14 |

|   | 5.7  | Conclu | asion                                            | 46 |

| 6 | Sign | na-Del | ta Modulator for DC-Coupled Neural Interfaces 14 | 19 |

|   | 6.1  | Introd | uction                                           | 49 |

|   |      | 6.1.1  | Principle of Operation                           | 19 |

|   |      | 6.1.2  | Design Considerations                            | 51 |

|   |      | 6.1.3  | 2nd Order Sigma-Delta Modulators                 | 53 |

|   |      | 6.1.4  | Decimation Filters                               | 55 |

|   |      | 6.1.5  | Comparison with Other ADC Topologies             | 56 |

|   | 6.2  | Implei | mentation                                        | 57 |

|   |      | 6.2.1  | Feedback Loop                                    | 58 |

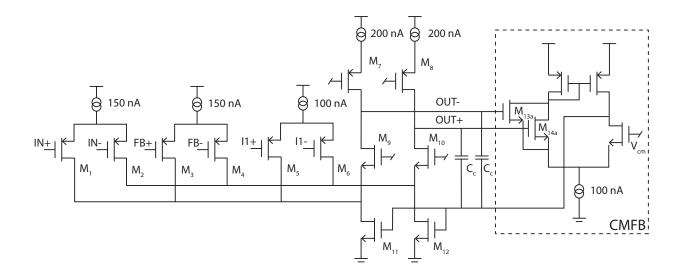

|   |      | 6.2.2  | Integrator Implementation                        | 32 |

|   |      | 6.2.3  | Comparator Implementation                        | 37 |

|   |      | 6.2.4  | Timing Diagram                                   | 38 |

|   | 6.3  | Result | s                                                | 70 |

|   |      | 6.3.1  | Measurements                                     | 72 |

|   | 6.4  | Concli | ısion                                            | 74 |

| 7                         | 7 Conclusion |                                       | 176 |  |

|---------------------------|--------------|---------------------------------------|-----|--|

|                           | 7.1          | Original Contributions                | 178 |  |

|                           | 7.2          | What Could Have Been Done Differently | 180 |  |

|                           | 7.3          | Thoughts About Future Work            | 181 |  |

| $\mathbf{A}_{\mathbf{j}}$ | ppen         | dix A - List of Publications          | 183 |  |

| Bi                        | bliog        | graphy                                | 184 |  |

# List of Tables

| 1.1 | Summary of Performance of The State-of-The-Art Neural Interfaces in Literature                       | 29  |

|-----|------------------------------------------------------------------------------------------------------|-----|

| 2.1 | Exchange Current Density and Young's Modulus of Selected Materials                                   | 48  |

| 2.2 | Measured Values of $\Re(Z_{Nb})$ and $\Re(Z_{Pt})$ , The Impedance of Niobium and Platinum Electrode | 52  |

| 2.3 | Brief Comparison of Analogue Front-End Topologies                                                    | 62  |

| 2.4 | Brief Comparison of Analogue to Digital Converter Topologies                                         | 62  |

| 3.1 | Estimated Bandwidths of Chosen Biological Signals                                                    | 74  |

| 3.2 | Power Consumption of Individual Components in the Manufactured CT ADC $$ .                           | 82  |

| 3.3 | Comparison with Other CT ADC Implementations                                                         | 86  |

| 4.1 | Simulated SNDR and ENOB of the 2nd Version of the CT ADC                                             | 108 |

| 4.2 | Comparison with Other CT ADC Implementations                                                         | 116 |

| 5.1 | Summary of Obtained Monte Carlo Post-Layout Simulation Results                                       | 134 |

| 5.2 | Results of Monte Carlo Simulations of the Control Loop's Phase Margin                                | 136 |

| 5.3 | Summary of Obtained Monte Carlo Post-Layout Simulation Results of the Circuit's 2nd version          | 140 |

| 5.4 | Results of Monte Carlo Simulations of Version 2 of the Control Loop's Phase |

|-----|-----------------------------------------------------------------------------|

|     | Margin                                                                      |

| 5.5 | Comparison of Neural Acquisition Reference Circuits in Literature           |

| 6.1 | Comparison with Recording Digitising Front-Ends in Literature 175           |

# List of Figures

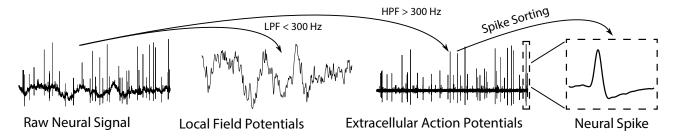

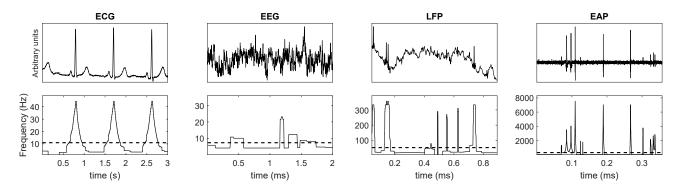

| 1.1 | Illustration of Neural Signals - LFPs, EAPs                                | 9  |

|-----|----------------------------------------------------------------------------|----|

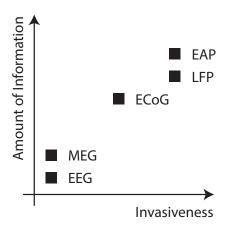

| 1.2 | Trade-Off Between Invasiveness and Amount of Information                   | 11 |

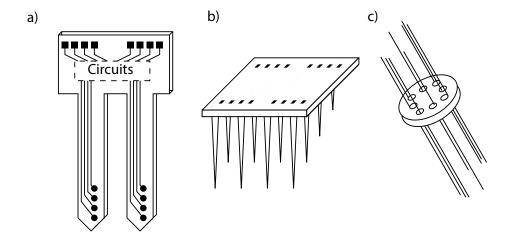

| 1.3 | Commonly Used Recording Electrodes                                         | 12 |

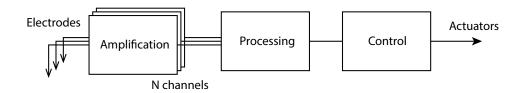

| 1.4 | Basic Blocks Typically Employed in a Functional BMI                        | 13 |

| 1.5 | Head Cross-Section With An Implanted Utah Array                            | 16 |

| 1.6 | Number of Operational Multi-Electrode Arrays (MEA) After Implantation in a |    |

|     | Study by J. C. Barresse et al                                              | 18 |

| 1.7 | Number of Observe-able Neurons in a Study by J. Kruger et al               | 19 |

| 1.8 | Distributed implants by Seo et al. and W. Biederman et al                  | 23 |

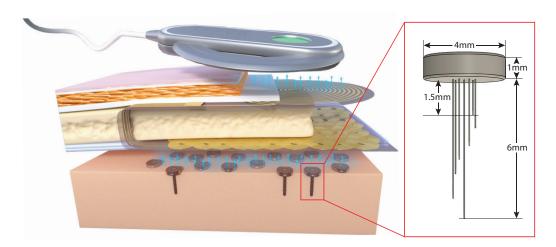

| 1.9 | Illustration of ENGINI                                                     | 24 |

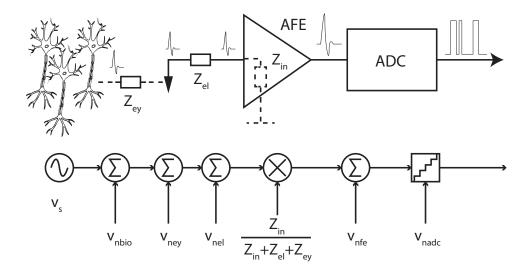

| 2.1 | Simplified Diagram of a Neural Signal Acquisition Chain                    | 34 |

| 2.2 | Equivalent Schematic of Electrode-Electrolyte Interface                    | 36 |

| 2.3 | Bode Plots of Typical Electrode Impedance (Re and Phase)                   | 40 |

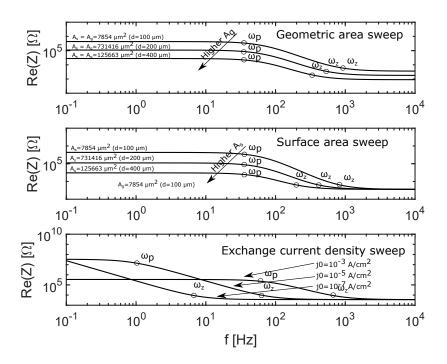

| 2.4 | Parameter Sweeps of Typical Electrode Impedance                            | 40 |

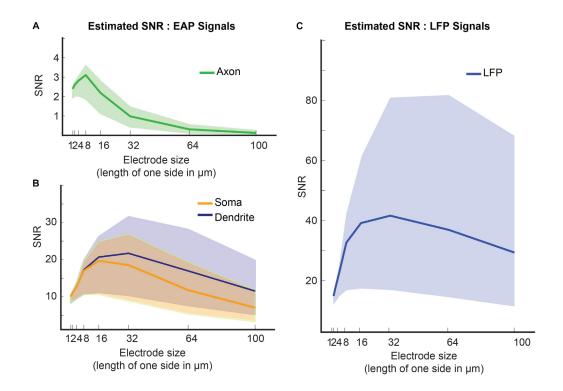

| 2.5 | Measured SNR vs Electrode size                                             | 42 |

<u>xvi</u> <u>LIST OF FIGURES</u>

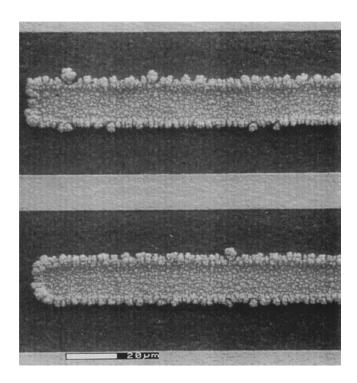

| 2.6  | Platinum-Black-Covered Electrodes                                     | 44 |

|------|-----------------------------------------------------------------------|----|

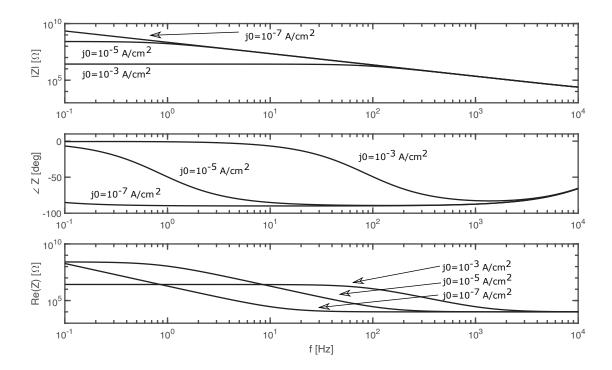

| 2.7  | Electrode Impedance Dependence on Exchange Current Density            | 46 |

| 2.8  | Relationship Between RMS Electrode Noise and Exchange Current Density | 47 |

| 2.9  | Experimental Setup for Electrode Impedance Characterisation           | 50 |

| 2.10 | Measured Impedance of Pt and Nb electrodes                            | 51 |

| 2.11 | Noise Power Density of Electrodes of Various Sizes                    | 54 |

| 2.12 | Harrison Amplifier                                                    | 55 |

| 2.13 | OTA Used in Harrison's amplifier                                      | 56 |

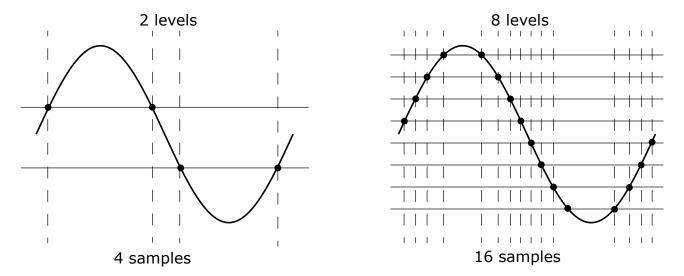

| 3.1  | Continuous-Time Sampling                                              | 67 |

| 3.2  | Illustration of Aliasing in CT Sampling                               | 70 |

| 3.3  | Illustration of Oversampling in CT Sampling                           | 71 |

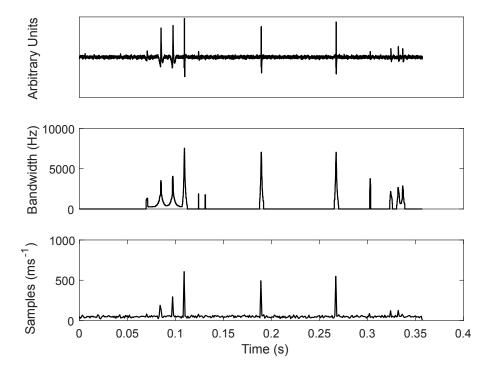

| 3.4  | Illustration of Bandwidth Changes in Biological Signal                | 73 |

| 3.5  | Instantenous Sampling Rate of EAP Signal                              | 75 |

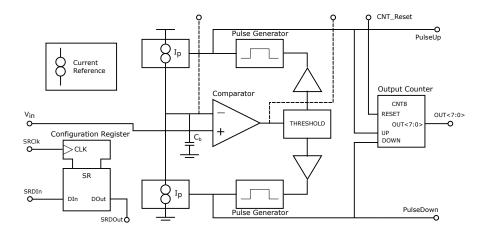

| 3.6  | Block Diagram of a CT ADC                                             | 78 |

| 3.7  | Simulated Output of the CT ADC                                        | 78 |

| 3.8  | CT ADC Microphotograph                                                | 81 |

| 3.9  | Platform Used to Test the Manufactured CT ADC                         | 81 |

| 3.10 | Power, SNDR and SFDR of The Manufactured ADC                          | 83 |

| 3.11 | Output Spectrum (1794 Hz)                                             | 83 |

| 3.12 | Output Spectrum (531 Hz)                                              | 84 |

| 3.13 | Reconstructed 531 Hz Sine Wave                                        | 84 |

LIST OF FIGURES xvii

| 3.14 | Reconstructed Sample Neural Spike                                                                                                          |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|

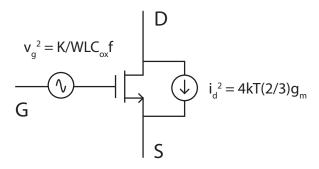

| 4.1  | Model of Noise in a MOSFET                                                                                                                 |

| 4.2  | Schematic of a Chopper-Stabilised Amplifier                                                                                                |

| 4.3  | Spectra of Signals Involved in Chopping                                                                                                    |

| 4.4  | Chopping Using the Quantised Version of the Input Signal                                                                                   |

| 4.5  | Autocorrelation and Spectra of Stochastic Choppers                                                                                         |

| 4.6  | Effect of Using a Stochastic Chopper                                                                                                       |

| 4.7  | Schematic of the Implemented Circuit                                                                                                       |

| 4.8  | Threshold Crossing Detector Implementation                                                                                                 |

| 4.9  | Spectrum of a Stochastic Chopper Generated Using an LFSR                                                                                   |

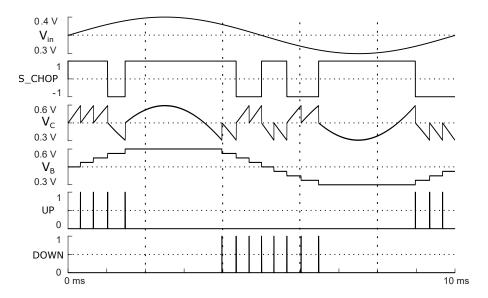

| 4.10 | Illustration of Internal Signals in Chopped CT-ADC                                                                                         |

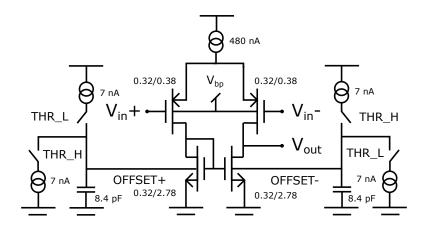

| 4.11 | Input Comparator Used in the CT ADC                                                                                                        |

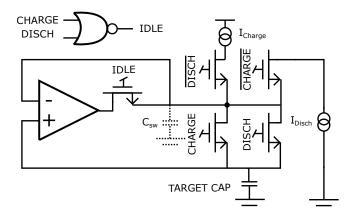

| 4.12 | Schematic of a Circuit Allowing Precise Charge Injection                                                                                   |

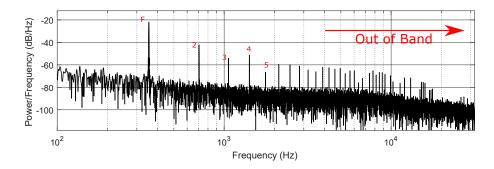

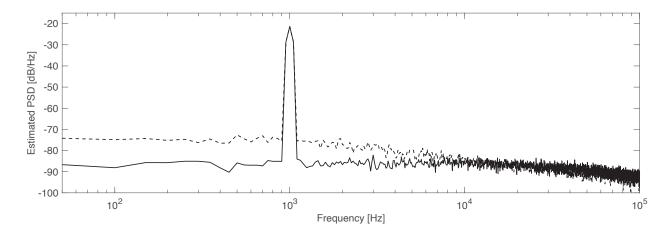

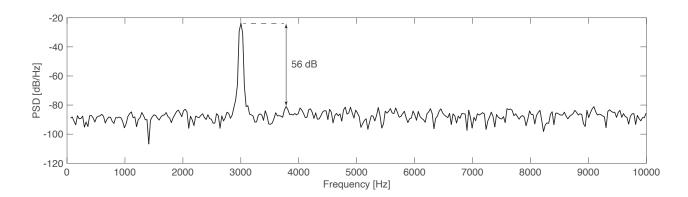

| 4.13 | Simulated PSD of a Reconstructed Signal Acquired Using a CT Sampling Scheme with and without Clockless Chopping (Numerical Simulation) 106 |

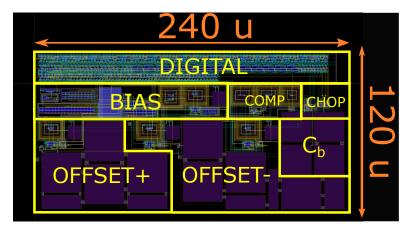

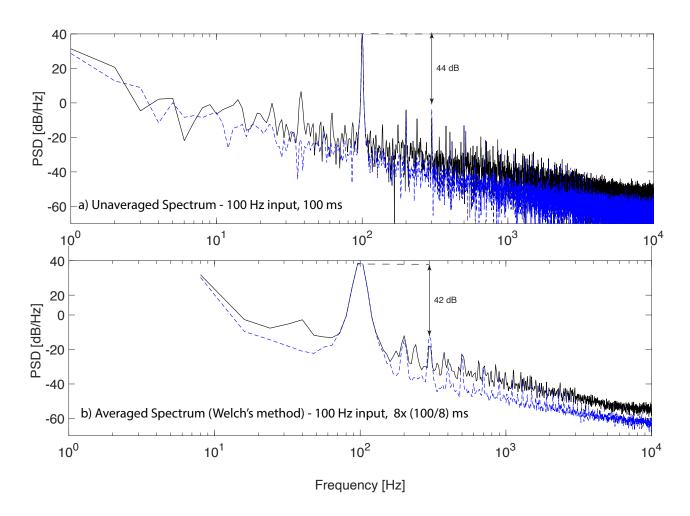

| 4.14 | Layout of the CT ADC                                                                                                                       |

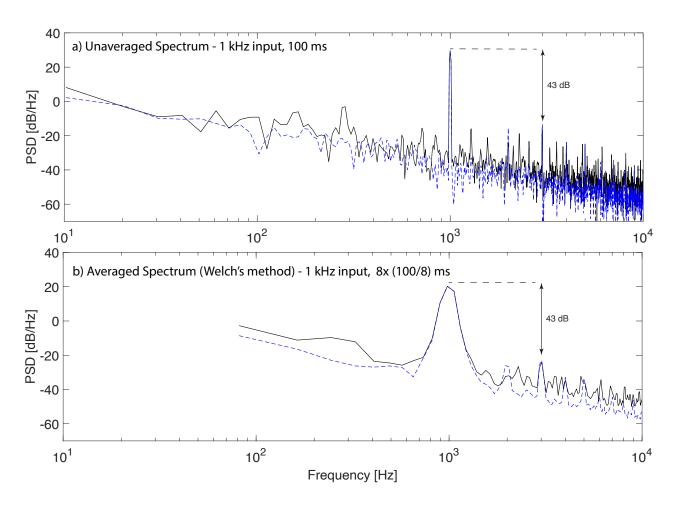

| 4.15 | Simulated PSD of a Reconstructed 100 Hz Signal Acquired Using CT ADC with and without Clockless Chopping (Circuit Simulation)              |

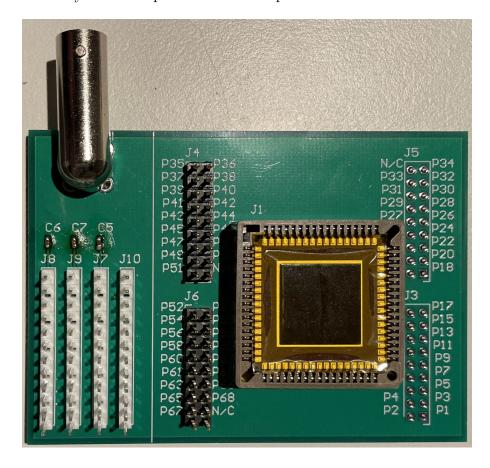

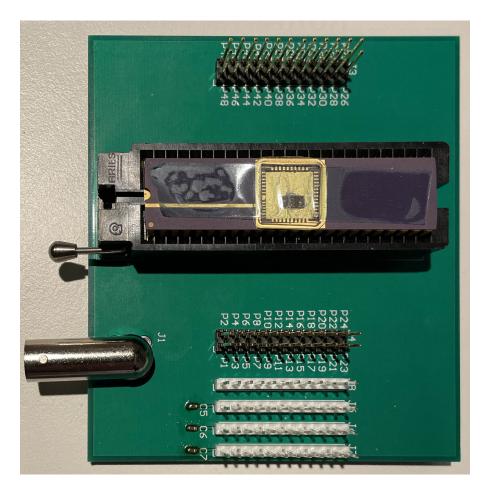

| 4.16 | Simulated PSD of a Reconstructed 1 kHz Signal Acquired Using CT ADC with and without Clockless Chopping (Circuit Simulation)               |

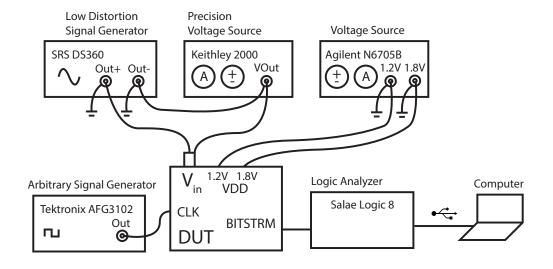

| 4.17 | Photograph of a PCB Used to Evaluate the 2nd Version of the Designed CT ADC110                                                             |

| 4.18 | Test Configuration Used to Evaluate the 2nd Version of CT ADC                                                                              |

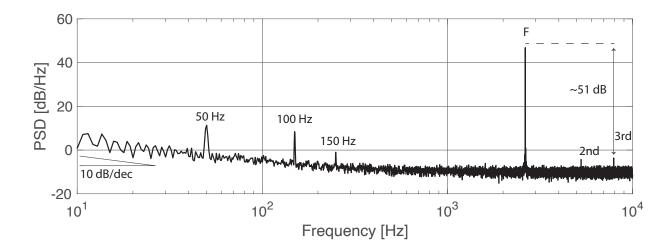

xviii LIST OF FIGURES

| 4.19 | Comparison of Measured Spectra of The CT ADC's Output With The Chopper              |

|------|-------------------------------------------------------------------------------------|

|      | Enabled and Disabled                                                                |

| 4.20 | Measured Spectra of The CT ADC's Output With The Chopper Disabled 112               |

| 4.21 | Variation of SNDR, SFDR and DR With Varying Input Frequency                         |

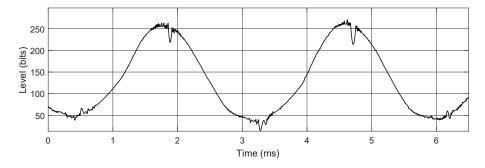

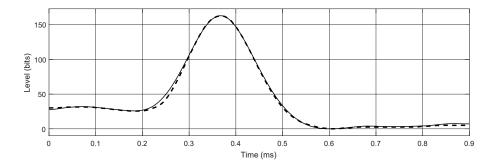

| 4.22 | Reconstruction of a Sample EAP Recorded Using The CT ADC                            |

| 4.23 | Reconstruction of a Sample EAP Recorded Using The CT ADC                            |

| 4.24 | Reconstruction of a Sample LFP+EAP Signal Recorded Using The CT ADC $115$           |

| 5.1  | Schematic of a Bandgap Reference Circuit                                            |

| 5.2  | Schematic of a $\beta$ -multiplier Reference Circuit                                |

| 5.3  | Illustration of Basic Voltage Regulator Topologies                                  |

| 5.4  | Illustration of a Conventional and Miller-Compensated Regulator                     |

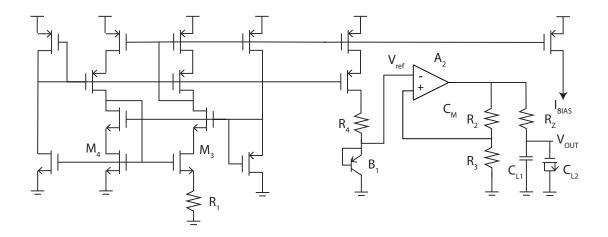

| 5.5  | Schematic of The Implemented Reference and Voltage Regulator                        |

| 5.6  | Small Signal Model of a Beta-Multiplier Reference                                   |

| 5.7  | Layout of the Implemented Reference Circuit and Regulator                           |

| 5.8  | Platform Used for Testing of the Designed Reference Circuit                         |

| 5.9  | Measured PSRR of The Manufactured Circuit                                           |

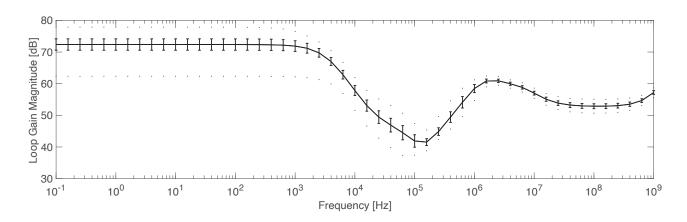

| 5.10 | Loop Gain of The Control Loop                                                       |

| 5.11 | Schematic of The Implemented 2nd Version of the Reference and Voltage Regulator 137 |

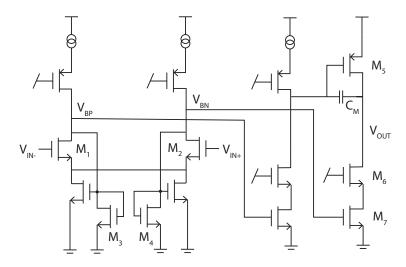

| 5.12 | Schematic of The Implemented Output Amplifier                                       |

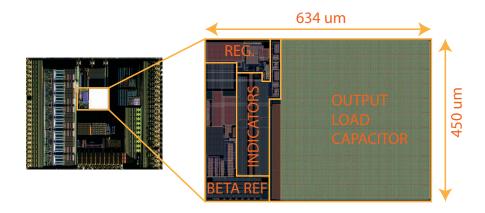

| 5.13 | Layout of the Implemented 2nd Version of Reference Circuit and Regulator 139        |

| 5.14 | PSRR of The 2nd Version of the Reference and Regulator                              |

LIST OF FIGURES xix

| 5.15 | Regulator Transient Resulting From Current Injection                                        |

|------|---------------------------------------------------------------------------------------------|

| 5.16 | Loop Gain of The Control Loop in Version 2 of The Regulator                                 |

| 5.17 | Test Setup Used to Measure the PSRR of the Reference Circuit                                |

| 5.18 | Photograph of the Used Testing PCB                                                          |

| 5.19 | Simulated and Measured PSRR of the Designed Reference Circuit                               |

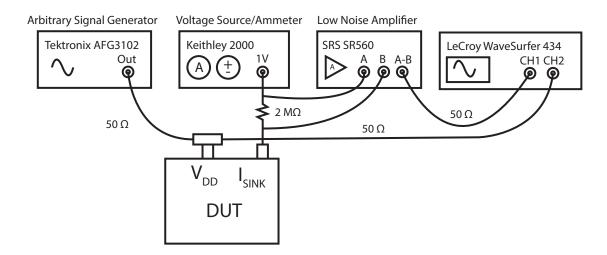

| 5.20 | Test Setup Used to Measure the PSRR of the Current Reference Circuit 144                    |

| 5.21 | Measured Reference Current Sink PSRR                                                        |

| 5.22 | Measured Reference Current Sink vs Supply Voltage                                           |

| 5.23 | Measured Reference Current Sink vs Applied Bias                                             |

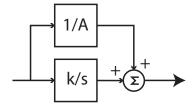

| 6.1  | Block Diagram of a Sigma-Delta Modulator                                                    |

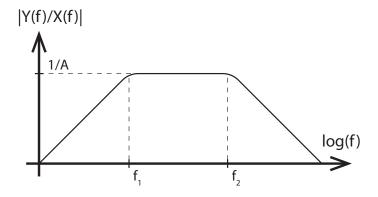

| 6.2  | Signal and Noise Transfer Function of a Sigma-Delta Modulator                               |

| 6.3  | Relationship Between the Oversampling Ratio and SNDR in a single-bit $\Sigma\Delta$ ADCs152 |

| 6.4  | Block Diagram of a 2nd Order Sigma-Delta Modulator                                          |

| 6.5  | Signal and Noise Transfer Function of a 2nd Order Sigma-Delta Modulator 154                 |

| 6.6  | Block Diagram of the Implemented $\Sigma\Delta$ Modulator                                   |

| 6.7  | Block Diagram of Signal Flow in a $\Sigma\Delta$ Modulator                                  |

| 6.8  | Block Diagram of Signal Flow in the Feedback Signal Path                                    |

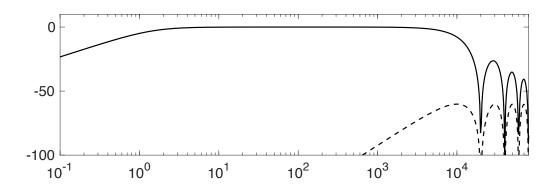

| 6.9  | Bode Plot of the Modulator's Transfer Function                                              |

| 6.10 | Charge Redistribution Network                                                               |

| 6.11 | Transfer Function of the Designed Modulator                                                 |

| 6.12 | Schematic of The Used Second Stage Transconductor                                           |

| 0.13 | Schematic of The Used First Stage Transconductor                             |

|------|------------------------------------------------------------------------------|

| 6.14 | Schematic of The Used StrongARM Latch                                        |

| 6.15 | Timing Diagram of Some Internal Signals                                      |

| 6.16 | Layout of The Designed Circuit                                               |

| 6.17 | Simulated Output PSD                                                         |

| 6.18 | PCB Used to Obtain Measured Results                                          |

| 6.19 | Test Setup Used To Characterise the Manufactured Sigma Delta Modulator $173$ |

| 6.20 | Measured Output Spectrum of The $\Sigma\Delta$ Modulator                     |

LIST OF ACRONYMS xxi

## List of Acronyms

ADC Analogue-to-Digital Converter

AFE Analogue Front-End

BCD Bipolar-CMOS-DMOS

BCI Brain-Computer Interface

BJT Bipolar Junction Transistor

BMI Brain-Machine Interface

CDMA Code-Division Multiple Access

CDS Correlated Double Sampling

CIC Cascaded Integrator-Comb

CL-LDO Capacitor-less Low Dropout Regulator

CMFB Common Mode Feedback

CMOS Complementary Metal-Oxide-Semiconductor

CSF Cerebrospinal Fluid

CT Continuous Time

CTAT Complementary to Absolute Temperature

DAC Digital-to-Analogue Converter

DC Direct Current

DT Discrete Time

DUT Device Under Test

EAP Extracellular Action Potential

ECG Electrocardiogram

ECoG Electrocorticography

EEG Electroencephalogram

ENGINI Empowering Next Generation Implantable Neural Interfaces

ENOB Effective Number of Bits

ESR Equivalent Series Resistance

FDA Food and Drug Administration of the United States

FOM Figure of Merit

ISM Industrial, Scientific and Medical

JFET Junction Field Effect Transistor

LDO Low Dropout Regulator

LFP Local Field Potential

LSB Least Significant Bit

LSK Load Shift Keying

MEA Multi-Electrode Array

MEG Magnetoencephalography

MOM Metal Oxide Metal

MOS Metal Oxide Semiconductor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

NEF Noise Efficiency Factor

NGNI Next Generation Neural Interfaces

NMOS n-Channel Metal Oxide Semiconductor

OSR Oversampling Ratio

PBS Phosphate Buffered Saline

PCB Printed Circuit Board

PMOS p-Channel Metal Oxide Semiconductor

PSRR Power Supply Rejection Ratio

PTAT Proportional to Absolute Temperature

PSD Power Spectral Density

RMS Root Mean Squared

SAR Successive Approximation Register

SFDR Spurious-Free Dynamic Range

SNDR Signal to Noise and Distinrrtion Ratio

SNR Signal to Noise Ratio

SRS Stanford Research Systems

STD Standard Deviation

STFT Short Time Fourier Transform

UVLO Undervoltage Lockout

ZTC Zero Temperature Coefficient

$\Sigma\Delta$  Sigma Delta

LIST OF SYMBOLS xxv

## List of Symbols

K<sup>+</sup> Potassium Cation

Cl<sup>-</sup> Chlorine Anion

Na<sup>+</sup> Sodium Cation

TnO<sub>5</sub> Tantalum Pentoxide

NaCl Sodium Chloride

A Amplitude

$A_q$  Geometric Area

$A_s$  Surface Area

$A_{in}$  Input Attenuation Factor

B Bandwidth

B(t) Time-Varying Bandwidth

$B_{avg}$  Average Bandwidth

$B_c$  Comparator Bandwidth

$B_{max}$  Maximal Bandwidth

BW Bandwidth

C Compression Ratio

$C_{dl}$  Double-Layer Capacitance

$C_{dl0}$  Zero Potential Double-Layer Capacitance

$C_{DS}$  Drain-Source Capacitance

$C_H$  Helmholtz Capacitance

$C_{GC}$  Gouy-Chapman Capacitance

$C_L$  Load Capacitance

$C_{ox}$  Oxide Capacitance

$C_p$  Parasitic Capacitance

$d_{ec}$  Eletrode-Cell Distance

$e_q$  Quantisation Error

E Young's Modulus

$f_c$  Corner Frequency or Clock Frequency

xxvi LIST OF SYMBOLS

$f_s$ Sampling Frequency  $f_t$ Tone Frequency Small Signal Transconductance of Device x  $g_{mx}$  $G_m$ Transconductance H(f)Transfer Function X(f)Fourier Transform of x(t)X(s)Laplace Transform of x(t)Output current  $i_{out}$ BJT Reverse Saturation Current  $I_0$ Drain Current  $I_D$ Total Consumed Current  $I_{tot}$ Sunk Current or Sourced Current  $I_s$  $J_0$ Exchange Current Density Exchange Current Density of Niobium  $J_{0,Nb}$ Exchange Current Density of Platinum  $J_{0,Pt}$ Boltzmann Constant k $K_f$ Flicker Noise Constant NResolution (Bits)  $N_q$ Number of Quantisation Levels PPower  $P_N$ Noise Power  $P_S$ Signal Power Electron Charge qSmall Signal Output Resistance of Device x  $r_{ox}$ Output Resistance  $r_{out}$ RNoise Reduction Factor  $R_x(\tau)$ Autocorrelation of x(t) $R_{ct}$ Charge Transfer Resistance

Drain-Source Resistance

$R_{DS}$

LIST OF SYMBOLS xxvii

$R_L$ Load Resistance  $R_s$ Spreading Resistance  $S_c(f)$ Chopper Spectrum  $S_x(f)$ Spectrum of x(t) $S_{ni}(f)$ Input Noise Spectrum  $SR_{in}$ Input Slew Rate Maximal Time Delay Pulse Length  $t_p$ TAmbient Temperature  $T_s$ Sampling Period Signal Voltage  $v_s$ Supply Voltage  $v_{dd}$ Quantisation Noise  $v_{nadc}$ Biological Noise  $v_{nbio}$ Electrode Noise  $v_{nel}$ Front-End Noise  $v_{nfe}$ Potential Across Electrode  $V_{el}$ Gate-Source Voltage  $V_{gs}$  $V_{out}$ Output Voltage Input-Referred RMS Noise  $V_{rms,in}$ Supply Voltage  $V_{supply}$  $V_t$ Thermal Voltage or Threshold Voltage WLGate Area Valence of Ions  $Z_{ey}$ Electrolyte Impedance  $Z_{ey}^{cyl}$ Electrolyte Impedance, Cylinder Approximation  $Z_{el}$ Electrode Impedance

$Z_{in}$

$Z_w$

Input Impedance

Warburg Impedance

LIST OF SYMBOLS

Size of Quantisation Level  $\Delta_q$  $\delta q$ Excess Charge  $\delta V_q$ Potential of One Quantisation Level Gate Coupling Coefficient  $\kappa$ Angular Frequency  $\omega$ Pole Frequency  $\omega_p$ Zero Frequency  $\omega_z$ Pole Located at Transistor Gate  $\omega_G$ Pole Located at The Output of a Circuit  $\omega_L$ Electrolyte Conductance  $\rho_{ey}$ Frequency Standard Deviation  $\sigma_f$ Time Standard Deviation  $\sigma_t$  $\sigma^2$ Variance Window Width  $\tau_w$ sinc(x)Sinc Function  $\sin(x)/x$  $\cosh(x)$ Hyperbolic Cosine  $\delta(t)$ Dirac Delta  $\Re(\cdot)$ Real Part Magnitude  $|\cdot|$ ∠. Angle

Energy of a Signal

Transform Pair

$E[\cdot]$

# Chapter 1

# Introduction and Motivation

The human brain has captured the curiosity of scientists and people ever since the early days of mankind and interest in its anatomy can be traced back as early as Ancient Greece [1] when people started observing brain injuries in soldiers wounded in battles and their effect on health and resulting disabilities. This led to the first steps in understanding the anatomy of the neural system and the function of some of its individual parts as well as the understanding that the brain is the center of thinking and intelligence. The science of the time, however, could not understandably answer deeper questions about the true nature of the neural system's operation and was limited to rudimentary observations.

This to a large extent remained the case throughout many centuries to come but was interrupted by an increased interest in the human body brought by the Renaissance which led to some of the first modern brain dissections and resulting advances in anatomy [2]. A deeper insight into the functioning of the brain and its tissue was, however, enabled by discoveries in a seemingly unrelated field - physics, more specifically the physics of electricity. This led to the, now notoriously known, experiment of Luigi Galvani conducted in 1791 [3] that perhaps for the first time showed a clear connection between electricity and the neural system by inducing movement in dissected frog legs using electrical stimuli. Galvani's experiment not only started a wave of interest in the research of electricity but also started a new scientific field of electrophysiology, a study of electric processes in the human body and their observation, eventually leading to

1.1. Motivation 3

the development of such diagnostic tools as Electrocardiograms (ECG), Electroencephalograms (EEG) and many others.

The understanding of a neuron as the basic building block of the neural system, would however only come about a hundred years later when J. E. Purkyne described the Purkinje cell which then became the first documented neuronal cell. The first recording of electrical activity observed in neurons was then reported in 1928 by E. Adrian [4] who was able to obtain it using a capillary electrometer. This gave the first insight into the inner functioning of the neural system and started an endeavour that would eventually lead to the development of a multitude of medical applications relying on electronics interfacing with the neural tissue to aiding people's well-being and helping in the treatment of various medical conditions and ailments.

#### 1.1 Motivation

While the publication of E. Adrian was perhaps the first documented example of a successful recording of electrical activity in neural tissue, there have at the time already been several publications documenting the effects of the opposite, the stimulation of the neural tissue with electricity. One of the early, most historically significant, results in this space can be attributed to E. Hitzig who demonstrated that electrical stimulation of brain tissue leads to involuntary eye movement in people, dogs and other animals in 1870 [5].

Arguably, this head start of about 60 years, when compared to recording efforts, was reflected in the earlier medical adoption and feasibility of brain stimulation as opposed to the use of neural recordings. One of the notable examples of the early pioneers of neurostimulation is W. Penfield who in 1936 demonstrated [6] a medical procedure based on stimulation of the brain to relieve epilepsy in patients. Building on this work, C.N. Shealy et al. [7] have demonstrated the use of a chronically implanted stimulator to reduce chronic pain in terminally ill cancer patient.

Those successful demonstrations soon led to the research of the possibility of stimulating other areas of the brain, thus enabling additional applications. As the brain is the center of cognition,

it is only natural to ask ourselves whether it is possible convey information into the brain by stimulating the neural system and thus replacing or enhancing one of the five basic senses. While inducing the sense of touch with electrical stimulation is arguably simple and most likely the first sense to have ever been electrically induced, hearing is another sense that early on became successfully interfaced to electronic circuits by means of stimulating the neural system in the form of cochlear implants restoring hearing in people with certain hearing impairments by directly stimulating the cochlear nerve.

#### 1.1.1 Cochlear Implants

The history and research of cochlear implants [8] on its own is a long and very elaborate topic that is seeing major contributions and additions until this day. Some of the original breakthrough work was done independently by W. House and A. Djourne with C. Eyries in the late 1950s and early 1960s having described the possibility of implanting a patient with a single-electrode implant stimulating the cochlea and to some extent returning the sensation of hearing. Some of the early experimental results of implanting those devices in people were obtained by P. Michelson who implanted [9] single-channel stimulators which led to the subjects being able to distinguish the pitch and amplitude of the played auditory stimuli. Those early implants were however not advanced enough to allow comprehension of natural language.

To understand how to improve on this, let us consider that the biological cochlea mechanically decomposes any sound-induced vibrations into various frequency bands in turn stimulating various sections of the auditory nerve [10]. Achieving better performing cochlear implants thus necessitates an increase in the amount of stimulating channels and therefore allowing more information to be conveyed to the neural system. To achieve this, it is necessary to decompose the auditory signal into separate frequency bands which requires the development of novel signal processing methods that would efficiently decompose the input sounds into individual spectral bands, all within the domain of an implanted device, resource-constrained both in terms of space as well as energy. As we will demonstrate throughout this thesis, the need to invent novel methods that solve engineering problems working around those limitations is a recurrent topic

1.1. Motivation 5

in the space of neural implants.

The earliest devices achieved spectral separation by employing analogue filter banks [10] but the fast-paced development of microprocessors soon led to them being replaced by more versatile digital processing techniques. One of the first multi-channel implants was demonstrated and implanted by G. Clark in 1979 [11] which led to initial successes in speech recognition within patients with cochlear prostheses [12]. Those advances eventually led to the FDA (Food and Drug Administration of the United States) approving the Nucleus 22 [13] as the first cochlear implant for general use in 1985. Nowadays, cochlear implants are arguably the most commonly used neural implants and an example of what the field can bring to improve lives and well-being of patients.

#### 1.1.2 Retinal Implants

Another example of neroprosthetics can be found in retinal implants that interface the nerve endings in the retina, thus allowing the return of the sense of vision to patients with some forms of visual impairments. The required complexity in terms of the needed amount of stimulation points as well as the signal processing arguably makes the development of those implants comparably more complicated to the cochlear implants which is reflected by their lengthier development and the current state of the art. Some of their earliest history [14] dates back to the late 1920s and early 1930s when B.O. Foerster demonstrated that electrically stimulating the visual cortex can lead to visual sensations perceived by the test subject. Another breaktrough was achieved in 1968 by G. S. Brindley et al. [15] having inserted an array of 81 electrodes touching the visual cortex of a blind patient allowing him to identify visible visual spots in consistent areas of the visual field upon their stimulation. This followed their previous estimation that 50 individual visual channels should provide sufficient visual clarity to allow the identification of letters. It is also interesting to note that this work presents early considerations for chronic implantation of electrode arrays and mentions the need for wireless data transmission in order to prevent a permanent puncture of the skin otherwise needed for wired connections.

While the early retinal prosthetic devices relied on direct stimulation of the visual cortex, later attempts at tackling the problem instead resorted to stimulating the neural endings in the retina, thus leading to a clearer mapping between electrode location and the corresponding point in the patient's visual field. Although leading to more successful implants, this also reduced the number of patients this technology can be indicated for as it e.g. excludes patients with a damaged optical nerve.

The research efforts have resulted in the development of Argus II [16], the first commercially available retinal prosthetic that was cleared by the FDA in 2013 for normal clinical usage prescribeable as a treatment for retinitis pigmentosa, a genetic disease that leads to a degradation of photoreceptor cells and a gradual visual loss. The Argus II relies on an array of 60 electrodes, thus providing a fairly limited resolution but, equally to the case of cochlear implants starting with a single channel, further research and development [17] is already leading to increases in the amount of channels and creation of more advanced devices is expected in the near future.

Both the state-of-the-art cochlear as well as retinal implants typically rely on the stimulation of nerve endings in the respective centres of the senses and while some of the early experiments with retinal prostheses attempted direct stimulation of the visual cortex in the brain, this is not an approach that is used in today's commercial products such as the Argus II. Similarly direct stimulation of the auditory cortex to treat deafness is not something that is typically attempted and is not used by clinically used cochlear implants although it has been researched in the past [18]. On the other hand, there is research suggesting that direct electrical stimulation of the auditory cortex can lead to relief in patients suffering from chronic tinnitus [19]. Although those applications are not very common, deep brain stimulation (DBS) has found extensive use in the relief of symptoms of Parkinson disease and suppression of tremors.

### 1.1.3 Recording Implants

So far we have considered neuroprostheses that convey information to the neural system by means of its stimulation. Let us now consider devices that achieve the opposite, the extraction of information from the neural system. While the first signs of electrical activity in the brain 1.1. Motivation 7

and the neural system were observed as long as several hundred years ago and E. Adrian was able to obtain a recording of a single neuronal activity in 1928, there was still a long way to being able to perform useful functions using the recorded neural signals. Before we dive into the discussion of how this can be achieved, let us consider some of the possible applications of such technologies, typically referred to as Brain-Machine Interfaces (BMI) or Brain-Computer Interfaces (BCI).

Perhaps the most obvious is the possibility of controlling a machine using one's thoughts. Barring various ideas from the world of science fiction, one of the applications receiving the biggest amount of interest is the possibility to aid people with spinal cord injuries [20] that lead to various levels of immobility in patients or, even more severely, patients with the locked-in syndrome [21] who are completely unable to communicate with the outside world and for whom a BCI becomes the only possible method of communication. This can come in the very rudimentary form of allowing control of a cursor [22] on a computer screen or lead to more advanced prostheses replacing the function of some muscles or limbs while allowing the patient to control a robotic arm using their thoughts [23]. Although the locked-in syndrome is not very common, spinal cord injuries leading to partial paralysis are a lot more frequent occurrence. Their incidence varies around the world but is typically between 10 and 50 cases per million people [24] and rises with age but notably peaks in people between 15 and 29 years old being mainly caused by falls and accidents in the respective age groups.

Aside from medical applications, it is easy to imagine that future BCIs could be used to facilitate other functions such as more natural control of computers using thoughts rather than using mice and keyboards [25], new forms of entertainment [26] made possible by more immersive virtual reality experience or even driving vehicles using thoughts [27]. Those possibilities have lately led to increased interest not only from the research community but also from commercial projects such as from Kernel and Neuralink who are hoping to capitalise on the expected growth of the BCI market. Arguably, the science and level of understanding of the human brain is still in its early days, making the research of BCIs a very interesting field, while at the same time having a great potential in improving the well-being and clinical outcomes of many patients.

## 1.2 Neural Signals

Before exploring some of the more detailed aspects of BCIs' operation, let us briefly consider the nature and origin of neural signals, as well as their typical stratification. Since the early days of the discovery of the Purkinje cell, it was understood that the activity of the neural system stems from the neuron as its basic building block. As described by S. Gibson [28], the operation of neurons is electrochemical in nature and can be described by reactions involving the exchange of K<sup>+</sup>, Cl<sup>-</sup> and Na<sup>+</sup> ions. In a largely abstract sense, a neuron can be considered a biochemical device that performs a series of some of the most basic mathematical operations, an integration and thresholding.

#### 1.2.1 Extracellular Action Potentials

In its resting state, a neuron has a large concentration of K<sup>+</sup> and Cl<sup>-</sup> ions inside its body. Following the mathematical integrator analogy, it receives its inputs from synapses, connections with other neurons, and when one of the synapses gets excited by an output of a neighbouring neuron, an ion channel is opened allowing an influx of Na<sup>+</sup> ions leading to a rising potential inside its body. At a certain point, the neuron reaches its peak polarisation and K<sup>+</sup> ions start flowing out of the neuron's body, thus returning its potential to a resting state. This results in a typical electrical potential response measurable outside the neuron's body termed the Extracellular Action Potential (EAP), also more colloquially referred to as a neural spike. This is the most elementary neural signal that gives us information about the activity of a single neuron and at the same time arguably is the most accurate and granular source of information about brain activity.

Inserting an electrode into neural tissue and obtaining a recording however leads to the acquisition of a far more complex signal as demonstrated by Figure 1.1. Due to the close proximity of neurons, it is typically impossible to obtain action potentials from isolated neurons and the recorded signal rather contains spikes generated by several neurons in the proximity of the inserted electrode. A technique called spike sorting [29; 28] is then typically employed to split

Figure 1.1: Illustration of a raw neural signal recorded by an invasive deep-subdural implant decomposed into LFPs, EAPs and individual spikes.

the EAP signal into spikes from individual neurons relying on the fact that each neuron has slightly different morphology resulting in different shape of the spikes it generates. A variety of algorithms and methods can then be employed to sort the recorded spikes and identify individual firing neurons.

#### 1.2.2 Local Field Potentials

In addition to EAPs from several neurons, a subdural neural recording also contains another signal called the Local Field Potential (LFP) as seen in Figure 1.1. The LFPs, as opposed to EAPs, give us information about general activity in the proximity of the inserted electrode. While there is still some discussion ongoing about the locality of LFPs [30], it is typically accepted that LFPs are representative of activity in the area of a 200-400 µm diameter around the inserted electrode. It is generally believed that the origin of LFPs is difficult to precisely explain [31], it is however accepted that its basis lies in mass activity of neurons surrounding the area, although its nature is more complicated than simply adding EAPs of surrounding neurons together.

EAPs and LFPs are separated in frequency which makes their separation for signal processing purposes simple. While the exact frequency threshold varies depending on used literature, one example [32] quotes LFPs and EAPs occupying frequency ranges of 1-300 Hz and 300 Hz to 3 kHz respectively. Similarly, the amplitudes of the two signals can largely differ. Although [32] states that both LFPs and EAPs can have an amplitude between 10 - 1 mV, it is typically agreed that neural spikes are an order of magnitude (20 dB) smaller than LFP signals. In addition to

valuable signals, a typical signal obtained from a neural electrode will also contain noise from a variety of sources as well electrode offset, both of which will be described in more detail later.

#### 1.2.3 Non-Invasive Recordings

While subdural neural recordings contain a large amount of information allowing the identification of individual neuronal activity, their acquisition requires the insertion of electrodes deep into the neural tissue, thus leading to an invasive surgery. This has led to the research of alternative methods of recording neural activity that are less invasive and offer a compromise between the amount of data that is acquired and the level of their invasiveness. From the methods that are still more invasive, we can mention recent research effort [33] exploring the possibility of recording neuronal activity using optical methods, thus potentially preventing the need to insert an electrode into the tissue directly. This would, however, still require an invasive operation to install the implant.

From the less invasive methods of neural signal recording, we can mention Electrocorticography (ECoG), Electroencephalography (EEG) [34] and Magnetoencephalography (MEG). ECoG involves placing an array of electrodes directly on the exposed tissue of the brain if done subdurally or above the dura if done epidurally and thus still requires an invasive operation needing an opening in the skull. EEG and MEG are, on the other hand, completely non-invasive and study neural signals by observing magnetic fields outside the skull in the case of an MEG or recording electrical signals on the surface of the skull in EEG's case. The simplicity of EEG recordings has led not only to its propagation in medicine but also in consumer devices offering a multitude of functions ranging from entertainment to well-being improvements.

In the case of non-invasive methods, any tissue inserted between the source of the signals, neurons, and the recording electrodes acts as a low-pass filter in both temporal as well as spatial sense and therefore leads to a loss of information. As demonstrated by Figure 1.2, there is therefore a trade-off between how invasive a neural recording method is and how much information can be obtained. This in turn limits the functions that can be performed based on the recorded signals. While it has been successfully demonstrated that EEG can be used

to control a cursor of a computer [22] or even a robotic arm [35] to a limited extent, it is generally accepted that the limited amount of independent channels and filtered nature of the acquired signals prohibits the creation of more advanced prostheses allowing e.g. the control of individual fingers on a robotic hand. To this end, it is necessary to explore invasive brain implants that allow the recording of LFPs and EAPs directly.

Figure 1.2: Demonstration of a trade-off between the invasiveness and the amount of information obtained from various neural recording methods.

## 1.3 Recording Neural Implants

As earlier mentioned, the recording of EAP and LFP signals requires the insertion of an electrode or an electrode array into the brain and thus an invasive operation involving creating an opening in the skull of the patient. Most of the historically early recordings [4; 36; 37] were obtained using a set of microwires that would be connected to an external amplifier, in the form of a large immobile table-top instrument, prohibiting any chronic use of such a setup. In addition, the early microwires were hindered by their lack of reproducibility i.e. their susceptibility to production variations and difficulties in their insertion, especially the insertion of their multitude in an array.

Since those early days, the aim of further research and development, therefore, has been to create devices that would allow chronic use by the patient while at the same time being easy to install. This has steered the direction of the development to the creation of fully integrated

implants that would be as small possible, while at the same time facilitating recordings from as many channels as possible without the need to connect external instruments, thus leading to a close link between the increased interest in the field of neural recordings and advances in microelectronics and semiconductor technology, permitting the creation of increasingly small electronic circuits [38]. The origins of those attempts can be traced to the 1970s when K.D. Wise and J.B. Angell presented [39] a multi-electrode array based on a silicon substrate that would eventually be called the Michigan probe, seen in Figure 1.3a. While the electrode array did not include a complete acquisition circuit on its substrate, it did contain a Junction Field Effect Transistor (JFET) pair that would form an amplifier when connected to external circuitry. This has significantly improved the state of the art at the time by reducing the dependence of the recording on the length of the wires as well as reducing its susceptibility to any induced interference.

Figure 1.3: Illustration of commonly used recording electrode configurations - a) Michigan probe, b) Utah array, c) Microwire array.

Another version of the probe [40] from the University of Michigan already contained amplifiers on the same substrate as the electrodes themselves.

An alternative method going in a similar direction and equally allowing the creation of an electrode array on a silicon substrate was devised in 1991 at The University of Utah leading to the creation of the Utah array [41]. As opposed to Michigan probes making use of planar electrodes, Utah arrays are composed of a grid of needles stemming from a silicon substrate as seen in Figure 1.3b. Similarly to the way electronic circuits can be integrated in Michigan

probes, there have been neural implant designs integrating electronic circuits with Utah arrays in a single implant [42]. While Michigan probes are better suited for recordings at various depths of the brain using their planar electrodes, Utah arrays can provide better lateral coverage but are limited to a single depth per needle site, although different needles can have various lengths. The commercially available Neuroport Array by Blackrock Microsystems is an example of a Utah array and, according to the manufacturer, is the only FDA-cleared chronic electrode array at the time of writing.

Finally, there have been designs based on arrays of microwires that are typically held together in a grid using a mechanical contraption such as [43]. A challenge in using a grid of microwires often stems from the difficulty in their connection to additional circuitry and the reproduction of such a process in addition to the difficulty of their insertion [44] due to the limited stiffness of the microwires.

## 1.4 Brain Machine Interfaces

So far we have discussed the possibility of integrating an amplifier in a neural implant to create a minimal neural recording device. This is however typically not sufficient to create a fully functional BMI performing a useful function. As shown in Figure 1.4, the entire BMI is typically composed of a multitude of recording electrodes, a set of amplifiers or complete analogue front-ends, a signal processing unit and finally a controller giving inputs to actuators, i.e. a robotic arm or a computer to facilitate the movement of a cursor.

Figure 1.4: Basic blocks typically employed in a functional BMI.

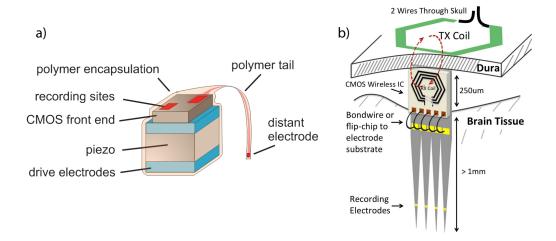

Integrating the analogue front-end in the implant directly is a step in a good direction because it leads to higher fidelity of the recordings but it does not solve the problem of the need to have a set of wires passing through the skull. To alleviate that, there has been a drive to create fully wireless implants that would not need any physical connection. This results in many challenges starting from the extraction of data from the implant to providing power to it. Some of those concepts were explored from early 2000s such as in the work by M Mojarradi et al. [45] that proposed a heterogeneous combination of an electrode array, a processing integrated circuit and a wireless transceiver bonded to a single block.

#### 1.4.1 Data Transmission

The challenges involved in the facilitation of data transmission begin in the amount of data that has to be transmitted. Although we previously mentioned that a neural spike occupies a bandwidth of up to 3 kHz, many acquisition circuits such as [46; 47] employ a sampling rate of 16 or even 20 kHz. Assuming that the transmission of a simple sample requires 16 bits in the data stream, we arrive at a data rate of 320 kbps. If an array of 96 electrodes, such as the commercially available Neuroport Array, is considered, the data rate rises to 30.7 Mbps, demonstrating how complicated the engineering challenge can become.

It is thus often advantageous to perform a degree of processing in the implant directly. A popular method involves the employment of spike sorting [48] which then limits the transmission to a simple bit sequence identifying a spike when it occurs. Other approaches involve various compression algorithms [49; 50] exploiting some properties of the neural signals and reducing the amount of data that has to be transmitted. Some solutions go a step further [51] and implement a circuit decoding intentions of the user, the output of which can be used to directly control a motorised prosthetic.

### 1.4.2 Power Delivery

Arguably an even larger challenge stems from the need to provide power to the implant aggravated by the fact that the amount of power available is often the limiting factor for the design of prostheses and one of their main constraints. In addition, even if the engineering challenge of continuously delivering power is solved, there is still a limit to how much power can be dissipated as the neural tissue is very sensitive to temperature changes, and heating it by more than a fraction of a kelvin can lead to its necrosis. It is usually quoted that this results in a limit to power dissipation of neural implants of 80 mW/cm<sup>2</sup> [52].

As the drive to develop completely wireless implants intensifies, a range of different approaches to the delivery of their power has been investigated, starting from the use of batteries. Although this might not seem a very suitable option, there is a precedent in their use for chronically implanted deep brain stimulators [53], quoting a typical lifetime of 3-5 years for single-use implants and more than 10 years for implants using rechargeable batteries. While technically feasible and used, the concept of implanting batteries inside the cranial cavity, however, still presents a large variety of issues as even rechargeable batteries have limited longevity and most kinds of chemical energy storage will involve the use of hazardous, biologically incompatible, materials.

Over the recent years many alternatives to using batteries have, therefore, been proposed, instead relying on wireless power delivery. The typically used methods [54] can be divided into three categories: ultrasound using a piezoelectric receiver, electromagnetic induction using a set of coils or light converted using photovoltaic cells. At the same time there have been initial attempts [55] to use biological fuel cells to power BMIs. Those would be connected to the patients's blood stream and generate electrical power from glucose contained in blood. While arguably still far from being practical with currently reported harvested steady-state power of  $3.4 \,\mu\text{W/cm}^2$  [54], this is a very promising approach for the future.

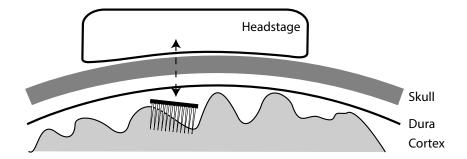

All other methods relying on conventional power delivery typically rely on a combination of a headstage mounted on the patient's head and subdural implants as seen in Figure 1.5. The headstage can be used both for the storage of energy, which might be in the form of easily replaceable batteries, as well as for performing of additional processing on the acquired signal outside of the constraints presented by implanted devices. As there is an inherent trade-off between how directional the link between the two system parts is and how efficient the link is, there is a need for accurate alignment between the headstage and the implant which can often

be difficult to achieve given the amount of natural movement of the tissue causing displacement between individual parts of the system.

Figure 1.5: Illustration of head cross-section with an implanted Utah array wirelessly coupled to a headstage.

#### 1.4.3 Chronicity and Failures

Although successful brain machine interfaces have already been constructed and demonstrated such as in the case [56] of a tetraplegic patient who was able to control a robotic arm using her thoughts, the current state-of-the-art BMIs suffer from limited chronicity and the impossibility of their deployment for everyday use. The BMI application presented in [56] involved the use of a commercially available Utah array connected by wires to a desktop computer used to decode the signals and control a robotic arm, a setup that is rather distant from a practical application. Nevertheless, the experiment demonstrated the feasibility of making a BMI that could help tetraplegic patients control robotic arms.

To understand the challenges faced by long-term chronic applications, we have to look at studies that have been conducted over extended periods of time. Some of the earlier examples can be found in work by P.J. Rousche and R.A. Normann [57] from 1998 who implanted 10 cats with Utah arrays and observed that after a period of 6 months, 60% of electrodes still showed some activity. At the same time the study revealed a range of issues that remain some of the biggest challenges of chronic implantations until today. The constant movement of the implant due to it being anchored in the soft brain tissue, has led to general instability of the recordings and inability to observe the same neuron for more than a few weeks. In addition, once the electrodes were explanted, most of them were covered in scar tissue grown as a reaction of the

organism to a foreign body. This phenomenon was explored in more detail by V. S. Polikov et al. [58], who have identified it as one of the most prominent barriers to the creation of truly chronic implants and it is generally believed that factors such as electrode shape and material contribute to the extent of the response.

A study by D. H. Szarowski et al. [59] has examined the effect of electrode geometry on the foreign body response and failed to show any significant relationship between the two. The authors however argue that the response can be divided into two separate processes - early and prolonged reactions, where the earlier is triggered by the immediate damage to the tissue caused by the insertion and is therefore dependent on the shape of the electrode, and the latter that is more affected by prolonged interactions and therefore more related to the material and general bio-compatibility of the electrode.

To improve the bio-compatibility of the implant, various methods have been explored, such as the incorporation of bioactive molecules to prevent growth of scar tissue. An interesting concept can be seen in work of D. R. Kipke et al. [60] who have developed a Michigan-style electrode incorporating a small cavity in the shank for the deployment of bioactive compounds such as drugs suppressing the foreign body response. A more recent review by J. W. Salatino et al. [61] mentions some successes of those methods in addition to stressing the importance of the use of materials that have similar mechanical properties to the brain tissue itself. It is argued that using softer materials results in smaller reaction but at the same time presents a challenge with insertion of the implant into the tissue. Importantly, it is noted that smaller feature sizes are preferred and keeping the volume of the implant to a minimum in general helps to reduce any adverse response of the organism.

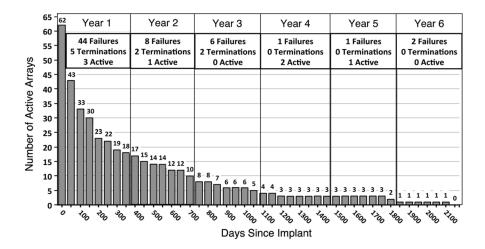

In general, there is a limited amount of studies with implants left in the host for more than a couple of years. An example of such is a study by J. C. Barresse et al. [62] who have implanted 27 non-human primates with 78 multi-electrode arrays (MEA) and observed their performance over a period of 5.75 years. This provides us with a unique insight to typical reasons for electrode failures as well as expected lifetime of electrodes. As seen in Figure 1.6, the amount of functional implants approximately follows exponential decay with a majority of

devices failing within the first year from implantation and the last MEA failing after 6 years of operation. It is noted that the main reason of failures were mechanical issues (30 MEAs) followed by biological causes (15 MEAs). While the main aim of this study was to observe the performance in recording of EAPs, it was observed that the LFP signal was still present for a longer period after EAPs were no longer observable from a particular recording electrode.

Figure 1.6: Number of operational multi-electrode arrays (MEA) after implantation in a study by J. C. Barresse et al. [62] (78 Utah-type MEAs implanted in non-human primates over a period of 6 years). Figure reproduced from [62].

To our best knowledge, the longest chronic recording achieved to date was 9 years long, done by N. Hatsopoulos [63] in non-human primates using a commercially available Utah array. Those reports of years-long recordings are however more a product of statistic deviation rather than a common occurrence.

Although the Utah array has to a large extent become the standard choice of MEA both for research and clinical practice, and is the only commercially produced FDA-cleared MEA, there is a multitude of arguments saying that they might not be the optimal solution for the next generation of recording implants. The study of J. C. Barrese et al. [62], having shown a median time to failure of just 182 days (mean of 387 days), can as well be considered one of them. It is, however, in general difficult to judge the chronicity of various types of MEAs due to a small number of studies that have been conducted over the period of several years.

Another study, conducted by R. J. Vetter [64] who implanted rodents with 12 multi-site Michigan probes, showed 11 of 12 probes still operational after a period of 127 days, also illustrating

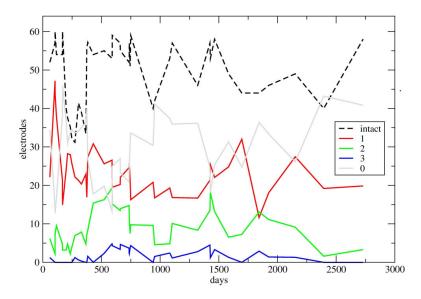

the potential of Michigan probes for chronic implantation. Similarly, some understanding of the potential of microwire-based MEAs can be found in studies of J. Kruger et al. [65] and M. A. Nicolelis et al. [66] who have both documented studies that observed microwire implants in non-human primates for extended periods of time.

M. A. Nicolelis et al. [66] have implanted three rhesus monkeys with a multitude of stainless, teflon-coated microwire implants in various cortical areas. In one monkey, the implant was left implanted for an extended period of 18 months after which it was still possible to identify EAPs of 58 individual neurons from 34 microwires (out of 96 implanted). The authors also note that no significant differences were observed in data collected immediately after surgery and after an additional period of 30 days.

J. Kruger et al. [65] have implanted one monkey with a 64-channel Ni-Cr-Al microwire array and observed the implant for a period of 7 years. A recording was then obtained in periodic intervals and the number of observe-able neurons was recorded as seen in Figure 1.7. This shows that there is no immediately apparent decrease in performance over the length of the study. The authors note that on some occasions the number of observe-able neurons increased and overall there was only a limited amount of amplitude decrease over time that would normally be associated with the growth of scar tissue and the foreign body response.

Figure 1.7: Number of observe-able neurons in a study by J. Kruger et al. [65] over period of 7 years using a 64-channel Ni-Cr-Al microwire array implanted in a monkey. Dashed line indicates the number of technically intact channels. Figure reproduced from [65].

While there is only a limited amount of studies conducted and a limited amount of data available to make a judgement, the results of those two studies examining microwire arrays [65; 66] as opposed to results obtained by J. C. Barresse et al. and R. J. Vetter et al. using Utah arrays and Michigan probes respectively, indicate that microwires might be more successful in performing chronic recordings. It is also worth noting that although both the microwire studies were only conducted with a limited amount of implanted animals, the implants did not fail completely in either of those studies. This is in contrast to what was reported by J. C. Barresse et al. [62] where all implants failed within a period of 6 years. The success of microwires can to some extent be connected with the earlier identified need to create implants that have mechanical properties similar to the host tissue. This is further supported by a study of Z. J. Du et al. [67] who have implanted stiff tungsten electrodes and ultrasoft polymer based electrodes into the cortex of rats for a period of 8 weeks. It was observed that the damage to the tissue was significantly smaller in the case of ultrasoft electrodes than when tungsten electrodes were used. It was also noted that the use of ultrasoft electrodes led to reduced foreign body response as evidenced by reduced glial cell growth.

The use of soft materials is difficult to achieve with rigid silicon-based structures such as Michigan probes or Utah arrays but significantly simpler with flexible metallic or polymer-based microwires. It can be argued that even microwire arrays made of stiff metals such as tungsten will be less rigid than a silicon-based structure. Those, on the other hand, achieve better manufacturing reproducibility and simplicity of implantation which led to their popularity and preferred usage but there is evidence to suggest that microwire arrays lead to better performance when used for chronic recordings.

#### 1.4.4 Local Field Potentials

Most of the studies presented so far have focused on obtaining recordings of EAPs and were looking at the amount of individually identifiable neurons as a measure of success. The study of J. C. Barresse et al. [62] however suggested that even after the EAP signal has disappeared in a particular channel due to extensive scar tissue growth, it is often still possible to record local

field potentials (LFPs). Those findings have further been noted by B. Pesaran et al. [68] and R. R. Harrison et al. [69] and can be explained by the fact that the glial cells that form the scar tissue result in the creation of a low-pass filter between the electrode and surrounding neurons, blocking the higher-frequency EAP but still allowing the lower-frequency LFPs to pass. If it is possible to obtain more chronic LFP recordings, a question then arises, whether it is possible to make brain machine interfaces solely reliant on LFPs and therefore less dependent on successful recording of high-frequency signals.

The relationship between local field potentials and spiking rates have been a subject to some debate in the community but it is generally believed that there is a close relationship between the two. To this end, B. Pesaran et al. [68] have observed neural activity in the cortex of macaque monkeys and observed correlations between certain LFP bands and spiking rates of individual neurons. A more recent work by A. Jackson and T. M. Hall [70] describes a method of extracting features from local field potentials, including features showing a high degree of correlation with unit spiking rates. In addition, there are other publications such as [71] by N. Ahmadi et al. that demonstrate algorithms for derivation of motor intentions from LFPs.

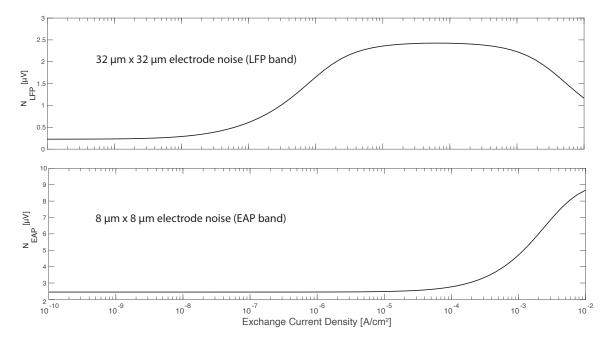

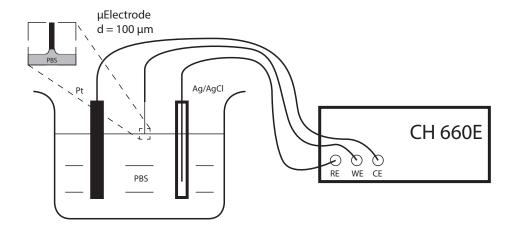

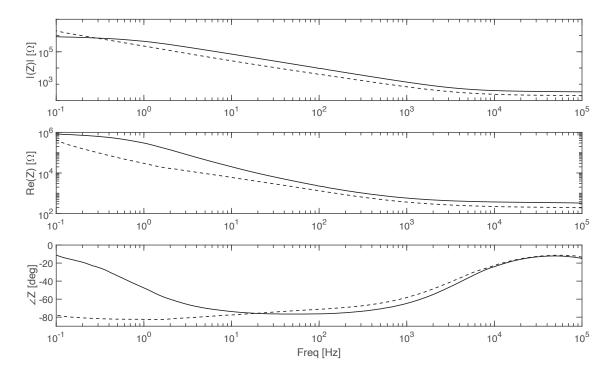

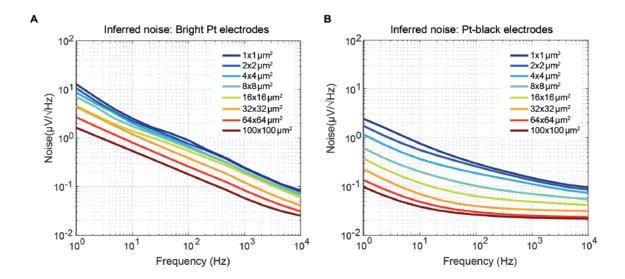

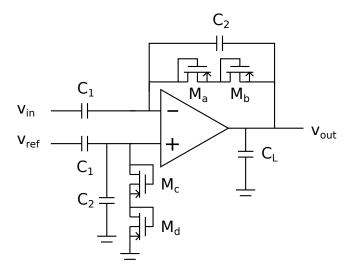

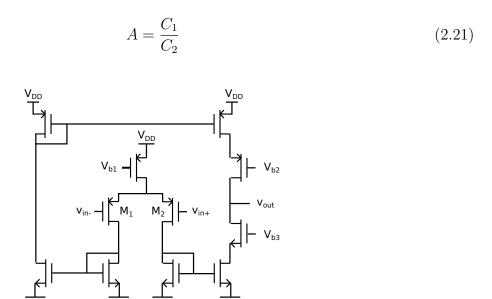

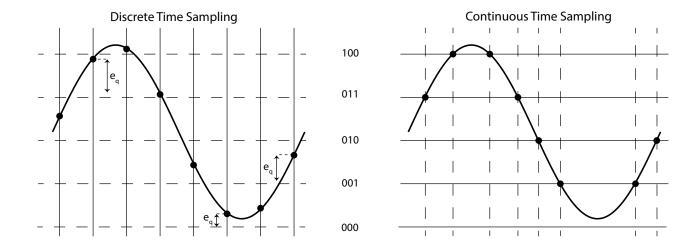

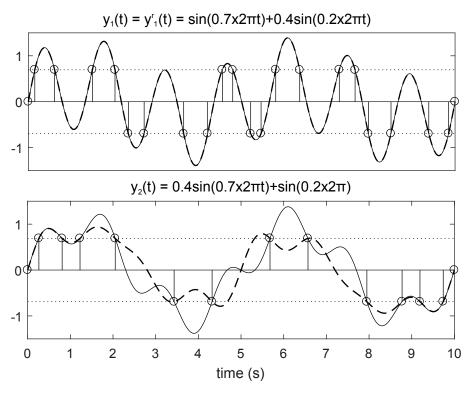

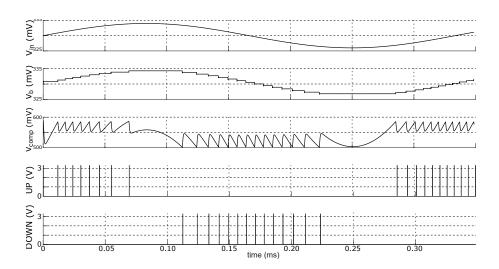

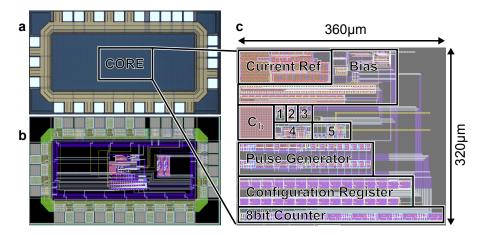

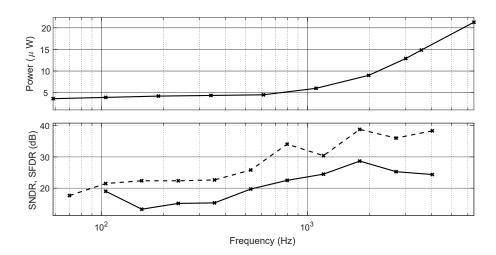

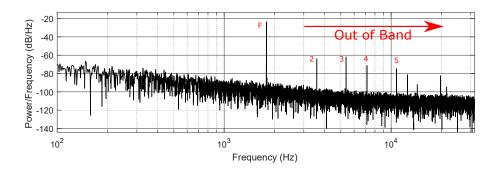

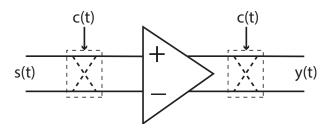

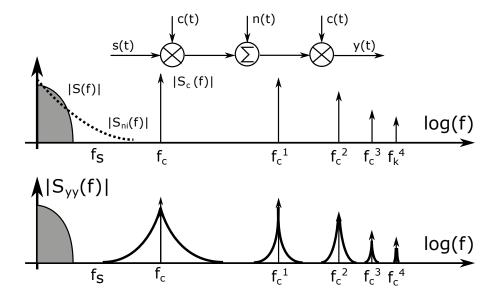

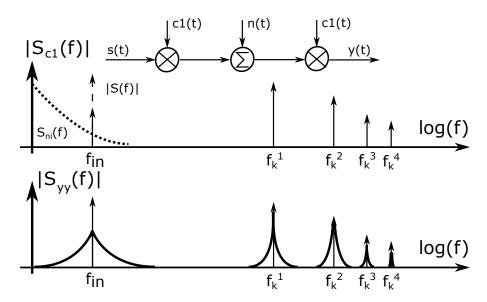

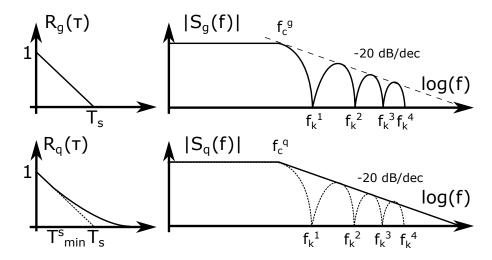

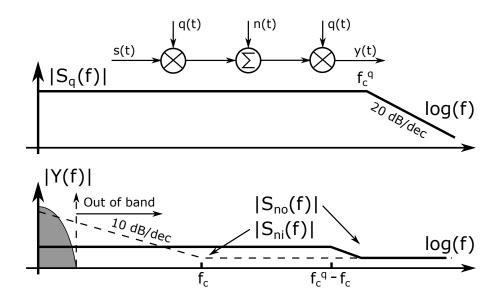

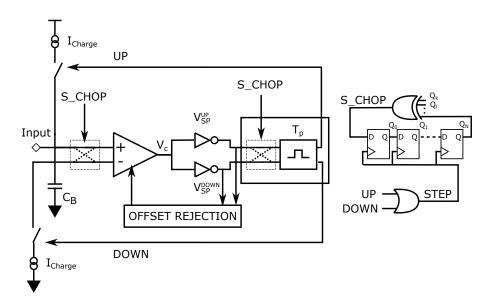

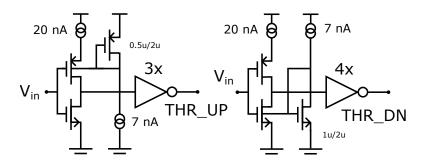

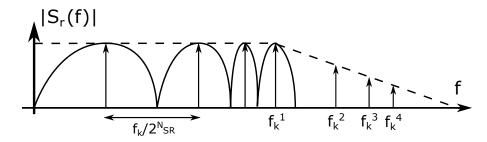

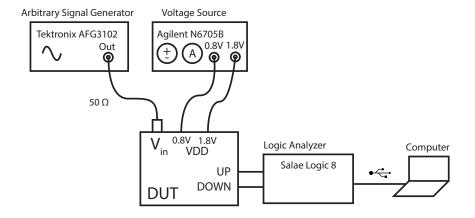

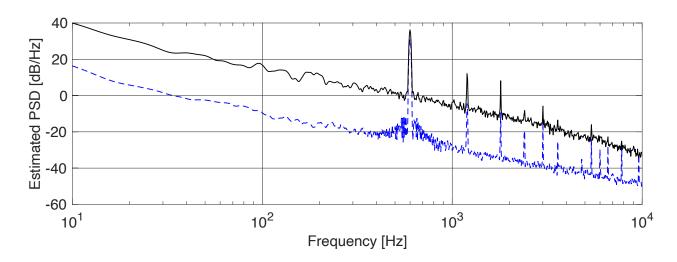

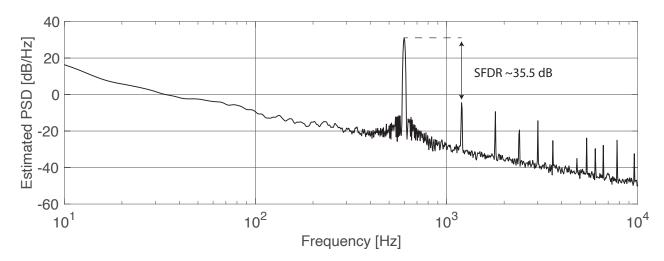

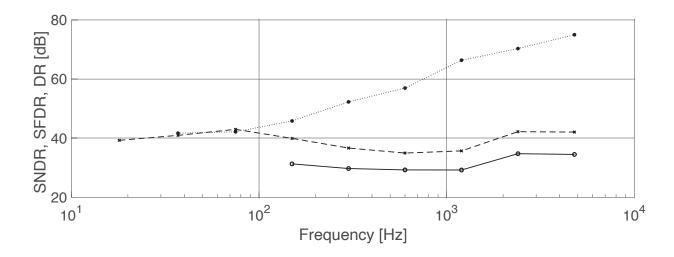

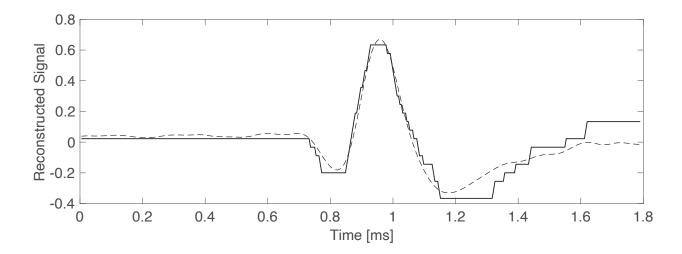

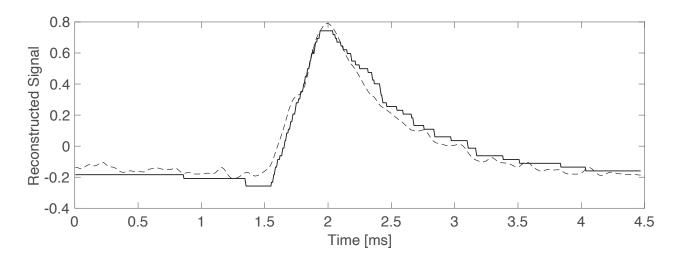

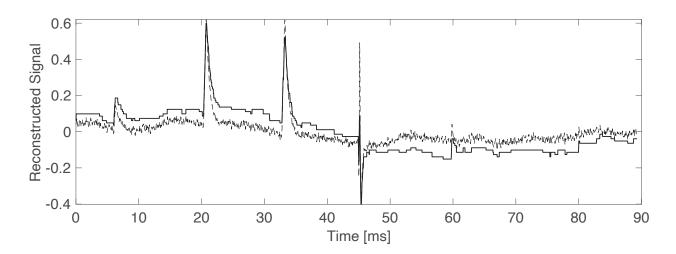

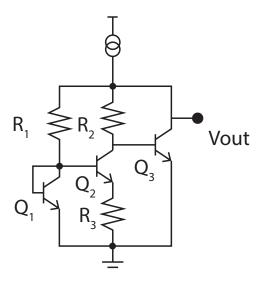

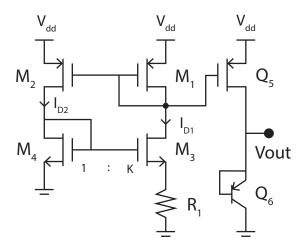

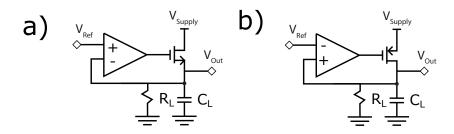

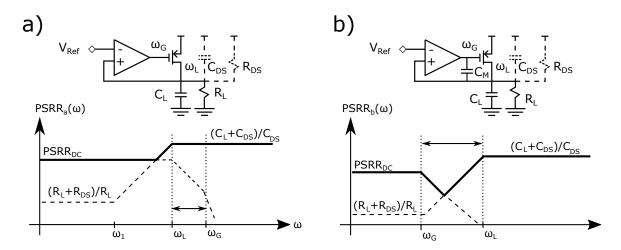

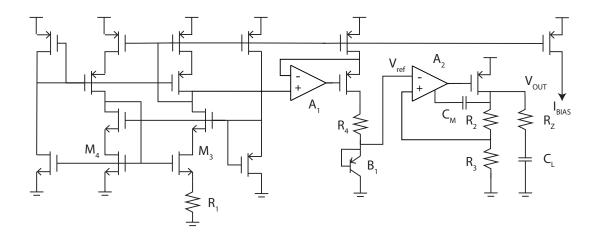

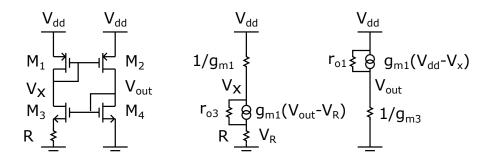

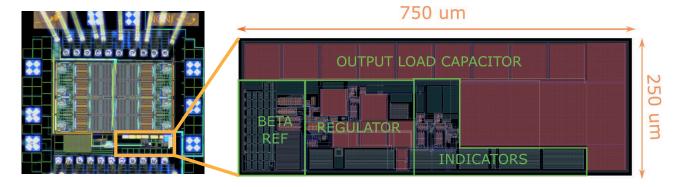

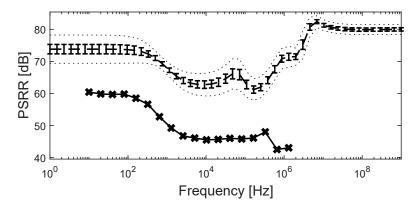

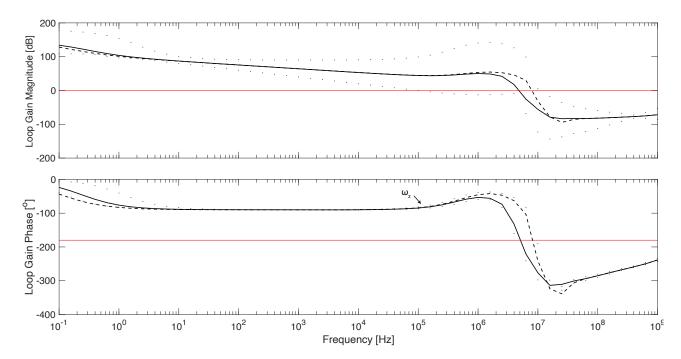

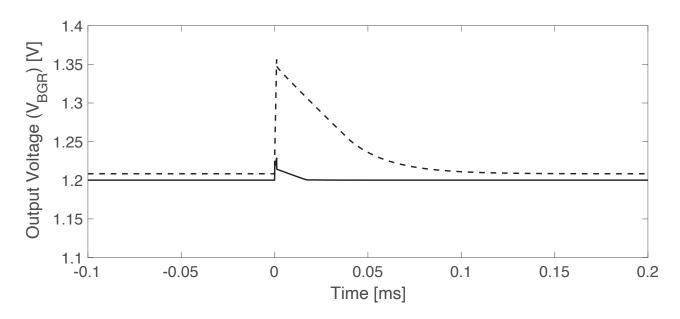

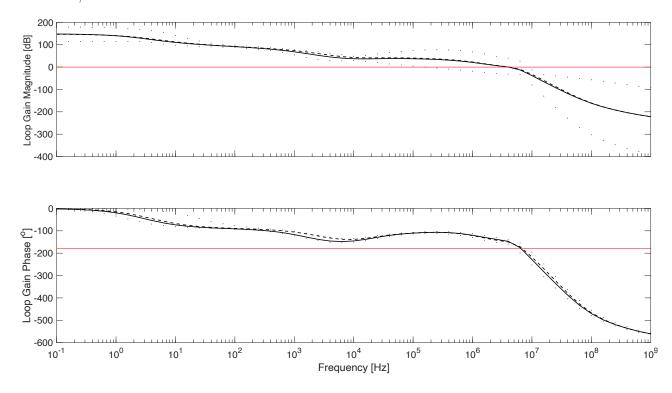

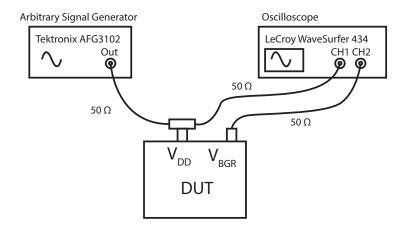

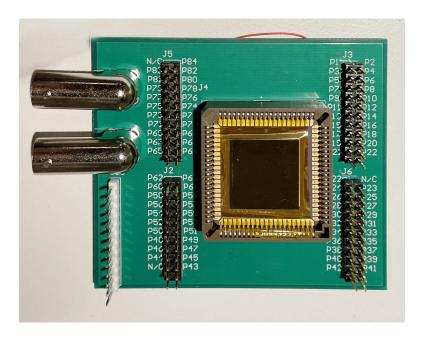

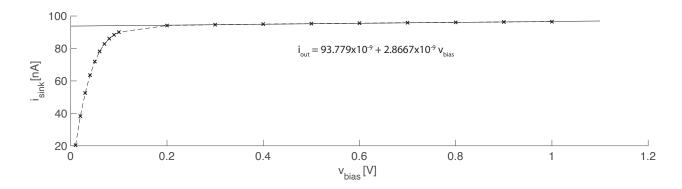

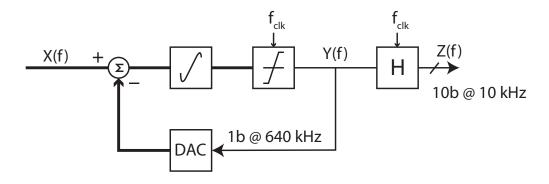

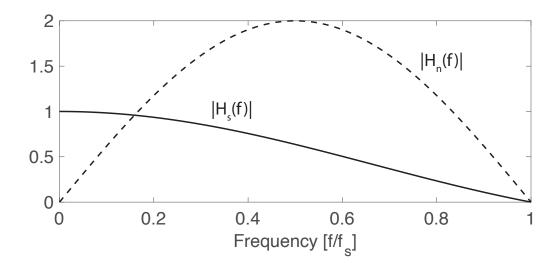

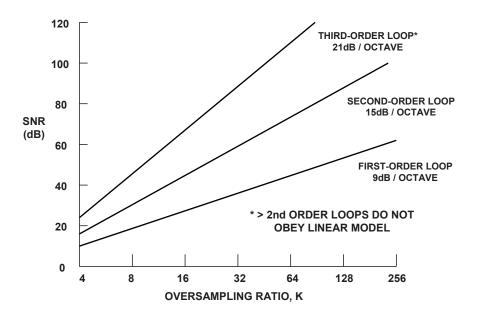

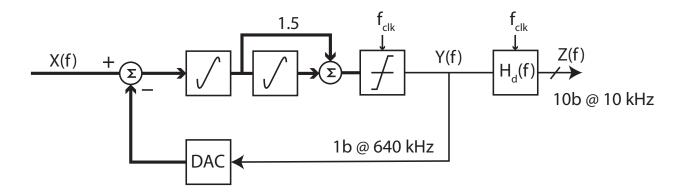

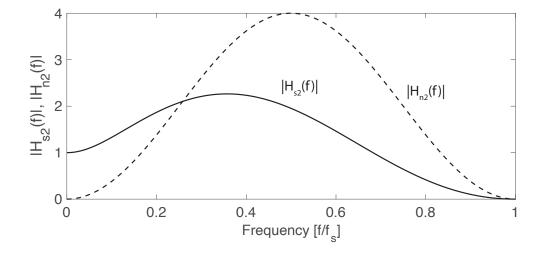

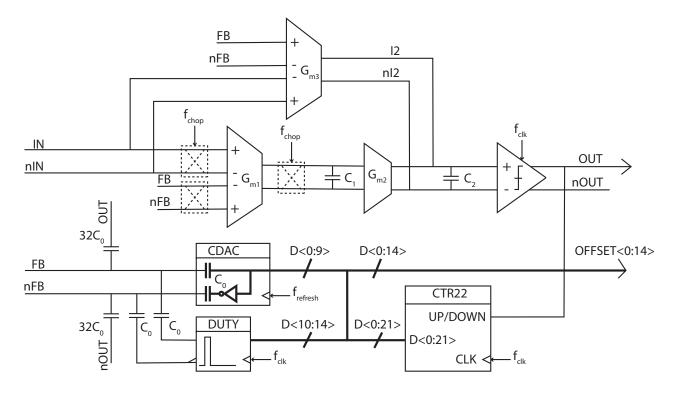

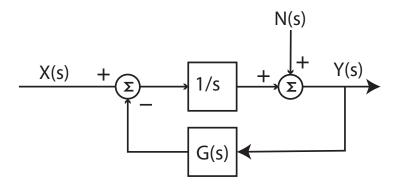

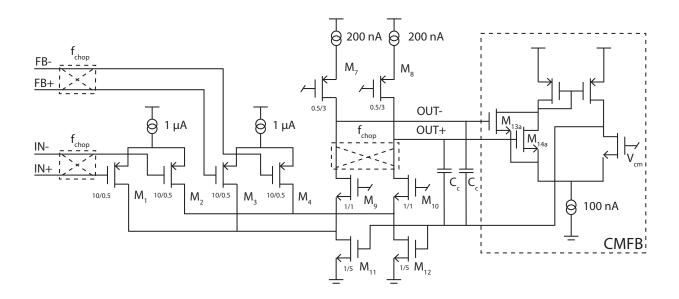

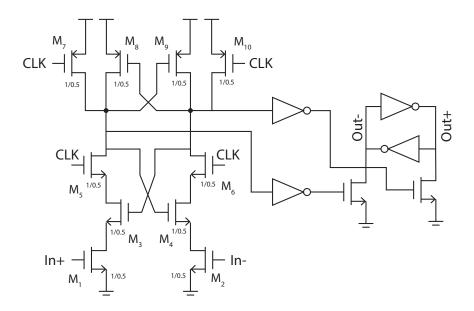

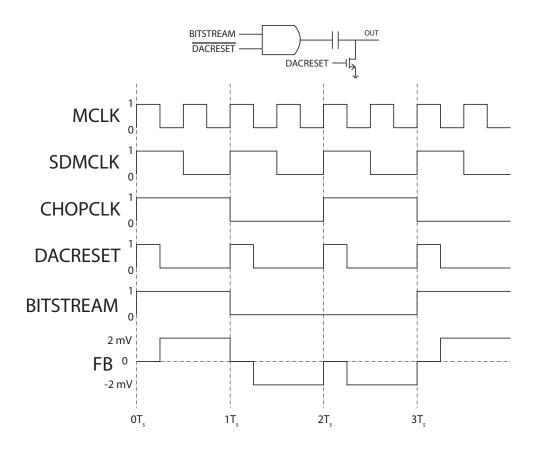

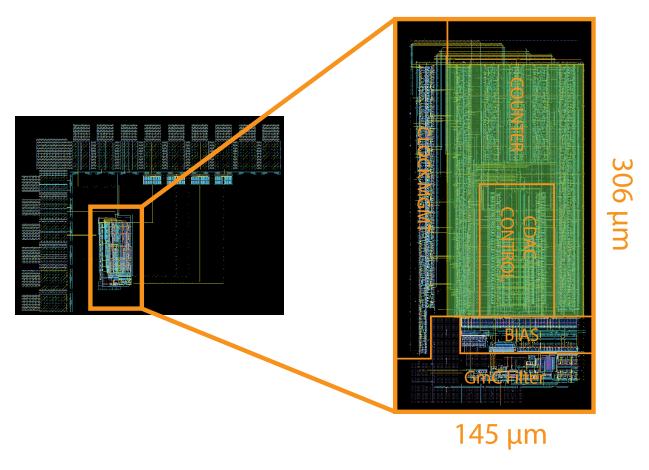

A more practical demonstration of the use of LFPs in BMIs can be seen in work by S. D. Stavisky et al. [72] who have implemented a practical BMI allowing a rhesus monkey implanted with a 96-channel Utah array to control a robotic arm. The decoder of the BMI was implemented in the form of a Kalman filter with both spiking activity and local field potentials as its inputs. It was then shown that a 99% success rate in conducting a randomised target task can be achieved even if all spiking input is removed from the filter and the BMI purely relies on LFP input.