## **Bangor University**

DOCTOR OF PHILOSOPHY

Nanofabrication approaches for Group IV Photonic MEMS devices

Panduranga, Parashara

Award date: 2020

Awarding institution: Bangor University

Link to publication

General rights Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal ?

Take down policy If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

# Nanofabrication approaches for Group IV Photonic MEMS devices

## PRIFYSGOL BANGOR UNIVERSITY

## Parashara Panduranga

Supervisor: Dr. Maziar P Nezhad

School of Computer Science and Electronic Engineering College of Environmental Sciences and Engineering

This dissertation is submitted for the degree of Doctor of Philosophy

December 2019

## **Declaration and Consent**

## **Details of the Work**

I hereby agree to deposit the following item in the digital repository maintained by Bangor University and/or in any other repository authorized for use by Bangor University.

| Author Name:                   |

|--------------------------------|

| Title:                         |

| Supervisor/Department:         |

| Funding body (if any):         |

| Qualification/Degree obtained: |

This item is a product of my own research endeavours and is covered by the agreement below in which the item is referred to as "the Work". It is identical in content to that deposited in the Library, subject to point 4 below.

## **Non-exclusive Rights**

Rights granted to the digital repository through this agreement are entirely non-exclusive. I am free to publish the Work in its present version or future versions elsewhere.

I agree that Bangor University may electronically store, copy or translate the Work to any approved medium or format for the purpose of future preservation and accessibility. Bangor University is not under any obligation to reproduce or display the Work in the same formats or resolutions in which it was originally deposited.

## **Bangor University Digital Repository**

I understand that work deposited in the digital repository will be accessible to a wide variety of people and institutions, including automated agents and search engines via the World Wide Web.

I understand that once the Work is deposited, the item and its metadata may be incorporated into public access catalogues or services, national databases of electronic theses and dissertations such as the British Library's EThOS or any service provided by the National Library of Wales.

I understand that the Work may be made available via the National Library of Wales Online Electronic Theses Service under the declared terms and conditions of use (http://www.llgc.org.uk/index.php?id=4676). I agree that as part of this service the National Library of Wales may electronically store, copy or convert the Work to any approved medium or format for the purpose of future preservation and accessibility. The National Library of Wales is not under any obligation to reproduce or display the Work in the same formats or resolutions in which it was originally deposited.

## Statement 1:

This work has not previously been accepted in substance for any degree and is not being concurrently submitted in candidature for any degree unless as agreed by the University for approved dual awards.

Signed ..... (candidate)

Date .....

## Statement 2:

This thesis is the result of my own investigations, except where otherwise stated. Where correction services have been used, the extent and nature of the correction is clearly marked in a footnote(s).

All other sources are acknowledged by footnotes and/or a bibliography.

Signed ..... (candidate)

Date .....

## Statement 3:

I hereby give consent for my thesis, if accepted, to be available for photocopying, for interlibrary loan and for electronic storage (subject to any constraints as defined in statement 4), and for the title and summary to be made available to outside organisations.

Signed ..... (candidate)

Date .....

**NB:** Candidates on whose behalf a bar on access has been approved by the Academic Registry should use the following version of **Statement 3**:

#### Statement 3 (bar):

I hereby give consent for my thesis, if accepted, to be available for photocopying, for interlibrary loans and for electronic storage (subject to any constraints as defined in statement 4), after expiry of a bar on access.

Signed ..... (candidate)

Date .....

#### <u>Statement 4</u>:

Choose one of the following options

| a) | I agree to deposit an electronic copy of my thesis (the Work) in the Bangor University (BU)<br>Institutional Digital Repository, the British Library ETHOS system, and/or in any other<br>repository authorized for use by Bangor University and where necessary have gained the<br>required permissions for the use of third party material.                                                  |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| b) | I agree to submit my thesis (the Work) electronically via Bangor University's e-submission system, however I <b>opt-out</b> of the electronic deposit to the Bangor University (BU)<br>Institutional Digital Repository, the British Library ETHOS system, and/or in any other repository authorized for use by Bangor University, due to lack of permissions for use of third party material. |  |

## In addition to the above I also agree to the following:

- 1. That I am the author or have the authority of the author(s) to make this agreement and do hereby give Bangor University the right to make available the Work in the way described above.

- 2. That the electronic copy of the Work deposited in the digital repository and covered by this agreement, is identical in content to the paper copy of the Work deposited in the Bangor University Library, subject to point 4 below.

- 3. That I have exercised reasonable care to ensure that the Work is original and, to the best of my knowledge, does not breach any laws including those relating to defamation, libel and copyright.

- 4. That I have, in instances where the intellectual property of other authors or copyright holders is included in the Work, and where appropriate, gained explicit permission for the inclusion of that material in the Work, and in the electronic form of the Work as accessed through the open access digital repository, *or* that I have identified and removed that material for which adequate and appropriate permission has not been obtained and which will be inaccessible via the digital repository.

- 5. That Bangor University does not hold any obligation to take legal action on behalf of the Depositor, or other rights holders, in the event of a breach of intellectual property rights, or any other right, in the material deposited.

- 6. That I will indemnify and keep indemnified Bangor University and the National Library of Wales from and against any loss, liability, claim or damage, including without limitation any related legal fees and court costs (on a full indemnity bases), related to any breach by myself of any term of this agreement.

Signature: ..... Date : .....

## Acknowledgements

Firstly, I would like to thank and express my gratitude towards my supervisor Dr. Maziar Nezhad for his guidance, support and assistance during the entire course of my study. Without his encouragement and inspiration, this thesis would not have been possible. I would also like to thank my colleague and lab-mate, Dr. Aly Abdou for always being extremely helpful and offering invaluable insight.

I have greatly enjoyed my time in Bangor, and strongly believe that it has contributed positively to my professional and personal development. The people in the School of Computer Science and Electronic Engineering have been extremely understanding and helpful during the course of my study. I would like to thank Dr. Paul Sayers, Mr. Ben Assinder, Mr. Iwan Jones and Mr. David Jones from the department. I would also like to acknowledge the help and advice provided by Dr. Li Chen and Dr. Mark Rosamond from the University of Leeds.

I would also like to acknowledge and thank the Sêr Cymru National Research Network for providing the financial support for my studies. In particular, I would like to thank Prof. Huw Summers, Mrs. Claudia Rabello Strugnell and Ms. Ruth Thomas for their help.

Finally, and most importantly, I would like to thank my wife, Rashmi, and my parents along with my family and friends, who have always been there for me and have provided me with their unconditional support, love, encouragement and help.

## Abstract

Photonics has attracted a great deal of interest due to the rapid growth of the telecommunications industry. As silicon has been studied for decades in the semiconductor and microelectronics industry, the experience and infrastructure developed can be implemented in the fabrication of photonic devices. Therefore, the development of new materials and processes for this application is crucial. In this thesis, the materials and techniques used in the fabrication of suspended structures and photonic devices are studied.

Anisotropic etching is an essential technique necessary for the fabrication of photonic devices such as waveguides. The need for a reliable and repeatable etching process is discussed, along with the development of anisotropic etching recipes for silicon, silicon nitride and nano-crystalline diamond (NCD). The effect of etch roughness, along with the methods to reduce the roughness is also discussed, as well as the effect of various etch parameters on the etch rate and selectivity.

Waveguides fabricated in nano-crystalline diamond (NCD) on a silicon substrate with a propagation loss of 4.6 dB/mm has been demonstrated. The silicon substrate has to be undercut in order to isolate the mode in the NCD core, as the guiding layer (NCD) has a lower refractive index than silicon. In order to achieve this, the silicon was isotropically etched through an ICP-RIE process using  $SF_6$ .

$SF_6$  has been studied as an isotropic silicon etchant as a replacement for vapour phase etchants such as  $XeF_2$ . The etch rate is strongly dependent on the feature size, density and shape. This dependency is theoretically analysed, and supported experimentally. Also, the effect of this chemistry on photonic materials such as NCD, silicon nitride and silica, as well as on commonly used masking materials such as photoresists has been investigated.

Finally, a novel bonding process, which avoids the use of top down isotropic etching is presented. This can be beneficial as it enables the integration of various materials with silicon.

## **Table of contents**

| Li | st of f | figures                                 | XV |  |  |  |  |

|----|---------|-----------------------------------------|----|--|--|--|--|

| Li | st of t | st of tables                            |    |  |  |  |  |

| 1  | Intr    | oduction                                |    |  |  |  |  |

|    | 1.1     | Background and Motivation               | 1  |  |  |  |  |

|    | 1.2     | Thesis Outline                          | 2  |  |  |  |  |

| 2  | Elec    | ctromagnetic wave theory and background | 5  |  |  |  |  |

|    | 2.1     | Introduction                            | 5  |  |  |  |  |

|    | 2.2     | Maxwell's Equations                     | 5  |  |  |  |  |

|    | 2.3     | Waveguides                              | 8  |  |  |  |  |

|    |         | 2.3.1 Modes in a Waveguide              | 9  |  |  |  |  |

|    |         | 2.3.2 Waveguide Configurations          | 10 |  |  |  |  |

|    | 2.4     | Optical Materials                       | 13 |  |  |  |  |

|    | 2.5     | Losses in Waveguides                    | 15 |  |  |  |  |

|    |         | 2.5.1 Scattering Losses                 | 15 |  |  |  |  |

|    |         | 2.5.2 Absorption Losses                 | 16 |  |  |  |  |

|    |         | 2.5.3 Radiation Losses                  | 16 |  |  |  |  |

|    | 2.6     | Dispersion                              | 17 |  |  |  |  |

|    | 2.7     | Numerical Methods                       | 19 |  |  |  |  |

|    | 2.8     | Coupling                                | 20 |  |  |  |  |

|    |         | 2.8.1 In-plane Couplers                 | 21 |  |  |  |  |

|   |      | 2.8.2    | Out-of-plane Couplers                | . 23 |

|---|------|----------|--------------------------------------|------|

|   | 2.9  | Summ     | nary and Perspective                 | . 25 |

| 3 | Fabi | rication | 1                                    | 27   |

|   | 3.1  | Introdu  | uction                               | . 27 |

|   | 3.2  | Sample   | e Preparation                        | . 27 |

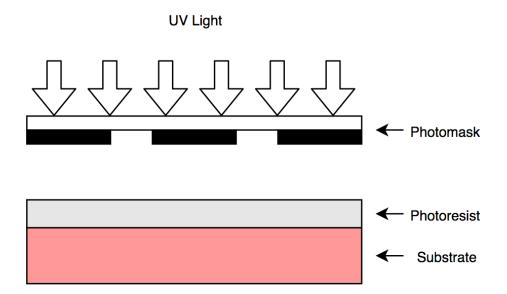

|   | 3.3  | Photol   | lithography                          | . 28 |

|   |      | 3.3.1    | Contact Lithography                  | . 30 |

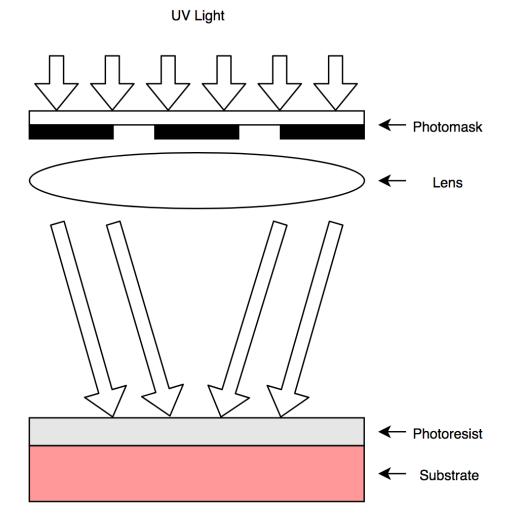

|   |      | 3.3.2    | Projection Lithography               | . 31 |

|   |      | 3.3.3    | Electron Beam Lithography            | . 32 |

|   |      | 3.3.4    | Photoresists                         | . 34 |

|   |      | 3.3.5    | Baking Steps During Photolithography | . 36 |

|   |      | 3.3.6    | Resist Removal                       | . 37 |

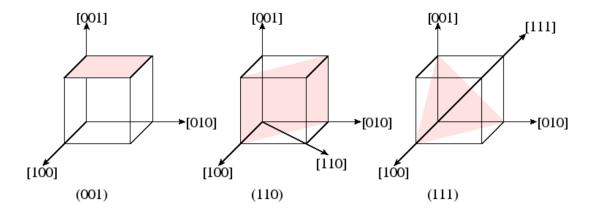

|   | 3.4  | Etchin   | 1g                                   | . 38 |

|   |      | 3.4.1    | Wet Etching                          | . 38 |

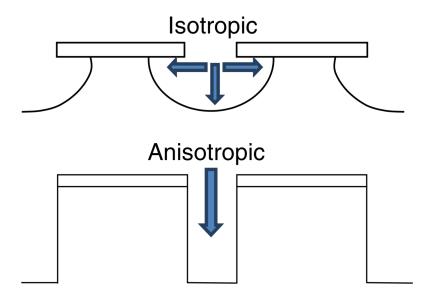

|   |      | 3.4.2    | Dry Etching                          | . 41 |

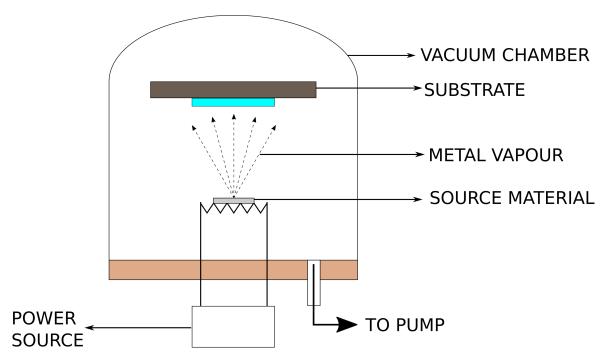

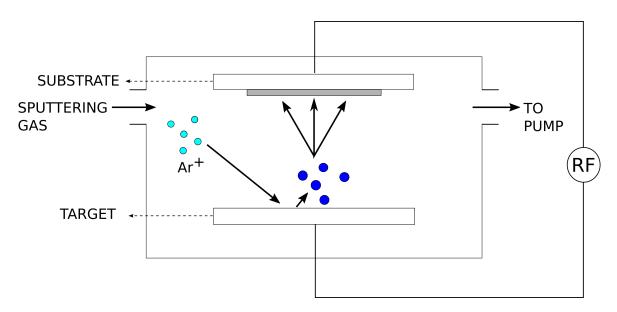

|   | 3.5  | Depos    | sition Techniques                    | . 53 |

|   |      | 3.5.1    | Thermal Evaporation                  | . 53 |

|   |      | 3.5.2    | Sputtering                           | . 55 |

|   | 3.6  | Metrol   | logy and Inspection                  |      |

|   | 3.7  | Summ     | nary and Perspective                 | . 59 |

| 4 | Anis | otropic  | c etching                            | 61   |

|   | 4.1  | Etch M   | Mechanisms                           | . 63 |

|   | 4.2  | Etch T   | Fools                                | . 64 |

|   | 4.3  | Reacto   | or Preparation                       | . 65 |

|   | 4.4  | Anisot   | tropic Silicon Etching               | . 65 |

|   |      | 4.4.1    | Purpose of Etch Gases                | . 66 |

|   |      | 4.4.2    | Black Silicon Method                 | . 68 |

|   |      | 4.4.3    | Experimental                         | . 70 |

|   |      |          | L .                                  |      |

|   |       | 4.4.4     | Results and Discussion                                                  | 82    |

|---|-------|-----------|-------------------------------------------------------------------------|-------|

|   | 4.5   | Anisot    | ropic Silicon Nitride Etching                                           | 84    |

|   |       | 4.5.1     | Sample Preparation and Mask Selection                                   | 88    |

|   |       | 4.5.2     | Experimental                                                            | 88    |

|   |       | 4.5.3     | Results and Discussion                                                  | 89    |

|   | 4.6   | Anisot    | ropic Nano-Crystalline Diamond (NCD) Etching                            | 90    |

|   |       | 4.6.1     | Experimental                                                            | 90    |

|   |       | 4.6.2     | Results and Discussion                                                  | 91    |

|   | 4.7   | Summ      | ary and Perspective                                                     | 92    |

| 5 | Air-  | clad sus  | spended nanocrystalline diamond ridge waveguides                        | 93    |

|   | 5.1   | Introdu   | uction                                                                  | 93    |

|   | 5.2   | Design    | 1                                                                       | 96    |

|   | 5.3   | Fabric    | ation                                                                   | 98    |

|   | 5.4   | Optica    | l Measurements                                                          | 100   |

|   | 5.5   | Summ      | ary and Perspective                                                     | 105   |

| 6 | Isotı | ropic sil | icon etch characteristics in a purely inductively coupled $SF_6$ plasma | a 107 |

|   | 6.1   | Introdu   | uction                                                                  | 107   |

|   |       | 6.1.1     | Semiconductor Etching                                                   | 107   |

|   |       | 6.1.2     | The SF <sub>6</sub> Isotropic ICP Etch                                  | 108   |

|   |       | 6.1.3     | Isotropic Etching in Photonic Device Fabrication                        | 110   |

|   | 6.2   | Experi    | mental                                                                  | 111   |

|   |       | 6.2.1     | Sample Preparation                                                      | 112   |

|   |       | 6.2.2     | Experimental Setup                                                      | 113   |

|   | 6.3   | Result    | s and Analysis                                                          | 117   |

|   | 6.4   | Summ      | ary and Perspective                                                     | 123   |

| 7 | Etch  | n rates o | of various materials in ICP $SF_6$ and their selectivity to silicon     | 125   |

|   | 7.1   | Introdu   | uction                                                                  | 125   |

|    | 7.2   | Experimental methods                             | 126 |

|----|-------|--------------------------------------------------|-----|

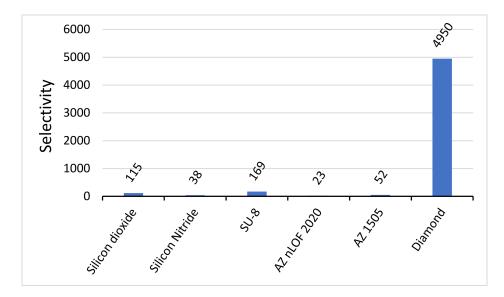

|    | 7.3   | Results and Discussion                           | 128 |

|    | 7.4   | Summary and Perspective                          | 134 |

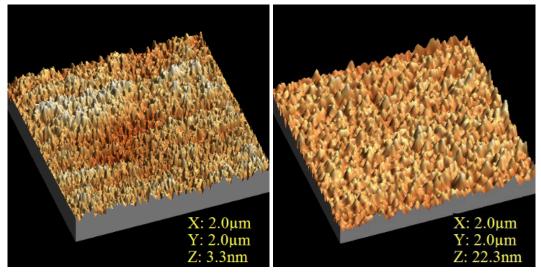

| 8  | Fabi  | rication of a suspended membrane through bonding | 135 |

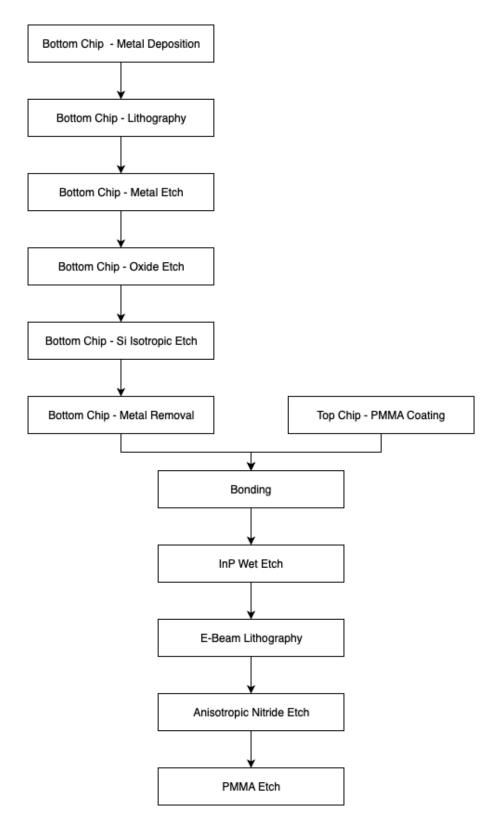

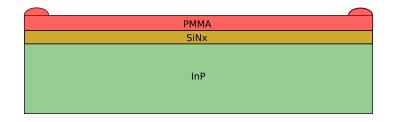

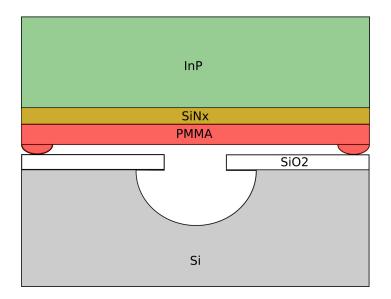

|    | 8.1   | Lower chip fabrication                           | 137 |

|    | 8.2   | Top chip fabrication                             | 139 |

|    | 8.3   | Chip scale bonding                               | 140 |

|    | 8.4   | Bonded chip fabrication                          | 142 |

|    | 8.5   | Summary and Perspective                          | 145 |

| 9  | Con   | clusion                                          | 147 |

|    | 9.1   | Future Vision                                    | 149 |

| Ap | pend  | ix A Photolithography recipes                    | 151 |

| Re | feren | ces                                              | 153 |

## List of figures

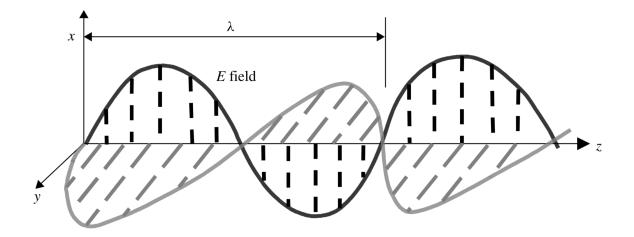

| 2.1  | A wave demonstrating transverse electric and magnetic fields                  | 8  |

|------|-------------------------------------------------------------------------------|----|

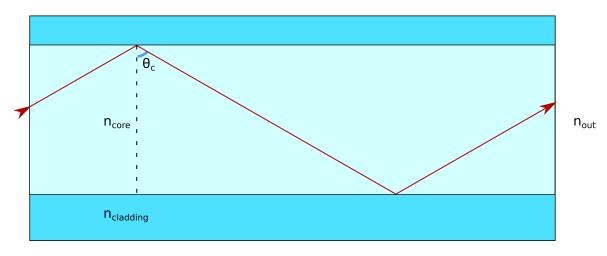

| 2.2  | A ray optics model demonstrating total internal reflection                    | 9  |

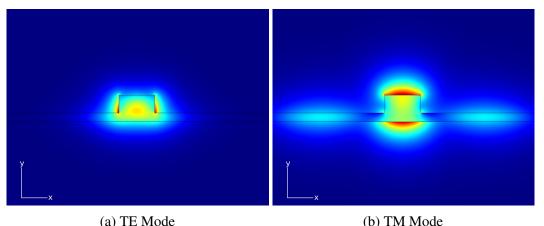

| 2.3  | Electric field profiles in a rib waveguide                                    | 10 |

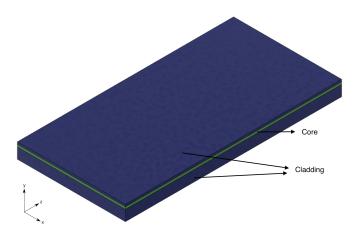

| 2.4  | A schematic depicting a slab waveguide                                        | 11 |

| 2.5  | A schematic depicting a rib waveguide                                         | 12 |

| 2.6  | A schematic depicting a strip waveguide                                       | 13 |

| 2.7  | Buried oxide layer thickness vs slab waveguide thickness to achieve less than |    |

|      | $0.001 \ dB/cm$ loss at 1550 nm                                               | 17 |

| 2.8  | Comparision of optical fibre core dimensions and a waveguide core of 300      |    |

|      | $nm \times 500 nm$                                                            | 21 |

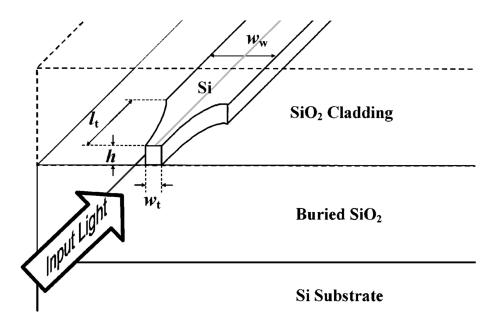

| 2.9  | Inverse taper coupling                                                        | 22 |

| 2.10 | A figure showing the coupling between an optical fibre and a grating coupler  | 24 |

| 3.1  | Steps in the photolithography process                                         | 29 |

| 3.2  | A schematic of the contact lithography process                                | 31 |

| 3.3  | A schematic of the proximity lithography process                              | 32 |

| 3.4  | A schematic of the projection lithography process                             | 33 |

| 3.5  | The crystalline structure of silicon along with the Miller indices            | 41 |

| 3.6  | Isotropic vs anisotropic etch profiles                                        | 43 |

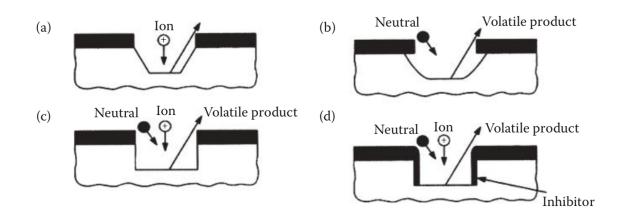

| 3.7  | Dry etching techniques                                                        | 46 |

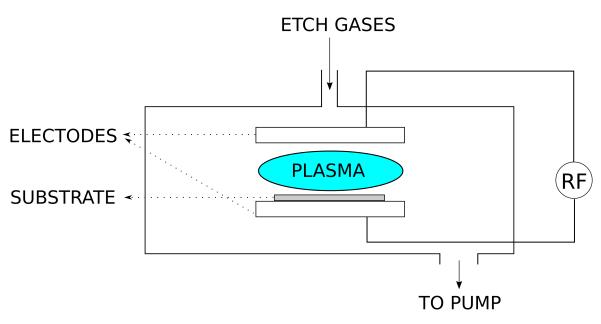

| 3.8  | A schematic layout of a plasma etching system                                 | 47 |

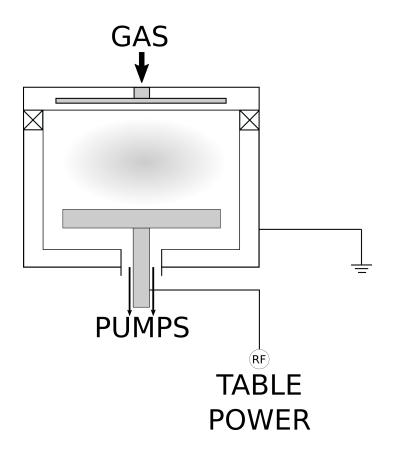

| 3.9  | A schematic layout of a CCP-RIE reactor                                       | 48 |

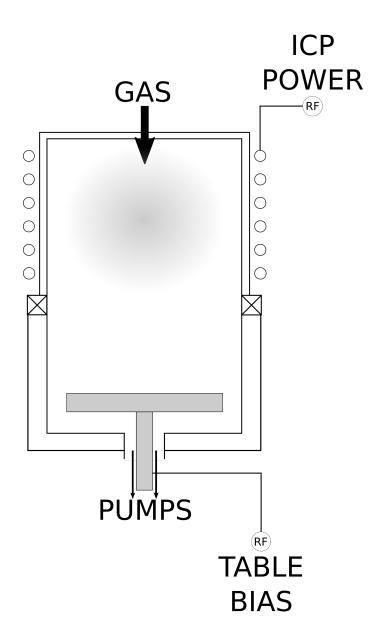

| 3.10 | A schematic layout of an ICP-RIE reactor                                                               | 50 |

|------|--------------------------------------------------------------------------------------------------------|----|

| 3.11 | Schematic of a thermal evaporator                                                                      | 55 |

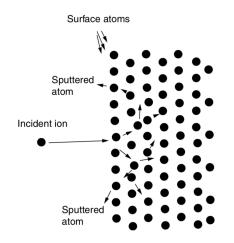

| 3.12 | Mechanism of physical sputtering                                                                       | 56 |

| 3.13 | Schematic of a sputter deposition system                                                               | 57 |

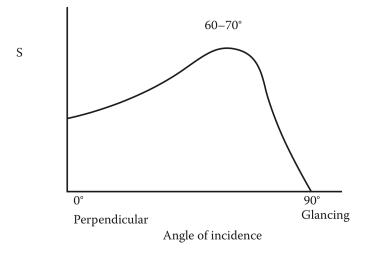

| 3.14 | Sputter yield vs angle of incidence                                                                    | 58 |

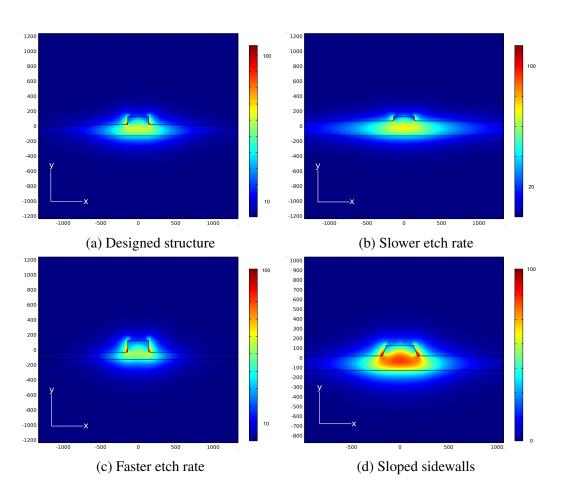

| 4.1  | Difference in mode shape due to undesirable etch characteristics                                       | 62 |

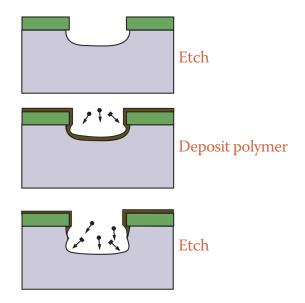

| 4.2  | A schematic depicting the etching principle of the Bosch process                                       | 67 |

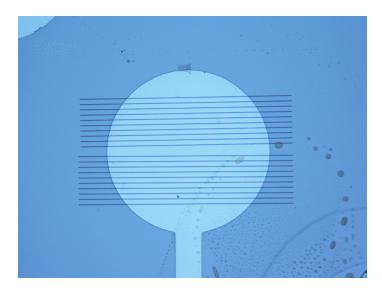

| 4.3  | Photoresist masks for etch characterisation                                                            | 72 |

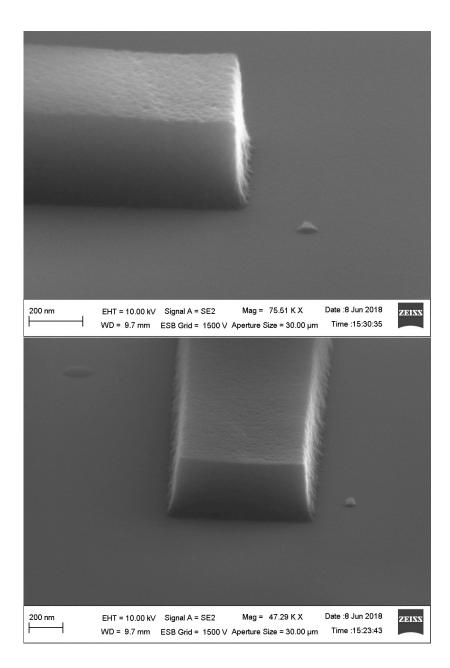

| 4.4  | MaN E-beam resist profile                                                                              | 73 |

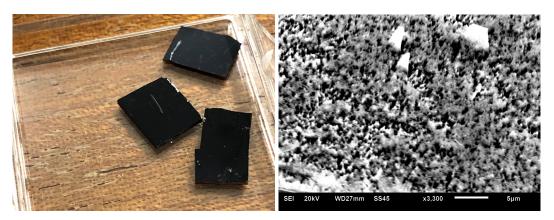

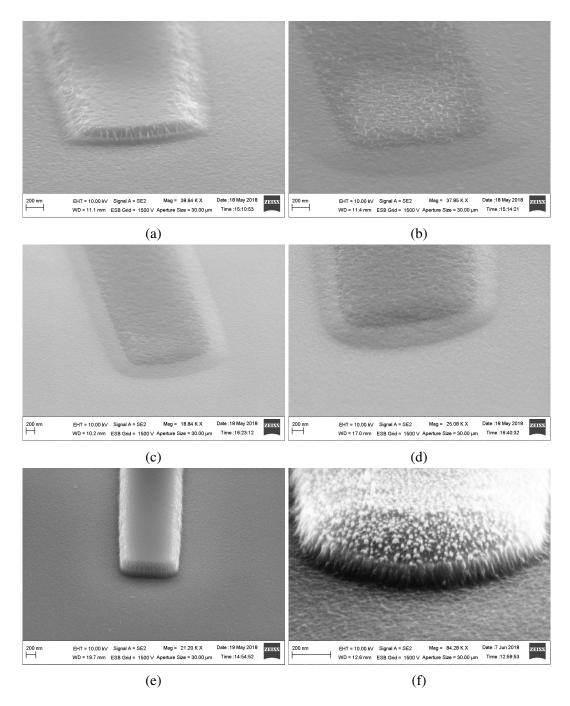

| 4.5  | Formation of black silicon                                                                             | 74 |

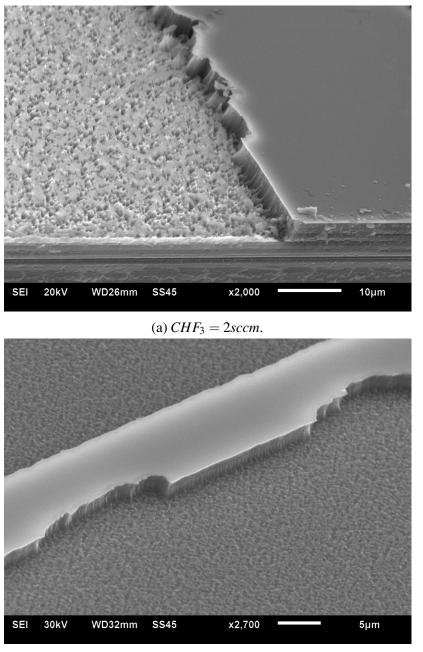

| 4.6  | Addition of $CHF_3$ to black silicon                                                                   | 76 |

| 4.7  | Optimal etch recipe without silicon carrier wafer                                                      | 77 |

| 4.8  | Etch profiles obtained using the black silicon method (with silicon carrier                            |    |

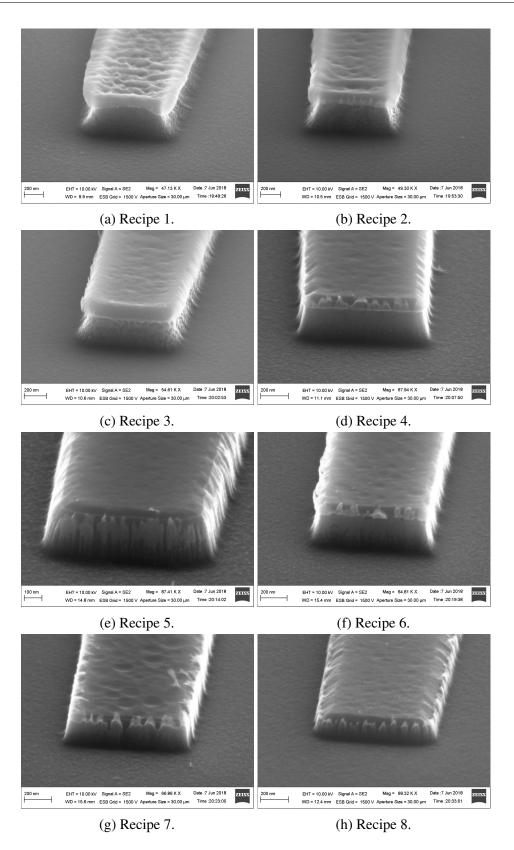

|      | wafer)                                                                                                 | 78 |

| 4.9  | Etch profiles obtained without $O_2$ (without silicon carrier wafer)                                   | 79 |

| 4.10 | Etch profiles obtained without $O_2$ (with silicon carrier wafer)                                      | 80 |

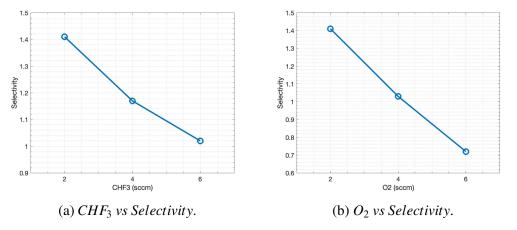

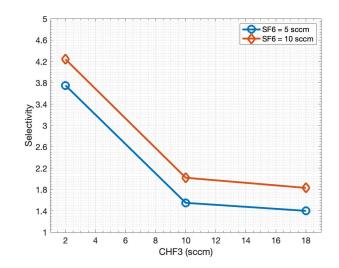

| 4.11 | The effect of gas flow rates on selectivity (black silicon method)                                     | 80 |

| 4.12 | The effect of $CHF_3$ flow rate on selectivity (No $O_2$ )                                             | 81 |

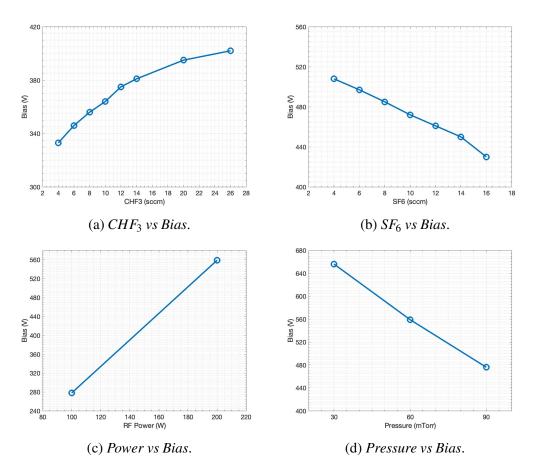

| 4.13 | The effect of etch parameters on Bias voltage                                                          | 82 |

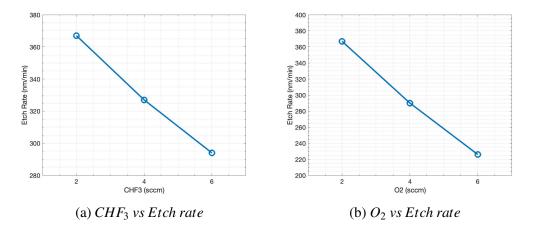

| 4.14 | The effect of gas flow rates on etch rate (black silicon method)                                       | 83 |

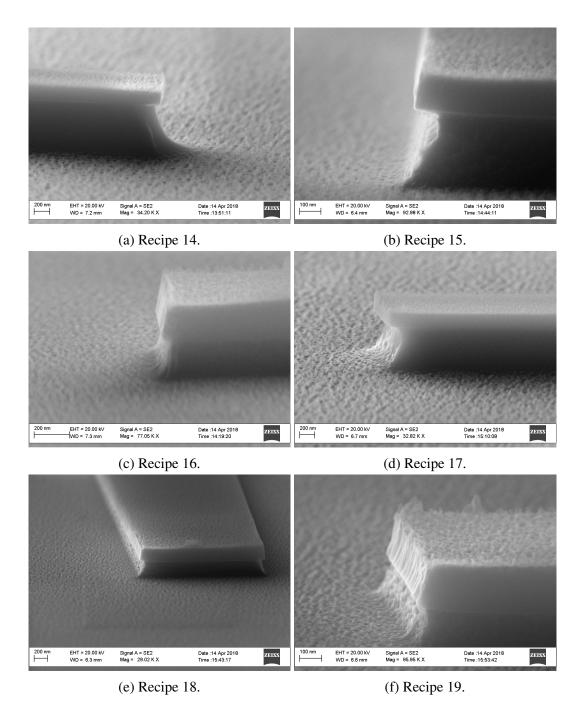

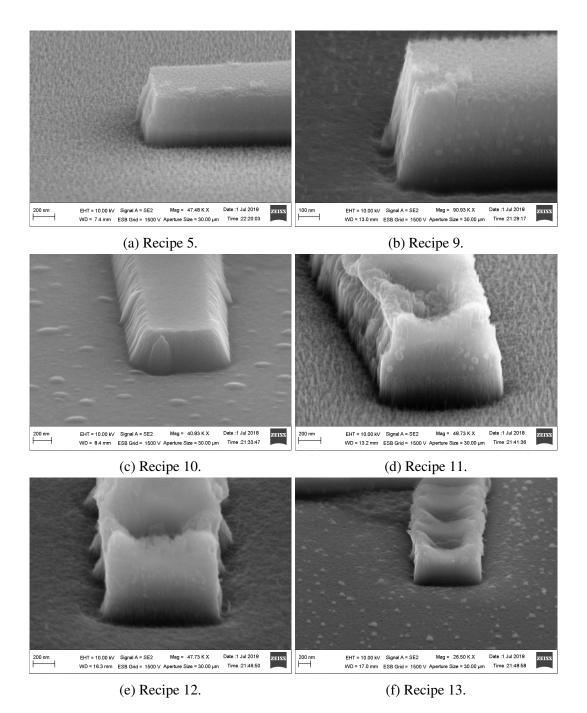

| 4.15 | Nitride etch profiles                                                                                  | 86 |

| 4.16 | Nitride etch profiles (with resist mask present)                                                       | 87 |

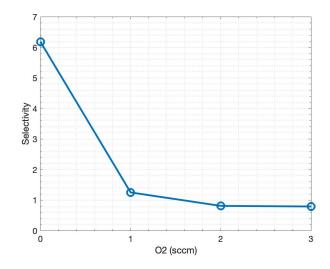

| 4.17 | The effect of $O_2$ flow rate on selectivity $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 89 |

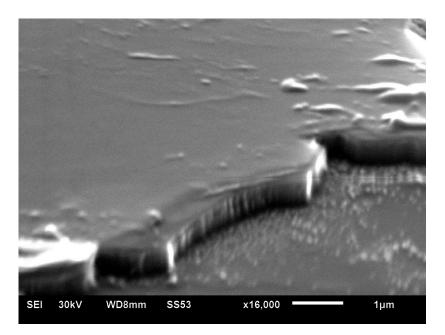

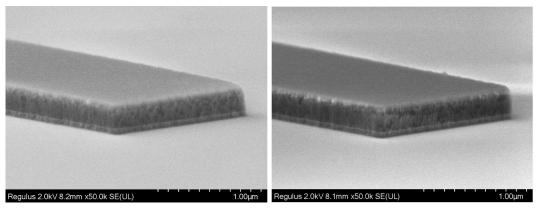

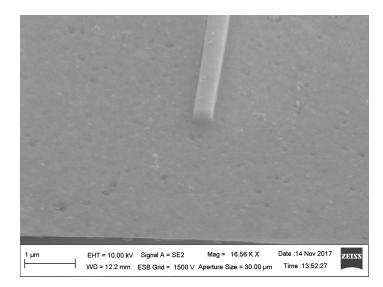

| 4.18 | Completed NCD waveguide.                                                                               | 91 |

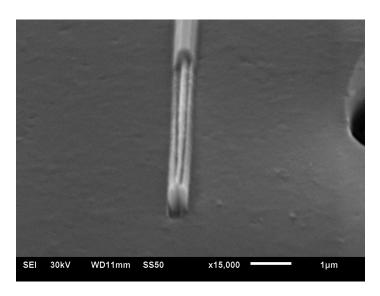

| 4.19 | NCD etch (with partial HSQ mask present).                                                              | 92 |

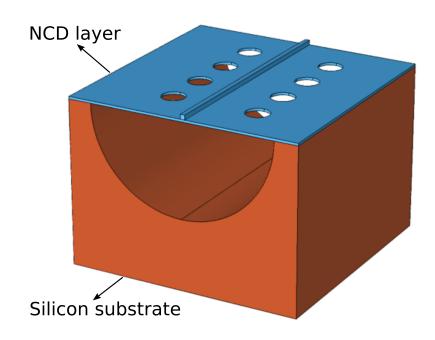

| 5.1  | Schematic of the proposed structure                                                                    | 95 |

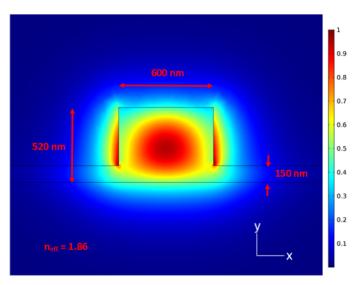

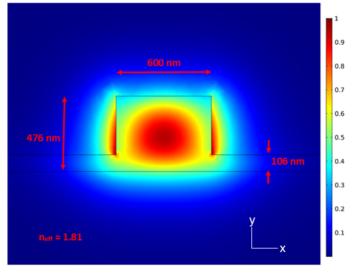

| 5.2  | Dimensions of the NCD waveguide                                                                        | 97 |

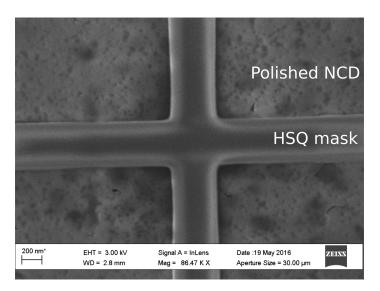

| 5.3  | SEM image of NCD surface after e-beam lithography of HSQ etch mask                                     | 99 |

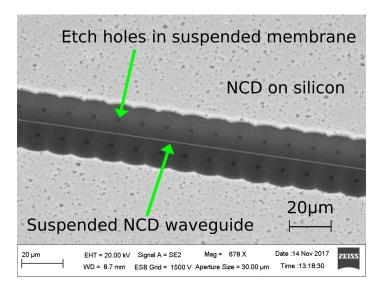

| 5.4  | SEM image of the undercut waveguide and membrane                                                  | 100          |

|------|---------------------------------------------------------------------------------------------------|--------------|

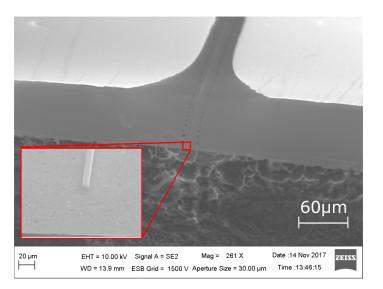

| 5.5  | SEM image of the input waveguide taper showing membrane sag                                       | 101          |

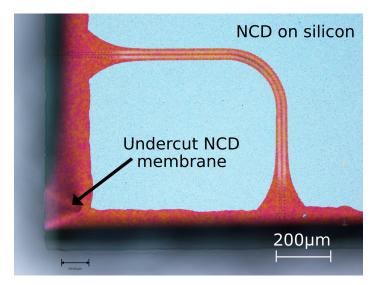

| 5.6  | Optical image of an undercut waveguide showing the sagging edges on the chip                      | <b>o</b> 102 |

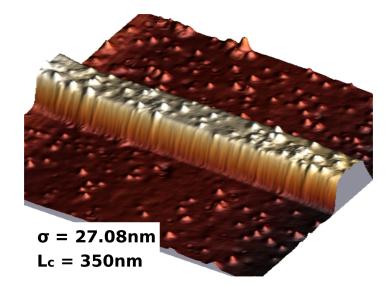

| 5.7  | AFM image of waveguide ridge with roughness measurements                                          | 103          |

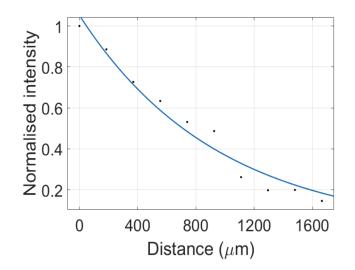

| 5.8  | Example of power decay measurement fitting                                                        | 104          |

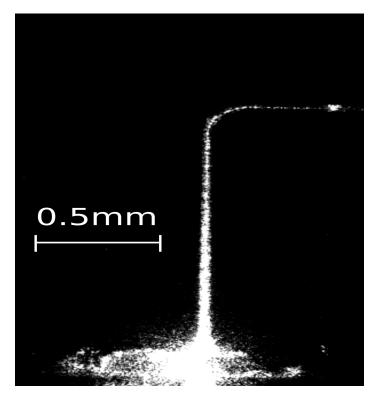

| 5.9  | IR image of the scattered light at 1.55 $\mu m$                                                   | 106          |

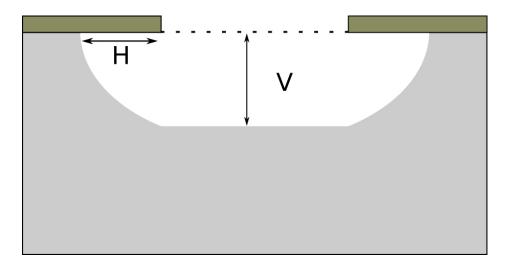

| 6.1  | A schematic of the definition of isotropy used, showing the location of the $H$                   |              |

|      | and V measurements                                                                                | 112          |

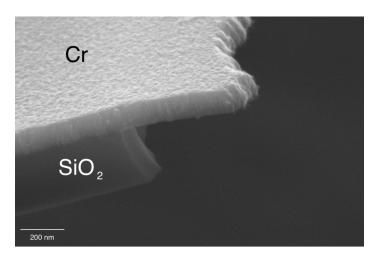

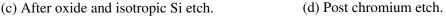

| 6.2  | The suspended edge of the chromium on silica mask, after isotropic removal                        |              |

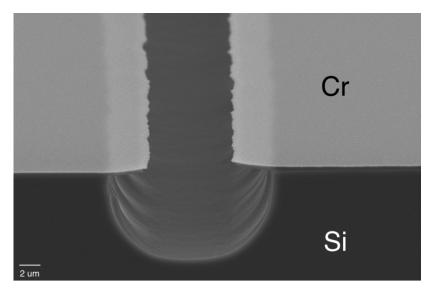

|      | of the underlying silicon in the $SF_6$ plasma $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 113          |

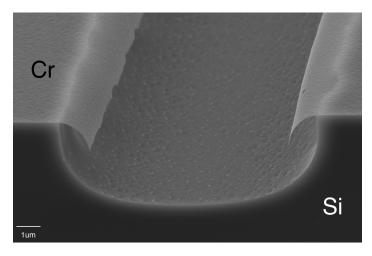

| 6.3  | Sag of the unsupported chromium mask layer during undercut                                        | 113          |

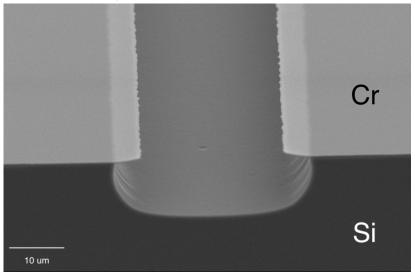

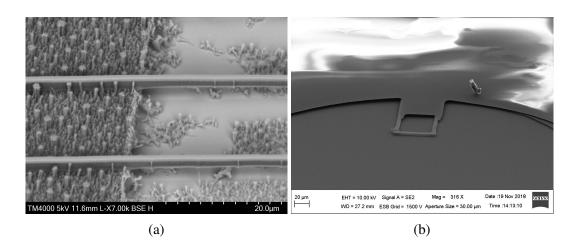

| 6.4  | SEM images of the 8 $\mu m$ and 28 $\mu m$ lines after the isotropic etch (5 mins) .              | 115          |

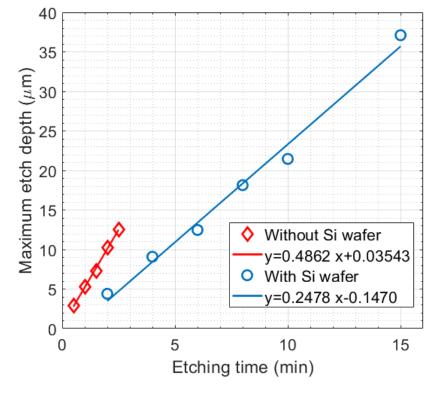

| 6.5  | Etch depth vs etch time with and without silicon carrier                                          | 116          |

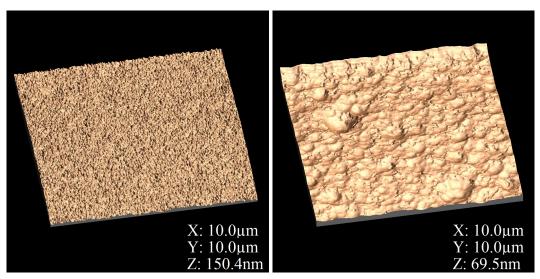

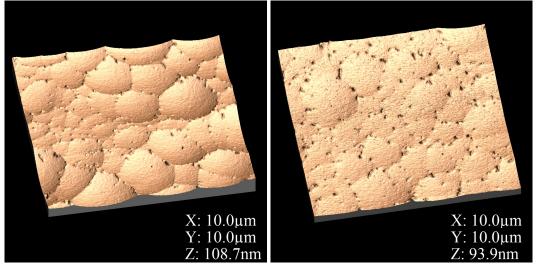

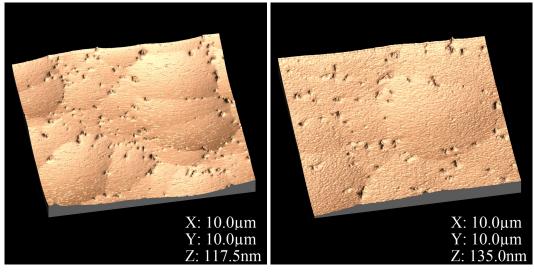

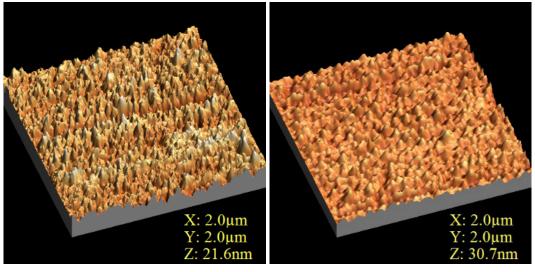

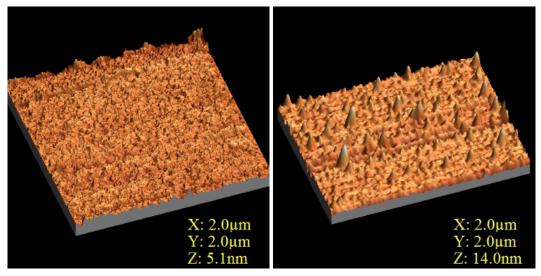

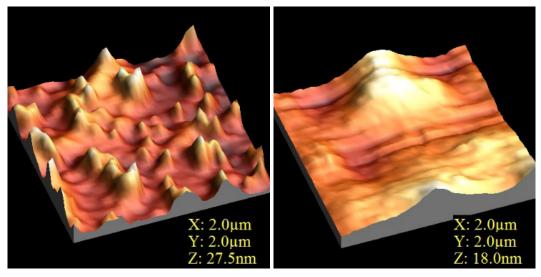

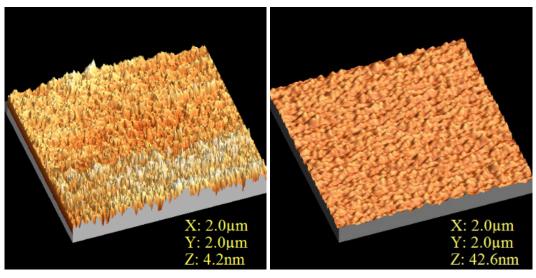

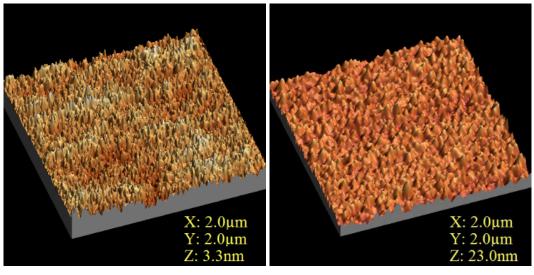

| 6.6  | AFM scans of the surface roughness for different etch times                                       | 118          |

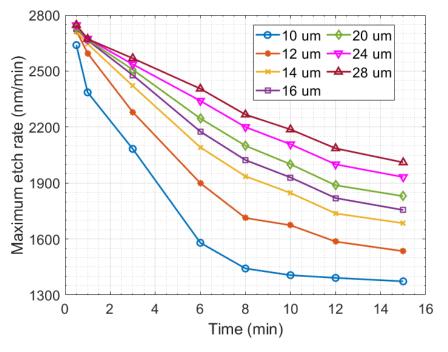

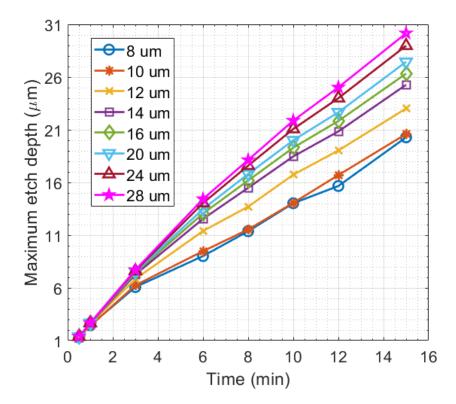

| 6.7  | Maximum etch rate vs etch time for pattern set 2                                                  | 119          |

| 6.8  | Etch depth vs etch time for pattern set 2                                                         | 119          |

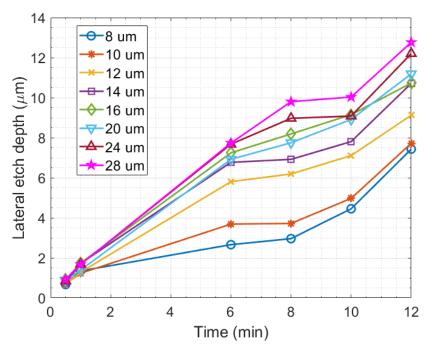

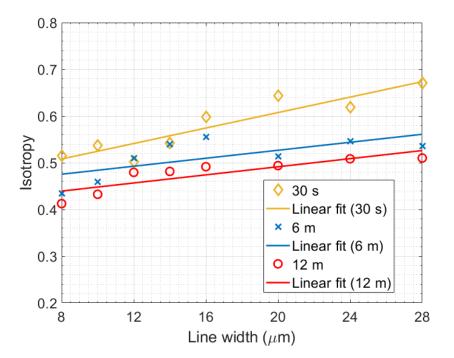

| 6.9  | Lateral etch depth vs etch time for pattern 2                                                     | 120          |

| 6.10 | Isotropy of the etch for a range of times vs line width                                           | 122          |

| 7.1  | Selectivity of silicon over tested materials in $SF_6$ ICP etching                                | 127          |

| 7.2  | AFM profiles of $Si_x N_y$ before and after 10 minutes of ICP $SF_6$ etching                      | 128          |

| 7.3  | AFM profiles of $SiO_2$ before and after 10 minutes of ICP $SF_6$ etching                         | 129          |

| 7.4  | AFM profiles of NCD before and after 10 minutes of ICP $SF_6$ etching                             | 130          |

| 7.5  | AFM profiles of AZ-1505 before and after 10 minutes of ICP $SF_6$ etching .                       | 131          |

| 7.6  | AFM profiles of AZ-nLOF 2020 before and after 10 minutes of ICP $SF_6$                            |              |

|      | etching                                                                                           | 132          |

| 7.7  | AFM profiles of SU-8 before and after 10 minutes of ICP $SF_6$ etching                            | 133          |

| 8.1  | Overview of the bonding process                                                                   | 136          |

| 8.2  | Bottom chip processing                                                                            | 137          |

| 8.3  | Silicon undercut for the bottom chip                                | 138 |

|------|---------------------------------------------------------------------|-----|

| 8.4  | Top chip with PMMA                                                  | 139 |

| 8.5  | Imperfect bond formed due to edge bead                              | 140 |

| 8.6  | Bonding using larger top chip                                       | 140 |

| 8.7  | Bonding quality                                                     | 141 |

| 8.8  | Bonded chip processing                                              | 142 |

| 8.9  | An image showing the suspended nitride membrane over voids with the |     |

|      | venting ducts visible                                               | 143 |

| 8.10 | An optical image of the bonded membrane over a void                 | 144 |

| 8.11 | E-beam patterns over void                                           | 144 |

| 8.12 | Suspended structures over void                                      | 145 |

## List of tables

| 3.1  | Kinetic data for air vs pressure                                             | 54  |

|------|------------------------------------------------------------------------------|-----|

| 3.2  | Dependence of sputtering yield on various factors                            | 57  |

| 4.1  | Black silicon initial parameters                                             | 71  |

| 4.2  | Black silicon recipe                                                         | 74  |

| 4.3  | Black silicon method - smooth surface                                        | 75  |

| 4.4  | Black silicon method - Varying flow rates                                    | 75  |

| 4.5  | Black silicon method - Varying pressure and power                            | 77  |

| 4.6  | Etching recipes without oxygen                                               | 81  |

| 4.7  | Black silicon method - selectivity and profile                               | 83  |

| 4.8  | Etching without oxygen - selectivity and profile                             | 84  |

| 4.9  | Initial nitride etching recipes                                              | 85  |

| 4.10 | Modified nitride etching recipes                                             | 88  |

| 4.11 | Optimal nitride etching recipe                                               | 88  |

| 4.12 | Optimal NCD etching recipe                                                   | 91  |

| 5.1  | Average loss measurements of various waveguides' segments                    | 102 |

| 6.1  | Etch rates of the 500 $\mu m$ circles                                        | 111 |

| 6.2  | Surface Roughness vs Time                                                    | 114 |

| 7.1  | Etch rates $(nm/min)$ of tested materials in $SF_6$ ICP etching              | 128 |

| 7.2  | RMS roughness $(nm)$ before & after 10 mins of $SF_6$ ICP plasma etching for |     |

|      | all materials and 1hr for NCD, and the % increase in RMS surface roughness   | 131 |

| 8.1 | PMMA etch parameters                                | 144 |

|-----|-----------------------------------------------------|-----|

| A.1 | S-1818 photoresist (1.7 $\mu m$ film thickness)     | 151 |

| A.2 | AZ nLof 2020 photoresist (2 $\mu m$ film thickness) | 152 |

| A.3 | AZ 1505 photoresist (450 nm film thickness)         | 152 |

| A.4 | SU8-5 (1.7 $\mu m$ film thickness)                  | 152 |

| A.5 | PMMA (1.75 $\mu m$ film thickness)                  | 152 |

## Chapter 1

## Introduction

## **1.1 Background and Motivation**

Silicon has become a ubiquitous material in the electronics and photonics industry, and with the advent of integrated circuits (ICs), the processing techniques required for the fabrication of these devices have drawn considerable interest. The advent of VLSI (very large scale integration) and ULSI (ultra large scale integration) has necessitated the need for miniturisation, and therefore the development of specialised techniques. Complementary metal-oxide semiconductor (CMOS) is the state of the art processing technology which forms the cornerstone of the IC industry. The entire manufacturing process has been optimised for extremely large volume manufacturing, resulting in high yields and uniformity.

Silicon also possesses favourable optical properties as its band gap of approximately 1.1 eV ensures that the material is transparent in the wavelengths used for optical communications (between 1.3 and 1.6  $\mu$ m). Silicon also has a high refractive index (3.4), which ensures high mode confinement, thereby enabling miniturisation. As a result, passive optical devices (such as waveguides) can be easily fabricated in silicon using the techniques developed for CMOS processing, thus utilising the existing manufacturing infrastructure. Various photonic components can be fabricated on a single chip, thereby forming photonic integrated circuits (PICs), which can be considered to be analogous to electronic ICs. Since PICs consist of many different individual components, it is very important that these components

are appropriately integrated with waveguides, since waveguides form the signal paths in the circuit. The interaction of the components can also be controlled via micro electromechanical systems (MEMS) actuation [1]. MEMS actuation has also been demonstrated in the realisation of switching arrays [2]. This requires the fabrication of suspended structures. Suspended waveguides can also increase the efficiency of chemical evanescent field sensing [3]. Hence, studying the methods and techniques used for the fabrication of these suspended structures is crucial.

In the work presented in this thesis, we present the design and fabrication of suspended structures, along with the development of the methods that are required to realise these devices. A suspended waveguide fabricated in nano-crystalline diamond (NCD) over silicon, using a novel fabrication process is demonstrated. We have also investigated in detail a related technique for the isotropic etching of silicon, which is required in the formation of membranes and overhanging structures. The effect of this etch on commonly used materials was also studied in order to understand its effect on these materials, and the results analysed. Finally, a unique bonding technique is presented, which can be used to fabricate suspended membranes.

## 1.2 Thesis Outline

The thesis is organised in chapters that are self-contained; the chapters that contain experimental work includes the necessary background required, experimental methods and results. Most of the SEM images in the thesis were acquired in the University of Manchester by Dr. Maziar Nezhad.

In Chapter 2, the theoretical background necessary for the understanding of the working of optical components such as waveguides is presented. Similarly, the basics of the fabrication techniques (such as lithography, dry and wet etching, and deposition) necessary for the fabrication of these devices is explored in Chapter 3.

The anisotropic etching of silicon, silicon nitride and NCD was studied in Chapter 4, with the focus being the fabrication of waveguides. It is important that the etch results in

vertical and smooth sidewalls in order to ensure that the losses are minimised. Engineering the etch is crucial, as the quality of the etch depends on various factors such as mask material, reactor size and material, pump capacity etc.

In Chapter 5, a hybrid group IV ridge waveguide platform is demonstrated, with potential application across the optical spectrum from ultraviolet to the far infrared wavelengths. The waveguides were fabricated by partial etching of sub-micron ridges in NCD grown on top of a silicon wafer. To create vertical confinement, the diamond film was locally undercut by exposing the chip to an isotropic fluorine plasma etch via etch holes surrounding the waveguides, resulting in a mechanically stable suspended air-clad waveguide platform. The optical simulations for this study were performed by Dr. Aly Abdou.

Chapter 6 consists of the study of the characteristics of isotropic etching of silicon in a purely inductively coupled  $SF_6$  plasma. Since the etch results are strongly dependent on mask features, we investigated both large area and narrow trench etch characteristics. Circles of diameter 500  $\mu m$  were used as a proxy for unpatterned surfaces and etched for different durations to establish the material etch rate and surface roughness.

In Chapter 7, we have investigated the effect of  $SF_6$  plasma on various commonly used materials that are used along with silicon. The etch rates of silicon dielectric derivatives,  $SiO_2$  and  $Si_xN_y$ , polymers (positive and negative photoresists and SU-8), and nanocrystalline diamond (NCD) were studied. In particular, the effect of  $SF_6$  on NCD has not been previously studied in depth, and therefore is of considerable interest.

In Chapter 8, the fabrication of a suspended membrane using a bonding process is described. This is an alternative method to the isotropic etch process that has been described earlier (in Chapter 5).

Finally, the conclusions are presented in Chapter 9, along with future vision and research considerations.

## **Chapter 2**

# Electromagnetic wave theory and background

## 2.1 Introduction

This chapter provides the theoretical background necessary for the work presented in this thesis. Here, a brief introduction to the fundamentals of electromagnetic theory along with a general background of photonic devices is given. The basic working principle as well as some of the commonly used configurations of dielectric waveguides is provided. The material properties of silicon, silica, silicon nitride, and diamond are also discussed. Both the waveguide configuration and the choice of material have an effect on the properties of the device, which are reviewed in this chapter. Finally, the common coupling techniques are discussed, as well as the numerical methods that are used to design photonic structures.

## 2.2 Maxwell's Equations

Maxwell's equations are a set of four equations that describe the behaviour of electromagnetic radiation. These equations were first proposed by James Maxwell in 1864 [4], and are commonly presented in the differential form as:

$$\nabla \times \mathbf{H} = \frac{\partial \mathbf{D}}{\partial t} + J, \qquad (2.1)$$

$$\nabla \times \mathbf{E} = -\frac{\partial \mathbf{B}}{\partial t},\tag{2.2}$$

$$\nabla \cdot \mathbf{D} = \boldsymbol{\rho},\tag{2.3}$$

$$\nabla \cdot \mathbf{B} = 0. \tag{2.4}$$

**E** and **H** are the electric and magnetic field vectors respectively, **D** is the electric displacement, **B** is the magnetic flux density, *J* is the current density and  $\rho$  is the charge density.

Usually in photonics source free situations in dielectric materials are considered. Hence, we can set  $\rho = J = 0$  [5]. Also, in isotropic and non-magnetic media the constitutive relations

$$\mathbf{D} = \boldsymbol{\varepsilon} \mathbf{E} = \boldsymbol{\varepsilon}_r \boldsymbol{\varepsilon}_0 \mathbf{E},\tag{2.5}$$

$$\mathbf{B} = \boldsymbol{\mu}_0 \mathbf{H},\tag{2.6}$$

are implicitly assumed. Applying these constraints to Equations 2.1-2.4, we get

$$\nabla \times \mathbf{E} = \frac{\partial}{\partial t} \mu_0 \mathbf{H}, \qquad (2.7)$$

$$\nabla \times \mathbf{H} = \frac{\partial}{\partial t} \boldsymbol{\varepsilon} \mathbf{E}, \qquad (2.8)$$

$$\nabla \cdot \mathbf{E} = 0, \tag{2.9}$$

$$\nabla \cdot \mathbf{H} = 0. \tag{2.10}$$

Through the above equations and the application of the vector identity

$$\nabla \times \nabla \times \mathbf{A} = \nabla \left( \nabla \cdot \mathbf{A} \right) - \nabla^2 \mathbf{A}, \tag{2.11}$$

we arrive at the Helmholtz equations.

$$\nabla^2 \mathbf{E} = \mu \varepsilon \frac{\partial^2 \mathbf{E}}{\partial t^2},\tag{2.12}$$

$$\nabla^2 \mathbf{B} = \mu \varepsilon \frac{\partial^2 \mathbf{B}}{\partial t^2}.$$

(2.13)

In vacuum,  $\varepsilon_r = \mu_r = 1$ , and the speed of the wave is given by [6]

$$c = \frac{1}{\sqrt{\varepsilon_0 \mu_0}}.$$

(2.14)

However, in dielectric media, the speed of the wave is slowed down by a factor equal to the refractive index of the material, n, where

$$n = \sqrt{\varepsilon_r \mu_r} = \sqrt{\varepsilon_r}.$$

(2.15)

An important property of an electromagnetic wave is the orientation of its field configurations, which is known as the polarisation of the wave. All electromagnetic waves can be represented as a superposition of different polarisation states [7]. The field components in the direction of propagation of the wave are used in order to categorise them. A Transverse Electric (TE) wave has no electric field in the direction of propagation and the Transverse Magnetic (TM) wave has no magnetic field in the direction of propagation. However, the field orientations cannot be sufficiently described through the transverse nature of the electric or the magnetic field. The direction of symmetry of the structure of interest should be considered in order to define the polarisation state. For example, co-axial structures such as optical fibres support Transverse Electromagnetic (TEM) modes, since they are symmetrical across the transverse plane.

Fig. 2.1 A wave demonstrating transverse electric and magnetic fields (From [8]).

Electromagnetic waves also transmit energy, and the rate of energy transportation can be obtained from Maxwell's equations. The net power flow is given by Poynting's theorem

$$\oint_{S} (\mathbf{E} \times \mathbf{H}) \, \partial S = -\frac{\partial}{\partial t} \int_{v} \left[ \frac{1}{2} \varepsilon \mathbf{E}^{2} + \frac{1}{2} \mu \mathbf{H}^{2} \right] \partial v - \int_{v} \sigma \mathbf{E}^{2} \partial v.$$

(2.16)

The quantity  $\mathbf{E} \times \mathbf{H}$  on the left hand side of the equation is known as Poynting Vector, which represents the instantaneous power density associated with the electromagnetic field at any given point [9].

## 2.3 Waveguides

A waveguide is a structure that can confine and direct the path of an electromagnetic wave. The principle of confining light inside a photonic waveguide is the same as that of in step-index fibres, i.e total internal reflection [10]. A medium of refractive index  $n_{core}$ surrounded by a material with refractive indices  $n_{cladding}$  confines light when  $n_{core} > n_{cladding}$ (Figure 2.2).

When light enters a region of higher refractive index from a region of lower refractive index at an angle exceeding critical angle  $\theta_c$ , the refracted fraction of the wave becomes

Fig. 2.2 A ray optics model demonstrating total internal reflection.

completely imaginary and all the power is carried by the reflected wave. The numerical aperture (*NA*) of the waveguide can be then defined as [11]:

$$NA = \sqrt{n_{core}^2 - n_{cladding}^2} = n_{out} sin(\theta_c).$$

(2.17)

In a dielectric waveguide, the power is carried in both the core and the cladding. This spacial distribution is often helpful while designing the waveguide structure. The confinement factor  $\Gamma$  is defined as the ratio of the power in the core to the total power.

$$\Gamma = \frac{\iint |E(x,y)|^2 dxdy}{\iint |E(x,y)|^2 dxdy}.$$

(2.18)

## 2.3.1 Modes in a Waveguide

The distribution of electric and magnetic fields inside the waveguide is given by the wave equations. In the case of a simple slab waveguide, Equations 2.12 and 2.13 become [12]

$$\frac{\mathrm{d}^2 E_y}{\mathrm{d}x^2} + (k^2 n^2 - \beta^2) E_y = 0, \qquad (2.19)$$

$$\frac{d}{dx}\left(\frac{1}{n^2}\frac{dH_y}{dx}\right) + (k^2 - \frac{\beta^2}{n^2})H_y = 0,$$

(2.20)

where  $\beta$  is called the propagation constant, and  $k_0 = \frac{2\pi}{\lambda_0}$  is the free space wavenumber. Equation 2.19 gives the field distribution of the TE mode, and Equation 2.20 gives the field distribution of the TM mode.

(a) TE Mode

Fig. 2.3 Normalised electric field profiles in a rib waveguide.

Every value of  $\beta$  from Equation 2.19 and Equation 2.20 corresponds to a unique guided mode in the waveguide. The modal effective refractive index  $n_{eff}$  can be defined as

$$n_{eff} = \frac{\beta}{k_0}.$$

(2.21)

A similar technique cannot be used to analyse more complicated waveguide configurations (such as strip or rectangular waveguide structures). In these cases, numerical methods are used.

#### 2.3.2 **Waveguide Configurations**

Dielectric waveguides can be fabricated in different configurations. Common configurations include slab waveguides, rib waveguides and strip waveguides.

#### **Slab Waveguide**

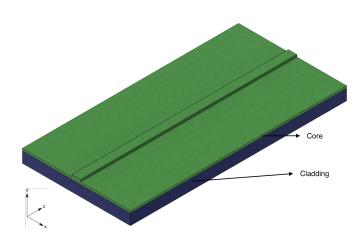

Slab waveguides are the simplest dielectric waveguide structures, consisting of a material of higher refractive index (which acts as the core) sandwiched between two layers of lower refractive indices (which act as cladding) (Figure 2.4). Typically the thickness of the core is in the order of half a wavelength [13] for single mode operation.

Fig. 2.4 A schematic depicting a slab waveguide. The core is shown in green and cladding in blue. The wave propagates along the z-axis.

Slab waveguides provide only lateral confinement, and therefore cannot provide horizontal confinement. Even though relatively complex integrated circuits have been demonstrated using slab waveguides [14] [15], most applications require confinement in two dimensions. This can be overcome using other waveguide designs.

#### **Rib Waveguide**

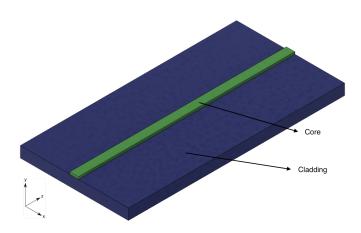

The rib waveguide structure (Figure 2.5) is formed by partially etching the guiding layer of a slab waveguide, forming an inverted 'T' profile. The central rib portion of this structure forms the main propagation area of the waveguide. This configuration is widely used as it is easily achievable on a Silicon-on-Insulator (SOI) platform using Complementary Metal-Oxide-Semiconductor (CMOS) fabrication techniques. The silicon dioxide ( $SiO_2$ ) layer of the SOI platform acts as the lower cladding, and therefore should be thick enough to account for the spatial distribution of the evanescent field.

Fig. 2.5 A schematic depicting a rib waveguide. The core is shown in green and bottom cladding in blue. Air acts as the upper and horizontal cladding layer. The wave propagates along the z-axis.

A disadvantage of the rib waveguide configuration is that the etching process has to be carefully designed to achieve the exact rib height required as the partially etched part of the structure has no etch stop mechanism. However, this can be overlooked as rib waveguides generally exhibit very low propagation losses compared to strip waveguides of similar dimensions [16].

#### **Strip Waveguide**

A strip waveguide is basically a thin strip of the core on top of the bottom cladding material (Figure 2.6). As with the rib waveguide configuration, the bottom cladding should be thick enough to isolate the evanescent mode from the handle material. There are a couple of distinguishing characteristics that strip waveguides exhibit compared to rib waveguides: the higher confinement due to the vertical edges of the waveguide affects the single mode condition (and therefore the waveguide dimensions) and the scattering losses tend to be higher as the mode interaction with the sidewalls is increased. Therefore, strip waveguides are more sensitive to sidewall roughness than rib waveguides [5] [17] [18].

Fig. 2.6 A schematic depicting a strip waveguide. The core is shown in green and bottom cladding in blue. Air acts as the upper and horizontal cladding layer. The wave propagates along the z-axis.

## 2.4 **Optical Materials**

Silicon is a widely used material in photonics because of its abundance in nature and as it offers the ability to fabricate devices using CMOS related fabrication techniques and infrastructure [19] [20], along with its other advantages. Silicon fabrication is a mature technology as it has been the material of choice for the manufacture of transistors. It is transparent in the commonly used telecommunication spectrum (roughly between 1.3  $\mu m$ and 1.6  $\mu m$ ), and since it has a high refractive index (3.4), it leads to high mode confinement and therefore reduction in the size of components [21]. Waveguide bends can designed to have small radii since silicon offers very high index contrast with materials like silicon dioxide and air. As it is a semiconductor, it has very low conductivity, though dopants such as boron and phosphorus can be added to increase it. Certain considerations have to be made while designing and fabricating silicon devices as they tend to be very sensitive to geometric variations and temperature perturbations because of their high refractive index and high thermo-optic coefficient [22]. Also, since silicon is an indirect band gap material, it requires integration of other materials as sources. For example, several active devices have been demonstrated using III-V based sources and detectors [23] [24] [25].

Silicon dioxide or silica ( $SiO_2$ ) is a very popular material in optical communication as it is used in optical fibres. Silica can be grown on silicon thermally, and it can be used as a mask material, as a structural material or as an optical material. As a masking material, it is commonly used as an etch mask for dry silicon etching. Optically, it can be used either as a core or a cladding material, owing to its refractive index of around 1.46. With the popularity of silicon on insulator (SOI) wafers, it is a very attractive platform for the realisation of a wide range of photonic devices. Doping of silicon and silicon dioxide can be used to alter the properties of the films, allowing for greater flexibility. Through metallisation and dry and wet etching techniques MEMS devices with electrostatic actuation can be fabricated on this platform.

Silicon nitride ( $Si_3N_4$ ) is another material that can be integrated with silicon, as it can be grown relatively easily on silicon and because of its mechanical, elastic and dielectric properties [26] [27]. Hence, it can be often used for fabricating suspended structures. It is also commonly used as an optical material, as waveguides with very low propagation losses have been demonstrated [28]. As with  $SiO_2$  it can be used as a masking material for silicon processing. Reducing film stress is especially important for creating suspended membranes and other structures. Hence nonstoichiometric silicon nitride films ( $Si_xN_y$ ) are deposited through Low Pressure Chemical Vapour Deposition (LPCVD) and Plasma Enhanced Chemical Vapour Deposition (PECVD), and this is referred to as low-stress nitride. It is deposited by decreasing the  $NH_3$  :  $SiH_2$  ratio [29], leading to higher levels of Si.

Diamond is attracting interest as an optical material recently [30], because of its low absorption, high refractive index, high thermal conductivity, high density and large Young's modulus [31]. Synthetic diamond can be differentiated by its grain size: single crystal diamond, micro crystalline diamond, and nanocrystalline diamond.

## 2.5 Losses in Waveguides

Waves propagating in waveguides will experience losses as they travel. Attenuation can occur through scattering, absorption or radiation. The power transmitted in a waveguide is  $P_z$  at point "z" on the waveguide, and it can be calculated by:

$$P_z = P_0 e^{-\alpha z},\tag{2.22}$$

where  $P_0$  is the initial power, and  $\alpha$  is the attenuation coefficient. The loss is also often described in decibels.

$$\alpha_{dB} = -10\log\left(\frac{P_z}{P_0}\right)/L \approx 4.343\alpha.$$

(2.23)

## 2.5.1 Scattering Losses

Scattering in waveguides primarily occurs due to roughness on the surface of the waveguide structure. This is known as interface scattering. However, scattering also can occur due to imperfections in the waveguide material like impurities, crystalline defects and grain boundaries, and this is called volume scattering. This is a function of the number and size of defects in the bulk material, and can be ignored in materials like silicon, but it can lead to significant losses in novel materials like nanocrystalline diamond.

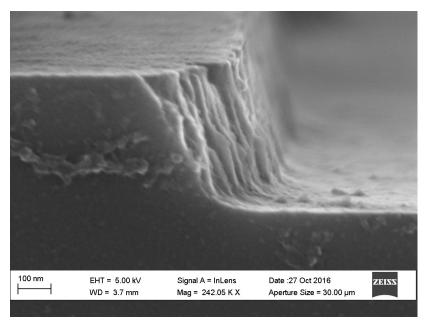

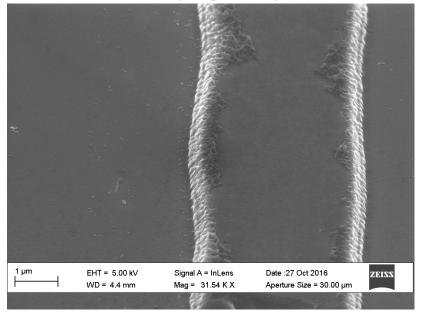

The interface scattering is usually a main contributor to the propagation loss in a waveguide, especially in higher order modes. This can be reduced through improvements to the fabrication process, though it cannot be completely eliminated. As the mode interaction with the sidewalls is significant in quasi-TE modes, reduction in sidewall roughness becomes very important. The influence of sidewall roughness and waveguide dimensions on propagation loss has been established [17] [32]. Therefore, the lithography and etching steps of the process have to be carefully designed to ensure smooth and vertical sidewalls. The use of electron beam lithography helps in defining the waveguide patterns in the resist more precisely, leading to reduction in imperfections before the etch process. The etch mechanism and the etch chemistry have to be carefully chosen in order to ensure not only smooth and vertical sidewalls, but also increase etch selectivity.

# 2.5.2 Absorption Losses

Absorption is a significant source of losses in dielectric materials, and can be classified into band edge absorption and free carrier absorption. Band edge absorption (also known as interband absorption) occurs when photons with energy greater than the material band gap energy get absorbed, therefore raising the electrons from the valence band to the conduction band. Therefore, waveguide materials must be chosen such that the band edge is lower than the wavelength. For example, silicon cannot be used as a waveguide material for wavelengths shorter than 1.1  $\mu m$ , as silicon is highly absorptive in that region [8]. Band edge absorption is especially strong in direct band gap semiconductors.

Free carrier absorption is the phenomenon which occurs when the energy from the photon is transferred to an electron in the conduction band, or a hole in the valence band. This leads to increase in its energy, and therefore increase in loss. In silicon waveguides, free carrier density is often changed in order to affect its refractive index.

## 2.5.3 Radiation Losses

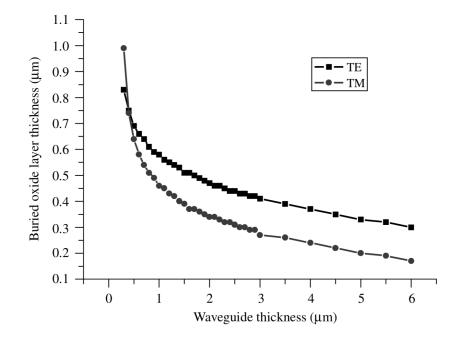

Radiation is another source of losses in optical waveguides, caused by modal energy lost to the surrounding material. This type of loss is generally negligible in straight, non-leaky waveguides, operating far from the cut-off region. In multi-mode waveguides, it is possible for energy to be coupled between propagation modes [33]. This leads to increased losses, as higher order modes tend to have higher radiation losses. In devices fabricated on the SOI platform, it is important that the buried oxide layer is thick enough to ensure that the mode does not leak into the silicon handle layer (Figure 2.7). This thickness depends on the wavelength being used as well as the waveguide dimensions, as smaller core dimensions lead to a greater fraction of the mode propagating in the cladding region. Figure 2.7 shows the minimum buried oxide thickness required to reduce radiation losses.

Fig. 2.7 Buried oxide layer thickness vs slab waveguide thickness to achieve less than 0.001 dB/cm loss at 1550 nm [8]. The various data points have been connected to provide a guide to the eye.

Another reason for radiation losses is because of turns or bends in the waveguide structures. In a bend, the wave has to propagate a longer distance on the outside compared to the inside, implying that velocity must be higher on the outside. This indicates that the refractive index on the outside of the bend is greater, attracting the mode towards it, and power starts leaking away from the core. Therefore, the bend radii must be designed to avoid this type of loss.

# 2.6 Dispersion

Generally, pulses are used in optical communication, and these pulses have a finite duration and can contain different frequencies making up the pulse. Dispersion refers to the phenomenon where different parts of the propagating wave travel at different velocities, and thus experience a spreading effect known as pulse broadening.

Dispersion in waveguides can be classified into the following categories:

1. Material Dispersion: It is important to discuss two quantities known as phase velocity and group velocity before material dispersion is defined. The phase velocity  $(V_{ph})$  is the velocity with which phase fronts propagate in the material, and can be related to the wavenumber (k) and the angular frequency  $(\omega)$  as [34]:

$$V_{ph} = \frac{\omega}{k}.$$

(2.24)

The group velocity in a medium is mathematically defined as the inverse of the derivative of the wavenumber with respect to the angular frequency [35]:

$$V_g = \left(\frac{\partial k}{\partial \omega}\right)^{-1} = \frac{c}{n_g(\omega)},\tag{2.25}$$

where  $n(\omega)$  is the refractive index, and the term group index  $(n_g)$  can be defined as

$$n_g = n(\omega) + \omega \frac{\partial n}{\partial \omega}.$$

(2.26)

Material dispersion occurs due to the wavelength dependence of the phase velocity and the group velocity in a given medium. The refractive index of a material is dependent on the wavelength, and this phenomenon is due to material dispersion.

- 2. Waveguide Dispersion: Since the propagation constant ( $\beta$ ) of the waveguide is a function of the wavelength, the phase velocity also changes with the wavelength. This leads to waveguide dispersion.

- 3. Intermodal Dispersion: Intermodal dispersion takes place in multimode waveguides as different modes travel with different velocities, with the lower order modes travelling at higher velocities. This can be overcome by designing the waveguides to operate in a single mode condition.

- 4. Birefringence: Birefringence describes the effect in which different polarisations in a material or structure travel at different velocities, i.e. possess different refractive indices.

Waveguides that have been designed to reduce birefringence have been demonstrated [36].

# 2.7 Numerical Methods

Analytical methods can be used to provide solutions for devices that have simple configurations, such as metallic waveguides. However, they cannot be used in the case of 2D dielectric waveguides, as they tend to be inaccurate. Historically "trial and error" methods have been used for this application. This has been primarily replaced by numerical methods, with the advent of fast computers. Numerical methods are generally solved through partial differential equations or integral equations, and though they usually provide approximate solutions, they are accurate enough for engineering needs [9]. The most commonly used numerical techniques are:

• Finite element method: This technique involves the solution of partial differential equations and was developed in the mid-20th century to be used in the field of structural engineering [37] [38]. Basically, it divides the domain into smaller and simpler elements, and solves the equations in these elements.

This method provides the solutions through four steps:

- Forming the elements

- Approximating the field values to be constant inside the element, and defining the necessary equations

- Assembling the elements of the domain

- Solving the equations

The main advantage of using the finite element method, is that the elements can be irregularly shaped and arranged, as opposed to the finite difference method which generally requires the elements to be arranged in grids.

• Finite difference method: The finite difference method is a numerical method which provides solutions for problems that are defined by a partial differential equation in a domain with boundary and/or initial conditions. The domain is initially divided into a grid of nodes. Then, the partial differential equations are approximated on the grid nodes through difference equations, and finally these equations are solved.

Finite Difference Time Domain (FDTD) is a technique developed by Kane Yee [39], and it approximates the equations in a grid in the time and spatial domains. FDTD divides the region into cubes known as "Yee Cells", in which the edges represent the electric fields, and the faces represent the magnetic fields. In this way, the field values of one are used to calculate the values for the next cell. FDTD is widely used because of its ease of use, and the various scripts available freely. However, it can be challenging to mesh irregular or curved surfaces, which increases the complexity.

- Method of moments: This technique solves the Maxwell's equations in their integral form by dividing the domain into equal elements. The values are evaluated inside the elements, and the overall system is the weighted sum of the individual elements.

- Eigenmode expansion method: The eigenmode expansion method provides solutions by dividing the device cross-section into a number of layers, and decomposing the fields in each layer into local eigenmodes [40]. Since the layers are divided in a single axis, the number of elements is far lesser than finite difference or finite element methods, therefore reducing the computation time greatly. Since this technique assumes that the structure is infinite in each layer, complex structures cannot be designed accurately.

# 2.8 Coupling

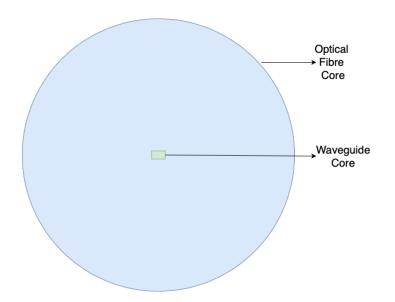

Apart from photonic circuits that have an internally integrated source and photodetector, light needs to be coupled in and out of the circuit. The light is carried via optical fibres (in a Gaussian-like mode), and this needs to be injected into and out of the chip. This leads to a major problem, as the optical fibres are much larger than the designed waveguide

dimensions; the standard mode size of telecommunication fibres is 10.4  $\mu m$  at 1550 nm, while waveguide dimensions are usually submicron. This problem is illustrated in Figure 2.8. If interfaced directly, losses often can be greater than 30 dB [41]. Therefore, an efficient method of power transfer must be used in order to minimize losses. In order to achieve good efficiency, the modes of the fibre and the waveguide must closely match in both the real space (spatial dimension) as well as the k-space (direction and magnitude of the propagation vector). Also, coupling efficiency is bidirectional, i.e the efficiency of coupling from the fibre to the waveguide is the same as from the waveguide to the fibre, assuming that there are no strong non linear effects.

Fig. 2.8 Comparision of optical fibre dimensions and a waveguide core of  $300 \text{ nm} \times 500 \text{ nm}$ .

Most of the commonly used coupling techniques can be classified into in-plane or out-ofplane coupling.

# 2.8.1 In-plane Couplers

In-plane or edge coupling techniques are usually the simplest and the most widely used methods. One of the edge coupling methods is end-fire coupling, which uses a lens to focus the light into the waveguide edge. Since the fibre field is Gaussian, the intensity distribution at the point r, defined axially is given by,

$$I = I_0 e^{-\frac{r^2}{\sigma^2}},$$

(2.27)

where  $\sigma$  is the 1/e width. To ensure optimal coupling, the lens setup must be adjusted such that the focused mode matches the dimensions of the waveguide as closely as possible.

Fig. 2.9 Inverse taper coupling [32].

Butt-coupling is another form of edge coupling. It is a particularly attractive method, as it offers a very cost effective and simple solution with good coupling efficiency. In order to achieve good efficiency, the mode size of the waveguide must be increased to match the fibre mode. This can be achieved through adiabatic tapers, which involves slowly expanding the mode size by modifying the dimensions of the waveguide core. Nano-inverse tapers can be used to increase the core size to match the fibre mode size in the horizontal direction, providing good coupling efficiency. This can be improved using 3-D tapers, but this increases the fabrication difficulty. Alternatively, inverse tapers provide a good compromise between efficiency and fabrication complexity. This structure consists of a taper which is narrowed adiabatically, and surrounded by a polymer [42] or silicon oxynitride [32] overlayer, which

is designed to match the fibre mode dimensions more closely. As a consequence, the mode is 'squeezed out' of the core and spreads into the overlay material (Figure 2.9).

The coupling efficiency can be calculated through the overlap integral [43]:

$$\eta = \eta_F \frac{\left|\int E_{fibre}(x, y) E^*_{waveguide}(x, y) dS\right|^2}{\int \left|E_{fibre}(x, y)\right|^2 dS \int \left|E_{waveguide}(x, y)\right|^2 dS},$$

(2.28)

where  $\eta_F$  is the transmission coefficient for normal incidence, and  $E_{fibre}$  and  $E_{waveguide}$  are the transverse components of the fibre and waveguide electric fields respectively.

Edge coupling techniques offer numerous reasons for choosing them as the design of choice:

- Broadband operation

- Ease of fabrication

- High coupling efficiency

- Non-sensitivity to polarization

However, there are drawbacks that have to be considered:

- Very sensitive to alignment

- Larger footprint on the chip

- Not compatible with wafer scale fabrication

- Requires additional dicing and/or polishing steps

## 2.8.2 Out-of-plane Couplers

Out-of-plane or grating couplers have been developed to overcome the limitations of in-plane couplers [44]. They offer a flexible device design, and low insertion losses of around 1 dB have been reported [45] [46]. The basic grating structure usually consists of a grid of

uniformly distributed gratings (smaller than the wavelength of the incident light) in the device layer therefore creating modulation in refractive index (Figure 2.10).

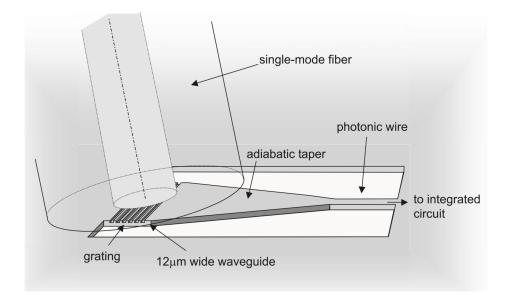

Fig. 2.10 A figure showing the coupling between an optical fibre and a grating coupler [25].

The period between the gratings is designed to aid constructive interference at the required wavelength leading to a coherent phase front, which is known as the Bragg condition. As a result, grating couplers are generally highly wavelength dependent. The Bragg relation is given by [47]:

$$\frac{2 \times n_{clad}}{\lambda} \times \cos(\theta_{out}) = \frac{2 \times n_{eff}}{\lambda} \times \cos(\theta_{in}) + \frac{2 \times q}{\Lambda}, \qquad (2.29)$$

where  $n_{clad}$  is the refractive index of the superstrate,  $\lambda$  is the wavelength,  $\theta_{out}$  is the angle of the tilt of the output light (where  $\theta = 0$  is the direction of waveguide propagation),  $n_{eff}$  is the weighted average of the refractive index in the etched and unetched areas,  $\theta_{in}$  is the angle into the waveguide, q is the order of diffraction and  $\Lambda$  is the grating period.

The above equation describes an infinitely long grating. In reality, every grating scatters a part of the light, and the rest propagates in the waveguide, exponential losing or gaining power depending on if it is an output or input coupler, respectively. For an air clad fibre coupling setup, the period for second order diffraction is given by:

$$\Lambda = \frac{\lambda}{n_{eff} - sin(\theta_{out})}.$$

(2.30)

# 2.9 Summary and Perspective

The fundamentals of electromagnetic wave theory along with design considerations required for the study were detailed in this chapter. The basic theory behind wave propagation has been described along with the commonly used waveguide configurations along with material choices for devices and coupling. Effects that govern the design of optical structures such as losses and dispersion have also been outlined. The concepts introduced in this chapter provide the essential background necessary for designing photonic devices, such as the waveguides in Chapter 5. Also, understanding factors that increase losses such as surface roughness help in formulating the recipes developed in Chapter 4. In the next chapter, the basic techniques necessary for the fabrication of nanophotonic structures have been described.

# Chapter 3

# Fabrication

# 3.1 Introduction

The fabrication of nanophotonic devices involves the use of processes such as lithography, etching and material deposition. An overview of these fabrication techniques have been detailed in this chapter along with their advantages and disadvantages. Most of the processes described are fairly commonly used in modern device fabrication.

# 3.2 Sample Preparation

The surface of the samples must be prepared for the fabrication steps, to reduce device failure rates. The main step in the surface preparation process is the cleaning of contaminants. The most common contaminants are atmospheric dust, particles because of dicing or cleaving, polymer residue from etching, photoresist residue, and oil or solvent residue. The commonly used process is the standard degrease which consists of:

- 5 minutes soak in methanol (with ultrasonic agitation)

- 5 minutes soak in acetone (with ultrasonic agitation)

- 2 to 5 minutes soak in isopropanol (with ultrasonic agitation)

- 2 minutes rinse in flowing de-ionised (DI) water

- $N_2$  blow dry

A quick dip (around 30 seconds) in hydrofluoric acid is also performed if a thin film of silicon dioxide has been formed. This process can be used in conjunction with an  $O_2$  dry plasma etch for a duration of 5 to 10 minutes. This is also known as "ashing" and helps in removing polymer and photoresist residue that might be left over. The organic impurities that might be present are removed in the degrease process where the acetone removes the impurities and the isopropanol removes the contaminated acetone.

Other cleaning processes like RCA and piranha etch are used in different situations. The RCA cleaning process is a series of steps consisting of general cleaning, particle removal, oxide removal, metal contamination removal, and finally drying of the substrate. Improper cleaning can lead to problems during oxidation, photolithography or deposition processes leading to yield loss. It can also lead to adhesion problems, which leads to the photoresist peeling from the substrate. The clean substrates are baked at above 150  $^{0}C$  for at least 5 minutes to assist in the desorption of  $H_2O$ . This is known as the dehydration bake, and immediately following this, adhesion promoters can be used. On silicon substrates, these materials form bonds with the surface and produce a polar association to the photoresist. A commonly used adhesion promoter is hexamethyldisilazine ( $(CH_3)_3SiNHSi(CH_3)_3$ ) or HMDS.

# **3.3** Photolithography

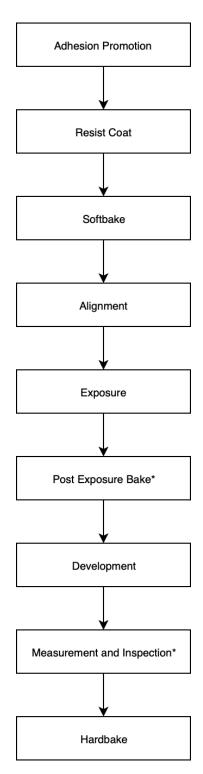

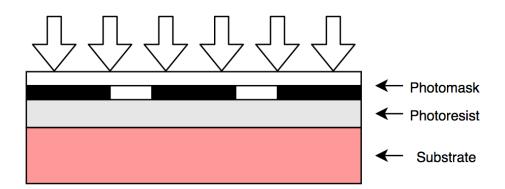

Photolithography is a process used to define patterns on to the substrate (illustrated in Figure 3.1). It is an indirect method of pattern transfer, and therefore the pattern needs to be initially transferred to an intermediate material (photoresist) and then transferred to the substrate through other methods. It uses Ultra Violet (UV) light to illuminate the photoresist (which is photo-sensitive) through a photomask consisting of the required pattern. The photomask is

Fig. 3.1 Steps in the photolithography process. The steps marked with asterisks are optional.

usually constructed using a quartz plate patterned using chromium. A few factors have to be considered during the design of the photomask.

- The minimum feature size should be larger than the tool and photoresist capability.

- Designs should account for user and process error.

- The photomask layout should account for tool limitations (such as range of motion of the objectives, maximum and minimum mask size, layout of vacuum lines etc.)

- The substrate material, crystalline orientation and the size of the edge bead must be considered.

- Process limitations such as non uniform etch rates, loading effects and critical dimensions should be considered.

The absorption spectrum of photoresists is designed to match the emission spectrum of the lamp used. The exposure does depend on different factors like resist type, resist thickness, substrate material, etc. Optical lithography can be broadly classified into contact lithography, proximity lithography and projection lithography.

# **3.3.1** Contact Lithography

Contact lithography is a process which uses a tool known as a mask aligner which is used to align and expose the samples (Figure 3.2). It uses a mask consisting of the pattern that needs to be transferred. The tool can be generally be used in two contact modes (hard contact and soft contact) or proximity mode. In the hard contact mode, the sample and the mask are brought together with force, which ensures that the mask and wafers are as close together as possible. Therefore, this method achieves the best resolution. The main drawback of this method is its sensitivity to resist edge beads and the degradation of the photomask. It can also cause cracking of the resist, if the film is brittle. The soft contact mode can overcome some of these drawbacks as this mode brings the sample and the mask together, but without excessive force. However, the compromise is lower resolution compared to the hard contact mode. In the proximity mode, the substrate is not in contact with the mask during exposure (Figure 3.3). This is the preferred method of operation when the feature sizes are large or if the resolution is not very important. Contact aligners provide alignment capabilities where the mask and the substrate can be aligned through the use of alignment marks. After the alignment, the mask and substrate are illuminated with light ranging from extreme UV (10-124 nm) to near UV (350-440 nm). Typically, a Hg lamp source is used as the source, and it consists of the g,h and i lines. The energy dose in  $J/cm^2$  is calculated by multiplying the lamp intensity in  $W/cm^2$  with the exposure time in seconds. Generally, contact lithography is not capable of very high resolution , but is the process of choice for processing thicker film resists. It is also favoured in experimental setups as it is relatively cost effective.

Fig. 3.2 A schematic of the contact lithography process.

## **3.3.2 Projection Lithography**

In projection based lithography systems, a lens is used to focus the pattern of the photomask onto the substrate, and therefore contact between the mask and the substrate does not take place (Figure 3.4). They are popular for use in wafer scale fabrication techniques. There are different types of projection based systems developed including projection scanners, stepper systems (1:1, 5:1 or 10:1), step and scan systems and double sided mask aligners

Fig. 3.3 A schematic of the proximity lithography process.

[48]. Steppers are one of most widely used projection lithography systems and they use a reticle to expose a single die at a time. The mask and the projection system then moves to the next die and repeats the exposure. In this way, the entire wafer is covered by a repeating pattern. Steppers using reduction lenses are generally favoured as they offer higher alignment accuracies and improved resolution.

## **3.3.3** Electron Beam Lithography

Electron Beam (or E-Beam) Lithography is a lithography technique which uses a beam of electrons to form the necessary patterns, compared with optical lithography which uses light. Since electrons have very short wavelengths, very high resolutions can be achieved, often in the range of 10 *nm*. This energised beam of electrons (usually between 5 KeV and 100 KeV) generated through a thermionic or field-emission cathode is focused over a resist material, and the resist is made soluble or insoluble depending on the tone of the resist. Since the beam size is small, negative tone resists are often preferred to pattern features like waveguides. Some of the commonly used electron beam resists are poly methyl methacrylate (PMMA), hydrogen silsesquioxane (HSQ), Ma-N 24xx series and ZEP series. E-Beam lithography offers many advantages over conventional optical lithography, principally the extremely

Fig. 3.4 A schematic of the projection lithography process.

small feature sizes that can be defined. It also removes the requirement of physical masks. The dosage and pattern control is also greater than optical lithography. However, certain considerations have to be made before choosing this technique:

- Because of electron scattering, the resolution is limited.

- The process is conducted in vacuum, increasing the complexity.

- This technique is considerably slower than optical lithography.

- Higher setup cost.

- Alignment errors while defining larger patterns.

The thickness of the resist film also plays an important role in the resolution. The electron beam can be broadened in the film because of electron scattering. For electron energy less than 50 KeV and resist thickness more than 0.25  $\mu m$ , the following expression can be used to approximate the beam broadening [49]:

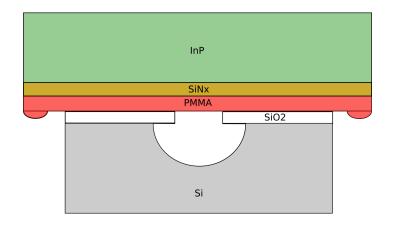

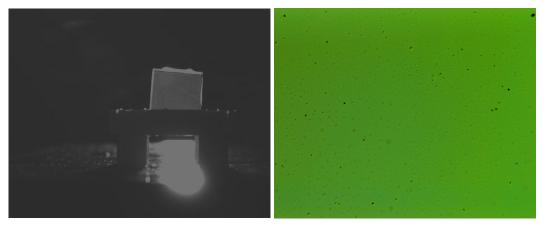

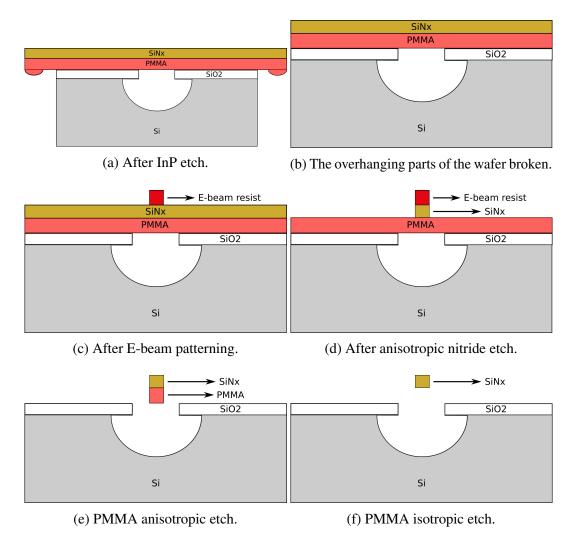

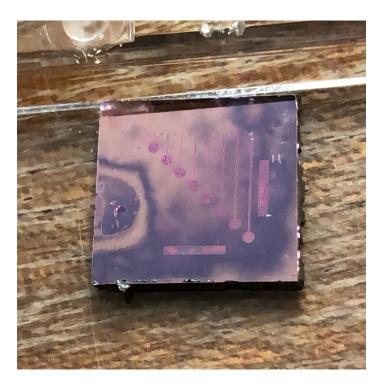

$$\sigma_f = \left(\frac{9.64t}{E}\right)^{1.75},\tag{3.1}$$