### **Bangor University**

### **DOCTOR OF PHILOSOPHY**

### Development of thin film flexible and transparent electronics

Kumar, Dinesh

Award date: 2019

Awarding institution: Bangor **University**

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 16. May. 2022

### **Bangor University**

### **DOCTOR OF PHILOSOPHY**

### Development of thin film flexible and transparent electronics

Kumar, Dinesh

Award date: 2019

Awarding institution: Bangor **University**

Link to publication

General rights

Copyright and moral rights for the publications made accessible in the public portal are retained by the authors and/or other copyright owners and it is a condition of accessing publications that users recognise and abide by the legal requirements associated with these rights.

- Users may download and print one copy of any publication from the public portal for the purpose of private study or research.

You may not further distribute the material or use it for any profit-making activity or commercial gain

You may freely distribute the URL identifying the publication in the public portal?

Take down policy

If you believe that this document breaches copyright please contact us providing details, and we will remove access to the work immediately and investigate your claim.

Download date: 07. Jan. 2020

# DEVELOPMENT OF THIN FILM FLEXIBLE AND TRANSPARENT ELECTRONICS

### **Dinesh Kumar**

## School of Computer Science and Electronic Engineering Bangor University

A thesis submitted in partial fulfilment for the degree of *Doctor of Philosophy*

October 2019

"Life is and will ever remain an equation incapable of solution, but it contains certain known factors."

Nikola Tesla

Abstract

### **ABSTRACT**

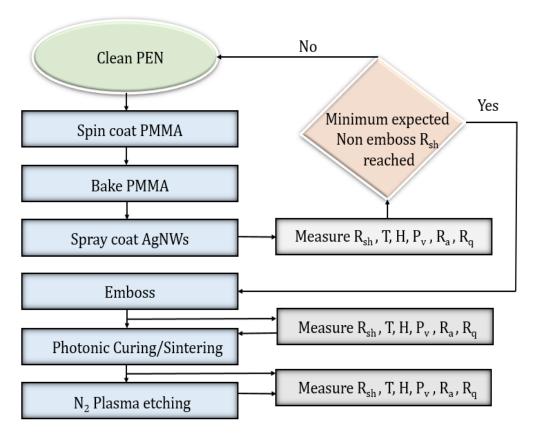

This thesis focuses on the development of transparent and flexible components such as silver nanowire (AgNW) based transparent conducting electrodes (TCEs) and metal oxide thin film transistors (TFTs) with the aim of improving the stability and performance under real-world conditions. The electrical and environmental stability of these components is, therefore, investigated. For AgNWs a 3-step post processing method was used to enhance the electrical, surface properties of AgNWs TCEs. Thermal embossing process parameters were optimised using a Taguchi orthogonal array, where pressure, time and temperature of the embossing step were all varied. An in-depth study of the effect of thermal embossing, effect of N2 plasma treatment and photonic sintering on the AgNW TCE properties was undertaken. X-ray photoelectron spectroscopy, atomic force microscopy and scanning electron microscopy analysis of AgNW TCEs revealed several mechanisms responsible for the reduction of sheet resistance and surface roughness. However, transmittance and haze remained unchanged after post processing of TCEs. Electrical and environmental stability of AgNW TCEs is investigated through accelerated lifetime testing (ALT) and method to enhance stability of AgNW TCEs are developed.

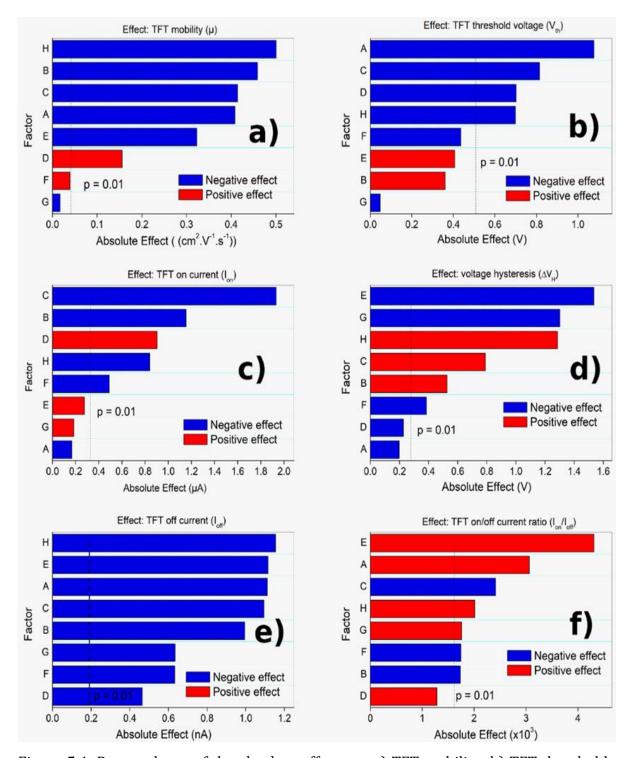

A Plackett-Burman design was applied to optimise the production of anodised ( $Al_2O_3$ ) dielectric films for ZnO thin film transistor (TFTs). A comprehensive study of the effect of the processing parameters on the performance of anodized  $Al_2O_3$  gate dielectric films for ZnO TFTs is conducted. The impact of the process factors on the overall performance of the ZnO TFTs is also investigated. The development of low voltage metal oxide TFTs based upon ZnO and flexible IGZO is reported using  $Al_2O_3$  as the gate dielectric. The performance of transparent IGZO TFTs base on AgNW and ITO gate electrode is also studied.

Understanding the origin of electrical instability in inorganic metal oxide TFTs over long periods is also essential to realize high performance circuits. In this thesis, the effects of positive gate bias stress (PGBS) on IGZO TFTs are also investigated. It was found that the threshold voltage,  $V_T$ , always shifted in the direction of the applied gate voltage. It was also observed that the threshold voltage shift,  $\Delta V_T$ , is reduced with CYTOP passivation and white light illumination. A density of states (DoS) analysis is carried out during PGBS to confirm the origin of trap states due to bias stressing.

Acknowledgements

### **ACKNOWLEDGEMENTS**

First of all, I would like to thank my supervisor, Dr. Jeff Kettle, for giving me this opportunity and for his support and guidance over the last four years. Without his continuous enthusiasm, encouragement, and help this research work would hardly have been completed.

I would like to thank Professor Dr. Lucas Fugikawa Santos of UNESP Rio Claro, SP, Brazil and my colleague Tiago for their support in anodisation work. I would also like to thank Prof. Graham C Smith of the University of Chester for his support analysis of X-ray photoelectron spectroscopy (XPS) of ZnO films, and SEM of AgNW films at Chester University. I would like to thank Dr. Emmanuel Brousseau from Cardiff University for obtaining high resolution SEM images of transparent electrodes.

I also owe thanks to all my colleagues at Bangor University for sharing this journey with me: Noel, Vasil, Tudur, Luke, Eifion, Colin, Nor, Ali, Helder, Ricardo, Paul Sayers, Iwan, Wendy, David, Julie, Siân and Gaynor.

I am in debt to my parents, family; my wife Sunita Devi, my twin kids Rishab Bhatia and Rishit Bhatia, brother Er Sunil Kumar, sisters Anita Kumari and Anjna Kumari, for being there and for believing in me for all these years. I owe my deepest gratitude to Govt. of India for their financial support.

Finally, I would like to thank "God" whose Divine light and warmth provided me the inspiration, faith and strength to carry out the research work. This thesis is dedicated to all of them.

Publications vi

### **PUBLICATIONS**

**1. Dinesh Kumar** and J. Kettle. "IGZO TFT performance investigation using Taguchi Orthogonal arrays." (Under review in Micro & Nano Letters)

- **2. Dinesh Kumar**, T. C. Gomes, N. Alves, L. F. Santos, G. C. Smith and Jeff Kettle "UV phototransistors based upon spray coated and sputter deposited ZnO TFTs" (Under review in IEEE Sensors Journal)

- 3. Dinesh Kumar, V. Stoichkov, E. Brousseau, G. C. Smith and J. Kettle. "High performing silver nanowires transparent conducting electrodes with a sheet resistance of  $2.5 \Omega \, \mathrm{Sq^{-1}}$  based upon a roll-to-roll compatible post-processing technique." *RSC Nanoscale* 11(2019) 5760.

- **4.** T. C. Gomes, **Dinesh Kumar**, L. F. Santos, N. Alves, J. Kettle. "Optimisation of the anodisation processing for aluminium oxide gate dielectrics in ZnO thin film transistors by multivariate analysis." *ACS Comb. Sci.*, 21 (2019) 370–379.

- **5.** V. Stoichkov, **Dinesh Kumar**, P. Tyagi, J. Kettle. "Multi stress testing of OPV modules for accurate predictive ageing and reliability predictions. *IEEE Journal of Photovoltaics* 8 (2018) 1058–1065.

- **6.** J. Kettle, V. Stoichkov, **Dinesh Kumar**, M. Corazza, S. Gevorgyan, F. K. "Using ISOS consensus test protocols for development of quantitative life test models in ageing of organic solar cells." *Sol. Energy Mater. Sol. Cells* 167 (2017) 53–59.

- **7. Dinesh Kumar**, V. Stoichkov, S. Ghosh, G. Smith, J. K. "Mixed-dimension silver nanowires for solution-processed, flexible, transparent and conducting electrodes with improved optical and physical properties. *Flex. Print. Electron.* 2 (2017) 15005.

#### PATENT APPLICATION

**Dinesh Kumar**, V. Stoichkov and J. Kettle, "Method for producing transparent conductor" UK patent application, No. 1706606.9 (GB)

### **BOOK CHAPTER PUBLISHED**

**Dinesh Kumar** and Jeff Kettle. Chapter: High performing metal-oxide semiconductor thin film transistors (**DOI**: 10.1049/PBCS073F ch12). Book Name: VLSI and Post-CMOS Devices, Circuits and Modelling. **Publisher: Institution of Engineering and Technology**, Publication City/Country Stevenage, United Kingdom.

Conferences vii

### **CONFERENCES**

Dinesh Kumar, Aly Abdou, Jeff Kettle. Half-volt IGZO flexible thin-film transistors with E-beam deposited Al<sub>2</sub>O<sub>3</sub> gate dielectric. First edition of the IEEE International Conference on Flexible and Printable Sensors and Systems - FLEPS 2019. (Oral presentation- paper published in IEEE explore digital library)

- 2. Jeff Kettle and **Dinesh Kumar**. Enhancing the stability of AgNW transparent conducting electrodes with 2.5Ω-Sq sheet resistance by the use of post-processing. First edition of the **IEEE International Conference on Flexible and Printable Sensors and Systems FLEPS** 2019 (Oral presentation- paper published in IEEE explore digital library)

- 3. Dinesh Kumar and Jeff Kettle. High performing AgNW transparent conducting electrodes with a sheet resistance of 2.5  $\Omega$  Sq-1 based upon a roll-to-roll compatible post-processing technique. Fifth Innovation in Large-Area Electronics Conference (innoLAE 2019) at Genome Campus Conference Centre in Cambridge, United Kingdom. (Oral presentation)

- **4. Dinesh Kumar** and Jeff Kettle. Control over voltage threshold shift in IGZO TFTs with enhanced electrical characteristics using novel passivation. **Fifth Innovation in Large-Area Electronics Conference (innoLAE 2019)** at Genome Campus Conference Centre in Cambridge, United Kingdom. (Poster presentation)

- 5. Dinesh Kumar, Tiago Gomes, Neri Alves, Jeff Kettle. Understanding UV Sensor Performance in ZnO TFTs through the Application of Multivariate Analysis. International Conference: IEEE SENSORS 2018 held at Delhi, India during 28-31 October 2018. (paper published in IEEE explore digital library)

- **6. D. Kumar**, V. Stoichkov, S. Ghosh, G.C. Smith, J. Kettle. Mixed dimensions silver nanowires thin, flexible, transparent and conducting electrodes with improved optical and physical properties. **International Conference: PVSAT-13** held at Bangor University, UK during 5-7 **April 2017**. (poster presentation)

- 7. Jeff Kettle, Vasil Stoichkov, Dinesh Kumar. Accelerated testing for predictive ageing in organic solar cells for outdoor applications. Third Innovation in Large-Area Electronics Conference (innoLAE 2017) at Genome Campus Conference Centre in Cambridge, United Kingdom. (Oral presentation)

- **8. D. Kumar,** V. Stoichkov, S. Ghosh, G.C. Smith, J. Kettle. Spray coated silver nanowire electrodes as a transparent electrode in OPVs. **Innovation in Large-Area Electronics Conference** (innoLAE 2016) at Genome Campus Conference Centre in Cambridge, United Kingdom. (poster presentation)

Contents

### **CONTENTS**

| Declaration and Consent                                      | i    |

|--------------------------------------------------------------|------|

| Abstract                                                     | iv   |

| Acknowledgements                                             | v    |

| Publications                                                 | vi   |

| Conferences                                                  | vii  |

| Contents                                                     | viii |

| Chapter 1. Introduction                                      | 1    |

| 1.1 Highlights and Structure of this Thesis                  | 3    |

| Chapter 2. Literature Review of Transparent Electronics      | 5    |

| 2.1 Review of Transparent and Flexible Electronics           | 5    |

| 2.1.1 Review of State-of-the-Art in Transparent Electrode    | s7   |

| 2.2 Review of Properties of Transparent Conductive Electrode | es8  |

| 2.2.1 Sheet Resistance (R <sub>sh</sub> )                    | 8    |

| 2.2.2 Transmittance (T)                                      | 10   |

| 2.2.3 Figure of Merit (FoM)                                  | 11   |

| 2.2.4 Mechanical Flexibility                                 | 11   |

| 2.3 Post Processing Treatment                                | 12   |

| 2.4 Physical and Chemical Deposition Techniques              | 14   |

| 2.5 Review of Thin Film Transistors and Circuits             | 14   |

| 2.6 Materials for Transparent and Flexible TFTs              | 17   |

| 2.6.1 Transparent and Flexible Substrates                    | 17   |

| 2.6.2 Dielectric Layers                                      | 18   |

| 2.6.3 Metal oxide semiconductors                             | 20   |

|    | 2.7 Device Structures of TFTs                                           | 22                         |

|----|-------------------------------------------------------------------------|----------------------------|

|    | 2.8 Operation Principles of TFTs                                        | 23                         |

|    | 2.9 Extraction of Performance Parameters of TFTs                        | 27                         |

|    | 2.10 State-of-the-Art Performance in Metal Oxide TFTs                   | 28                         |

|    | 2.11 Process Optimization Techniques                                    | 29                         |

|    | 2.11.1 Taguchi Orthogonal Arrays                                        | 29                         |

|    | 2.11.2 Properties of Orthogonal Arrays                                  | 31                         |

|    | 2.11.3 Assumptions of the Taguchi Method                                | 32                         |

|    | 2.11.4 Plackett-Burman Design                                           | 33                         |

|    | 2.12 Accelerated Lifetime Testing                                       | 34                         |

|    | 2.12.1 Quantitative Accelerated Life Tests (QALT)                       | 34                         |

|    | 2.13 Electrical and Environmental effects in AgNW Films                 | 35                         |

|    | 2.14 Summary                                                            | 35                         |

| Ch | apter 3. Experimental Methods Used for Fabrication and Characterization | 37                         |

|    | 3.1 AgNWs solution Preparation                                          | 37                         |

|    | 3.1.1 Materials and AgNW Solution Preparation                           | 37                         |

|    |                                                                         |                            |

|    | 3.1.2 Fabrication Steps of AgNW Electrodes                              | 39                         |

|    | 3.1.2 Fabrication Steps of AgNW Electrodes                              |                            |

|    |                                                                         | 39                         |

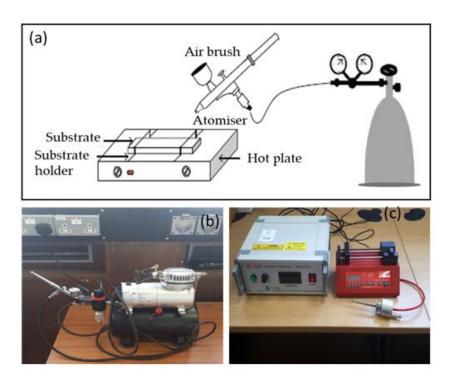

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39<br>40                   |

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39<br>40<br>40             |

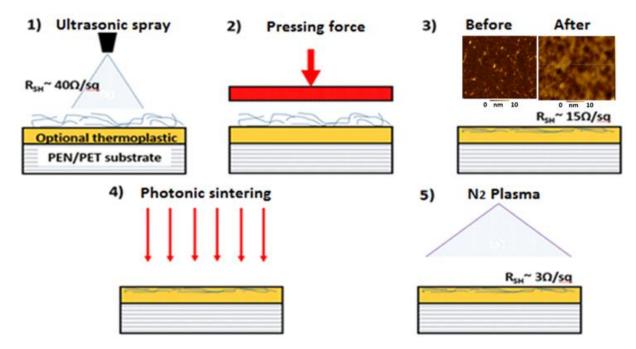

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39<br>40<br>40<br>42       |

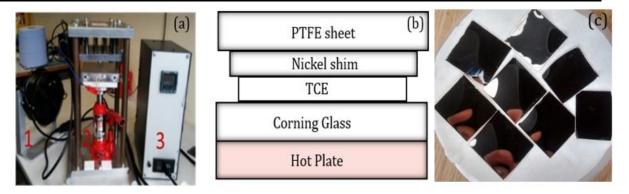

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39<br>40<br>40<br>42<br>44 |

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39 40 40 42 44 44          |

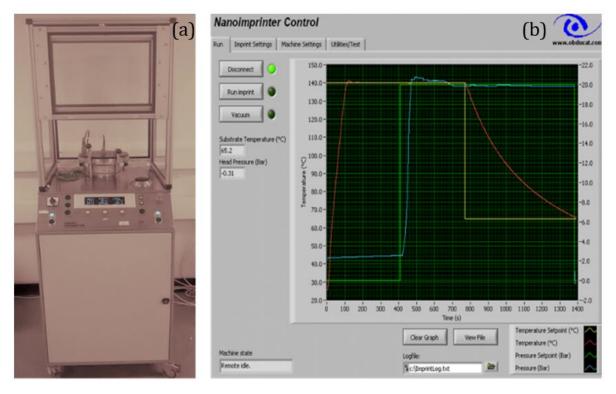

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39 40 42 44 44             |

|    | 3.1.3 Experimental Setup for Spray Coating AgNWs                        | 39 40 40 42 44 44 44       |

| 3.3.5 Lift-Off Process                                                      | 48        |

|-----------------------------------------------------------------------------|-----------|

| 3.4 Characterization of TCEs and TFTs                                       | 48        |

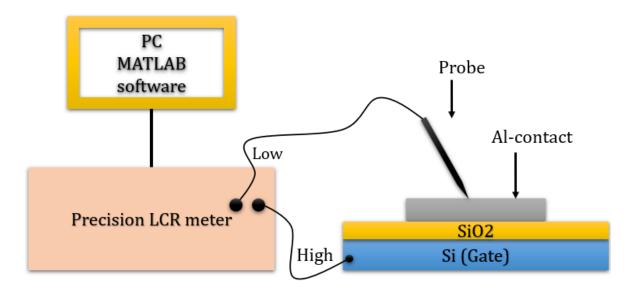

| 3.4.1 TFT CV/Cf and MIM Capacitance Characterization                        | 48        |

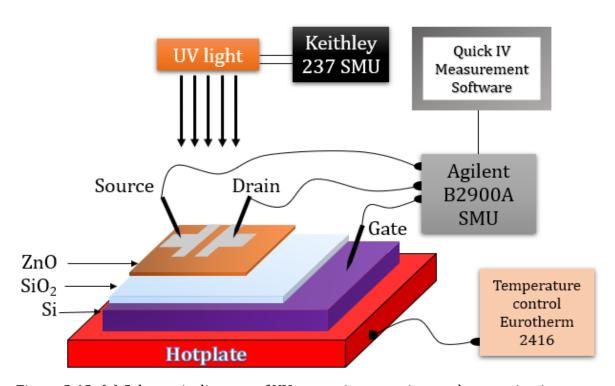

| 3.4.2 UV Saturation Experiment Setup                                        | 49        |

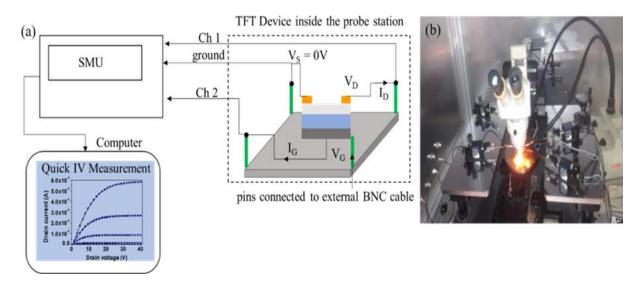

| 3.4.3 TFT Current Voltage (IV) Characterization                             | 49        |

| 3.4.4 IV Characterization and Accelerated Lifetime Testing (ALT) of Agl     | NW TCEs   |

|                                                                             | 50        |

| 3.4.5 Setup for Sheet Resistance Measurement of AgNW TCEs                   | 52        |

| 3.4.6 Atomic Force Microscopy                                               | 52        |

| 3.4.7 Scanning Electron Microscopy                                          | 53        |

| 3.4.8 Optical Characterization                                              | 53        |

| 3.4.9 White light interferometry (WLI) and haze measurements                | 53        |

| 3.4.10 Bias Stress Characterization                                         | 54        |

| 3.5 Extraction of the Density of Trap State Using the Grünewald Model       | 55        |

| Chapter 4. Application of Thermal Embossing to Enhance the Properties       | s of      |

| AgNW TCEs                                                                   | 57        |

| 4.1 Initial AgNW TCE Fabrication and Optimisation                           | 57        |

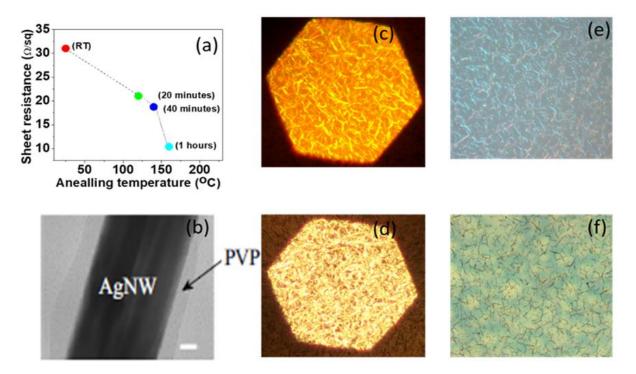

| 4.2 Effect of Thermal Embossing on AgNW TCEs Properties                     | 58        |

| 4.3 Taguchi Orthogonal Array Optimisation before and after Thermal Embo     | ssing     |

| Process                                                                     | 60        |

| 4.4 Effect of Photonic Curing and N <sub>2</sub> Plasma on AgNW TCEs        | 62        |

| 4.5 Effect of Post Processing on Electrical and Optical Performance of AgNW | / TCEs 63 |

| 4.6 Surface Topographic Properties                                          | 64        |

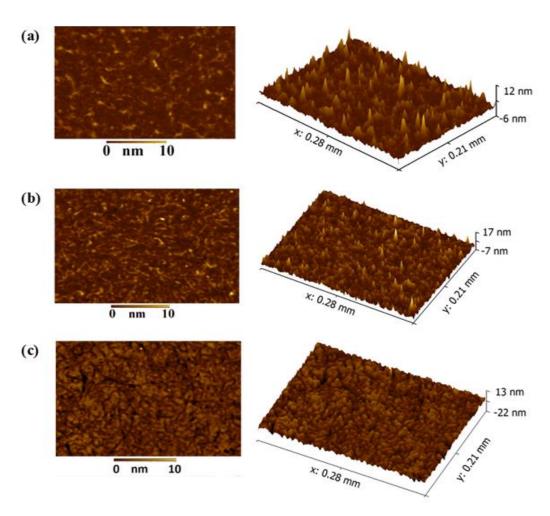

| 4.6.1 Surface Topographic Properties Before and After Post Processing       | 64        |

| 4.6.2 Application of Zinc Oxide Nanoparticles to Further Improve Surfa      |           |

| Properties                                                                  | 66        |

| 4.6.3 Demonstration of OPV Device                                           | 68        |

| 4.7 Mixed AgNW TCEs                                                                    | 70          |

|----------------------------------------------------------------------------------------|-------------|

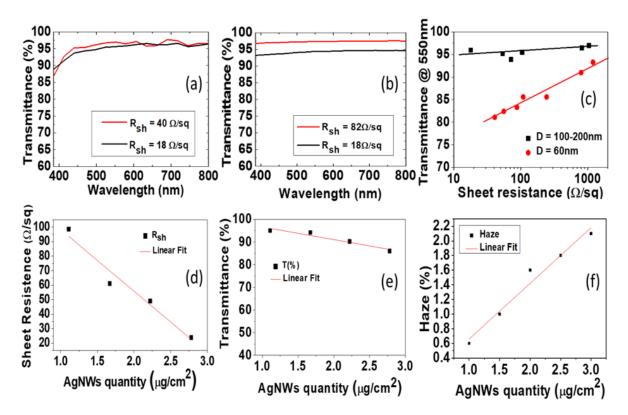

| 4.7.1 Optical and Electrical Properties                                                | 72          |

| 4.7.2 Surface Roughness                                                                | 74          |

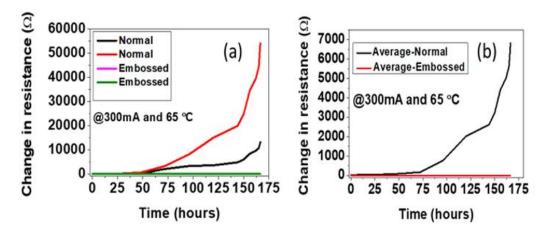

| 4.8 Effect of Post Processing on Stability of AgNW Films                               | 76          |

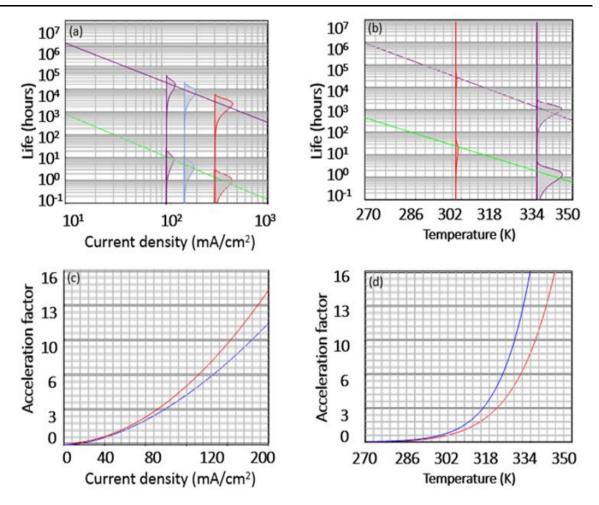

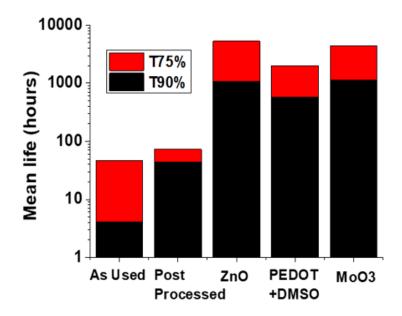

| 4.9 QALT Testing of the Reliability of AgNW Films                                      | 77          |

| 4.10 Adhesion and Mechanical Testing                                                   | 80          |

| 4.11 XPS Analysis of the AgNW Films                                                    | 81          |

| 4.12 Summary                                                                           | 83          |

| Chapter 5. Development of ZnO TFTs Using Design of Experiments (1                      | DOE)        |

| Techniques                                                                             | 84          |

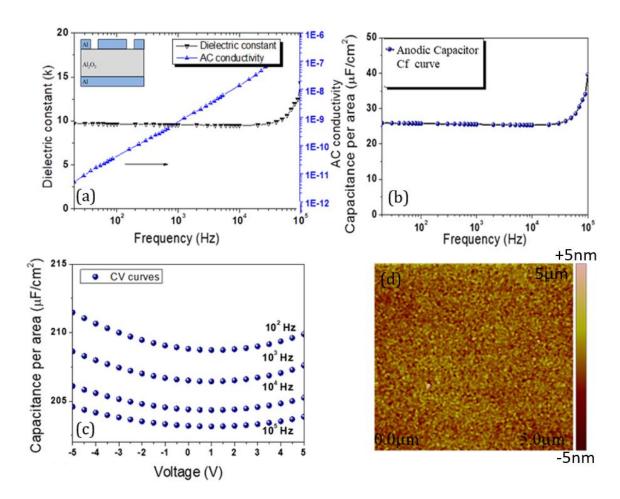

| 5.1 Development of High-k Dielectric (Al <sub>2</sub> O <sub>3</sub> )                 | 85          |

| 5.2 Optimisation of Anodic Al <sub>2</sub> O <sub>3</sub> using Plackett-Burman Design | 87          |

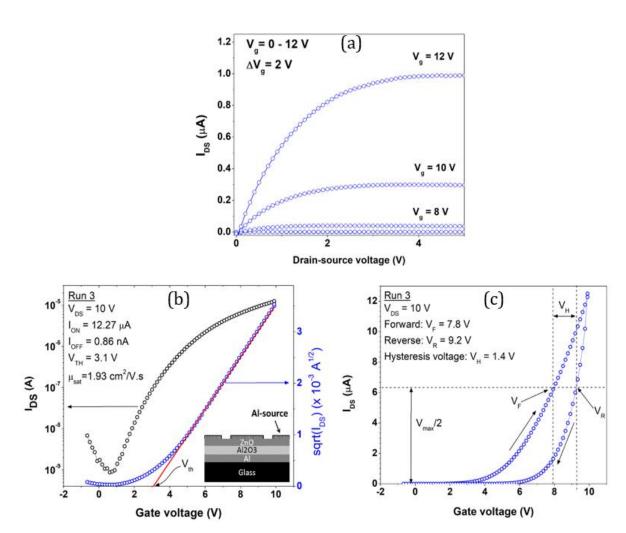

| $5.3\ ZnO\ TFT$ using anodic $Al_2O_3$ as the gate dielectric                          | 89          |

| 5.4 Influence of the Dielectric Layer Fabrication Factors on the ZnO TFT               | rs .        |

| Characteristics                                                                        | 91          |

| 5.5 ZnO TFT Overall Performance                                                        | 98          |

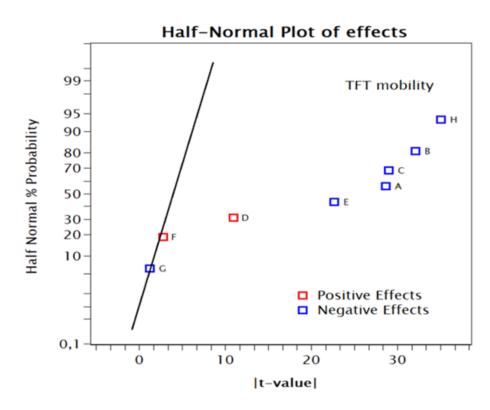

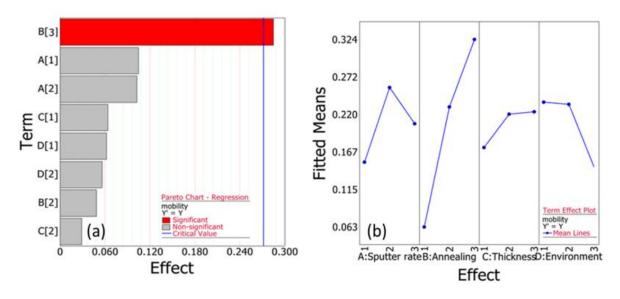

| 5.6 Optimisation of Sputter Coated ZnO TFTs using Taguchi OA                           | 100         |

| 5.6.1 Pareto Chart and Term Effects for Mobility                                       | 101         |

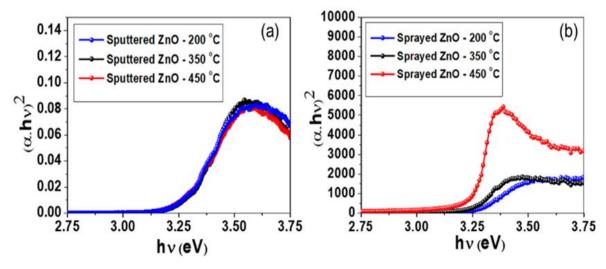

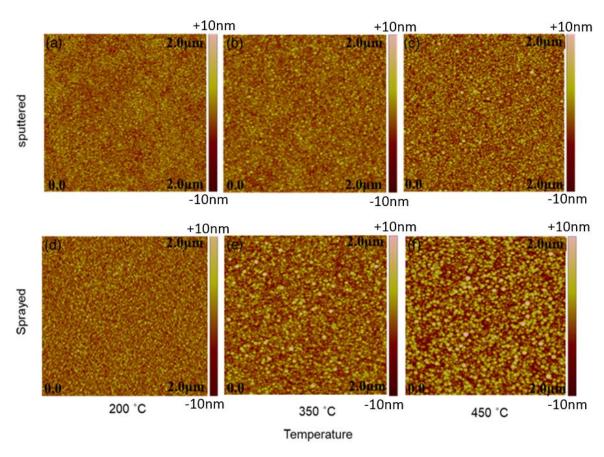

| 5.7 Comparison of Sprayed and Sputtered ZnO TFTS                                       | 103         |

| 5.7.1 Optical Spectroscopy of ZnO Films                                                | 103         |

| 5.7.2 Atomic Force Microscopy of ZnO Films                                             | 104         |

| 5.7.3 X-Ray Diffraction of ZnO Films                                                   | 105         |

| 5.7.4 XPS Analysis of the ZnO Films                                                    | 107         |

| 5.7.5 Surface Chemistry                                                                | 109         |

| 5.8 Electrical Characterization of ZnO Thin-Film Transistors Fabricated                | using Spray |

| and Sputter Deposition                                                                 | 112         |

| 5.9 UV Saturation Experiment                                                           | 115         |

| 5.10 Sumn   | nary119                                                                 |

|-------------|-------------------------------------------------------------------------|

| Chapter 6.  | Effect of Bias Stressing on Indium Gallium Zinc Oxide TFTs and          |

| Flexible TF | Ts121                                                                   |

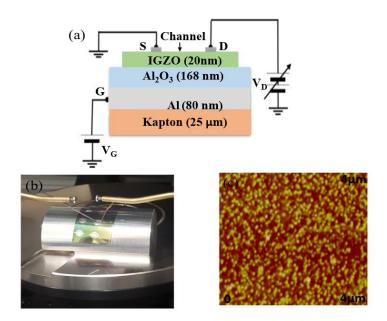

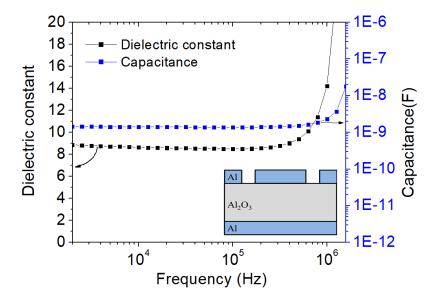

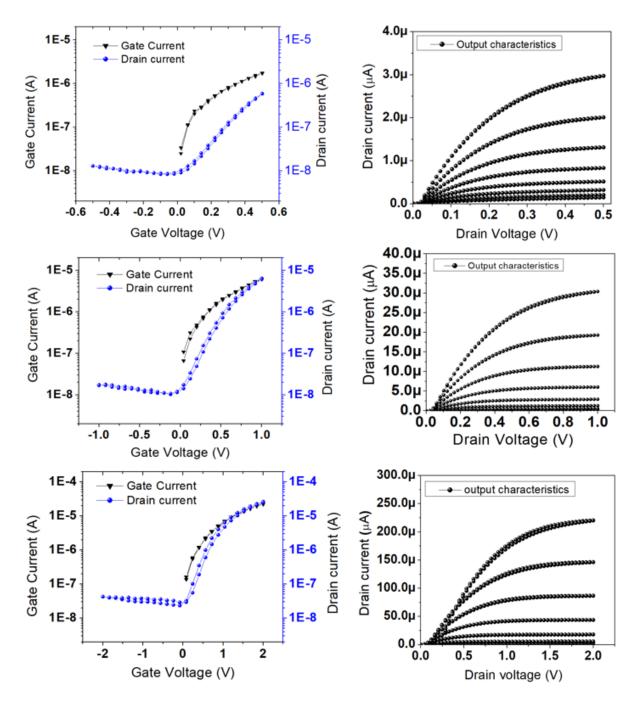

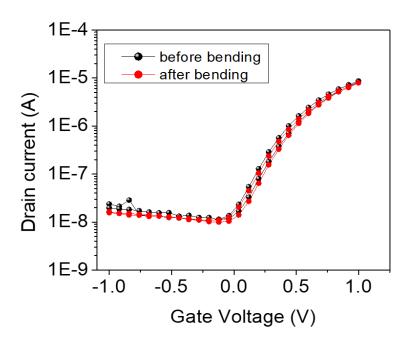

| 6.1 Experi  | mental details122                                                       |

| 6.2 Effect  | of CYTOP Passivation on Performance of IGZO TFTs123                     |

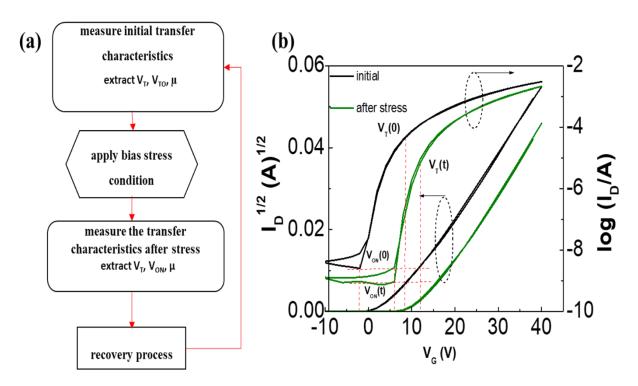

| 6.3 Bias St | ressing of IGZO TFTs123                                                 |

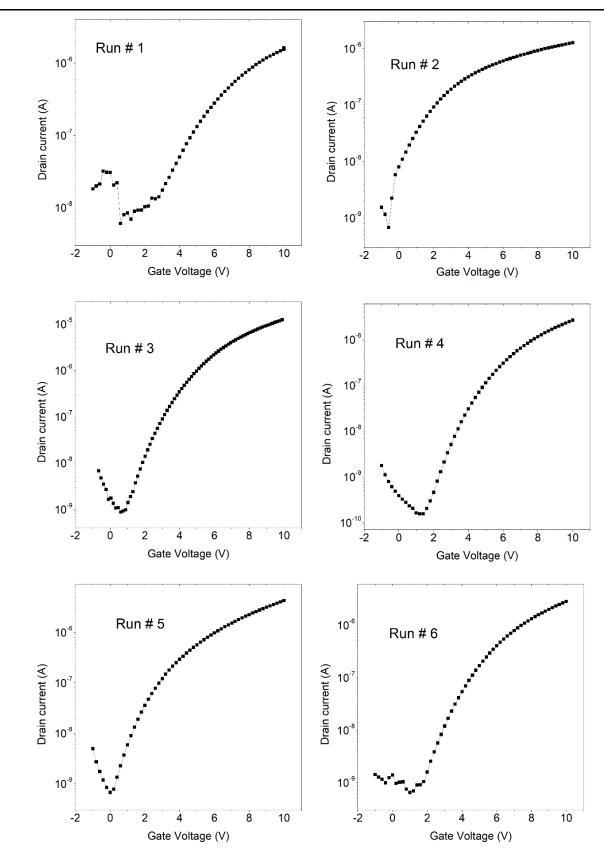

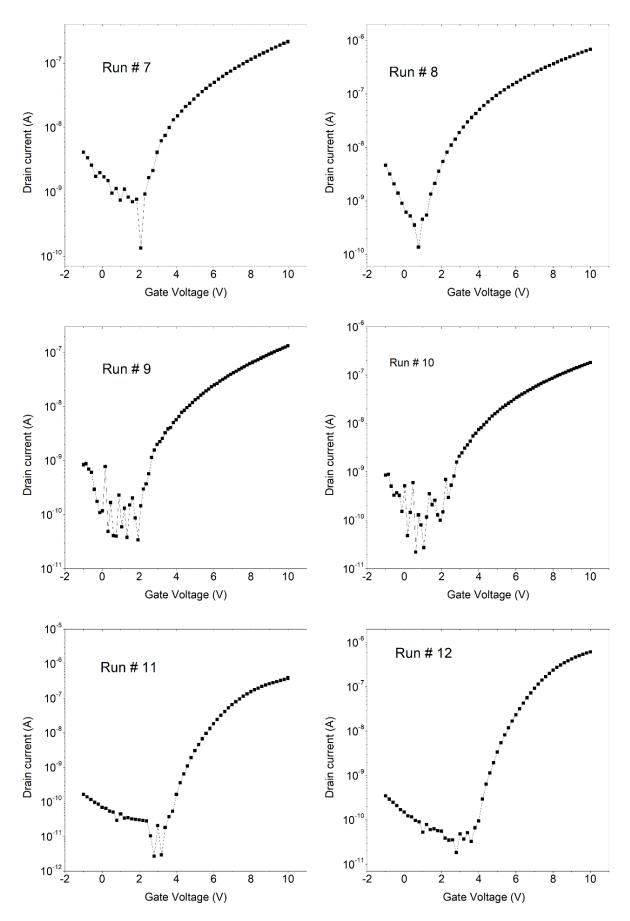

| 6.3.1 (     | Comparison of Unpassivated Positive Gate Bias Stress124                 |

| 6.4 Recove  | ery Procedure127                                                        |

| 6.5 Effect  | of CYTOP Passivation, White light (WL) and Positive Gate Bias stress129 |

| 6.6 CV Mea  | asurements Before and After Bias Stressing130                           |

| 6.7 Densit  | y of States (DOS) Analysis131                                           |

| 6.8 Low Vo  | oltage Flexible TFTs134                                                 |

| 6.9 Transp  | parent IGZO TFTs on AgNW and ITO Electrodes139                          |

| 6.10 Sumn   | nary141                                                                 |

| Chapter 7.  | Conclusions and Further Work142                                         |

| 7.1 Conclu  | sions142                                                                |

| 7.2 Future  | Work144                                                                 |

| References  | 149                                                                     |

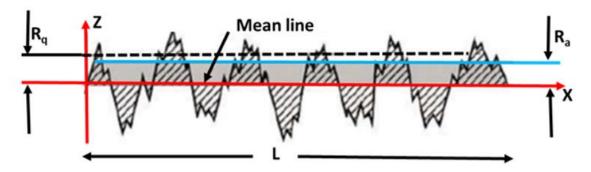

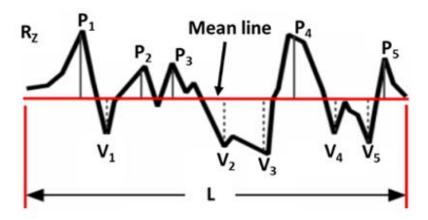

| Appendix A  | Surface Roughness ParametersI                                           |

| Roughnes    | sI                                                                      |

| Appendix B  | Fabrication recipe of AgNWs TCEsIII                                     |

| Appendix C  | Aluminum Anodization Process and Transfer CurvesVI                      |

### **Chapter 1. Introduction**

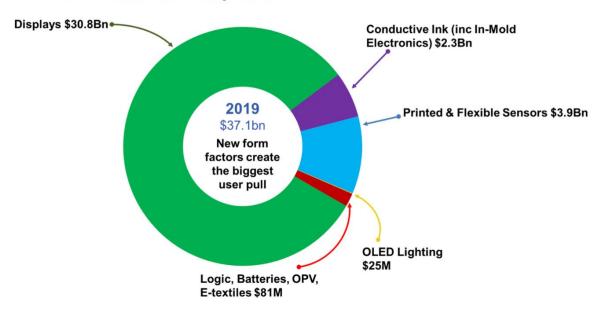

There has been significant research to realise the high performance of transparent and flexible electronics. Market demand for high-performance electronics has also increased because of new emerging applications. It is now estimated that the market for flexible electronics will reach \$300 billion by 2028, with growth from \$29.28 billion in 2017 to over \$63 billion in 2023 [1]. Flexible electronics could transform the way we make and use electronic devices. Many applications that require bendability to conform to the curved surface are driving the progress in the field, which in turn opens the door to futuristic applications such as foldaway smartphone displays, solar cells on plastic substrates, advanced medical devices, mobile health, and wearable sensors [2]. The anticipation is that these new form-factors will expand the scope of microelectronics and lead to further innovation. However, materials, packaging and manufacturing must evolve together with these devices to make these concepts economical and environmentally sustainable. Added value features such as flexibility and transparency have the potential to radically transform the electronics industry and spur a new era of growth. Figure 1.1 shows the current market size of the printed, organic and flexible electronics industry for year 2019 [3].

### 2019 Market Snapshot

Figure 1.1: Current market size of the printed, organic and flexible electronics industry [3].

Transparent electronics use transparent conductive oxides (TCOs) [4], wide bandgap semiconductors [5], 1-D inorganic nanostructures [6] and nanomaterials like metallic silver nanowires (AgNWs). Over the past two decades the use of transparent conductive materials has rapidly increased as a result of the increasing demand for display technology [7] and the development of thin film based solar cells. TCEs are also a crucial component of next generation electronic devices such as portable organic solar cells, organic light emitting diodes (OLEDs), bendable displays, touch screens, modern personal electronic devices, and transparent stretchable heater [8][9]. AgNWs with well-defined dimensions is a promising material for electrical and optical devices, particularly for flexible transparent conductive electrodes (TCEs). They are considered a strong competitor as a substitute to Indium Tin Oxide (ITO) in many of the applications. One of the primary reasons for this is that the incumbent technology (ITO) is not flexible; upon repeated bending, the films are known to crack and lose conductivity [10], which is particularly prohibitive for future product emergence of flexible electronic devices. When deposited from solution, AgNWs combine several advantages such as high optical transparency, low sheet resistance (R<sub>sh</sub>) and mechanical flexibility. Despite the significant progress in TCEs represented by the above reports, understanding the stability issues and challenges such as long-term environmental stability, high surface roughness, electrical shorting problems must be overcome to fully integrate these new electrodes into high performance commercial devices and circuits.

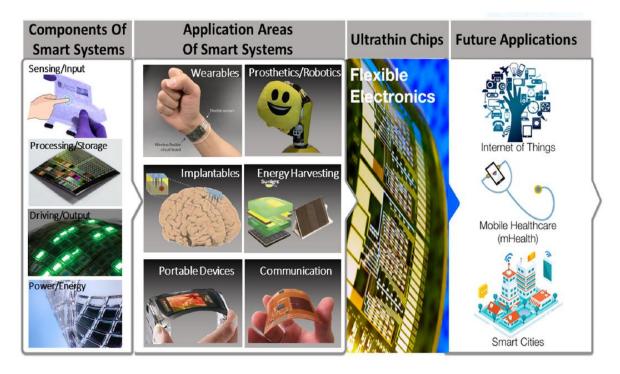

High mobility thin-film transistors are also crucial for future high resolution and fast response flexible displays [11]. The issue of low mobility (~1 cm² V-¹s⁻¹) of electrons in amorphous silicon (a-Si) based TFT backplanes has led to the rise of new technologies that will overcome this problem. Metal oxides are one of such replacement technologies that have been researched and gained huge industry acceptance over the last few years. Today the display industry is extensively using metal-oxide TFT backplane technology in displays based on liquid crystal and light emitting diode (LEDs). Zinc oxide (ZnO) and especially indium gallium zinc oxide (IGZO) has been extensively studied over the last few decades, with much current academic and industrial research and development. Other favourable aspects of ZnO include its broad chemistry leading to many opportunities for wet chemical etching, low power threshold for optical pumping, radiation hardness, and biocompatibility. Optical pumping is a process in which light is used to raise (or "pump") electrons from a lower energy level in an atom to a higher energy level. ZnO and related compounds (IGZO) offer carrier mobility of more than 10cm²V-¹s⁻¹ approaching 100cm²V-

<sup>1</sup>s<sup>-1</sup> [12][13]. High mobility oxide semiconductors, along with high-k gate dielectrics, are projected to be key ingredients for future transparent and emerging flexible and stretchable electronics [14]. Shown in Figure 1.2 are the applications of flexible electronics such as sensing, computing, data storage, and energy.

Figure 1.2: Applications of flexible electronics enabled through underpinning research in areas such as sensing, computing, data storage, and energy [1].

This thesis investigates high performance transparent components including AgNW TCEs for OPV, metal oxide TFTs and their electrical and environmental stability as outlined in the next section.

### 1.1 Highlights and Structure of this Thesis

This thesis focuses on the development of transparent and flexible components such as silver nanowire transparent conducting electrodes (AgNW TCEs), metal oxide TFTs with the aim of improving their stability and performance under real world conditions.

The highlights of this research are:

- The world leading Figure of Merit (FOM = 933) of AgNW TCE which is 2 × better as compared with current literature.

- Detailed stability analysis of AgNW TCE performance as a function of temperature and high current conditions.

Demonstration of improved electrical and surface roughness performance of flexible AgNW TCEs using post R2R processing techniques (thermal embossing, N<sub>2</sub> plasma treatment and photonic sintering).

- Demonstration of mixed dimension AgNWs for solution-processed, flexible, transparent and conducting electrodes with improved optical and physical properties.

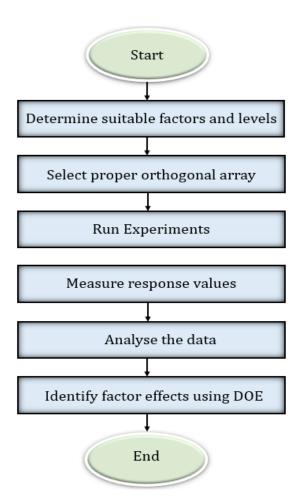

- Demonstration of improved performance of metal oxide TFTs and demonstration of process optimisation techniques such as Taguchi orthogonal array and Plackett-Burman Design for screening active factors.

- Demonstration of flexible, low voltage and transparent IGZO TFTs with high performance.

The structure of this thesis is as follows:

**Chapter 2** provides a background of the science behind this research. In this chapter, a state-of-the-art review of transparent electronics, AgNW TCEs, and their post processing, metal oxide TFT development is discussed. Then, the TFT operation and the electrical characteristics, as well as the density of states, are explained. Finally, the electrical and environmental stability of AgNW TCEs is discussed.

**Chapter 3** reports the experimental methods, setups used for manufacturing and characterisation of flexible TCEs and Metal oxide TFTs.

**Chapter 4** is the first results chapter demonstrating the outcomes of flexible TCEs, TCEs post processing and performance optimisation using Taguchi Orthogonal Arrays. Also presented are the results from solution processed mixed dimension AgNW flexible TCEs with improved the optical and physical properties. Finally, the effect of post processing on high current and temperature stability of AgNW TCEs has been investigated.

**Chapter 5** reports the ZnO based TFTs development, as well as optimisation of high-k anodic dielectric (Al<sub>2</sub>O<sub>3</sub>) for TFTs using Plackett-Burman design.

**Chapter 6** presents the effect of positive gate bias stressing on IGZO TFTs, flexible IGZO TFTs performance. Moreover, transparent AgNW film gated IGZO TFTs electrical, optical performance are reported and compared with TFTs on incumbent ITO transparent electrodes.

**Chapter 7** summarises the main results from the thesis and discusses possible directions for further work.

### Chapter 2. Literature Review of Transparent Electronics

This chapter details the current state and progress in the following areas investigated during this Ph.D.: silver nanowire based (AgNW) transparent conductive electrodes (TCEs) and metal oxide thin film transistors (TFTs). Basic fundamental background theory of TCEs and metal oxide TFTs are presented. Electrical, optical and physical properties, as well as deposition methods and post processing of AgNW TCEs, are reviewed. Then, the materials for TCEs, TFTs and n-channel TFT operation principles are explained. Furthermore, process optimization techniques such as Taguchi Orthogonal Arrays (OA) and Plackett-Burman Design (PBD) are detailed. Finally, the environmental and electrical stability of TCEs and TFTs are discussed.

### 2.1 Review of Transparent and Flexible Electronics

This section reviews the state of the art concerning transparent and flexible electronics, with the focus on AgNW based TCEs as well as ZnO and IGZO based TFTs. Flexible and transparent electronics presents a new age of electronic technologies. Recently, various applications in wearable electronics, flexible transparent OLED displays [15]–[20], radiofrequency identifications (RFIDs) [21] and sensing systems [22]–[25] have been demonstrated. Also, the technical progress in metal oxide TFTs is a significant factor for promoting the development of transparent and flexible displays [26]–[31].

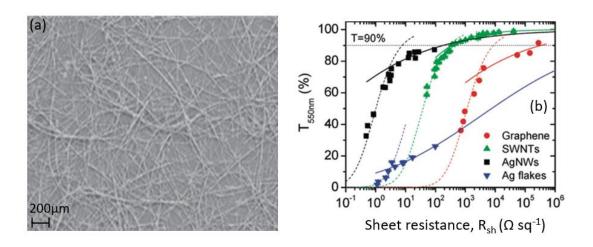

Figure 2.1: (a) SEM image of a AgNW transparent electrode, (b) Optical transmittance as a function of sheet resistance for silver, graphene and single walled carbon nanotubes (SWNTs) [32].

Shown in Figure 2.1(a) are SEM images of a AgNW transparent electrode, (b) Transmittance as a function of sheet resistance for silver, graphene, single walled carbon nanotubes (SWNTs). It is evident that AgNWs are one of the most promising in terms of electrical and optical performance, outperforming graphene and SWNTs. This is because even low density of AgNWs on substrate produces high transmittance and low sheet resistance.

Shown in Table 2.1 is a general guide to the different transparent conductive material electrode fabrication.

Table 2.1: General guide to transparent conductive material electrode fabrication [33]. + symbols indicate positive results – symbols represent poor results.

| Fabrication method <sup>a</sup>       | TCOs        | Graphene             | CNTs                | AgNWs               |

|---------------------------------------|-------------|----------------------|---------------------|---------------------|

| Chemical vapour deposition            | +++         | +++                  | +                   | -                   |

| Sputtering                            | +++         | -                    | -                   | -                   |

| Spin coating                          | -           | +                    | ++                  | ++                  |

| Spray deposition                      | ++          | +                    | +++                 | +++                 |

| Screen printing                       |             | +                    | ++                  | ++                  |

| Cost                                  | Low-high    | High                 | High                | Medium              |

| Processing temperature (°C)           | > 200b-1000 | RT-1000 <sup>c</sup> | RT-700 <sup>c</sup> | RT-700              |

| Uniformity                            | +++         | +                    | ++                  | ++                  |

| Typical thickness (nm)                | 100-300     | <5                   | <10                 | 25>600 <sup>d</sup> |

| Typical Rsh $\Omega$ sq $^{	ext{-}1}$ | 5-100       | 30-5000              | 60-300              | 1-50                |

| Transmission (at 550 nm)              | 80-97 %     | 80-96 %              | 80-91 %             | 80-96 %             |

<sup>&</sup>lt;sup>a</sup> Fabrication method refers to the production of electrodes directly, not to the production of the integral components which are used to fabricate the network.

The search for materials which can be used to make thin films that simultaneously show high transparency, low sheet resistance [34] and flexibility [35] has mainly focused on nanostructures such as conducting polymer [36], graphene [37], carbon nanotubes (CNT) [38], copper nanowires [39] and AgNWs [40]–[43]. Nanowires are one dimensional nanostructures possessing diameter of the order of a nanometer (10<sup>-9</sup> meters). CNT, graphene, and transparent conducting polymer films show low conductivity as compared to metal nanostructures and hence metallic nanostructures are

<sup>&</sup>lt;sup>b</sup> Deposition temperatures of transparent conductive oxides (TCOs) frequently need several hundred degrees Celsius or the use of vacuum processes such as sputtering.

<sup>&</sup>lt;sup>c</sup> Networks can be fabricated at room temperature (RT) but if device fabrication requires high temperature processes vacuum or encapsulation is required to stabilize the films.

<sup>&</sup>lt;sup>d</sup> Thickness is diameter and density dependent though with high mechanical pressure it can be reduced to the diameter of a single nanowire.

an appealing alternative. Metallic nanostructured materials are normally solution processed and deposited as disordered percolation networks. A solution process technique, such as spray coating can be used to readily prepare AgNW TCEs [44], [45]. Spray pyrolysis is a process in which a thin film is deposited by spraying a solution on a heated surface. This process can be carried out at low temperature (<80 °C) and does not require any vacuum equipment.

The focus of this thesis is on AgNWs films so CNT, graphene, and TCO are not discussed. There are three specific advantages of AgNW networks as transparent conductive materials. First is the low sheet resistances attainable with AgNW percolative networks, which can be approximately  $10~\Omega \text{sq}^{-1}$ . Secondly, they can demonstrate flexibility on plastic substrates and thirdly they possess high transparency in the infrared region of the electromagnetic spectrum [46]. However, creating TCEs with high conductivity and transparency is not a trivial matter, since these properties are often mutually exclusive. Nevertheless, AgNW based TCEs are relatively less expensive and are compatible with a roll-to-roll manufacturing process [47]–[52].

### 2.1.1 Review of State-of-the-Art in Transparent Electrodes

Over the last couple of decades, extensive work has been performed for the development of new TCEs. Shown in Table 2.2, is a summary of the best performing AgNW TCEs compared with other TCEs and their fabrication processes.

Table 2.2: A summary of the best performing non TCO electrodes compared with other TCEs.

| Reference                       | Material      | FoM   | Rsh (Ω sq <sup>-1</sup> ) | T(%) | Remark/Process          |  |

|---------------------------------|---------------|-------|---------------------------|------|-------------------------|--|

| L. Li et al. [53]               | metal grid    | 198.3 | 9.8                       | 83.1 | Photolithography        |  |

| J. Y. Lee <i>et al.</i> [54]    | AgNWs         | 150   | 16                        | 86   | Solution process        |  |

| Y. Jia <i>et al.</i> [55]       | AgNWs         | 207.3 | 35                        | 95   | Dynamic Heating Method  |  |

| H. Du <i>et al.</i> [56]        | AgNWs         | 212.8 | 7.1                       | 79.2 | Spin coating            |  |

| C. Preston et al. [57]          | AgNWs         | 300   | 13                        | 91   | Lamination process      |  |

| L. J. Andres <i>et al.</i> [58] | AgNWs         | 338   | 20.2                      | 94.7 | Spray coating           |  |

| A. Kim <i>et al.</i> [59]       | ZnO/AgNWs/ZnO | 487.9 | 8                         | 91   | DC magnetron sputtering |  |

| S. H. Jo <i>et al.</i> [60]     | CNT/PEDOT:PSS | 6     | 280                       | 80   | spray coating           |  |

| N. Kim <i>et al.</i> [61]       | PEDOT:PSS     | 76    | 46.1                      | 90   | Solution process        |  |

| S. Bae Jo <i>et al.</i> [62]    | Graphene      | 116.1 | 30                        | 90   | CVD                     |  |

In early 2008 J. Y. Lee *et al.* demonstrated one of the first solution processed AgNW network TCEs [54]. Since then, a major focus has been on the inorganic synthesis methods to synthesize significant quantities of metallic nanowires, such as copper or

AgNWs, with well controlled physical dimensions, formulated into stable dispersions [46], [63]–[68]. A. Kim *et al.* reported the best performing composite electrode based on AgNWs and ZnO films showing sheet resistance 8  $\Omega$  sq<sup>-1</sup> and transmittance 91% at 550 nm [59], although this process relied on a vacuum deposition step.

### 2.2 Review of Properties of Transparent Conductive Electrodes

TCEs are characterised by various electrical and optical properties such as sheet resistance, transmittance and haze [69], [70]. As TCEs play a critical role in electronic devices including liquid crystal displays, OLEDs and photovoltaics, the preferred TCE properties generally depend on their application. For instance, large optical haze (percentage of the transmitted light which is scattered) is disadvantageous to applications of TCEs in most electronic displays, however, large haze can enhance efficiency in photovoltaics because of the extended optical path length which increases the probability of photon absorption by the photosensitive material [71][72]. Irrespective of device type, the two most significant performance parameters are the TCE sheet resistance and optical transmittance. Thermal stability, processability and chemical compatibility with other materials, and work function are other key parameters.

Shown in Table 2.3 are the desired properties of transparent conductive TCEs for main applications in photovoltaics, OLEDs, film heaters and touch screens.

Table 2.3: Desired properties of transparent conductive electrodes for main applications [33]. The number of plus symbols indicates the importance of the property to the application.

| Application   | Transparency | Conductivity | Flexibility | Haze |

|---------------|--------------|--------------|-------------|------|

| Photovoltaics | +++          | +++          | +           | +++  |

| OLED          | ++           | ++           | +           | +    |

| Film Heaters  | +            | +++          | ++          | +    |

| Touch Screens | +++          | ++           | ++          | +    |

### 2.2.1 Sheet Resistance (R<sub>sh</sub>)

In terms of electrical properties, the low sheet resistance is usually desired. The sheet resistance of a TCE is a critical factor that requires precise control during the electrode fabrication process depending on the desired application. For example, in modern displays and touchscreen applications, in order to allow for fast screen response, the sheet resistance of the TCE has to be as low as possible. In the case of AgNWs, several physical characteristics of the nanowires themselves and network morphology affect the electrical

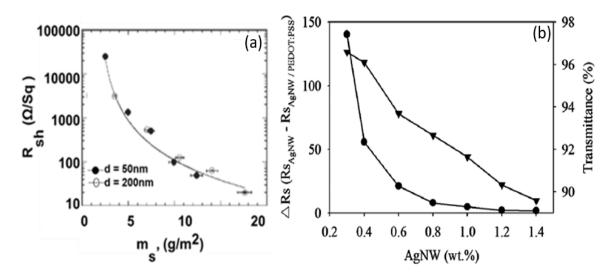

properties of nanowire networks and the sheet resistance [73]. In general, there is an increase in resistance of the network with a decrease in the length of the nanowires used and this trend is continued if the nanowire diameter is decreased [40], [46], [74]. For very low values of nanowire diameter, surface scattering effects lead to an increase in sheet resistance. Shown in Figure 2.2 (a) are the sheet resistance of AgNW films as a function of increased silver content and (b) AgNW weight percent (wt. %). As more AgNW material is deposited percolation network becomes bigger and more AgNWs junctions are created, leading to a decrease in the sheet resistance.

Figure 2.2: (a) The sheet resistance of AgNW films as a function of silver content and (b) the sheet resistance differences between single-layer AgNW films and AgNW/PEDOT:PSS films and the transmittance at 550 nm as a function of the concentration of AgNWs [75].

The nanowire density, which is deposited onto a substrate, plays a major role in the conduction properties of the network. In many studies, it has been shown that increasing the number of nanowires decreases the resistance; however, this also results in a decrease in the optical transmission of the network. Literature shows that the sheet resistance decreased with an increase in AgNW contents on the substrate [76],[77], as shown in figure 2.2 (a). Maintaining an equilibrium between the electrical and optical properties has long been a challenge for transparent conductive materials and fabrication processes. Electrical conductivity requirements differ according to the application of TCEs, for example, solar cells require a TCE sheet resistance on the scale of  $10\Omega$  sq<sup>-1</sup> [78][79]. Sheet resistance (R<sub>sh</sub>) is normally measured using a four point probe, from which sheet resistance can be calculated from equation 2.1 [80], where,  $\rho(t)$  is the film

sheet resistivity, t is film thickness, V is the applied voltage and I is the current passing through TCE. This equation is used in this thesis for sheet resistance calculations.

$$R_{Sh} = \frac{\rho(t)}{t}$$

Eq. 2.1

$$\rho(t) = \frac{t * V(4.532)}{I}$$

Eq. 2.2

### 2.2.2 Transmittance (T)

Another important property of transparent electrodes is transmittance. Percentage transmittance is defined as the percentage of light passing through the AgNW network exclusive of the absorption in the reference substrate and is given by the following equation 2.3:

$$\%T = \frac{S(\lambda) - D(\lambda)}{R(\lambda) - D(\lambda)} \times 100\%$$

Eq. 2.3

Where, S is the intensity of light at wavelength  $\lambda$ , D is the dark intensity at wavelength  $\lambda$ , and R is the reference intensity at wavelength  $\lambda$ .

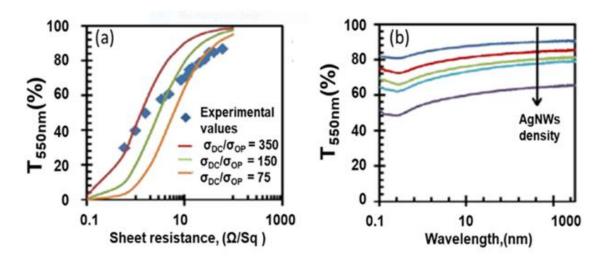

Figure 2.3: (a) Plot of AgNW film transmittance ( $\lambda$  = 550 nm) versus sheet resistance data for films deposited on PET (b) Transmittance spectra for various AgNW films [81].

Shown in Figure 2.3 (a) is the plot of AgNW film transmittance ( $\lambda$  = 550 nm) versus sheet resistance data for films deposited on polyethylene terephthalate (PET) and Figure 2.3 (b) is the transmittance spectra for various AgNW films. It has also been shown

in the literature that longer AgNWs form a better network due to longer conducting paths, lower deposition density and an increased number of junctions between AgNWs, leading to lower junction resistance and high transmittance [82]. These factors indicate that the optimum of AgNWs should be longer, as this can improve the conductivity of TCEs, and thinner AgNWs as this decreases the deposition area and light scattering, improving the optical transparency and haze.

### 2.2.3 Figure of Merit (FoM)

To evaluate the trade-off between Transmittance (T) and sheet resistance ( $R_{sh}$ ) values, a combined 'Figure of Merit' can be used to evaluate the quality of a transparent electrode. The Figure of merit (FoM) is often reported in the literature [58][83] and is given by equation 2.4. This equation is used in this thesis for FOM calculations.

$$FOM = \frac{188.5}{R_{sh}(\sqrt{\frac{1}{T}} - 1)}$$

[58] Eq. 2.4

The best reported FoM [59] of composite AgNW/ZnO TCE to date is 487.9. In this work AgNWs form a random percolating network embedded between the ZnO layers prepared by direct current (DC) magnetron sputtering at room temperature.

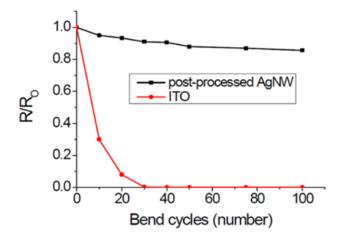

### 2.2.4 Mechanical Flexibility

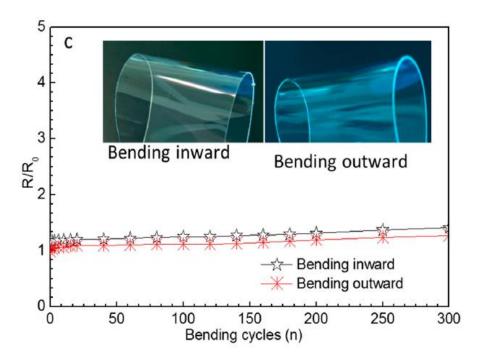

In contrast to ITO, AgNW TCEs on plastic are mechanically flexible. The literature confirms that the mechanical flexibility of the AgNW electrodes is particularly good. For example, J. Kettle *et al.* demonstrated that AgNWs TCE remains robust even after extortionate bending tests (100 cycles with a bending radius of 20 mm) [58]. After testing, no modification of the optical properties was observed and a drop lower than 5% in sheet resistance after 100 bending cycles were recorded. Conversely, ITO electrodes showed a drop of 77% in sheet resistance after the first 10 bending cycles and catastrophic failure after 20 cycles during the same test.

Recently, Y. Wang *et al.* reported that the relative change in sheet resistance of the film over 300 bending cycles of outward and inward bending was less than 1.5% and the films exhibited good conductivity and heating performance [84]. Figure 2.4 shows the relative change in the sheet resistance of the AgNW TCE versus the number of bending

cycles, where R and  $R_0$  represent the sheet resistance of films before and after the bending test, respectively.

Figure 2.4: Example of a transparent conductive electrode showing the relative change in the sheet resistance of the AgNW TCE versus the number of bending cycles [79].

### 2.3 Post Processing Treatment

After the AgNW deposition process, some nanowires protrude from the TCE surface and some of them lie on top of each other, which results in increased surface roughness to a few hundred nanometers. However, much lower surface roughness is needed for various TCE applications. For instance, the active films in organic solar cells are thin (typically between 100 to 300nm) [85]. Optical, electrical and physical properties of AgNW based transparent electrodes depends on a number of factors including type of AgNWs [58],[86], deposition process [87] and also post treatment of electrodes such as thermal annealing [88][89], mechanical pressing [90]–[92], fast sintering [93], etc.

To enhance the quality and performance of TCEs, post-processing treatments on electrodes are needed. For example, H. H. Khaligh  $\it et al.$  reported the hot rolling of AgNW TCEs for surface roughness minimization, achieving the root-mean-square surface roughness (Rq) of 7nm and the maximum peak-to-valley (Pv) value 30 nm, making the electrodes suitable for typical organic devices [91]. In addition, the adhesion of the AgNWs to the substrate significantly increased with this process.

Shown in Table 2.4 are the surface roughness data of the AgNW electrodes post processed using a hot rolling process.

Table 2.4: Surface roughness data of the annealed AgNW TCEs and post processed using hot rolling [94].

| Post treatment | RMS Roughness, Rq<br>(nm) | Max peak to valley, Pv<br>(nm) |

|----------------|---------------------------|--------------------------------|

| Annealed       | 14                        | >90                            |

| Rolled         | 7                         | <30                            |

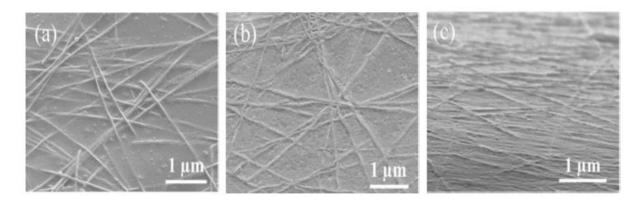

Shown in Figure 2.5 are SEM images of tilted (45°) AgNW film on PET after (a) annealing, and (b) hot rolling. (c) shows a SEM image of a tilted (85°), a hot-rolled electrode which demonstrates that the nanowires are embedded in the substrate surface.

Figure 2.5: SEM images of tilted (45°) AgNW film on PET after (a) annealing, (b) hot rolling. (c) SEM image of a tilted (85°) hot-rolled electrode [91].

The post treatment on TCEs is shown to mostly affect the resistance and surface roughness of the nanowire network. Even though AgNW TCEs have better electrical and optical properties, some drawbacks need to be addressed. For example, one major issue is too high surface roughness of AgNW TCEs which causes shorting of device electrodes [95]. This imposes difficulties to integrate AgNW TCEs in many electronic devices such as solar cells and TFTs.

A simple post processing technique used is plasma treatment of the surface of AgNW TCEs for the reduction of the sheet resistance cited in the literature. For example, Jun Li *et al.* demonstrated that argon (Ar) plasma treatment removes the residual surfactant, polyvinylpyrrolidone (PVP), and enhances the contact between adjacent AgNWs. They reported AgNWs TCEs with a sheet resistance of 7.2  $\Omega$  sq<sup>-1</sup> and a transmittance of 78% at 550 nm [96].

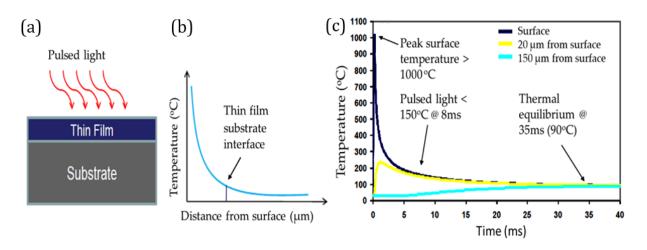

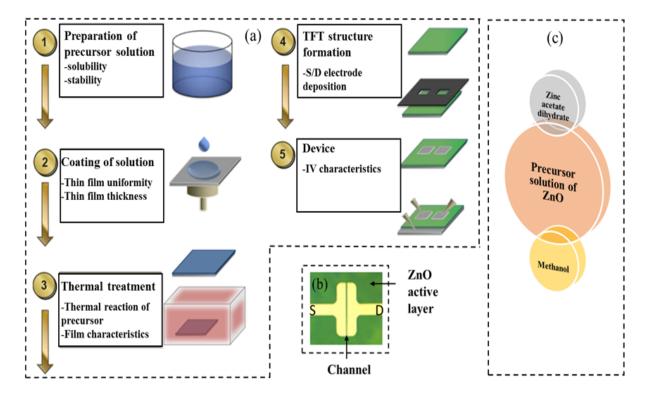

Another new technology for post processing AgNW TCEs is photonic curing that allows the sintering of AgNWs on low temperature, flexible substrates such as paper and plastic in less than 2 ms [97][98]. D. J. Lee *et al.* reported improvements in sheet resistance of AgNW TCE using the intense pulsed light (IPL) method, which welds the interconnections among AgNWs in a short time without heat or pressure treatment [99], [100]. They achieved the sheet resistance of  $12.6 \Omega \text{ sq}^{-1}$  with a transmittance of 85.7% at 550 nm.

### 2.4 Physical and Chemical Deposition Techniques

Physical methods such as sputtering, evaporation, laser deposition and chemical methods like chemical vapour deposition, sol-gel, chemical bath deposition, electroplating have been used for preparing TCEs. The best performances are generally obtained using physical methods such as chemical vapor deposition (CVD) or plasma-enhanced chemical vapor deposition (PECVD). However, these are not generally scalable to roll to roll manufacturing processes. Historically some of the earliest TCEs were deposited by solution processing using spray pyrolysis.

Based on the direct fabrication of devices, there are many deposition techniques for semiconductors and electronic materials. To obtain thin films with good quality, two common deposition techniques: physical and chemical depositions are used. Shown in Table 2.5 is a summary of the above mentioned deposition techniques.

| Physical deposition        | Chemical deposition           |

|----------------------------|-------------------------------|

| Vacuum thermal evaporation | Sol-gel technique             |

| Electron beam evaporation  | Chemical bath deposition      |

| Laser beam evaporation     | Spray pyrolysis technique     |

| Molecular beam epitaxy     | Electroplating technique      |

| Ion plating evaporation    | Low pressure (LPCVD)          |

| DC sputtering              | Plasma enhanced (PECVD)       |

| RF sputtering              | Atomic layer deposition (ALD) |

Table 2.5: A summary of deposition techniques [101].

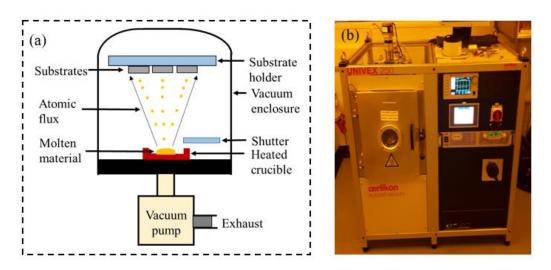

In this thesis, the spray pyrolysis technique, electron beam evaporation and radio frequency (RF) sputtering for deposition of thin films were used.

### 2.5 Review of Thin Film Transistors and Circuits

TFTs are widely used as a backplane to drive display components, such as LCD, OLED, and even  $\mu$ -LCD. Response time and resolution of display highly dependent upon the mobility

of charge carriers and hence high mobility TFTs are crucial for future high resolution and fast response flexible displays [102].

A TFT is a type of field-effect transistor (FET) made by depositing thin films of a semiconductor layer as well as the dielectric layer and metallic contacts over a supporting substrate. The main differentiator from other FET technologies is that common substrate is glass or polyimide, unlike conventional FETs, where the semiconductor is used as substrate. Glass and certain plastic films are good insulators and this limits the leakage current to a minimum. In 1962, P. K. Weimer [103] fabricated the first *n*-channel TFT employing a top gate, staggered structure with micro-crystalline cadmium sulfide (CdS) deposited by evaporation in vacuum as the channel layer and silicon monoxide as the dielectric layer. These TFTs possessed field-effect mobility values of 1.1 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>and an on-off current ratio of 10.

Since these early studies, a number of materials have been utilised in TFTs. Metal oxides, such as ZnO and IGZO, show better air stability and higher electron mobility. However, oxide-based TFTs so far provide only high-performance n-channel TFTs, which prevents the realization of CMOS technology. Therefore, organic-inorganic hybrid complementary structures comprised of n-type oxide semiconductor and p-type organic semiconductor can be potential candidates for complementary circuit design.

Metal oxide semiconductors have been demonstrated the TFTs with a number of materials specifically ZnO [104]–[106], zinc tin oxide (ZTO) [107]–[111], indium zinc oxide (IZO)[112]–[114], indium gallium oxide (IGO)[115], and indium gallium zinc oxide (IGZO) [103], [116]–[122].

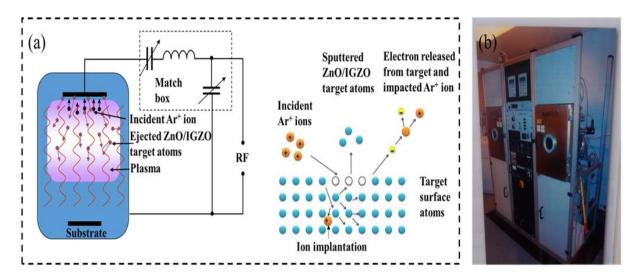

Amongst metal oxide semiconductors, IGZO, ZnO, and IZO are more attractive because they can be processed at room temperature whilst maintaining good performance, making them compatible with flexible substrates and consequently reducing manufacture costs. IGZO and IZO films, which are normally deposited by physical vapor deposition or RF-magnetron sputtering at room temperatures, show amorphous nature and still achieve high electron mobility. The amorphous material structure of the IGZO films is stable up to 500 °C in air. Due to this, IGZO and IZO are predominantly attractive for microelectronic circuits on flexible substrates and mobility as high as 100 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, and on/off current ratio of 10<sup>7</sup> have been demonstrated. For example, C. M. Hsuet *et al.* [123] fabricated IGZO films on glass substrates using cosputtering, demonstrating high carrier mobility around about 163.4 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>.

The rapid progress in the field of n-channel metal oxide TFTs has motivated research on p-channel metal oxide TFTs to realise metal oxide-based CMOS circuits that enable low power consumption, large-area electronics. For example, C. W. Shih, reported high performance p-tin oxide (SnO) thin-film transistor (p-TFT) by a simple process of reactive sputtering from a tin (Sn) target under oxygen environment, demonstrating high field effect mobility 7.6 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>, subthreshold slope 140 mV/dec, and on-off current ratio  $3 \times 10^4$  [124]. Nickel oxide (NiO) is an attractive p-type semiconductor because its properties are very beneficial for many photocatalytic, battery, electrochromic and chemical sensing applications [125]. Fukai Shan  $et\ al.$  reported a full solution processed NiOx/AlOx TFTs with an operating voltage of 3.5 V that exhibits high hole mobility of around 25 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup> [126]. E. Fortunato  $et\ al.$  reported copper oxide (Cu<sub>2</sub>O) based TFTs deposited by reactive RF magnetron sputtering at room temperature and the TFTs exhibited field-effect mobility of 3.9 cm<sup>2</sup>V<sup>-1</sup>s<sup>-1</sup>and an on/off ratio of  $2 \times 10^2$ .

Oxide TFTs based electronics are not limited to lab scale research but are now expanding to the commercialization in display applications. W. J. Nam *et al.* successfully fabricated and demonstrated 55-inch OLED TV using IGZO TFTs [127]. Additional applications have also been demonstrated such as ring oscillators by Jiawei Zhang *et al.* [128], a complementary circuit based on *n*-type IGZO and *p*-type tin monoxide (SnO) with an oscillation frequency of 2.63kHz and the peak-to-peak oscillation amplitude 36.1 V at a supply voltage of 40 V.

The ongoing research and continuous increase in TFT performance could establish new markets. A complementary electronic device requires both p-channel and n-channel TFTs. Complementary inverters are preferred compared to only n or p-channel inverters because they allow low power consumption, higher gains, and low noise margins. Reported complementary inverters on glass or flexible substrates are mostly composed of organic TFTs for both p-channel and n-channel. Devices in organic electronics, p-type material development occurred much quicker. Among organic semiconductors, p-type pentacene has been the most widely studied material, with hole mobility values of  $0.1 \sim 1 \text{ cm}^2 \text{ V}^{-1} \text{ s}^{-1}$ . However, recent development has seen hole mobilities >10 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup> [129] reported for solution processed polymers. Therefore, hybrid organic-inorganic complementary structures composed of the n-type oxide semiconductor and p-type organic semiconductor are potential candidates for circuit design based on CMOS technology. For example, Takeya  $et\ al$ . reported solution-processed organic( $C_{10}$ -DNBDT-NW)-inorganic(IZO) hybrid CMOS inverter exhibiting a high gain reaching 890 [130].

### 2.6 Materials for Transparent and Flexible TFTs

In this section properties of various materials used for manufacturing transparent and flexible TFTs are described. They include transparent and flexible substrates, dielectric layer materials of different kinds.

### 2.6.1 Transparent and Flexible Substrates

TCEs and TFTs are usually made on optically transparent substrates. The properties of plastic substrates affect quality and carrier transportation behaviour and limit maximum fabrication temperature. Polymer optical films can be classified according to the glass transition temperature ( $T_g$ ) into three types [131]: (1) conventional polymers ( $T_g < 100\,^{\circ}$ C), (2) common high temperature polymers ( $100 \le T_g < 200\,^{\circ}$ C), and (3) high temperature polymers ( $T_g \ge 200\,^{\circ}$ C). Glass transition temperature is the temperature, below which the physical properties of plastics change to those of a glassy or crystalline state. Table 2.6 lists the basic properties of three kinds of polymer substrates, which are presently widely used, namely polyimide (PI), polyethylene-napthalate (PEN) and polyethylene terephthalate (PET).

Table 2.6: Basic properties of commonly used flexible transparent substrates [132].

| Material | T <sub>g</sub> ( <sup>0</sup> C ) | λ <sub>c</sub> (nm) | CTE (ppm °C) | Chemical resistance |           |

|----------|-----------------------------------|---------------------|--------------|---------------------|-----------|

|          |                                   |                     |              |                     | roughness |

| PI       | 300                               | 500                 | 12           | Good                | Good      |

| PEN      | 140                               | 380                 | 20           | Good                | Moderate  |

| PET      | 80                                | 300                 | 33           | Good                | Moderate  |

| PDMS     | -120                              | 200                 | 301          | Good                | Poor      |

Among all of the flexible substrates, PI shows the highest  $T_g$ , the smallest coefficient of thermal expansion (CTE) and surface roughness. Additionally, PI has also good chemical stability in acid, alkali and organic solvents. Though the cut-off wavelength ( $\lambda_c$ ) is in the visible range, the PI substrates have deep colour and poor optical transmittance. Colourless and optically transparent polyimide (CPI) films have only recently been developed. It appears that the CPI substrates will be one of the best choices for next generation flexible transparent electronics [133]. The optical transparency of PET substrates is good (>85%) [134] and they are currently widely used as the protection layer in various liquid crystal displays devices (LCDs), such as televisions, computers and cell phones. However, the main drawback of PET is its low  $T_g$  ( $\approx 80~{}^{\circ}\text{C}$ ), which may bring challenges in device fabrication, integration and operation. Furthermore, PET possesses

a high-water vapour transmission rate. PEN substrate has a higher  $T_g$  (  $\approx 140~{}^{\circ}\text{C}$ ) than PET, which makes it a suitable substrate for manufacturing devices [135]. Recently, polydimethylsiloxane (PDMS) substrates are used in flexible electronics applications. PDMS is a type of elastomer and upon flexing and stretching, it induces no plastic deformation [136]. Also, it shows high optical transmittance, short  $\lambda_c$ , which makes PDMS the perfect substrate for the emerging stretchable electronics [137]. It is worth noting that ultra-thin (25-100  $\mu$ m) flexible glass [138], [139], for example, Willow by Corning company [140], is also regarded as a promising substrate for flexible transparent electronics. It shows a higher processing temperature ( $\sim 500~{}^{\circ}\text{C}$ ), good resistance to scratching and higher optical transmittance [141]. However, up to now, a few pieces of research on flexible glass were reported in the literature.

To decrease the surface roughness of substrates and gas permeability, as well as increase the chemical resistance and adhesion of the films, a barrier or encapsulation layer is often used onto the substrates. The commonly used encapsulation materials are  $Al_2O_3$ ,  $Si_3N_4$ , SiO and  $SiO_2$ , which are electrically insulating and easily grown by chemical vapour deposition [142]–[145].

### 2.6.2 Dielectric Layers

The quality of the dielectric and the semiconductor/dielectrics interface is of vital importance in many transparent electronic applications. Currently, there are three types of dielectric materials that are commonly used in flexible metal oxide TFTs.

**Inorganic dielectrics:** Silicon dioxide (SiO<sub>2</sub>) and silicon nitride (Si<sub>3</sub>N<sub>4</sub>) are two kinds of inorganic dielectric materials adopted from a-Si:H and poly-Si TFTs. Nevertheless, the high deposition temperature (above  $100\,^{\circ}$ C) for high-quality films by plasma enhanced chemical vapour deposition (PECVD) hinders their application on flexible substrates. Instead of SiO<sub>2</sub> [146], high-k dielectrics (Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>) are more widely used in flexible transparent metal oxide TFTs, because they can be synthesized at low temperature by atomic layer deposition (ALD) or solution processes like anodization of aluminum [147]. Inorganic dielectrics, such as Al<sub>2</sub>O<sub>3</sub>, exhibit low-temperature fabrication convenience and result in excellent device performance. However, mechanical failure may occur when the films are under tensile or compressive strains.

**Organic dielectrics:** Organic dielectric materials [148], such as poly(methyl methacrylate) (PMMA) and polystyrene (PS), can sustain larger strain [149] because the

molecules in them are linked through the van der Waals forces and/or hydrogen bonds which are weak interactions. In addition, simple and low-cost processes, such as spin coating and printing, can be used to deposit polymer dielectrics. More recently, low-k fluorinated polymers such as CYTOP have been used as dielectric materials [150]–[152]. Also, CYTOP has been used as a passivation layer in TFTs due to its hydrophobic nature [153], [154].

**Organic/inorganic hybrid dielectrics**: Even though polymeric dielectrics withstand greater strain than their inorganic counterparts and can relax the stress in the channel layer, they have some drawbacks. Firstly, polymers are usually soft, and consequently, the deposition of the channel layer may induce damage inside the polymer layer or at the polymer/channel interface, which will significantly influence the transport behaviour of charge carriers. Secondly, the dielectric constants (k) of most polymers are relatively low (2.5-2.6 for PVP). Thirdly, the polymeric dielectrics are more hydrophobic than inorganic materials, which is undesirable for the direct growth of channel semiconductors [155]. By utilizing a stacked organic/inorganic hybrid gate dielectric, [156] these problems can be solved. Also, by introducing inorganic nanoparticles into polymer matrices to form polymer nanocomposites. This was achieved, for example, Lai et al. fabricated a nanocomposite dielectric by incorporating high-k Al<sub>2</sub>O<sub>3</sub> nanoparticles into polymer PVP films [157]. Majewski and co-workers reported solution processed high-k nanocomposite/low-k polymer bilayer (Barium strontium titanate and barium zirconate nanoparticles were dispersed in a poly (vinylidene fluoride-co-hexafluoropropylene) P(VDF-HFP) polymer matrix) gate dielectric used for the fabrication of organic field-effect transistors (OFETs) that operate effectively at 1V [158].

Various approaches can be used to manufacture flexible electronic devices. Each of them has its distinct requirements regarding the process parameters and utilized materials:

- (1) A silicon wafer thinned down to thicknesses below 50  $\mu$ m becomes flexible, however, investigation on bending limits before a mechanical fracture or failure occurs needs to be carried out [159].

- (2) The thinned die can then be attached to a flexible substrate [160].

- (3) Devices can be manufactured on polymers such as PET or PEN, which are attached to a rigid, low-cost substrate.

- (4) Transfer printing methods can be used to fabricate electronic devices on a large scale, and then transferred to a plastic substrate.

- (5) Direct fabrication of devices on unconventional flexible substrates can combine the advantages of standard semiconductor technologies and large area processing, but suffers from the limited thermal stability of flexible substrates [161]. In this thesis, the latter approach was adopted for device fabrication.

### 2.6.3 Metal oxide semiconductors

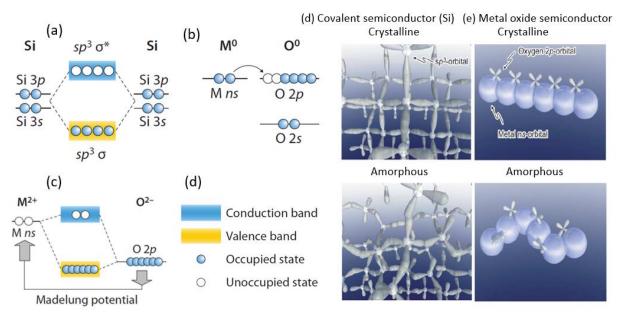

The oxides of post-transition metals such as ZnO and IGZO have been known for a decade and these materials have large bandgap and wide controllability of carrier concentration, which can make them useful for transparent thin film transistor (TFTs) applications. The conduction mechanism in metal oxide semiconductors is very different from that in conventional Si-based semiconductors. Amorphous silicon has poor carrier transport properties ( $\sim 1 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ ) relative to single crystalline silicon materials ( $\sim 500 \text{ cm}^2\text{V}^{-1}\text{s}^{-1}$ ). This is associated to the structure and conduction mechanism between amorphous and single crystal materials. Si has a strong covalent bond, and the conduction band minimum (CBM) and valence band maximum (VBM) are made of anti-bonding (sp<sup>3</sup>  $\sigma$  \*) and bonding  $(sp^3 \sigma)$  states of Si hybridized orbitals, and its bandgap is formed by the energy splitting of the  $\sigma$  -  $\sigma$  \* level shown by Figure 2.6 (a). The mobility of amorphous silicon is small, as carrier transport is controlled by hopping between localized tail states and band conduction is not achieved. Therefore, this hopping mechanism is strongly related to the local range order or structure, such as the strained and disordered chemical bonds from rather deep and high density of localized states below conduction band minimum (CBM) and above valence band maximum (VCM), causing the carrier trapping process. On the other hand, the oxide semiconductors have strong ionicity and charge transfer occurs from heavy metal ion to oxygen atoms shown by Figure 2.6 (b). When heavy metal ions and oxygen ions come close, charge transfer occurs due to largely different electron affinity and ionization potential (Figure 2.6 (c)). In addition, the Madelung potential which comes from the difference between cations and anions by virtue of their opposing charges stabilizes the ionized states during the ionic bonding process. As a result, in Figure 2.6 (c), the Madelung potential induces the energy splitting and the conduction band minimum (CBM) is occupied the 2p orbital of oxygen and the valence band maximum un-occupied by ns orbital of cations.

Figure 2.6: Schematic electronic structures of silicon and ionic oxide semiconductors. (a–c) [163].Bandgap formation mechanisms in (a) covalent and (b, c) ionic semiconductors. Closed and open circles denote occupied and unoccupied states, respectively. (d, e) Schematic orbital drawings for the carrier transport paths in crystalline and amorphous semiconductors [164]. (d) Covalent semiconductors with sp<sub>3</sub> orbitals (e) metal oxide semiconductors with the s-orbital overlap of metal cation.

The CBMs with large spatial sized s-orbital of heavy cations overlaps with the neighbouring metal s orbital, and makes the conduction path for carriers which are not influenced largely by disordered local structure. This is the reason why metal oxide semiconductors have high mobility even though there is an amorphous structure. Figure 2.6 shows the schematic drawing of the structure Si-based and metal oxide semiconductors structure. Figure 2.6 (a) is the Si semiconductor layer which has the hopping mechanism to transfer the electron carriers. In single crystal structure, there is a transfer path with hopping mechanism because of the long-range order in crystal structure using sp³ hybridization orbitals, and have a large amount of electron field mobility. However, the amorphous structure does not have any long-range order in this structure, and electron carriers cannot move fast in this structure because of the barrier with random structure. In a metal oxide semiconductor, large sized s-orbital of metal ion has an overlapping between an adjacent atom, and there provides the current path of electron carrier. Even though there has an amorphous structure in the metal oxide layer, s-orbital is easy to overlap as shown in Figure 2.6 (b).

Amorphous oxide semiconductors have a potential fluctuation above the mobility edge and the distribution of potential barriers exists in the conduction band. These

different paths cause different conductance for electron transmission over the potential barrier. In other words, the carrier density creates the degenerated conduction for amorphous IGZO and crystalline IGZO.

The low defect density in the a-IGZO layer is the reason why IGZO has a good subthreshold slope in the transfer curve. This is therefore possible to apply the low voltage driven TFTs for having low power consumption.

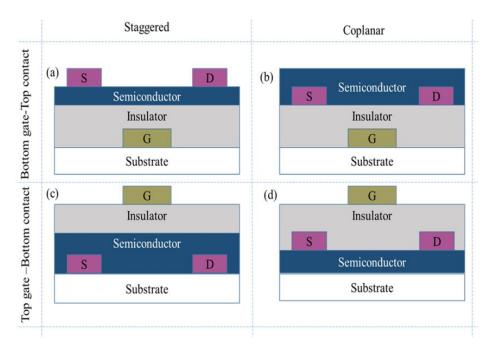

### 2.7 Device Structures of TFTs

Shown in Figure 2.7 are the typical TFTs device structures [165], determined by the position of the gate, source, and drain contacts relative to the active semiconductor film [166]. The basic structures are either coplanar or staggered. In a staggered structure, also called top-contact structure, the gate contact is on the opposite side of the semiconductor film from the source and drain contacts, as shown in Figure 2.7 (a) and (c). In such an arrangement, the source-drain contacts are in direct contact with the induced channel. In a coplanar structure, also called bottom-contact structure, the gate, source, and drain contacts are all located on the same side of the semiconductor film, as shown in Figure 2.6 (b) and (d). TFTs are also categorized as bottom gate (Figure 2.7 (a) and (b)) or top gate ((Figure 2.7 (c) and (d)) based on the position of gate. In this thesis, we have used bottom-gate top-contact structure.

Figure 2.7: Cross-sections of simplified TFT device configurations: (a) Bottom-gate staggered structure (top-contact); (b) Bottom-gate coplanar structure (bottom-contact); (c) Top-gate staggered structure; (d) Top-gate coplanar structure [167].

### 2.8 Operation Principles of TFTs

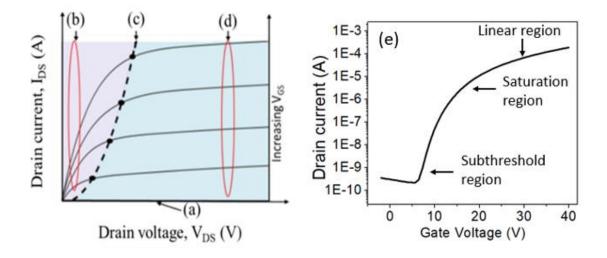

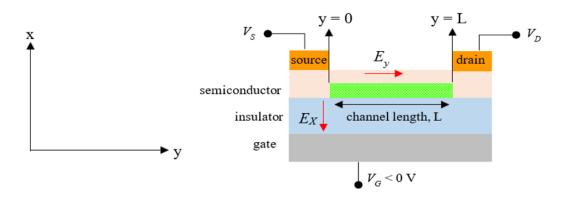

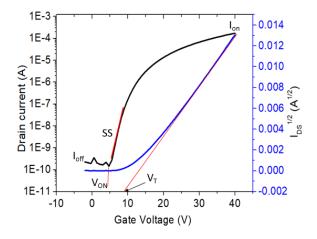

The TFT is a three-terminal device, in which a voltage (positive for *n*-type and negative for p-type material) applied to gate electrode controls current flow between source and drain electrodes under an applied voltage bias [168]. In electron transporting TFTs, modulation of a negative channel current flowing between the metallic source and drain terminals by the applied positive gate voltage (V<sub>G</sub>) forms the basis of the device operation. The gate electrode is always separated from the semiconductor by the gate dielectric. The source terminal is always grounded (Vs=0V). Electrode materials with appropriate work functions (i.e. matching energies) are selected to optimize electron injection and reduce parasitic effects such as contact resistance. Application of V<sub>G</sub> modulates the conductivity of the semiconductor region in proximity of the gate dielectric. When a source-drain voltage ( $V_{DS}$ ) is applied to the device, injected charge carriers (holes or electrons for pchannel and *n*-channel devices, respectively) accumulate at the semiconductor/insulator interface giving rise to a channel current that flows between the source and drain terminals. When the electric field strength corresponding to VDS is significantly smaller than that of V<sub>G</sub>, the TFT operates in the so-called 'linear' regime: the distribution of electrons across the channel is uniform and the channel drain current (I<sub>D</sub>) varies linearly with the applied V<sub>DS</sub>. If the field strengths corresponding to V<sub>G</sub> and V<sub>D</sub> are comparable, the device enters the 'saturation' regime, where I<sub>D</sub> saturates and becomes independent of V<sub>DS</sub>. This is the point at which the depletion of electrons occurs at the region closest to the drain electrode, and thus the channel is described as pinched-off.

Figure 2.8 shows the four regions of *n*-channel TFT operation (a) off region (b) linear region (c) pinch off points (d) saturation region in a bottom-gate top-contact metal oxide TFT output characteristics and (e) transfer characteristics of n- channel TFT.

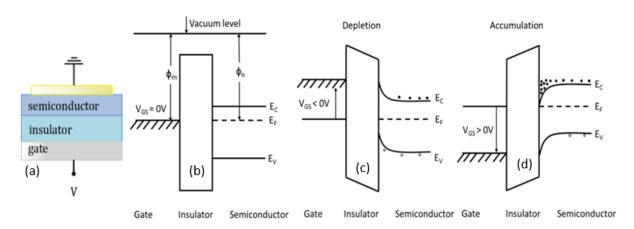

An oxide TFT device can be considered as two capacitor plates separated by an insulator between source/drain contact and gate contact as shown in figure 2.9 (a). To better understand the working of metal oxide TFTs, the energy band diagrams of a metal insulator semiconductor (MIS) structure are shown in Figure 2.9. Different from metal oxide semiconductor field-effect transistor (MOSFET) operations using an inversion-mode, organic or oxide semiconductor TFTs are operated in the accumulation-mode [169][170]. Figure 2.9 shows several energy band diagrams as viewed through the gate of an *n*-channel TFT operating in such mode. For simplicity, hereafter the operation of TFTs will be reviewed by assuming an oxide semiconductor channel.

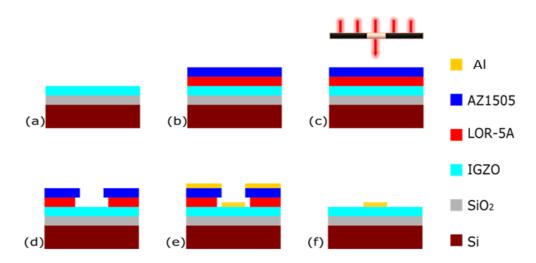

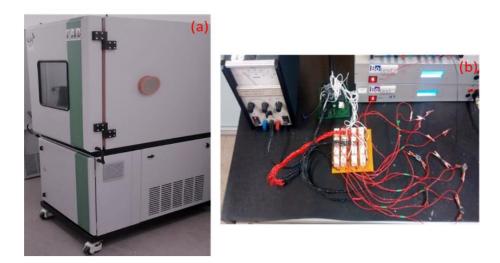

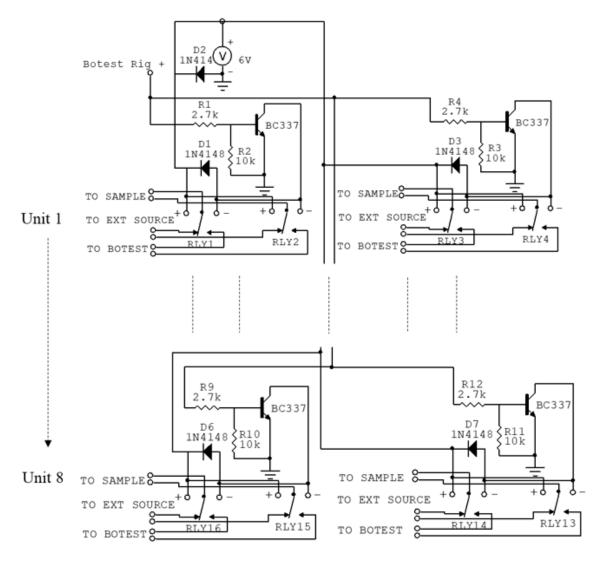

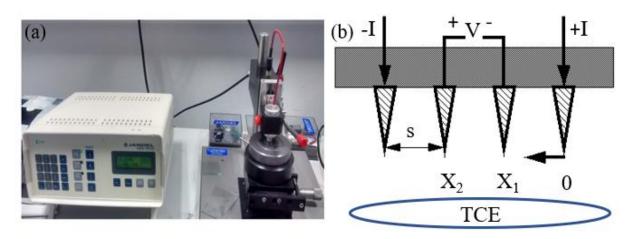

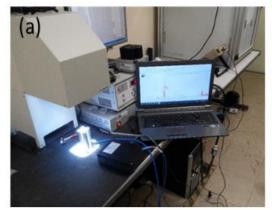

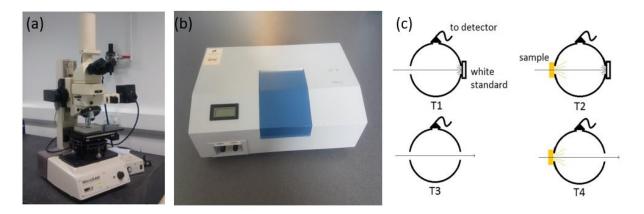

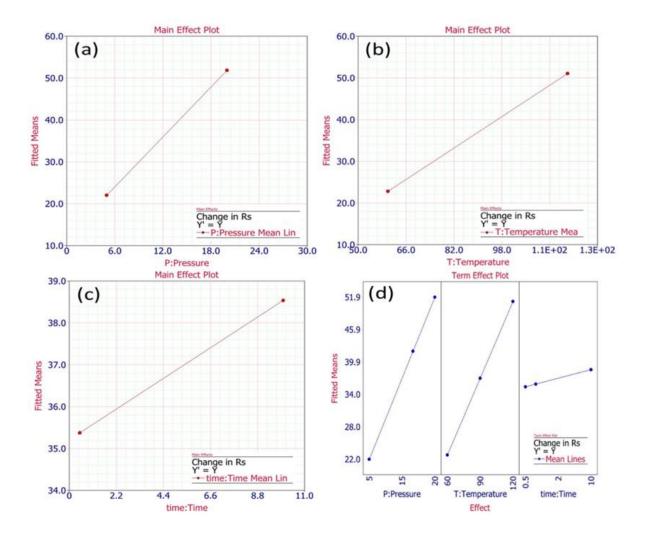

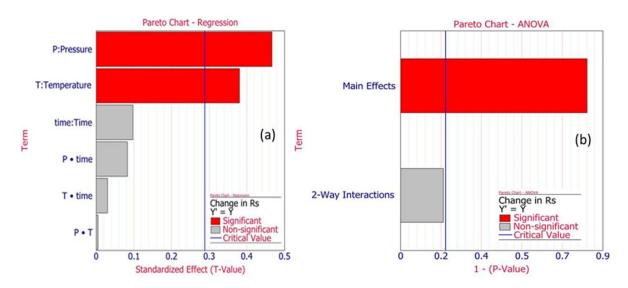

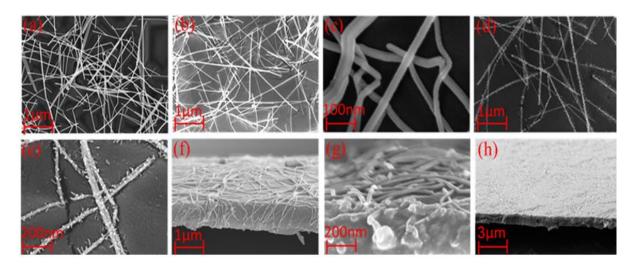

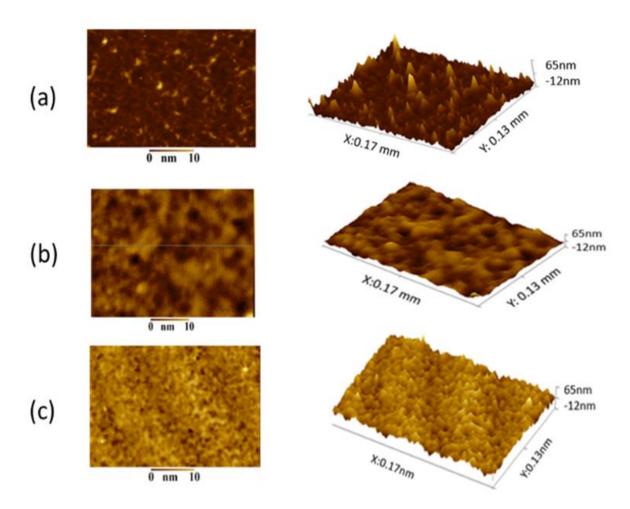

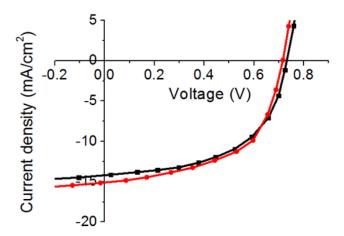

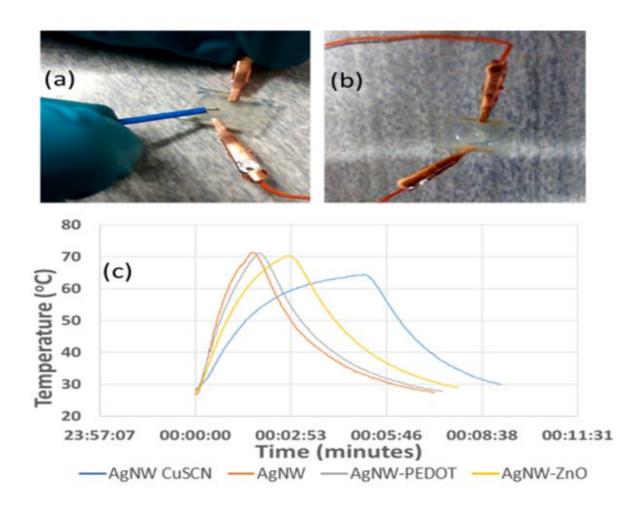

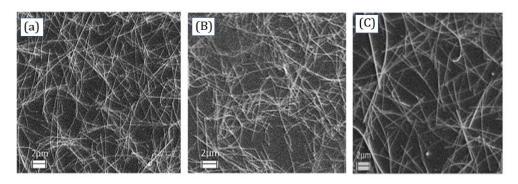

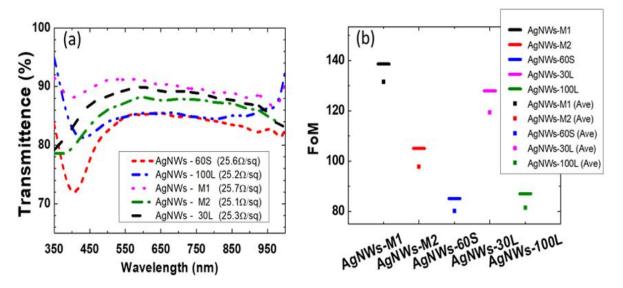

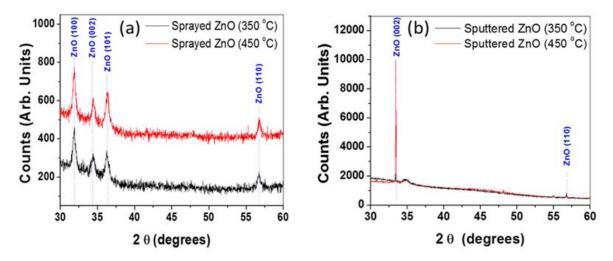

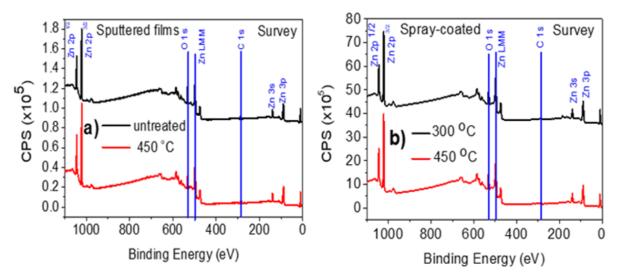

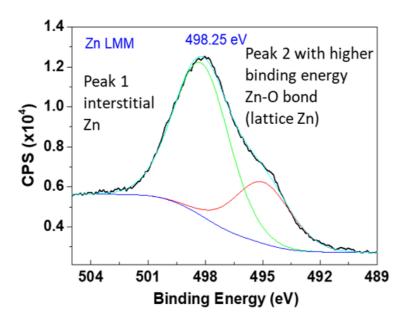

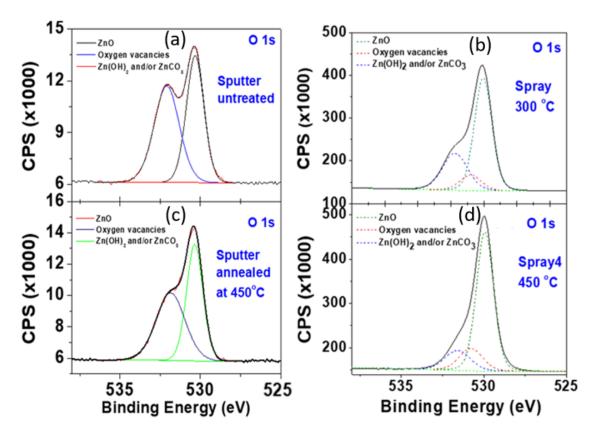

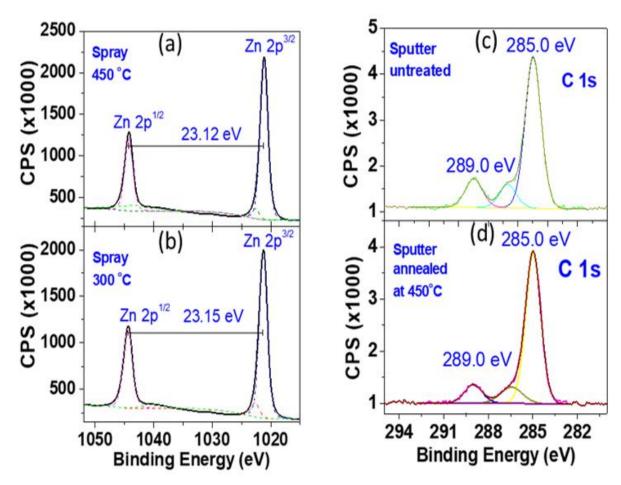

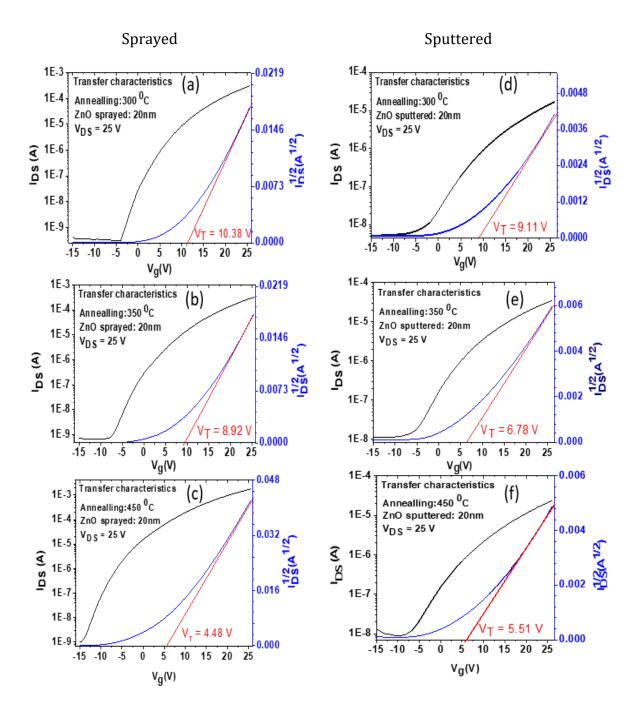

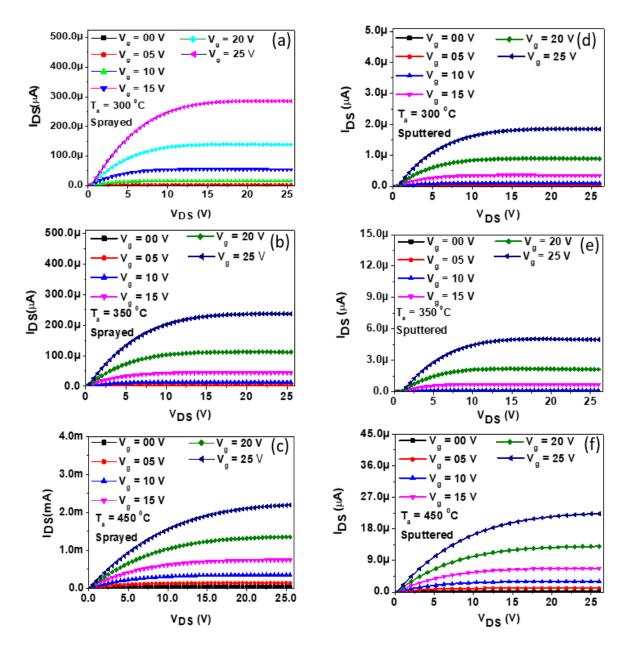

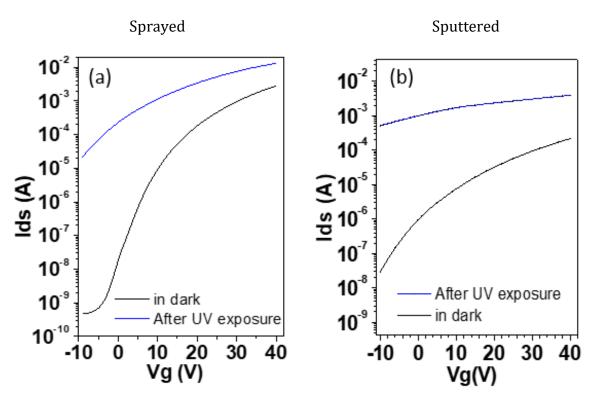

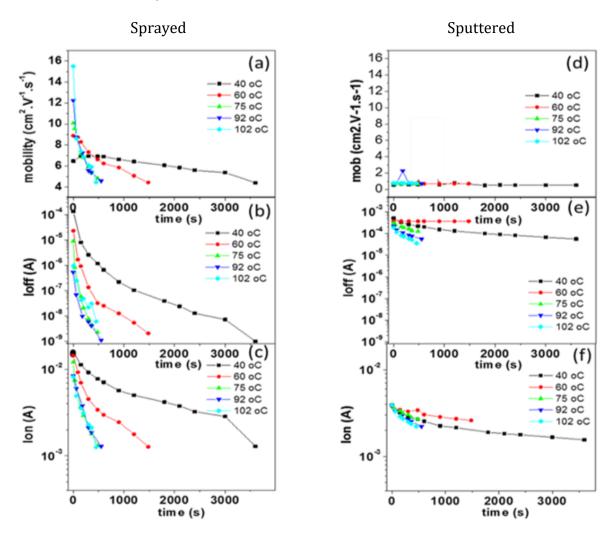

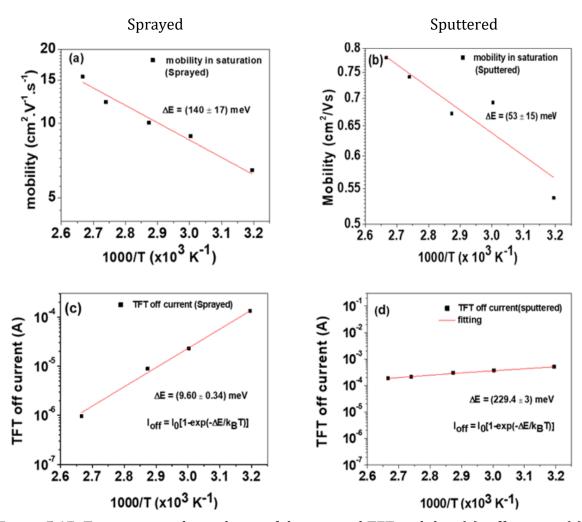

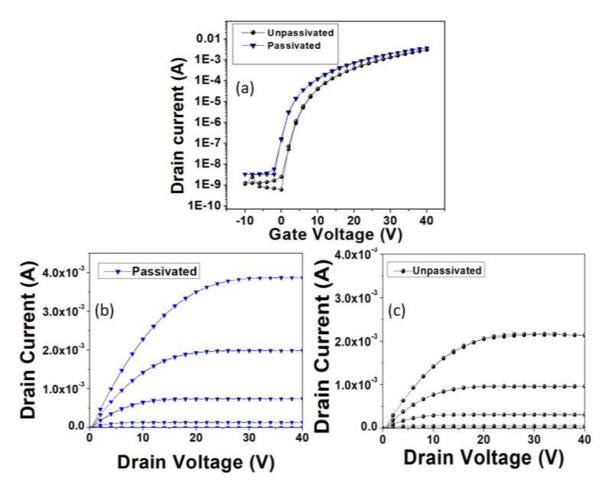

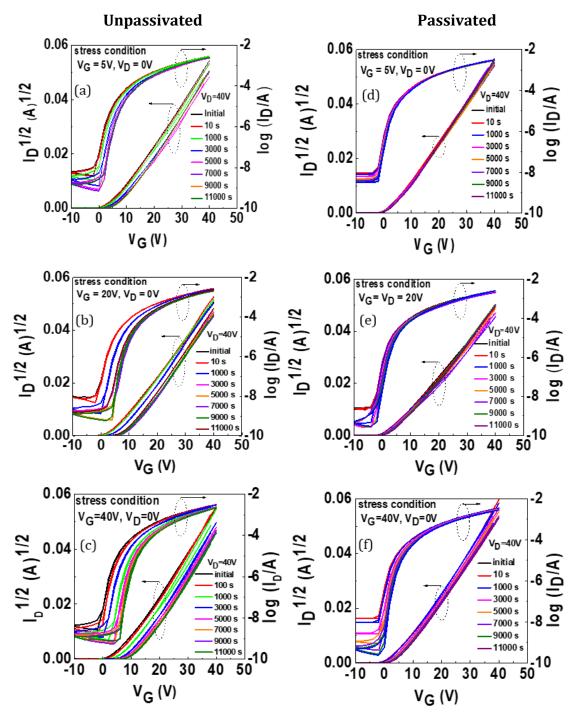

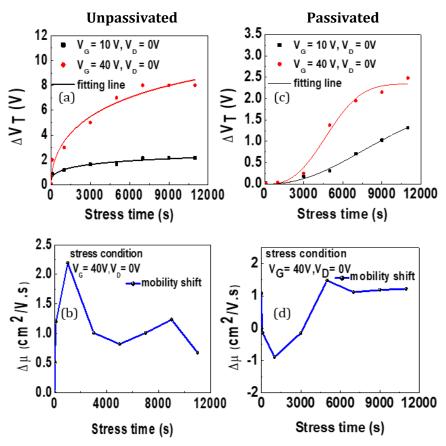

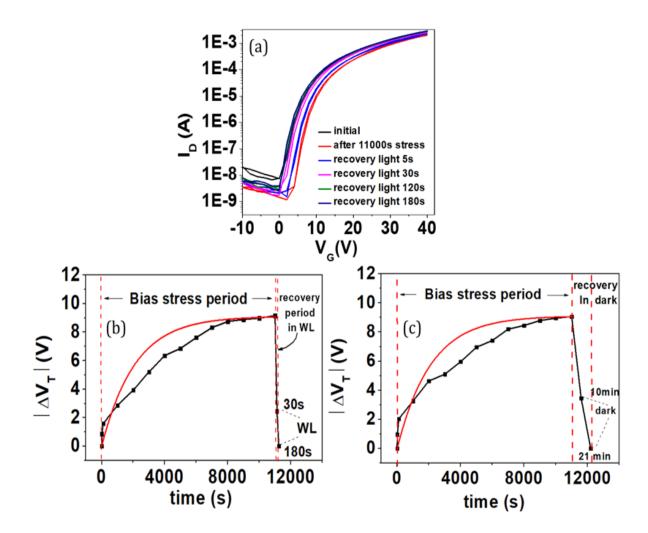

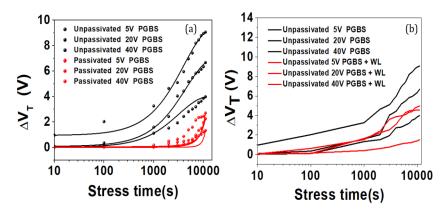

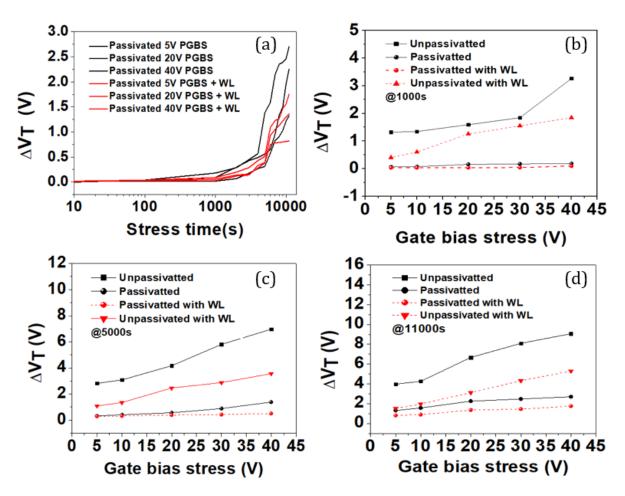

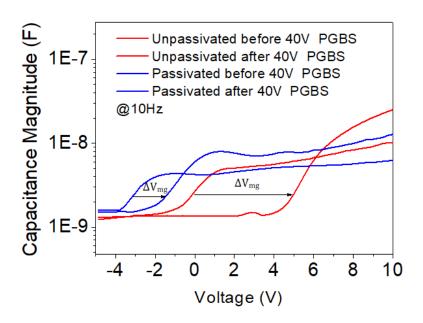

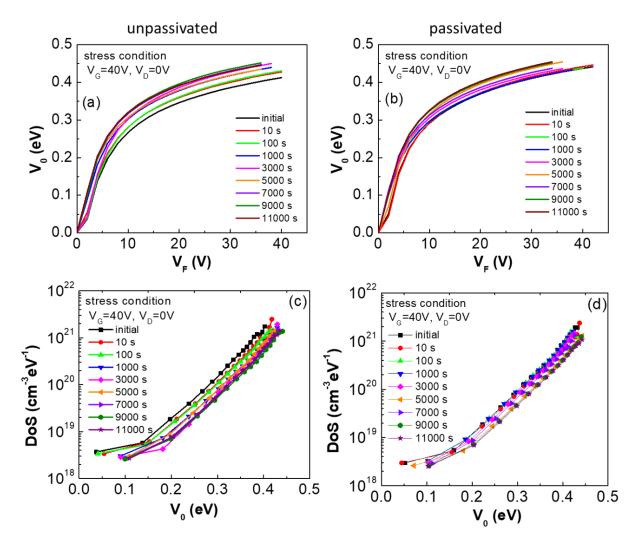

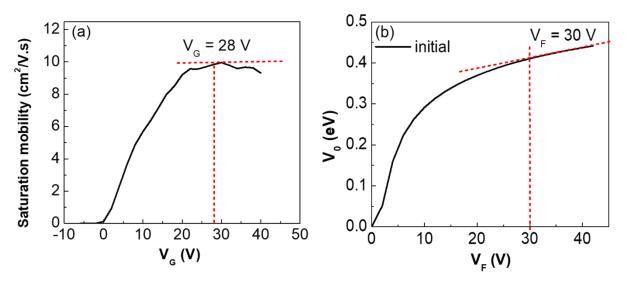

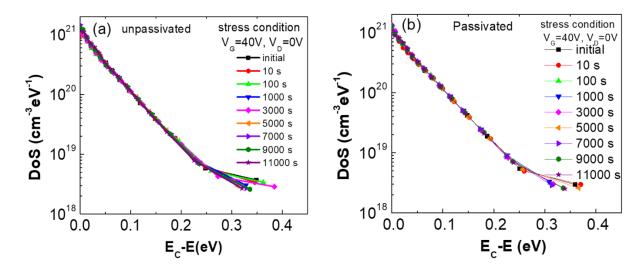

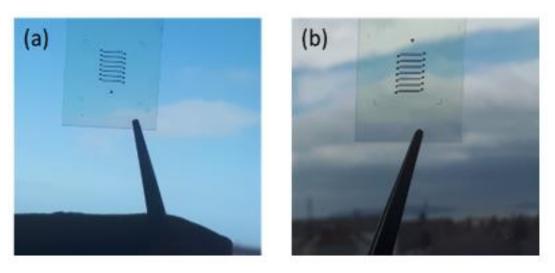

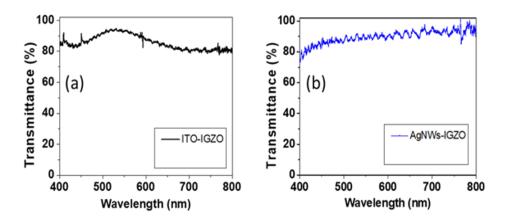

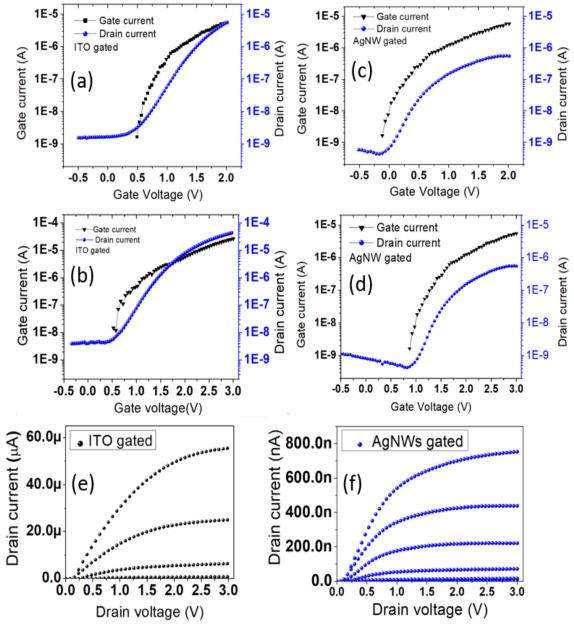

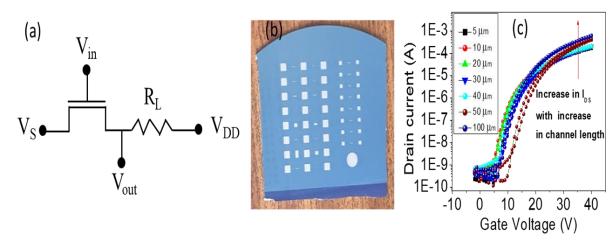

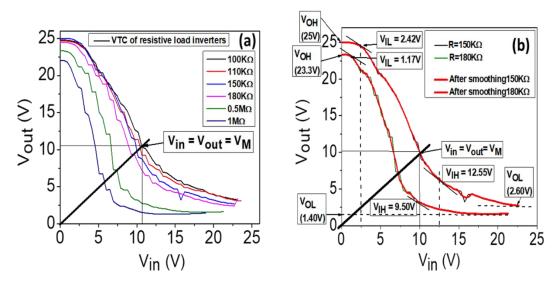

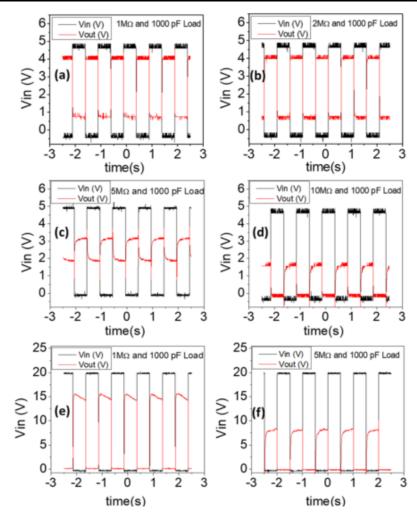

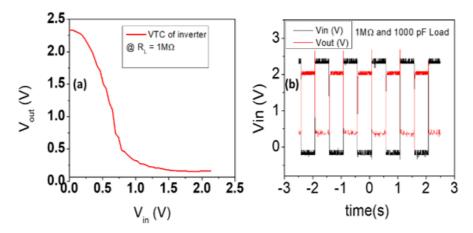

Figure 2.8: (a) Schematic cross-section representation of a MIS capacitor. Energy band diagrams of MIS capacitor as viewed through the gate for different biasing conditions: (b) equilibrium, (c)  $V_{GS} < 0$  V, and (d)  $V_{GS} > 0$  V [166].