This is a repository copy of Large-signal charge control modeling of photoreceivers for applications up to 40 Gb/s.

White Rose Research Online URL for this paper: http://eprints.whiterose.ac.uk/9033/

### Article:

Helme, J.P, Houston, P.A and Tan, C.H (2009) Large-signal charge control modeling of photoreceivers for applications up to 40 Gb/s. IEEE Journal of Quantum Electronics, 45 (7). pp. 833-839. ISSN 0018-9197

https://doi.org/10.1109/JQE.2009.2013127

## Reuse

Unless indicated otherwise, fulltext items are protected by copyright with all rights reserved. The copyright exception in section 29 of the Copyright, Designs and Patents Act 1988 allows the making of a single copy solely for the purpose of non-commercial research or private study within the limits of fair dealing. The publisher or other rights-holder may allow further reproduction and re-use of this version - refer to the White Rose Research Online record for this item. Where records identify the publisher as the copyright holder, users can verify any specific terms of use on the publisher's website.

## **Takedown**

If you consider content in White Rose Research Online to be in breach of UK law, please notify us by emailing eprints@whiterose.ac.uk including the URL of the record and the reason for the withdrawal request.

# Large-Signal Charge Control Modeling of Photoreceivers for Applications up to 40 Gb/s

John P. Helme, Peter A. Houston, and Chee Hing Tan

Abstract—A charge control model was used to simulate the sensitivity and responsivity in a range of photodetector configurations including heterojunction bipolar phototransistors (HPTs), PIN-HBT, and APDs. Our simulations enabled for the first time a direct comparison of the performance between these photodetectors to be made. Simulations have been performed at bit rates from 2 to 40 Gb/s using various combinations of device design parameters (layer thickness, source resistance, and dc base voltage). For a BER = 10<sup>-9</sup> at 40 Gb/s the best sensitivity of approximately -20 dBm was achieved using an optimized APD-HBT configuration, followed by sensitivities of approximately -14 dBm using optimized PIN-HBTs and HPTs. These results were found to agree well with published experimental data.

*Index Terms*—APDs, heterojunction bipolar phototransistors (HBTs), photoreceivers.

## I. INTRODUCTION

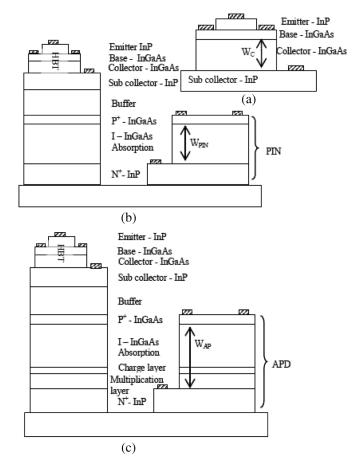

IT-RATES are set to rise to 40 Gb/s in next-generation optical fiber systems and there is a requirement to maximize the sensitivity such that repeater stations can be widely spaced. Devices that may be used as photoreceivers include the APD, PIN diode, metal—semiconductor—metal (MSM) diode, the heterojunction bipolar phototransistor (HPT), erbium-doped fiber amplifier-PIN (EDFA-PIN), and optically controlled MESFET [1]. Of these devices, the HPT, the PIN-HBT, and the APD-HBT are promising candidates because of their built-in gain and relative simplicity. These devices are shown schematically in Fig. 1 and are the subject of this study.

The HPT has the same structure as the HBT, where the BC region is used to absorb the light and the intrinsic gain of the transistor amplifies the signal, eliminating the need for interconnects. The photocurrent is injected directly into the base in an HPT rather than through the base resistance in the case of a PIN-HBT but the HPT has to be relatively large to accommodate the fiber diameter. PIN diodes operate at high speed and are readily compatible with HBT technology. Two integration schemes exist for the PIN-HBT combination. The first is the shared layer scheme where the base–collector (BC) region of the HBT also acts as the i-region for absorption in the PIN [2]–[6]. This design is simpler to implement, requiring a less complex grown structure and a simpler fabrication process [2], and is generally preferred for this reason. However, although the area of each element can be optimized for

Manuscript received October 13, 2008; revised November 11, 2008. Current version published May 28, 2009.

The authors are with the Department of Electronic and Electrical Engineering, University of Sheffield, Sheffield S1 3JD, U.K. (e-mail: j.p. helme@sheffield.ac.uk; p.a.houston@sheffield.ac.uk; c.h.tan@sheffield.ac.uk).

Digital Object Identifier 10.1109/JQE.2009.2013127

Fig. 1. Schematic diagrams of the (a) HPT, (b) separate PIN-HBT, and (c) APD-HBT material structures. The shared layer PIN-HBT is fabricated from the same structure as the HPT, but with two mesas, one of which has the emitter layer removed to form the PIN diode.

speed and fiber coupling efficiency, a compromise between the transit delays and absorption efficiency is required. The second scheme uses separate layer structures for the PIN and the HBTs, allowing the layer structures of both to be independently optimized [7], [8]. Parasitics associated with interconnects [9] are a drawback for both PIN-HBT structures. APDs provide internal gain through the impact ionization process, which is intrinsically noisy in most III–V semiconductors, but work on APDs with thin avalanche regions has allowed the excess noise factor associated with the ionization to be reduced [10]. This has enabled APD-based receivers to achieve high sensitivities [11]–[13]. However, the gain–bandwidth product of current APDs operating at optical communication wavelengths are around 170 GHz at best. Therefore, at 40 Gb/s, only a small improvement in sensitivity is expected for stand-alone APDs.

Although the devices studied here are promising detectors for future high-speed communication systems, no detailed theoretical comparison has been carried out that would enable the choice of the best scheme for set system design parameters to be carried out. Various theoretical models have been presented for both the HPT [14], [15] and the PIN-HBT [16]. However, these models are lacking in that they either neglect often significant transit times or are circuit-based and do not offer the same physical insight as a purely physics-based analytical model. The transistors in this paper are modeled using charge control, together with the effects of the carriers drifting through the depletion regions (treated intrinsically), rather than approximating the transit with a diffusion capacitance as in a circuit model. This modeling is described in more detail in [17] for the HPT where the time-dependent output currents are produced, enabling realistic eye diagrams to be generated, including the effects of noise. In this paper, the modeling methodology is extended to include a PIN-HBT (two configurations) and an APD-HBT combination. This allows the effects of increasing complexity of the receiver from the HPT to a shared layer scheme PIN-HBT, a PIN-HBT with separate PIN and collector layer, and a proposed monolithic APD-HBT structure to be compared. The APD-HBT combination is considered since a hybrid APD-HBT has been shown experimentally to achieve high sensitivity [18]. The APD could be integrated on the same wafer as the HBT if the APD structure is grown first, followed by a buffer layer, and then the HBT layer, as illustrated in Fig. 1. This structure should minimize parasitic effects. The model allows the photodetectors to be directly characterized in terms of sensitivity, responsivity, bit rate, and design parameters. We compare three simple schemes (HPT, PIN-HBT, and APD-HBT), each involving only one amplifying transistor but all could be included with more complicated transimpedance amplifiers to improve the performance of the detector [2]. The sensitivities of the devices are calculated at different frequencies and a direct comparison of optimized designs for different applications is achieved.

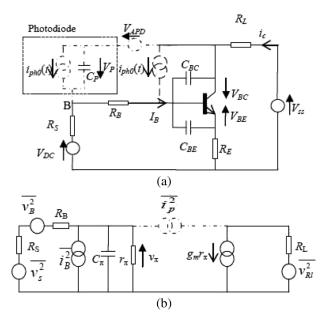

# II. CHARGE CONTROL MODELING OF HPT AND PIN-HBT

The equivalent circuit diagrams of the HPT and the diode-HBT are shown in Fig. 2(a), where the dashed lines represent the connections inherent in the HPT and the dashed—dot lines are interconnects between the diode and the HBT.  $V_{\rm APD}$  is an optional extra voltage source for controlling the avalanche gain in the APD. The avalanche duration in the APD can become significant at higher avalanche gains, and therefore, a mean current impulse response is included in the modeling. The BC region of the HPT is essentially a reverse-biased PIN diode, thus, the form of the photocurrent  $i_{\rm ph0}(t)$  is the same in the HPT and PIN-HBT and is given in [17].  $i_{\rm ph0}(t)$  includes

Fig. 2. Circuit diagrams of the HPT and the PIN-HBT. (a) Large-signal charge control model and (b) small-signal noise model. Circuitry only applying to the HPT is shown in dashed lines and that only to the PIN-HBT is shown in dashed—dot lines. Solid lines are common to both devices.

the drift and diffusion currents in the depletion region but excludes the charging of any geometric capacitance, as described later in Section III. In the APD-HBT,  $i_{\rm ph0}(t)$  is calculated by convolving the impulse response [19] with the input bit train.

The base current must supply any transient charges in the transistor, i.e., the charge on the base-emitter (BE) and BC junction capacitances and the positive charge required to balance out the excess electron charge in the base and collector regions. The base bias considered here is a voltage source  $V_{\rm dc}$  and resistor  $R_S$  as shown in Fig. 2(a). Variation of these parameters allows for a tradeoff between effective gain and speed, resulting in improved sensitivity performance at high bit rates over a current source biased device [17]. Following the procedure outlined in [17], expressions for the collector current can be extended to include the photodiode as in Fig. 2(a), as shown at the bottom of the page, where  $I_S$  is the saturation current of the BE diode,  $C_{\mathrm{BC}}$  and  $C_{\mathrm{BE}}$  are the base–collector and base–emitter junction capacitance, respectively,  $V_{\rm dc}$  and  $V_{\rm BE}$  are the base bias voltage and base-emitter junction voltage, respectively, and  $R_S$ ,  $R_B$ ,  $R_E$ , and  $R_L$  are the source, base, emitter, and load resistances, respectively.  $i'_{\rm ph0}$  is the first differential of the photocurrent with respect to time,  $R_{SUM} = R_B + R_S + R_E$ ,  $R_{Eff} = R_L + k_1 R_E$ , and  $k_1 = (R_B + R_S)/R_{SUM}$ .  $\beta$  is the dc gain given by  $\tau_e/\tau_B$ , where  $au_e$  is the minority electron lifetime in the base and  $au_B$ is the base transit time. k is the Boltzmann constant, T is the absolute temperature, and e is the electronic charge. This is a

$$\frac{di_{c}}{dt}\Big|_{\text{HPT}} = \frac{\beta \frac{V_{\text{dc}} - V_{\text{BE}} + (R_{B} + R_{S})i_{\text{ph0}}(t) + C_{\text{BC}}R_{E}(R_{B} + R_{S})i'_{\text{ph0}}(t)}{R_{\text{SUM}}} - \left(\frac{\beta R_{E}}{R_{\text{SUM}}} + 1\right)i_{c}}{\tau_{e} + \frac{\beta \tau_{\text{ce}}}{2} + \beta R_{\text{Eff}}C_{\text{BC}} + \beta \frac{kT}{e(i_{c} + I_{S})}(C_{\text{BE}} + k_{1}C_{\text{BC}})} \tag{1}$$

key expression similar to (10) in [17] with the addition of  $R_S$  in the biasing circuit and including a time-varying photocurrent for completeness.

The increased parasitics associated with the integration of PIN-HBTs and APD-HBTs have not been included since they are specific to individual designs, and therefore, cannot be accurately calculated. From a performance comparison point of view, the intrinsic (neglecting interconnect effects) performance of the three photodetection schemes is of interest.

In the circuits shown in Fig. 2(a), it is assumed that the collector current flows though a load resistor without any further amplification, but the form of the current derived here may be applied to further amplification stages, which can be used to improve the performance of the receiver unit as described in [2], [8], [16], and [21].

## III. TRANSIENT PHOTOCURRENT

In the HPT and PIN diode, the light is absorbed in a decaying exponential throughout the collector (i-region). The electrons and holes are separated by the electric field in the absorption region, with the electrons drifting to the n-side and holes to the p-side. This changing distribution of electrons and holes changes the electric field in the collector, causing a displacement current that can be accounted for by using the Ramo–Shockley theorem. Considering illumination from the p-side of the PIN (i.e., through the emitter of the HPT) and summing the drift current due to the electrons and holes, and this displacement current gives the total photocurrent as

$$i_{\rm ph}(t) = i_{\rm ph0}(t) - C_{\rm jn} \frac{dV_{\rm jn}}{dt}$$

(2)

where  $i_{\rm ph0}(t)$  is the time-dependent primary photocurrent that is calculated according to Ramo–Shockley. The second term in (2) is the displacement current that occurs due to the changing junction voltage, equivalent to the charging of the junction capacitance.

The light in an APD is absorbed as a decaying exponential in the absorption region and the photocurrent from this is then amplified by avalanche multiplication in the avalanche region. Increased avalanche gain extends the transit effects and are included in the APD impulse response, calculated in [19]. To find the photocurrent,  $i_{\rm ph0}(t)$ , for the APD, the impulse response is convolved with a rectangular pulse train. The APD impulse response is a weighted mean of the impulse response of each carrier. The effects of deadspace on the excess noise factor and the effective transit times in the APD are included. In the calculation of the APD impulse response, it is assumed that the electrons and holes travel at their respective saturation velocities, but their differing ionization coefficients and ionization threshold energies are taken into account.

## IV. Noise

The sources of noise in the photoreceivers are the thermal noise from the load resistor, source resistor, and the base resistance, and the shot noise due to the collector and base currents in the transistor [14]. An additional source of shot noise in the PIN-HBT and APD-HBT occurs as the photocurrent flows across the junction in the diode. The excess noise factor of the

APD is calculated according to [22]. The shot noise from the APD is increased by the excess noise factor and the avalanche multiplication relative to the shot noise in the PIN diode, before being amplified by the HBT. The HBT circuit acts as a low-pass filter to the noise and the small-signal noise analysis by Liu [20] is used. The expressions derived in [17] for the base and load thermal noise and the base and collector current shot noise are the same for the diode-HBT receiver. At the frequencies of interest, the diode capacitance has a negligible effect on the small-signal frequency response and can be neglected. The source resistor is in series with the base resistance, and therefore, the response to the source noise is the same as the base thermal noise. The resultant equivalent noise circuit is shown in Fig. 2(b). The diode shot noise must be included in the diode-HBT and is given by

$$\overline{i_c^2}\Big|_{\text{diode-HBT}} = \overline{i_c^2}\Big|_{\text{HPT}} + 2eFMi_{\text{ph}0}B_n$$

(3)

where  $\overline{i_c^2}|_{\mathrm{HPT}}$  is similar to that from [17], F is the noise factor, M is the avalanche multiplication, and  $B_n$  is the noise bandwidth. An additive Gaussian noise distribution is assumed [23], which is superimposed on the calculated signal in order to calculate the bit error rate (BER) as described in [17].

#### V. RESULTS AND DISCUSSION

We modeled InP/InGaAs devices here, but the model could be applied to other materials by changing the material parameters. The output characteristics for the photodetectors considered include bit rate, sensitivity, and responsivity. The material systems of the different schemes considered are shown in Fig. 1.

The diameter of the photodetector portion of the receiver is important since it affects the fiber coupling efficiency and capacitance in the device. This is particularly important in the HPT since the forward-biased base-emitter junction capacitance contributes significantly to the delays. The tradeoff between coupling efficiency and capacitance is somewhat removed in the diode-HBT since the coupling of light is into the separate reverse-biased photodiode, allowing the HBT junction capacitances to be reduced. This independence of transistor capacitance and optical coupling efficiency is a major advantage of the PIN-HBT over the HPT, and offers greater design flexibility.

The diameters of the optical window PIN diode, APD and the HPT are taken as 9  $\mu$ m, giving a diode or an emitter area of 63.6  $\mu$ m². The base–collector diameter has been set at 8  $\mu$ m in the HPT. An emitter area of 5  $\mu$ m² and the base–collector junction area of 10  $\mu$ m² are used in the separate HBTs. A minimum lateral dimension of 1  $\mu$ m is assumed in the HBT, i.e., an emitter width of 1  $\mu$ m, and the spacing between the base contact and the emitter edge of 1  $\mu$ m is used in calculating the base resistance. The base resistance is calculated as the resistance of the base material between the base contact and the emitter edge. It is a function of the base thickness that is used to define the dc gain  $\beta$ . The base–emitter bias source resistance  $R_S = 100~\Omega$  unless otherwise specified and the load is 50  $\Omega$ .

The receivers are characterized by sensitivity and responsivity. The sensitivity is defined as the minimum power of the light that passes though the absorption region to achieve BER =

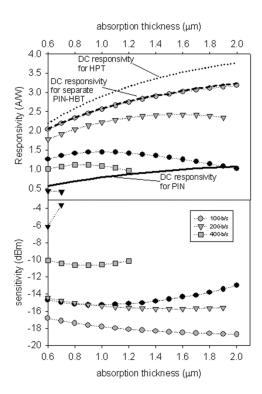

Fig. 3. (a) Responsivity and (b) sensitivity as a function of dc base–emitter voltage,  $V_{\rm dc}$ . Calculated values at 10 Gb/s (circles), 20 Gb/s (triangles), and 40 Gb/s (squares) for HPT (solid symbols), shared PIN-HBT (open symbols), and separate PIN-HBT (gray symbols) are shown.

$10^{-9}$ . Intersymbol interference was not included in our analysis. In order to account for coupling and other external limitations, the optical power applied to the device is given by  $P_0/\eta_{\rm ext}$ , where  $\eta_{\rm ext}$  is the external efficiency. The frequency-dependent responsivity is defined by the minimum change in collector current  $(\Delta i_c)$ , which indicates a digital "1" divided by the input power. The sensitivity has a direct bearing on repeater station spacing in a fiber optic system. The responsivity affects the voltage that appears across the load resistance that will be applied to subsequent electronics.

The effect of the base-emitter dc bias voltage on the sensitivity and responsivity is shown in Fig. 3 for transistors with  $\beta = 10$  and absorption thickness  $W = 0.6 \,\mu\text{m}$ . In the HPT and the shared layer PIN-HBT, the latter defines the collector thickness, but in the separate PIN-HBT, the collector thickness has been reduced to  $0.2 \mu m$  to reduce the collector transit delay [the second term in the denominator of (1)]. Increasing the dc bias voltage increases the collector current that reduces the emitter dynamic resistance. However, as the latter is reduced, the effective gain is increased since more primary photocurrent flows into the base of the transistor. This has the effect of increasing the overall charging delay [17], leading to a closure of the eye and a reduction in the responsivity if charging delays are significant with respect to the bit rate. This can be seen in Fig. 3(a), where the responsivity initially improves with increasing gain (controlled by  $V_{\rm dc}$ ) for the two lower bit rates, but then decreases as the charging delays become important. The increasing gain also initially improves the sensitivity, but it too starts to degrade [Fig. 3(b)]. The factors contributing to the degradation of the sensitivity are the increased charging delays, an increase in

Fig. 4. (a) Responsivity and (b) sensitivity as a function of absorption thickness for the HPT (solid symbols) and the separate PIN-HBT (gray symbols) at bit rates of 10 Gb/s (circles), 20 Gb/s (triangles), and 40 Gb/s (squares). The maximum responsivity from each device and that of a PIN diode are represented by lines.

the noise due to a reduced  $r_\pi$ , and an increase in the base shot noise with larger base current. The complex interplay between these many factors makes it difficult to explain all the trends in Fig. 3 in a simple fashion. However, in the two PIN-HBT configurations, the reduced HBT areas possible compared to the HPT mean that the capacitance delays play a smaller part in the degradation of the device performance. Optimizing the collector thickness for reduced collector transit delay without compromising the capacitor charging delay in the separate PIN-HBT leads to the improved performance compared to the HPT alone and the shared PIN-HBT device.

Increasing  $\beta$  in the model by reducing the base thickness, while keeping the collector current constant, leads to some degradation in the sensitivity due to increasing delays from the Miller effect. The dc responsivity does not increase linearly with  $\beta$  since the effective gain is determined by the bias conditions as well as  $\beta$ .

One of the most important factors affecting the performance of the HPT and PIN-HBT is the absorption thickness. The responsivity and sensitivity are plotted as a function of absorption thickness in Fig. 4(a) and (b), respectively, for the HPT (absorption thickness = collector thickness) and the separate layer PIN-HBT (absorption thickness = PIN I-region) for a collector current of 1 mA. The tradeoffs inherent in the choice of collector thickness of the HPT and shared layer PIN-HBT are increasing its thickness to increase the internal quantum efficiency and reduce the base–collector capacitance on the one hand, versus reducing the thickness to minimize the collector transit times on the other hand. To preserve clarity, only the HPT and separate

PIN-HBT devices are compared in Fig. 4. The collector thickness in the HBT of the separate PIN-HBT has been set at  $0.2 \mu m$ as a compromise between the capacitance charging delays and the collector transit delay in the HBT. An optimum absorption thickness is evident for some of the curves in Fig. 4(a) and (b). The optimum thickness is smaller for the HPT compared to the separate PIN-HBT since the collector transit delays rapidly become dominant in the HPT. In the separate PIN-HBT, the sensitivity and responsivity only start to degrade when the transit delays in the PIN diode are significant with respect to the inverse bit rate. For comparison, the calculated dc responsivity for the HPT, separate PIN-HBT, and a single PIN diode are shown in Fig. 4(a). The dc responsivities were calculated using  $R = e/hv(1 - \exp(-\alpha W))$  applied to the absorption regions in each. At 40 Gb/s the responsivity of the separate PIN-HBT is close to the dc value for a PIN diode. At 10 and 20 Gb/s, the responsivity of the separate PIN-HBT is much greater than the PIN alone, while the HPT has higher and lower responsivity values at 10 and 20 Gb/s, respectively, compared to the value for the PIN diode. In the HPT, the biasing condition of 1 mA leads to large capacitance delay that prevents the operation of the HPT at 40 Gb/s. Hence, no results for HPTs at 40 Gb/s are shown in Fig. 4.

The most complicated structure considered here is the APD-HBT [Fig. 1(c)]. Alongside the factors discussed before for the HPT and separate PIN-HBT, the avalanche gain in the APD can be used to optimize the performance of an APD-HBT receiver. In Fig. 5, the avalanche gain is varied by changing the applied APD bias. The HBT has a collector thickness of 0.2  $\mu$ m and  $\beta = 10$ . The modeled InGaAs/AlInAs APD has an absorption layer thickness of 0.6  $\mu$ m and an avalanche region of 150 nm. The charge layer, which is 50 nm thick and doped at  $5 \times 10^{17}$  cm<sup>-3</sup>, is designed to ensure that the high field in the avalanche regions does not extend into the absorption region. The APD structure was chosen such that tunneling current is negligible and the noise from the APD is dominated by the multiplied photocurrent shot noise. This enables the avalanche gain and excess noise factor to be well controlled. The responsivity and sensitivity as a function of avalanche gain have been plotted in Fig. 5(a) and (b), respectively, using the model described in Section III. Initial improvement in both sensitivity and responsivity of the receiver with increasing avalanche gain can be clearly seen. The optimum values of avalanche gain occur at a point where the diode transit times and excess avalanche noise start to close the eye. The APD avalanche duration increases with increased avalanche gain and dominates the delay at lower gain for the higher frequencies. Consequently, the responsivity that can be achieved at 40 Gb/s is lower than the maximum (dc) at 10 and 20 Gb/s, but is still larger than the responsivity achieved by the separate layer PIN-HBT at 40 Gb/s (shown by the solid symbols in Fig. 5 at gain = 1).

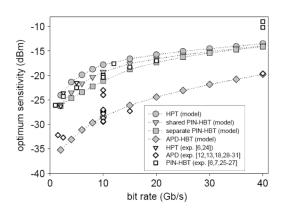

To optimize and compare all the devices considered, simulations were performed at bit rates from 2 to 40 Gb/s and the design parameters of layer thickness, source resistance, and dc base voltage have been varied. The avalanche multiplication, adjusted by the APD supply voltage  $V_{\rm APD}$  is a further variable used in the optimization of the APD-HBT. The input power is adjusted until a BER of  $10^{-9}$  is achieved, and this is then

Fig. 5 APD-HBT (a) receiver responsivity and (b) sensitivity as a function of avalanche gain in the APD for bit rates of 10 Gb/s, 20 Gb/s, and 40 Gb/s. The solid symbols are PIN-HBT receiver simulations which can be thought of as an APD-HBT with an avalanche gain of unity.

taken to be the sensitivity. The device structure that achieves the best sensitivity at a given bit rate is taken to be the optimum device and the line plotted in Fig. 6 is the locus of these optimums. Thus, each point at a given bit rate is a different optimized device. The separate layer PIN-HBT achieves sensitivities of -21.1 and -14.1 dBm, which represents 2.3 and 0.6 dB improvement over the HPT, for bit rates of 10 and 40 Gb/s, respectively. This improvement is due to the reduced collector transit times in the HBT which is achieved without loss of internal efficiency, and the reduced capacitance of the separate transistor. The shared layer PIN-HBT has no real advantage over the HPT considered here. At the highest and lowest bit rates considered, the photoreceivers have similar sensitivity performance. At low bit rates, the optimum absorption thickness for each detector is large (limited to a maximum of 2  $\mu$ m in the optimization process). Since the switching period is large compared with the delay times in each of the devices at low bit rates, the responsivity and sensitivity are not degraded by the delays. At the highest bit rates, the optimum gain is reduced in all three devices; therefore, each starts to look more like a PIN diode and their response is similar. At bit rates around 10 Gb/s, the collector transit delays are significant with respect to the bit period. There is, therefore, a strong tradeoff between collector thickness and responsivity/sensitivity in the HPT and shared layer PIN-HBT. The PIN diode thickness can be kept large, increasing the responsivity and giving higher sensitivity, in the separate layer PIN-HBT at these bit rates. The PIN-HBT has the advantage that the photodetector area can be increased to ease fiber alignment with less degradation of the sensitivity than in the HPT. If it is of interest to increase responsivity at the high bit

Fig. 6. Calculated optimum sensitivities for HPT, shared layer PIN-HBT, separate PIN-HBT, and APD-HBT as a function of bit rate are represented by gray symbols. Experimental data for HPTs, PIN-HBTs, and APD-based receivers are represented by open symbols.

rates, e.g., through increasing effective gain using bias, it is the separate layer PIN-HBT whose sensitivity will degrade least.

The APD-HBT receiver has a clear advantage over the other receivers, achieving -28.7 and -19.9 dBm (translates to >140 GHz gain-bandwidth product) at 10 and 40 Gb/s, respectively. The decrease in the difference of the sensitivity of the APD receiver compared to the other devices at high speeds is expected since the optimum avalanche gain is decreased due to avalanche duration delays, and therefore, the APD begins to behave more like a PIN diode. At speeds greater than 40 Gb/s, Fig. 6 indicates that the APD-HBT performance will approach that of the PIN-HBT since the optimum avalanche gain will tend toward one.

Data from [6] and [24] for the HPT, [6], [7], and [25]–[27] for the PIN-HBT, and [12], [13], [18], [28]–[31] for the APD-HBT have been plotted to compare with experimental data. The differences between calculation and experimental data up to 20 Gb/s are within  $\pm 1$  dB for the HPT and PIN-HBT receivers, which seems reasonable given that measured sensitivity values can vary by as much as  $\pm 1$  dB between identical channels of a PIN-HBT photoreceiver in [32]. At 40 Gb/s, parasitics due to interconnects between the PIN diode and the HBT, which have been neglected here, are likely to degrade the experimental results compared to the modeling.

The measured sensitivities of hybrid APD-based photoreceivers from [12], [13], [18], and [28]–[31] are plotted and show a good fit to the simulated line. It should be noted that a waveguide APD, which removes the tradeoff between transit times and absorption efficiency, is used to achieve the record result of –19 dBm at 40 Gb/s [12]. Furthermore, the circuitry used in the photodetectors above 10 Gb/s includes transimpedance amplifiers, which improve the sensitivity of the photodetectors [21] but have not been included here.

We have also optimized these photodetectors under more stringent conditions of BER =  $10^{-10}$  and BER =  $10^{-12}$ . The predicted optimum sensitivities achieved at 40 Gb/s are summarized in Table I. Under these conditions, the APD-HBT offers the highest sensitivities of -19.5 and -19 dBm, while the HPT has the lowest sensitivities of -13.2 and -12.8 dBm, for BER of  $10^{-10}$  and  $10^{-12}$ , respectively.

TABLE I

PREDICTED OPTIMUM SENSITIVITIES OF VARIOUS PHOTODETECTORS FOR THE

TWO HIGHER BERS

| Device                 | BER=10 <sup>-10</sup> | BER=10 <sup>-12</sup> |

|------------------------|-----------------------|-----------------------|

| HPT                    | -13.2 dBm             | -12.8 dBm             |

| Shared-Layer PIN-HBT   | -13.7 dBm             | -13.3 dBm             |

| Separate-Layer PIN-HBT | -13.9 dBm             | -13.4 dBm             |

| APD-HBT                | -19.5 dBm             | -19.0 dBm             |

### VI. CONCLUSION

Large-signal charge control models based on the same theory for the HPT, the PIN-HBT, and the APD-HBT have been developed. These photoreceivers have been optimized in terms of sensitivity, responsivity, and design parameters, which enable the schemes to be compared directly for the first time.

The HPT and PIN-HBT are very similar devices in both operation and fabrication, including a similar layer structure. One disadvantage of the PIN-HBT is that it is a slightly more complicated photodetector than the HPT because of the need for two mesas and the interconnects between them. The parasitic capacitance and inductance associated with the interconnects have not been included in this modeling. The advantage of the separate mesas is the decoupling of the capacitances in the transistor (which affect the speed) and the area of the photoreceiver (which affects the coupling efficiency). The HPT is simpler, being only one mesa, but the need to minimize area to reduce capacitance is limited by the need for efficient optical coupling. For the active detection area considered here (63.6  $\mu$ m<sup>2</sup>), there is little to be gained from using the shared layer PIN-HBT. Using a separate layer for the PIN diode to the collector removes the tradeoff between internal efficiency and collector transit delays. The APD-HBT receiver is the best performer, but at the expense of a more complicated structure. Optimizing the growth of such a structure could be problematic and the yield may be low. However, the increased sensitivity afforded by the APD suggests that APD-based receivers will be key to next-generation systems.

Optimum sensitivities of -13.5 dBm for the HPT, -14.1 dBm for the separate layer PIN-HBT, and -19.9 dBm for the APD-HBT have been calculated for single transistor amplifier receivers operating at 40 Gb/s (for BER =  $10^{-9}$ ) using a single pass of light. This trend remains when calculations were repeated for BER =  $10^{-10}$  and  $10^{-12}$  showing that the APD-HBT offers the highest sensitivities as the bit rate increases.

#### REFERENCES

- P. Chakrabarti and V. Rajamani, "A proposed OEIC receiver using MESFET photodetector," *J. Lightw. Technol.*, vol. 17, no. 4, pp. 659–668, Apr. 1999.

- [2] N. R. Das and A. J. Deen, "On the performance analysis and design of an integrated front-end PIN/HBT photoreceiver," *IEEE J. Quantum Electron.*, vol. 40, no. 1, pp. 78–91, Jan. 2004.

- [3] D. Huber, R. Bauknecht, C. Bergamaschi, M. Bitter, A. Huber, T. Morf, A. Neiger, M. Rohner, I. Schnyder, V. Schwarz, and H. Jackel, "InP–In-GaAs single HBT technology for photoreceiver OEIC's at 40 Gb/s and beyond," J. Lightw. Technol., vol. 18, no. 7, pp. 992–1000, Jul. 2000.

- [4] E. Sano, K. Sano, T. Otsuji, K. Kurishima, and S. Yamahata, "Ultra-high speed, low power monolithic photoreceiver using InP/In-GaAs double-heterojunction bipolar transistors," *Electron. Lett.*, vol. 33, pp. 1047–1048, 1997.

- [5] S. Chandrasekhar, M. K. Hoppe, A. G. Dentai, C. H. Joyner, and G. J. Qua, "Demonstration of enhanced performance of an InP InGaAs heterojunction phototransistor with a base terminal," *IEEE Electron Device Lett.*, vol. 12, no. 10, pp. 550–552, Oct. 1991.

- [6] S. Chandrasekhar, L. M. Lunardi, A. H. Gnauck, R. A. Hamm, and G. J. Qua, "High-speed monolithic P-I-N/HBT and HPT/HBT photoreceivers implemented with simple phototransistor structure," *IEEE Photon. Technol. Lett.*, vol. 5, no. 11, pp. 1316–1318, Nov. 1993.

- [7] L. M. Lunardi, S. Chandrasekhar, A. H. Gnauck, C. A. Burrus, R. A. Hamm, J. W. Sulhoff, and J. L. Zyskind, "A 12-Gb/s high-performance, high-sensitivity monolithic P-I- N/HBT photoreceiver module for long-wavelength transmission-systems," *IEEE Photon. Technol. Lett.*, vol. 7, no. 2, pp. 182–184, Feb. 1995.

- [8] S. Chandrasekhar, L. M. Lunardi, A. H. Gnauck, D. Ritter, R. A. Hamm, M. B. Panish, and G. J. Qua, "A 10 Gbit/s OEIC photoreceiver using InP/InGaAs heterojunction bipolar-transistors," *Electron. Lett.*, vol. 28, pp. 466–468, 1992.

- [9] P. Bhattacharya, Semiconductor Optoelectronic Devices, 2nd ed. Upper Saddle River, NJ: Prentice Hall, 1997.

- [10] K. F. Li, D. S. Ong, J. P. R. David, G. J. Rees, R. C. Tozer, P. N. Robson, and R. Grey, "Avalanche multiplication noise characteristics in thin GaAs p(+) i-n(+) diodes," *IEEE Trans. Electron Devices*, vol. 45, no. 10, pp. 2102–2107, Oct. 1998.

- [11] H. Matsuda, A. Miura, H. Irie, S. Tanaka, K. Ito, S. Fujisaki, T. Toyonaka, H. Takahashi, H. Chiba, S. Irikura, R. Takeyari, and T. Harada, "High-sensitivity and wide-dynamic-range 10 Gbit/s APD/preamplifier optical receiver module," *Electron. Lett.*, vol. 38, pp. 650–651, 2002

- [12] T. Torikai, T. Nakata, T. Kato, and K. Makita, "40-Gbps waveguide avalanche photodiodes," presented at the presented at the Opt. Fiber Commun. Conf., Anaheim, CA, 2005, unpublished.

- [13] B. F. Levine, J. A. Valdmanis, R. N. Sacks, M. Jazwiecki, and J. H. Meier, "-29 dBm sensitivity, InAIAs APD-based receiver for 10 Gb/s Long-Haul (LR-2) applications," in *Proc. Opt. Fiber Commun. Conf.*, 2005, vol. 5, p. 3.

- [14] J. C. Campbell, "Phototransistors for lightwave communications," Semiconductors and Semimetals, vol. 22, pp. 389–447, 1985.

- [15] R. A. Milano, P. D. Dapkus, and G. E. Stillman, "An analysis of the performance of heterojunction phototransistors for fiber optic communications," *IEEE Trans. Electron Devices*, vol. 29, no. 2, pp. 266–274, Feb. 1982.

- [16] K. H. Yan, A. L. Gutierrez-Aitken, X. K. Zhang, G. I. Haddad, and P. Bhattacharya, "Design, modeling, and characterization of monolithically integrated InP-based (1.55 μm) high-speed (24 Gb/s) p-i-n/HBT front-end photoreceivers," *J. Lightw. Technol.*, vol. 14, no. 8, pp. 1831–1839, Aug. 1996.

- [17] J. P. Helme and P. A. Houston, "Analytical modeling of speed response of heterojunction bipolar phototransistors," *J. Lightw. Technol.*, vol. 25, no. 5, pp. 1247–1255, May 2007.

- [18] H. Matsuda, A. Miura, Y. Okamura, H. Irie, K. Ito, T. Toyonaka, H. Takahashi, and T. Harada, "High performance of 10-Gb/s APD/preamplifier optical-receiver module with compact size," *IEEE Photon. Technol. Lett.*, vol. 15, no. 2, pp. 278–280, Feb. 2003.

- [19] C. H. Tan, P. J. Hambleton, J. P. R. David, R. C. Tozer, and G. J. Rees, "Calculation of APD impulse response using a space- and time-dependent ionization probability distribution function," *J. Lightw. Technol.*, vol. 21, no. 1, pp. 155–159, Jan. 2003.

- [20] W. Liu, Handbook of Heterojunction Bipolar Transistors. New York: Wiley Interscience, 1998.

- [21] Y. Baeyens, G. Georgiou, J. S. Weiner, A. Leven, V. Houtsma, P. Paschke, Q. Lee, R. F. Kopf, Y. Yang, L. Chua, C. Chen, C. T. Liu, and Y. K. Chen, "InP D-HBT ICs for 40-Gb/s and higher bitrate lightwave tranceivers," *IEEE J. Solid-State Circuits*, vol. 37, no. 9, pp. 1152–1159, Sep. 2002.

- [22] M. M. Hayat, B. E. A. Saleh, and M. C. Teich, "Effect of dead space on gain and noise of double-carrier-multiplication avalanche photodiodes," *IEEE Trans. Electron Devices*, vol. 39, no. 3, pp. 546–552, Mar. 1992

- [23] J. Gowar, Optical Communication Systems, 2nd ed. London, U.K.: Prentice-Hall, 1993.

- [24] S. Chandrasekhar, A. H. Gnauck, R. A. Hamm, and G. J. Qua, "The phototransistor revisited—All-bipolar monolithic photoreceiver at 2 Gb/s with high-sensitivity," *IEEE Trans. Electron Devices*, vol. 39, no. 11, pp. 2677–2678, Nov. 1992.

- [25] S. Chandrasekhar, B. C. Johnson, M. Bonnemason, E. Tokumitsu, A. H. Gnauck, A. G. Dentai, C. H. Joyner, J. S. Perino, G. J. Qua, and E. M. Monberg, "An InP InGaAs P-I-N HBT monolithic transimpedance photoreceiver," *IEEE Photon. Technol. Lett.*, vol. 2, no. 7, pp. 505–506, Jul. 1990.

- [26] L. M. Lunardi, S. Chandrasekhar, A. H. Gnauck, C. A. Burrus, and R. A. Hamm, "20-Gb/s monolithic P-I-N/HBT photoreceiver module for 1.55-mu-m applications," *IEEE Photon. Technol. Lett.*, vol. 7, no. 10, pp. 1201–1203, Oct. 1995.

- [27] R. Vetury, I. Gontijo, Y. Z. Liu, K. Krishnamurthy, R. Pullela, and M. J. Rodwell, "High sensitivity and wide-dynamic-range optical receiver for 40 Gbit/s optical communication networks," *Electron. Lett.*, vol. 39, pp. 91–92, 2003.

- [28] H. Hamano, T. Yamamoto, Y. Nishizawa, Y. Oikawa, H. Kuwatsuka, A. Tahara, K. Suzuki, and A. Nishimura, "10 Gbit/s optical front end using si-bipolar preamplifier IC, flipchip APD, and slant-end fiber," *Electron. Lett.*, vol. 27, pp. 1602–1605, 1991.

- [29] Y. Miyamoto, K. Hagimoto, and T. Kagawa, "A 10 Gb/s high-sensitivity optical receiver using an InGaAs-InAlAs superlattice APD at 1.3-mu-m 1.5-mu-m," *IEEE Photon. Technol. Lett.*, vol. 3, no. 4, pp. 372–374, Apr. 1991.

- [30] V. Rajamani and P. Chakrabarti, "A proposed ultra low-noise optical receiver for 1.55 mu m applications," *Opt. Quantum Electron.*, vol. 35, pp. 195–209, 2003.

- [31] E. M. Kimber, B. L. Patel, I. Hardcastle, and A. Hadjiifotiou, "High-performance 10 Gbit/s PIN-FET optical receiver," *Electron. Lett.*, vol. 28, pp. 120–122, 1992.

- [32] S. Chandrasekhar, L. D. Garrett, L. M. Lunardi, A. G. Dentai, C. A. Burrus, and E. C. Burrows, "Investigation of crosstalk performance of eight-channel p-i- n/HBT OEIC photoreceiver array modules," *IEEE Photon. Technol. Lett.*, vol. 8, no. 5, pp. 682–684, May 1996.

John P. Helme received the M.Eng. and Ph.D. degrees in electronic engineering from the University of Sheffield, Sheffield, U.K., in 2000 and 2006, respectively. Since January 2006, he has been a Research Assistant with the Department of Electronic and Electrical Engineering, University of Sheffield. His current research interests include the modeling of high-speed III–V and optical terahertz rectenna.

**Peter A. Houston** received the B.Sc. degree (with first-class honors) in physics and the Ph.D. degree on the measurement of the velocity of electrons in GaAs at very high electric fields by the time-of-flight technique from Strathclyde University, Glasgow, U.K., in 1972 and 1975, respectively.

From 1975 to 1978, he was with GEC Hirst Research Centre, where he developed liquid-phase epitaxial growth of GaAs structures for MESFETs. In 1978, he was a Lecturer with the Department of Electronic and Electrical Engineering, University of Sheffield, Sheffield, U.K., where he helped set up, was promoted as a Senior Lecturer and subsequently a Reader in October 1996, is currently a Professor of electronic devices and the Head of the Department of Electronic and Electrical Engineering, and also a Co-Director of the Engineering and Physical Sciences Research Council (EPSRC) National Centre for III–V Technologies. From 1986 to 1987, he spent a one-year leave of absence with Bell Northern Research (now NORTEL), Ottawa, ON, Canada, where he worked on the development of HBTs. His current research interests cover include a wide range of III–V materials systems, HBT and HEMT device fabrication and modeling, ballistic transport effects, and piezoelectric strained layers.

Chee Hing Tan received the B.Eng. and Ph.D. degrees in electronic engineering from the University of Sheffield, Sheffield, U.K., in 1998 and 2002, respectively.

He is currently a Senior Lecturer with the Department of Electronic and Electrical Engineering, University of Sheffield. His current research interests include experimental and theoretical investigation of excess noise, breakdown, and jitter in Si and III–V APDs and SPADs, design of high-speed APDs and HPTs, and infrared photodetectors.