## Silicon-compatible high-hole-mobility transistor with an undoped germanium channel for low-power application

Seongjae Cho, In Man Kang, Kyung Rok Kim, Byung-Gook Park, and James S. Harris Jr.

Citation: Applied Physics Letters 103, 222102 (2013); doi: 10.1063/1.4833295

View online: http://dx.doi.org/10.1063/1.4833295

View Table of Contents: http://scitation.aip.org/content/aip/journal/apl/103/22?ver=pdfcov

Published by the AIP Publishing

Over **700** papers & presentations on multiphysics simulation

## Silicon-compatible high-hole-mobility transistor with an undoped germanium channel for low-power application

Seongjae Cho,<sup>1</sup> In Man Kang,<sup>2</sup> Kyung Rok Kim,<sup>3,a)</sup> Byung-Gook Park,<sup>4</sup> and James S. Harris, Jr.<sup>5</sup>

(Received 11 October 2013; accepted 8 November 2013; published online 25 November 2013)

In this work, Ge-based high-hole-mobility transistor with Si compatibility is designed, and its performance is evaluated. A 2-dimensional hole gas is effectively constructed by a AlGaAs/Ge/Si heterojunction with a sufficiently large valence band offset. Moreover, an intrinsic Ge channel is exploited so that high hole mobility is preserved without dopant scattering. Effects of design parameters such as gate length, Ge channel thickness, and aluminum fraction in the barrier material on device characteristics are thoroughly investigated through device simulations. A high on-current above  $30 \,\mu\text{A}/\mu\text{m}$  along with a low subthreshold swing was obtained from an optimized planar device for low-power applications. © 2013 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [http://dx.doi.org/10.1063/1.4833295]

Germanium (Ge) is a material with versatility in both electronics and photonics due to its relatively high electron mobility ( $\leq 3900 \text{ cm}^2/\text{V} \cdot \text{s}$ ) compared with that of silicon (Si)  $(\leq 1500 \text{ cm}^2/\text{V} \cdot \text{s})$  and its peculiar energy-band structure in that a local conduction band  $(E_C)$  minimum exists at the  $\Gamma$  valley  $(\mathbf{k} = 0)$  in the momentum space). Because of these virtues, Ge has been adopted for a wide range of applications in high-speed electronic devices and group-IV-based optical components.<sup>2-6</sup> Another merit of Ge is found in its prominently high hole mobility among the most prevalent semiconductors used for functional devices as shown in Table I.<sup>1,7–9</sup> Although the smaller energy bandgap ( $E_g = 0.8 \,\mathrm{eV}$  at the  $\Gamma$ valley and 0.66 eV at the L valley) of Ge offers the opportunity for fabricating photonic components in the infrared regime, it has a drawback in that it makes it more difficult to realize higher electrical reliability and endurance in metal-oxide-semiconductor field-effect transistors (MOSFETs). 10-12 Also, efforts are required prior to gate oxide deposition to passivate the surface to suppress the interface leakage induced by the instability of Ge dangling bonds. 13–15

In the present study, a high-hole-mobility transistor (HHMT) with an undoped Ge channel is designed and characterized by device simulation. By using an intrinsic Ge channel, there is no loss in hole mobility owing to dopant scattering, and the leakage current by band-to-band tunneling between the channel and drain is significantly reduced. Following the configuration of conventional metal-semiconductor FETs (MESFETs), the high- $\kappa$  dielectric used as the gate oxide in Ge MOSFETs is replaced by an AlGaAs epitaxial layer due to its small lattice mismatch with Ge,

which greatly simplifies the fabrication by eliminating complicated steps for gate oxidation which substantially reduces the mobility degradation owing to surface scattering. Moreover, the AlGaAs/Ge heterojunction is an ideal structure for the effective quantum confinement of holes to form 2-dimensional hole gas (2DHG) due to its large valence band offset ( $\Delta E_{\rm V} = 0.834 + 0.147x$ , where x is Al fraction in AlGaAs for x < 0.45). At the same time, Ge has higher graftability to Si, which realizes monolithic integration on a Si platform with advanced electronic devices and optical components.  $^{6,19,20}$

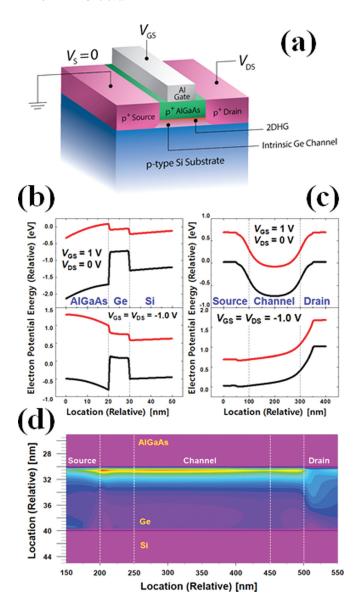

Figure 1(a) shows the schematic a real view of the simulated Ge HHMT. Gate length  $(L_{\rm G})$ , Ge channel thickness  $(T_{\rm Ge})$ , and aluminum (Al) fraction have been treated as the device variables. Al (work function = 4.06 eV) was used for the gate metal. The p-type Si substrate had a doping concentration of  $10^{15}$  cm<sup>-3</sup> and  $p^+$  source and drain were doped at  $10^{19}$  cm<sup>-3</sup>. The  $p^+$  AlGaAs barrier had a thickness of 30 nm, and its doping concentration was  $10^{18}$  cm<sup>-3</sup>. For higher accuracy in the simulation, multiple models including field-and concentration-dependent models, a Shockley–Read–Hall recombination model, and a quantum model were activated in cooperation. Figures 1(b) and 1(c) demonstrate the simulated energy-band diagrams in the vertical (at the device center) and lateral (across the Ge channel) directions, respectively. In each figure, the upper and lower parts show

TABLE I. Comparison of hole mobilities of intrinsic semiconductors (units in  $cm^2/V \cdot s$ ).

| Si  | GaAs | InAs | InP | GaN | SiC | Ge   |

|-----|------|------|-----|-----|-----|------|

| 450 | 400  | 500  | 200 | 300 | 100 | 1900 |

<sup>&</sup>lt;sup>1</sup>Department of Electronic Engineering, Gachon University, Gyeonggi-do 461-701, South Korea

<sup>&</sup>lt;sup>2</sup>School of Electronics Engineering, Kyungpook National University, Daegu 702-701, South Korea

<sup>&</sup>lt;sup>3</sup>School of Electrical and Computer Engineering, Ulsan National Institute of Science and Technology, Ulsan 689-798, South Korea

<sup>&</sup>lt;sup>4</sup>Inter-university Semiconductor Research Center (ISRC) and Department of Electrical and Computer Engineering, Seoul National University, Seoul 151-742, South Korea

<sup>&</sup>lt;sup>5</sup>Department of Electrical Engineering, Stanford University, Stanford, California 94305, USA

a) Author to whom correspondence should be addressed. Electronic mail: krkim@unist.ac.kr. Tel.: +82-52-217-2122

FIG. 1. Device configurations. (a) Areal view of the simulated device. (b) Energy-band diagrams at the device center in the vertical direction (upper: off-state, lower: on-state). (c) Energy-band diagrams along the channel beneath the AlGaAs/Ge interface (upper: off-state, lower: on-state). (d) Formation of 2DHG at the on-state,  $V_{\rm GS} = V_{\rm DS} = -1.0 \, \rm V$ .

diagrams in the off- and on-states (off-state:  $V_{\rm GS} = 1.0 \, \rm V$ ,  $V_{\rm DS} = 0 \, \text{V}$ ; on-state:  $V_{\rm GS} = V_{\rm DS} = -1.0 \, \text{V}$ ). It is assured from the figures that the band arrangement for effective hole confinement is not interrupted in any circumstance, and that the energy barrier seen by the free holes is completely lowered by an operation voltage as small (in magnitude) as  $-1.0 \,\mathrm{V}$ . Figure 1(d) illustrates the hole current density obtained by simulation in a magnified view of the intrinsic Ge channel, by which the formation of 2DHG is more tangibly confirmed. From a fabrication point of view, it might be a tricky task to achieve seamless interfacing of the heterojunctions in the HHMT and Ge/Si interface should be more challenging than AlGaAs/Ge site since the lattice mismatch between Ge and Si (4%) is much larger than that between AlGaAs and Ge (within 0.08%). However, it is a relieving feature that the conduction carriers of the HHMT are drifted along the AlGaAs/Ge interface away from Ge/Si interface in its drive mode, and further, a permissibly smooth relaxed Ge/Si interface can be also obtained by a cyclic epitaxy technique combining low-temperature growth and flash annealing.<sup>21</sup>

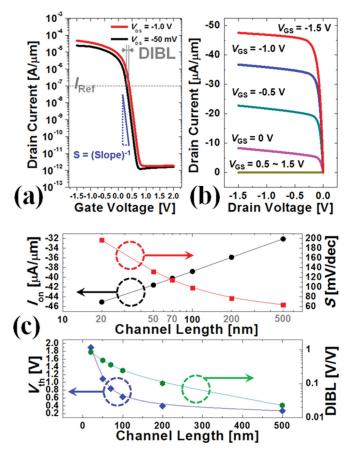

Figures 2(a)-2(c) show the electrical performances of a Ge HHMT with varying  $L_{\rm G}$  from 500 nm down to 20 nm with other design variables fixed at  $T_{\text{Ge}} = 10 \,\text{nm}$  and Al fraction = 0.3. Figures 2(a) and 2(b) depict the transfer and output characteristics of a device with  $L_{\rm G} = 200\,{\rm nm}$ . In the transfer curves, it is observed that gate-induced drain leakage (GIDL) by band-to-band tunneling is effectively suppressed, and a steep subthreshold slope (SS) is obtained. Subthreshold swing (S) is defined as the reciprocal of the maximum instantaneous SS (in absolute value),  $S = |[d(\log_{10}|I_D|)/dV_{GS}|_{max}]^{-1}|$ , as illustrated in the inset. The extracted S under the given condition was less than 80 mV/dec. The output curves are similar to typical curves of p-type MOSFETs (PMOSFETs) and evenly spaced by  $V_{GS}$ . Figure 2(c) illustrates collectively the direct-current (DC) parameters as functions of  $L_G$ . The on-state current ( $I_{on}$ ) shows a monotonic increase, while S is degraded as  $L_G$  is scaled down, where S values are checked only at the high drain voltage  $(V_{DS}) = -1.0 \,\mathrm{V}$ . Threshold voltage  $(V_{th})$  becomes positively higher, and drain-induced barrier lowering (DIBL) increases as  $L_{

m G}$  shrinks.  $V_{

m th}$  was defined by the constant-current method at a reference  $I_D$  of  $I_{Ref} = 10^{-7}$  $A/\mu m$ , and DIBL was extracted mathematically from the amount of  $V_{\rm th}$  shift normalized by the  $V_{\rm DS}$  change (in

FIG. 2. Electrical characteristics as a function of  $L_{\rm G}$ . Validation of Ge HHMT by (a) transfer and (b) output characteristics from a device with  $L_{\rm G}=200\,{\rm nm},~T_{\rm Ge}=10\,{\rm nm},$  and Al fraction = 0.3. (c) DC parameters as a function of  $L_{\rm G}$ :  $I_{\rm on}$  and S (upper);  $V_{\rm th}$  and DIBL (lower) ( $T_{\rm Ge}=10\,{\rm nm},$  Al fraction = 0.3).

absolute value), DIBL =  $|\Delta V_{\rm th}/\Delta V_{\rm DS}| = |(V_{\rm th}|_{V\rm DS} = -1.0~{\rm V} - V_{\rm th}|_{V\rm DS} = -50~{\rm mV})/[-1.0~{\rm V} - (-50~{\rm mV})]|$  (unit in V/V), as indicated in Fig. 2(a). Although further device optimization by geometrical rendering into a fin-shaped-channel FET (FinFET), double-gate (DG) or multiple-gate (MuG) FET, a nanowire FET would produce improvements in S and DIBL,  $^{22-29}$  and it is an encouraging fact that high current drivability reaching some tens of amperes per unit width has been obtained from an unaltered in-plane Ge HHMT.

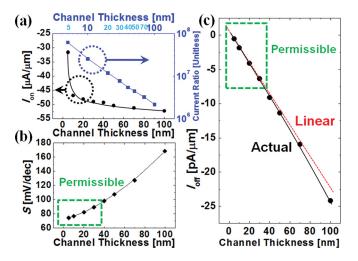

Figures 3(a)-3(c) illustrate the DC parameters for varying  $T_{\text{Ge}}$  from 5 nm to 100 nm keeping the other variables constant at  $L_G = 200 \,\mathrm{nm}$  and Al fraction = 0.3. Figure 3(a) depicts  $I_{\text{on}}$  and current ratio ( $I_{\text{on}}/I_{\text{off}}$ ,  $I_{\text{off}}$ : off-state current) as a function of  $T_{\text{Ge}}$ .  $I_{\text{on}}$  shows a monotonic increase with  $T_{\text{Ge}}$ but the extremely thin channel below 10 nm needs to be avoided to secure sufficient current drivability. It is noticeable that the change in  $I_{\rm on}$  by modulating  $T_{\rm Ge}$  over 100 nm is much larger than that by  $L_{\rm G}$  scaling over 500-nm range, which implies that controlling  $T_{Ge}$  is more steering factor in determining the current drivability of Ge HHMT. However, the current ratio decreases with increasing  $T_{\text{Ge}}$ , and  $T_{\text{Ge}}$ should be kept thin below the upper limit to obtain a high current ratio. The trade-off relation between  $I_{\rm on}$  and current ratio implies that a large portion of optimal design should be placed on  $T_{Ge}$ . S is plotted as a function of  $T_{Ge}$  in Fig. 3(b). To obtain a small swing (tentatively, with a reference of  $100\,\mathrm{mV/dec}$ ),  $T_{\mathrm{Ge}}$  needs to be kept thin below  $40\,\mathrm{nm}$ . This supports that the swing characteristics of Ge HHMT would be superior to those of Ge PMOSFETs fabricated on Ge bulk substrate. Along with S,  $I_{\text{off}}$  can also play a role as an index of gate controllability in a thin-body electron device. Figure 3(c) depicts  $I_{\text{off}}$  as a function of  $T_{\text{Ge}}$ .  $I_{\text{off}}$  is linearly scaled with  $T_{\text{Ge}}$  since  $I_{\text{off}}$  would be proportional to the area (device width (constant = 1  $\mu$ m) ×  $T_{Ge}$ ) normal to hole flux assuming that the gate has complete controllability over the thin Ge channel, which leads to a plot of  $I_{\rm off}$  as a linear function of  $T_{\rm Ge}$ .  $I_{\rm off}$  increases with  $T_{\rm Ge}$  linearly up to  $T_{\rm Ge} = 30$  nm; however, the plot shows a hyperlinear trend above that thickness, as indicated by the linear and actual lines in Figure 3(c). It is implied that  $T_{\text{Ge}}$  needs to be falling into the permissible range (green box in the figure) in order to have a strong gate controllability over the channel. Considering the overall

FIG. 3. Electrical characteristics as a function of  $T_{\rm Ge}$  ( $L_{\rm G}$  = 200 nm, Al fraction = 0.3). (a)  $I_{\rm on}$  and current ratio ( $I_{\rm on}/I_{\rm off}$ ). (b)  $S_{\rm o}$  (c)  $I_{\rm off}$ .

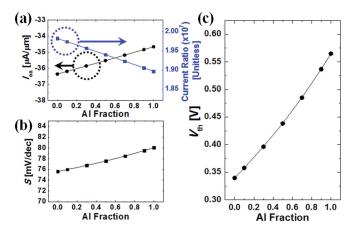

FIG. 4. Electrical characteristics as a function of Al fraction ( $L_{\rm G}=200\,{\rm nm}$ ,  $T_{\rm Ge}=10\,{\rm nm}$ ). (a)  $I_{\rm on}$  and current ratio ( $I_{\rm on}/I_{\rm off}$ ). (b) S. (c)  $V_{\rm th}$ .

results,  $T_{\rm Ge}$  is a crucial design variable that should be optimally determined, possibly with a permissible range of  $T_{\rm Ge} = 10 \, \rm nm$  to 30 nm, for higher current drivability and strong gate controllability.

Figures 4(a)-4(c) demonstrate the effects of the Al fraction in the AlGaAs barrier material on the current characteristics of the Ge HHMT. The other variables were kept constant at  $L_G = 200 \,\mathrm{nm}$  and  $T_{Ge} = 10 \,\mathrm{nm}$ . Compared with the previous two design variables, the Al fraction has a relatively small effect on the device performance. The change in  $I_{\rm on}$  was as small as  $2\,\mu\text{A}/\mu\text{m}$ , and the current ratio also showed a small change of 10<sup>5</sup>, which is below a percent order change compared with the base value of 10<sup>7</sup> over the full sweep of the Al fraction from 0 to 1, as shown in Figure 4(a). S is also almost invariable with the Al fraction, as shown in Figure 4(b), where the change in S is found to be only 3 mV/dec by the full scaling of the Al fraction. A relatively more distinguishable change is observed by modulating the Al fraction in the  $V_{\rm th}$  shift, as plotted in Figure 4(c). However, its effect on  $V_{\rm th}$  is still smaller than that of another variable,  $L_{\rm G}$ . These results ensure that the electrical performance of the Ge HHMT has a strong tolerance against deviation in the Al fraction that might occur during the epitaxy process; this is another advantage of the device, even from a more practical point of view.

We optimally designed a silicon-compatible AlGaAs/Ge/Si heterojunction HHMT considering the channel length, channel thickness, and Al fraction of the barrier. It has been confirmed that an effective quantum confinement of holes forming a 2DHG was achieved by the material system, which confirms the feasibility of the device for low-power applications. Improved reliability, simpler fabrication, higher current drivability that eliminates both dopant and surface scattering, and stronger process tolerance make the Ge HHMT favorable and highly competitive with conventional Si CMOS and Ge PMOSFETs.

This work was supported by the Center for Integrated Smart Sensors funded by the Korean Ministry of Science, ICT & Future Planning as Global Frontier Project (CISS-2012M3A6A6054186) and by the Pioneer Research Center Program through the National Research Foundation of Korea funded by the Ministry of Science, ICT & Future Planning (Grant No. 2012-0009594).

- <sup>1</sup>S. M. Sze, *Physics of Semiconductor Devices*, 2nd ed. (John Wiley & Sons, Inc., New York, 1981), pp. 13, 849.

- <sup>2</sup>C. R. Selvakumar and B. Hecht, IEEE Electron Device Lett. **12**, 444 (1991). <sup>3</sup>Y. Kamata, Mater. Today **11**, 30 (2008).

- <sup>4</sup>Y.-H. Kuo, Y. K. Lee, Y. Ge, S. Ren, J. E. Roth, T. I. Kamins, D. A. B. Miller, and J. S. Harris, Nature **437**, 1334 (2005).

- <sup>5</sup>O. Fidaner, A. K. Okyay, J. E. Roth, R. K. Schaevitz, Y.-H. Kuo, K. C. Saraswat, J. S. Harris, Jr., and D. A. B. Miller, IEEE Photonics Technol. Lett. **19**, 1631 (2007).

- <sup>6</sup>S. Cho, B.-G. Park, C. Yang, S. Cheung, E. Yoon, T. I. Kamins, S. J. B. Yoo, and J. S. Harris, Jr., Opt. Express **20**, 14921 (2012).

- <sup>7</sup>C. Claeys and E. Simoen, *Germanium-Based Technologies: From Materials to Devices* (Elsevier, Oxford, 2007), p. 368.

- <sup>8</sup>D. J. As, D. Schikora, A. Greiner, M. Lubbers, J. Mimkes, and K. Lischka, Phys. Rev. B **54**, R11118 (1996).

- <sup>9</sup>W. J. Schaffer, H. S. Kong, G. H. Negley, and J. W. Palmour, *Proceedings of the 5th Conference on Silicon Carbide and Related Materials*, Institute of Physics Conference Series Vol. 137, edited by M. G. Spencer (Institute of Physics Publishing, London, 1994), pp. 155–159.

- <sup>10</sup>M. K. Husain, X. V. Li, and C. H. de Groot, IEEE Trans. Electron Devices 56, 499 (2009).

- <sup>11</sup>C.-W. Chen, C.-T. Chung, J.-Y. Tzeng, P.-H. Li, P.-S. Chang, C.-H. Chien, and G.-L. Luo, IEEE Trans. Electron Devices 60, 1334 (2013).

- <sup>12</sup>W. Rindner, Appl. Phys. Lett. **6**, 225 (1965).

- <sup>13</sup>S. J. Whang, S. J. Lee, F. Gao, N. Wu, C. X. Zhu, J. S. Pan, L. J. Tang, and D. L. Kwong, Tech. Dig.-Int. Electron Devices Meet. 2004, 307–310

- <sup>14</sup>W.-S. Jung, J. H. Nam, J.-Y. J. Lin, S. Ryu, A. Nainani, and K. C. Saraswat, in *Proceedings of 2012 International Silicon-Germanium Technology and Device Meeting (ISTDM), Berkeley, USA, 4–6 June 2012* (The Institute of Electrical and Electronics Engineers, 2012), pp. 1–2.

- <sup>15</sup>M. Zhao, R. Liang, J. Wang, and J. Xu, Appl. Phys. Lett. **102**, 142906 (2013)

- <sup>16</sup>Atlas User's Manual: Device Simulation Software (Silvaco, Inc., Santa Clara, USA, 2013).

- <sup>17</sup>W. Liu, Fundamentals of III-V Devices: HBTs, MESFETs, and HFETs/HEMTs (John Wiley & Sons, Inc., New York, 1999), pp. 330–345.

- <sup>18</sup>J. S. Harris, Jr., Class Notes from EE327 Properties of Semiconductor Materials (Stanford University, 2013).

- <sup>19</sup>S. Cho, S. H. Park, B.-G. Park, and J. S. Harris, Jr., in *Proceedings of 2011 International Semiconductor Device Research Symposium (ISDRS)*, *College Park, USA*, 7–9 *December 2011* (The Institute of Electrical and Electronics Engineers, 2011), pp. 1–2.

- <sup>20</sup>S. Cho, I. M. Kang, T. I. Kamins, B.-G. Park, and J. S. Harris, Jr., Appl. Phys. Lett. **99**, 243505 (2011).

- <sup>21</sup>A. Nayfeh, "Heteroepitaxial Growth of Relaxed Germanium on Silicon," Ph.D. dissertation (Stanford University, 2006).

- <sup>22</sup>International Technology Roadmap for Semiconductors (ITRS), 2011 ed., Process Integration, Devices & Structures (PIDS) Chapter (2011).

- <sup>23</sup>B.-G. Park, S. W. Hwang, and Y. J. Park, *Nanoelectronic Devices* (Pan Stanford Publishing Pte. Ltd., Singapore, 2012), pp. 228–239, 274–283.

- <sup>24</sup>B.-G. Park, J. Y. Song, J. P. Kim, H. Jeong, J. H. Lee, and S. Cho, Microelectron. J. 40, 769 (2009).

- <sup>25</sup>Y. Taur, IEEE Electron Device Lett. **21**, 245 (2000).

- <sup>26</sup>J. S. Lee, S. Cho, B.-G. Park, J. S. Harris, and I. M. Kang, J. Semicond. Technol. Sci. 12, 230 (2012).

- <sup>27</sup>M.-S. Lee, S.-M. Joe, J.-G. Yun, H. Shin, B.-G. Park, S.-S. Park, and J.-H. Lee, J. Semicond. Technol. Sci. 12, 360 (2012).

- <sup>28</sup>C.-W. Lee, A. Afzalian, N. D. Akhavan, R. Yan, I. Ferain, and J.-P. Colinge, Appl. Phys. Lett. **94**, 053511 (2009).

- <sup>29</sup>P. Razavi and G. Fagas, Appl. Phys. Lett. **103**, 063506 (2013).