# Real-time, synchronous, data-flow programming: the language "SIGNAL" and its mathematical semantics

Paul Le Guernic, Albert Benveniste

#### ▶ To cite this version:

Paul Le Guernic, Albert Benveniste. Real-time, synchronous, data-flow programming: the language "SIGNAL" and its mathematical semantics. [Research Report] RR-0533, INRIA. 1986. inria-00076021

HAL Id: inria-00076021

https://hal.inria.fr/inria-00076021

Submitted on 24 May 2006

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

UNITÉ DE RECHERCHE INRIA-RENNES

Institut National de Recherche en Informatique et en Automatique

Domaine de Voluceau Rocquencourt BP105 78153 Le Chesnay Cedex France

Tél:(1)39635511

all by

### Rapports de Recherche

Nº 533

REAL-TIME, SYNCHRONOUS, DATA-FLOW PROGRAMMING: THE LANGUAGE "SIGNAL" AND ITS MATHEMATICAL SEMANTICS

Paul LE GUERNIC

Albert BENVENISTE

Juin 1986

# REAL - TIME, SYNCHRONOUS, DATA - FLOW PROGRAMMING: THE LANGUAGE «SIGNAL» AND ITS MATHEMATICAL SEMANTICS.

Publication Interne n° 298 112 pages

June 1986

Paul Le Guernic, Albert Benveniste

IRISA/INRIA, Campus de Beaulieu F35042 RENNES CEDEX, FRANCE

Abstract: We present the kernel of the language SIGNAL. SIGNAL is a data-flow, real-time, synchronous language which was primarily designed for real-time control and signal processing task specification and implementation. Unlike classical data-flow or real-time languages, SIGNAL: is based on a synchronous notion of time. The semantics is of operational style, and allows to derive a complete static calculus of the timing of every SIGNAL process, called its clock calculus. Hence, the programming language SIGNAL is also a formal system to reason about timing and concurrency.

Résumé: Cet article présente le langage SIGNAL. SIGNAL est un langage de type flot de données, temps – réel, synchrone, dont le domaine d'application primitif est la spécification et la mise en œuvre de tâches temps – réel dans les domaines du traitement du signal et de l'automatique. Contrairement aux langages classiques temps – réel ou flot de données, SIGNAL utilise un temps logique de type synchrone. La sémantique est de type opérationnel, et permet de fonder un calcul statique complet du comportement temporel d'un processus SIGNAL: son calcul d'horloge. Le langage de programmation SIGNAL est donc aussi un système formel permettant de manipuler simultanément le temps et le parallélisme.

Paul LE GUERNIC

Albert BENVENISTE

# REAL-TIME, SYNCHRONOUS, DATA-FLOW PROGRAMMING: THE LANGUAGE SIGNAL AND ITS MATHEMATICAL SEMANTICS

Publication interne no 298

Juin 1986

#### **Table of Contents**

| 1. | INTR | ODUCTI  | ON.           |                                        | 1   |

|----|------|---------|---------------|----------------------------------------|-----|

| •  |      |         |               | e in SIGNAL: synchronous languages.    | . 2 |

|    | 1.2  | About   | the seman     | tics of SIGNAL and its clock calculus. | 3   |

|    | 1.3  |         |               | ne article, a guide to the reader.     | 5   |

|    |      |         |               |                                        |     |

| 2. | THE  | KERNEI  | OF THE        | LANGUAGE SIGNAL                        | 7   |

|    | 2.1  | Notatio | ns, definiti  | ons, and axioms                        | 7   |

|    |      | 2.1.1   | The give      | n instantaneous language               | 7   |

|    |      | 2.1.2   | SIGNAL        | expressions.                           | 8   |

|    |      | 2.1.3   | <b>Axioms</b> |                                        | 10  |

|    | 2.2  | The ba  | sic instruc   | tions                                  | 10  |

|    |      | 2.2.1   | Generato      | rs .                                   | 11  |

|    |      |         | 2.2.1.1       | Functions                              | 11  |

|    |      |         | 2.2.1.2       | Delay                                  | 12  |

|    |      |         | 2.2.1.3       | Filter                                 | 12  |

|    |      |         | 2.2.1.4       | Merge                                  | 13  |

|    |      |         | 2.2.1.5       | Condition                              | 13  |

|    |      | 2.2.2   | Interconn     | nection operators                      | 14  |

|    |      |         | 2.2.2.1       | Relabelling of input ports             | 14  |

|    |      |         | 2.2.2.2       | Relabelling of output ports            | 15  |

|    |      |         | 2.2.2.3       | Collateral                             | 16  |

|    |      |         | 2.2.2.4       | The p-connection                       | 18  |

| 3. | THE  | BEHAV   | IORAL SEI     | MANTICS.                               | 21  |

| •  | 3.1  |         | ons and de    | •                                      | 21  |

|    |      | 3.1.1   |               | nd histories.                          | 21  |

|    |      |         | 3.1.1.1       | Input events.                          | 21  |

|    |      |         |               | Input histories.                       | 22  |

|    |      | 3.1.2   |               | transitions, acceptances and refusals. | 22  |

|    |      |         | 3.1.2.1       | Allowed transitions.                   | 22  |

|    | ,    |         | 3.1.2.2       | Acceptances, refusals.                 | 23  |

|    |      | 3.1.3   |               | and runs.                              | 23  |

|    |      |         | 3.1.3.1       | Actions                                | 23  |

|    |      |         | 3.1.3.2       | Runs.                                  | 23  |

|    |      | 3.1.4   | Example       |                                        | 24  |

|    | 3.2  |         | problems.     |                                        | 26  |

|    |      | 3.2.1   | •             | ability of a transition.               | 26  |

|    |      | 3.2.2   | Time - c      | orrectness                             | 26  |

|    |      |         |               | Example 2                              | 26  |

|    |      |         |               | Example 3                              | 27  |

|    |      |         | 0000          | Francis A                              | 27  |

|            |      | 3.2.3     | Determinism.                                                | 28 |

|------------|------|-----------|-------------------------------------------------------------|----|

|            |      |           | 3.2.3.1 Example 5                                           | 28 |

|            |      | 3.2.4     | Weak determinism.                                           | 29 |

|            |      |           | 3.2.4.1 Input – output events.                              | 29 |

|            |      |           | 3.2.4.2 Input – output – allowed transitions.               | 29 |

| ٠          |      |           | 3.2.4.3 Weak determinism.                                   | 29 |

| 4.         | CON  | GRUENT    | PROCESSES.                                                  | 31 |

| 5.         | THE  | CLOCK C   | ALCULUS.                                                    | 37 |

|            | 5.1  | Analysis  | of further simple examples; some consequences.              | 37 |

|            |      | 5.1.1     | The example 6                                               | 37 |

|            |      | 5.1.2     | Clocks as equivalence classes of simultaneous signals.      | 38 |

|            |      | 5.1.3     | Clock transforms due to generators: an informal discussion. | 39 |

|            | 5.2  | The sub   | language SIG.                                               | 39 |

|            | 5.3  | The mat   | hematical model of SIG.                                     | 40 |

|            | 5.4  | The cloc  | k calculus of a SIGNAL process.                             | 41 |

|            |      |           | The clock calculi of the generators of SIGNAL.              | 41 |

|            |      |           | Clock transfers due to the interconnection operators.       | 43 |

|            | 5.5  | . •       | clock calculi.                                              | 44 |

|            |      |           | The equation aX2+bX+c=0.                                    | 44 |

|            |      |           | Solving systems of equations.                               | 46 |

|            | 5.6  |           | the examples.                                               | 48 |

|            |      |           | Example 2, continued.                                       | 48 |

|            |      |           | Example 4, continued.                                       | 49 |

|            |      |           | Example 6, continued.                                       | 50 |

|            |      | 5.6.4 l   | Example 7.                                                  | 51 |

| 6.         | DATA | A DEPEND  | DENCIES.                                                    | 53 |

|            | 6.1  | Further e | examples                                                    | 53 |

|            |      | 6.1.1     | Example 8.                                                  | 53 |

|            |      |           | Example 9.                                                  | 53 |

|            | 6.2  |           | ditional dependence graph.                                  | 54 |

|            |      |           | Definition and basic properties.                            | 54 |

|            | 6.3  |           | n of the conditional dependence graph.                      | 58 |

|            |      |           | The conditional dependence graph of the generators,         | 58 |

|            |      |           | Fransfers due to interconnection operators.                 | 59 |

|            | 6.4  |           | the examples.                                               | 60 |

|            |      |           | Example 8, continued                                        | 61 |

|            |      |           | Example 9, continued                                        | 61 |

|            | •    | 6.4.3 E   | Example 10                                                  | 63 |

| <b>7</b> . | MAIN | THEORE    |                                                             | 67 |

|            | 7.1  | Cuts, and | d related basic lemmas.                                     | 67 |

|    |     | 7.1.1    | Cuts.                                                                  | 67                                                                                                                                                                                                                   |

|----|-----|----------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    |     | 7.1.2    | Transfers of cuts.                                                     | 68                                                                                                                                                                                                                   |

|    |     |          | 7.1.2.1 Input relabelling.                                             | 68                                                                                                                                                                                                                   |

|    |     |          | 7.1.2.2 Output relabelling.                                            | 68                                                                                                                                                                                                                   |

|    |     |          | 7.1.2.3 Collateral.                                                    | 68                                                                                                                                                                                                                   |

|    |     |          | 7.1.2.4 The p - connection.                                            | 68                                                                                                                                                                                                                   |

|    |     | 7.1.3    | Basic properties of cuts.                                              | 69                                                                                                                                                                                                                   |

|    |     |          | 7.1.3.1 Computable transitions.                                        | 69                                                                                                                                                                                                                   |

|    |     |          | 7.1.3.2 Time – correctness.                                            | 69                                                                                                                                                                                                                   |

|    |     |          | 7.1.3.3 Determinism.                                                   | 70                                                                                                                                                                                                                   |

|    | 7.2 | Province | g the clock calculus.                                                  | 70                                                                                                                                                                                                                   |

|    |     | 7.2.1    | The map CLOCK defined on SIGNAL processes.                             | 70                                                                                                                                                                                                                   |

|    |     |          | 7.2.1.1 CLOCK acting on generators.                                    | 70                                                                                                                                                                                                                   |

|    |     |          | 7.2.1.2 Complete definition of the map CLOCK.                          | 71                                                                                                                                                                                                                   |

|    |     | 7.2.2    |                                                                        | 72                                                                                                                                                                                                                   |

|    |     |          | 7.2.2.1 Deleting the memories of CLOCK(P).                             | 72                                                                                                                                                                                                                   |

|    |     |          | 7.2.2.2 Restricting the data types.                                    | 72                                                                                                                                                                                                                   |

|    |     |          | 7.2.2.3 CLOCK*(P) is identical to the clock calculus of P.             | 73                                                                                                                                                                                                                   |

|    | 7.3 | The cl   | ock calculus as a tool to check timing properties of a SIGNAL process. | 73                                                                                                                                                                                                                   |

|    | ,   |          |                                                                        |                                                                                                                                                                                                                      |

|    | THE | COMPLI   | ITATIONAL SEMANTICS.                                                   | 77                                                                                                                                                                                                                   |

| 8. |     |          | ata – flow computational semantics.                                    |                                                                                                                                                                                                                      |

|    | 8.1 |          | Data – flow graphs.                                                    |                                                                                                                                                                                                                      |

|    |     | 8.1.1    | 8.1.1.1 Data – flow graphs of some examples.                           |                                                                                                                                                                                                                      |

|    |     | 8.1.2    | The computational semantics of data – flow graphs.                     |                                                                                                                                                                                                                      |

|    |     | 0.1.2    | 8.1.2.1 Semantics of the nodes.                                        |                                                                                                                                                                                                                      |

|    |     |          | 8.1.2.2 The semantics of data – flow graphs.                           |                                                                                                                                                                                                                      |

|    | 8.2 | The se   | equential computational semantics.                                     |                                                                                                                                                                                                                      |

|    | 0.2 | 8.2.1    | The domains of $GA(P)$ .                                               | 84                                                                                                                                                                                                                   |

|    |     | 0.2.1    | 8.2.1.1 The states of $GA(P)$ .                                        | 84                                                                                                                                                                                                                   |

|    |     |          | 8.2.1.2 The outputs of $GA(P)$ .                                       | _                                                                                                                                                                                                                    |

|    |     |          | 8.2.1.3 The inputs of $GA(P)$ .                                        | . 86                                                                                                                                                                                                                 |

|    |     | 8.2.2    | The transitions of $GA(P)$ .                                           | 86                                                                                                                                                                                                                   |

|    |     | 0.2.2    | 8.2.2.1 Defining the output $ET$ .                                     | 86                                                                                                                                                                                                                   |

|    | ,   |          | 8.2.2.2 Defining the input.                                            | 68<br>69<br>69<br>70<br>70<br>70<br>71<br>72<br>72<br>73<br>73<br>77<br>77<br>77<br>77<br>79<br>80<br>81<br>84<br>84<br>84<br>84<br>85<br>86<br>86<br>86<br>86<br>86<br>86<br>86<br>86<br>86<br>86<br>86<br>88<br>88 |

|    |     |          | 8.2.2.3 Defining the new state.                                        | 87                                                                                                                                                                                                                   |

|    |     | 8.2.3    | Running $GA(P)$ .                                                      | 88                                                                                                                                                                                                                   |

|    | •   | 8.2.4    | Examples.                                                              | - 88                                                                                                                                                                                                                 |

|    |     | 8.2.5    | Separate compilation.                                                  | 90                                                                                                                                                                                                                   |

|    |     |          |                                                                        |                                                                                                                                                                                                                      |

| _  |     | .nc      | DTI C CVANDI C                                                         | മാ                                                                                                                                                                                                                   |

| 9. |     |          | BTLE EXAMPLE.                                                          |                                                                                                                                                                                                                      |

|    | 9.1 |          | me – multiplexer: the program. lock calculus of the MUXSYNCHRO.        | 95                                                                                                                                                                                                                   |

|    | 9.2 | 9.2.1    | Clock calculus of COUNTMOD.                                            | 95                                                                                                                                                                                                                   |

|    |     |          | Clock calculus of VAR                                                  | 95                                                                                                                                                                                                                   |

|    |     | J.Z.C    | WIGGR GUIGHIG OF TARE                                                  | ~~                                                                                                                                                                                                                   |

|         | 9.2.3 The clock calculus of MUXSYNCHRO                | 96   |

|---------|-------------------------------------------------------|------|

| 9.3     | The conditional dependence graph.                     | 97   |

|         | 9.3.1 The conditional dependence graph of COUNTMOD.   | 97   |

|         | 9.3.2 The conditional dependence graph of VAR.        | 97   |

|         | 9.3.3 The conditional dependence graph of MUXSYNCHRO. | . 98 |

| 9.4     | An introduction to the dynamical clock calculus.      | 100  |

|         | 9.4.1 The clock calculus of MUXSYNCHRODYN.            | 101  |

|         | 9.4.2 Discussion.                                     | 101  |

| 10. CON | ICLUSION.                                             | 103  |

|         |                                                       | •    |

## Chapter One INTRODUCTION.

The purpose of the language SIGNAL is to take place as an entry point in the two chains

{ high-level task specification } → { VLSI implementation }

{ high-level task specification } → { distributed system implementation }

in the areas of real-time signal or image processing, real-time control systems, and, more generally,  $C^3$ -type applications.

To achieve these goals, SIGNAL has been designed to be at the same time

- an executable language

- · a formal system to reason about timing

- a formal system to reason about parallelism and concurrency.

Hence, the core of the language SIGNAL is based on a formal model; the purpose of this report is to present simultaneously the kernel of SIGNAL, the mathematical model it is based upon, and the formal proof system it provides on the above mentioned aspects. The detailed discussion about the characteristics of the selected fields of application, together with the programming style of the language, can be found in [Le Guernic & al. 1986], [Le Guernic & al. 1985].

SIGNAL is related to two classes of languages: the real-time languages, and the data-flow languages. Classical real-time languages, such as ADA [ADA 1980], LTR [LTR 1978] are basically asynchronous even if they provide explicit synchronisation mechanisms, and consider only one notion of absolute time reference (the "physical" time), hence their non deterministic character is impossible to control in a formal way. Again is the language OCCAM [OCCAM 1983] fully asynchronous in nature, but its rendez-vous mechanism is directly derived from the mathematical model CSP [Hoare 1978, Brookes & al. 1984], so that the guaranteed properties of CSP are still found in OCCAM whatever its (correct!) machine implementation is.

Data – flow programming is now a recognized way to ensure functional execution of a program on a machine with distributed memory and control [Ackermann & Dennis 1979, Dennis 1974]. Again is the execution fully asynchronous in nature, but the functional behaviour is guaranteed thanks to the following rule of executability of an operation: a data – flow actor can fire when it has data tokens on all its input arcs, it then produces result token(s) on its own output arcs. Unfortunately, the data – flow control machanism creates an overhead when it has to be implemented on a

classical Von Neumann architecture; and this can be the case when micro-actors of macro data-flow architectures are Von Neumann oriented; see [Chase 1984, Gaudiot 1985] for fully data-flow oriented architectures. Models of data-flow computing have been studied by Kahn [Kahn 1974, Kahn & Mc Queen 1977] using the notion of Dynamic Network Processes, see also [De Bruin & Boehm 1985].

SIGNAL is a synchronous data – flow language, a notion which will become clear throughout this article. A consequence is that SIGNAL programs can be implemented on data – flow architectures, but also on Von Neumann architectures without any overhead for a token – based control mechanism. To achieve this, SIGNAL handles a quite new notion of time, which makes this language very close to real – time ones, as the reader may convince himself.

#### 1.1 The notion of time in SIGNAL: synchronous languages.

Real-time synchronous languages refer to the notion of time in a completely new point of view. This point of view was first taken by the imperative language ESTEREL [Berry & Cosserat 1984, Tanzi 1985], and is also used by the data-flow oriented languages LUSTRE [Bergerand & al. 1985] and SIGNAL. Let us outline the principles of synchrony. Synchronous real time systems differ from asynchronous ones in the two following aspects:

- concerning the internal mechanisms of the system: every action (communication or operation on data) is instantaneous, i.e. has zero duration;

- concerning the communications with the external world: the set of the possible input stimuli is fixed and known in advance, and input flows are specified through both 1/ the values they carry, and 2/ a total ordering of the «instants» at which these values are available at the input ports.

We refer the interested reader to [Berry & Cosserat 1984] for a detailed discussion about the relevance of the assumption of zero duration of the actions. Of course, the assumption 2/ above is the fundamental feature which characterizes the way synchronous systems do communicate with the external world, compared to asynchronous ones. Let us illustrate further this point on a simple example.

Consider a real time system with two inputs

1. a data input carrying an ordered file of data, named x;

#### 2. an interrupt input port named s.

Then, the specification of an input history according to the synchronous point of view must be of the form

$$\perp$$

$s_2 \perp s_4 \dots$

$x_1 x_2 x_3 \perp \dots$

i.e. both the values (as usually,  $\perp$  denotes the absence of data) and their interleaving must be specified. The time reference is nothing but the index t = 1, 2, 3, ... of the successive flashes of data; this notion of time is thus *local*, i.e. assigned to a given system. When several subprocesses communicate, their own time is generally subordinated to the time of the global system, this point will be clarified in the sequel. To summarize, the essentially nondeterministic character of the asynchronous communications with the external world is concentrated here in some (ignored) external mechanism which decides this global ordering. Primitive required to specify and implement these mechanisms are precisely the only ones that are missing to let SIGNAL be a real-time language in the usual sense.

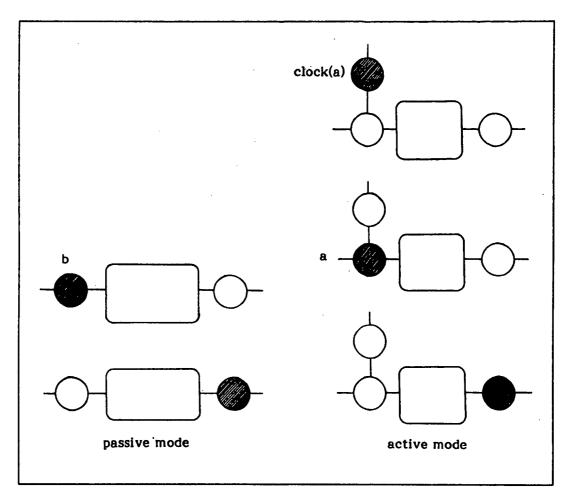

A key feature which characterizes the language SIGNAL with respect to the other synchronous languages such as ESTEREL and LUSTRE is its ability to run according to a mixed passive (i.e. data – driven in the data – flow framework) and active (i.e. demand – driven) mode of communication with the external world. On the other hand, for example, ESTEREL possesses only the passive mode. This basic feature allows in SIGNAL to tune internal clocks to the external communications, that are more frequent than the clock of the input stimuli. This mechanism is fundamental in both  $C^3$  – systems and in RTL – level simulations of SIGNAL programs.

#### 1.2 About the semantics of SIGNAL and its clock calculus.

Apart from the CSP denotational model of the language OCCAM [Brookes & al. 1984], we must emphasize on the denotational model of Dynamic Network Processes introduced by Kahn [Kahn 1974], and further studied by De Bruin and Boehm [De Bruin & Boehm 1985]. This model reveals the difficulty to handle the denotational approach in data – flow oriented systems transforming histories, which is the case of SIGNAL; in fact the second author recognized the same difficulty when writing a simple denotational model for synchronous systems [Benveniste 1985]. The reason is that to study the causality correctness of networks of processes requires the use of a difficult continuation technique [De Bruin & Boehm 1985] to prove the existence of correct fixpoint

solutions to the corresponding system of equations in the semantic domain. On the other hand, the reader can also refer to [Berry & Cosserat 1984] for an interesting discussion about the use of algebras of processes such as CCS [Milner 1980] or MEIJE [Boudol & al. 1984] as a semantic domain for the language ESTEREL. We choosed to follow the same approach as [Berry & Cosserat 1984] to give the semantics of SIGNAL, i.e. to use a direct structural operational semantics a la Plotkin [Plotkin 1981].

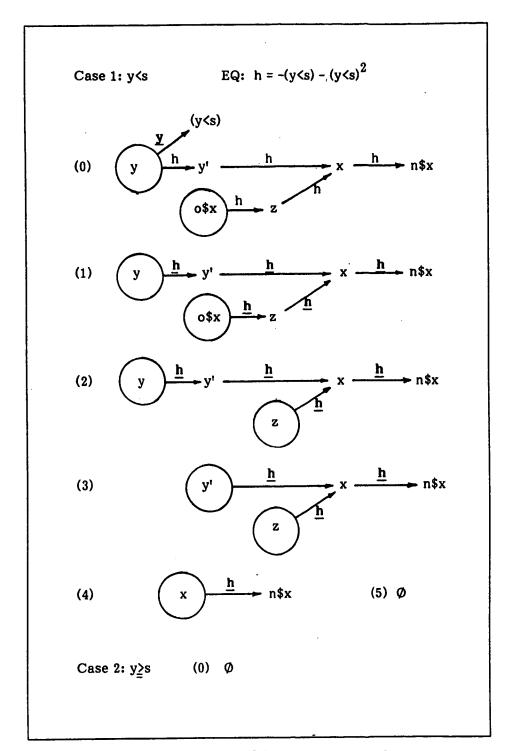

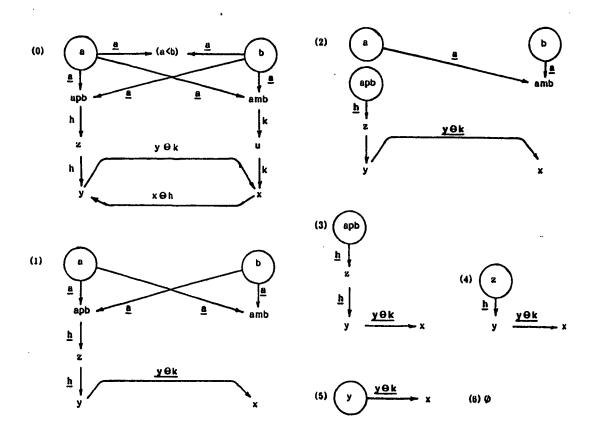

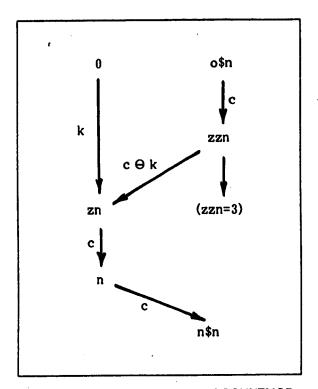

The larger flexibility of SIGNAL possesses also its drawbacks as couterparts, let us discuss briefly this point. First, some elementary SIGNAL processes induces synchrony constraints at their input ports; for example x := a + b requires that the inputs a and b be simultaneously available, i.e. have the same rate; this causes a great advantage in the efficiency of the implementation of SIGNAL programs, but this turns out to allow the programmer to write programs that can be time—incorrect. Second, the counterpart of this flexibility is that a SIGNAL process is generally nondeterministic, even if correct. The kind of semantics we use allows us to clarify these points, and to give precise definitions for "time—correctness", "determinism" and so far. As a matter of fact, this approach provides us with a simple mechanism (the technique of "cuts") to reduce a SIGNAL process to some system of polynomial equations over the commutative field Z/3Z which summarizes the timing behaviour of this process: its CLOCK CALCULUS. The checking of all timing properties of a process (such as time—correctness, determinism,...) can be directly read on the solution of this system of polynomial equations; let us point out that all polynomial functions in Z/3Z are of degree at most 2, so that the algorithm is rather staightforward.

A byproduct of the clock calculus is the possibility to get necessary and sufficient conditions for a SIGNAL process to exhibit deadlocks. The key tool is the *conditional dependence graph*, where the data dependencies are labelled by the clock that causes the considered dependency. This allows SIGNAL to accept as correct programs that are currently rejected by the dependency checker of ESTEREL. Finally, this conditional dependence graph is the convenient intermediate level of compilation for SIGNAL programs which allows *separate compilation*.

Finally, we should emphasize that we do not use the formalism of transitions as a part of the compiler of SIGNAL. Transitions are only used as theoretical tools to study notions and prove theorems. The only objects the compiler will handle are the clock calculus and the conditional dependence graph, as the computational semantics shows. The advantage is that these objects can be handled far more efficiently than transitions, so that we hope to design an efficient compiler.

#### 1.3 Organization of the article, a guide to the reader.

In the chapter 2 the kernel of SIGNAL is presented as an algebra of processes characterized by sets of transitions. First, elementary processes (called generators) are presented, then the interconnection operators are presented, which generate the complete SIGNAL algebra from these generators. This chapter is thus concerned only with syntax. The basic method is to extend a given functional instantaneous (i.e. classical) language to a language handling flows. This approach allows to introduce the key notion of *computable transitions*, that will be of importance in the sequel.

The behavioral semantics is introduced in the chapter 3; this is the part of the semantics which defines completely the temporal behavior of SIGNAL processes. Fundamental notions such as time – correctness and determinism are formally introduced and illustrated on process transitions.

A sufficient condition for checking the process congruence is given in the chapter 4; this conditions relies on the investigation of some suitable canonical form, which turns out to completely describe the network corresponding to a given process.

The chapter 5 is the fundamental one: the clock calculus is introduced in some informal way, and analysed. Its power is then illustrated on several intricate examples.

The data dependencies are analysed in the chapter 6. The key tool we introduce for this purpose is the conditional dependence graph.

The chapter 7 presents the main theorem, which states tight sufficient conditions to check time – correctness, determinism, and computability (i.e. absence of deadlock due to data dependencies). The powerful method of «cuts» is introduced for this purpose, and provides us with a rigorous justification of the clock calculus, as well as ways to build other clock calculi.

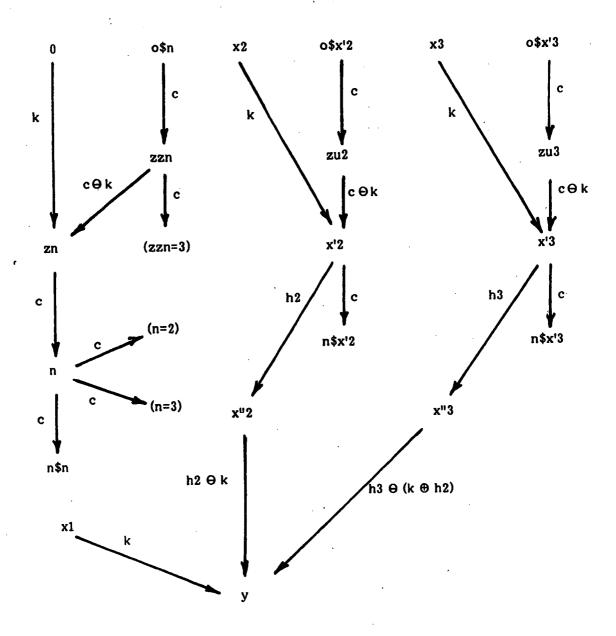

The computational semantics, i.e. the execution scheme of correct SIGNAL processes, is presented in the chapter 8. We show first how to derive a data-flow execution scheme for a correct SIGNAL process; the key point here is that, thanks to the static analysis performed by the clock calculus and the conditional dependence graph, there is no need for multiple token files in the execution of correct SIGNAL programs. Then we give the sequential computational semantics in the sense of [Berry & Cosserat 1984], i.e. we give an algorithm to build an automaton which successively fires all the generators involved in a given event of a SIGNAL process; this automaton is directly derived from the clock calculus and the conditional dependence graph.

Finally, a more subtle example is analysed in the chapter 9: the time-multiplexer. Time-

multiplexing data is a wellknown task, but is impossible to perform with other synchronous languages, since an internal clock must be introduced, which is faster than the clock of the input signal. Nevertheless, the tools we have developed can prove that the proposed SIGNAL program is time-correct and deterministic. Finally, we illustrate on this example the relevance or more powerful clock calculi which could also be derived from the method of cuts.

For a first reading, the reader could get rapidly the flavour of the language and its semantics by reading the chapters 2 (introduction of the language), 5 (clock calculus), and 6 (conditional dependence graph), together with the examples of the chapter 3. These chapters are easy to follow, and provide a good insight on the techniques we used. For example, the clock calculus itself is a good way to get intuition about time – correctness.

# Chapter Two THE KERNEL OF THE LANGUAGE SIGNAL

In this chapter, we introduce the kernel language SIGNAL, which we shall call simply SIGNAL, using the syntax of the transitions rules a la Plotkin. The principle of the kernel of the language SIGNAL is the following: we consider that an instantaneous functional language is given. Here, "instantaneous" means that the objects these functions are applied to are no more flows of data, but rather single elements. That is to say we assume we know the notions of functions and their domains of definition, and that we know a theory to calculate the dependencies induced by these functions. Then, the only job we shall accomplish is to extend this given instantaneous language to a new one, where the functions are no more applied to single elements, but rather transform histories into histories; this claim has to be understood in an informal fashion, since this point will in fact only be investigated in the behavioral semantics we shall give in the next chapter.

#### 2.1 Notations, definitions, and axioms

#### 2.1.1 The given instantaneous language

For the kernel language, we shall consider that a standard theory of functions is available; furthermore, recursivity will be forbidden. The basic instructions of this language are

$$X:=\exp$$

(2-1)

where exp denotes generically a set of expressions known by this language; here, X denotes a formal value, while exp generally involves other formal values. A program is nothing but a set of such assignments, where identical names refer to identical formal values. Among the set of expressions, we shall distinguish the *primitive boolean expressions*, such as

x < y

whereas boolean expressions are built from primitive ones using the boolean operations and, or, not.

The only important notion we shall use is the notion of dependency analysis (or causality in the

framework of [Berry and Cosserat 1984]) of a system of functions. To deal with this problem, we shall introduce the notation

$$X(a,b,c) \tag{2-2}$$

to express that the formal values a, b, c appear as arguments in the right handside of the assignment X: = exp. This relation is extended to be transitive. In our instantaneous language, recursivity will be forbidden; programs that do not exhibit recursivity will be called *computable*. The following criterion will be used in the sequel:

**DEFINITION** 1: An instantaneous program is computable if and only if there is no formal value x such that

$$x(x)$$

$\square$  (2-3)

A computable program thus defines a set of functions, together with their compositions rules through the identity of the names of some of their arguments. As a consequence, in a computable program, suitable substitutions yield an equivalent program where every formal value X depends only upon free formal values. This finishes the presentation of the instantaneous language.

#### 2.1.2 SIGNAL expressions.

To describe a SIGNAL expression, we shall use the formalism of transition rules a la Plotkin. The following example shows such a syntax:

$$< mem[omem] > \frac{p[x]}{q[y:=exp]} \rightarrow < mem[nmem:=exp'] >$$

(2-4)

In this example, *mem* denotes a memory, p an input port, and q an output port; mem[omem], p[x] expresse the fact that mem and p respectively carry the values omem and x, whereas the instructions  $y:=\exp$ ,  $nmem:=\exp$ ' have to be taken in the sense of the instantaneous language we have introduced before.

We shall need a special value, called undefined, and denoted for short by 1. This value does not

belong to the domains of the formal values of the instantaneous language we have introduced. Roughly speaking,  $\bot$  has to be interpreted as the absence of value.

We are now ready to introduce SIGNAL expressions.

**DEFINITION 1**: a SIGNAL expression is a 5 - uple

#### where

- P is the name of the expression

- \$P is a finite set of memories (or states)

- ?P is a finite set of input ports

- IP is a finite set of output ports

- TRANS is a finite set of transitions (see below) .

Memories and ports will generically be referred to as carriers. A transition is a rule of the form

$$\langle P \rangle \frac{?P}{P} \rightarrow \langle P' \rangle$$

(2-5)

#### where

- \$P denotes a list of terms of the form z[omem] where z is a memory and omem the value carried by z before the transition;

- \$P' denotes a list of terms of the form z[nmem: = exp], where the memories are the same as before, nmem is the value carried after the transition, and nmem: = exp is an instruction of the instantaneous language;

- ?P is a list of terms of the form p[x], where p is an input port carrying the value x, or of the form  $p[\bot]$ ; if p is of boolean type, the expression p[x]; x = tt, ff expresses that the considered transition can be applied when the carried value x is respectively true or false:

- !P is a list of terms of the form  $q[y: = \exp]$ , where q is an output port carrying the value y, while  $y: = \exp$  is an instruction of the instantaneous language, or of the form  $q[\bot]$ ; the expression  $q[y: = \exp]$ ; y = tt, ff is used in the same way as before.

The set of the memories, input and output ports is defined in a *static* way, while carried values depend on the transitions as we shall see later.

Example

$$P\{\$in\ ?in\ !out\} = \langle in[x] \rangle \frac{in[y]}{out[z:=\ ify>0\ then\ x+y\ else\ x]} \rightarrow \langle in[x:=y] \rangle$$

denotes the program "  $out_t = if in_t > 0$  then  $in_{t-1} + in_t$  else  $in_{t-1}$ ". We are now ready to state the axioms that a SIGNAL process must satisfy.

#### **2.1.3 Axioms**

Every SIGNAL expression P must satisfy the following list of axioms:

#### S-AXIOMS :

- S1: different input ports must have different names; different output ports must have different names (however a common name can be used for an input and an output port of the same process).

- ullet S2: if every port of a given transition carries the value  $\bot$  , then the values in the memories are unchanged after the transition.  $\Box$

COMMENTS: The axiom S1 means that ports are labelled via names. The axiom S2 is rather fundamental: it expresses that nontrivial transitions require communications with the external world; of course, only nontrivial transitions have to be given to specify a process.

We are now ready to introduce the basic instructions of SIGNAL using the syntax of the transition rules.

#### 2.2 The basic instructions

Here follow a list of the basic instructions of the language SIGNAL, and the corresponding shortened syntax we shall use to refer to them:

generators (names refer to ports):

• function:  $(q_1,...,q_l) := \exp(p_1,...,p_k)$

delay: q: = \$p

• filter: out: = in when control

merge: out: = main default second

• condition: h: = tt(C)

connection operators (capitals refer to processes, whereas lower cases refer to ports):

• relabelling of input ports: Q = P?a:b

• relabelling of output ports: Q = Pla:b

• collateral: P = Q&R

• p – connection: Q = P@x

#### 2.2.1 Generators

#### 2.2.1.1 Functions

Let

$$y_1 := \exp_1$$

$$y_k$$

: =  $\exp_k$

be instructions of the static language, where, according to (2-2),

$$y_1(x_1,...,x_n)$$

$$y_k(x_1, ..., x_n)$$

and set  $exp = (exp_1, ..., exp_k)$ ; then

$$(q_1,...,q_k) := \exp \{\$. ? p_1,...,p_n | q_1,...,q_k\}$$

$$<.> \frac{p_1[x_1]...p_n[x_n]}{q_1[y_1:=\exp_1]...q_k[y_k:=\exp_k]} \rightarrow <.>$$

(2-6)

COMMENTS: The condition that all input values must be defined plays a fundamental role in SIGNAL: it means that all input ports of a function must be involved in a non trivial transition. For example, we refuse to assign any meaning to x := y+z when y and z are not simultaneously available; as a matter of fact, we assume that such event should never occur if the program were correct. Recall that this is an arbitrary choice which is consistent with the domain of application we have in mind. This instruction extends the classical static functions to functions acting on flows. For instance, x := y+z roughly means  $x_t := y_t + z_t$  for every instant t, although this interpretation has to be handled with some care, since our notion of time is not unique, but rather multiform, as we have explained before.

#### 2.2.1.2 Delay

$$\langle in[x] \rangle = \frac{in[y]}{out[w:=x]} \rightarrow \langle in[x:=y] \rangle$$

(2-7)

COMMENT: the delay behaves then like a fifo register.

#### 2.2.1.3 Filter

out: = main when control {\$. ?main,control !out}

<.>

$$\frac{main[x] control[y]}{out[w:=x]} \rightarrow <.>$$

<.>  $\frac{main[\bot] control[y]}{out[\bot]} \rightarrow <.>$

$$<.> \frac{main[x] control[\bot]}{out[\bot]} \rightarrow <.>$$

(2-8)

COMMENT: the control port acts as a control signal: the value carried by the main port is lost if this control signal fails to be available.

#### 2.2.1.4 Merge

out : = main default second {\$. ?main, second !out}

<.>

$$\frac{main[x] second[y]}{out[w:=x]} \rightarrow <.>$$

<.>

$$\frac{main[x] second[\bot]}{out[w:=x]} \rightarrow <.>$$

<.>

$$\frac{main[\bot] second[y]}{out[w:=y]} \rightarrow <.>$$

(2-9)

COMMENT: Please, note that this "merge" operator is deterministic, since a priority has been stated in his definition.

#### 2.2.1.5 Condition

Here, c denotes a port of boolean type:

$$h: = tt(c) \{\$. ?c!h\}$$

=

<.>  $\frac{c[z]; z = tt}{h[w: = tt]} \rightarrow <.>$

<.>  $\frac{c[z]; z = ff}{h[\bot]} \rightarrow <.>$  (2-10)

where tt, ff respectively denote the boolean values true, false. In other words, the condition extracts the instants at which a boolean value is true.

CONCLUSION: It is easy to verify that these generators are SIGNAL processes, i.e. verify the S-AXIOMS. S1 has to be verified on the syntax of each instance of the given generator; on the other hand, the other axioms are trivially satisfied.

**SHORTENED NOTATION:** To avoid to write several times trivial assignments such as p[x := u], we shall simply substitute the corresponding formal values, thus writing for instance p[u], and substituting x by u in the considered transition. For instance, the first transition of when will be written simply

$$<.> \frac{main[x] control[y]}{out[x]} \rightarrow <.>$$

This shortened notation will be used in the sequel.

#### 2.2.2 Interconnection operators

The presentation of these follows the *structural conditional rewriting rules* of Plotkin, we shall comment on the first instruction. In the sequel, \$, \$' denote for short the list of the memories of a process, together with the values they carry; *?list* (resp. *!list*) denotes a list of input (resp. output) ports together with the values they carry. In the sequel, the notation \* P: transition \* will be used to indicate that the considered transition is a transition of the process P.

#### 2.2.2.1 Relabelling of input ports

Q = P?a:b is obtained as follows when both a and b are input ports of P: the same values are broadcasted to the ports a and b, and this results in a single port, named b. This is the only case in which the relabelling is different from a crude change of names.

(i) a doesn't belong to ?P:

$$P?a:b = P$$

(ii) a belongs to ?P but b doesn't:

$$P: < \$ > \frac{a[x]?list}{!list'} \rightarrow < \$' >$$

$$P?a:b : < \$ > \frac{b[x]?list}{list'} \rightarrow < \$' >$$

with the corresponding transition with  $\bot$  instead of x.

(iii) a and b belong to ?P:

P:

$$<$$

\$ >  $\frac{a[x]b[x]?list}{!list'} \rightarrow <$ \$'>

P?a:b:  $<$ \$ >  $\frac{b[x]?list}{!list'} \rightarrow <$ \$'>

with the corresponding transition with  $\bot$  instead of x.

HOW TO READ THE RULES: these rules are presented according to the syntax

The rule means that, to know the transitions of Q, one has to substitute to the transition of P the corresponding transition. Note that, in the transition (iii), the two input values carried by a and b are constrained to be the same.

PROPERTIES OF INPUT RELABELLING:

- (a) If P satisfies the axioms S1 and S2, so does P?a:b

- (b)  $?(P?a:b) = (?PU\{b\}) \{a\}$  if  $a \in ?P$

#### 2.2.2.2 Relabelling of output ports

To satisfy the axiom S1, the relabelling Q = Pla:b is not defined when both a and b are output ports of P. Otherwise, the meaning of this operator is obvious, and its definition is as follows.

(i) a doesn't belong to IP:

$$P!a:b = P$$

(ii) a belongs to IP:

$$\frac{P: < \$ > \frac{? \text{list}}{! \text{list}' \text{a}[\texttt{x}]} \rightarrow < \$' >}{P \text{la:b}: < \$ > \frac{? \text{list}}{! \text{list}' \text{b}[\texttt{x}]} \rightarrow < \$' >}$$

with the corresponding transition with  $\bot$  instead of x.

#### PROPERTIES OF OUTPUT RELABELLING:

(a) if P satisfies the axioms S1 and S2, and if a and b are not both output ports of P, then Pla:b satisfies also these axioms.

(b)

$$I(P|a:b) = (IPU\{b\}) - \{a\}$$

if  $a \in IP$ .

#### 2.2.2.3 Collateral

The operator collateral, denoted by  $Q = P_1 \& P_2$  is defined only when  $P_1$  and  $P_2$  have no common output port, to satisfy the axiom S1. The same values are broadcasted to the input ports having the same name. When  $P_1$  and  $P_2$  have no common input port, these processes are allowed to participate or not to a transition of the resulting process Q. The definition of the collateral is now given. In this definition,  $list[\bot]$  means that the mentioned ports all carry the value  $\bot$ ; this notation will be useful to mention that one of the subprocesses building the collateral does not participate to the considered transition of the resulting process Q. The label \$ refers to a list of memories, together with the values they carry.

- (i)  $P_1$  and  $P_2$  have no common input port:

- (i.a)  $P_2$  doesn't participate to the transition:

$$P_{1}: <\$_{1} > \frac{? list_{1}}{! list'_{1}} \to <\$'_{1}> \qquad P_{2}: <\$_{2} > \frac{? list_{2}[\bot]}{! list'_{2}[\bot]} \to <\$_{2}>$$

$$P_{1}\&P_{2}: <\$_{1} + \$_{2} > \frac{? list_{1}: ? list_{2}[\bot]}{! list'_{1}: ! list'_{2}[\bot]} \to <\$'_{1} + \$_{2}>$$

- (i.b)  $P_1$  doesn't participate to the transition: symmetric definition

- (i.c)  $P_1$  and  $P_2$  both participate to the transition:

$$\frac{P_{1}: <\$_{1} > \frac{? \text{list}_{1}}{! \text{list}_{1}} + <\$'_{1}> \qquad P_{2}: <\$_{2} > \frac{? \text{list}_{2}}{! \text{list}_{2}} + <\$'_{2}>}{P_{1}\&P_{2}: <\$_{1} + \$_{2} > \frac{? \text{list}_{1}: ? \text{list}_{2}}{! \text{list}_{1}: |\text{list}_{2}|} + <\$'_{1} + \$'_{2}>}$$

(ii) If a belongs to  $?P_1$  and  $?P_2$ , then choose a name b which is not a member of  $?P_1 \cup ?P_2$ ; the formula

$$P_1 & P_2 = ((P_1?a:b) & P_2) ?b:a$$

allows to define  $P_1$  &  $P_2$  by induction.

COMMENT:  $\$_1 + \$_2$  denotes the direct sum of sets. In other words, processes interconnected in collateral do not share variables.

#### PROPERTIES OF COLLATERAL:

- (a) If  $P_1$  and  $P_2$  satisfy the axioms S1 and S2, then so does  $P_1$  &  $P_2$ .

- (b) The operator & is commutative and associative.

- (c) The & satisfies the following properties:

- $\bullet$  ?(P&Q) = ?P U ?Q

- $\bullet \ !(P&Q) = !P \ U \ !Q$

- \$(P&Q) = \$(P) + \$(Q)

where \$(P) denotes the set of the memories of P.  $\square$

PROOF: rather easy although tedious.

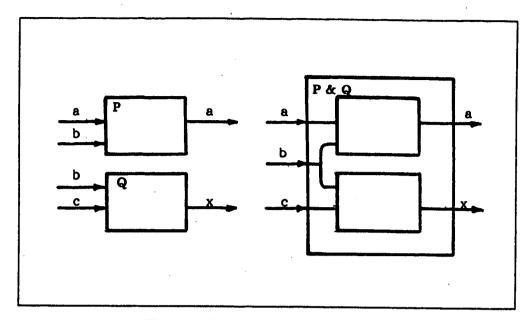

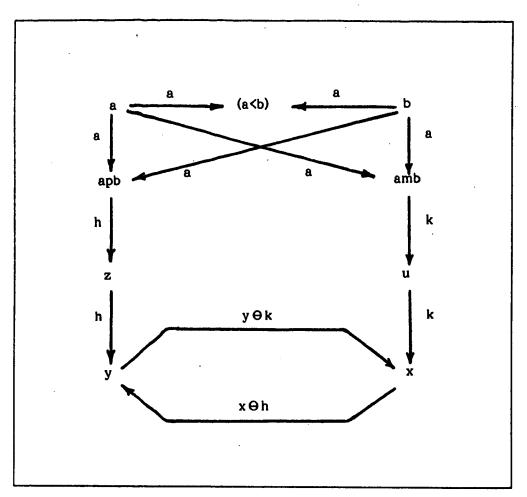

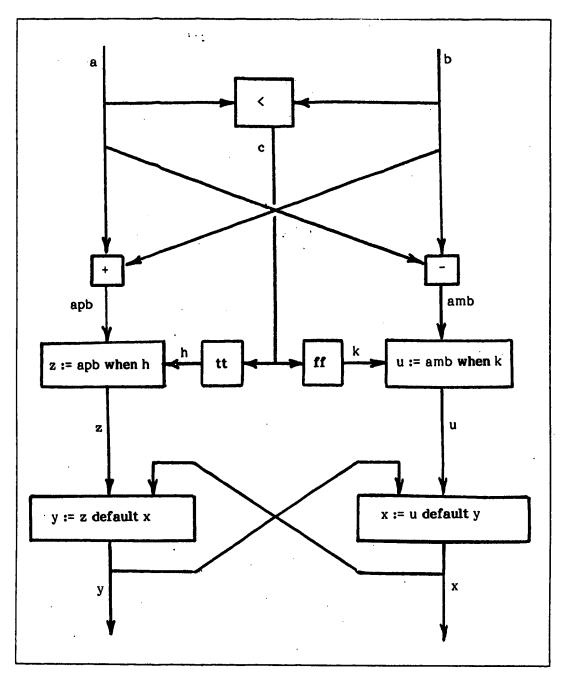

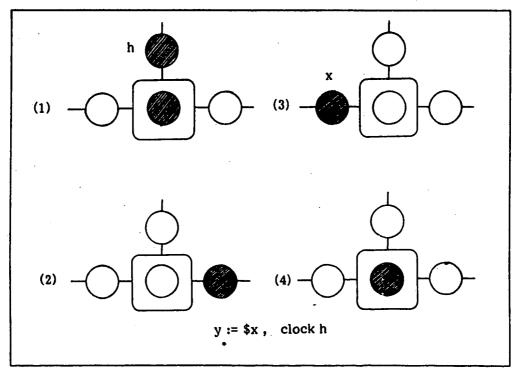

Figure 1. Block - diagram of the collateral

#### 2.2.2.4 The p-connection

The p-connection, denoted by Q = P@b, is intended to connect the output port named b to the input port of P possessing the same name. This operator is the key of process interconnections.

(i) if b doesn't belong to both ?P and !P, then

$$P@b = P.$$

(ii) Otherwise

$$\frac{P: <\$ > \frac{? \text{list } b[x]}{! \text{list' } b[x]} \rightarrow <\$'>}{P@b: <\$ > \frac{? \text{list}}{! \text{list' } b[x]} \rightarrow <\$'>}$$

(2-11)

with the corresponding transition with  $\bot$  instead of x.

WARNING: this rule is in general not effective. In fact, while values carried by input ports are free (since they are formal values), values carried by output ports are not! As a consequence, we don't

know in general the meaning of the requested transition of the original expression P, where the value x is requested at both the input port b and the output port b. To study this problem, let us investigate in more details the possible transitions of the original expression P; according to (2-5), a transition of P is of the form

$$<$$

\$>  $\frac{? list \ b[y]}{! \ list' \ b[x:=\exp]}$   $\rightarrow$  <\$'>

where \$, list, are the usual shortages. Then, two situations may occur

- x(y) holds, so that the requested transition (2-11) for P would result in the forbidden dependency x(x);

- x(y) does not hold, so that we are free to replace the formal value y carried by b by the formal value x, so that the requested transition (2-11) clearly makes sense in this case.

We shall say in this case that this transition is computable. SIGNAL expressions all transitions of which are computable are said to be computable.

If (2-11) is computable for every transition of P, we shall say that b is free in P. Then, the following theorem is easy to prove:

#### PROPERTIES OF p - CONNECTION:

- (a) If P satisfies S1 and S2, then P@b can be defined if and only if b is free in P; in this case, P@b also satisfies S1 and S2.

- (b) In this case, we have, if  $b \in ?P \cap !P$

- $?(P@b) = ?P \{b\}$

- $!(P@b) = !P \square$

In the sequel, we shall provide an algorithm to detect whether or not a requested p-connection is feasible; the job we have to achieve is to detect instantaneous short-circuits in the dependencies of the data at a given instant.

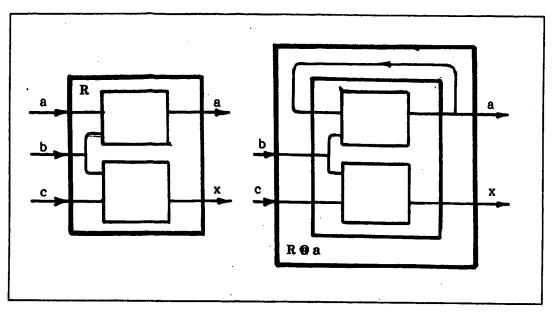

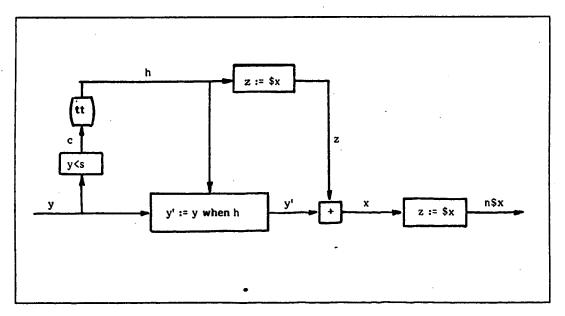

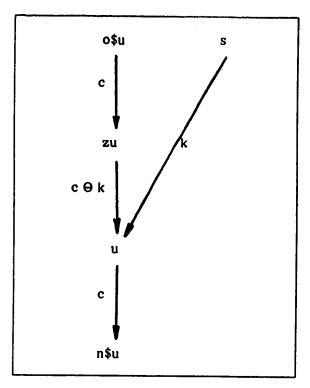

Figure 2. Block - diagram of the p-connection

CONCLUSION: We have introduced the language SIGNAL using the syntax of Conditional Rewriting Rules of Plotkin. The generators and interconnection operators generate an algebra of SIGNAL expressions: members of this algebra will be called SIGNAL processes, or processes for short.

# Chapter Three THE BEHAVIORAL SEMANTICS.

In the preceding chapter, we have defined SIGNAL processes as sets of transitions. The purpose of the behavioral semantics is to define how SIGNAL processes transform histories. Before to present this semantics, we shall need some further notations and definitions.

#### 3.1 Notations and definitions.

We shall denote by small greek letters an arbitrary effective value associated with a formal one. For example, if n is a formal value of integer type,  $\nu$  will denote one among the integers 1,2,3,... Effective values can be substituted for formal values in instructions of the static language, thus returning another effective value as a result.

Given a port p of a SIGNAL process, we shall denote by V(p) the domain of the effective values carried by p, and we set

$$V^*(p) = V(p)U\{\bot\}$$

(3-1)

#### 3.1.1 Events and histories.

#### 3.1.1.1 Input events.

Let P be a SIGNAL process, and let  $?P = \{p_1, ..., p_n\}$  be the set of the input ports of P. An input event of P is an n-uple

$$\varepsilon = \{(p_1, \varepsilon_1), ..., (p_n, \varepsilon_n)\}$$

where

$$\{\varepsilon_1,...,\varepsilon_n\} \in V^*(\rho_1)x...xV^*(\rho_n)$$

#### 3,1.1.2 Input histories.

An input history of P is a (possibly infinite) sequence  $\{\epsilon(t)\}_{t\geq 0}$  of input events of P.

To get insight in the behavioral semantics, the reader should consider that the intuitive meaning of histories is the following: given a process P

- the status of its memories before a transition summarizes the past of P

- the input event ε(0) is the present of P

- the other part of the input history, namely  $\{\varepsilon(t)\}_{t>0}$  represents the future of P.

#### 3.1.2 Allowed transitions, acceptances and refusals.

We shall denote by T(P) the set of the transitions of P, and by  $o\mu$  the k-uple of the effective values carried by the memories of P before these transitions .

#### 3.1.2.1 Allowed transitions.

Given an input event  $\varepsilon$ , we shall denote by  $T(o\mu, \varepsilon)$  the sets of the non trivial computable transitions of P that accept  $\varepsilon$  in the following sense

$T \in T(o\mu, \varepsilon)$

$$T = \langle \$[o\mu] > \frac{p_1(\varepsilon_1) \dots p_n(\varepsilon_n)}{f} \to \langle \$[n\mu] \rangle$$

(3-2)

$T(o\mu, \varepsilon)$  is the set of the transitions that are *allowed* by  $(o\mu, \varepsilon)$ . For a process all transitions of which are computable, acceptances can be checked immediately, since the expressions carried by the output ports can be rewritten so as to depend upon input values only.

see (2-11)

#### 3.1.2.2 Acceptances, refusals.

The pair  $(o\mu, \varepsilon)$  is an acceptance of P if  $T(o\mu, \varepsilon) \neq \phi$ ; otherwise,  $(o\mu, \varepsilon)$  is a refusal of P.

#### 3.1.3 Actions and runs.

#### 3.1.3.1 Actions

Given a process P, with  $\{\varepsilon(t)\}_{t\geq 0}$  as input history, and denoting by T an element of  $T(o\mu, \varepsilon(0))$ , an *action* of P is a map

$$(o\mu, \varepsilon(0)) \xrightarrow{f} (n\mu, \varepsilon(1))$$

defined by

$$T = \langle \$[o\mu] \rangle \frac{\rho_1(\varepsilon_1(0)) \dots \rho_n(\varepsilon_n(0))}{f} \rightarrow \langle \$[n\mu] \rangle$$

(3-3)

Note that a process generally possesses several actions, since  $T(o\mu,\epsilon)$  is generally not a singleton.

#### 3.1.3.2 Runs.

A finite run of P is a finite iteration of actions of P:

$$(o\mu(0), \varepsilon(0)) \xrightarrow{f_0} (o\mu(1), \varepsilon(1)) \xrightarrow{f_1} \dots \rightarrow (o\mu(t), \varepsilon(t))$$

(3-4)

of actions of P. Since the set of finite runs is ordered by prefixing, standard continuity arguments allow to extend this notion to *denumerable runs*. A finite or denumerable run will simply be called a *run*.

#### 3.1.4 Example 1.

We shall illustrate on a simple example the behavior of a SIGNAL process. Consider the following program, where, to simplify, we shall assume that k is a pure clock, i.e. possesses only a single value T:

$$P \{ n \ | \ y,z,n \} = ( (y := z+1) \& (z := n) \& (n := y \ when \ k) ) @ y,z,n \}$$

The transitions of the generators are

function +

$$<.> \frac{z[u]}{y[w:=u+1]} \to <.>$$

(3-5)

delay

$$\langle n[u] \rangle \frac{n[v]}{z[u]} \rightarrow \langle n[v] \rangle$$

(3-6)

when

$$<.> \frac{y[v] \ k[T]}{n[v]} \rightarrow <.> (i)$$

$$<.> \frac{y[\bot] \ k[T]}{n[\bot]} \rightarrow <.> (ii)$$

$$<.> \frac{y[v] \ k[\bot]}{n[\bot]} \rightarrow <.> (iii)$$

$$(3-7)$$

Transfers due to the &'s, and to the @'s yield finally the set of transitions

$$< n[u] > \frac{k[T]}{z[u] \ y[u+1] \ n[u+1]} \rightarrow < n[u+1] > (i)$$

$$< n[u] > \frac{k[T]}{z[\bot] \ y[\bot] \ n[\bot]} \rightarrow < n[u] > (ii)$$

(3-8)

The transition (3-8-i) results from the selection of the transition (3-7-i) in the application of the rules of the collateral and of the p-connection; the transition (3-8-ii) is due to the selection of the transition (3-7-ii), whereas the selection of the transition (3-7-iii) is forbidden because of the rule of the p-connection. If the initial value of the memory is 0, a provable run is

$$\langle n[0] \rangle = \frac{k[T]}{z[0] \ y[1] \ n[1]} \rightarrow$$

$\langle n[1] \rangle = \frac{k[T]}{z[1] \ y[2] \ n[2]} \rightarrow$

$\langle n[2] \rangle = \frac{k[T]}{z[2] \ y[3] \ n[3]} \rightarrow \dots$

(3-9)

which corresponds to a counter of the occurrences of the input k. But, since anyone of the transitions (3-8) can be fired with the same input stimulus, this process is obviously non deterministic: for example, an other provable run is

$$< n[0] > \frac{k[T]}{z[\bot] \ y[\bot] \ n[\bot]} \rightarrow$$

$$< n[0] > \frac{k[T]}{z[0] \ y[1] \ n[\bot]} \rightarrow$$

$$< n[1] > \frac{k[T]}{z[\bot] \ y[\bot] \ n[\bot]} \rightarrow < n[1] > \dots$$

(3-10)

In fact, this example shows a situation similar to the one studied in the counterexample of [Brock & Ackermann, 1981], and we shall see later that SIGNAL is a convenient answer to the paradox studied therein.

#### 3.2 Some problems.

#### 3.2.1 Computability of a transition.

Recall that a transition is said to be *computable* if the static instructions it uses does not exhibit short circuits such as x(x) in the sense of (2-3). We need effective criteria to recognize computable from non computable transitions, and to prove that all the transitions of a process will be computable. This will be the subject of the chapter about data dependencies.

#### 3.2.2 Time - correctness.

Given a process P and a subset  $\{p_1, ..., p_n\}$  of ?P, we shall say that the set  $\{p_1, ..., p_n\}$  is time-incorrect if

$$\exists \, \xi = \{ \, \xi_i \}_{i=1...n}, \, \, \xi_i \, \text{ effective value, such that} \\ \forall (\, \varepsilon, \eta) \, \text{ input event with } \, \varepsilon = \{ (p_1, \varepsilon_1), ..., (p_n, \varepsilon_n) \}, \, \varepsilon_i = \xi_i \, \text{ or } \, \varepsilon_i = \bot, \\ \{ (o\mu; \varepsilon, \eta) \, \text{ acceptance of } P \} \Rightarrow \{ \, \varepsilon_i = \bot \, \forall i \}$$

Roughly speaking, a subset of ports is time – incorrect if there exists a memory status and a set of candidate effective values for these ports which cannot be used whatever the other input candidates are.

A process which possesses no time-incorrect subset of input ports is said to be *fully time-correct*. Criteria of time-correctness will be obtained thanks to the *clock calculus* we shall introduce later.

#### 3.2.2.1 Example 2

Consider the following program

$$P \{ \$. ?a,b !z,x \} = ((x := a default b) \& (z := a+x)) @x$$

The function "+" requires that a and x be available simultaneously, which implies that a must be available every time b is. This illustrate the fact that a SIGNAL process can exhibit synchronization constraints at its input ports. This is a fundamental remark, since the environment of this process must be in accordance with such constraints. Note that this process is fully time - correct.

#### 3.2.2.2 Example 3

Consider the following program

$$P \{ \$. \ ?a,b \ !h,x,z \} = ((h := tt[a>0]) \& (x := a \ when \ h) \& (z := b+x)) @h,x$$

This program is intuitively time-correct; the relative timing of the input ports a and b is determined by the occurrences t of the condition [a>0], so that the synchronisation constraint on the input ports of P is somewhat more subtle in this case. This is enlightened by the set of the transitions of P, which are obtained using the rules we have defined:

<.>

$$\frac{a[u] \ b[v]}{(a > 0)[y := u > 0] : y = tt \ h[tt] \ x[u] \ z[w := u + v]} \rightarrow <.> (i)$$

<.>

$$\frac{a[u] \ b[\bot]}{(a > 0)[y] : y = ft \ h[\bot] \ x[\bot] \ z[\bot]} \rightarrow <.> (ii)$$

An acceptance can always be extracted from any candidate input effective values for a and b, so that this process is fully time-correct; however, note that b can starvate because of its environment since it is never used if a is always  $\leq 0$ , but it cannot starvate by itself.

#### 3.2.2.3 Example 4

Consider the following program

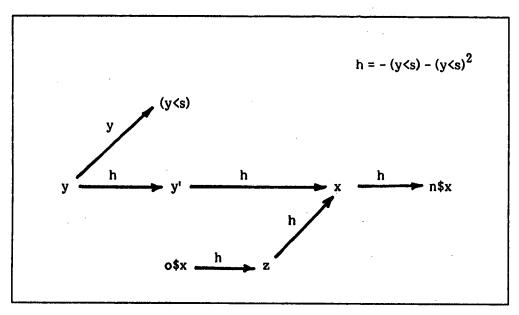

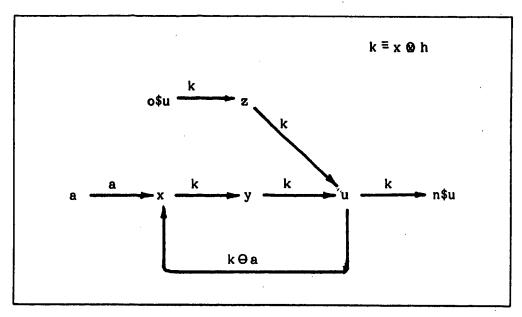

$$P \{ \$. \ ?a,b \ !h,x \} = ((h := tt[a < b]) \& (x := a when h) \& (z := x + b)) @h,x$$

The meaning of this program is "add b to a if a < b". Evaluating the condition [a < b] requires that a and b be available at the same rate. However, the instruction c : c = x + b requires that c = x + b requir

<.>

$$\frac{a[u] \ b[v]}{(a < b)[z: = u < v]:z = tt \ h[tt] \ x[u] \ z[w: = u + v]} \rightarrow <.>$$

(3-11)

which can be rewritten as

$$<.> \frac{a[u] \ b[v] : u < v}{(a < b)[z: = u < v] \ h[tt] \ x[u] \ z[w: = u + v]} \rightarrow <.>$$

(3-12)

so that no acceptance can be extracted from the input candidate (u = 1, v = 0). Consequently, the set of all the input ports of P is time – incorrect.

#### 3.2.3 Determinism.

As usually a process P is said to be deterministic if the set of its runs defines a continuous function from the set of the input histories into the set of output histories. A SIGNAL process is generally non deterministic, as the example 1 has shown. One of the main contributions of the clock calculus is to give also simple and effective criteria to check in a static way whether or not a SIGNAL process is indeed deterministic. The example 1 is a non deterministic process, since the set of the allowed transitions is not a singleton. An other example is the following.

#### 3.2.3.1 Example 5

Consider the following program, which is a slight modification of the example 1:

$$P \{ n \ ?k \ !y,z,n,x \} = ((y := z + 1) \& (z := sn) \& (n := y \ when \ x) \& (x := k \ default \ z) @ y,z,n,x \}$$

The application of the rules yields the following transitions for this process:

$$< n[u] > \frac{k[T]}{z[u] \ y[u+1] \ n[u+1] \ x[T]} \rightarrow < n[u+1] > (i)$$

$< n[u] > \frac{k[T]}{z[\bot] \ y[\bot] \ n[\bot] \ x[T]} \rightarrow < n[u] > (ii)$

$$< n[u] > \frac{k[\bot]}{z[u] \ y[u+1] \ n[u+1] \ x[u]} \rightarrow < n[u+1] >$$

(iii) (3-13)

These transitions accept the same input event with the same memory status: this process is non deterministic. As a matter of fact, if the transition (iii) is always selected, the process never uses the input event. Note that in the examples 1 and 5, if the locations of the  $\bot$  at the output ports are specified together with the memory status and input event, then only a single transition can be chosen. Since this property can also be of interest, we shall introduce it now.

#### 3.2.4 Weak determinism.

#### 3.2.4.1 Input - output events.

Let P be a SIGNAL process, and denote by  $?P = \{p_1, ..., p_n\}$ ,  $!P = \{q_1, ..., q_k\}$  the sets of the input and output ports of P. an *input-output event* (i-o event for short) is a pair

$$(\varepsilon, \kappa)$$

,  $\varepsilon$  input event,  $\kappa \subset P$

As before, i-o event allow us to define i-o histories.

#### 3.2.4.2 Input - output - allowed transitions.

Given an i-o event  $(\varepsilon, \kappa)$  and a memory status  $o\mu$ , we shall denote by  $T_{i-o}(o\mu, \varepsilon, \kappa)$  the set of the computable transitions of P which are as in (3-2) and furthermore exhibit  $\bot$  as carried exactly by those ports belonging to  $\kappa$ . This set is the set of the i-o-allowed transitions associated to  $(o\mu, \varepsilon, \kappa)$ .

#### 3.2.4.3 Weak determinism.

A process P is said to be weakly deterministic if the set of its runs defines a continuous function from the set of the i-o histories into the set of the output histories. The examples 1 and 5 are weakly deterministic processes, but processes that are not weakly deterministic can be built as well.

CONCLUSION: We have introduced the behavioral semantics of SIGNAL processes. As we have shown, SIGNAL processes are generally non deterministic. Moreover, as we have shown,

the rule of the functions can be a cause of existence of refusals for a given process. Finally, non computable processes can be constructed with the language SIGNAL. As the reader have seen, these properties could be checked on the transitions of the process, although the arguments we have used in the analysis of the example 4 are not obvious to formalize. But this would be a formidable task in the case of complex programs, where the complete set of allowed transitions is long to obtain. The major task of the forthcoming chapters will be to give much more efficient criteria to check these properties in a static way.

# Chapter Four CONGRUENT PROCESSES.

The aim of this section is to give an algorithm to detect if two apparently different processes are in fact identical, in the sense that they behave exactly in the same fashion when connected to any environment. The algorithm simply consists in a reduction of the process to some canonical form, which characterizes any congruence class. The present algorithm is borrowed from [Gautier 1984].

#### **DEFINITION 2**:

- (i) Two processes P and Q are said to be *congruent* if they admit the same transitions, up to a global bijection between the names of their respective memories, and a global bijection between the names of the the carried values of P and the carried values of Q.

- (ii) Two processes P and Q are said to be *equivalent* if they admit the same transitions up to bijections, respectively between the names of their ports, the names of their memories, and the names of their carried values.  $\Box$

Our definition of congruence is in accordance with the usual one: two processes are congruent in the sense of the above definition, if and only if they behave similarly when they are connected to a given arbitrary process. On the other hand, it is immediate to transform equivalent processes into congruent ones through a relabelling of their ports, so that we shall only give an algorithm to transform any process into an equivalent canonical form. This section is devoted to the proof of the basic theorem 2.

Before to state and prove this theorem, we shall need some further properties of the interconnection operators. Here, "internal properties" refers to properties involving a single operator, while "external properties" refers to properties involving different operators.

#### INTERNAL PROPERTIES OF INTERCONNECTION OPERATORS.

- 1. & is associative and commutative.

- 2.  $\emptyset$  is commutative in the sense that, when a is free in P and b is free in  $P \otimes a$ , then b is free in P and a is free in  $P \otimes b$ , and vice versa. In this case, it is true that  $(P \otimes a) \otimes b = (P \otimes b) \otimes a$ , denoted by  $P \otimes a \otimes b$ .

**PROOF**: we shall only prove (2), since (1) is already known. To prove (2), we shall make use of the theory of dependency for static functions. To denote that a static function x(...) does not depend on the value y, we shall write

$$x(>y<) \tag{4-1}$$

To denote that a value z is substituted for y in a static function x, we shall write

$$x^{y \leftarrow z} \tag{4-2}$$

When z is itself the value of a static function, the substitution results in the composition of the corresponding maps. We are now ready to begin the proof. Let us denote respectively by y and x (resp. y' and x') the values carried by the ports ?a and b (resp. ?b and b). Assume that a is free in a, and b free in a0 free in a2. Then, according to the notation (4-1), we have first

$$x(>y<) \tag{4-3}$$

Thanks to (4-3), it is possible to define P@a. According to the rule of the p-connection, the ports ?b and !b of this latter process respectively carry the values

Since b is free in P@a, we have

$$x'^{y\leftarrow x}(>y'<) \tag{4-4}$$

But (4-4) implies that

$$X'(>y'<) \tag{4-5}$$

and also

$$x'(>y<) \quad \text{or} \quad x(>y'<) \tag{4-6}$$

But (4-5) means that b is free in P, so that we can define P@b; as a consequence, the ports ?a and !a respectively carry the values

But, thanks to (4-6), we have

$$x^{y'\leftarrow x'}(>y<)$$

so that a is free in P@b. That (P@a)@b = (P@b)@a can be proven in the same way. This finishes the proof.  $\square$

As a consequence, the above mentioned operators can be used as disordered lists. Note that the relabelling is non commutative as yhe following example shows: (P?a:b)?b:c is generally different from (P?b:c)?a:b, so that, in the sequel, a repeated use of relabellings has to be considered as an ordered list. We are now ready to state and to prove the main theorem of this section.

**THEOREM 2**: Every process P is equivalent to a process  $P_o$ , which is said to be in *canonical* form, i.e. of the form

$$P_0 = (\&(G ?a:x !b:y)) @c$$

(4-7)

#### where

- G is a generic name of generator

- ?a:x denotes a list of input relabellings, and !b:y a list of output relabellings; a and b

denote generic names of ports of generators, while x and y are not port names of

generators;

- &(...) denotes a list of collaterals with (...) as generic subprocess;

- @c denotes a list of p connections.

P equivalent to  $P_o$  will be denoted by

$$P \approx P$$

Moreover, this canonical form is unique in the following sense: if  $P_o$  and  $P'_o$  are two equivalent canonical forms, then there exists a bijection mapping the port names of  $P'_o$  on the port names

of  $P_o$  such that the resulting (non ordered) lists &(G...) and &(G'...); be the same, up to a permutation on the relabellings .

PROOF: The formula (4-7) exhibits the following hierarchy between the different interconnection operators:

The proof of the theorem (which is a constructive one) relies on the construction of a suitable permutation of the different operators to achieve the ordering indicated in (4-8). Since every permutation is the composition of a sequence of transpositions (i.e. permutations involving only 2 terms), the proof of the theorem is a direct consequence of the following list of properties we shall state without proof. In these formulas, by convention, the name w, which will appear on the right handside of the character  $\approx$ , will generically denote a name of port which is not used in the left handside. Of course, the below listed equivalences are valid only when both sides are well defined SIGNAL processes (i.e. do satisfy the S-axioms). Here follow the list of formulas:

EXTERNAL PROPERTIES OF THE INTERCONNECTION OPERATORS.

- $(P@x) & Q \approx ((P?x:w|x:w) & Q) @w$

- (P@x) ?a:b ≈ (P ?x:w ?a:b !x:w) @w