## Formal Methods for Schedulings of Latency-Insensitive Designs

Julien Boucaron, Jean-Vivien Millo, Robert de Simone

## ▶ To cite this version:

Julien Boucaron, Jean-Vivien Millo, Robert de Simone. Formal Methods for Schedulings of Latency-Insensitive Designs. [Research Report] RR-6149, INRIA. 2007, pp.25. inria-00137495v2

## HAL Id: inria-00137495 https://hal.inria.fr/inria-00137495v2

Submitted on 22 Mar 2007  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# Formal Methods for Scheduling of Latency-Insensitive Designs

Julien Boucaron

— Jean-Vivien Millo — Robert de Simone

## N° 6149

Mars 2007

Thème COM

ISSN 0249-6399 ISRN INRIA/RR--6149--FR+ENG

## Formal Methods for Scheduling of Latency-Insensitive Designs

Julien Boucaron , Jean-Vivien Millo , Robert de Simone

Thème COM — Systèmes communicants Projets Aoste

Rapport de recherche $\,$ n° 6149 — Mars 2007 — 32 pages

**Abstract:** (*Latency-Insensitive Design*) theory was invented to deal with SoC *timing closure* issues, by allowing arbitrary fixed integer latencies on long global wires. Latencies are coped with using a *resynchronization* protocol that performs dynamic scheduling of data transportation. Functional behaviour is preserved.

This dynamic scheduling is implemented using specific synchronous hardware elements: *Relay-Stations (RS)* and *Shell-Wrappers (SW)*. Our first goal is to provide a formal modeling of RS and SW, that can then be formally verified.

As turns out, resulting behaviour is k-periodic, thus amenable to *static* scheduling. Our second goal is to provide formal hardware modeling here also. It initially performs *Throughput Equalization*, adding integer latencies wherever possible; residual cases require introduction of *Fractional Registers* (*FRs*) at specific locations.

Benchmark results are presented, run on our KPassa tool implementation.

**Key-words:** repetitive cyclic scheduling, formal models, synchronous languages, digital circuits, latency insensitive designs, Systems-on-chip, electronic system-level design

## Méthodes formelles pour ordonnancer des systèmes Latency-Insensitive

**Résumé :** La théorie de Conception Insensible aux latences (LID) a été inventée pour traiter des questions de clôture temporelle dans les Systèmes-sur-Puce (SoC). L'objectif est d'autoriser des latences arbitraires (mais constantes) sur les longues connexions globales du système. Les différences entre latences sont gérées par un protocole de contrôle de flux, qui aboutit à une resynchronisation par ré-ordonnancement dynamique des transports de données.

Un aspect important de la théorie est de définir des éléments synchrones, de nature matérielle, permettant de synthétiser ces mécanismes protocolaires et les implantations de connexions latentes qui les supportent: ce sont les *Station-Relais*, pour diviser les connexions en segments de latence unitaire, et les *Conteneurs* de composants IP pour définir l'horloge explicite d'activation de ces composants. Notre premier but dans ce rapport est de donner une spécification formelle de ces éléments, qui puissent être combinés et dont la correction effective soit effectivement prouvée.

Il apparaît ensuite que, sous certaines hypothèses naturelles de structure, le comportement des systèmes LID se révèle ultimement k-periodique, et donc que des ordonnancements statiques se révèlent calculables de manière exacte avant exécution. Ceci utilise des travaux déjà établis dans d'autres contextes, que nous rappelons. Nous utilisons ensuite ces résultats pour optimiser radicalement l'implantation des protocoles, substituer des Registres Fractionnaires (FR) plus simples aux Stations de Relais, et rendre superflue la signalisation du contrôle de flux. Ceci réclame plusieurs étapes, dont une *égalisation* en valeur entière des latences admissibles dans les boucles comportementales, et un calcul d'accessibilité pour déterminer les lieux résiduels d'insertion de FRs.

Ces algorithmes ont été implantés dans un logiciel KPASSA, dont nous étudions l'efficacité sur des cas d'étude.

**Mots-clés :** ordonnancement cyclique répétitif, modèles formels, langages synchrones, circuits digitaux, systèmes insensibles à la latence, Système-sur-Puce, Conception de systèmes electroniques

### 1 Introduction

Long wire interconnect latencies induce time-closure difficulties in modern SoC designs, with propagation of signals across the die in a single clock cycle is problematic. The theory of *Latency-Insensitive Design (LID)*, proposed originally by Luca Carloni, Kenneth McMillan and Alberto Sangiovanni-Vincentelli [7, 8], offers solutions for this issue. This theory can roughly be described as such: an initial fully synchronous reference specification is first desynchronized as an asynchronous network of synchronous block components (a *GALS* system); it is then re-synchronized, but this time with proper interconnect mechanisms allowing specified (integer-time) latencies.

Interconnects consist of fixed-sized lines of so-called *Relay-Stations*. These *Relay-Stations*, together with *Shell-Wrapper* around the synchronous *Pearl* IP blocks, are in charge of managing the signal value flows. With their help proper regulation of the signal traffic is performed. Computation blocks may be temporarily paused at times, either because of input signal unavailability, or because of the inability of the rest of the network to store their outputs if they were produced. This latter issue stems from the limitation of fixed-size buffering capacity of the interconnects (*Relay-Station* lines).

Since their invention *Relay-Stations* have been a subject of attention for a number of research groups. Extensive modeling, characterization and analysis were provided in [9, 14, 13].

We mentioned before that the process of introducing latencies into synchronous networks introduced, at least conceptually, an intermediate asynchronous representation. This corresponds to *Marked Graphs* [16], a well-studied model of computation in the literature. The main property of *Marked Graph* is the absence of choice which matches with the absence of control in *LID*.

Marked Graphs with latencies were also considered under the name of Weighted Marked Graphs (WMG)[19]. We shall reduce WMGs to ordinary Marked Graphs by introducing new intermediate Transportation Nodes (TN), akin to the previous Computation Nodes (CN) but with a single input and output link. In fact LID systems can be thought of as WMGs with buffers of capacity 2 (exactly) on link between Computation and/or Transportation Nodes. The Relay-Stations and Shell-Wrappers are an operational means to implement the corresponding flow-control and congestion avoidance mechanisms with explicit synchronous mechanisms.

The general theory of WMG provides many useful insights. In particular it teaches us that there exists static repetitive scheduling for such computational behaviors [6, 2]. Such static kperiodic schedulings have been applied to software pipelining problems [18, 5], and later SoC LID design problems in [12]. But these solutions pay in general little attention to the form of buffering elements that are holding values in the scheduled system, and their adequacy for hardware circuit representation. We shall try to provide a solution that "perfectly" equalizes latencies over reconvergent paths, so that token always arrive simultaneously at the *Computation Node*. Sadly, this cannot always be done by inserting an integer number of latency under the form of additional transportation sections. One sometimes need to hold back token for one step discriminatingly ans sometimes does not. We provide our solution here under the form of *Fractional Registers (FR)*, that may hold back values according to an (input) regular pattern that fits the need for flowcontrol. Again we contribute explicit synchronous descriptions of such elements, with correctness properties. We also rely deeply on a syntax for schedule representation, borrowed from the theory of *N-synchronous processes* [15].

Explicit static scheduling that uses predictable synchronous elements is desirable for a number of issues. It allows *a posteriori* precise re-dimensioning of glue buffering mechanisms between local synchronous elements to allow the system to work, and this without affecting the components themselves. Finally, the extra virtual latencies introduced by equalization could be absorbed by the local computation times of *CN*, to resynthesize them under relaxed timing constraints.

We built a prototype tool for equalization of latencies and *Fractional Registers* insertion. It uses a number of elaborated graph-theoretical and linear-programming algorithms. We shall briefly describe this implementation.

**Contributions:** Our first contribution is to provide a formal description of *Relay-Stations* and *Shell-Wrappers* as synchronous elements [4], something that was never done before in our knowl-

edge (the closest effort being [10]). We introduce local correctness properties that can easily be model-checked; these generic local properties, when combined, ensure the global property of the network.

We introduce the *Equalization process* to statically schedule a *LID* Specification: slowing down "too fast" cycles while maintaining the original throughput of the *LID* Specification. **The goal** is to simplify the *LID* protocol.

But rational difference of rates may still occur after *Equalization process*, we solve it by adding *Fractional Registers (FR)*, that may hold back values according to a regular pattern that fits the need for flow-control.

We introduce a new class of *smooth* schedules that optimally-minimizes the number of FRs used on a statically scheduled LID design.

Article Outline: In the next Section we provide some definitional and notational background on various models of computations involved in our modeling framework, together with an explicit representation of periodic schedules and firing instants; with this we can state historical results on k-periodic scheduling of WMGs. In Section 3 we provide the synchronous reactive representation of Relay-Stations and Shell-Wrappers, show their use in dynamic scheduling of Latency-Insensitive Design, and describe several formal local correctness properties that help with the global correctness property of the full network. Statically scheduled LID systems are tackled in Section 4; we describe an algorithm to build a statically scheduled LID, possibly adding extra virtual integer latencies and even Fractional Registers. We provide a running example to highlight potential difficulties. We also present benchmarks result of a prototype tool which implements the previous algorithms and their variations. We conclude with considerations on potential further topics.

## 2 Modeling Framework

#### 2.1 Computation nets

We start from a very general definition, describing what is common of all our models.

**Definition 1** (Computation Network Scheme). We call *Computation Network Scheme* (*CNS*) a graph whose vertices are called *Computation Nodes*, and whose arcs are called *links*. We also allow arcs without a source vertex, called *input links*, or without target vertex, called *output links*.

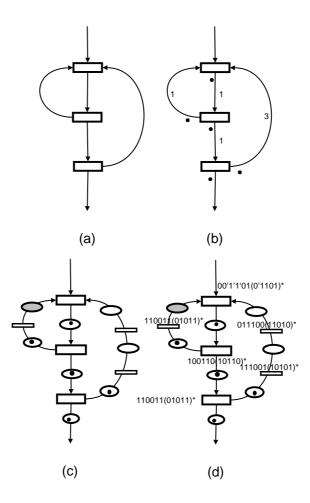

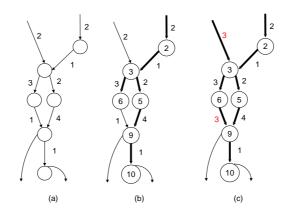

An instance of a *CNS* is depicted on Figure 1 (a).

The intention is that *Computation Nodes* perform computations by **consuming a data on** each of its incoming *links*, and producing as a result a new data on each of its outgoing *links*.

The occurrence of a computation thus only depends on data presence and not their actual values, so that data can be safely abstracted as *tokens*. A *CNS* is choice free.

In the sequel we shall often consider the special case where the *CNS* forms a strongly connected graph, unless specified explicitly.

This simple model leaves out the most important features, that are mandatory to define its operational semantics under the form of behavioral firing rules. Such features are:

- the *initialization* setting (where do tokens reside initially),

- the nature of *links* (combinatorial wires, simple registers, bounded or unbounded *place*, ...),

- and the nature of *time* (synchronous, with computations firing simultaneously as soon as they can, or asynchronous, with distinct computations firing independently).

Setting up choices in these features provides distinct Models of Computation.

Figure 1: (a) An example of CNS (with rectangular Computation Nodes), (b) a corresponding WMG with latency features and token information, (c) a SMG/LID with explicit (rectangular) Transportation Nodes and (oval) places/Relay-Stations, dividing arcs according to latencies, (d) a LID with explicit schedules

#### 2.2 Synchronous/asynchronous versions

**Definition 2.** A Synchronous Reactive Net (S/R net) is a CNS where time is synchronous: all Computation Nodes fire simultaneously. In addition links are either (memoryless) combinatorial wires or simple registers, and all such registers initially hold a token.

The S/R model conforms to synchronous digital circuits or (single-clock) synchronous reactive formalisms [3]. The network operates "at full speed": there is always a value present in each register, so that CNs operates at each instant. As a result, they consume all values (from registers and through wires), and replace them again with new values produced in each register. The system is *causal* iff there is at least one register along each cycle in the graph. Causal S/R nets are well-behaved in the sense that their semantics is well-founded.

**Definition 3.** A Marked Graph is a CNS where time is asynchronous: computations are performed independently, provided they find enough tokens in their incoming links; links have a place holding a number of tokens; in other words, Marked Graphs form a subclass of Petri Nets. The initial marking of the graph is the number of tokens held in each place. In addition a Marked Graph is said to be of capacity k if each place can hold no more than k tokens. There is a simple way to encode *Marked Graphs* with capacity as *Marked Graphs* with unbounded capacity: this requires to add a reverse *link* for each existing one, which contains initially a number of tokens equal to the difference between the capacity and the initial marking of the original *link*.

It was proved that a strongly connected *Marked Graph* is live (each computation can always be fired in the future) iff there is at least one token in every cycle in the graph [16]. Also, the total number of tokens in a cycle is an invariant, so strongly connected *Marked Graphs* are k-safe for a given capacity k.

Under proper initial conditions S/R nets and *Marked Graphs* behave essentially the same, with S/R systems performing all computations simultaneously "at full rate", while similar computations are now performed independently in time in *Marked Graph*.

**Definition 4.** A Synchronous Marked Graph (SMG) is a Marked Graph with an ASAP (As Soon As Possible) semantics: each Computation Node (transition) that may fire due to the availability of it input tokens immediately does so (for the current instant).

SMGs and the ASAP firing rule are underlying the works of [6, 2], even though they are not explicitly given name there.

Figure 1 (c) shows a Synchronous Marked Graph. Note that SMGs depart from S/R models: here all tokens are not always available.

#### 2.3 Adding latencies and time durations

We now add latency information to indicate transportation or computation durations. These latencies shall be all along constant integers (provided from "outside").

**Definition 5.** A Weighted Marked Graph (WMG) is a CNS with (constant integer) latency labels on links. This number indicates the time spent while performing the corresponding token transportation along the link.

We avoid computation latencies on CNs, which can be encoded as transportation latencies on links by splitting the actual CN into a begin/end\_CN. Since latencies are global time durations, the relevant semantics which take same into account is necessarily ASAP. The system dynamics also imposes that one should record at any instant "how far" each token is currently in its travel. This can be modeled by an age stamp on token, or by expanding the WMG links with new Transportation Nodes (TN) to divide them into as many sections of unit latency. TNs are akin to CNs, with the particularity that they have unique source and target links. This expansion amounts to reducing WMGs to (much larger) plain SMGs. Depending on the concern, the compact or the expanded form may be preferred.

Figure 1 (b) displays a *Weighted Marked Graph* obtained by adding latencies to figure (a), which can be expanded into the SMG of figure (c).

For correctness matters there should still be at least one token along each cycle in the graph, and less token on a *link* than its prescribed latency. This corresponds to the correctness required on the expanded SMG form.

**Definition 6.** A Latency-Insensitive Design (LID) is a WMG where the expanded SMG obtained as above uses places of capacity 2 in between CNs and TNs.

This definition reads much differently than the original one in [8]. This comes partly from an important concern of the authors then, which is to provide a description built with basic components (named *Relay-Stations* and *Shell-Wrappers*) that can easily be implemented in hardware. Next Section 3 provides a formal representation of *Relay-Stations* and *Shell-Wrappers*, together with their properties.

**Summary** CNS lead themselves quite naturally to both synchronous and asynchronous interpretations. Under some easily expected initial conditions, these variants can be shown to provide the same input/output behaviours. With explicit latencies to be considered in computation and data transportation this remains true, even if congestion mechanisms may be needed in case of bounded resources. The equivalence in the ordering of event between a synchronous circuit and a LID circuit is shown in [7], and equivalence between a MG and a S/R design is shown in [20].

#### 2.4 Periodic behaviors, throughput and explicit schedules

We now provide the definitions and classical results needed to justify the existence of static scheduling. This will be used mostly in Section 4, when we develop our formal modeling for such scheduling using again synchronous hardware elements.

**Definition 7** (Rate, throughput and critical cycles). Let G be a WMG graph, and C a cycle in this graph.

The rate R of the cycle C is equal to  $\frac{T}{L}$ , where T is the number of tokens in the cycle, and L is the sum of latencies of the arcs of this given cycle.

The *throughput* of the graph is defined as the minimum rate among all cycles of the graph. A cycle is called *critical* if its rate is equal to the *throughput* of the graph.

A classical result states that, provided simple structural correctness conditions, a stronglyconnected WMG runs under a ultimately k-periodic schedule, with the throughput of the graph [6, 2]. We borrow notation from the theory of *N*-synchronous processes [15] to represent these notions formally, as explicit analysis and design objects.

**Definition 8** (Schedules, periodic words, k-periodic schedules). A pre-schedule for a CNS is a function Sched :  $N \to w_N$  assigning an infinite binary word  $w_N \in \{0, 1\}^{\omega}$  to every Computation Node and Transportation Node N of the graph. Node N is activated (or triggered, or fired, or run) at global instant i iff  $w_N(i) = 1$ , where w(i) is the  $i^{th}$  letter of word w.

A pre-schedule is a *schedule* if the allocated activity instants are in accordance with the token distribution (the lengthy but straightforward definition is left to the reader). Furthermore, the schedule is called ASAP if it activates a node N whenever all its input tokens have arrived (according to the global timing).

An infinite binary word  $w \in \{0,1\}^{\omega}$  is called *ultimately periodic*: if it is of the form  $u.(v)^{\omega}$  where u and  $v \in \{0,1\}^*$ , u represents the initialization phase, and v the periodic one.

The *length* of v is noted |v| and called its *period*. The number of occurrences of 1s in v is denoted  $|v|_1$  and called its *periodicity*. The *rate* R of an ultimately periodic word w is defined as  $\frac{|v|_1}{|v|}$ .

A schedule is called k-periodic whenever for all  $N, w_N$  is a periodic word.

Thus a schedule is constructed by simulating the CNS according to its (deterministic) ASAP firing rule.

Furthermore, it has been shown in [2] that the length of the stationary periodic phase (called period) can be computed based on the structure of the graph and the (static) latencies of cycles: for a CSCC (Critical Strongly Connected Component) the length of the stationary periodic phase is the GCD (Greatest Common Divisor) over latencies of its critical cycles. For instance assume a CSCC with 3 critical cycles having the following rates: 2/4, 4/8, 6/12, the GCD of latencies over its critical cycles is: 4. For the graph, the length of its stationary periodic phase is the LCM (Least Common Multiple) over the ones computed for each CSCCs. For instance assume the previous CSCC and another one having only one critical cycle of rate 1/2 then the length of the stationary periodic phase of the whole graph is 2.

Figure 1(d) shows the schedules obtained on our example. If latencies were "well-balanced" in the graph, tokens would arrive simultaneously at their consuming node; then, the schedule of any Node should exactly be the one of its predecessor(s) shifted right by one position. However it is not the case in general when some input tokens have to stall awaiting others. The "difference" (target schedule minus 1-shifted source schedule) has to be coped with by introducing specific buffering

elements. This should be limited to the locations where it is truly needed. Computing the static scheduling this allows to avoid adding the second register that was formerly needed everywhere in RSs, together with some of the backpressure scheme.

The issue arises in our running example only at the top-most *Computation Node*. We indicate it by prefixing some of the inactive steps (0) in its schedule by symbols: lack of input from the right input *link* ('), or from the left one (').

## 3 Synchronous to LID: Dynamic Schedule

In this Section we shall briefly recall the theory of *Latency-Insensitive Design*, and then focus on formal modeling with synchronous components of its main features [4].

LID theory was introduced in [7]. It relies on the fact that links with latency, seen as physical long wires in synchronous circuits, can be segmented into sections. Specific elements are then introduced in between sections. Such elements are called *Relay-Stations (RS)*. They are instantiated at the oval places in Figure 1(c). Instantaneous communication is possible inside a given section, but the values have to be buffered inside the RS before it can be propagated to the next section. The problem of computing realistic latencies from physical wire lengths was tackled in [11], where a physical synthesis floor-planner provides these figures.

*Relay-Stations* are complemented with so-called *Shell-Wrappers (SW)*, which compute the firing condition for their local synchronous component (called *Pearl* in *LID* theory). They do so from the knowledge of availability of input token and output storage slots.

#### 3.1 Relay-Stations

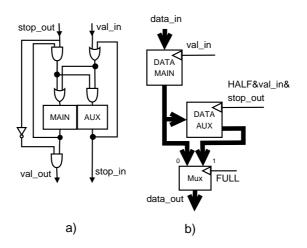

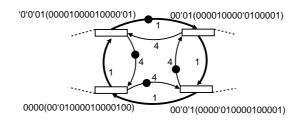

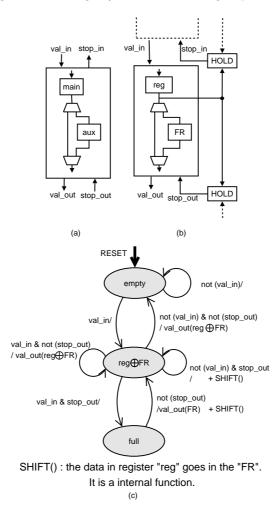

The signaling interface of a *Relay-Station* is depicted in Figure 2. The val signals are used to propagate tokens, the stop signal are used for congestion control. For symmetry here stop\_out is an input and stop\_in an output.

Figure 2: Relay-Station - Block Diagram

Intuitively the *Relay-Station* behaves as follows: when traffic is clear (no stop), each token is propagated down at the next instant from the one it was received. When a **stop\_out** signal is received because of downward congestion, the *RS* keeps its token. But then, the previous section and the previous *RS* cannot be warned instantly of this congestion, and so the current *RS* can perfectly well receive another token at the same time it has to keep the former one. So there is a need for the *RS* to provide a second auxiliary register slot to store this second token. Fortunately there is no need for a third one: in the next instant the *RS* can propagate back a **stop\_in** control information to preserve itself from receiving yet another value. Meanwhile the first token can be sent as soon as **stop\_out** signals are withdrawn, and the *RS* remains with only one value, so that in the next step it can already allow a new one and not send its congestion control signal. Note that in this scheme there is no undue gap between the token sent.

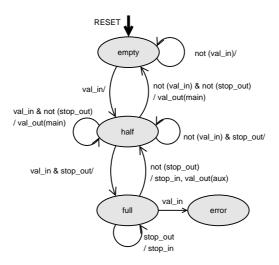

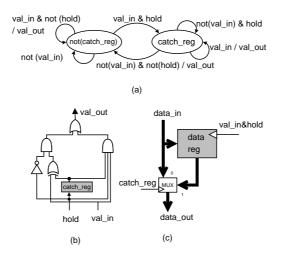

This informal description is made formal with the description of a synchronous circuit with two registers describing the RS in Figure 3, and its corresponding synchart [1] (in Mealy FSM style) in Figure 4.

The syncchart contains 4 states:

empty when no token are currently buffered in the RS; in this state the RS simply waits for a valid input token coming, and store it in its main register then it goes to state half. stop\_out signals are ignored, and not propagated upstream, as this RS can absorb traffic.

Figure 3: Relay-Station - a) Control Logic b) Data Path

Figure 4: Relay-Station synchart

- half when it holds one token; Then the RS only transmits its current, previously received token if ever it does not receive an halting stop\_out signal. If halting is requested, (stop\_out), then it retains its token, but must also accept a potential new one coming from upstream (as it has not sent any back-pressure holding signal yet). In the second case it becomes full, with the second value occupying its "emergency" auxiliary register. If the RS can transmit (stop\_out = false), it either goes back to empty or retrieve a new valid signal (val\_in), remaining then in the same state. On the other hand it still makes no provision to propagate back-pressure (in the next clock cycle), as it is still unnecessary due to its own buffering capacity.

- full when it contains two tokens; then it raises in any case the stop\_in signal, propagating to the upstream section the hold-out stop\_out signal received in the previous clock cycle. If it does not itself receive a new stop\_out, then the line downstream was cleared enough so that it can transmit its token; otherwise it keeps it and remains halted.

- error is a state which should never be reached (in an *assume/guarantee* fashion). The idea is that there should be a general precondition stating that the environment will never send

the *val\_in* signal whenever the RS emits the *stop\_in* signal. This should be extended to *any* combination of RS, and build up a "sequential care-set" condition on system inputs. The property is preserved as a postcondition as each RS will guarantee correspondingly that *val\_out* is *not* sent when *stop\_out* arrives.

*NB:* The notation *val\_out(main)* or *val\_out(aux)* means emit the signal *val\_out* taking its value in the buffer, respectively, *main* or *aux*.

**Correctness properties** Global correctness depends upon an assumption on the environment (see description of **error** state above). We now list a number of properties that should hold for *Relay-Stations*, and further *links* made of a connected line  $L_n(k)$  of *n* successive *RS* elements and currently containing *k* values (remember that a line of *n* RS can store 2n values).

On a single RS:

- $\Box \neg (stop\_out \land val\_out)$  (back-pressure control takes action immediately);

- $\Box$  ((stop\_out \land X(stop\_out))  $\Rightarrow$  X(stop\_in) (a stalled RS gets filled in two steps)

where  $\Box$ ,  $\Diamond$ ,  $\mathcal{U}$  and X are the traditional Always, Eventually, Until and Next (linear) temporal logic operators. More interesting properties can be asserted on lines of RS elements (we assume that by renaming stop\_{in, out} and val\_{in, out} signals form the I/O interface of the global line  $L_n(k)$ ):

- $\Box$  ( $\neg$ stop\_out  $\Rightarrow \neg X^n(stop\_in)$ ) (free slots propagate backwards);

- $\Box((stop\_out \ U \ X^{(2n-k)}(true)) \Rightarrow X^{(2n-k)}(stop\_in))$  (overflow);

- $(\Diamond val\_in \land \Box(\Diamond(\neg stop\_out)) \Rightarrow \Diamond val\_out$  (if traffic is not completely blocked from below from a point on, then tokens get through)

The first property is true of any line of length n, the second of any line containing initially at least k tokens, the third of any line.

We have implemented RSs and lines of RSs in the Esterel synchronous language, and modelchecked combinations of these properties using  $EsterelStudio^{1} \mathbb{M}$ .

#### 3.2 Shell-Wrappers

The purpose of *Shell-Wrappers* is to trigger the local *Computation Node* exactly when tokens are available from each *input link*, and there is storage available for result in *output links*. It corresponds to a notion of *clock gating* in circuits: the *SW* provides the logical clock that activates the IP component represented by the *CN*. Of course this requires that the component is physically able to run on such an irregular clock (a property called *patience* in *LID* vocabulary), but this technological aspect is transparent to our abstract modeling level. Also, it should be remembered that the *CN* is supposed to produce data on all its outputs while consuming on all its inputs in each computation step. This does not imply a combinatorial behavior, since the *CN* itself can contain internal registers of course. A more fancy framework allowing *computation latencies* in addition to our communication latencies would have to be encoded in our formalism. This can be done by "splitting" the node into a **begin\_CN** and a **end\_CN** nodes, and installing internal transportation links with desired latencies between them; if the outputs are produced with different latencies one should even split further the node description. We shall not go into further details here, and keep the same abstraction level as in *LID* and *WMG* theories.

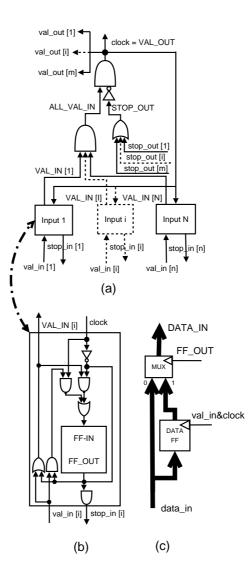

The signal interface of SWs consists of val\_in and stop\_in signals indexed by the number of *input links* to the SW, and of val\_out and stop\_out signals indexed by the number of its *output links*. There is an output clock signal in addition, to fire the local component. This last signal

$<sup>^{1}</sup>EsterelStudio^{\mathbb{T}\!M}$  is a trademark of  $Esterel\ Technologies$

Figure 5: (a) Shell-Wrapper Circuitry, (b) Input module, and (c) Data Path

will be scheduled at the rate of local firing thus. Note that it is here synchronous with all the val\_out signals when values are abstracted into tokens.

The operational behavior of the SW is depicted as a synchronous circuit in Figure 5 (a), where each **Input i** module has to be instantiated with the Figure 5 (b), with its signals properly renamed, finally driving the data path in Figure 5 (c). The SW is combinatorial, it takes one clock cycle to pass from RSs before the SW, through the SW and its *Pearl*, and finish into RSsin outputs of the SW. The *Pearl* is *Patient*, the state of the *Pearl* is only changed when clock (periodic or sporadic) occurs.

The  $SW\!$  works as follows:

- the internal *Pearl's clock* and all *val\_out<sub>i</sub>* valid output signals are generated once we have all *val\_in* (signal *ALL\_VAL\_IN* in Figure 5 (a)), while *stop* is false. The internal *stop* signal itself represents the disjunction of all incoming *stop\_out<sub>j</sub>* signals from outcoming channels (signal *STOP\_OUT* in Figure 5 (a));

- the buffering register of a given input channel is used meanwhile as long as not all other input tokens are available (Figure 5 (b));

- so, internal *Pearl's clock* is set to false whenever a backward  $stop\_out_j$  occurs as true, or a forward  $val\_in_i$  is false. In such case the registers already busy hold their *true* value, while others may receive a valid token "just now";

- $stop_in_i$  signals are raised towards all channels whose corresponding register was already loaded (a token was received before, and still not consumed), to warn them not to propagate any value in this clock cycle. Of course such signal cannot be sent in case the token is currently received, as it would raise a causality paradox (and a combinatorial cycle).

- flip-flop registers are reset when the *Pearl's* clock is raised, as it consumes the input token. Following the previous remark, the signal  $stop_in_i$  holding back the traffic in channel *i* is raised for these channels where the token have arrived before the current instant, even in this case.

**Correctness properties** Again we conducted a number of model-checking experiments on *SWs* using ESTEREL STUDIO:

- $\Box((\exists j, stop\_out_j) \lor \Rightarrow \neg clock)$  where j is an input index;

- $\Box((\exists j, stop\_out_j) \Rightarrow (\forall i, \neg val\_out_i))$  where j/i is an input/output index respectively;

- $\Box((\forall j, \neg stop\_out_j \land \neg X(stop\_out_j)) \Rightarrow (X(clock) \Rightarrow \exists i, X(val\_in_i)))$  where j, i are input index (if the SW was not suspended at some instant by output congestion, and it triggers its pearl the next instant, then it has to be because it received a new value toke on some input at this next instant)

On the other hand, most useful properties here would require syntactic sugar extensions to the logics to be easily formulated (like "a token has had to arrive on each input before or when the SW triggers its local *Pearl*", but they can arrive in any order).

As in the case of RSs, correctness also depends on the environmental assumption that  $\forall i, stop\_in_i \Rightarrow \neg val\_in_i$ , meaning that upward components must not send a value while this part of the system is jammed.

#### 3.3 Tool implementation

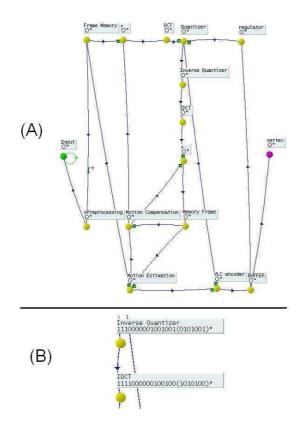

We built a prototype tool named  $KPASSA^2$  to simulate and analyze a *LID* system made of a combination of previous components.

Simulation is eased by the following fact: given that the ASAP synchronous semantics of *LID* ensures determinism, for closed systems each state has exactly one successor. So we store states that were already encountered to stop the simulation as soon as a state already visited is reached.

While we will come back to the main functions of the tool in the next Section, it can be used in this context of dynamic scheduling to detect where the back-pressure control mechanisms are really been used, and which *Relay-Stations* actually needed their secondary register slot to preserve from traffic congestion.

#### 4 Synchronous to LID: Static Scheduling

We now turn to the issue of providing static periodic schedules for *LID* systems. According to the previous philosophy governing the design of *Relay-Stations*, we want to provide solutions where tokens are not allowed to accumulate into *places* in large numbers. In fact we will attempt to *equal-ize* the flows so that tokens arrive as much as possible simultaneously at their joint *Computation Nodes*.

We try to achieve our goal by adding new virtual latencies on some paths that are *faster* than others. If such an ideal scheme could lead to *perfect equalization* then the second buffering slot

<sup>&</sup>lt;sup>2</sup>stands for K-Periodic Asap Schedule Simulation and Analysis, pronounced "Que pasa ?"

mechanism of *Relay-Stations* and the back-pressure control mechanisms could be done without altogether. However it will appear that this is not always feasible. Nevertheless integer latency equalization provides a close approximation, and one can hope that the additional correction can be implemented with smaller and simpler *Fractional Registers*.

Extra virtual latencies can often be included as computational latencies, thereby allowing the re-design of local *Computation Nodes* under less stringent timing budget.

As all connected graphs, general (connected) *CNS* consist of Directed Acyclic Graphs of strongly connected components. If there is at least one cycle in the net it can be shown that all cycles have to run at the rate of the slowest to avoid unbounded token accumulation. This is also true of input token consumption, and output token production rates. Before we deal with the (harder) case of strongly connected graphs that is our goal, we spend some time on the (simpler) case of acyclic graphs (with a single *input link*).

#### 4.1 DAG Case

We consider the problem of equalizing latencies in the case of Directed Acyclic Graphs (DAGs) with a single source *Computation Node* (one can reduce DAGs to this sub-case if all inputs are arriving at the same instant), and no initial token is present in the DAG.

**Definition 9** (DAG Equalization). In this case the problem is to *equalize* the DAG such that all paths arriving to a *Computation Node* are having the *same latency* from inputs.

We provide a sketch of the abstract algorithm and its correction proof.

**Definition 10** (Critical Arc). We define an arc as *critical* if it belongs to a path of maximal latency  $Max_l(N)$  from the global source *Computation Node* to the target *Computation Node* N of this arc.

**Definition 11** (Equalized Computation Node). We define a *Computation Node* N which is having only incoming *critical* arcs to be an *equalized Computation Node*, i.e from any path from the source to this *Computation Node* we have the same latency  $Max_l(N)$ .

If a *Computation Node* has only one incoming arc then this arc will be *critical* and this *Computation Node* will be *equalized* by definition.

The core idea of the algorithm is first to find for each *Computation Node* N of the graph what is its maximal latency  $Max_l(N)$  and to mark incoming *critical* arcs; Then the second idea is to saturate all non-critical arcs of each *Computation Node* of the DAG in order to obtain an *equalized* DAG.

The first part of the algorithm is done through a modified *longest-path algorithm*, marking incoming *critical* arcs for each *Computation Node* of the DAG and putting for each *Computation Node* N its maximal latency  $Max_l(N)$  (as shown in algorithm 1).

The second part of the algorithm is done as follows (see algorithm 2): Since it may exist incoming arcs of a *Computation Node* N that are not *critical*: it exists an  $\epsilon$  integer number that we can add such that the non-*critical* arc becomes *critical*. We can compute this integer number  $\epsilon$  easily through this formula:  $Max_l(N) = Max_l(N') + non\_critical\_arc_l + \epsilon$ , where N' is the source *Computation Node* passing through the *non-critical arc* and reaching the *Computation Node* N. Now, the non-*critical* arc through the add of  $\epsilon$  is *critical*.

We apply this for all non-*critical* arcs of the *Computation Node* N, then the *Computation Node* is *equalized*.

Finally, we apply this for all Computation Nodes of the DAG, then the DAG is equalized.

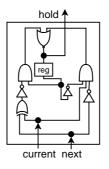

An instance of the *unequalized*, *critical* arcs annotated and *equalized* DAG is shown in Figure 6:

Starting from the *unequalized* graph in Figure 6 (a):

| <b>Algorithm 1</b> procedure recursive_longest_path ( $NODE$ source)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Require: Graph is a DAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| for all ARC arc of source.getOutputArcs() do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| $NODE \text{ node} \leftarrow \operatorname{arc.getTargetNode}();$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| $unsigned int currentLatency \leftarrow arc.getLatency() + source.getLatency();$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| { if the latency of this path is greater }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| if $node.getLatency() \leq currentLatency$ then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| arc.setCritical(true);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| node.setLatency(currentLatency);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| { update arcs critical field for "node" }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| for all ARC node_arc of node.getInputArcs() do                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $if \ node\_arc.getLatency() + node\_arc.getSourceNode().getLatency() < currentLatency() <$ |

| then                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $node\_arc.setCritical(false);$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| else                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $node\_arc.setCritical(true);$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| end if                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| end for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

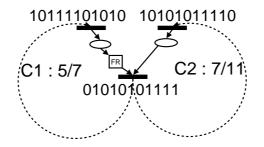

| { recursive call on "node" to update the whole sub-graph }                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |