# Verification of clock constraints: CCSL Observers in Esterel

Charles André

# ▶ To cite this version:

Charles André. Verification of clock constraints: CCSL Observers in Esterel. [Research Report] RR-7211, INRIA. 2010, pp.59. inria-00458847

# HAL Id: inria-00458847 https://hal.inria.fr/inria-00458847

Submitted on 22 Feb 2010

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers. L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

INSTITUT NATIONAL DE RECHERCHE EN INFORMATIQUE ET EN AUTOMATIQUE

# Verification of clock constraints: CCSL Observers in Esterel

Charles André

# N° 7211

February 2010

Thème COM

ISSN 0249-6399 ISRN INRIA/RR--7211--FR+ENG

# Verification of clock constraints: CCSL Observers in Esterel

### Charles André\*

Thème COM — Systèmes communicants Projet Aoste

Rapport de recherche n° 7211 — February 2010 — 59 pages

**Abstract:** The Clock Constraint Specification Language (CCSL) has been informally introduced in the specifications of the UML Profile for Modeling and Analysis of Real-Time and Embedded systems (MARTE). In a previous report entitled "Syntax and Semantics of the Clock Constraint Specification Language", we equipped a kernel of CCSL with an operational semantics. In the present report we pursue this clarification effort by giving a mathematical characterization to each CCSL constructs. We also propose a systematic approach to the formal verification of CCSL constraints with dedicated Observers. A comprehensive library of Esterel modules, which supports this approach, is provided.

Key-words: CCSL, UML, time constraints, verification, observer, Esterel

\* Université de Nice Sophia Antipolis

# Vérification de contraintes d'horloges : Observateurs CCSL en Estérel

**Résumé :** Le langage de Spécification de Contraintes d'Horloges (connu sous le nom de Clock Constraint Specification Language ou sous l'acronyme CCSL) a été introduit de façon informelle dans le document de spécification du profil UML pour la modélisation et l'analyse des systèmes temps réel et embarqués (MARTE). Dans un précédent rapport intitulé "Syntax and Semantics of the Clock Constraint Specification Language" nous avons défini une sémantique opérationnelle pour un noyau de CCSL. Le présent rapport poursuit cet effort de formalisation en donnant une caractérisation mathématique précise à chaque élément du langage CCSL. Nous proposons également une approche systématique pour la vérification formelle de contraintes CCSL s'appuyant sur le concept d'Observateur. Une bibliothèque complète de modules Esterel est fournie pour la mise en œuvre de cette approche.

Mots-clés : CCSL, UML, contraintes temporelles, vérification, observateurs, Esterel

## 1 Introduction

Modeling of distributed systems, as well as electronic systems with multi-cores or multiclock domains, needs multiple time bases. The UML profile for *Modeling and Analysis of Real-Time and Embedded* systems [1] (MARTE) addresses this modeling issue through its rich *model of Time*. MARTE also introduces the concept of *clock constraints* and proposes the non-normative language CCSL (short for *Clock Constraint Specification Language*) for specifying such constraints.

The MARTE time model has been first presented at the 10<sup>th</sup> international conference on *Model Driven Engineering Languages and Systems* [2]. This paper introduced the concepts of time bases, *clocks* and clock constraints. CCSL appeared only in a few illustrative examples. On the other hand, the OMG specification of MARTE contains neither a precise syntax nor a formal semantics for CCSL; only an informal (English) semantics is given. This lack of formal description of CCSL has been partially filled in our research report entitled "Syntax and Semantics of the Clock Constraint Specification Language" [3], which described a kernel of CCSL and provided a structural operational semantics for this kernel. The present report contributes further to the semantics of CCSL by giving full mathematical characterization of the clock relations and clock expressions of CCSL.

CCSL has also been used in *verification of time requirements* [4,5]. The first reference proposed simulation of CCSL specifications to find constraint violations. The second one dealt with formal verification: we first specified time constraints of a simplified signal processing application with CCSL, and we then used *model checking* techniques to verify that an Esterel program effectively met these specifications. Esterel [6, 7] is an imperative synchronous language, well-suited to control-dominated system programming. As usual with synchronous languages [8,9], we applied an *observer*-based approach [10] for safety property verification. The second contribution of the present report is to propose a general approach to CCSL constraint checking with CCSL-observers.

The report consists of three main sections. The first section introduces the *multiform logical* time, the *clocks*, and the *clock constraints*. A clock constraint is a *clock relation* that applies to two *clock expressions*. In this section, all the clock relations from the kernel CCSL, and two often used derived relations (*alternation* and *synchronization*), are mathematically defined. The primitive clock expressions of the kernel CCSL, and some derived expressions are characterized in the same way.

The second section first explains the concept of *observer*. Then, a general approach is proposed for the implementation of (CCSL) *observers*, *generators*, and *adaptors*, which are modules that implement clock relations, clock expressions, and CCSL clocks, respectively. The behavior of each module is dictated by the operational semantics given in the previous report on CCSL [3]. For each relation, the condition under which the relation is *violated* is clearly stated.

The third section describes, in details, an Esterel module library library that implements the proposed verification approach.

# 2 Clock Constraint Specification Language

#### 2.1 Multiform logical time

MARTE Time model deals with both discrete and dense time. In MARTE, a *clock* gives access to a *time structure* made of *time bases*, which are themselves ordered sets of *instants*. A clock can be either *chronometric* or *logical*. The former is related to "physical time" while the latter is not. This report focuses on the structural relations between clocks and these relations do not differentiate between chronometric and logical clocks. However, some relations only apply to discrete clocks (logical or chronometric) and others apply to both discrete and dense clocks. Dense clocks considered in MARTE are necessarily chronometric. Logical clocks refer to discrete-time logical clocks and represent *logical time*.

Leslie Lamport [11] introduced logical clocks in the late 70's. The logical clocks associate numbers (logical timestamps) with events in a distributed system, such that there exists a consistent total ordering of all the events of the system. These clocks can be implemented by counters with no actual timing mechanisms. In the 80's, the synchronous languages [12] introduced their own concept of logical time. This logical time shares with Lamport's time the fact that they need not actually refer to physical time. Logical time only relies on (partial or total) ordering of instants. In what follows, we consider logical time in the sense of synchronous languages. In the synchronous language Signal, a *signal s* is an infinite totally ordered sequence  $(s_t)_{t\in\mathbb{N}}$  of typed elements. Index t denotes a *logical instant*. At each logical instant of *its* clock, a signal is present and carries a unique value. Signal is a multi-clock (or polychronous) language: it does not assume the existence of a *global clock*. Instead, it allows multiple logical clocks. Signal composition is ruled by operators which are either mono-clock operators (composing signals defined on a same clock) or multi-clock operators (allowing composition of signals having different clocks).

Indeed, a logical clock can be associated with any event. This point of view has been adopted in the MARTE time model [1, Chap. 10]. A logical clock "ticks" with each new occurrence of its associated event. Synchronous languages like Esterel exploit this property. In an Esterel program, time may be counted in seconds, meters, laps... (see the Berry's RUNNER program [7] which describes the training of a runner). This variety of events supporting time leads to the concept of *multiform time*. More technical examples can be found in automotive applications. For instance, the electronic ignition is driven by the angular position of the crankshaft rather than by a chronometric time (see our study of a knock controller in a 4-stroke engine [13]).

In this report, we consider only (discrete) logical clocks and their relationships through *clock constraints*. Many aspects are extendable to dense clocks, but these are not addressed in this report.

#### 2.2 Clocks

In the MARTE time model, a clock is a model element giving access to the time structure underlying the application. A clock refers to a time base. In this report, we adopt a simplified

model, already used in our papers (see for instance [14]). This model hides the concept of time base and considers that a clock directly owns an ordered set of instants.

A Clock is a 5-tuple  $\langle \mathcal{I}, \prec, \mathcal{D}, \lambda, u \rangle$  where  $\mathcal{I}$  is a set of instants,  $\prec$  is a quasi-order relation on  $\mathcal{I}$ , named strict precedence,  $\mathcal{D}$  is a set of labels,  $\lambda : \mathcal{I} \to \mathcal{D}$  is a labeling function, u is a symbol, standing for a *unit*. For logical clocks, u is often called tick, it can be processorCycle as well or any other logical activation of a behavior. The ordered set  $\langle \mathcal{I}, \prec \rangle$  is the temporal structure associated with the clock.  $\prec$  is a total, irreflexive, and transitive binary relation on  $\mathcal{I}$ .

A discrete-time clock is a clock with a discrete set of instants  $\mathcal{I}$ . Since  $\mathcal{I}$  is discrete, it can be indexed by natural numbers in a fashion that respects the ordering on  $\mathcal{I}$ : let  $\mathbb{N}^* = \mathbb{N} \setminus \{0\}$ , idx :  $\mathcal{I} \to \mathbb{N}^*$ ,  $\forall i \in \mathcal{I}$ , idx(i) = k if and only if i is the  $k^{\text{th}}$  instant in  $\mathcal{I}$ .

For any discrete time clock  $c = \langle \mathcal{I}_c, \prec_c, \mathcal{D}_c, \lambda_c, u_c \rangle$ , c[k] denotes the  $k^{\text{th}}$  instant in  $\mathcal{I}_c$  (*i.e.*,  $k = \text{idx}_c$  (c[k])). For any instant  $i \in \mathcal{I}_c$  of a discrete time clock, "*i* is the unique immediate predecessor of *i* in  $\mathcal{I}_c$ . For simplicity, we assume a virtual instant the index of which is 0, and which is the (virtual) immediate predecessor of the first instant. *i*" is the unique immediate successor of *i* in  $\mathcal{I}_c$ , if any.

#### 2.2.1 Time structure

A Time Structure is a pair  $(C, \preccurlyeq)$  where C is a set of clocks,  $\preccurlyeq$  is a binary relation on  $\bigcup_{c \in C} \mathcal{I}_c$ , named precedence.  $\preccurlyeq$  is reflexive and transitive. From  $\preccurlyeq$  we derive four new relations:

- Coincidence ( $\equiv \triangleq \preccurlyeq \cap \preccurlyeq^{-1}$ ),

- Strict precedence  $(\prec \triangleq \preccurlyeq \setminus \equiv)$ ,

- Independence ( $\parallel \triangleq \overline{\prec \cup \prec^{-1}}$ ), and

- Exclusion  $(\# \triangleq \prec \cup \prec^{-1})$ .

The graphical representation of instant relations is given in Table 1.

| instant relation        | $\operatorname{symbol}$ | graphical representation |

|-------------------------|-------------------------|--------------------------|

| strict precedence       | $\prec$                 |                          |

| (non strict) precedence | $\preccurlyeq$          | >                        |

| coincidence             | ≡                       |                          |

| exclusion               | #                       | #                        |

#### Table 1: Instant relations

Let  $I = \left(\bigcup_{c \in C} \mathcal{I}_c\right) / \equiv$  (the set of instants quotiented by the equivalence relation  $\equiv$ ). The Time Structure  $T = \langle C, \preccurlyeq \rangle$  is well-structured if  $\langle I, \preccurlyeq \rangle$  is a partially ordered set (POset).

#### 2.3 Clock constraints

Specifying a full time structure using only instant relations is not realistic. Moreover a set of instants is usually infinite, thus forbidding an enumerative specification of instant relations. Hence the idea to extend relations to clocks. We have introduced the concept of *clock constraints* in the MARTE specification (chapter 10) and also a dedicated language for expressing such constraints: CCSL [1, Annex C.3]. This language is non normative (the MARTE profile implementors are not obliged to support it). The semantics of CCSL given in the specification is informal. A first formal semantics, based on mathematical expressions has been proposed in a paper [14] and a research report [15], which is an extended version of the paper. A precise definition of the syntax of a *kernel* of CCSL along with a structural operational semantics is now available [3,16]. This semantics is the golden reference for the CCSL constraint solver implemented in TimeSquare<sup>1</sup>, the software environment that supports CCSL and the MARTE time profile.

Clock constraints are classified into four categories:

- 1. coincidence-based constraints (also known as synchronous constraints),

- 2. precedence-based constraints (also known as asynchronous constraints),

- 3. mixed constraints, which combine synchronous and asynchronous aspects,

- 4. NFP chronometric constraints (NFP stands for Non Functional Property).

The last category, which is pertinent for chronometric clocks only, is not considered in this report.

A CCSL specification S consists of *clock declarations* and a set of binary *clock relations*. These relations apply to clocks or *clock expressions*. A *run* (execution sequence) represents a legal evolution. Each *step* of the run consists of a set of clocks that are fired<sup>2</sup>. Of course, all the clocks fired during a step must respect S. For each clock, at any step of a run, the operational semantics of CCSL [3] allows the computation of an enabling condition (necessary condition for the clock to fire) and the change in state induced by its possible firing.

The basic (*i.e.*, part of the kernel) clock relations, some usual derived clock relations, and a set of clock expressions are presented in the next subsections. Most of these definitions are borrowed from the previously mentioned papers on CCSL.

#### 2.4 Clock relations

#### 2.4.1 Primitive clock relations

Let a and b two discrete time clocks. Five primitive relations on clocks are defined:

6

<sup>&</sup>lt;sup>1</sup>http://www-sop.inria.fr/aoste/dev/time\_square

<sup>&</sup>lt;sup>2</sup>"A clock fires" or "a clock ticks" are two equivalent expressions equally used in this report.

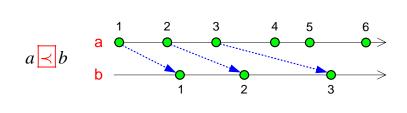

• Subclocking:  $a \subset b$  is a synchronous clock relation. There exists a mapping h from  $\mathcal{I}_a$  to  $\mathcal{I}_b$  which is injective and order preserving. a is said to be a sub-clock of b, and b a super-clock of a.

$$a \subset b \Leftrightarrow \left( (\forall k \in \mathbb{N}^{\star}, a[k] \in \mathcal{I}_{a}) (\exists l \in \mathbb{N}^{\star}, b[l] \in \mathcal{I}_{b}) (a[k] \equiv b[l] = h(a[k])) \right) \land (1)$$

$$\left( (\forall k_{1}, k_{2} \in \mathbb{N}^{\star}, a[k_{1}], a[k_{2}] \in \mathcal{I}_{a}) (a[k_{1}] \prec a[k_{2}] \Rightarrow h(a[k_{1}]) \prec h(a[k_{2}])) \right)$$

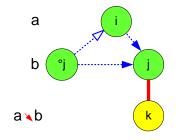

$$a \subset b$$

Figure 1: Exemple of subclocking.

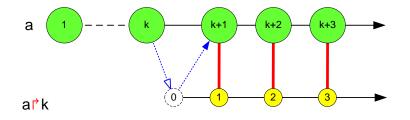

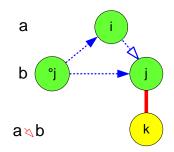

• Tight Subclocking:  $a \oplus b$  is a subclocking relation in which the image of  $\mathcal{I}_a$  by h is an interval of  $\mathcal{I}_b$ . In a formal way:

Figure 2: Exemple of tight subclocking.

In this example clock a is finite  $(|\mathcal{I}_a| = 3)$  and j = 1.

• Strict precedence:  $a \prec b$  is an asynchronous clock relation. a is said to be strictly faster than b, and b strictly slower than a.

$$a \prec b \Leftrightarrow (\forall k \in \mathbb{N}^{\star}, b[k] \in \mathcal{I}_b) ((a[k] \in \mathcal{I}_a) \land (a[k] \prec b[k]))$$

(3)

Figure 3: Exemple of strict precedence.

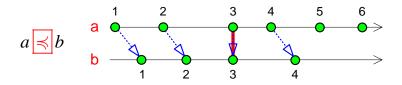

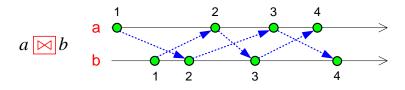

• *Precedence:*  $a \bowtie b$  is similar to the previous one but considering the non strict precedence instead. a is said to be faster than b, and b slower than a.

$$a \bowtie b \Leftrightarrow (\forall k \in \mathbb{N}^{\star}, b[k] \in \mathcal{I}_b) ((a[k] \in \mathcal{I}_a) \land (a[k] \preccurlyeq b[k]))$$

$$\tag{4}$$

Figure 4: Exemple of non strict precedence.

In this example, note that a[3] and b[3] are coincident.

• Exclusion: a # b means that a and b have no coincident instants.

$$a \ \# \ b \Leftrightarrow \left( \forall j \in \mathbb{N}^*, a[j] \in \mathcal{I}_a \right) \left( \forall k \in \mathbb{N}^*, b[k] \in \mathcal{I}_b \right) \left( \neg (a[j] \equiv b[k]) \right)$$

(5)

#### 2.4.2 Derived clock relations

We mention three often used derived clock relations: Equality, Alternation, Synchronization.

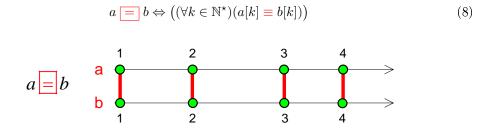

**Equality** a = b is a typical synchronous clock relation derived from tight subclocking.

$$a = b \Leftrightarrow (a \in b) \land (b \in a) \tag{6}$$

Hence, there is a bijection between instants of a and b. This bijection is order preserving and the instants are point-wise coincident:  $\forall k \in \mathbb{N}^*, a[k] \equiv b[k]$ . Hence another characterization of the clock equality relation is given in equation 7.

$$a \equiv b \Leftrightarrow \left( \left( \forall k \in \mathbb{N}^{\star}, a[k] \in \mathcal{I}_{a} \right) \left( b[k] \in \mathcal{I}_{b} \right) \land \left( a[k] \equiv b[k] \right) \right) \land$$

$$\left( \left( \forall k \in \mathbb{N}^{\star}, b[k] \in \mathcal{I}_{b} \right) \left( a[k] \in \mathcal{I}_{a} \right) \land \left( a[k] \equiv b[k] \right) \right)$$

$$(7)$$

INRIA

For infinite sets, the specification simplifies to equation 8:

Figure 5: Exemple of clock equality.

The next two relations are asynchronous. They involve precedence relations and auxiliary clocks. Given a clock c, we denote c\$1 the tight sub-clock of c such that

$$(\forall k \in \mathbb{N}^{\star}, c[k+1] \in \mathcal{I}_c) (c\$1[k] \in \mathcal{I}_{c\$1}) \land (c\$1[k] \equiv c[k+1])$$

$$(9)$$

In other words, c\$1 is c deprived of its first instant. We will see later on page 18, how this can be easily defined with clock expressions.

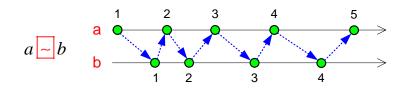

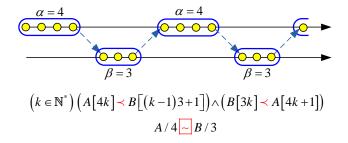

**Alternation**  $a \sim b$ . The strict form of alternation can be specified as

$$a \sim b \Leftrightarrow (a \prec b) \mid (b \prec a\$1) \tag{10}$$

The composition of clock relation (operator |) imposes the conjunction of the relations. So, the alternation can be also defined as

$$a \sim b \Leftrightarrow \left(\forall k \in \mathbb{N}^{\star}, a[k+1] \in \mathcal{I}_a\right) \left( (b[k] \in \mathcal{I}_b) \land (a[k] \prec b[k] \prec a[k+1]) \right)$$

(11)

Figure 6: Exemple of strict alternation.

This definition is far simpler when only infinite sets are considered:

$$a \sim b \Leftrightarrow (\forall k \in \mathbb{N}^*) (a[k] \prec b[k] \prec a[k+1])$$

(12)

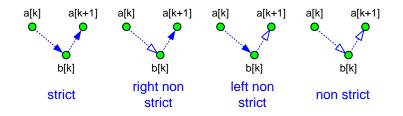

For the sake of simplicity, from now on, we give only definitions for infinite sets. Since there exists a non strict form of precedence  $(\checkmark)$ , three other variants of alternation can be defined.

• RNS-alternation (right non-strict alternation)

$$a \sim = b \Leftrightarrow (\forall k \in \mathbb{N}^*) (a[k] \preccurlyeq b[k] \prec a[k+1])$$

(13)

• LNS-alternation (left non-strict alternation)

$$a = b \Leftrightarrow (\forall k \in \mathbb{N}^*) (a[k] \prec b[k] \preccurlyeq a[k+1])$$

(14)

• NS-alternation (non-strict alternation, which is both right and left non-strict)

$$a = b \Leftrightarrow (\forall k \in \mathbb{N}^{\star}) (a[k] \preccurlyeq b[k] \preccurlyeq a[k+1])$$

(15)

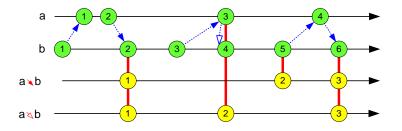

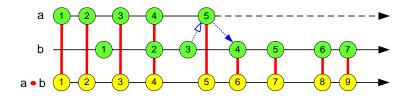

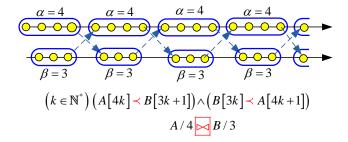

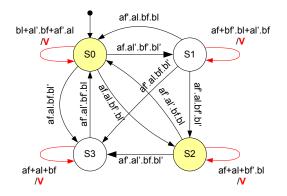

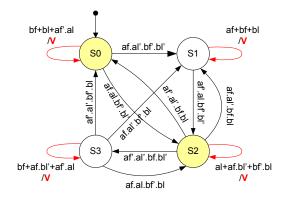

Figure 7: Various forms of alternation.

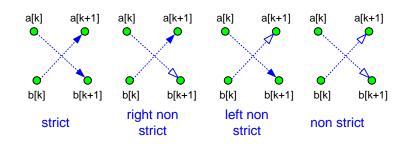

**Synchronization** This relation, unlike the alternation, does not impose a strict ordering on instants of a and b. Instead, the  $k^{th}$  instants of a and b are not ordered, but they both precede the  $k + 1^{th}$  instants of a and b. Figure 8 shows an example of strict synchronization. This relation is borrowed from the General Net Theory and stands for a synchronic distance of 2 (see Reisig's book [17], chapter 4).

Figure 8: Exemple of strict synchronization.

Like the alternation, synchronization has four variants:

$$a \bowtie b \Leftrightarrow \left( \left( a \prec b\$1 \right) \mid \left( b \prec a\$1 \right) \right) \tag{16}$$

$$a \bowtie b \Leftrightarrow \left( \left( a \preccurlyeq b\$1 \right) \mid \left( b \prec a\$1 \right) \right) \tag{17}$$

$$a = \bowtie b \Leftrightarrow \left( \left( a \prec b\$1 \right) \mid \left( b \preccurlyeq a\$1 \right) \right) \tag{18}$$

$$a = b \Leftrightarrow \left( \left( a \preccurlyeq b\$1 \right) \mid \left( b \preccurlyeq a\$1 \right) \right) \tag{19}$$

Using quantifiers, the infinite forms can be redefined as follows:

• synchronization (strict synchronization)

$$a \bowtie b \Leftrightarrow (\forall k \in \mathbb{N}^*) ((a[k] \prec b[k+1]) \land (b[k] \prec a[k+1]))$$

$$(20)$$

• RNS-synchronization (right non-strict synchronization)

$$a \bowtie b \Leftrightarrow (\forall k \in \mathbb{N}^{\star}) ((a[k] \preccurlyeq b[k+1]) \land (b[k] \prec a[k+1]))$$

(21)

• LNS-synchronization (left non-strict synchronization)

$$a \sqsubseteq b \Leftrightarrow (\forall k \in \mathbb{N}^{\star}) ((a[k] \prec b[k+1]) \land (b[k] \preccurlyeq a[k+1]))$$

(22)

• NS-synchronization (non-strict synchronization, which is both right and left non-strict)

$$a = b \Leftrightarrow (\forall k \in \mathbb{N}^{\star}) ((a[k] \preccurlyeq b[k+1]) \land (b[k] \preccurlyeq a[k+1]))$$

(23)

Figure 9: Various forms of synchronization.

### 2.5 Clock expressions

A clock expression defines a new implicit clock. In this subsection we name this implicit clock  $\mathsf{c}.$

#### 2.5.1 Index independent clock expressions

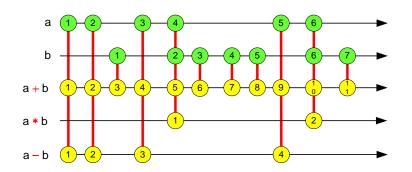

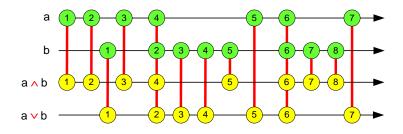

**Clock union** a + b defines a clock that ticks whenever **a** or **b** ticks.

Let c = a + b the following properties hold:

1)

$$(a \subset c) \land$$

2)  $(b \subset c) \land$

3)  $((\forall i \in \mathcal{I}_c) (\exists j \in \mathcal{I}_a \cup \mathcal{I}_b) i \equiv j)$

$$(24)$$

Equations 24-1 and 24-2 state that c is a super-clock of both a and b. Equation 24-3 makes c minimal with respect to the subclocking relation.

**Clock intersection** a \* b defines a clock that ticks whenever both a or b tick.

Let

$$c \equiv a * b$$

the following properties hold:

1)  $(c \subset a) \land$

2)  $(c \subset b) \land$

3)  $((\forall i \in \mathcal{I}_a) (\forall j \in \mathcal{I}_b) (\exists k \in \mathcal{I}_c) (i \equiv j) \Rightarrow (i \equiv k))$

(25)

Equations 25-1 and 25-2 state that c is a sub-clock of both a and b. Equation 25-3 makes c maximal with respect to the subclocking relation.

**Clock difference** a - b defines a clock that ticks whenever **a** ticks but **b** does not.

Let

$$c \equiv a - b$$

the following properties hold:

1)  $(c \subset a) \land$

2)  $((\forall i \in \mathcal{I}_a, \nexists j \in \mathcal{I}_b, i \equiv j) (\exists k \in \mathcal{I}_c) i \equiv k)$

(26)

Equation 26-1 states that c is a sub-clock of a. Equation 26-2 makes c maximal with respect to the subclocking relation by ensuring that all the instants of a not coincident with an instant of b have a coinciding instant in c.

Figure 10 illustrates the three clock expressions just defined.

Figure 10: Exemples of clock expressions union, intersection, and difference.

#### 2.5.2 Index dependent clock expressions

As from  $a \not \in k$ , where k is a natural number, defines a clock that is a tight sub-clock of a starting after index k.

$$c \equiv a \nvDash k \Leftrightarrow (c \in a) \land (c[1] \equiv a[k+1])$$

$$(27)$$

This clock expression is illustrated in figure 11. The virtual initial instant of  $a \nvDash k$ , indicates that the *birth* of this clock is between instant k and k + 1 of clock a.

Figure 11: Exemples of clock expression 'as from'.

A variant of this expression is  $a \not\uparrow *$ . It is dynamically evaluated during a *run* and takes  $\chi(a)$  as its parameter.

**Sup**  $a \lor b$  defines a clock that is the fastest among all the clocks slower than a and b (equation 28).

Let

$$\mathcal{C}_{a,b}^{\preccurlyeq} = \left\{ d \in \mathcal{C} \mid \left(a \mid d\right) \land \left(b \mid d\right) \right\}, \quad \left(\forall c' \in \mathcal{C}_{a,b}^{\preccurlyeq}\right) \left(\left(a \lor b\right) \mid c'\right)$$

(28)

This fixpoint relation can be also expressed using instants:

Let

$$c \equiv a \lor b$$

the following properties hold:

$(\forall k \in \mathbb{N}^{\star}, c[k] \in \mathcal{I}_c)$

1)  $(a[k] \in \mathcal{I}_a) \land$

2)  $(b[k] \in \mathcal{I}_b) \land$

3)  $\left(c[k] \equiv \begin{cases} a[k] \text{ if } b[k] \preccurlyeq a[k] \\ b[k] \text{ if } a[k] \preccurlyeq b[k] \end{cases} \right)$

(29)

Equations 29-1 and 29-2 state that for any instant c[k] of c, there exist instants with the same index in both a and b. Equation 29-3 imposes that c[k] is coincident with the later of a[k] and b[k]. Note that the two branches of the case-statement (equation 29-3) are not exclusive. There may be the case that  $c[k] \equiv a[k] \equiv b[k]$ .

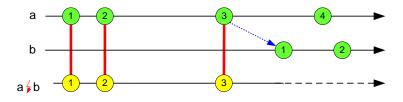

Inf  $a \wedge b$  defines a clock that is the slowest among all the clocks faster than a and b (equation 30).

Let

$$\mathcal{C}_{a,b}^{\succcurlyeq} = \left\{ d \in \mathcal{C} \mid \left( d \preccurlyeq a \right) \land \left( d \preccurlyeq b \right) \right\}, \ \left( \forall c' \in \mathcal{C}_{a,b}^{\succcurlyeq} \right) \left( c' \preccurlyeq (a \land b) \right)$$

(30)

This fixpoint relation can be also expressed using instants:

Let  $c = a \wedge b$  the following properties hold:

$$\left( \forall k \in \mathbb{N}^{\star}, c[k] \in \mathcal{I}_{c} \right)$$

$$1) \left( \left( a[k] \in \mathcal{I}_{a} \right) \land \left( b[k] \in \mathcal{I}_{b} \Rightarrow a[k] \preccurlyeq b[k] \right) \land \left( c[k] \equiv a[k] \right) \right) \lor$$

$$2) \left( \left( b[k] \in \mathcal{I}_{b} \right) \land \left( a[k] \in \mathcal{I}_{a} \Rightarrow b[k] \preccurlyeq a[k] \right) \land \left( c[k] \equiv b[k] \right) \right)$$

$$(31)$$

Equation 31-1 imposes that any instant c[k] of c coincides with instant a[k] when a[k] precedes b[k] or b[k] does not exist. Equation 31-2 imposes that c[k] coincides with instant b[k] when b[k] precedes a[k] or a[k] does not exist. Note that if  $a[k] \equiv b[k]$ , the two equations 31-1 and 31-2 are not exclusive. In this case,  $c[k] \equiv a[k] \equiv b[k]$ . Figure 12 shows the sup and inf of two clocks.

Figure 12: Exemples of clock expressions sup and inf.

#### 2.5.3 Clock expressions with clock death

**Upto**  $a \notin b$  defines a clock c that ticks whenever a ticks up to the first tick of b. As of this tick, c dies (can not tick any more).

Let

$$c \equiv a \notin b$$

the following properties hold:

1)  $(c \subset a) \land$

2)  $((\forall k \in \mathbb{N}^*, a[k] \in \mathcal{I}_a)(a[k] \prec b[1]) \Rightarrow (c[k] \equiv a[k]))$

(32)

Equation 32-1 imposes c to be a sub-clock of a. Equation 32-2 specifies that any instant of a that strictly precedes the first instant of b, is coincident with an instant of c. Figure 13 is an illustration where  $|\mathcal{I}_a| = 3$ .

Figure 13: Exemples of clock expression upto.

The clock expression *awaiting*, which also dies, is defined on page 15.

#### 2.5.4 Clock expressions with schedule

Here, schedule has the meaning of a plan that gives a list of events or tasks and the times at which each one should happen or be done. More precisely, the schedule associated with an expression contains the future times at which the clock should tick in coincidence with a given clock. Clock expressions like *sampling* have a very short schedule that contains at most one future coincidence. Others, like *defer* or *filtering* may be arbitrary large.

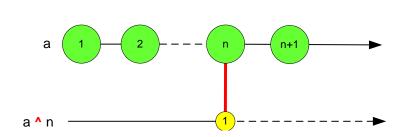

**Awaiting** a n, where  $n \in \mathbb{N}^*$ , is a synchronous clock expression. This expression waits for the  $n^{\text{th}}$  strictly future tick of a. On this occurrence, a ticks once and dies.

Let  $c \equiv a n$  the following properties hold:

1)

$$(|\mathcal{I}_c| = 1) \land$$

(33)

2)  $((\exists a[n] \in \mathcal{I}_a)(c[1] \equiv a[n]))$

Note that  $a^n$  ticks once and dies (see figure 14).

Figure 14: Exemple of clock awaiting.

**Strict sampling** a > b is a mixed clock expression (*i.e.*, based on both precedence and coincidence). It defines a subclock of b that ticks whenever clock a has ticked at least once since the previous tick of b. Figure 15 shows the corresponding instant ordering.

Figure 15: Strict sampling instant ordering.

Let

$$c \equiv a > b$$

the following properties hold:

1)  $(c \subset b) \land$

2)  $((\forall i \in \mathcal{I}_a)(\exists j \in \mathcal{I}_b, \circ j \preccurlyeq i \prec j) \Rightarrow (\exists k \in \mathcal{I}_c, j \equiv k))$

(34)

Equation 34-1 says that c is a subclock of b. Equation 34-2 specifies the ordering relations given in figure 15.

**Non strict sampling** a > b is also a mixed clock expression, similar to the previous one, just changing the precedence relations. Figure 16 shows the corresponding instant ordering.

Figure 16: Non strict sampling instant ordering.

Let c = a > b the following properties hold:

1)

$$(c \ c \ b) \land$$

(35)

2)  $((\forall i \in \mathcal{I}_a)(\exists j \in \mathcal{I}_b, {}^{\circ}j \prec i \preccurlyeq j) \Rightarrow (\exists k \in \mathcal{I}_c, j \equiv k))$

Figure 17 highlights the different behaviors of the strict and non strict clock expression samplings.

Figure 17: Exemple of clock sampling.

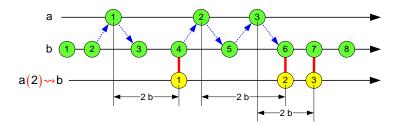

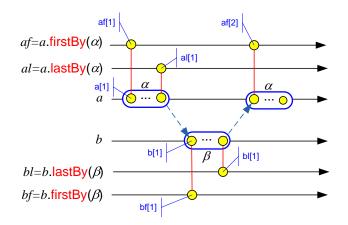

**Defer**  $a(n) \rightarrow b$  is also a mixed clock expression that deals with multiple future scheduled ticks. Figure 18 shows the corresponding instant ordering.

Figure 18: Defer instant ordering.

Let c = a(n) b the following properties hold:

1)

$$(c \ c \ b) \land$$

2)  $((\forall i \in \mathbb{N}^*, a[i] \in \mathcal{I}_a)(\exists n_i \in \mathbb{N}^*))$  (36)

$(\exists j \in \mathbb{N}^*, j \ge n_i, b[j] \in \mathcal{I}_b, b[j - n_i] \preccurlyeq a[i] \prec b[j - n_i + 1])$

$(\exists k \in \mathbb{N}^*, c[k] \in \mathcal{I}_c, c[k] \equiv b[j]))$

Figure 19 shows clock expression 'defer' when n is a constant. In this case, the clock expression is also known as clock expression 'delayedFor'.

Figure 19: Exemple of clock expression 'defer'.

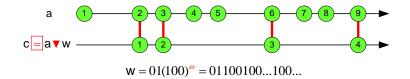

**Filtering**  $a \checkmark w$ , where w is a binary word is a often used synchronous clock expression. Binary words are described in Annex A.

$$a \checkmark w \Leftrightarrow \left( (\forall k \in \mathbb{N}^*, c[k] \in \mathcal{I}_c) (c[k] \equiv a[w \uparrow k]) \right)$$

(37)

$w \uparrow k$  denotes the index of the  $k^{\text{th}}$  '1' in the binary word w. So, c is a sub-clock of a. Example in figure 20 considers a periodic binary word (transient part '01', periodic part '100'). Note that the operation \$1 defined in equation 9 might have been defined by filtering, using the periodic binary word  $0(1)^{\omega}$ .

Figure 20: Exemple of filtering by a binary word.

#### 2.5.5 Clock expression concatenation

**Concat**  $a \bullet b$  defines a clock c that ticks whenever a ticks up to the death of a. As of this tick, c ticks whenever b ticks.

Let  $c = a \bullet b$  the following properties hold:

Let

$$l = |\mathcal{I}_a|, \ (\forall k \in \mathbb{N}^*, c[k] \in \mathcal{I}_c)$$

1)  $((k \leq l) \land (c[k] \equiv a[k])) \lor$  (38)

2)  $((k > l) \land (\exists m \in \mathbb{N}^*, b[m] \preccurlyeq a[l] \prec b[m+1]) \land (b[k+m-l] \in \mathcal{I}_b)$

$\land \ (c[k] \equiv b[m+k-l]))$

Equation 38-1 deals with the case when a is alive, whereas equation 38-2 addresses the case when a is dead. Figure 21 is an illustration where  $l = |\mathcal{I}_a| = 5$  and m = 3.

Figure 21: Exemples of clock expression concat.

### **3** Observers

#### 3.1 Verification by observers

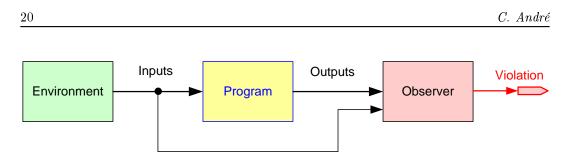

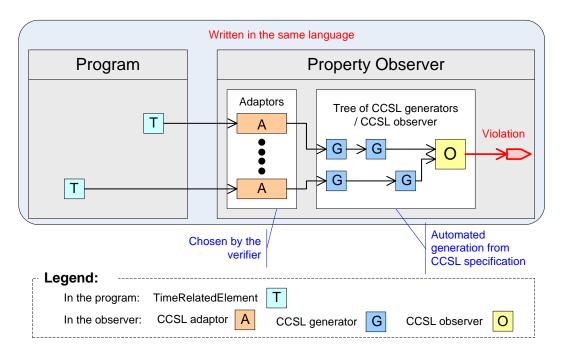

Verification by observers is a technique widely applied to synchronous languages [10]. The principle is given in figure 22. An observer (right-hand box in the figure) is a reactive program expressing a safety property P that has to be verified for a program (middle box). In synchronous language, the observer is put in (synchronous) parallel with the program. The observer has a unique output that signals possible violations of P. The observer receives the same input signals as the program. It also receives its output signals. Thus, the observer is purely passive: it only listen to the program without interfering with it. Often, a property holds only under some contexts. The assumptions made on the system environment are represented by another reactive program called *Environment* (left box in the figure). The Environment only generates useful input sequences.

The verification consists of checking that the synchronous parallel composition of the three reactive programs Environment, Program, and Observer never emits a violation for any input sequence provided by the Environment. The analysis can be done by standard reachability analysis techniques. If the property is false, an input sequence leading to the violation can be generated. This is called a counter-example.

Figure 22: Property checking of reactive programs.

With the synchronous languages, the observers can be written in the very same language as the program to verify. This is illustrated with the language Esterel. Before, we give a guide-line for implementing CCSL observers.

### 3.2 Principle of the implementation

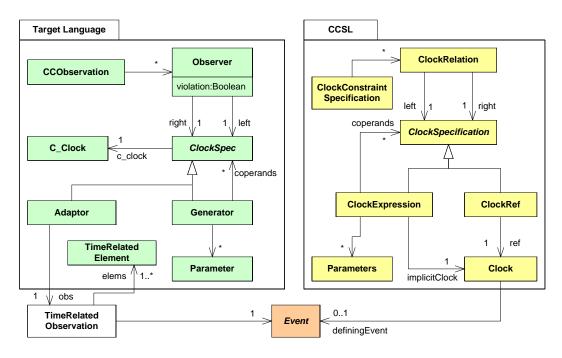

Figure 23: Metamodel for property observation.

We are interested in temporal property checking. These properties are expressed in CCSL and rely on the concept of logical clocks. On its left side, figure 23 contains a metamodel for temporal property observations. The simplified metamodel of CCSL has been put on

the right-hand side. The correspondance between the metamodel elements is summarized in table 2. In our approach, we adopt a uniform naming convention for the identifiers of programming elements related to time property observations. The third column gives these prefixes.

| CCSL                         | Target Language | Prefix  |

|------------------------------|-----------------|---------|

| ClockConstraintSpecification | CCObservation   |         |

| ClockRelation                | Observer        | Ccsl_R_ |

| ClockExpression              | Generator       | Ccsl_E_ |

|                              | Adaptor         | Ccsl_A_ |

| Clock                        | C_Clock         | c_      |

Table 2: Metamodel element correspondances.

Conceptually, a logical clock may represent an *event* whose occurrences are represented by the instants of the clock. An *adaptor* yields a  $C\_Clock$ , representation of a CCSL clock in the target language. To determine whether a  $c\_clock$  has to tick or not, the adoptor observes the state of one or several objects<sup>3</sup> of the program (property elems in the metamodel). For instance, in VHDL, a rising edge of a signal a, while a signal b is set to '1' (statement "a'event and a='1' and b='1'') may represent an event and thus be associated with a c\\_clock. A generator represents a CCSL clock expression. Like an adaptor, a generator has a c\\_clock as output. Finally, an *observer* represents a CCSL clock relation. In the target language implementation an observer provides a Boolean called violation.

We propose a modular approach. For a given target language (Esterel in this report), we provides a library of modules for observers, generators, and adaptors. Figure 24 illustrates the use of such a library for property verification. The next three sub-sections describe what should be the behavior of the various observers, generators, and adaptors, independently of any target language. The behavior results from the operational semantics of CCSL described in the report on the *kernel* CCSL [3]. This semantics transforms any CCSL specification S into a Boolean expression [S]. These Boolean expressions use extended logical operators defined in table 3.

| Operator          | Meaning                    | Equivalent expression                      |

|-------------------|----------------------------|--------------------------------------------|

| $i \Rightarrow j$ | implication                | $\neg i \lor j$                            |

| i = j             | equality                   | $(i \wedge j) \vee (\neg i \wedge \neg j)$ |

| i # j             | $\operatorname{exclusion}$ | $\neg(i \land j)$                          |

| $i\oplus j$       | exclusive disjunction      | $(\neg i \wedge j) \vee (i \wedge \neg j)$ |

Table 3: Extended logical operators

<sup>&</sup>lt;sup>3</sup>Here, object has not the restrictive meaning given by object languages. An object can be a variable (e.g., in C), a signal (e.g., Esterel, VHDL), etc.

Figure 24: Use of CCSL observer libraries.

For each clock c,  $\chi(c)$  is the index of its current instant in a run, and  $[\![c]\!]$  is a Boolean variable associated with c. When this variable is true, the associated clock can be fired at the current step.

#### 3.3 Observers of clock relations

#### 3.3.1 Observers for primitive clock relations

Table 4 groups together semantic information relative to the primitive clock relations. The first column indicates the relation, the second column the enabling condition, the third column the possible changes in state induced by clock firings. The last column gives the logical expression for the *violation* of the clock relation. This expression is the logical negation of the condition contained in the second column. An observer must evaluate the violation condition and update an internal state, if needed.

| Table 4: | Violations | of | primitive | clock | relations |

|----------|------------|----|-----------|-------|-----------|

|----------|------------|----|-----------|-------|-----------|

| Relation      | Enabling                                                      | Changes | Violation                         |

|---------------|---------------------------------------------------------------|---------|-----------------------------------|

| $a \subset b$ | $\llbracket a \rrbracket \Rightarrow \llbracket b \rrbracket$ |         | $[\![a]\!] \wedge \neg [\![b]\!]$ |

Continued on next page

22

| Relation     | Enabling                                                                                 | Changes                                                                                                                                                                                                                                              | Violation                                                |

|--------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|

| $a \oplus b$ | $\llbracket a \rrbracket = \llbracket b \rrbracket$                                      |                                                                                                                                                                                                                                                      | $\llbracket a \rrbracket \oplus \llbracket b \rrbracket$ |

| a # b        | $\llbracket a \rrbracket \# \llbracket b \rrbracket$                                     |                                                                                                                                                                                                                                                      | $\llbracket a \rrbracket \wedge \llbracket b \rrbracket$ |

| $a \prec b$  | $(\delta=0) \Rightarrow \neg \llbracket b \rrbracket$                                    | $\delta \leftarrow \begin{cases} \delta + 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ \delta - 1 & \text{if } \neg \llbracket a \rrbracket \land \llbracket b \rrbracket \\ \delta & \text{otherwise.} \end{cases}$ | $(\delta=0)\wedge [\![b]\!]$                             |

|              | $(\delta = 0) \Rightarrow (\llbracket b \rrbracket \Rightarrow \llbracket a \rrbracket)$ | $\delta \leftarrow \begin{cases} \delta + 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ \delta - 1 & \text{if } \neg \llbracket a \rrbracket \land \llbracket b \rrbracket \\ \delta & \text{otherwise.} \end{cases}$ | $(\delta=0)\wedge [\![b]\!]\wedge\neg [\![a]\!]$         |

where  $\delta \triangleq \chi(a) - \chi(b)$

#### 3.3.2 Observers for derived clock relations

**Equality** At any step of a run, for any existing clocks a and b, the clock relation  $a \equiv b$  is the same as the tight subclocking relation. The condition and the validation are the same as those of the tight subclocking (see table 5).

**Alternation** This relation is not primitive. Its enabling and violation conditions result from a composition of the enabling and violation conditions of the composed relations.

Starting with the definition  $a \sim b \Leftrightarrow (a \prec b) \mid (b \prec a\$1)$ , we apply the transformations rules to each precedence. This yields the enabling condition

$$\left(\left(\chi(a) = \chi(b)\right) \Rightarrow \neg \llbracket b \rrbracket\right) \land \left(\left(\chi(a) - 1 = \chi(b)\right) \Rightarrow \neg \llbracket a \rrbracket\right)$$

(39)

Introducing  $\delta \triangleq \chi(a) - \chi(b)$ , condition 39 becomes

$$\left(\left(\delta=0\right) \Rightarrow \neg \llbracket b \rrbracket\right) \land \left(\left(\delta=1\right) \Rightarrow \neg \llbracket a \rrbracket\right)$$

$$\tag{40}$$

The changes in state for the two precedence relations are the same, and therefore apply to the alternation relation as well.

$$\delta \leftarrow \begin{cases} \delta + 1 & \text{if } [\![a]\!] \land \neg [\![b]\!] \\ \delta - 1 & \text{if } \neg [\![a]\!] \land [\![b]\!] \\ \delta & \text{otherwise.} \end{cases}$$

(41)

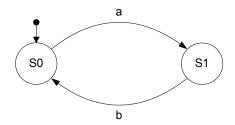

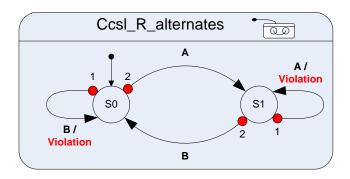

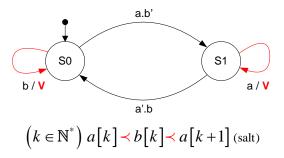

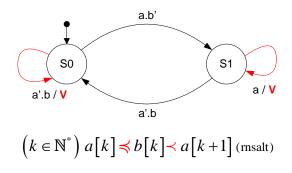

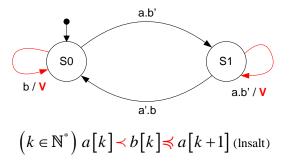

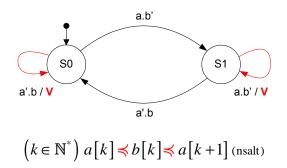

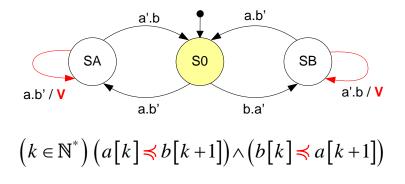

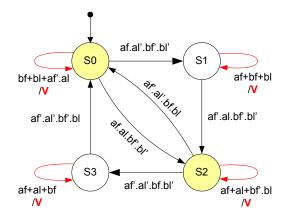

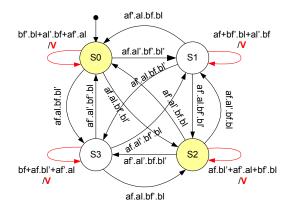

Starting with the initial condition  $\delta = 0$ , from equations 40 and 41 we deduce that only two values  $\delta = 0$  and  $\delta = 1$  are possible. Therefore, alternation can be be specified by the FSM shown in figure 25, where S0 corresponds to the enabling condition  $\delta = 0$ , whereas state

S1 corresponds to  $\delta = 1$ . While the state machine associated with a precedence observer is infinite, the composition of the two precedence relations involved in an alternation results in a 2-state machine. This graphical specification of clock relations is exploited in Annex B.

Figure 25: FSM of the strict alternation relation.

The violation condition for the alternation is the negation of the enabling condition 40:

$$\left(\left(\delta=0\right)\wedge\left[\!\left[b\right]\!\right)\vee\left(\left(\delta=1\right)\wedge\left[\!\left[a\right]\!\right)\right)\tag{42}$$

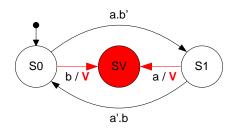

The FSM of the alternation observer (figure 26) is obtained by adding a sink state (SV), and violation transitions, shown as red arcs. V is the violation signal. The original specification of the alternation observer (table 5) a priori needs integers for encoding  $\delta$ . The FSM (figure 26) can be preferred for the observer implementation because it can be encoded with simple Boolean variables. Table 5 groups together the results in equational forms.

Figure 26: FSM detecting the violation of the strict alternation relation.

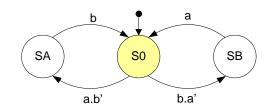

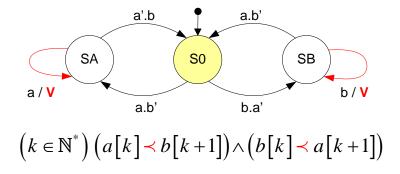

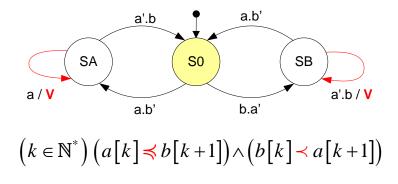

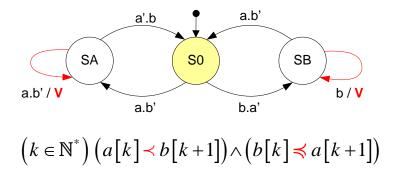

**Synchronization**  $a \bowtie b$ , which defined as  $(a \prec b\$1) \mid (b \prec a\$1)$ , can be transformed similarly. The details are skipped and gathered in table 5. There exist only three values for  $\delta$ : 0, 1, and -1. States S0, SA, and SB correspond to conditions  $\delta = 0$ ,  $\delta = 1$ , and  $\delta = -1$  respectively. Here again, a FSM can be used to specify the behavior of the synchronization (figure 27). Note that in this FSM, when a and b tick simultaneously in state S0, the state is unchanged. This is why the transition has not been explicitly drawn.

Figure 27: FSM of the strict synchronization relation.

| Relation     | Enabling                                                                                                                                        | Changes                                                                                                                                                                                                                                              | Violation                                                                                                                             |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| $a \equiv b$ | $\llbracket a \rrbracket = \llbracket b \rrbracket$                                                                                             |                                                                                                                                                                                                                                                      | $\llbracket a \rrbracket \oplus \llbracket b \rrbracket$                                                                              |

| a ~ b        | $ \begin{pmatrix} (\delta = 0) \Rightarrow \neg \llbracket b \rrbracket \\ \land \\ ((\delta = 1) \Rightarrow \neg \llbracket a \rrbracket ) $  | $\delta \leftarrow \begin{cases} 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ 0 & \text{if } \neg \llbracket a \rrbracket \land \llbracket b \rrbracket \\ \delta & \text{otherwise.} \end{cases}$                   | $ \begin{pmatrix} (\delta = 0) \land \llbracket b \rrbracket \\ \lor \\ ((\delta = 1) \land \llbracket a \rrbracket ) \end{pmatrix} $ |

|              | $ \begin{pmatrix} (\delta = 1) \Rightarrow \neg \llbracket a \rrbracket \\ \land \\ ((\delta = -1) \Rightarrow \neg \llbracket b \rrbracket ) $ | $\delta \leftarrow \begin{cases} \delta + 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ \delta - 1 & \text{if } \neg \llbracket a \rrbracket \land \llbracket b \rrbracket \\ \delta & \text{otherwise.} \end{cases}$ | $ig((\delta=1)\wedge \llbracket a rbracketig]ig) igvee igvee((\delta=-1)\wedge \llbracket b rbracketig)$                              |

Table 5: Violations of derived clock relations

where o  $\chi(a)$  $-\chi(0)$

The observers for the various forms of alternation and synchronization are given in Annex B as FSM.

#### 3.4 Generators for clock expressions

With each clock expression, we associate a generator. It generates clock ticks and maintains an internal state according to the presence or absence of ticks of its operand clocks. In this sub-section, generators are grouped according to the kind of their internal state. The results are presented in a tabular form: the expression in the first column, the condition to generate a tick in the second column, the possible changes in state in the third column, and the initial state in the last column. The last three columns reflect the operational semantics of CCSL [3].

#### Combinatorial generators 3.4.1

For these generators, emitting a tick results only from the presence/absence of incoming clock ticks. This group concerns the clock expressions union, intersection, and difference. No internal state is needed.

| Expression | Ticks when                                                   | Changes | Initial |

|------------|--------------------------------------------------------------|---------|---------|

| a+b        | $\llbracket a \rrbracket \vee \llbracket b \rrbracket$       |         |         |

| a * b      | $\llbracket a \rrbracket \land \llbracket b \rrbracket$      |         |         |

| a-b        | $\llbracket a \rrbracket \land \neg \llbracket b \rrbracket$ |         |         |

Table 6: Combinatorial generators

#### 3.4.2 Clock index dependent generators

The clock expressions sup and inf depends on the difference  $(\delta)$  between the indexes of the two clock operands. The integer  $\delta$  is the internal state. It keeps track of the incoming ticks.

| Expression                     | Ticks when                                                                                                                                                                                                                                                                                                         | Changes                                                                                                                                                                                                                                              | Initial      |

|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| a  ightharpoondown k           | $\llbracket a \rrbracket$                                                                                                                                                                                                                                                                                          | $\chi \leftarrow \begin{cases} \chi + 1 & \text{if } \llbracket a \rrbracket \\ \chi & \text{otherwise.} \end{cases}$                                                                                                                                | $\chi = 0$   |

| $a \lor b$                     | $ \begin{array}{l} \left( \left( \delta < 0 \right) \land \llbracket a \rrbracket \right) \lor \\ \left( \left( \delta = 0 \right) \land \left( \llbracket a \rrbracket \land \llbracket b \rrbracket \right) \right) \lor \\ \left( \left( \delta > 0 \right) \land \llbracket b \rrbracket \right) \end{array} $ | $\delta \leftarrow \begin{cases} \delta + 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ \delta - 1 & \text{if } \neg \llbracket a \rrbracket \land \llbracket b \rrbracket \\ \delta & \text{otherwise.} \end{cases}$ | $\delta = 0$ |

| $a \wedge b$                   | $ \begin{array}{l} \left( \left( \delta < 0 \right) \land \llbracket b \rrbracket \right) \lor \\ \left( \left( \delta = 0 \right) \land \left( \llbracket a \rrbracket \lor \llbracket b \rrbracket \right) \right) \lor \\ \left( \left( \delta > 0 \right) \land \llbracket a \rrbracket \right) \end{array} $  | $\delta \leftarrow \begin{cases} \delta + 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ \delta - 1 & \text{if } \neg \llbracket a \rrbracket \land \llbracket b \rrbracket \\ \delta & \text{otherwise.} \end{cases}$ | $\delta = 0$ |

| where $\delta \triangleq \chi$ |                                                                                                                                                                                                                                                                                                                    | •                                                                                                                                                                                                                                                    |              |

Table 7: Clock index dependent generators

## 3.4.3 Generators for clocks with death

The clock expression  $a \notin b$  dies on the first tick of **b**. The internal state is a Boolean *isDead*. Boolean values are denoted as 0 and 1, for **false** and **true**, respectively.

Table 8: Generators for clocks with death

| Expression | Ticks when                                                                       | Changes                                                  | 5                         | Initial    |

|------------|----------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------|------------|

| a ∳ b      | $ egisDead \land (\llbracket a \rrbracket \land \lnot \llbracket b \rrbracket) $ | $isDead \leftarrow \begin{cases} 1\\ isDead \end{cases}$ | if $[\![b]\!]$ otherwise. | isDead = 0 |

#### 3.4.4 Generators for clocks with schedule

| Expression            | Ticks when                                                                                                    | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Initial                                   |

|-----------------------|---------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| $a^n$                 | $\begin{bmatrix} a \end{bmatrix} \land \\ (bw = 1)$                                                           | $bw \leftarrow \begin{cases} v & \text{if } [\![a]\!] \land (bw = 0.v) \\ 0 & \text{if } [\![a]\!] \land (bw = 1) \\ bw & \text{otherwise.} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $bw = 0^{\llbracket n \rrbracket - 1} .1$ |

| a > b                 | $ \begin{matrix} \llbracket b \rrbracket \land \\ (bw = 1) \end{matrix} $                                     | $bw \leftarrow \begin{cases} 1 & \text{if } \llbracket a \rrbracket \\ 0 & \text{if } \llbracket b \rrbracket \land \neg \llbracket a \rrbracket \\ bw & \text{otherwise.} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bw = 0                                    |

| a > b                 | $ \begin{array}{l} \llbracket b \rrbracket \land \\ ((bw = 1) \\ \lor \llbracket a \rrbracket ) \end{array} $ | $bw \leftarrow \begin{cases} 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ 0 & \text{if } \llbracket b \rrbracket \\ bw & \text{otherwise.} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bw = 0                                    |

| $a \checkmark w$      | $ \begin{matrix} \llbracket a \rrbracket \\ (bw = 1.v) \end{matrix} $                                         | $bw \leftarrow \begin{cases} v & \text{if } [\![a]\!] \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bw = w                                    |

| $a (n) \rightarrow b$ | $\begin{bmatrix} b \end{bmatrix} \land \\ (bw = 1.v)$                                                         | $bw \leftarrow \begin{cases} v & \text{if } \llbracket a \rrbracket \land (bw = 0.v) \\ 0 & \text{if } \llbracket a \rrbracket \land (bw = 1) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} 1 & \text{if } \llbracket a \rrbracket \\ 0 & \text{if } \llbracket b \rrbracket \land \neg \llbracket a \rrbracket \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} 1 & \text{if } \llbracket a \rrbracket \land \neg \llbracket b \rrbracket \\ 0 & \text{if } \llbracket b \rrbracket \land \neg \llbracket b \rrbracket \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{if } \llbracket a \rrbracket \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{if } \llbracket a \rrbracket \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{if } \llbracket b \rrbracket \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{if } \llbracket a \rrbracket \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{if } \llbracket a \rrbracket \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{if } \llbracket b \rrbracket \land (bw = b.v) \\ bw & \text{otherwise.} \end{cases}$ $bw \leftarrow \begin{cases} v & \text{otherwise.} \\ v & \text{otherwise.} \end{cases}$ | bw = 0                                    |

where v is a binary word

#### 3.4.5 Generators for clock concatenation

The concatenation  $a \bullet b$  is rewritten into b when a dies.

| Table 10: | Generators | for | clock | concatenation |

|-----------|------------|-----|-------|---------------|

| Expression        | Ticks when                | Changes                   |              |                                     | Initial                  |

|-------------------|---------------------------|---------------------------|--------------|-------------------------------------|--------------------------|

| $a \bullet expr2$ | $\llbracket a \rrbracket$ | $expr \leftarrow \langle$ | $\int expr2$ | $ \  \   \text{if} \ a. is Dead \\$ | $expr = a \bullet expr2$ |

|                   |                           |                           | expr         | otherwise.                          |                          |

#### 3.5 Adaptors

An adaptor has to generate ticks of a c\_clock according to the state of one or several objects of the program. Collectively, the states of these objects characterize an event of interest for the system. Such events are greatly dependent on the application, and the way to detect their occurrences is language specific. So, there is little to say about adaptors in general.

# 4 Esterel implementation

In this section we propose a library of Esterel modules that implement the general concepts of adaptors, observers, and generators introduced in the previous chapter. The code is written in Esterel v7, version v7\_60 for Esterel Studio 6.1.

### 4.1 Data and interface units

Esterel allows separate programming of data, interface, and module units. Genericity is also supported. Existence of various units and genericity are exploited in our implementation of CCSL observers in Esterel.

#### C clocks

To implement CCSL observers in Esterel, we have first to decide how to represent a CCSL clock. We have chosen a *pair of pure signals*. The presence of the signal 'presence' represents a tick of the associated clock. The second signal 'alive' reflects the status of the clock: the clock is alive when the signal is present, whereas the clock is not existing (not yet created or dead) when the signal is absent. The two signals are grouped together in a *port*, and a c clock is a port typed by C\_Clock\_Intf.

```

interface C_Clock_Intf:

output presence;

output alive;

end interface

```

Other data and interface units will be defined in the following sub-sections.

#### 4.2 Adaptors

In Esterel a logical clock can be associated with any signal. This clock ticks whenever the signal is present. Hence, an Esterel adaptor maps an Esterel signal to a c\_clock. We have to distinguish between pure and valued signals.

#### 4.2.1 Pure signal adaptor

For a pure signal A, the adaptor code is obvious:

```

1 module Ccsl_A_pure:

2 input A;

3 port c_A: C_Clock_Intf;

4

5 sustain {

6 c_A.alive,

7 c_A.presence if A

8 }

```

9 10 end module

Note that c\_A.alive is emitted at each instant (line 6) when this module is active.

#### 4.2.2 Valued signal adaptor

For a valued signal, the adaptor code is also very simple. It is a generic module which considers only the presence status of the input signal.

```

module Ccsl A valued:

1

2

generic type T;

input A: T;

3

port c_A: C_Clock Intf;

4

5

sustain {

6

c_A.alive,

7

c_A.presence if A

8

}

9

10

end module

11

```

In line 2, a generic type is introduced. It types signal A (line 3). The actual type must be given at the module instantiation. When the module is active, signal  $c_A$ .presence is emitted whenever the input signal A is present (line 8).

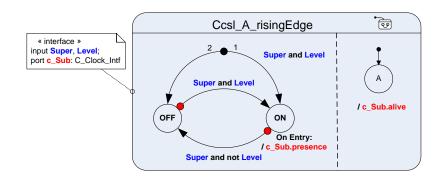

#### 4.2.3 Rising-edge signal adaptor

Since the presence status of a signal is not persistent, hand-shake in Esterel is often implemented as

abort sustain resquest when response

The actual event in this case is the "rising edge" of signal request (*i.e.*, a signal present at the first instant of the sustain). The adaptor Ccsl\_A\_risingEdge represents this behavior (Synchart in figure 28).

Note that the first two adaptors are so simple that their code is usually in-lined.

#### 4.3 Observers

#### 4.3.1 Observer interface

Each CCSL relation observer has two input c\_clocks and one output that signals possible violations. This fix interface can be specified by an interface.

Figure 28: SyncChart of the Rising Edge adaptor.

```

interface Ccsl_R_Intf:

port c_A: mirror C_Clock_Intf;

port c_B: mirror C_Clock_Intf;

output Violation;

end interface

```

Port c\_A is typed "mirror C\_Clock\_Intf" (line 2). This means that the port consists of the signals declared in interface C\_Clock\_Intf but with their direction reverted (imposed by the keyword 'mirror'). It is the same for port c\_b, line 3. As for Violation, it is a pure signal emitted as soon as a violation occurs. Each Observer module includes this interface in its code (statement "extends Ccsl\_R\_Intf;").

#### 4.3.2 Subclocking

```

module Ccsl_R_subclock:

extends Ccsl_R_Intf;

sustain Violation if c_A.presence and not c_B.presence

end module

```

The statement **sustain** (line 4) emits Violation if c\_A ticks while c\_B does not. This condition is directly extracted from table 4, first row, last column.

```

4.3.3 Tight subclocking

```

This clock relation should be tested when  $c_a$  is alive. In Esterel, this is easily done by waiting for  $c_a$  to be born (line 3), and checking the violation (line 5) while  $c_a$  is alive (lines 4-6).

```

module Ccsl_R_tightsubclock:

extends Ccsl_R_Intf;

await immediate c_A. alive;

abort

sustain Violation if c_A.presence xor c_B.presence

```

```

6 when not c_A.alive

7 end module

```

Line 5 encodes  $V = (c_a \oplus \land c_b)$  from table 4.

#### 4.3.4 Exclusion

The third clock relation observer emits Violation if both  $c_A$  and  $c_B$  tick.

```

module Ccsl_R_exclusive:

extends Ccsl_R_Intf;

sustain Violation if c_A.presence and c_B.presence

end module

```

#### 4.3.5 Precedences

The precedence observers are more complex. They have to maintain an internal counter (delta). The strict and non strict version have common behavior and they differ on their violation conditions (see table 4). Their code can be combined and the discremination done by a generic constant set at the observer module instantiation. The discreminant is the the generic constant KIND, the type of which is a the enumeration Ccsl\_Strictness\_Kind defined in a data unit.

```

data Ccsl_Types:

type Ccsl_Strictness_Kind =

enum {

STRICT=0, NONSTRICT=1, LNS=2, RNS=3

};

end data

```

The precedence observer is a generic module.

```

module Ccsl R precedes:

1

extends Ccsl_Types;

2

extends Ccsl R Intf;

3

constant KIND: Ccsl Strictness Kind;

5

generic constant UMAX: unsigned;

6

type CounterType = unsigned<UMAX>;

7

signal Delta: value CounterType init 0 in

9

sustain {

10

Violation if

11

(\mathbf{pre}(? \text{Delta}) = 0) and c B. presence and

12

((KIND = STRICT) or ((KIND=NONSTRICT) and not c A. presence)),

13

? Delta \le sat < UMAX > (pre(? Delta) + 1) if

14

not Violation and c A. presence and not c B. presence,

15

? Delta \le pre(? Delta) - 1 if

16

```

```

not Violation and not c_A.presence and c_B.presence

```

```

18 }

19 end signal

```

```

20

21 end module

```

This observer module deserves explanations:

- two constants must be provided at the module instantiation: KIND and UMAX; the latter is the expected maximal value for Delta;

- CounterType is a generic type which contains natural numbers from 0 to UMAX-1;

- Delta counts the difference on the numbers of ticks of c\_a and c\_b (lines 15-18);

- at each instant the violation condition is tested (lines 12–14);

- the value of Delta is changed only if there is no violation, this ensures that Delta is never decremented below 0 (line 17).

- since Esterel applies strict arithmetic rules, we have to assert that Delta never exceeds value UMAX-1, hence the use of the sat<UMAX>() predefined function.

#### 4.3.6 Equality

This clock relation is similar to the tight sub-clocking on page 30, but must be *always* valid: there is no longer conditions on the birth and death of clocks.

```

module Ccsl_R_equal:

extends Ccsl_R_Intf;

sustain Violation if c_A.presence xor c_B.presence

```

```

4 end module

```

#### 4.3.7 Alternation

The violation conditions for the four variants of alternation are given in annex B.1. They are specified as FSMs. In Esterel they are better specified as SyncCharts. The usage of explicit priority on transition makes the arc labels simpler. For instance, figure 29) is the syncChart equivalent to the FSM in figure 33. Both check the strict alternation.

A generic module specifies the four variants.

```

module Ccsl_R_alternates:

extends Ccsl_Types;

extends Ccsl_R_Intf;

constant KIND: Ccsl_Strictness_Kind;

signal Turn: value bool init '0 in

loop

```

17

Figure 29: SyncChart of the alternation observer.

| 8       | if pre(?Turn) then                                                            |

|---------|-------------------------------------------------------------------------------|

| 9       | //stateS1                                                                     |

| 10      | $\mathbf{i} \mathbf{f}$ (KIND = STRICT) or (KIND = RNS) then                  |

| 11      | if                                                                            |

| 12      | <b>case</b> c_A.presence <b>do</b>                                            |

| 13      | emit Violation                                                                |

| 14      | <b>case</b> c_B.presence <b>do</b>                                            |

| 15      | $\mathbf{emit} \ \mathrm{Turn} ( \ '0 )$                                      |

| 16      | end if                                                                        |

| 17      | $	extbf{else}$ // (KIND = LNS) or (KIND = NONSTRICT)                          |

| 18      | if                                                                            |

| 19      | <b>case</b> c_A.presence <b>and not</b> c_B.presence <b>do</b>                |

| 20      | emit Violation                                                                |

| 21      | <b>case</b> c_A.presence <b>and</b> c_B.presence                              |

| 22      | <b>case</b> c_B.presence <b>do</b>                                            |

| 23      | $\mathbf{emit} \ \mathrm{Turn}(\ 0)$                                          |

| 24      | end if                                                                        |

| 25      | end if                                                                        |

| 26      | else                                                                          |

| 27      | //stateS0                                                                     |

| $^{28}$ | ${f if}~~({ m KIND}~=~{ m STRICT})~~{f or}~~({ m KIND}~=~{ m LNS})~~{f then}$ |

| 29      | if                                                                            |

| 30      | <b>case</b> c_B.presence <b>do</b>                                            |

| 31      | emit Violation                                                                |

| $^{32}$ | <b>case</b> c_A.presence <b>do</b>                                            |

| 33      | $\mathbf{emit} \ \mathrm{Turn}(\ 1)$                                          |