## Dynamic reconfiguration and low power design: towards self-adaptive massively parallel embedded systems

Rabie Ben Atitallah

#### ▶ To cite this version:

Rabie Ben Atitallah. Dynamic reconfiguration and low power design: towards self-adaptive massively parallel embedded systems. Computer Science [cs]. Université de Valenciennes et Hainaut-Cambrésis, 2014. tel-01104009

HAL Id: tel-01104009

https://hal.inria.fr/tel-01104009

Submitted on 18 Jan 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

## Université de Valenciennes et du Hainaut-Cambrésis THÈSE

Soutenance prévue publiquement le 04 December 2014 pour obtenir le titre de

L'HABILITATION À DIRIGER DES RECHERCHES EN INFORMATIQUE

par

Rabie Ben Atitallah

## Dynamic reconfiguration and low power design: towards self-adaptive massively parallel embedded systems

#### Composition du jury

Rapporteurs : Patrick Garda Professeur Université de Pierre et Marie Curie

Dragomir Milojevic Professeur École Polytechnique de Bruxelles

Loïc Lagadec Professeur ENSTA Bretagne

Examinateurs : Michel Auguin Directeur de Recherche Université Nice Sophia Antipolis

Jean-Luc Dekeyser Professeur Université de Lille1

Abdelhakim Artiba Professeur Université de Valenciennes

#### UNIVERSITÉ DE VALENCIENNES ET DU HAINAUT-CAMBRÉSIS

## Acknowledgements

First of all, I am very grateful to Prof. Patrick GARDA from the University of Pierre et Marie Curie (France), Prof. Dragomir MILOJEVIC from École polytechnique de Bruxelles (Belgium) and Prof. Loïc Lagadec from ENSTA Bretagne for having kindly accepted to serve as reviewers on my Habilitation defense committee.

### The summary

This thesis summarizes my experience in the attractive academic research of embedded systems that started at November 2004 as a PhD student at the University of Lille1. Actually, I prepared my PhD thesis in Computer Science in the frame of the European Interreg project ModEasy that stands for MOdel Driven dEsign for Automotive Safety embedded systems. In March 2008, I defended my research work entitled "Multiprocessor systemon-chip modeling and simulation - performance and energy consumption estimation". This experience gave me the opportunity to discover the embedded system domain that enables innovation through intelligent products covering a large spectrum of industries (multimedia, communication, transportation, etc.). During this period, I made profit of being a member of the DaRT<sup>1</sup> INRIA team to learn about different research areas. Indeed, this team gathered several researchers from different backgrounds (parallel architecture, modeling, compilation, etc.), all contributing in one project called Gaspard. At the end of my PhD, I succeeded to efficiently contribute in this project by publishing with all the team members and by presenting the Gaspard tool at FDL<sup>2</sup> 2008 in a tutorial session. This successful experience was my main motivation to continue in the academic research domain adopting the topic of Dynamic reconfiguration and low power design: towards self-adaptive massively parallel embedded systems. In the following, I will detail the compelling story of my research career path.

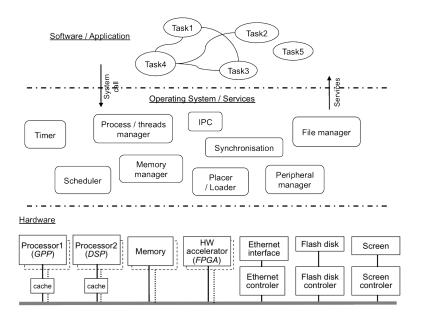

The birth era. In November 2004 when I joined the INRIA DaRT team-project led by Professor Jean-Luc Dekeyser in Lille, the team was only two years old. Its main research topic was about the co-design of System-on-Chip (SoC) for intensive signal processing applications. The main challenges addressed by this project were the following i) The definition of a UML profile for SoC co-modeling, ii) The compilation devoted to data-parallel structures for efficient mapping on multiprocessor platforms, and iii) The functional simulation using SystemC. Based on my fundamentals in electronic domain, I linked between the research topics of DaRT and the low level design. With the help of my supervisors, I focused on Multiprocessor System-on-Chip (MPSoC) simulation and Design Space Exploration (DSE).

In the first design steps, MPSoC simulation has an important impact in reducing the time to market of the final product. However, MPSoC have become more and more complex and heterogeneous. Consequently, traditional approaches for system simulation at lower levels cannot adequately support the complexity of future MPSoC. In my PhD thesis, I proposed a framework composed of several simulation levels. This enables early performance evaluation in the design flow. The proposed framework is useful for DSE and permits to find rapidly the most adequate Architecture/Application configuration. In the first part of the thesis, I presented an efficient simulation tool composed of three levels that offer several performance/energy trade-offs. The three levels are differentiated by the accuracy of architectural descriptions based on the SystemC-TLM standard. In the second part, I was interested in the MPSoC energy consumption. For this, I enhanced the simulation framework with flexible and accurate energy consumption models. Finally in the third part, a compilation chain based on a Model Driven Engineering (MDE) approach was developed and integrated in the Gaspard environment. This chain allows automatic SystemC code generation from

<sup>1.</sup> DaRT team-project at INRIA Lille Nord Europe (2004-2012)

<sup>2.</sup> FDL: Forum on specification & Design Languages, 2008, Stuttgart, Germany

high level MPSoC modeling.

Since 2005, I started teaching micro-architecture and assembly language for undergraduate students at University of Valenciennes and Hainaut-Cambrésis (UVHC).

The emergence era. After my PhD defence, I got my first Post-doc position at IN-RIA Lille-Nord Europe in the frame of the FUI ("Fonds Unique Interministériel" in french) Ter@ops project under the supervision of Professor Pierre Boulet. This project brought together the main french industrial actors in embedded systems (Thales, Thomson, EADS, MBDA, Dassault, RENAULT, VALEO, CEA, etc.) in addition to the academic laboratories (INRIA, ENSTA, IEF, etc.). The objective of the project was to define a multi-domain massively parallel architecture and its corresponding tools. The proposed architecture was able to embed heterogeneous accelerators optimised for the target application domains. A design environment was needed to optimise and to map the application on the parallel architecture. Due to the experience I gained during my PhD in the field of embedded multiprocessor system design, I was invited to participate in this project. The subject of my Post-doc dealt with automatic code generation of an execution model described with SystemC from the standard MARTE profile (Model and Analysis Real-Time Embedded System). Indeed, in the Ter@ops project a particular attention was given to the use of standards to facilitate the interoperability between the different tools of the partners. During this work, the MARTE profile was extended to be able to specify the deployment of software and hardware components. Moreover, the toolchain developed during my thesis was modified to generate a SystemC simulation for multi-processor from the MARTE profile, which led to a new version of our Gaspard tool. Despite the lack of scientific mobility, this Post-doc allowed me to benefit from several advantages. First, highlighting my PhD work in the context of an industrial project. Second, making contacts with the industrial actors during the regular meetings of the Ter@ops project. Hence, I succeeded to identify better the challenges and to expand my knowledge in the embedded system domain.

Since October 2008, I got a second Post-doc fellowship for one year at LAMIH<sup>3</sup> laboratory funded by the PrimaCare ANR<sup>4</sup> project. PrimaCare aims at designing Driver Assistance System (DAS) for automotive based on Multiple Target Tracking (MTT) algorithms. My research subject focused on the optimisation and the improvement of the MTT system as an application specific System-on-Chip (SoC) implemented on FPGA. I developed a heterogeneous architecture (Microblaze with hardware accelerators) taking into account the constraints of the automotive embedded system in terms of performance, low cost and reliability.

During this period in addition to my research activities, I supervised several master research students and taught embedded system design at UVHC and Lille1 at the master level. Scientific dissemination was also a part of my activities by participating in the thematic days organised by the national GdRs ("Groupe de Recherche" in french) SoC-SiP (System-on-Chip System-in-Package) and ASR ("Architecture, Systèmes et Réseaux" in french). As a member of the HiPEAC <sup>5</sup> European Network of Excellence, I participated in the main organised events such as summer schools and conferences. In March 2009, I contributed in the writing of the OpenPeople proposal for a request of ANR funding.

<sup>3.</sup> LAMIH : Laboratoire d'Automatique, de Mécanique et d'Informatique industrielles et Humaines UMR CNRS/UVHC 8201

<sup>4.</sup> ANR: Agence Nationale de Recherche

<sup>5.</sup> http://www.hipeac.net/

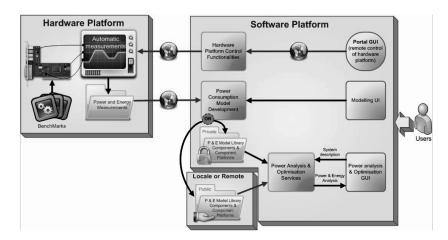

OpenPeople stands for Open Power and Energy Optimization PLatform and Estimator. In parallel, I started looking for a permanent position as an Associate Professor in France and I succeeded to join the scientific staff of UVHC.

The maturity era. Since September 2009, I obtained a full-time position as an Associate Professor at UVHC and a member of LAMIH within the DIM <sup>6</sup> team that gathers researchers from different backgrounds (operational research, artificial intelligence, embedded systems, etc.). For five years, I have been investigating, with my colleagues, this complementarity in order to provide a satisfactory answer to the crucial design challenges of modern embedded systems targeting intelligent transportation applications. I am particularly grateful to Professor Abdelhakim Artiba (optimisation and scheduling) and Associate Professor David Duvivier (decision making and simulation) for their fruitful collaborations on this topic (2 PhD students co-supervising, research projects, publications, etc.).

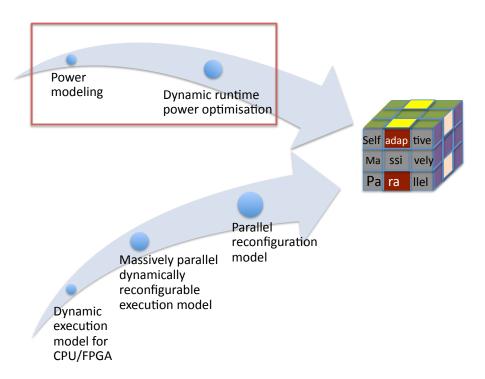

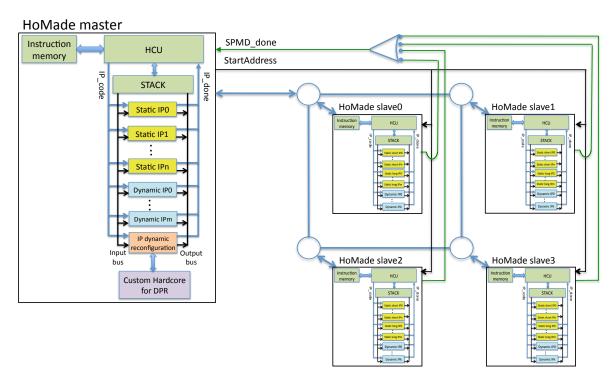

With an agreement between the UVHC and INRIA, I had the status of Associated Researcher at INRIA Lille Nord Europe within the DaRT team until the end of 2012. I managed the contributions of the team in the OpenPeople ANR project and I co-supervised the PhD thesis of Santhosh Kumar Rethinagiri [100] entitled "System-level power estimation methodology for MPSoC based platforms". In 2012, I also participated in the creation of the new INRIA project-team DreamPal (Dynamic Reconfigurable Massively Parallel Architectures and Languages). The DreamPal team addresses the following topics: designing massively parallel dynamically reconfigurable architectures, proposing execution models as well as dedicated programming languages for them, and designing software engineering tools for those languages. I am particularly grateful to Professor Jean-Luc Dekeyser for our successful collaboration on this topic (4 PhD students co-supervising, research projects, patents, publications, etc.).

Today, some of my research works were completed (Santhosh Kumar Rethinagiri's PhD, George Afonso's PhD, Omar Souissi's PhD); others are in progress (Venkatasubramanian Viswanathan's PhD, Karim Mohamed Ali's PhD, and Wissem Chouchene's PhD) or still at an exploratory stage. The obtained results are currently relevant enough to contribute to the maturity of my research activity. I am deeply indebted to all my PhD and Master students, and Post-doc colleagues, who contributed actively to the different results summarized in this document.

The content of this document mainly relies on the results of three PhDs: Santhosh Kumar Rethinagiri (December 2009 - March 2013), George Afonso [49] (August 2010 - July 2013), and Venkatasubramanian Viswanathan (February 2012 - January 2015). While for the PhD of Omar Souissi (October 2011 - September 2014) is targeting scheduling techniques for path planning on a high performance heterogeneous CPU/FPGA architecture. But for the content coherence, the results of this thesis are not included in this document.

During this period, significant highlights can be cited: co-supervising of three graduated PhD students, patents, publishing journal papers in IEEE transactions and ACM transactions, acquiring research contracts with ANR (Agence Nationale de Recherche) and industrial partners (Airbus Group, Airbus Helicopters, Nolam Embedded Systems, etc.), winning best paper award, being a member of the steering committee of GdR ASR, participating in the organization of scientific conferences, being responsible for technology transfer action with Airbus Helicopters, etc.

<sup>6.</sup> DIM (Decision, Interaction, Mobility): http://www.univ-valenciennes.fr/LAMIH/en/dim-overview

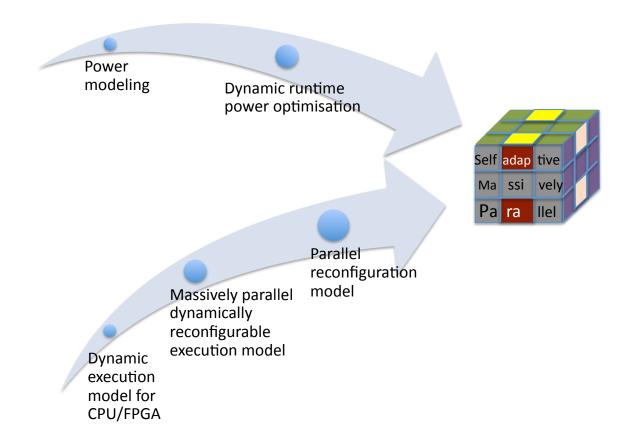

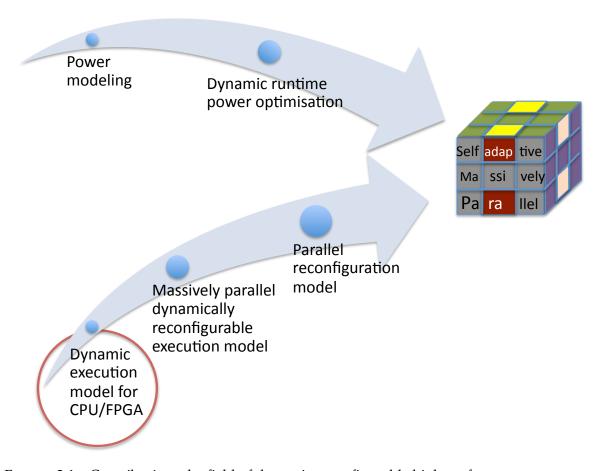

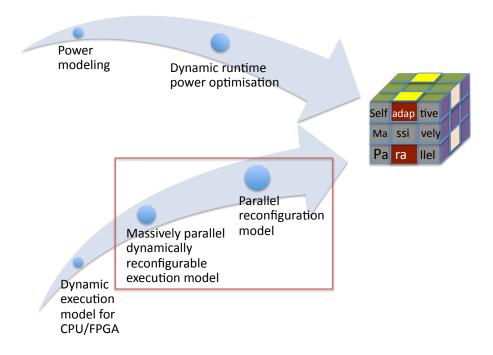

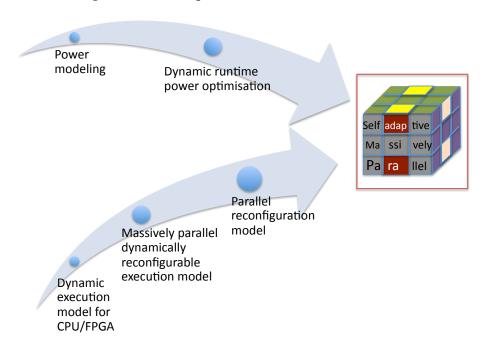

Rationale of this synthesis document. This document is a summary of my scientific contributions since my Post-doc. It aims to show coherently how my research activities on the design of dynamic reconfigurable system and low power design are leading towards self-adaptive massively parallel embedded systems.

Modern embedded applications are becoming more and more sophisticated and resource demanding. The concerned applications covers several domains such as avionic, multimedia, etc. The computation requirements for such systems are very important in order to meet real-time constraints and high quality of services. Furthermore, power consumption becomes a critical pre-design metric in complex embedded systems. Runtime adaptivity according to the system requirements or the environment variations is also a challenging characteristic which brings additional complexity to the design flow.

For addressing the above challenges, my research works are directed towards designing parallel and dynamic architecture to deal with the potential parallelism and the adaptivity inherent from the application. Mainly, we rely on multiprocessor and reconfigurable systems that could offer better power efficiency. According to the application context, the architecture can be homogeneous or heterogeneous to satisfy a specific need or to optimise better some parameters. In each step of our work, we defined the efficient dynamic execution model that handles the heterogeneity and the parallelism concepts. To cope with the development complexity, we proposed the efficient design methodology and we provided the appropriate framework regarding the application domain. This complexity is reduced by the means of Electronic System Level (ESL) tools such as simulator, power estimator, and prototyping environment.

How to consider the contents of this document. All the results reported in Chapters 2, 3 and 4 have been already published or under revision in peer-reviewed journals and conferences. In order to easily assess my achievements, a section named *discussion* is provided at the end of each chapter. Therefore, a major part of the presented material comes from the related publications. Most of my papers cited as references in this document are online available on the websites of editors or on my website.

## **Table of contents**

| Ta | ble o | f contents                                                                | vii |

|----|-------|---------------------------------------------------------------------------|-----|

| 1  | Intr  | oduction                                                                  | 1   |

|    | 1.1   | Context of the work                                                       | 3   |

|    | 1.2   | Trends and challenges                                                     | 3   |

|    |       | 1.2.1 Parallelism and heterogeneity for energy efficiency                 | 3   |

|    |       | 1.2.2 Design methodology and development tools                            | 5   |

|    |       | 1.2.3 Industrial manufacturing process                                    | 6   |

|    | 1.3   | Contributions                                                             | 6   |

|    |       | 1.3.1 CPU/FPGA dynamic execution model for avionic simulation and test    | 7   |

|    |       | 1.3.2 Energy/power-aware design for homogeneous and heterogeneous         |     |

|    |       | MPSoC:                                                                    | 11  |

|    |       | 1.3.3 Massively parallel dynamically reconfigurable execution model       | 14  |

|    | 1.4   | Outline                                                                   | 17  |

|    |       |                                                                           |     |

| 2  |       | J/FPGA Dynamic Execution Model for Avionic Simulation and Test            | 19  |

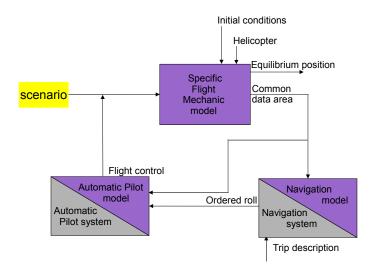

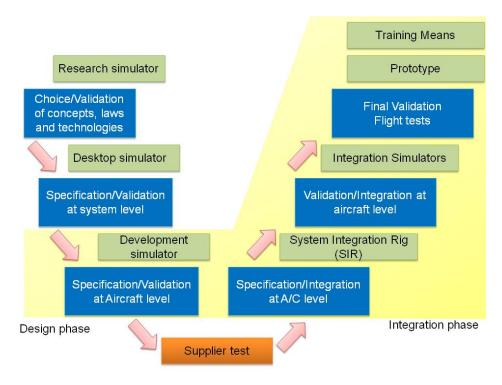

|    | 2.1   | Main challenges for avionic simulation and test                           | 22  |

|    | 2.2   | Related works                                                             | 23  |

|    | 2.3   | Reconfigurable-centric avionic design process                             | 25  |

|    |       | 2.3.1 Essential of simulation and test avionic domains                    | 25  |

|    |       | 2.3.2 The proposed design process                                         | 26  |

|    | 2.4   | Reconfigurable computing for simulation                                   | 28  |

|    |       | 2.4.1 The heterogeneous CPU/FPGA hardware environment                     | 29  |

|    |       | 2.4.2 The execution model                                                 | 30  |

|    |       | 2.4.3 Xillybus: making FPGAs talk PCIe easier                             | 31  |

|    |       | 2.4.4 Real-time simulator supporting heterogeneous CPU/FPGA architecture  |     |

|    |       | 2.4.5 Design methodology                                                  | 34  |

|    | 2.5   | Reconfigurable computing for test                                         | 35  |

|    |       | 2.5.1 Examples of avionic communication protocols                         | 37  |

|    |       | 2.5.2 Towards the convergence between the simulation and the test domains | 39  |

|    | 2.6   | Towards reconfigurable computing for embedded avionic applications        | 40  |

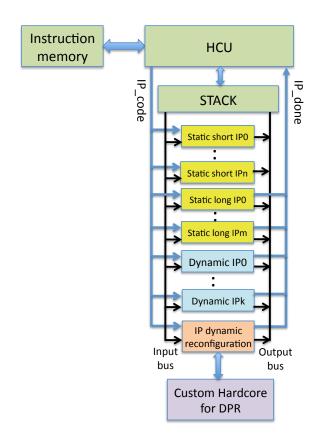

|    |       | 2.6.1 Example of runtime reconfigurable system                            | 42  |

|    | 2.7   | Experimental results                                                      | 43  |

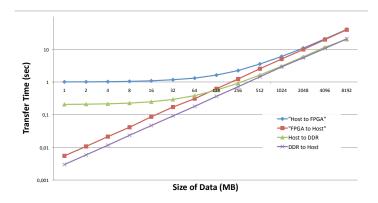

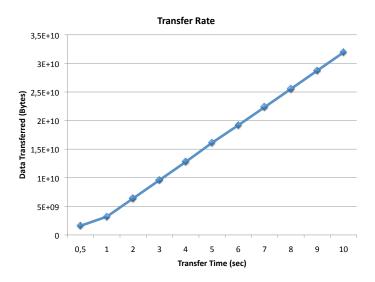

|    |       | 2.7.1 Simulation environment results                                      | 43  |

|    |       | 2.7.2 Test environment results                                            | 46  |

|    |       | 2.7.2.1 FPGA resource utilization                                         | 46  |

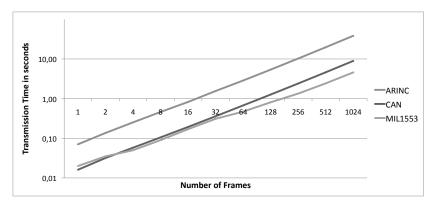

|   |     | 2.7.2.2 Transmission times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 47        |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

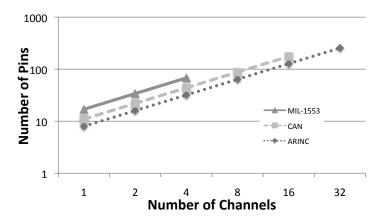

|   |     | 2.7.2.3 Number of I/O pins and channels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 47        |

|   |     | 2.7.2.4 Scalability                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 48        |

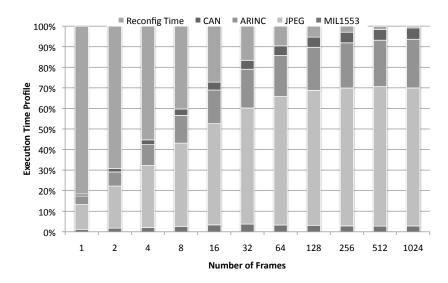

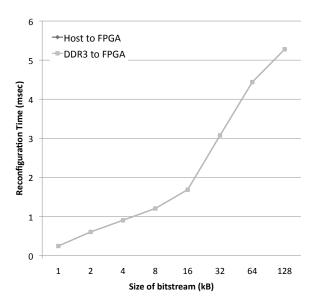

|   |     | 2.7.3 Embedded avionic application results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 49        |

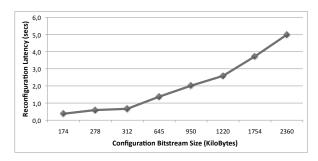

|   |     | 2.7.3.1 Reconfiguration latency and application profile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 49        |

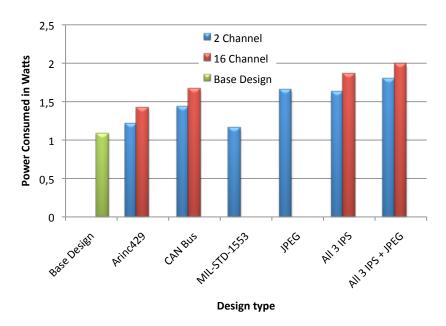

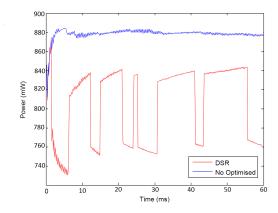

|   |     | 2.7.3.2 Power estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50        |

|   | 2.8 | Discussion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 51        |

|   |     | 2 io custom in the contract of | 01        |

| 3 | Ene | rgy/Power-Aware Design Methodology for MPSoC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | <b>53</b> |

|   | 3.1 | Main challenges for low power design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 56        |

|   | 3.2 | Related works                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 58        |

|   | 3.3 | The Open-PEOPLE platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 61        |

|   | 3.4 | Background notions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 62        |

|   | 3.5 | Power-aware design methodology:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65        |

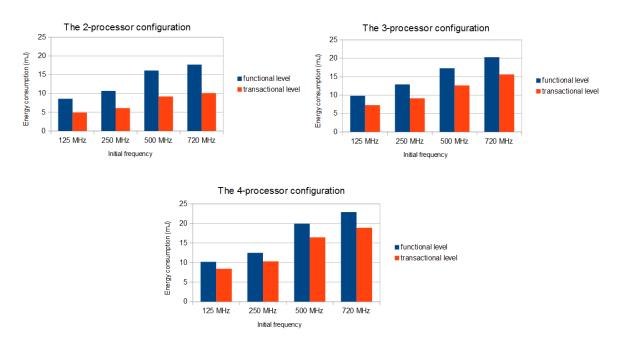

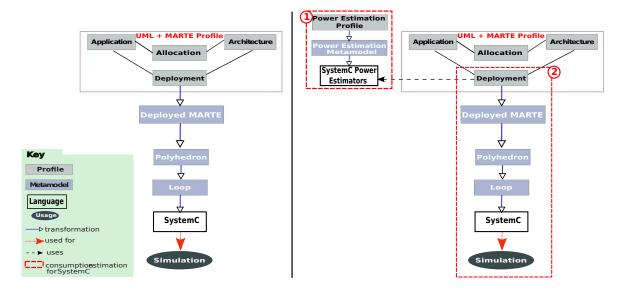

|   |     | 3.5.1 Functional-level power estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 66        |

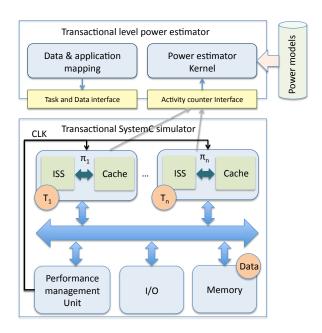

|   |     | 3.5.2 Transactional-level power estimation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 67        |

|   |     | 3.5.3 Optimisation process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 68        |

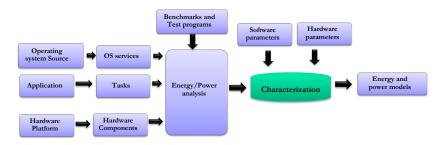

|   | 3.6 | Consumption modeling / power models                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 68        |

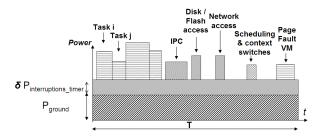

|   |     | 3.6.1 Power modeling of OS services                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 69        |

|   |     | 3.6.1.1 The context switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 69        |

|   |     | 3.6.1.2 The scheduling routines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 72        |

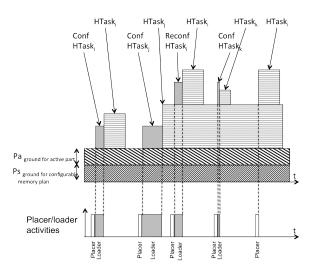

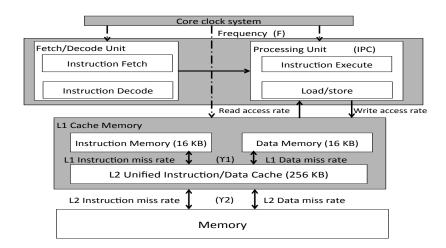

|   |     | 3.6.2 Transactional power modeling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 72        |

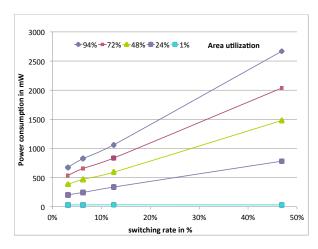

|   |     | 3.6.3 FPGA power model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 74        |

|   | 3.7 | The multi-level design space exploration:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 75        |

|   | 0.7 | 3.7.1 The JPEG case-study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | <b>75</b> |

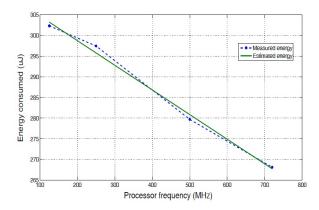

|   |     | 3.7.1.1 Monoprocessor architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75        |

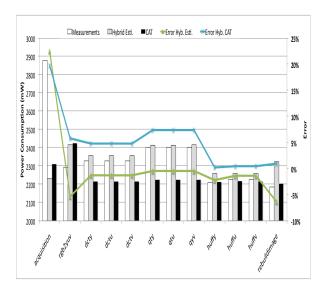

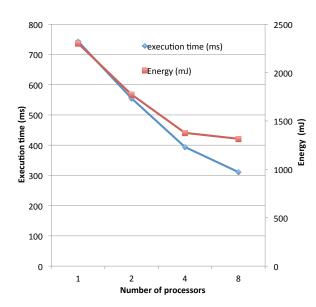

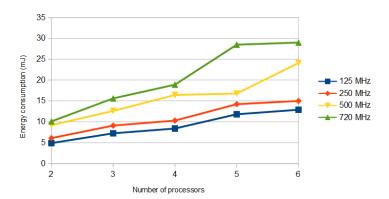

|   |     | 3.7.1.2 Homogeneous multiprocessor architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 77        |

|   |     | 3.7.1.3 Hardware accelerator design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 77        |

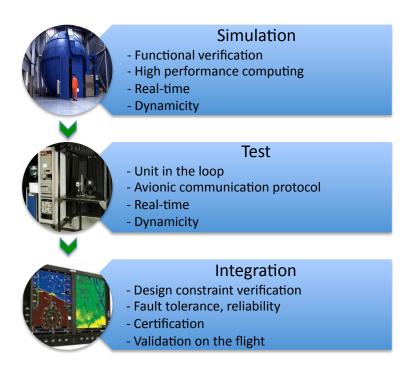

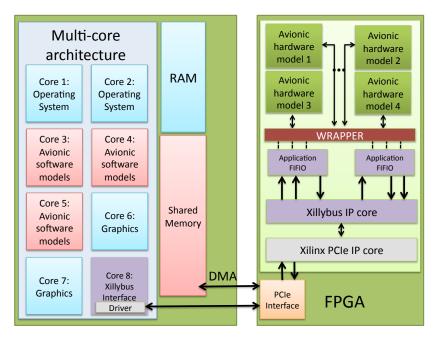

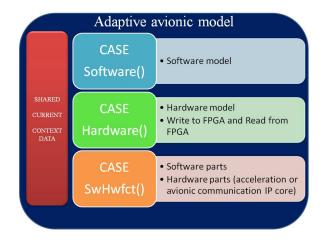

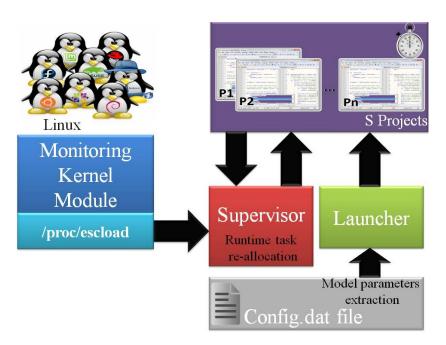

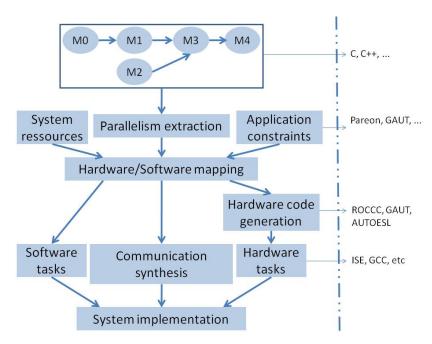

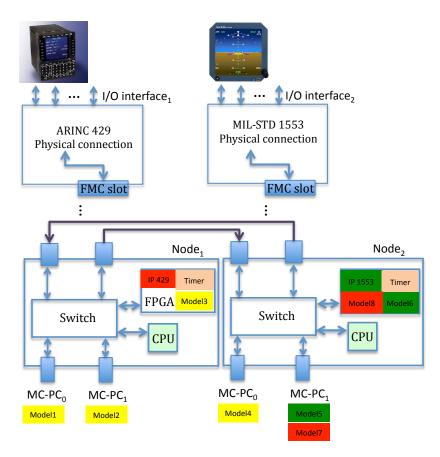

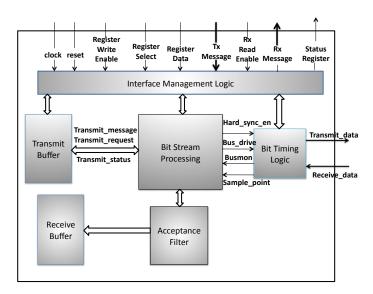

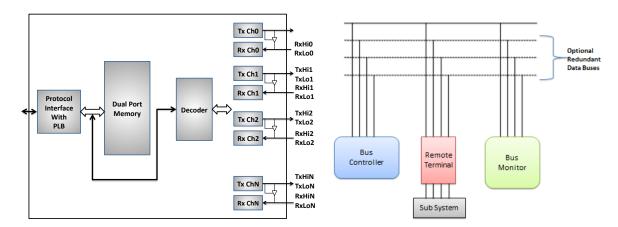

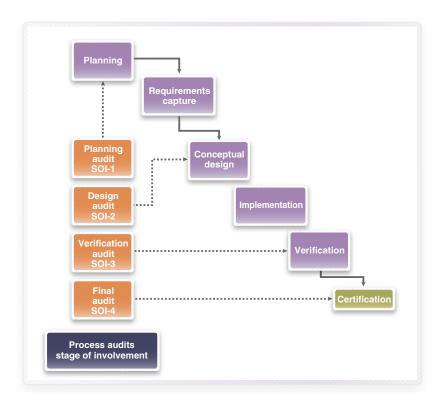

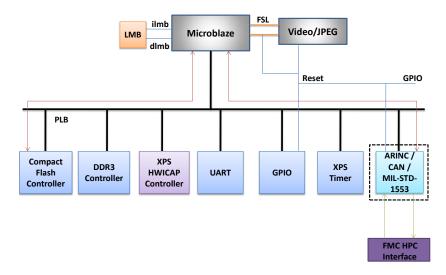

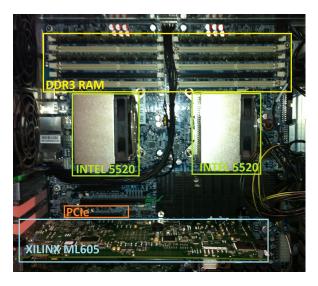

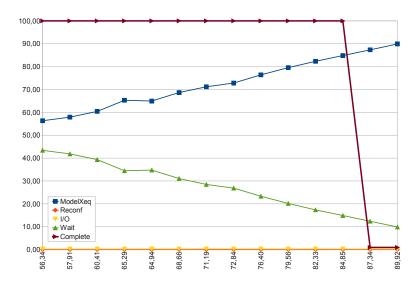

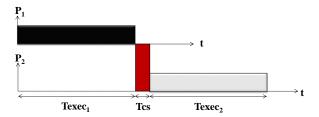

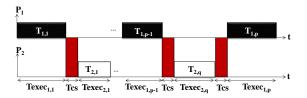

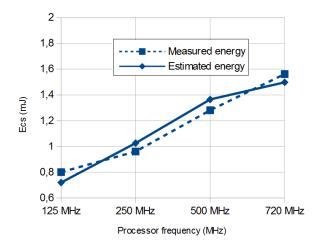

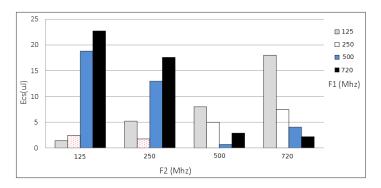

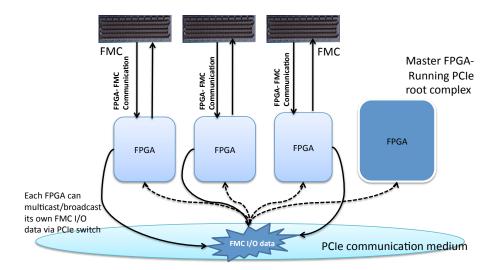

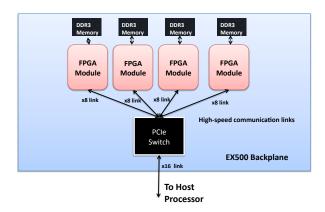

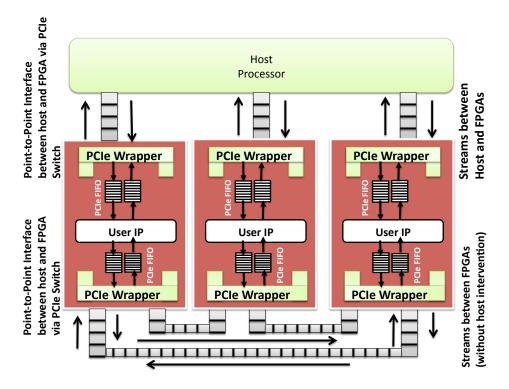

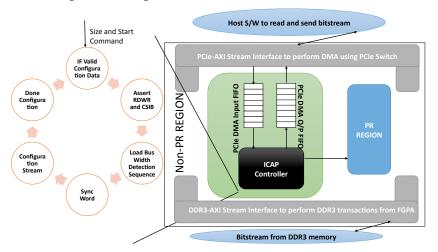

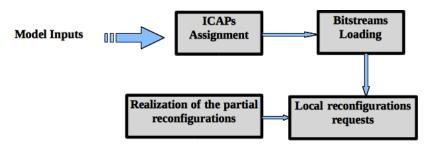

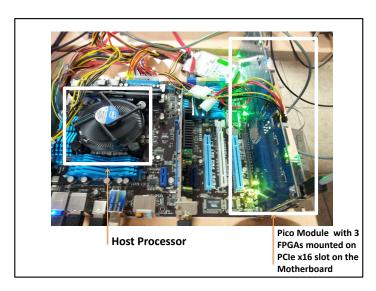

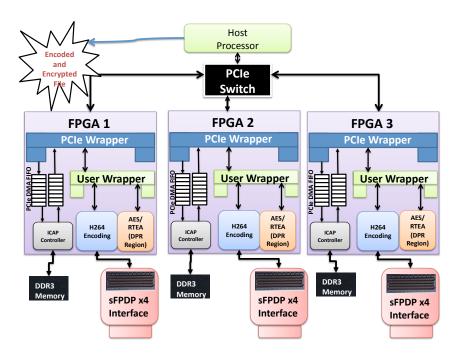

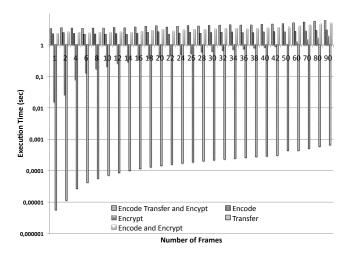

|   |     | 3.7.1.4 Extrapolation for complete MPSoC architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 78        |