# Scaling the solution of large sparse linear systems using multifrontal methods on hybrid shared-distributed memory architectures

Mohamed Wissam Sid Lakhdar

## ▶ To cite this version:

Mohamed Wissam Sid Lakhdar. Scaling the solution of large sparse linear systems using multifrontal methods on hybrid shared-distributed memory architectures. Other [cs.OH]. Ecole normale supérieure de lyon - ENS LYON, 2014. English. NNT: 2014ENSL0958. tel-01111259

HAL Id: tel-01111259

https://hal.inria.fr/tel-01111259

Submitted on 30 Jan 2015

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

### THÈSE

en vue de l'obtention du grade de

## Docteur de l'Université de Lyon, délivré par l'École Normale Supérieure de Lyon

Discipline: Informatique

Laboratoire : Laboratoire de l'Informatique du Parallélisme - UMR5668 - LIP

École Doctorale : Informatique et Mathématiques

présentée et soutenue publiquement le 1<sup>er</sup> Décembre 2014

par Monsieur Wissam M. SID-LAKHDAR

Scaling the solution of large sparse linear systems using multifrontal methods on hybrid shared-distributed memory architectures

Directeur de thèse : Jean-Yves L'EXCELLENT

Devant la commission d'examen formée de :

Mr Patrick AMESTOY

Mr Iain DUFF

Rapporteur

Mr Jean-Yves L'EXCELLENT

Mme Xiaoye Sherry LI

Mr Jean-François MÉHAUT

Mr François PELLEGRINI

Mr Antoine PETITET

Rapporteur

Examinateur

Examinateur

## Abstract

The solution of sparse systems of linear equations is at the heart of numerous application fields. While the amount of computational resources in modern architectures increases and offers new perspectives, the size of the problems arising in today's numerical simulation applications also grows very much. Exploiting modern architectures to solve very large problems efficiently is thus a challenge, from both a theoretical and an algorithmic point of view. The aim of this thesis is to address the scalability of sparse direct solvers based on multifrontal methods in parallel asynchronous environments.

In the first part of this thesis, we focus on exploiting multi-threaded parallelism on shared-memory architectures. A variant of the Geist-Ng algorithm is introduced to handle both fine grain parallelism through the use of optimized sequential and multi-threaded BLAS libraries and coarser grain parallelism through explicit OpenMP based parallelization. Memory aspects are then considered to further improve performance on NUMA architectures: (i) on the one hand, we analyse the influence of memory locality and exploit adaptive memory allocation strategies to manage private and shared workspaces; (ii) on the other hand, resource sharing on multicore processors induces performance penalties when many cores are active (machine load effects) that we also consider. Finally, in order to avoid resources remaining idle when they have finished their share of the work, and thus, to efficiently exploit all computational resources available, we propose an algorithm which is conceptually very close to the work-stealing approach and which consists in dynamically assigning idle cores to busy threads/activities.

In the second part of this thesis, we target hybrid shared-distributed memory architectures, for which specific work to improve scalability is needed when processing large problems. We first study and optimize the dense linear algebra kernels used in distributed asynchronous multifrontal methods. Simulation, experimentation and profiling have been performed to tune parameters controlling the algorithm, in correlation with problem size and computer architecture characteristics. To do so, right-looking and left-looking variants of the LU factorization with partial pivoting in our distributed context have been revisited. Furthermore, when computations are accelerated with multiple cores, the relative weight of communication with respect to computation is higher. We explain how to design mapping algorithms minimizing the communication between nodes of the dependency tree of the multifrontal method, and show that collective asynchronous communications become critical on large numbers of processors. We explain why asynchronous broadcasts using standard tree-based communication algorithms must be used. We then show that, in a fully asynchronous multifrontal context where several such asynchronous communication trees coexist, new synchronization issues must be addressed. We analyse and characterize the possible deadlock situations and formally establish simple global properties to handle deadlocks. Such properties partially force synchronization and may limit performance. Hence, we define properties which enable us to relax synchronization and thus improve performance. Our approach is based on the observation that, in our case, as long as memory is available, deadlocks cannot occur and, consequently, we just need to keep enough memory to guarantee that a deadlock can always be avoided. Finally, we show that synchronizations can be relaxed in a state-of-the-art solver and illustrate the performance gains on large real problems in our fully asynchronous multifrontal approach.

## Acknowledgment

Je tiens tout d'abord à remercier mon encadrant, Jean-Yves L'EXCELLENT. J'ai eu la chance de le connaître et de le côtoyer, et ai pu me rendre compte de ces qualités remarquables, aussi bien humaines que professionnelles. Durant des années, il a consacré un temps incommensurable à me former, à m'encourager et à me guider, outrepassant largement son rôle d'encadrant. Pour tout cela et bien plus encore, merci Jean-Yves.

Je souhaite ensuite remercier Patrick AMESTOY, de m'avoir suivi, des premiers pas en master jusqu'à l'achèvement de la thèse, de m'avoir promulguer de très précieux conseilles, et surtout, de m'avoir permis d'acquérir cette vision globale des choses, fondamentale à la recherche scientifique.

J'aimerai tout particulièrement remercier Iain DUFF et Jean-François MÉHAUT de m'avoir fait l'honneur d'être les rapporteurs de ma thèse. Leurs remarques m'ont été d'une grande aide, et m'ont permis d'améliorer la qualité de mon manuscrit.

Je voudrai aussi remercier Sherry LI, François PELLEGRINI et Antoine PETITET de bien avoir accepté d'être membres de mon jury, et d'avoir fait l'effort de voyager de très loin a cette occasion.

Aussi, je tiens à remercier les membres de l'équipe MUMPS et de l'équipe ROMA (ainsi que de membres d'autres équipes :-), d'avoir été des amies et même une seconde famille, et pour tout ces moments forts agréables et enrichissants que l'on a passé ensemble.

Enfin, j'aimerai remercier les personnes sans qui rien n'aurai été possible, a savoir, ma famille, et tout particulièrement, mon père et ma mère. Ils ce sont sacrifiés toute leur vie pour nous permettre a mon frère et a moi même de nous épanouir et d'atteindre nos objectifs.

La dernière personne que j'aimerai remercier, non des moindres, est mon oncle et mentor: Daddy. Aussi longtemps que je me souvienne, il a toujours joué et continue à jouer un rôle clef dans ma vie. Je lui dédie cette thèse.

## Contents

| 1            | Bac  | kground                                                                          | 3                                                                                        |  |  |

|--------------|------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|--|

|              | 1.1  | Introduction                                                                     | 3                                                                                        |  |  |

|              | 1.2  | Solution methods                                                                 | 5                                                                                        |  |  |

|              |      | 1.2.1 Direct methods                                                             | 5                                                                                        |  |  |

|              |      | 1.2.2 Iterative methods                                                          | 6                                                                                        |  |  |

|              | 1.3  | Sparse direct methods                                                            | 6                                                                                        |  |  |

|              |      | 1.3.1 Analysis phase: Sparse matrices and graphs                                 | 7                                                                                        |  |  |

|              |      | 1.3.1.1 Adjacency graph                                                          | 7                                                                                        |  |  |

|              |      | 1.3.1.2 Symbolic factorization: filled graph                                     | 7                                                                                        |  |  |

|              |      | 1.3.1.3 Reordering and permutations                                              | 8                                                                                        |  |  |

|              |      | 1.3.1.4 Dependencies between variables and elimination tree                      | 10                                                                                       |  |  |

|              |      | 1.3.1.5 Supernodes                                                               | 11                                                                                       |  |  |

|              |      | 1.3.1.6 Symmetric and unsymmetric matrices                                       | 11                                                                                       |  |  |

|              |      | 1.3.2 Factorization phase: left-looking, right-looking and supernodal approaches | 11                                                                                       |  |  |

|              |      |                                                                                  | 13                                                                                       |  |  |

|              | 1.4  | Parallelism on shared- and distributed-memory architectures                      | 14                                                                                       |  |  |

|              |      |                                                                                  |                                                                                          |  |  |

| Ι            | Sha  | ared-memory environments                                                         | 17                                                                                       |  |  |

| $\mathbf{A}$ | Intr | roduction of part I                                                              | 19                                                                                       |  |  |

|              | A.1  |                                                                                  | 19                                                                                       |  |  |

|              | A.2  |                                                                                  | 21                                                                                       |  |  |

| <b>2</b>     | Mu   | tithreaded node and tree parallelism                                             | 23                                                                                       |  |  |

|              | 2.1  | 1                                                                                | 5<br>6<br>6<br>7<br>7<br>8<br>10<br>11<br>11<br>11<br>13<br>14<br><b>17</b><br><b>19</b> |  |  |

|              |      | -                                                                                | 23                                                                                       |  |  |

|              |      | 2.1.2 Directive-based loop parallelism                                           | 24                                                                                       |  |  |

|              |      |                                                                                  | 24                                                                                       |  |  |

|              | 2.2  | Introduction of multithreaded tree parallelism                                   | 25                                                                                       |  |  |

|              |      |                                                                                  | 26                                                                                       |  |  |

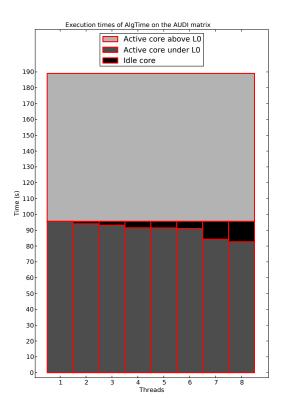

|              |      | 2.2.2 Minimizing the global runtime (ALGTIME algorithm)                          | 27                                                                                       |  |  |

|              |      | 2.2.2.1 Algorithm principle                                                      | 27                                                                                       |  |  |

|              |      | 2.2.2.2 Performance model                                                        | 29                                                                                       |  |  |

|              |      | 2.2.3 Simulation                                                                 | 30                                                                                       |  |  |

|              |      | 2.2.4 Implementation of the factorization phase                                  | 31                                                                                       |  |  |

|              |      | 2.2.5 Experiments                                                                | 39                                                                                       |  |  |

| 3            | Impact of NUMA architectures on multithreaded parallelism |                                                                                  |           |  |  |  |  |  |

|--------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|-----------|--|--|--|--|--|

|              | 3.1                                                       | Impact of memory locality and affinity                                           | 35        |  |  |  |  |  |

|              |                                                           | 3.1.1 Impact of memory allocation policies on dense factorization performance .  | 36        |  |  |  |  |  |

|              |                                                           | 3.1.2 Adaptation of $\mathcal{L}_{th}$ -based algorithms for NUMA architectures  | 37        |  |  |  |  |  |

|              |                                                           | 3.1.3 Effects of the interleave policy                                           | 38        |  |  |  |  |  |

|              | 3.2                                                       | Resource sharing and racing                                                      | 40        |  |  |  |  |  |

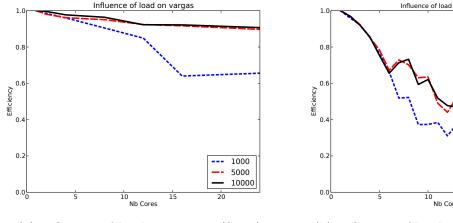

|              | 0.2                                                       | 3.2.1 Impact of machine loading on dense factorization performance               | 40        |  |  |  |  |  |

|              |                                                           |                                                                                  | 42        |  |  |  |  |  |

|              | 0.0                                                       | 1                                                                                |           |  |  |  |  |  |

|              | 3.3                                                       | Summary                                                                          | 43        |  |  |  |  |  |

| 4            | Rec                                                       | cycling Idle Cores                                                               | <b>45</b> |  |  |  |  |  |

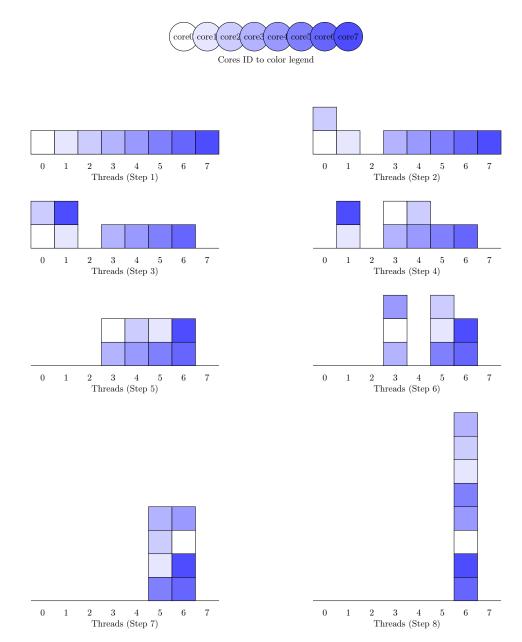

|              | 4.1                                                       | Motivation                                                                       | 45        |  |  |  |  |  |

|              | 4.2                                                       | Core idea                                                                        | 46        |  |  |  |  |  |

|              | 4.3                                                       | Detailed algorithm                                                               | 47        |  |  |  |  |  |

|              | 4.4                                                       | Implementation                                                                   | 48        |  |  |  |  |  |

|              | 4.5                                                       | Optimization for earlier core detection                                          | 50        |  |  |  |  |  |

|              | 4.6                                                       | •                                                                                | 52        |  |  |  |  |  |

|              | 4.0                                                       | Experimental study                                                               |           |  |  |  |  |  |

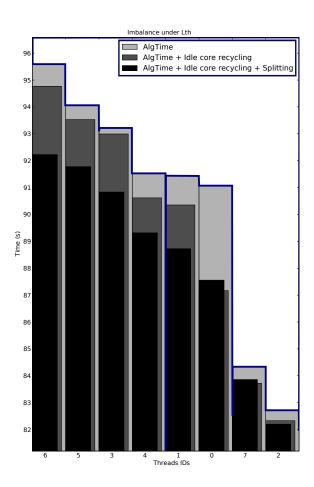

|              |                                                           | 4.6.1 Impact of ICR                                                              | 52        |  |  |  |  |  |

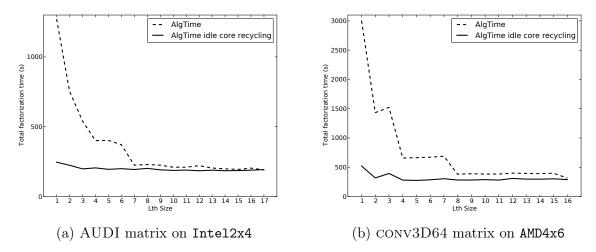

|              |                                                           | 4.6.2 Sensitivity to $\mathcal{L}_{th}$ height                                   | 53        |  |  |  |  |  |

|              | 4.7                                                       | Conclusion                                                                       | 54        |  |  |  |  |  |

| В            | Con                                                       | nclusion of part I                                                               | 55        |  |  |  |  |  |

|              | B.1                                                       | Summary                                                                          | 55        |  |  |  |  |  |

|              | B.2                                                       | Real life applications                                                           | 56        |  |  |  |  |  |

| В            | D.2                                                       | B.2.1 Electromagnetism                                                           | 56        |  |  |  |  |  |

|              |                                                           |                                                                                  | 56        |  |  |  |  |  |

|              | D a                                                       | 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                            |           |  |  |  |  |  |

|              | В.3                                                       | Discussion                                                                       | 57        |  |  |  |  |  |

|              |                                                           | B.3.1 Multithreaded solve phase                                                  | 57        |  |  |  |  |  |

|              |                                                           | B.3.2 Scheduling threads in multithreaded BLAS                                   | 57        |  |  |  |  |  |

|              |                                                           | B.3.3 Path to shared-distributed memory environments                             | 58        |  |  |  |  |  |

|              |                                                           |                                                                                  |           |  |  |  |  |  |

| II           | H                                                         | ybrid-memory environments                                                        | 59        |  |  |  |  |  |

| $\mathbf{C}$ | Intr                                                      | roduction to part II                                                             | 61        |  |  |  |  |  |

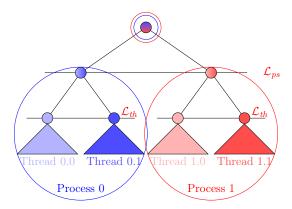

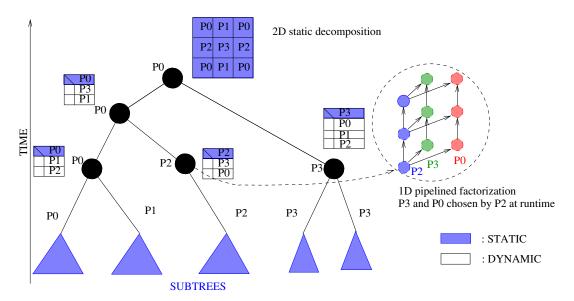

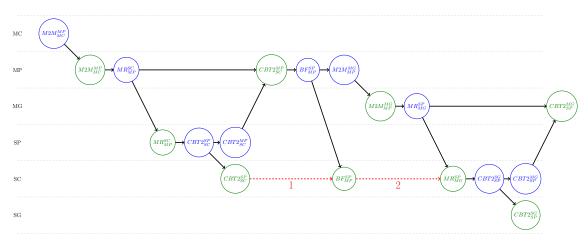

|              | C.1                                                       | Types of parallelism                                                             | 61        |  |  |  |  |  |

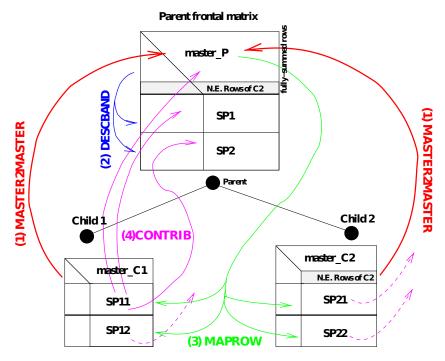

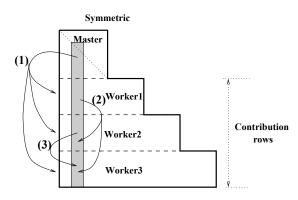

|              | C.2                                                       | Distributed-memory node assembly algorithm                                       | 63        |  |  |  |  |  |

|              | C.3                                                       | Distributed-memory node factorization algorithm                                  | 63        |  |  |  |  |  |

|              | C.4                                                       | Management of asynchronism and communication                                     | 64        |  |  |  |  |  |

|              | C.5                                                       | Experimental environment                                                         | 66        |  |  |  |  |  |

|              | C.5                                                       | •                                                                                |           |  |  |  |  |  |

|              |                                                           | C.5.1 Summary of main notations used in PartII                                   | 66        |  |  |  |  |  |

| 5            | Dist                                                      | tributed-memory partial factorization of frontal matrices                        | 69        |  |  |  |  |  |

|              | 5.1                                                       | Introduction                                                                     | 69        |  |  |  |  |  |

|              | 5.2                                                       | Preliminary study on an example                                                  | 69        |  |  |  |  |  |

|              |                                                           | 5.2.1 Experimental environment                                                   | 70        |  |  |  |  |  |

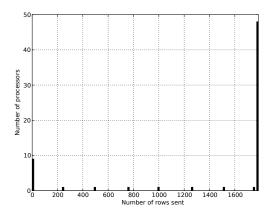

|              |                                                           | 5.2.2 Description of the experimental results                                    | 71        |  |  |  |  |  |

|              | 5.3                                                       | Right-looking and Left-looking 1D acyclic pipelined asynchronous partial factor- | • •       |  |  |  |  |  |

|              | 0.0                                                       | izations                                                                         | 73        |  |  |  |  |  |

|              |                                                           |                                                                                  |           |  |  |  |  |  |

|              |                                                           | 5.3.1 Model and Simulator                                                        | 73        |  |  |  |  |  |

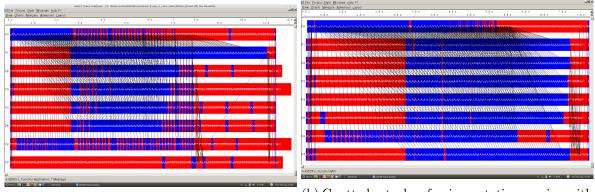

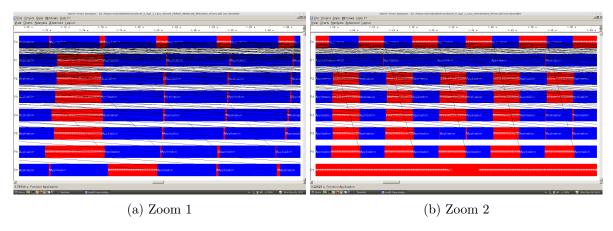

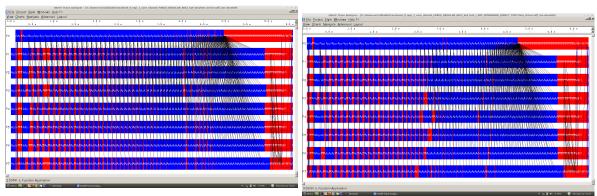

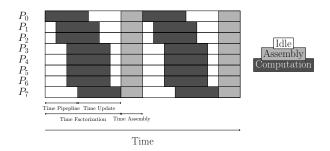

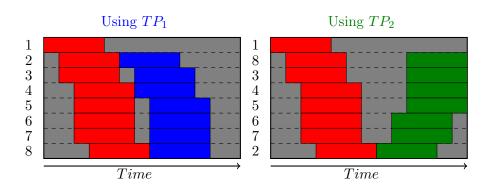

|   |       | 5.3.2 Gantt-charts with RL and LL factorizations on the master                                                   | 75              |

|---|-------|------------------------------------------------------------------------------------------------------------------|-----------------|

|   |       | 5.3.3 Communication memory evolution                                                                             | . 77            |

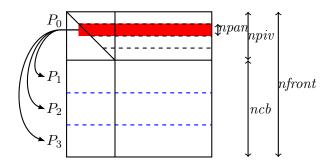

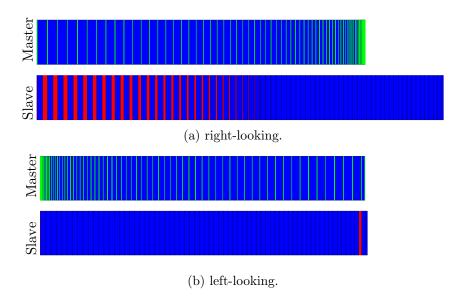

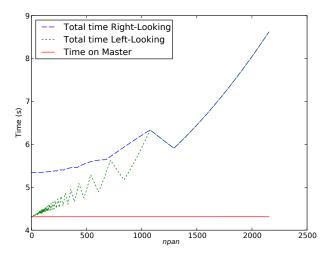

|   |       | 5.3.4 Influence of the granularity parameter <i>npan</i>                                                         | . 78            |

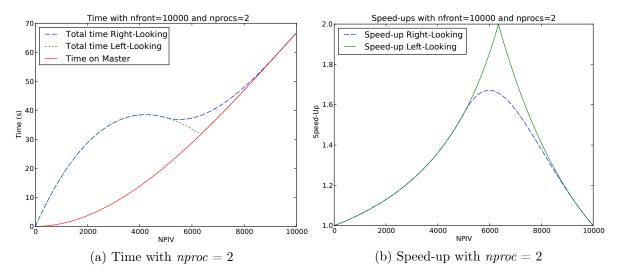

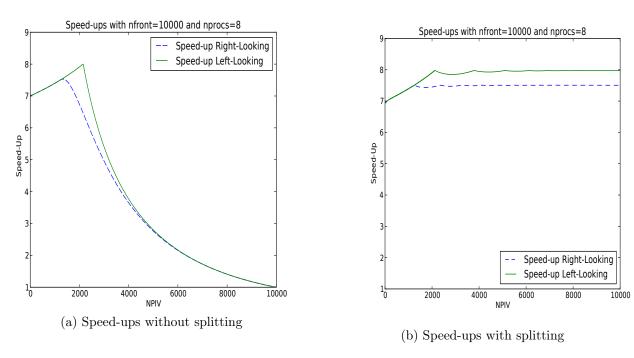

|   |       | 5.3.5 Influence of <i>npiv</i> and <i>nfront</i> on the load balance                                             | . 78            |

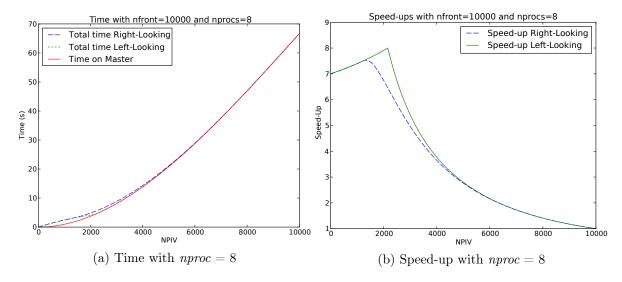

|   |       | 5.3.6 Influence of the scalability parameter $nproc$                                                             | . 79            |

|   | 5.4   | Communication schemes                                                                                            | . 80            |

|   |       | 5.4.1 Sharing bandwidth for panel transmission ( <i>IBcast</i> )                                                 | . 80            |

|   |       | 5.4.2 Impact of limited bandwidth                                                                                | . 80            |

|   |       | 5.4.3 Experimental Results                                                                                       | 81              |

|   | 5.5   | Computation schemes                                                                                              | . 82            |

|   |       | 5.5.1 Impact of limited GFlops rate                                                                              | . 82            |

|   |       | 5.5.2 Multi-Panel factorization in shared-memory                                                                 | . 83            |

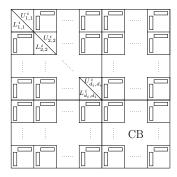

|   |       | 5.5.2.1 Multiple levels of blocking                                                                              | . 83            |

|   |       | 5.5.2.2 Choice of block sizes                                                                                    | 85              |

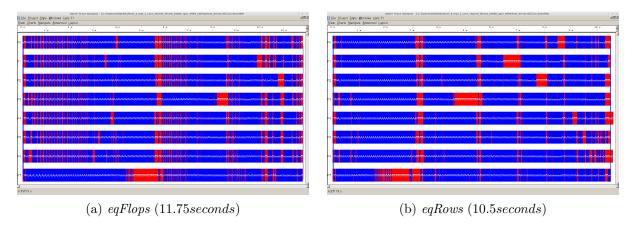

|   |       | 5.5.2.3 BLAS performance on RL-like vs LL-like patterns                                                          | . 86            |

|   |       | 5.5.2.4 Experimental results on sparse matrices                                                                  | . 87            |

|   |       | 5.5.3 Multipanel factorization in hybrid-memory                                                                  | . 88            |

|   | 5.6   | Conclusion                                                                                                       | . 89            |

| _ |       |                                                                                                                  |                 |

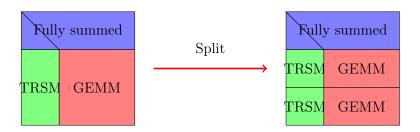

| 6 | 6.1   | nitations of splitting to improve the performance on multifrontal chains  Introduction                           | <b>91</b><br>91 |

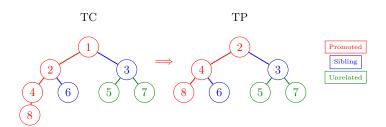

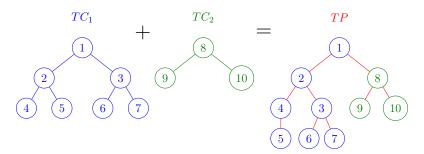

|   | 6.2   | Splitting                                                                                                        |                 |

|   | 0.2   | 6.2.1 Splitting algorithms                                                                                       |                 |

|   |       | 6.2.2 Results of splitting                                                                                       |                 |

|   | 6.3   | (Re)Mapping                                                                                                      |                 |

|   | 0.0   | 6.3.1 Remapping strategies                                                                                       |                 |

|   |       | 6.3.2 Remapping model                                                                                            |                 |

|   |       | 6.3.3 Restart algorithm                                                                                          |                 |

|   |       | 6.3.4 Theoretical results                                                                                        |                 |

|   |       | 6.3.5 Experimental results and bottlenecks of the approach                                                       |                 |

|   |       |                                                                                                                  |                 |

| 7 |       | nimizing assembly communications                                                                                 | 103             |

|   | 7.1   | Introduction                                                                                                     |                 |

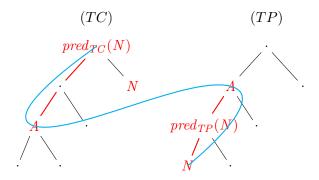

|   |       | 7.1.1 Problem definition                                                                                         |                 |

|   |       | 7.1.2 Assignment problem                                                                                         |                 |

|   |       | 7.1.3 State of the Art                                                                                           |                 |

|   | 7.0   | 7.1.4 Overview                                                                                                   |                 |

|   | 7.2   | Algorithm to minimize assembly communications in the general case 7.2.1 Hungarian Method on Blocks of rows (HMB) |                 |

|   |       |                                                                                                                  |                 |

|   |       | 7.2.2 Fronts characteristics and ordering of the rows                                                            |                 |

|   | 7.9   | 7.2.3 Hungarian Method on Rows (HMR)                                                                             |                 |

|   | 7.3   | Special case of split chains                                                                                     |                 |

|   |       | 7.3.1 Illustrative Example                                                                                       |                 |

|   | 7.4   | 7.3.2 Remapping algorithm                                                                                        |                 |

|   | 7.4   | Simulation results                                                                                               |                 |

|   |       | 7.4.1 Results in the general case                                                                                |                 |

|   |       | 7.4.2. Total remapping communication volume                                                                      |                 |

|   |       | 7.4.2.1 Total remapping communication volume                                                                     |                 |

|   | 75    | Conclusion                                                                                                       | 118             |

|   | 4 . 1 | A 8 0 0 10 5 0 0 0                                                                                               |                 |

| 8 | Syn | nchronizations in distributed asynchronous environments                                            | 121  |  |  |  |  |  |  |

|---|-----|----------------------------------------------------------------------------------------------------|------|--|--|--|--|--|--|

|   | 8.1 | Introduction                                                                                       | 121  |  |  |  |  |  |  |

|   |     | 8.1.1 Motivation                                                                                   | 123  |  |  |  |  |  |  |

|   |     | 8.1.2 Goal                                                                                         | 123  |  |  |  |  |  |  |

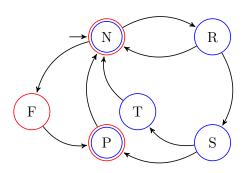

|   |     | 8.1.3 Theory of deadlocks                                                                          | 124  |  |  |  |  |  |  |

|   |     | 8.1.4 Models and general assumptions                                                               | 125  |  |  |  |  |  |  |

|   | 8.2 | Deadlock issues                                                                                    | 126  |  |  |  |  |  |  |

|   |     | 8.2.1 Deadlock prevention solutions                                                                |      |  |  |  |  |  |  |

|   |     | 8.2.1.1 Global order on processes in broadcast trees                                               | 126  |  |  |  |  |  |  |

|   |     | 8.2.1.2 One buffer per active front on each process                                                | 127  |  |  |  |  |  |  |

|   |     | 8.2.1.3 One additional buffer per cycle                                                            |      |  |  |  |  |  |  |

|   |     | 8.2.2 Deadlock avoidance solutions                                                                 | 128  |  |  |  |  |  |  |

|   |     | 8.2.2.1 Global order on tasks                                                                      | 129  |  |  |  |  |  |  |

|   |     | 8.2.2.2 Application of global task order and impact of task graph topolog                          | y129 |  |  |  |  |  |  |

|   |     | 8.2.2.3 Deadlock avoidance vs. deadlock prevention approaches                                      | 131  |  |  |  |  |  |  |

|   | 8.3 | Performance issues                                                                                 | 131  |  |  |  |  |  |  |

|   |     | 8.3.1 Impact of broadcast trees on performance                                                     | 132  |  |  |  |  |  |  |

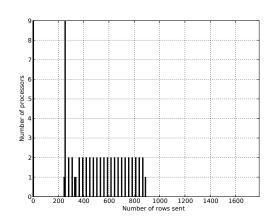

|   |     | 8.3.1.1 Effect of broadcast trees on pipelining                                                    | 132  |  |  |  |  |  |  |

|   |     | 8.3.1.2 Characterisation of compatible broadcast trees                                             | 134  |  |  |  |  |  |  |

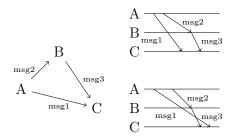

|   |     | 8.3.2 Asynchronous Broad Cast $(ABC_w)$ Trees                                                      | 136  |  |  |  |  |  |  |

|   |     | 8.3.2.1 $ABC_w$ trees in multifrontal chains                                                       | 136  |  |  |  |  |  |  |

|   |     | 8.3.2.2 $ABC_w$ trees in multifrontal trees                                                        | 138  |  |  |  |  |  |  |

|   | 8.4 | (Re)Mapping-aware synchronization issues                                                           | 140  |  |  |  |  |  |  |

|   |     | 8.4.1 Static mapping with static remapping                                                         |      |  |  |  |  |  |  |

|   |     | 8.4.1.1 Deadlock prevention                                                                        | 141  |  |  |  |  |  |  |

|   |     | 8.4.1.2 Deadlock avoidance                                                                         | 141  |  |  |  |  |  |  |

|   |     | 8.4.2 Dynamic mapping with dynamic remapping                                                       | 142  |  |  |  |  |  |  |

|   | 8.5 | Conclusion                                                                                         | 142  |  |  |  |  |  |  |

| a | Δηι | plication to an asynchronous sparse multifrontal solver                                            | 145  |  |  |  |  |  |  |

| J | 9.1 | Introduction                                                                                       |      |  |  |  |  |  |  |

|   | 9.2 | Former synchronization solutions in MUMPS                                                          |      |  |  |  |  |  |  |

|   | 9.3 | Proposed minimal synchronization solutions in MUMPS                                                |      |  |  |  |  |  |  |

|   | 0.0 | 9.3.1 Identification of messages with fronts                                                       |      |  |  |  |  |  |  |

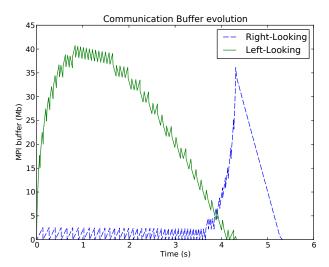

|   |     | 9.3.2 Communication buffer management system                                                       |      |  |  |  |  |  |  |

|   |     | 9.3.3 Dynamic scheduling decisions                                                                 |      |  |  |  |  |  |  |

|   | 9.4 | Preliminary experimental results                                                                   |      |  |  |  |  |  |  |

| A |     | 9.4.1 Results on chains                                                                            |      |  |  |  |  |  |  |

|   |     | 9.4.2 Results on trees                                                                             |      |  |  |  |  |  |  |

|   | 9.5 | Conclusion                                                                                         |      |  |  |  |  |  |  |

| D | Cor | nclusion of part II                                                                                | 155  |  |  |  |  |  |  |

| ر | 201 | notable of part II                                                                                 | 100  |  |  |  |  |  |  |

| A | -   | plementation remarks                                                                               | 161  |  |  |  |  |  |  |

|   | A.1 | Details on the application of the interleave policy for the use of $\mathcal{L}_{th}$ -based algo- | 1.01 |  |  |  |  |  |  |

|   | ۸ ۵ | rithms on NUMA architectures                                                                       |      |  |  |  |  |  |  |

|   | A.2 | How to associate message tags to tasks?                                                            | 102  |  |  |  |  |  |  |

| R | Duk | bligations related to the thosis                                                                   | 165  |  |  |  |  |  |  |

## General Introduction

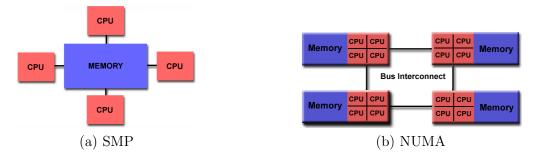

At the time when scientists started using computers for solving linear systems of equations, they were still able to solve them by hand. Since that time, each increase in the problem size has induced the need for more powerful computers. In turn, the fulfilment of this need has opened the door to ever increasing problem sizes and has brought an increasing interest in the subject. The solution of sparse systems of linear equations is nowadays at the heart of numerous application fields. Such systems now contain billions of unknowns, making them hard to solve without involving advanced algorithms and techniques. Modern computers, which are being used to solve them, have been also increasing in size. They now contain hundreds of thousands of computing units, at the forefront of technology, organized into structures of increasing complexity, with distributed-memory machines composed of nodes interconnected with hierarchies of networks, each shared-memory node containing, in turn, hierarchies of processors and memories, called NUMA<sup>1</sup> architectures. Exploiting modern architectures to solve very large problems efficiently has become a challenge, from both a theoretical and an algorithmic point of view. For instance, as the cost of synchronizations increases along with the number of computing resources, it has become worthwhile to handle parallelism in an asynchronous way.

The aim of this thesis is to address the scalability of the solution of such systems in parallel asynchronous environments. We consider here the case of the LU factorization of a sparse matrix using the so-called multifrontal method, where the factorization of a sparse matrix boils down to a succession of computations on smaller dense matrices. We provide the necessary background in Chapter 1. The rest of the thesis is then organized in the following two parts.

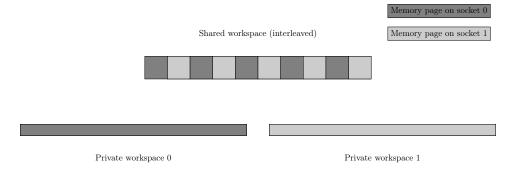

In the first part, we focus on improving the exploitation of multithreaded parallelism on shared-memory architectures. An algorithm is introduced to handle both fine and coarser grain parallelisms through the use of optimized sequential and multithreaded linear algebra libraries and through the use of explicit parallelization directives, respectively. In order to take advantage of modern NUMA architectures, it is necessary to consider memory aspects. On the one hand, we analyse the influence of memory locality and exploit adaptive memory allocation strategies to manage data over threads. On the other hand, we also consider resource sharing and machine load effects on multicore processors, which induces performance penalties when many cores are active simultaneously. Finally, to further improve performance, we try to exploit efficiently all computational resources available by avoiding resources remaining idle when they finish their share of the work. We propose an algorithm which is conceptually very close to the work-stealing approach and that consists in dynamically assigning idle cores to busy threads/activities.

In the second part of the thesis, we aim at improving the scalability of processing large problems on hybrid shared-distributed memory architectures.

<sup>&</sup>lt;sup>1</sup>Non-Uniform Memory Access.

As they lie at the heart of distributed asynchronous multifrontal methods, we will first study the specific dense linear algebra kernels used in such methods, through simulations, experimentations and profiling. We then optimize them and tune the parameters controlling them, that depend on problem sizes and computer architecture characteristics. Because of their nice numerical properties, we are concerned with distributions of dense frontal matrices in a single dimension (so called 1D), and we revisit right-looking and left-looking variants of the 1D LU factorization with partial numerical pivoting within a distributed-memory context. Additionally, when computations are accelerated with multithreaded shared-memory parallelism, the relative weight of communication with respect to computation increases.

In particular, when the sets of processes which are used in two related tasks are distinct, a type of communications that can be costly may consist in migration operations aiming at ensuring a good load balance. We therefore explain how to design efficient mapping and remapping algorithms that minimize the amount of communication associated with such operations.

Furthermore, on large numbers of processors, one-to-all asynchronous communications become a bottleneck for performance. We thus explain how asynchronous broadcast algorithms can be used effectively in a fully-asynchronous environment. When several such broadcasts coexist, deadlock issues can arise because of limited memory for communication. Managing them often comes at the price of synchronizations which hinder performance. We will therefore discuss deadlock prevention and deadlock avoidance approaches that relax synchronizations (and maximize performance) while controlling memory for communication.

Throughout this thesis, we will use a state-of-the-art asynchronous sparse direct solver to validate our algorithms. This allows us to illustrate performance gains with experiments on large real-life problems on modern computer architectures.

This work was granted access to the HPC resources of CALMIP under the allocation 2014-P0989 and to GENCI resources under allocation x2014065063.

## Chapter 1

## Background

## 1.1 Introduction

In this chapter, we give an overview of the existing methods to solve linear systems of the form

$$Ax = b (1.1)$$

where A is a large sparse matrix of order n, and where x and b are vectors (or matrices) of size n (or  $n \times m$ ). Given the matrix A and the right-hand side b, the goal is to find the unknown x.

In this chapter, we give a short overview of existing methods to solve this problem and provide some background that will be useful for the remainder of the thesis. We will guide the reader through the successive steps, from the (possible) origin of the problem to its solution, based on an illustrative example from a typical physical application.

Illustrative example Let us suppose that a physicist needs to simulate a phenomenon, such as, for example, the thermodynamic evolution of a simple metal plate. The physical law governing the evolution of temperatures in this system is given by the heat equation, described by the following partial differential equation

$$\frac{\partial u}{\partial t} - \alpha \nabla^2 u = 0 \quad , \tag{1.2}$$

where  $u \equiv u(x, y, t)$  is the temperature at a given position in space and time, and  $\alpha$  is the thermal diffusivity of the plate. This equation comes along with additional initial and boundary conditions appropriate to the problem at hand.

In practice, exact analytical solutions u(x, y, t) that give the values of u at every point and any time are simply out of reach. Instead, we usually try to find approximate solutions restricted to a discrete subset of points and at discrete time intervals. The widely used methods to find such approximate solutions are the finite-difference method (FDM) and the finite-element method (FEM). The main steps of these approaches are the following.

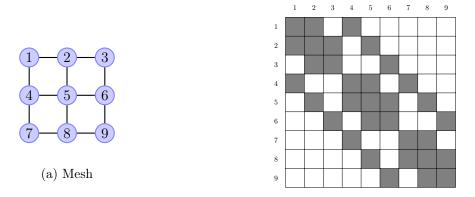

The first step consists in *discretizing* the system by choosing a relevant subset of points (or polygons forming a *mesh*) that will represent it. For the sake of simplicity, we will consider in our example a finite-difference discretization of the plate using only 9 points (See Figure 1.1a).

The second step then consists in applying the PDEs on the discretized mesh, taking into account the dependencies between neighbours. This step typically relies on an approximation of the derivative of a function f at a given point a in space or time, which can take the form:

$$f'(a) \approx \frac{f(a+h) - f(a)}{h}$$

,

where the discretization step h should be sufficiently small for the approximation to be accurate.

Considering that a - h, a, and a + h are part of the discretization, second order derivatives can also be approximated:

$$f''(a) \approx \frac{f(a+h) - 2f(a) + f(a-h)}{h^2}$$

(1.3)

(b) Sparse matrix. Nonzero (gray). Zero (white).

Figure 1.1: Discretization mesh and corresponding sparse matrix

The so-called explicit methods can then be applied to directly compute the approximate solution at any point and at any time  $t + \Delta t$ , given the state of its neighbours (and itself) at time t. However, due to stability issues, such methods tend to be inapplicable in practice. Indeed, the stability condition generally comes in the form  $\Delta t < h^2 * constant$ . Therefore, choosing a small space step h (to get a reasonably good spatial resolution) will require a prohibitively small time step  $\Delta t$ . The so-called implicit methods may be applied instead. They are not subject to any stability condition but require the solution of a linear system at each time step. They rely on a formulation of the equations yielding a linear system of equations, where the old state of the system is represented by the vector b, while the new state of the system, which is given by x, must be found through the solution of the linear system. As an example, let us consider the case of equation (1.2) applied to the point (numbered 5) at the middle of the mesh in Figure 1.1a. We note  $u_i(t)$  the approximate value of u at point i of the mesh at time t. Approximating the time derivative by  $\frac{u_5(t+\Delta t)-u_5(t)}{\Delta t}$ , and generalizing the second derivative approximation of equation (1.3) to the Laplacian of the heat equation in two dimensions, we obtain one of the equations of the aforementioned linear system:

$$u_5(t+\Delta t) - \frac{\alpha \Delta t}{h^2} (u_2(t+\Delta t) + u_4(t+\Delta t) - 4u_5(t+\Delta t) + u_6(t+\Delta t) + u_8(t+\Delta t)) = u_5(t) .$$

After forming the linear system, the next step is the one that concerns us, i.e. finding x (in Equation (1.1)). The key point to notice here is that the matrix A generated by an implicit method is usually **sparse**, i.e. with many **zero** entries (See Figure 1.1b).

Indeed, as each row or column of the matrix represents a link between the corresponding vertex in the mesh and a neighbour, and as the number of neighbour vertices of each vertex is usually limited, the number of nonzero entries (denoted by NNZ) of the matrix is usually O(n). This sparsity of the matrix makes the exploitation of the zero entries worthwhile for reducing computations and resources, as will be shown in Section 1.3.

## 1.2 Solution methods

The mathematical solution of the problem defined by equation (1.1) is simply

$$x = A^{-1}b$$

(1.4)

However, using  $A^{-1}$  explicitly is computationally tough and often numerically unstable. There are two main families of approaches for the solution of linear systems: **direct methods** and **iterative methods**.

#### 1.2.1 Direct methods

In general, it is hard to find the solution of a system immediately. However, methods do exist for matrices with special characteristics.

For example, when the matrix is diagonal  $(A \equiv D)$ , the solution is simply given by

$$x_i = \frac{b_i}{D_{ii}} {.} {(1.5)}$$

Moreover, when the matrix is orthogonal  $(A \equiv Q)$ , as the inverse of an orthogonal matrix coincides with its transpose, the solution is given by

$$x = Q^T b (1.6)$$

Furthermore, when the matrix is triangular, say lower triangular,  $(A \equiv L)$ , the solution is obtained by successively computing each  $x_i$  as:

$$x_i = \frac{b_i - \sum_{j=1}^{i-1} L_{i,j} x_j}{L_{i,i}}, \ i = 1, \dots, n \ . \tag{1.7}$$

The idea behind direct methods is to **decompose** or **factorize** the (general) matrix A into a product of (special) matrices, for which it is easier to find a solution

$$A = A_1 \times A_2 \times \dots \times A_k \quad . \tag{1.8}$$

The solution of the system is then obtained by solving each subsystem successively, using

$$\begin{cases} y_1 = A_1^{-1}b, \\ y_{i+1} = A_{i+1}^{-1}y_i, i = 1, \dots, k-1, \\ x = y_k. \end{cases}$$

(1.9)

Various direct methods exist, with various computational costs and various advantages. For general square unsymmetric matrices, the LU decomposition may be used. It consists in factorizing A as

$$A = LU (1.10)$$

where L is a lower triangular matrix with 1's on the diagonal and U is an upper triangular matrix. The solution x of the system is then obtained by applying successively two triangular solution schemes: a **forward elimination** on L followed by a **backward substitution** on U.

A possible implementation of the LU decomposition is depicted in Algorithm 1.1, where the matrix A is overwritten by its factors L and U.

**Algorithm 1.1:** LU decomposition algorithm (algorithm of Doolittle). A is overwritten by its LU factors such that the upper triangular part of A (including the diagonal) is the U factor, and the strictly lower triangular part of A is that of the L factor (as the diagonal of L is composed of 1's and is not stored).

Some variants exist that can help increase the performance in the case where the matrix A exhibits some special properties. For example, the  $LDL^T$  decomposition can be applied on symmetric matrices. Moreover, the  $LL^T$  decomposition, also known as the **Cholesky** decomposition, can be applied on a symmetric positive definite matrix. In addition, other very important methods exist, which can be applied to the general case, such as the QR and the SVD decompositions.

In this thesis, we will focus on the LU decomposition, although most algorithms and ideas can also be applied to  $LDL^T$  and  $LL^T$  decompositions.

#### 1.2.2 Iterative methods

The main principle of an iterative method is to generate a sequence of iterates  $x^{(k)}$ , which converge to the solution of the linear system Ax = b. These essentially involve matrix-vector products, but are often combined with preconditioning techniques, where one considers the linear system (MA)x = Mb where MA has better convergence properties than A (ideally  $M = A^{-1}$ ) and where the systems My = z are easier to solve than Ax = b.

Basic iterative methods (stationary methods) compute the next iterate  $x^{(k+1)}$  as a function of  $x^{(k)}$  only (Jacobi method) or as a function of  $x^{(k)}$  and the already updated elements of  $x^{(k+1)}$  (Gauss-Seidel method). More advanced methods like Krylov methods (e.g., Conjugate gradients, GMRES) build a subspace of increasing size at each iteration, in which the next iterate is found. It must be noted that iterative methods can be combined with direct methods, either to build a preconditioner (e.g. incomplete LU factorizations), or to design hybrid methods (like block Cimmino [23] or domain decomposition methods where a direct solver is used within each domain [55]).

Therefore any progress in sparse direct methods will also impact those hybrid direct-iterative methods that, depending on the problem properties and size, can be well adapted (e.g. relatively well conditioned three-dimensional problems of very large sizes).

## 1.3 Sparse direct methods

When dealing with sparse matrices, Algorithm 1.1 performs many operations on zeros, which can be avoided to limit the amount of work compared to a dense factorization.

Although they differ in some aspects, direct methods, when applied to sparse matrices (sparse direct methods), usually rely on the same three main steps to find the solution of a linear system of equations. The first step, the **analysis phase**, consists in analysing the large sparse matrix A and in defining a graph representing the dependencies between computations on smaller dense blocks. The purpose is: (i) to estimate and limit the amount of computations and resources required for the factorization; and (ii) to apply a pre-processing to the matrix in order to improve

its numerical characteristics. The second step, the **factorization phase**, consists in decomposing the matrix into its factors. This is done by applying the corresponding computations to the graph that was produced in the first step. The third step, the **solve phase**, consists in applying the forward elimination and backward substitution to get the solution vector x of the linear system.

In the following sections, we will detail the first two steps, which are the most relevant for our work. For the sake of clarity, we illustrate our explanations by running on the example in Figure 1.1b.

## 1.3.1 Analysis phase: Sparse matrices and graphs

During the analysis phase, the original sparse matrix is analysed in order to prepare the factorization. Permutations are sought to limit the work during the factorization.

## 1.3.1.1 Adjacency graph

The structure of any sparse matrix A may be represented by its associated **adjacency graph**  $\mathcal{G}(A)$ .

**Definition 1.1** (Adjacency graph). The adjacency graph of a matrix A is a graph  $\mathcal{G}(A) = (\mathcal{V}, \mathcal{E})$  such that:

- there are n vertices, each vertex  $v_i \in \mathcal{V}$  represents the variable i (row or column) of A,

- there is an edge  $\langle v_i, v_j \rangle \in \mathcal{E}$  iff  $a_{ij} \neq 0 \land i \neq j$ .

This formalism is the basis of all the further steps. When the matrices are symmetric, or just structurally symmetric, the associated graph can be considered to be undirected, while it must be directed in the case of matrices with an unsymmetric structure. In this section, we only consider the structurally symmetric case and thus undirected graphs.

In our example, the adjacency graph of the matrix in Figure 1.1b simply corresponds to the mesh we presented in Figure 1.1a, with edges between i and j when  $a_{ij}$  is nonzero.

### 1.3.1.2 Symbolic factorization: filled graph

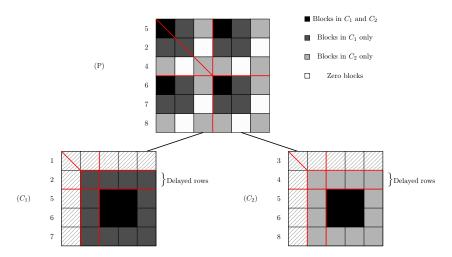

When applying an LU decomposition to a matrix A with a symmetric structure, by applying a succession of pivot eliminations, the sparsity pattern of A changes, together with  $\mathcal{G}(A)$ . Indeed, when eliminating a pivot in Algorithm 1.1, the right-looking update of the trailing matrix (A(p+1:n,p+1:n)) in the algorithm) changes some zeros from that submatrix into nonzeros, thus increasing the computational cost for the rest of the factorization. Indeed, eliminating a pivot p in A modifies entries  $a_{ij}$ , i,j>p, for which both  $a_{ip}$  and  $a_{pj}$  are nonzero. Performing this elimination on  $\mathcal{G}(A)$  creates a **clique**, i.e. a fully connected graph, between all its direct neighbours  $\{v \in \mathcal{V} | < v, v_p > \in \mathcal{E} \lor < v_p, v > \in \mathcal{E} \}$ . Considering that we must then factorize the trailing matrix A(p+1:n,p+1:n), we then remove  $v_p$  from  $\mathcal{V}$  and all its adjacent edges from  $\mathcal{G}(()A)$ . This creation of edges in  $\mathcal{G}(A)$  corresponds to the introduction of nonzeros in places previously occupied by zeros in A. This phenomenon is known as **fill-in**. After the LU decomposition is completed, we define the result of the successive transformations on the adjacency graph  $\mathcal{G}(A)$  of A as the **filled graph** of A, i.e, the adjacency graph  $\mathcal{G}(F)$  of F = L + U, the **filled matrix** of A.

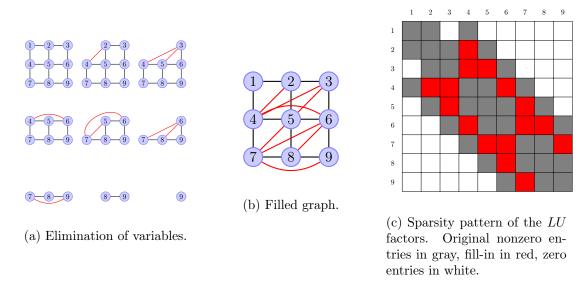

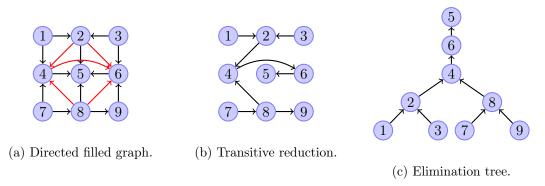

Figure 1.2 illustrates these concepts on our example. The fill-in is represented in (dark) red in all subfigures. Figure 1.2a illustrates the successive graph transformations induced by each step of pivot eliminations on A. Figure 1.2b represents the resulting filled graph. Finally, Figure 1.2c

shows the sparsity pattern of the resulting L and U matrices given the original pattern of A. Taking the example of pivot 1, the update operation in Algorithm 1.1 is  $A(2:9,2:9) = A(2:9,2:9) - A(2:9,1) \times A(1,2:9)$  which, considering that there are only a few zeros in column 1 and row 1, modifies entries  $a_{2,2}$ ,  $a_{2,4}$ ,  $a_{4,2}$ ,  $a_{4,4}$ . Because  $a_{2,4}$  and  $a_{4,2}$  were originally zero, fill-in occurs, which corresponds to an edge between vertices 2 and 4 in the graph.

Figure 1.2: Construction of the filled-graph (fill-in in red).

#### 1.3.1.3 Reordering and permutations

Unfortunately, the increase in the number of nonzeros, due to the fill-in phenomenon, increases the amount of computations and resources. Fortunately, **reordering** (or **permuting**) the rows and columns of the matrix may greatly reduce the fill-in.

The mathematical meaning of permuting the rows and columns of a matrix A corresponds to multiplying it on the left and on the right by permutation matrices, i.e. square binary matrices that have exactly one entry 1 in each row and each column, and '0's elsewhere. This results in the modified matrix

$$A' = PAQ , \qquad (1.11)$$

where P permutes the rows of the matrix, and Q permutes the columns. As we are considering matrices with a symmetric structure, we impose  $Q = P^T$  in order to maintain symmetry, which amounts to renumbering the variables of the matrix. The problem of finding an optimum permutation matrix P (or an ordering of the variables) that minimizes the fill-in (or the amount of computations) is NP-complete [114]. There are, however, two main classes of ordering heuristics, which apply to the case of symmetric matrices.

- Bottom-up approaches rely on local criteria to decide, at each iteration, which variable to eliminate. Several algorithms exist that consist in eliminating, at each iteration, the variable in the graph which has the lowest degree of connectivity or which induces the minimum fill. Among these algorithms, the most common are:

- The Minimum Degree algorithm (MD) with its variants

- \* Approximate Minimum Degree [10] (AMD)

- \* Multiple Minimum Degree [83] (MMD)

- The Minimum Fill algorithm (MF) with its variants

- \* Approximate Minimum Fill [4, 90] (AMF)

- \* Multiple Minimum Fill [97] (MMF)

- \* A recent MF implementation by [89]

- **Top-down** approaches are based on **global** considerations. They recursively partition the graph associated with the matrix, isolating the variables of the partitions at each level of recursion. *Nested-Dissection* techniques [53, 54] belong to this class of heuristics.

- In practice, partitioning libraries such as PORD [102], METIS [73] and SCOTCH [32, 93] implement hybrid schemes. Top-down approaches are first used to obtain partitions of a certain granularity, on which bottom-up approaches are then applied to finish the work.

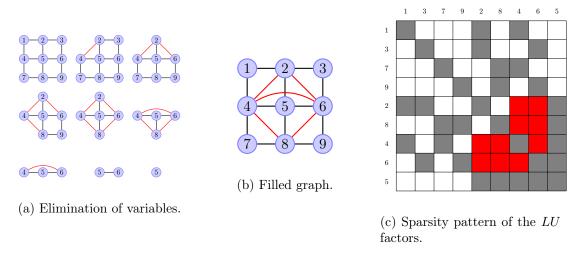

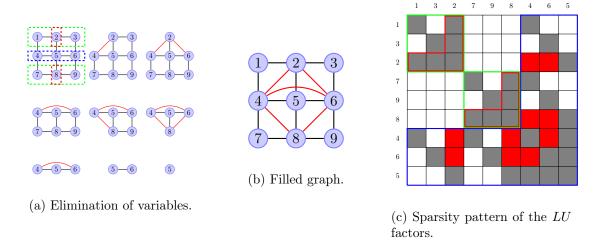

Figure 1.3: Minimum Degree ordering (fill-in in red).

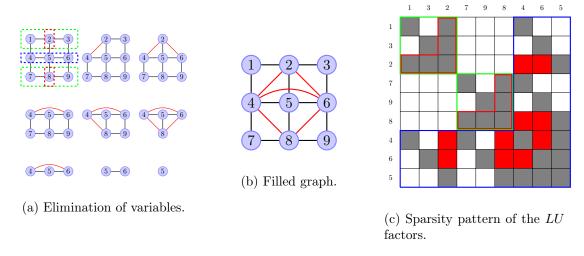

Figure 1.4: Nested-dissection ordering (fill-in in red).

In the case of our example, we illustrate the different steps and the effect of the application of the *Minimum Degree* and *Nested Dissection* algorithms in Figures 1.3 and 1.4, respectively.

At each step of the minimum degree algorithm, the vertex with smallest degree in the filled subgraph at the corresponding step is chosen, leading, in our example, to the elimination order 1-3-7-9-2-8-4-6-5 (ties are broken arbitrarily). Concerning nested dissection, we can see in Figure 1.4 the first level of dissection with the blue set of variables (4,5,6) separating the two green domains consisting of variables (1,2,3) and (7,8,9). By ordering the separator last, large zero blocks appear in the matrix at the intersection of the two domains, in which no fill-in will appear. This idea is applied recursively, leading (for example) to the elimination order 1-3-2-7-9-8-4-6-5.

#### 1.3.1.4 Dependencies between variables and elimination tree

As we have seen, the elimination of a pivot during an LU decomposition generally impacts the remaining non-eliminated variables and the structure of the submatrix that is not yet factored. However, when the matrix is sparse, the pivot variable y may be **independent** from another variable z. y will then have no impact on z. This is then a source of parallelism: y and z could then be processed independently. More formally, we rely on the following definitions.

**Definition 1.2** (Direct dependency). Given two variables y and z such that y is eliminated before z, we say that z directly depends on y ( $y \rightarrow z$ ) iff  $l_{zy} \neq 0$  (or  $u_{yz} \neq 0$ , since we consider matrices with a symmetric structure). Equivalently,  $y \rightarrow z$  iff there is an edge between y and z in the filled graph of A, or if column y has a direct impact on column z.

**Definition 1.3** (Filled directed graph). We define the filled directed graph  $\lceil \mathcal{G}(F) \rceil$  of a matrix A as the filled graph of A in which undirected edges between a pair of nodes y and z have been replaced by directed edges that respect the elimination order  $(y \to z)$  if y is eliminated before z).

We show in Figure 1.5a the directed filled graph  $\lceil \mathcal{G}(F) \rceil$  for our example, in the case of nested dissection. It is the same graph as the undirected filled graph  $\mathcal{G}(F)$  of Figure 1.4b except that edges are now oriented in a way compatible with the ordering.

**Definition 1.4** (Independent variables). Two variables y and z are independent iff there is no edge between y and z in the transitive closure of the filled directed graph  $\lceil \mathcal{G}(F) \rceil$  of A. Said differently, there is no path between y and z in  $\lceil \mathcal{G}(F) \rceil$ .

The independence between variables is a key characteristic upon which sparse direct methods rely. It may be exploited to express the potential **parallelism** of the computations.

Although the dependencies may be observed in  $\lceil \mathcal{G}(F) \rceil$ , it is difficult to visualize them there, as it contains many paths. We may then build the **transitive reduction** of the filled graph of A, which exhibits the dependencies in the most compact way. It is a minimum edge graph that has the same reachability relation (or transitive closure) as  $\lceil \mathcal{G}(F) \rceil$ .

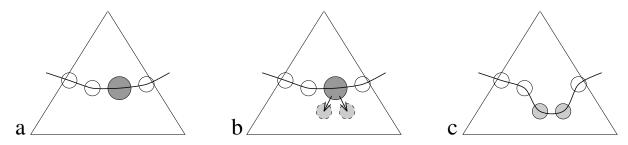

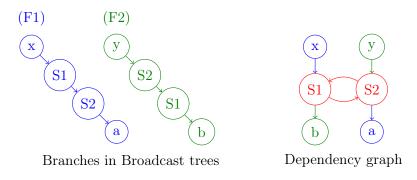

As the dependencies always follow the order defined by the ordering, there are no cycles in  $\lceil \mathcal{G}(F) \rceil$ . It is thus a **directed acyclic graph** (**DAG**). In this case, its transitive reduction is unique. Furthermore, when the matrix A is structurally symmetric, the DAG is actually a tree, known as the **elimination tree**. We refer the reader to [87] for detailed information on elimination trees in a more general context. This elimination tree is a key structure on which sparse direct methods rely, as it denotes not only the order of the computations, but also reveals the possible parallelism to be exploited. Indeed, any computation occurring on separate branches of the tree could be executed in parallel. This kind of parallelism is called **tree parallelism**.

Figure 1.5b shows the transitive reduction of the filled-graph from Figure 1.5a (resulting from a nested-dissection ordering). Figure 1.5c then shows the elimination tree representation of the transitive reduction of our example.

Figure 1.5: Transitive reduction and Elimination tree based on Nested-dissection ordering

## 1.3.1.5 Supernodes

In dense linear algebra, the operations related to pivot elimination and the update of the remaining variables are not performed on single pivots, but rather on sets of pivots, for performance issues. This allows for the use of very efficient BLAS routines to accomplish such operations. On sparse matrices, we could then use the same approach by grouping the variables with the same (or similar [19]) sparsity structures. The resulting sets of variables are called **supernodes**. In our example, we can group for instance variables 4, 5 and 6 into a single supervariable or supernode, leading to an amalgamated tree, sometimes called an assembly tree. An example of an assembly tree, where variables 4, 5, and 6 have been amalgamated to form a supernode, is given in Figure 1.6, which we will further discuss in the description of the multifrontal method. The LU factorization can then be generalized to work on supernodes instead of single variables. This allows the use of dense linear algebra kernels on matrices with higher dimension, leading to higher performance. One then talks of supernodal methods. One thing to notice is that the nodes and supernodes in Figure 1.5c are the separator variables in the nested-dissection ordering of Figure 1.4. At the first level of dissection, the blue set of variables dissecting the two green sets of variables represent the set of variables at the root of the tree. Then, each green subset is recursively dissected by the red set of variables, which in turn represents the child supernodes of the root of the tree.

Because large amounts of computations are done at each supernode, parallelism can in that case also be exploited within the nodes of the tree. The resulting type of parallelism is called **node parallelism**.

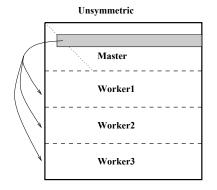

#### 1.3.1.6 Symmetric and unsymmetric matrices

All the results considered so far concern (structurally) symmetric matrices. The same approach may be adapted to the case of unsymmetric matrices. The elimination tree described above will be in this case a DAG. Among the many ways of handling such matrices, one of them consists in working on the symmetrized structure of the matrix (i.e.  $A^T + A$ ) and applying the above techniques on it. In the remainder of this thesis, even though we consider the unsymmetric LU decomposition, we will always consider the symmetric or symmetrized structure of the matrix  $(A^T + A)$ .

## 1.3.2 Factorization phase: left-looking, right-looking and supernodal approaches

We discuss in this section the factorization phase, and how the numerical factorization can be performed on sparse matrices. We delay to Section 1.3.3 the discussion of the multifrontal method, a particular sparse direct method on which we will focus in this thesis.

We consider here two main types of operations occurring during LU decompositions, known as FACTO and UPDATE (using the notations of [40]):

- The Facto(i) operation applied on column i divides by  $a_{ii}$  the under-diagonal part of i.

- The UPDATE(i,j) operation uses column  $A_i$  to update column  $A_j$ .

Considering that A is overwritten by the factors (L and U) so that eventually, A = L + U - I, we have more formally the following definitions:

```

• Facto(A_j): A_j(j+1:n) \leftarrow A_j(j+1:n)/a_{jj};

```

```

• UPDATE(A_i, A_j): A_j(i+1:n) \leftarrow A_j(i+1:n) - a_{ij}.A_i(i+1:n).

```

Algorithm 1.1 can be formulated using these notations, leading to Algorithm 1.2.

```

for i = 1 to n do

FACTO(A_i);

for j = i to n do

UPDATE(A_i, A_j);

```

**Algorithm 1.2:** Dense right-looking factorization algorithm.

There are n Facto operations during the whole factorization, where n is the order of the matrix. In the case of sparse matrices, the elimination tree represents a **partial order** or **topological order** on these operations and some of the UPDATE $(A_i, A_j)$  operations can be skipped when i and j are independent. Indeed, a node in the elimination tree must be processed after all its children. Formally, if j is an ancestor of i in the tree, then, Facto $(A_j)$  has to be performed after Facto $(A_i)$ .

In spite of these dependency constraints, the structure of the elimination tree still provides some freedom to schedule the Facto operations, and once this scheduling is fixed, there still remain some more flexibility to schedule the UPDATE operations. Among all the possible schedules, there are two main families of approaches: the so-called left-looking and right-looking methods. On the one hand, left-looking algorithms delay the UPDATE operations as late as possible: all the UPDATE(\*, $A_j$ ) are performed just before Facto( $A_j$ ), looking to the left to nonzero entries in row j. On the other hand, right-looking algorithms perform the UPDATE operations as soon as possible: all the UPDATE( $A_i$ ,\*) operations are performed immediately after Facto( $A_i$ ), looking right to all columns that need to be updated.

```

for j = 1 to n do

foreach i such that i \to j (see Definition 1.2) do

UPDATE(A_i, A_j);

FACTO(A_j);

```

**Algorithm 1.3:** General left-looking factorization algorithm.

Algorithms 1.3 and 1.4 illustrate the left-looking and the right-looking factorizations, respectively.

The **supernodal method** refers to either the sparse left-looking or right-looking methods explained above, when generalized to supernodes instead of single variables. Supernodal methods are used in several well-known sparse direct solvers, for example the sequential version of **SuperLU**, which implements a left-looking approach [38].

```

for i = 1 to n do

FACTO(A_i);

foreach j such that i \to j (see Definition 1.2) do

UPDATE(A_i, A_j);

```

**Algorithm 1.4:** General right-looking factorization algorithm.

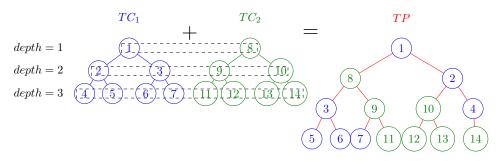

#### 1.3.3 Multifrontal method

The **multifrontal method** [45, 46, 87, 101] has been introduced in the 80's and fully exploits the elimination tree [86] in the sense that the task dependency and the communication scheme of a multifrontal scheme is fully described by the node dependency of the elimination tree. It is quite different in this respect from the right-looking and left-looking approaches described in the previous section. It should be noticed that the "good" properties of memory locality of the multifrontal approach have been used over the years to efficiently address vector- and RISC-based shared memory computers as well as distributed memory computers.

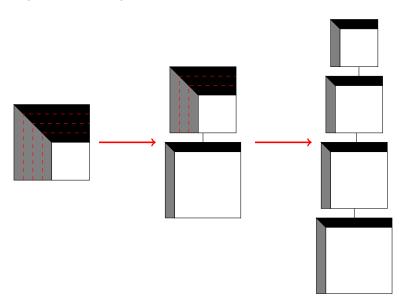

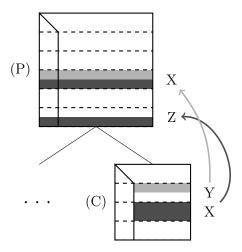

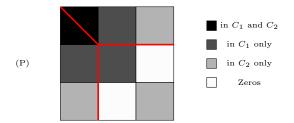

In a nutshell, the order of the FACTO operations is thus defined by the elimination tree, as in the previously described methods. However, the UPDATE operations are not performed directly from the factorized columns to the updated ones anymore. Instead, the result of the update (a.k.a. contribution) of a variable i to a variable j (with  $i \rightarrow j$ ) is carried throughout the path from i to j in the elimination tree (or assembly tree). The idea is to build a **contribution block** (or **Schur complement**) associated to each (super)node, as a condensed representation of all the contributions from the pivots in the current subtree to the ancestors depending on them in the elimination tree. This is possible because, at each step of the processing of a node, we build a dense matrix, so-called frontal matrix, capable of storing all contributions from the children in the elimination tree. In terms of data dependency, processing a node of the elimination tree will thus only depend on the processing of its children.

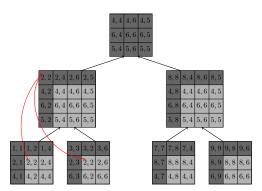

Figure 1.6: Assembly tree based on the Nested-dissection ordering. Each node of the tree is a front. The dark gray part of each front represents the fully-summed rows and columns of that front, and each light gray part represents the contribution block of that front. Curved arrows illustrate the assembly of an element in a parent front from the contribution blocks of its children fronts.

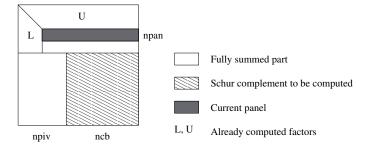

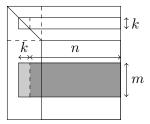

The data structure that we use at each node of the tree is thus a dense matrix <sup>1</sup> we call **frontal matrix**, or simply, **front**. It comprises two parts. First, we have the so-called **fully-summed** rows and columns, which correspond to the supernode variables that must be factorized. Once

<sup>&</sup>lt;sup>1</sup>Usually square, in case of (structurally) symmetric matrices, and rectangular in case of unsymmetric matrices, or in other multifrontal methods, like in sparse QR decompositions.

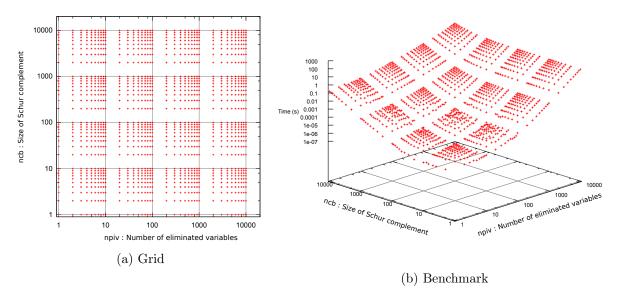

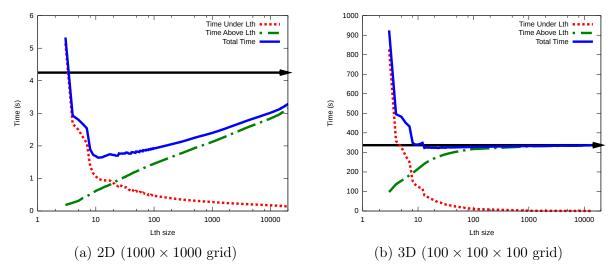

factorized, this part is referred to as **factors**. Second, we have the contribution block of the supernode, which is the remaining square part (see Figure 1.6), and which corresponds to the Schur complement resulting from the factorization of the fully-summed rows and columns. We will denote by nfront the order (size) of a front, by npiv the number of pivots eliminated at this front, and by ncb the size of its contribution block. We thus have the relation nfront = npiv + ncb. Figure 1.6 illustrates the association of the frontal matrices with the nodes of the elimination tree on a symmetrized matrix. For unsymmetric multifrontal factorizations, we refer the reader to [17, 37, 48].

The multifrontal factorization then consists in traversing the tree while applying a series of tasks on each front. First, we allocate the front in memory and initialize all its entries to zero. Second, we assemble it by applying an extend-add operation (i.e. addition) of the entries from the contribution blocks of the children fronts together with the values of the elements of the current front in the original sparse matrix A. Third, we apply a **partial** LU decomposition to the front, i.e. only the fully-summed part is factorized, the contribution block only being updated with the factorized part. A full factorization is performed on the root of the tree as there is no contribution block there. Finally, in multifrontal implementations, we stack the front's contribution block, i.e. we compress it in memory to free up some of it for reuse in future computations. The process of accessing to contribution blocks using a stack mechanism depends on the fact that nodes of the tree are processed following a post-order (recursively traversing children subtrees from left-most to right-most before travesing the root). We remark that the amount of memory dedicated to contribution blocks depends on the order in which the tree is processed. In practice, a postorder defined by Liu [84], or a more general topological order [71, 85] is followed, aiming at reducing memory consumption. After stacking the contribution block, factor entries are generally also made contiguous in memory to save space, or can be written to disk in the case of so called **out-of-core** solvers [1, 103].

Early implementations of parallel multifrontal methods are discussed by Duff [43, 44]. We will further discuss in Chapters A and C some mechanisms and implementations in shared-memory and distributed-memory environments, respectively. This will be explained in the context of MUMPS [13, 15], the multifrontal solver that we use.

We end this section by making a remark on numerical pivoting, which has not been discussed yet. Numerical pivoting is essential to ensure a stable LU factorization. In sparse linear algebra, threshold partial pivoting is generally used, in which a pivot is accepted if it is larger than a threshold u multiplied by the largest entry in the column, with  $0 \le u \le 1$  (u = 1 for partial pivoting). Finding acceptable pivots requires permutation of the rows/columns of the matrix, leading to dynamic tasks graphs. In the case of the multifrontal method, numerical stability may prevent a fully summed pivot from beeing eliminated. In that case, the pivot is delayed to the parent front where it will be eliminated if it is stable with respect to the threshold pivoting criterion. A pivot may be delayed several times (to an ancestor), until it becomes stable thanks to the assemblies from other siblings. In the worst case, the pivot may be delayed until the root, where it can always be chosen. In practice, the tree structure in the multifrontal method is maintained, but the size of the fronts increases, in an unpredictable way.

## 1.4 Parallelism on shared- and distributed-memory architectures

When desining sparse solvers, much attention has been paid to shared-memory and distributed-memory architectures.

Multithreaded sparse direct solvers aimed at addressing multicore environments have been the object of much work [7, 21, 28, 36, 39, 49, 61, 67, 70, 81, 100]. These solvers tend to use serial,

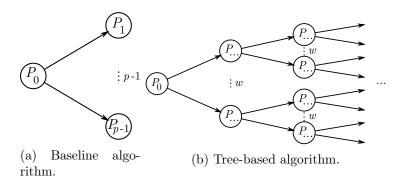

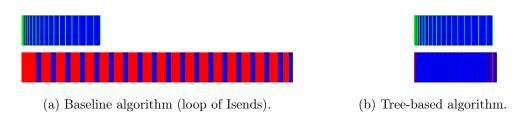

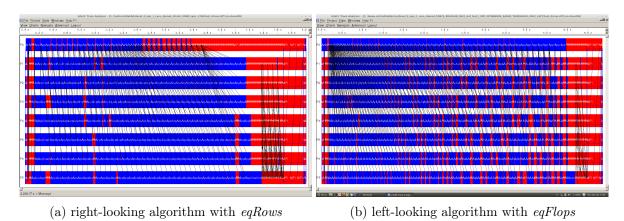

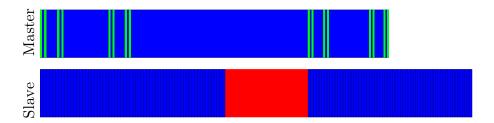

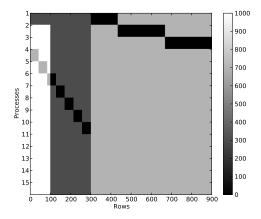

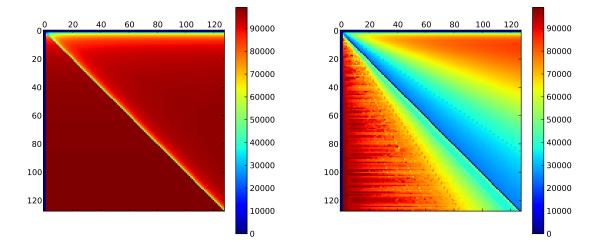

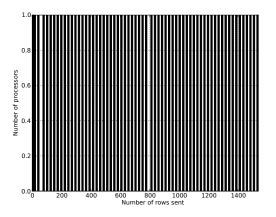

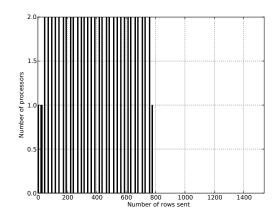

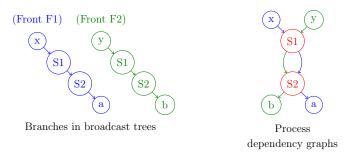

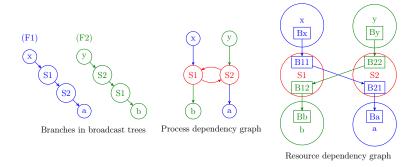

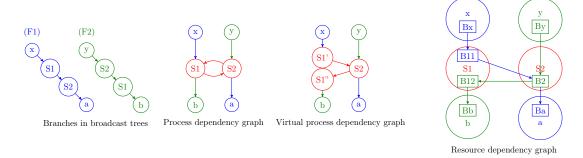

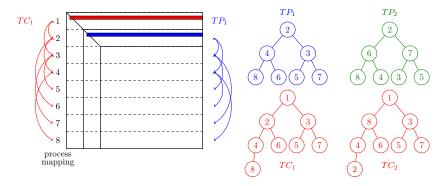

rather than multithreaded, BLAS (Basic Linear Algebra Subprograms [78]) libraries as building blocks, applied to dense matrices whose size is sometimes too small to make multithreaded BLAS efficient. Those solvers manage all the parallelism themselves, through the use of multithreading technologies like Cilk [24] and OPENMP [31]. We will focus on OPENMP, as it is a widely used standard.