#### **Purdue University**

### Purdue e-Pubs

Department of Computer Science Technical Reports

Department of Computer Science

1992

# Remote Memory Backing Storage for Distributed Virtual Memory Operating Systems (Thesis)

James Griffoen

Report Number: 92-052

Griffoen, James, "Remote Memory Backing Storage for Distributed Virtual Memory Operating Systems (Thesis)" (1992). *Department of Computer Science Technical Reports.* Paper 973. https://docs.lib.purdue.edu/cstech/973

This document has been made available through Purdue e-Pubs, a service of the Purdue University Libraries. Please contact epubs@purdue.edu for additional information.

#### REMOTE MEMORY BACKING STORAGE FOR DISTRIBUTED VIRTUAL MEMORY OPERATING SYSTEMS

James Griffioen

CSD-TR-92-052 August 1991

а

# Remote Memory Backing Storage for Distributed Virtual Memory Operating Systems \*

James Griffioen

Department of Computer Science Purdue University West Lafayette, IN 47906 email: jng@cs.purdue.edu

#### Abstract

The virtual memory abstraction aids in the design and implementation of portable applications. Virtual memory allows applications to execute in an arbitrarily large memory space, independent from the physical memory size of the underlying machine.

Conventional virtual memory operating systems use magnetic disks for backing storage. Magnetic disks provide high data transfer rates, large storage capacity, and the ability to randomly access data, making them an appealing backing storage medium. However, the average seek time of a magnetic disk is several orders of magnitude slower than memory access times. Recent advances in CPU speeds, network bandwidth, and memory sizes have made new types of backing storage with improved performance and greater functionality feasible.

This thesis investigates a new model for virtual memory in which dedicated, large-memory machines provide backing storage to virtual memory systems executing on a set of client machines in a distributed environment. Dedicated *memory servers* provide clients with a large, shared memory resource. Each memory server machine is capable of supporting heterogeneous client machines executing a wide variety of operating systems. Clients that exceed the capacity of their local memory access remote memory servers across a high-speed network to obtain additional storage space. Clients use a highly efficient, special

<sup>&</sup>quot;This paper was originally published as: James Griffioen, Remote Memory Backing Storage for Distributed Virtual Memory Operating Systems, PhD thesis, Department of Computer Science, Purdue University, West Lafayette, IN, August 1991. This technical report was created in response to a sudden (and somewhat delayed) barrage of requests for the original thesis. Please use the original thesis citation when citing this work.

purpose, reliable, data streaming, network architecture independent communication protocol to transfer data to and from the memory server. To reduce the delay associated with accessing remote memory, memory servers use efficient algorithms and data structures to retrieve data, on average, in constant time. In addition to providing a highly-efficient backing store, the model allows data sharing between clients and improves file system performance by offloading the file server.

This thesis also describes the design and implementation of a prototype system. Measurements obtained from the prototype implementation clearly demonstrate the viability of systems based on the model. The prototype shows that remote memory systems offer performance competitive with, and in some cases better than, existing virtual memory systems. Moreover, rapid advances in network bandwidth, CPU speeds, and memory sizes make the model an attractive basis for the design of future distributed systems.

-----

į.

÷

## TABLE OF CONTENTS

| LIST OF                    | TABLES                                                                                                                                                                                                                                      | ix ,                                          |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| LIST OF                    | FIGURES                                                                                                                                                                                                                                     | x                                             |

| TRADE                      | MARKS                                                                                                                                                                                                                                       | xiii                                          |

| ABSTR                      | ACT                                                                                                                                                                                                                                         | xiv                                           |

| 1. INT                     | RODUCTION                                                                                                                                                                                                                                   | 1                                             |

| 1.1<br>1.2<br>1.3<br>1.4   | Virtual Memory Operating Systems1.1.1Segments and Pages1.1.2Memory Management Policies1.1.3Virtual Memory Techniques1.1.4Virtual Memory Hardware SupportConventional Backing StorageRemote Memory Backing StorageOrganization of the Thesis | 2<br>3<br>4<br>7<br>9<br>10<br>11<br>12<br>14 |

| 2. TE<br>2.1<br>2.2<br>2.3 | RMINOLOGY                                                                                                                                                                                                                                   | 14<br>15<br>18                                |

|                            | E REMOTE MEMORY MODEL                                                                                                                                                                                                                       | 20                                            |

| 3.1<br>3.2                 | The Model                                                                                                                                                                                                                                   | 21<br>25<br>26<br>31                          |

v

32324.1Design Goals Hierarchical Design 34 4.2Incorporating Virtual Memory into a Hierarchical Design . . . 36 4.2.136 4.2.240 4.2.342 The Hardware Layer 424.3.1The Architecture Interface Layer 44 4.3.246. 47 4.4.148 4.4.2Virtual Memory Management 504.5 Page Replacement 504.5.153 4.5.2544.5.3Related Work 554.6564.7Summary A HIGH-SPEED REMOTE MEMORY COMMUNICATION PROTOCOL 58 5. 59 5.1 Design Goals 60 5.1.160 5.1.2625.1.3Conceptual View Of The RMCP Protocol 63 5.265 5.3XPP Message Types ..... 66 5.3.169 5.3.2Message Sequencing 715.3.3745.3.476 5.3.5The NAFP Protocol 80 5.4Fragmentation and Reassembly 80 5.4.1 83 5.4.284 5.4.387 5.4.4Related Work 87 5.590 5.6

4.

Page

A REMOTE MEMORY BACKING STORE 91 6. . . . . . . . . . . . . . . . . 91 6.1Design Goals 6.2 A Logical Memory Server 94 98 6.3 99 6.3.16.3.2Physical Memory Management 1026.3.3103 1046.3.4Enhancing Performance 6.4 109 6.5109 6.6 Summary 113A PROTOTYPE REMOTE MEMORY MODEL SYSTEM ..... 7. 1157.1 1157.2VM Xinu: The Client Operating System ..... 1177.2.1Overview 1177.2.21187.2.3Porting 1187.2.4 120 1207.37.41217.4.11227.4.21241257.51277.5.17.5.21297.5.3 1347.5.41387.6 Summary 141 8. 1438.1 Hierarchical Design 143 8.2 144 8.3 Remote Memory Service for Heterogeneous Machines . . . . . . . . 145 8.4 145146 8.5 Data Sharing 146 8.5.1 8.5.2 147 8.5.3 148 148 8.6

Page

|              |   | Ρ | age |

|--------------|---|---|-----|

| BIBLIOGRAPHY | - | • | 150 |

| VITA         | • |   | 158 |

•

.

### LIST OF TABLES

~ · ·

| Table | 9                                                                                                                                                                                               | Page |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 5.1   | XPP message types                                                                                                                                                                               | 68   |

| 7.1   | Average round trip delay to store or fetch an 8K byte page to or from a<br>Sun 3/50 NFS file server from a diskless Sun 3/50 client running SunOS.                                              | 127  |

| 7.2   | Average delay that results from storing or fetching an 8K byte page to or from a local disk drive on a Sun 3/50 executing SunOS                                                                 | 128  |

| 7.3   | Average round trip delay for VM Xinu paging to a memory server vs.<br>SunOS paging to NFS. Both systems used a Sun 3/50 client and a Sun<br>3/50 server.                                        | 129  |

| 7.4   | Average round trip delay for VM Xinu paging to a memory server vs.<br>SunOS paging to a local disk.                                                                                             | 130  |

| 7.5   | The time to store/fetch an 8K byte page when the memory server executes<br>on various UNIX systems. In each case, the clients consist of Sun 3/50<br>machines executing VM Xinu                 | 131  |

| 7.6   | Paging times from a DECstation 3100 executing VM Xinu. The time shown is the round trip delay to store/fetch a 4K byte page to or from a memory server executing on the specified architecture. | 133  |

| 7.7   | A breakdown of the time required to process an 8K byte request from a Sun 3/50 client paging to a Sun 3/50 memory server. The percentage is calculated from a total paging time of 31 ms.       | 139  |

| 7.8   | Sequence of requests observed at the memory server for various pending list lengths. The letter f denotes a fetch request and the letter s denotes a store request.                             | 141  |

~

### LIST OF FIGURES

## Figure

## Page

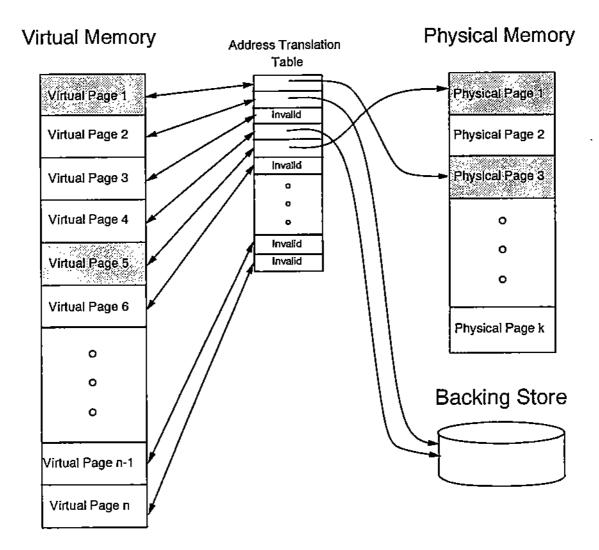

| 1.1 | Virtual to physical address translation. The operating system maintains<br>an address translation table for each virtual address space. The address<br>translation table contains exactly one entry for every virtual page and<br>specifies the true location of the data (i.e., physical memory or backing                                                                                           |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | storage)                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

| 2.1 | The OSI Reference Model                                                                                                                                                                                                                                                                                                                                                                               | 17 |

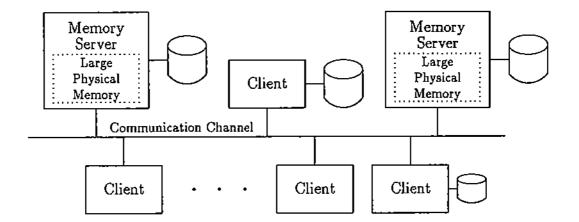

| 3.1 | An example remote memory model architecture                                                                                                                                                                                                                                                                                                                                                           | 22 |

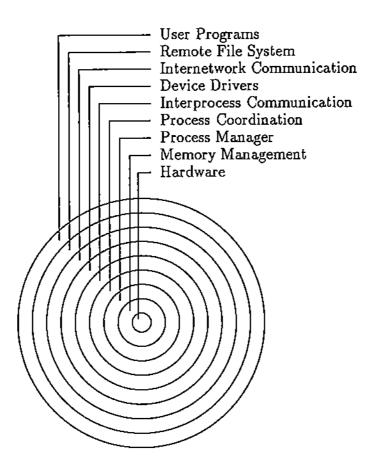

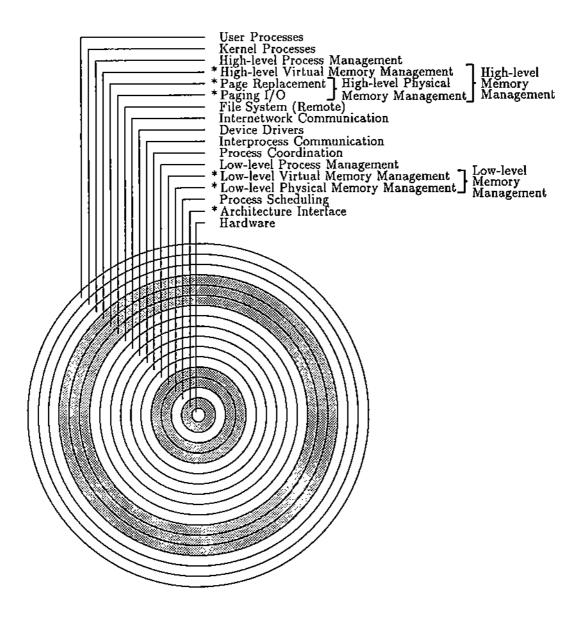

| 4.1 | The hierarchy of layers in the Xinu operating system                                                                                                                                                                                                                                                                                                                                                  | 37 |

| 4.2 | A layering model for a hierarchically-designed virtual memory operating system. The *'s identify the virtual memory system components of the hierarchy.                                                                                                                                                                                                                                               | 38 |

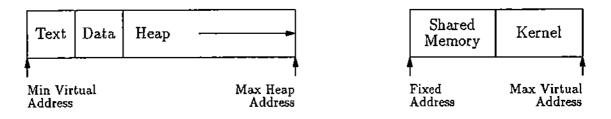

| 4.3 | The structure of an address space in VM Xinu                                                                                                                                                                                                                                                                                                                                                          | 48 |

| 4.4 | The location of thread specific data within an address space                                                                                                                                                                                                                                                                                                                                          | 49 |

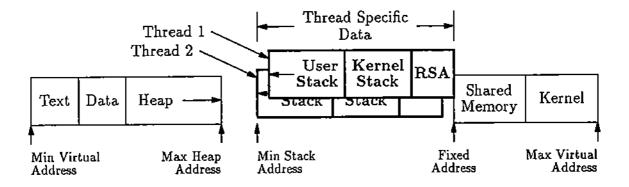

| 4.5 | The organization of the virtual memory system in VM Xinu                                                                                                                                                                                                                                                                                                                                              | 51 |

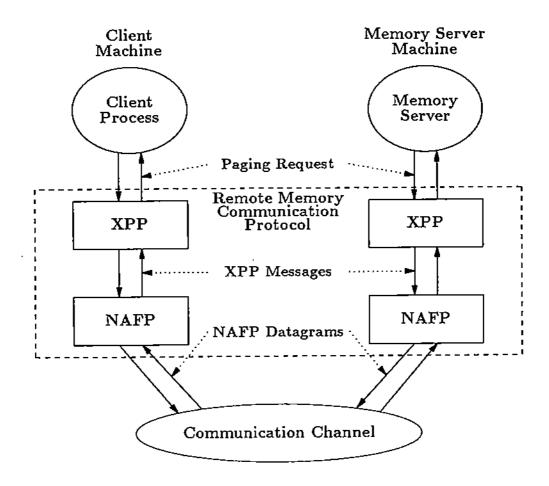

| 5.1 | The two layers of the remote memory communication protocol. A client<br>initiates an XPP request which travels down through the layers, across the<br>communication channel, and back up through the layers to the memory<br>server. The memory server processes the request and sends an XPP reply<br>back through the layers and across the communication channel to the<br>waiting client process. | 64 |

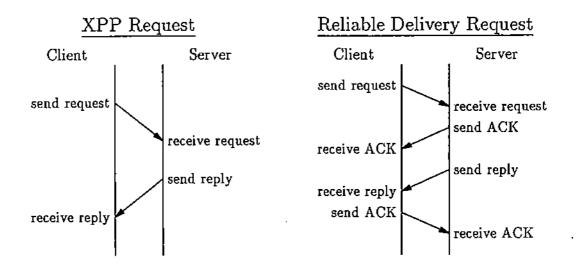

| 5.2 | Protocols that guarantee reliable delivery use 4 messages to process a request. XPP only uses 2 messages for most paging requests                                                                                                                                                                                                                                                                     | 70 |

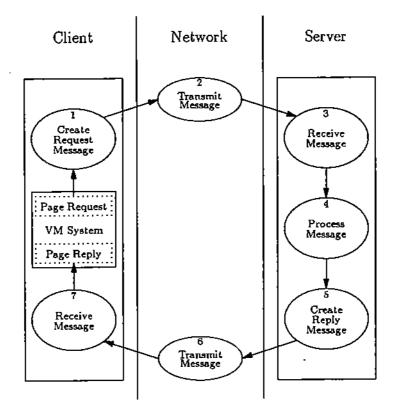

| 5.3 | The stages of an XPP message. The client machine processes stages 1<br>and 7, the communication channel stages 2 and 6, and the server stages<br>3, 4, and 5. All three execute concurrently.                                                                                                                                                                                                         | 75 |

-

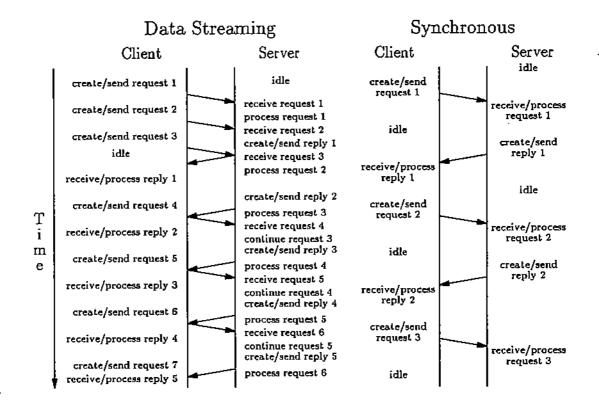

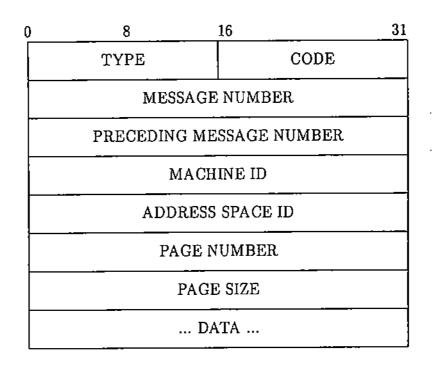

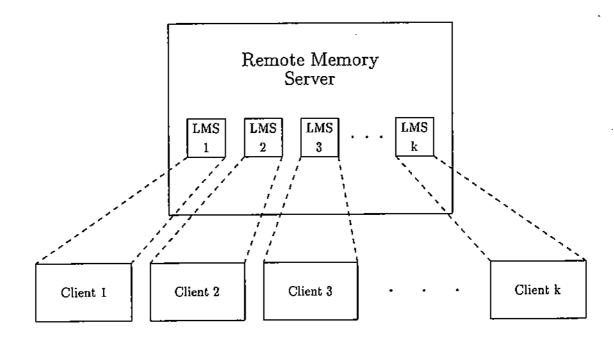

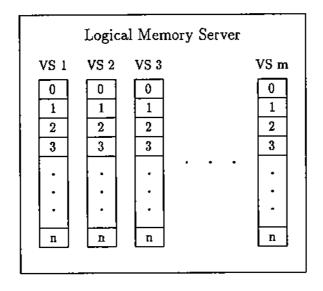

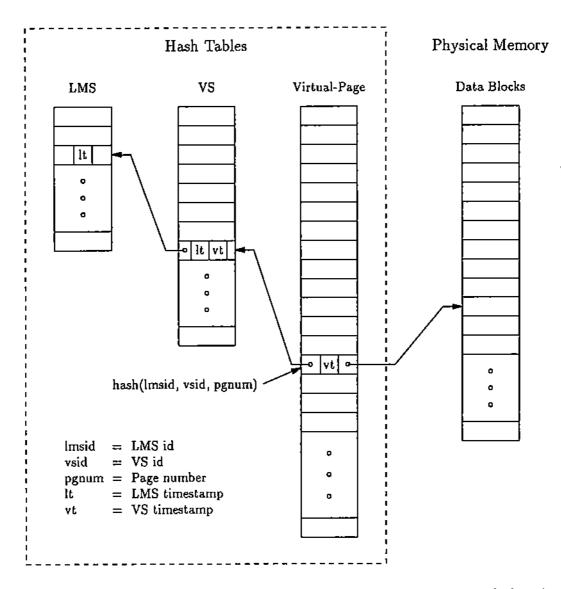

Page Figure Data streaming vs. synchronous sends. Data streaming with a pending 5.4list of length 3 keeps the system busy, while synchronous sends result in a substantial amount of idle time. In each case, time moves down the page and shows the messages transferred. 77 5.5The two components of an XPP message. 78 5.6The fields in an XPP message. The first 8 fields make up the XPP header, and the remainder of the message comprises the XPP data area. . . . . 79 The format of an NAFP packet. 5.785 The remote memory server provides each client with its own Logical Mem-6.1 ory Server (LMS) and regulates/protects the LMS from access by other clients. 95The organization of a Logical Memory Server. A Logical Memory Server 6.2organizes the memory space into Virtual Segments (VS), each subdivided into pages. 96 6.3 The three hash tables: LMS hash table, VS hash table, and the virtualpage hash table. Each virtual-page table entry contains the owner's timestamp and a pointer to the owner's VS table entry. Each VS table entry contains the current timestamp for the VS, an LMS timestamp, and a pointer to the owner's LMS table entry. 107 7.1 The Prototype System Configuration. 116 7.2The mapping from VM Xinu to an LMS. Xinu's virtual memory system defines the mapping from Xinu's process structure and address space layout to the memory layout of an LMS. 119 The memory server folding function. 1247.3 The double hashing algorithm for a fetch request. The algorithm assumes 7.4126 Average round trip delay to store or fetch an 8K byte page as a function 7.5 of the server load. The times indicate the average round trip delay experienced by Sun 3/50 client machines paging to a memory server executing on a SPARCstation 1+. Note that at 100 requests per second the server

Figure

Page

7.6

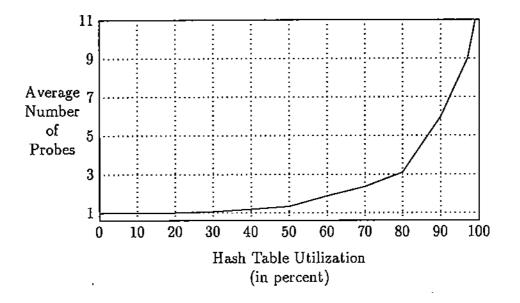

Measured performance of the double hashing algorithm as a function of the hash table utilization.

137

7.7

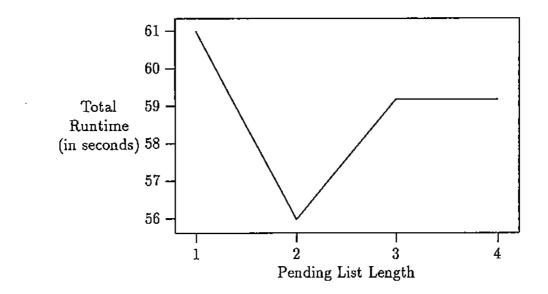

The total run time of the sequential access test program as a function of the pending list length.

140

.

#### TRADEMARKS

IBM is a registered trademark of International Business Machines Corporation.

RT PC, RISC System/6000, and AIX are trademarks of International Business Machines Corporation.

VAX, MicroVAX, VAXstation, DECstation, VMS, and Ultrix are trademarks of Digital Equipment Corporation.

Sun 3, SPARC, SPARCstation, SunOS, NFS, and NeWS are trademarks of Sun Microsystems, Inc.

Sequent Symmetry and Dynix are trademarks of Sequent Computer Systems.

UNIX is a registered trademark of AT&T.

Ethernet is a trademark of XEROX.

proNET and proNET-10 are trademarks of the Proteon Corporation.

The X Window System is a trademark of Massachusetts Institute of Technology.

#### 1. INTRODUCTION

Virtual memory operating systems have had a significant impact on the design and implementation of computer software. Computer hardware originally provided no support for virtual memory. Both the operating system and user programs executed in a single, unprotected, fixed size address space [Dij68, CMDD62, Org72, RT74]. As a result, programming was an art in which programmers spent large amounts of time and effort reducing the size of their programs to stay within the memory space constraints imposed by the hardware (e.g., see [Knu69, Den70]). Even the operating system conserved memory to maximize the amount of memory available for user programs [RT74, Com84].

Advances in computer technology over the past two decades have revolutionized computer programming and operating system design. Today, most conventional computer architectures, including personal computers, provide hardware support for virtual memory. The hardware assists the operating system in creating independent, protected, virtual address spaces, and provides support for detecting illegal memory accesses. The hardware allows the operating system to map portions of an address space to physical memory and other portions of the address space to backing storage. In the past, magnetic disks have served as the backing store of choice. However, recent technology advances in CPU speeds, network bandwidth, and memory sizes have made new types of backing store feasible.

This thesis proposes and investigates a new model for designing distributed systems in which dedicated, large memory machines provide high-speed backing storage to virtual memory systems executing on a set of distributed client machines. This chapter reviews the design of conventional virtual memory operating systems, discusses conventional backing storage, and introduces the concept of *remote memory backing storage*.

#### 1.1 Virtual Memory Operating Systems

Operating systems that provide support for virtual memory use the virtual memory support provided by the hardware to create large virtual address spaces in which user applications execute. A virtual address space is a logical address space, independent from the machine's physical memory space. The virtual memory abstraction allows programmers to design and implement applications that do not depend on the size of the physical memory of the underlying machine. Programmers are not constrained by a machine-dependent physical memory size because each application executes in an arbitrarily large virtual address space.<sup>1</sup> Virtual memory simplifies program design by allowing programmers to focus on problem solving instead of machine-dependent constraints. Virtual memory allows the size of a program to exceed the size of the physical memory. In addition, the virtual memory system can place each application in a separate address space, protected from all other applications. Protected address spaces eliminate elusive bugs that arise as a result of errors in programs that reference memory locations outside their region [Den70, Den80].

In a virtual memory, applications use virtual addresses to identify logical memory locations. Virtual addresses are not necessarily bound to physical memory addresses. Instead, virtual addresses are bound to physical addresses dynamically at run-time. A virtual memory operating system<sup>2</sup> creates the illusion of an arbitrarily large virtual address space by mapping a small portion of the virtual space to physical storage. The physical storage space consists of *main memory* and *backing storage*. Main memory

<sup>&</sup>lt;sup>1</sup>Although they are much less common, there exist a few systems that support small, fixed-size, virtual address spaces (e.g., smaller than the size of the physical memory); however, these systems exhibit the same protection/sharing properties as systems that support large virtual address spaces.

<sup>&</sup>lt;sup>2</sup>Throughout this thesis we will refer to operating systems that provide virtual memory support as virtual memory operating systems.

refers to the high-speed memory physically located on the machine.<sup>3</sup> Backing storage refers to some type of secondary storage media, typically having access times slower than those of main memory. The operating system maps certain regions of the virtual space to main memory and maps the remaining virtual regions to the backing store. When the user applications exhaust all available main memory, the operating system moves data from main memory to the backing store. Later, when the data is needed, the virtual memory system retrieves the data from the backing store.

#### 1.1.1 Segments and Pages

Virtual memory operating systems typically organize memory into segments or pages [Den70]. A segment is a variable size memory region consisting of a contiguous set of memory locations. The programmer or the operating system defines the segments that comprise an application. Each segment is defined by a (segment number, segment length) pair and has a set of protection values that permit or prohibit access to the data contained in the segment.

Segments mirror the typical organization of an application. An application usually contains several distinct regions, each having a particular purpose. For example, an application often contains one or more text regions (e.g., user code or shared libraries), one or more regions for data structures, and a stack region. In a segmented architecture, each of these regions corresponds to a segment. Multiple virtual address spaces may share a segment, and each segment has a set of protection values to prohibit unauthorized access. Because applications are often organized in a modular fashion, segments provide an attractive method for organizing the memory space.

Virtual addresses in a segmented system consist of a segment number and an offset within segment. The operating system typically uses an address translation table to map virtual addresses to physical memory locations. In a segmented system, the address translation table stores the base address of each segment (i.e., where the segment resides in physical memory) and the length of the segment. When translating

<sup>&</sup>lt;sup>3</sup>Main memory is also referred to as primary memory.

a virtual memory address to a physical memory address, the system extracts the segment number from the virtual address, locates the corresponding segment entry in the address translation table, verifies that the offset does not exceed the segment length, and adds the base address to the offset to obtain the desired physical memory address.

The difficulty with segments is that a contiguous set of physical memory locations large enough to hold the segment must be located before a segment can be loaded into memory. A special case of segmentation, call *paging*, eliminates the problem of locating a contiguous memory region large enough to store the segment.

A page is a fixed-size segment. The system divides the virtual memory space into fixed-size segments called *pages*, and divides the physical memory space into fixed-size segments called *frames*. In a paged system all segments have the same size. Because the segment size is fixed, the system can store a segment (page) in any frame. Consequently, loading a page from the backing store simply requires locating an unused frame in which to store the page.

Virtual addresses in a paged system consist of a *page number* and an *offset* within page. In a paged system, the operating system uses an address translation table called a *page table* to map virtual addresses to physical addresses (either in primary memory or on the backing storage) as shown in Figure 1.1.

Segmentation and paging can be combined to reduce the overhead associated with virtual memory (e.g., large address translation tables or long memory allocation delays). Segmented paging and paged segmentation, as described in [Den70] and [PS85], combine segmentation and paging to capitalize on the advantages of both systems.

#### 1.1.2 Memory Management Policies

A virtual memory system uses three basic policies to govern the storage of data: a placement policy, fetch policy, and replacement policy [Den70]. A placement policy specifies the location in memory where data should be placed. A fetch policy determines when data should be loaded from the backing store. A replacement policy

Figure 1.1 Virtual to physical address translation. The operating system maintains an address translation table for each virtual address space. The address translation table contains exactly one entry for every virtual page and specifies the true location of the data (i.e., physical memory or backing storage).

determines which segments/pages should be removed from memory and placed on the backing store. Determining the optimal set of policies for a particular system is a difficult task, and much work has been devoted to the evaluation of various virtual memory policies [Bel66, Den70, ADU71, Den80].

In a paged system, the division of physical memory into uniform frames results in a trivial placement policy. The virtual memory system simply chooses any frame that is available. Moreover, because the operating system typically does not know which pages an application will require in the future, most paged virtual memory systems use a fetch policy called *demand paging*. Under demand paging, the virtual memory system does not retrieve data from the backing store until the data is needed. Although many paged virtual memory systems use the simplistic placement and fetch policies mentioned above, page systems use a wide variety of replacement policies.

The replacement policy defines the rules used to replace data stored in the physical memory. Replacement policies specify the characteristics of segments/pages that should be removed from the physical memory and stored on the backing store. For example, a replacement policy might target the least-recently-used page, the oldest page (first page allocated), or the least-frequently-used page as the page to replace next. A replacement algorithm implements the replacement policy. Because most hardware does not supply the information needed to implement the replacement policy directly (e.g., most hardware does not provide the support required to identify the least-recently-used page), replacement algorithms typically approximate the replacement policy.

Replacement algorithms can be classified as *global* or *local* replacement algorithms. Global replacement algorithms choose the next frame to replace from a global set of frames (i.e., all the frames in the system). Local replacement algorithms allocate a fixed number of frames to each application. When an application needs another frame, a local replacement algorithm chooses a frame from the local set of frames allocated to the application. Example global replacement algorithms include Least Recently Used (LRU), Least Frequently Used (LFU), and Most Frequently Used (MFU). Unfortunately, these algorithms require special hardware support to keep a reference count or timestamp for every physical page.<sup>4</sup> Two common global replacement algorithms, the Clock algorithm and the First-In-First-Out algorithm, do not require special hardware support, which makes them more attractive than LRU, LFU, and MFU [Bel66, Den70, PS85, Tan87, LKKQ89]. Local replacement algorithms include Working Set Replacement, Page Fault Frequency, and Working Size [Den80, Fin88]. In addition, most global replacement algorithms can double as local replacement algorithms.

#### 1.1.3 Virtual Memory Techniques

The physical memory management component of a virtual memory system provides the mechanisms required to transfer data from primary memory to the backing store and from the backing store to primary memory. Three common virtual memory techniques for transferring data between primary memory and the backing store are:

- Overlays: are segments of an application's memory space that are never accessed simultaneously. The application writer knows the structure of the program and defines the overlays. The application assumes the responsibility of transferring the overlays to and from the physical memory at runtime. Overlays require no operating system support or modifications to the operating system.

- Swapping: temporarily removes the entire contents of an application's virtual memory space and places it on the backing store. When the application resumes, the operating system must swap the entire virtual memory space into memory. If the kernel has long-term scheduling information available, it can quickly free up large amounts of physical memory by swapping out applications that will remain blocked for a substantial amount of time.

<sup>&</sup>lt;sup>4</sup>We use the phrase special hardware support to refer to hardware support not provided by many, if any, conventional architectures.

Paging: temporarily removes individual segments/pages of an application's virtual memory space rather than the entire memory space. The virtual memory system transfers certain segments/pages from the application's memory space to the backing store and then retrieves them before, or when, the application attempts to access them.

Overlays are often considered a virtual memory technique although they do not require that an application execute in a virtual address space. Consequently, overlays are especially useful for hardware that does not support virtual memory. However, the burden of physical memory management falls on the application writer who must carefully analyze the program's behavior, determine the segments of the application that can be overlaid, and write the code to transfer overlays to and from the backing store. Swapping, like overlays, can be used on hardware that does not provide virtual memory support. Swapping allows the operating system to quickly reclaim large amounts of memory by grouping multiple segments or pages together (e.g., all the pages of a process' address space) and transferring them all to backing storage at once. Unfortunately, in many cases the removal of entire processes effectively reduces the level of multi-programming. Paging reclaims memory without reducing the level of multi-programming [PS85]. However, paging typically requires hardware support for virtual memory. Because the operating system does not know in advance which pages an application will require, the operating system relies on the hardware to inform the virtual memory system of accesses to non-resident pages.

The simplicity and uniform treatment of memory<sup>5</sup> in a paged system have made paged systems very popular. Many conventional hardware architectures and virtual memory operating systems provide support for paged virtual memory systems. Consequently, the remainder of this thesis will focus on paged systems although many of the ideas and results presented in this thesis can be applied to segmented systems as well.

<sup>5</sup>Uniform treatment of memory refers to the uniform nature of equal size segments. See [Den70].

#### 1.1.4 Virtual Memory Hardware Support

Most conventional computer architectures provide hardware support for virtual memory; however, memory management hardware differs substantially from one machine to another. For example, the Digital Equipment Corporation VAX architecture uses three distinct page tables to map a virtual address space [Dig85]. Each page table maps a single contiguous virtual region of an address space, limiting each address space to a maximum of three virtual segments.

The Sun Microsystems, Inc. Sun 3 architecture uses a special purpose memory management unit (MMU) chip to support virtual memory [Sun86]. The MMU chip contains a fixed-size, high-speed memory that caches a fixed number of page table entries. The operating system must store all other page table entries in the host's memory. Unlike the VAX, the Sun 3 MMU chip can map an arbitrary number of virtual regions in an address space, resulting in large, sparse, virtual address spaces.

The IBM RT/PC and the IBM RS/6000 also support large, sparse, address spaces, but use inverted page tables to reduce the amount of memory allocated for page table storage [CM88, IBM90b, IBM90a]. The hardware uses a hashing function to locate virtual to physical mappings in the inverted page table when performing address translations.

The MIPS chip, used in the Digital Equipment Corporation DECstation series, does not support page tables [Kan89]. Instead, it uses a small, fixed-size translation. lookaside buffer (TLB) containing (process id, virtual page, physical page) triples, which it uses to translate virtual addresses to physical addresses.

Clearly, existing virtual memory hardware varies significantly across vendors. Despite the differences, the basic functionality provided by each architecture is the same. In particular, all the architectures provide hardware address translation and allow programs to use virtual addresses rather than physical addresses when accessing instructions and data.

#### 1.2 Conventional Backing Storage

Once a page has been selected for replacement, the virtual memory system moves the page to the backing store. Early virtual memory systems implemented overlays and used a swapping drum for backing storage [Dij68]. Drums provided stable storage and supported random access.

Today, most virtual memory operating systems use magnetic disks for backing storage [PS85]. Magnetic disks provide high data transfer rates, large storage capacity, and the ability to randomly access data, which makes them an appealing backing. storage medium. The operating system usually reserves a fixed-size, contiguous region of the disk for backing storage and writes blocks of data directly to the reserved region (i.e., no additional file structure or other organizational structure is imposed on the raw storage provided by the disk) [LL82, Bac86, LKKQ89].

Although magnetic disks support random access, the average retrieval time for a magnetic disk is several orders of magnitude slower than that of physical memory [Hab89, Hag89]. The majority of the disk access time is consumed by the *seek* operation which positions the disk arm over the desired data. Consequently, operating systems often attempt to minimize the number of seek operations. Moreover, depending on the disk device, the virtual memory system may use a complex placement policy to optimize for large data transfers to or from the disk.

More recent virtual memory systems have added a level of abstraction to the paging paradigm [GMS88, OCD+87]. These systems use the file abstraction to hide the underlying storage device from the virtual memory system and allow the operating system to store data on the disk using high-level file operations. The virtual memory system does not need to know the characteristics or organization of the underlying disk device because the file system handles the storage of data on the disk. Some operating systems provide support for a distributed file system and allow diskless machines to use remote files for backing storage [GMS88, Nel86, Wel86]. Unfortunately, using files for backing storage increases the overhead associated with paging. Writing data to a file usually requires a minimum of 2 disk accesses (1 or more to write the data and 1 to update the directory structure), whereas writing directly to the disk requires only 1 access [PS85, Bac86, LKKQ89]. Moreover, file systems often attempt to improve performance with techniques such as *read-ahead*. Read-ahead assumes that most programs access files sequentially and attempts to prefetch additional data whenever the system reads from a file. However, when applied to random access paging activity, prefetching wastes valuable buffer space, degrading both paging and file system performance.

#### 1.3 Remote Memory Backing Storage

Current technology trends provide the impetus to re-evaluate conventional backing storage. In particular, CPU speeds, network bandwidth, and memory sizes are increasing at a rapid pace, and the future promises more advances in these areas [Ous90, Par90]. These changes have made new forms of backing storage with added functionality and competitive performance (i.e., competitive with conventional disks whose speeds have remained relatively constant [Hab89, Ous90]) feasible. Current trends in memory technology create the possibility of machines with very large memories. We envision a distributed system with enough physical memory to back much, if not all, of the virtual memory being used by applications throughout the system. In this new model for virtual memory, dedicated, large-memory machines provide highspeed remote memory backing storage to virtual memory systems executing on a set of client machines. In a remote memory system, the client virtual memory systems share the large memory resource. In addition, the high-speed, random access remote memory combined with high-speed networks and processors create the possibility of remote memory backing storage with performance competitive with, or better than, conventional disk backing storage, which is plagued by slow seek times.

Remote memory backing storage differs from conventional magnetic disk backing storage in several ways, and many of the differences affect the design of the client operating system. The most obvious difference between remote memory backing storage and disk backing storage involves reliability. When an operating system issues a read or write operation to a disk, the disk hardware executes the desired operation and then reports the status of the operation (e.g., success or failure). Because network hardware does not report the success or failure of a network transmission, the hardware may lose remote paging requests without signaling an error. In addition, because clients access remote memory across a network, the server may asynchronously accept requests from multiple clients. Disks, however, can only process one read/write request at a time. The operating system cannot issue another disk operation until the previous operation completes. Clients, on the other hand, may interrupt the server with a second or third request before the server finishes processing the first request. If the system does not monitor the number of outstanding requests, a client could swamp the server. Moreover, the network may deliver requests to the server out of order.

Operating systems that use magnetic disks for backing storage maintain data structures that manage the allocation and deallocation of the disk space. However, in the remote memory model, the memory server manages the backing store, which frees the client operating systems from maintaining data structures that manage the backing store.

Because disks have relatively slow seek times (i.e., random access performance), conventional virtual memory systems attempt to improve performance using techniques such as *read-ahead* or *delayed writes* to reduce the number of seek operations. Remote memory backing storage does not suffer from this problem because memory, unlike a disk, provides constant-time random access to data.

#### 1.4 Organization of the Thesis

Chapter 2 defines terminology used throughout the remainder of the thesis. Chapter 3 presents the *Remote Memory Model* and briefly describes the three basic components of the model: the client virtual memory operating system, the communication protocol, and the memory server. Chapter 3 concludes by discussing advantages and disadvantages of systems based on the model.

Chapter 4 describes a hierarchical virtual memory operating system designed to support remote memory backing storage. Chapter 5 presents a high-speed communication protocol used by the client virtual memory system to transfer data to and from the memory server. Chapter 6 describes the design of a highly efficient memory server capable of supporting multiple client machines simultaneously. Chapter 6 also describes the high-level abstraction used by the memory server to support heterogeneous client machines.

Chapter 7 describes a prototype implementation and presents experimental results obtained from the prototype. The results demonstrate the viability of the remote memory model and show that performance is competitive with existing distributed systems.

Finally, chapter 8 presents conclusions drawn from the research and outlines directions for future research.

#### 2. TERMINOLOGY

This chapter defines terminology used throughout the remainder of the thesis. We assume the reader has a basic understanding of operating system and network terminology. A basic description of operating system terminology can be found in Peterson *et. al.* [PS85]. Denning presents an overview of virtual memory in [Den70]. Tannenbaum [Tan81] and Comer [Com88] describe network communication and distributed systems. In addition to basic terminology, this chapter clarifies ambiguous terms by defining them in the context of this thesis.

#### 2.1 Virtual Memory Operating Systems

An operating system manages a computer's resources and provides support for multiprogramming. A virtual memory operating system supports an abstraction called virtual memory where each application executes in a logical memory space much larger than the size of the machine's physical memory space. Application programs use logical virtual addresses, as opposed to physical addresses, to access memory locations. Virtual memory hardware translates virtual addresses to physical addresses to locate the data specified by a virtual address. The hardware component that provides support for virtual memory is called the memory management unit (MMU). An MMU typically uses an address translation table called a segment table or page table to translate virtual addresses to physical addresses (see Section 1.1.1). When the MMU encounters an invalid page table entry, the MMU raises a page fault exception to indicate that the virtual address could not be translated or a protection violation has occurred (e.g., a write access to a read-only page). Virtual memory operating systems categorize data storage media as primary storage or backing storage. Primary storage refers to the memory physically located in the computer, while backing storage refers to data storage media other than primary storage. Typically the backing store is characterized by slower access times than primary storage. For most conventional systems, backing storage refers to a magnetic disk drive. The virtual memory system uses the primary storage to cache data that will be accessed in the near future and stores all other data on the backing store.

The virtual memory system divides each virtual address space into segments or  $pages.^1$  In the case of a paged system, the virtual memory system divides the physical memory (primary storage) into fixed size *frames*. The size of a frame is determined by the hardware, while the size of a page is set by the operating system. Consequently, the size of a page may differ from the size of a frame. However, most virtual memory operating systems define the size of a page to be the same as the size of a frame.

Conventional virtual memory operating systems use the abstraction of a process to provide multiprogramming [PS85]. A process consists of a virtual address space and a point of execution within the address space. The virtual memory system allows multiple processes to execute simultaneously. More recent systems support multithreaded processes [Ras86, OCD+87, CG91]. A thread is defined to be a point of execution within a process' address space. All threads execute in parallel but execute at separate points in the code. The advantage of multi-threaded processes is the ability to concurrently manipulate shared data within a process.

#### 2.2 Network Communication

Computers uses a *communication channel* to communicate with other computers. A communication channel can be a physical network (e.g., an Ethernet) or a logical (virtual) network consisting of multiple physical networks connected by gateways [Com88, Tan81].

<sup>&</sup>lt;sup>1</sup>Section 1.1.1 describes segments and pages.

A datagram is the basic unit of transfer across a communication channel. Many conventional communication channels provide unreliable datagram service. Unreliable datagram service refers to a connectionless message-based data transmission model in which the communication channel allows computers to send and receive datagrams but does not guarantee that the datagrams will arrive at the destination. Instead, the communication channel only guarantees to make a *best effort* to deliver each datagram [Nar88].

Each datagram has a fixed, architecture-dependent, maximum size. The maximum size of a datagram is called the maximum transmission unit (MTU). Many virtual network architectures provide data transfer across multiple physical network architectures connected by gateways. Although the virtual network defines a virtual MTU for the size of a datagram, each underlying physical network architecture defines its own MTU, which may be less than the MTU specified by the virtual network architecture. In this case, the virtual network fragments virtual datagrams into physical datagrams, or packets, such that the size of each packet is less than the smallest MTU of the underlying physical network architectures.

A protocol defines the language that hosts use to communicate. In order for two or more hosts to communicate, they must agree upon a protocol before communication can begin. A protocol specifies the format and meaning of the information as the information travels from one host to another. Protocols also define the set of operations to perform when errors occur.

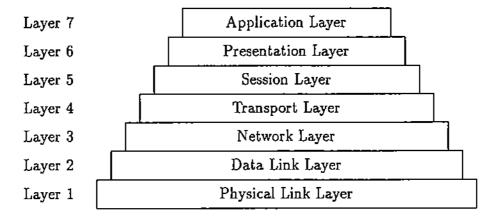

A network architecture is defined by a set of layered protocols called a protocol stack [McF76, Com88, Sta91]. Figure 2.1 illustrates the protocol stack used in the International Standards Organization Open Systems Interconnection (ISO OSI) Reference Model. When a message travels from one host to another, the message traverses the layers of the protocol stack. Each layer of the protocol stack provides a set of services and may only use the services provided by the layers below. Organizing the network communication task into multiple layers simplifies the design process by breaking the communication task into smaller, managable pieces.

Figure 2.1 The OSI Reference Model.

Communication channels transmit data at a rate specified in *bits per second* (bps). For the purposes of this thesis, we use the relative terms *high-speed* and *high-bandwidth* to describe communication channels capable of transmitting data at rates in excess of 10 megabits per second (Mbps).<sup>2</sup>

Host machines (and gateways) often enqueue incoming messages until the host has a chance to process the messages. When a packet travels from one host to another it may experience one or more *queueing delays*. The time a message spends in the queue waiting to be processed is called the *queueing delay*. In the case of a virtual network where a message traverses several gateways, a message experiences a queueing delay at each gateway between the sender and the receiver.

One measure of the performance of a communication channel is the average transmission delay. The transmission delay is the amount of time required to transmit a message from one host to another. Another measure of performance is the round trip time (RTT). In the client-server model, the round trip time refers to the elapsed time between the time at which a client first sends a request message to a server and the time at which the client receives the acknowledgement or reply message from the server. We will often refer to the round trip time as the round trip delay.

$<sup>^{2}</sup>$ As we will see in chapter 7, a 10 Mbps communication channel provides acceptable performance (i.e., competitive with conventional systems).

#### 2.3 Distributed Systems

A distributed system consists of multiple computers called hosts, or nodes, connected by a communication channel. A host or node is a general purpose computer that typically executes an operating system and supports user-level applications. The communication channel allows hosts to communicate information by sending and receiving messages. A heterogeneous distributed system consists of host machines with a variety of hardware architectures.

In a distributed system, each node provides a subset of the services available to the users of the system. Together the nodes comprise a system with full functionality and a complete set of services. In contrast, a *stand-alone* system consists of a single computer which provides a complete set of services without the aid of any other computers.

Many conventional distributed systems use the *client-server model* of computing [Com87, Tan81]. Systems based on the client-server model identify common operations or functions and define them as a *service*. A *server process* performs one or more services and allows other hosts in the distributed system to use the services it provides. A server presents a well-defined interface to the service(s) it performs. Applications throughout the distributed system know and use the well-defined interface to access the service. Application programs access the service by sending a request message across the communication channel to the server process. When an application issues a request message, the application becomes a *client* of the server. The server receives the request message from the client, performs the service requested in the message, and returns the results to the client in a reply message. For example, one node might provide a file service while a second node provides a computational service and a third node interacts with the user via a user-interface. Although none of the nodes constitute a complete system, when combined together, the nodes provide all the services available to the user. The advantage of the client-server model is that it functions correctly when the server and the client are on the same machine (e.g., a stand-alone system) or when the server and the client are on separate machines (e.g., a distributed system). In addition, the model partitions the system functions into independent, self-contained services that form an elegant, modular system.

#### 3. THE REMOTE MEMORY MODEL

Virtual memory operating systems afford programmers the luxury of developing applications that assume an arbitrarily large memory space. Virtual memory frees programmers from architecture-dependent memory constraints and allows them to produce highly portable, architecture-independent applications. The operating system creates the illusion of an arbitrarily large memory by mapping a small portion of the virtual memory space to physical storage. The physical storage space consists of primary memory and a backing store (typically, a magnetic disk). The operating system maps certain regions of the virtual address space to physical memory and maps the remaining regions to the backing store. The virtual memory system manages (i.e., allocates and reclaims) the primary memory and the backing store. Typically the virtual memory system maps regions that have a high probability of being accessed in the near future to physical memory in an attempt to minimize access to the backing store.

Conventional distributed systems execute a virtual memory operating system on each node in the system. Each virtual memory system independently manages its local, private memory. No mechanism exists for the virtual memory system on one machine to use unused memory on another machine. The virtual memory systems do not interact and have no means of sharing the physical memory located on the various nodes. That is, conventional distributed systems preallocate and assign private physical memory to each machine instead of allowing all the machines to share the physical memory resources. Consequently, the virtual memory system only allows applications to use local memory. When the applications exceed the capacity of the local memory, the virtual memory system moves application text and data to the machine's private backing store instead of using unused memory elsewhere in the system.

Current trends in memory technology create the possibility of machines with large memories. We envision a distributed system with enough physical memory to back much, if not all, of the virtual memory being used by applications throughout a distributed system. This chapter describes a new virtual memory model called the *remote memory model*. The remote memory model defines a distributed system in which all the machines share a large, physical memory resource. The system provides simple and efficient mechanisms for accessing the large memory resource and allows every machine's virtual memory system to access the memory resource. Instead of preallocating and installing all the physical memory resources as private memory on the individual machines, the model combines some of the physical memory resources together into a single, large, globally accessible, memory resource and provides efficient access to the memory. Consequently, the virtual memory systems all share the memory resource.

The remainder of this chapter describes the remote memory model and the assumptions we make about the model. It identifies the properties of the model and describes advantages and disadvantages of building systems based on the model.

#### 3.1 The Model

The remote memory model describes a new architecture for designing distributed systems. The model proposes a new virtual memory architecture that enhances both the functionality and the performance of distributed systems. It defines the various components of the system, the role each component plays, and the interaction between the various components.

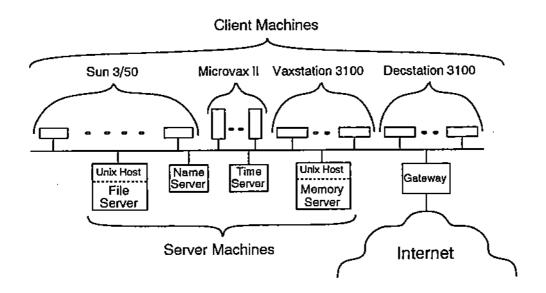

Figure 3.1 illustrates an example remote memory model architecture. The system consists of multiple *client* machines, one or more *memory server* machines, various other servers (e.g., time servers, name servers, or file servers), and a communication channel interconnecting all the machines. In the remote memory model, memory

Figure 3.1 An example remote memory model architecture.

server machines provide additional memory storage space for the virtual memory systems executing on the client machines. Instead of parceling out the memory resources to individual machines where the memory is installed as private memory, the remote memory model provides a large memory resource which all the clients share. In the remote memory model, client machines access the memory server to obtain additional storage space.

Each client machine has a local memory capable of satisfying the client's normal processing demands. However, for jobs requiring large amounts of memory, clients use the large memory of the memory server for additional storage space. When the memory requirements of an application exceed the capacity of the local memory, the client's virtual memory system stores some of the application's data on the memory server. When the application attempts to access data not cached in the local memory, the virtual memory system intercepts the access, transfers the desired data from the memory server to the client's local memory, and resumes execution. To free local memory, the virtual memory system periodically transfers data from the local memory to the memory server. Each client's local memory functions as a high-speed cache of the large, shared, memory resource on the memory server.

All the client machines connect to the communication channel and contain the necessary hardware support required to send and receive messages across the communication channel. A client machine may be anything from a small microprocessor (e.g., a sensor device) to a multi-user time-sharing system (e.g., a workstation or main-frame). Each client machine executes a virtual memory system, typically assisted by address translation hardware. The virtual memory system has the functionality required to access the large storage space located on the memory server. That is, the virtual memory system understands the protocol used to communicate with the server as well as the operations provided by the server. The virtual memory system hides the location of the data (i.e., whether the data exists in local memory or remote memory) from the application. The client's virtual memory system, with the help of the memory server, creates the large virtual address spaces visible to the applications.

Large memory machines called *memory servers* provide shared, high-speed remote memory storage to the virtual memory systems executing on the client machines. Memory servers do not execute user applications. Instead, memory servers are dedicated machines whose sole purpose is to provide remote data storage. Each memory server machine has a large amount of storage space. The storage space consists of physical memory and a mass storage device (e.g., disk drive). The total size of the storage space on a memory server must exceed the expected maximum combined memory usage of all the client machines. Clearly, the maximum memory usage depends on the specific system configuration.

Although memory servers may use secondary storage to increase the total amount of storage space, memory servers do not require virtual memory support from the hardware. For performance or economic reasons the designer of a memory server machine may chose to omit the MMU. In this case, the memory server must provide all virtual memory management (e.g., swapping to secondary storage) in software. However, each memory server machine must have the network communication hardware required to communicate with the client machines it serves. Because memory server machines only require the aforementioned hardware, they are relatively simple machines (i.e., they do not require serial ports, video boards, monitors, or an MMU) and can be viewed as a "black box" providing high-speed data storage.

The communication channel provides every client with the ability to send and receive messages to and from the memory server. The communication channel acts like a high-speed bus or backplane connecting multiple processors to a shared memory. However, the communication channel differs from a bus in several ways. The model assumes the communication channel provides unreliable datagram delivery. That is, the model only assumes the communication channel makes a *best effort* to deliver each datagram [Nar88].

Assuming unreliable datagram service allows the model to encompass a wide variety of network architectures. For example, the unreliability assumption allows the model to use both reliable and unreliable network hardware. Similarly, the datagram delivery assumption allows the model to use network architectures that provide datagram delivery (packets with a fixed maximum size), message delivery (logical messages of arbitrary size), or byte-stream delivery (using record marking to emulate datagrams). Moreover, the model does not restrict the communication channel to a low-level protocol in the protocol stack. Consequently, the model may use a link-level physical network architecture (e.g., Ethernet) or a transport-level virtual network architecture (e.g., TCP/IP) as the communication channel.

Although the example communication channel shown in Figure 3.1 appears to provide broadcast capabilities, the remote memory model does not assume a broadcast facility. The model only assumes that a communication path exists from every client to the memory server. Consequently, other communication technologies, such as point-to-point network architectures, may serve as the communication channel.

The remote memory model provides an alternative to conventional distributed systems. The model approaches virtual memory differently than conventional distributed systems by allowing clients to share a large, globally accessible, memory resource. Memory servers act as monitors for the memory resource, allocating memory to clients based on their needs. The remote memory model also provides the client virtual memory systems with the opportunity to interact via shared data. The above functionality differences together with high performance make the remote memory model an attractive alternative to conventional distributed systems.

#### 3.1.1 Design Decisions

The general form of the model, described in the previous section, encompasses a wide variety of system architectures. This section further defines various unspecified aspects of the model. In particular, we make some design decisions that result in a more precise or focused definition of the model. However, the design decisions are not part of the model. They simply refine the definition of the model to provide the functionality and performance we desire.

The continued proliferation of computer architectures make heterogeneous systems a reality that cannot be ignored. Consequently, the model should support heterogeneous distributed systems. The size of a virtual address space, physical memory size, page size, byte order, and word size may differ from machine to machine. Moreover, client machines may execute heterogeneous operating systems, each with its own virtual address space configuration, process structure, and replacement policy. Despite these differences, memory servers must provide remote memory to all client machines, regardless of the client's architecture or operating system.

We assume the majority of clients execute a multi-user or multi-tasking virtual memory operating system with support for multiple virtual address spaces. Although clients use remote memory instead of a local disk for backing storage, the model does not assume diskless clients. Client machines may use a local disk for permanent storage (e.g., a local file system). To simplify the model and the design of the client virtual memory system, we assume each client only accesses one memory server even if multiple servers exist.<sup>1</sup>

<sup>&</sup>lt;sup>1</sup>The single server restriction also facilitates rapid prototyping and experimental evaluation of systems based on the model.

Each memory server machine has a large physical memory capable of backing most, if not all, of the virtual memory being used by the applications throughout the system. Recent advances in memory technology allow each memory server to have hundreds of megabytes, gigabytes, or possibly even terabytes of physical memory. As we mentioned earlier, each memory server must have a storage space whose total size exceeds the maximum memory usage of the clients. Consequently, a memory server may use secondary storage to increase the total storage space on the server. However, for performance reasons, the memory server should have a large physical memory to reduce the number of accesses to secondary storage.

One of the goals of the remote memory model is to provide high-speed access to additional memory storage. Consequently, the communication channel should have a high bandwidth and low delay. Although the communication channel may be unreliable, the channel should exhibit a relatively low error rate. These requirements typically restrict the communication channel to high-speed local area networks (LANs) or metropolitan area networks (MANs). Example communication channels include Ethernet (10 Mbps), proNET (10 or 80 Mbps), and FDDI (100 Mbps) [Dig80, RHF90]. Virtual network architectures (e.g., TCP/IP networks, OSI networks) may be used as the communication channel as long as they adhere to the high-speed communication requirement.

#### 3.1.2 Characteristics of the Model

Having described the remote memory model, this section focuses on characteristics of the model and briefly examines advantages and disadvantages of designing systems based on the model.

Perhaps the most apparent difference between the remote memory model and conventional distributed systems is the high-speed data storage offered by the memory server. Client applications that require large amounts of memory obtain additional high-speed memory from the memory server. In addition to providing a large, highspeed storage space, the remote memory model has the following desirable characteristics:

## Shared Access

Each memory server provides data storage to multiple client machines simultaneously. All the client virtual memory systems concurrently access the memory server to store and retrieve data. Instead of preallocating a fixed amount of memory to each client, the memory server allows the client virtual memory systems to share the memory resource by dynamically assigning and reassigning the memory resource to clients based on their changing needs. In addition, the server does not limit the number of clients it will serve. Each memory server allows an arbitrary number of clients to access its memory.

## Shared Data

The remote memory server provides a centralized memory, accessible to all client machines. The globally accessible memory resource provides the opportunity for clients to efficiently share data. Although the model permits data sharing among clients, the model does not specify the mechanisms used to share data. Depending on the type of data sharing desired, the memory server may implement data sharing mechanisms that allow read-only sharing, read-write sharing, or no sharing [Li86, LH89]. Because multiple client machines often execute a given application, use a given library, or memory map a given file (e.g., a font file or a static database), even a simple read-only sharing mechanism significantly reduces the amount of server memory consumed by client data. A more complex sharing mechanism might use the server as a centralized monitor to implement read-write distributed shared memory. The centralized monitor would grant or deny access to shared regions and provide the coherency control required to maintain consistent copies of the data on all the client machines. In short, the model allows the memory server to support several shared data models.

#### Arbitrarily Large Storage Capacity

Memory servers employ virtual memory techniques to create an arbitrarily large memory resource in which clients may store data. Although memory servers have very large memories, the amount of memory on any given server remains fixed and depends on the server's underlying architecture and hardware configuration. To provide an arbitrarily large storage space, independent from the physical memory size of the memory server, a memory server uses one or more secondary storage devices (e.g., disk drives) and a replacement policy to substantially enlarge the server's storage capacity. When the client machines collectively exhaust the physical memory on the server, the server transfers client data to secondary storage, thereby freeing physical memory for additional client data. As a result, client machines are completely unaware of the two-level storage space.

Memory servers hide the size of their physical memory from the clients they serve much like a virtual memory operating system hides the size of the underlying machine's physical memory from the applications executing on the machine. In a virtual memory operating system the machine's physical memory size does not constrain the amount of virtual memory an application can obtain. Similarly, the memory server's physical memory size does not restrict the amount of backing storage a client can obtain. Consequently, a client may use any memory server, regardless of the server's physical memory size.

Offloading File Server

The remote memory model improves file system performance by removing paging activity from the file system. Similarly, memory servers improve virtual memory system performance by providing high-speed backing storage. Removing paging activity from the file system significantly reduces contention for the disk and eliminates many extra head movement operations. Virtual memory systems that use a file system for backing storage compete with all the user-level processes for the file system's resource. In the case of a remote file server, the virtual memory system competes with the user-level processes of all the machines in the system. The file system gives no special privileges or priority to requests from the virtual memory system because it cannot distinguish between user-level file access and virtual memory system paging operations.

File systems often optimize performance for the most common file access patterns. Many file systems attempt to improve performance with techniques such as *read-ahead*. Read-ahead assumes sequential file access and prefetches extra data each time an application reads from a file. However, in many cases, the paging activity generated by the virtual memory system results in random data access as opposed to sequential data access. When applied to paging activity, prefetching wastes valuable buffer space and degrades both paging and file system performance. Separating paging activity from file activity allows us to implement each operation efficiently. Unlike file servers, memory servers understand paging activity and can be designed to make intelligent decisions regarding storage and retrieval of data.

# Multiple Forms of Remote Memory

The remote memory model does not define the operations allowed on remote memory, nor does it specify the behavior or reliability of remote memory in all situations. Consequently, the remote memory model allows system designers to define the operations and reliability provided by remote memory to meet the needs of their particular system. We already mentioned several possible semantics for providing shared data between clients. The model also allows the memory server to store and retrieve data with various reliability guarantees. For example, the client virtual memory systems may view remote memory as a less efficient form of local memory, but similar in all other respects. Given this definition, the memory server provides high-speed volatile storage similar to the client's high-speed volatile local memory. A different definition of remote memory may require *reliable storage*. In this case, the memory server must use a non-volatile storage device to store a copy of all the data written to remote memory. Another definition may require *reliable storage* and *reliable retrieval*. In this case, multiple memory servers may cooperate to provide fault tolerance and insure that clients can access remote memory at all times.

#### Exploits Technological Advances

Network bandwidth, CPU speeds, and computer memory sizes are increasing at a rapid rate. The remote memory model exploits these particular hardware technologies and will continue to exhibit better performance as the technology advances. The average seek time on a magnetic disk, however, has remained relatively constant. In the future, we expect the remote memory model to offer performance several times faster than systems that page to a local disk.

These advantages make the remote memory model an attractive model for designing distributed systems. However, the model is not without its drawbacks. Because memory servers provide a centralized memory service, they present a potential bottleneck. If the number of requests becomes too large for the server to handle, the server's ability to respond quickly and efficiently to requests will deteriorate and degrade the performance of the client virtual memory systems. Because all clients access remote memory across the communication channel, the communication channel poses a potential bottleneck. As the number of clients increase, the amount of data traveling to and from the server increases and consumes a significant portion of the communication channel's bandwidth. Moreover, remote memory traffic may compete with all other network traffic for the communication channel's bandwidth. Despite these potential problems, the remote memory model's attractive properties combined with the possibility of performance competitive with, or better than, conventional magnetic disk backing storage make the remote memory model an attractive model for designing distributed systems.

#### 3.2 Summary

This chapter describes a new model for designing distributed systems. The model proposes a new virtual memory architecture in which dedicated, large-memory machines serve as backing store for virtual memory systems operating on a set of heterogeneous client machines. The dedicated memory server allows sharing of the large physical memory resource and provides fast access to data.

The remote memory model has several desirable properties. Memory servers provide high-speed data storage to virtual memory systems executing on heterogeneous client machines. The centralized nature of the memory server provides clients with the opportunity to share data. The remote memory model improves file system performance by offloading the file server. Separating file activity from paging activity allows us to implement each operation efficiently. Finally, the model appears promising for the future because it exploits the rapid technology advances in network bandwidth, CPU speeds, and memory size. In short, the remote memory model provides an attractive alternative for designing distributed systems.

## 4. A CLIENT VIRTUAL MEMORY SYSTEM

In the remote memory model, the client virtual memory system communicates with the memory server to access remote memory backing storage. As you will recall from the description of the remote memory model presented in chapter 3, each memory server provides remote memory backing storage to heterogeneous client machines executing a variety of virtual memory operating systems. Consequently, the only requirement of the client operating system is that it must provide support for remote memory backing storage. The virtual memory system must understand (and use) the set of operations provided by the memory server. In addition, the operating system must implement the communication protocol used to communicate with the memory server.

This chapter presents the design of a virtual memory operating system with support for remote memory backing storage. The system presented here serves as an example of how to incorporate remote memory backing storage into a virtual memory operating system. The same mechanisms and approach could be applied to a wide variety of existing operating systems, thereby allowing them to make use of remote memory backing storage.

#### 4.1 Design Goals

In the remote memory model, the virtual memory component of the client operating system provides the support required to access remote memory backing storage. While designing the client virtual memory system, we identified several additional design goals indirectly related to the basic goal of incorporating remote memory backing storage into the virtual memory system. In particular, we envisioned a client virtual memory operating system with the following characteristics:

Architecture Independence

In order to execute the operating system on a wide variety of client architectures, the operating system must exhibit a high degree of portability. In particular, the virtual memory system must not depend on the underlying hardware architecture. Clearly, architecture dependencies will exist, but the design should limit and isolate them as much as possible.

Hierarchical Design

Operating systems are large, complicated pieces of software. Experience with the simplicity, flexibility, and clarity of existing hierarchically-designed operating systems demonstrates the benefits of designing operating systems in a hierarchical fashion [Com84, Dij68, Lis72, SAG<sup>+</sup>72].

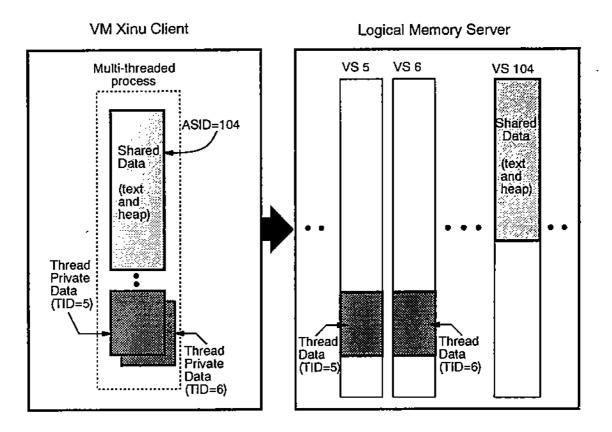

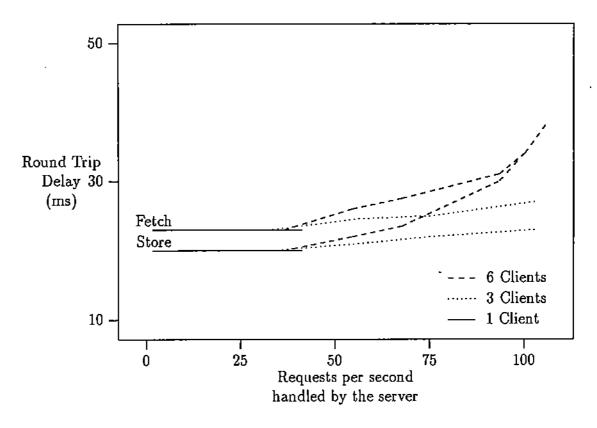

Multiple Threads of Control