# Photolithography methods for 3D microstructures and 3D stacking devices

## **Muhammed Hassen Ahmed**

Researcher, Jimma University, Ethiopia muhammed.hassen1@ju.edu.et

#### **Article History**

# Article Submission 04 October 2021 Revised Submission 16 November 2021 Article Accepted 18 December 2021 Article Published 20 January 2022

#### Abstract

A framework streamlining instrument for lithography is made and seemed to create 3D micro-arrangements utilizing light-film photo material resists. Since, the two technique confines in greyscale lithography: presentation partition theme and improvement timescale are settled in this way for a client indicated target 3D profile. This gives a proficient and persuading elective as opposed to standard experimentation-based framework plan. As far as possible were asserted by collecting assorted 3D micro-arrangements and the evaluations uncovered unimaginable quantized synchronization with the objective profile. Likewise, Edgeportrayed nm scale lines are organized in silicon utilizing optical lithography with benchmark materials and preparing device are impeccable with short warm copying through 3D three-dimensional (3D) Integrated Circuit structures. A CVD process is utilized to depict optical spacers with photo-resist spread to arrangement covered layers.

# Keywords: photolithography, 3D devices, masking, chemical vapor deposition

### I. Introduction

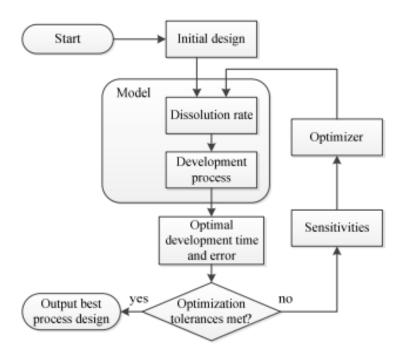

By and large, photolithography is to perceive planar organization in a silicon-substrate. The fashion construction is 3-D, yet restricted to only two unquestionable statures. Therefore, various 3-D photolithography strategies are announced. These astoundingly increment the course of action flexibility for the coordinator, as they permit client picked freestyle constructions to be added up in the photo-resist. Thicker photo-resists changed the course of action adaptability. This uninhibitedly formed thick photoresist layer would then have the choice to be utilized as vital polymer. The arranging methodology for photolithography shouldn't be a high distinction process the degree that presentation, regardless, it can in like way be released up towards focus introduction estimations and in this manner, almost the entire way improvement rates. 3D photolithography is worked on utilizing variable-parcel acquaintance procedures with control the near to advance importance in the photo-resist and termed as gray-scale lithography. By the by, this framework reliably doesn't speedy exemplary outcomes because of spatial dissipating of disintegrating velocity in the photo-resist and, as necessities be, requires labour-intensive alterations by experimentation to discover pleasing system limits. To beat this damage, a particularly mechanized method streamlining framework, as appeared in Figure 1, is made dependent upon computational system preoccupation, affectability assessment and movement techniques.

This methodology can commonly reimburse undesired effects, for instance, inclined sidewalls in light of isolating in the level bearing. The exceptional pieces of this strategy are: (1) the yields are the two refreshed procedure limits, for instance introduction section summary and improvement time (2) Dissolution rate are settled conventionally with target profile data. Stacking of encouraged circuit gadget layers can astoundingly manufacture thickness, decline power use. The essential specific bit of breathing space offered by 3D stack is decreasing of interconnect delay. The Manufacturing improvement financially open for generally moderate speed, high-thickness applications. Gathering of higher speed 3D ICs despite everything requires specific reactions with heat scattering and improvement of single precious stone silicon for semiconductor channels inside a 3D structure. The sparkle disseminating issue can be tended to by utilizing ultra-low force circuit structure frameworks and extreme scaling. The 3D IC process stream controls a breaking point on the most ludicrous technique temperature for long lengths in the wake of binding the principal level of devices.

ISSN: 2250-0839 © IJNPME 2022

Figure 1. A flowchart showing optimization approach

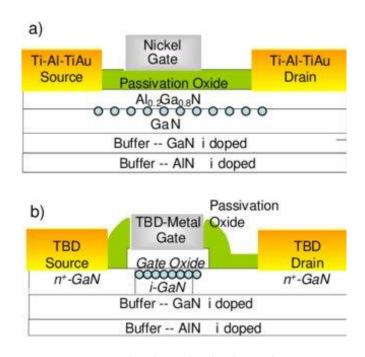

Figure 2. Edge Defined Lithography

Doping spread along clear silicon grain limits is greater by a few colossal degrees than in single significant stone silicon. Attentive temperature organize is of prime immensity when stirring up a system stream for 3D ICs.

Edge-depicted lithography guarantees straightforwardness, normal, high-throughput, and particularly controlled reaction for expand the life of projection lithography frameworks. The edge-portrayed lithography strategy, as appeared in Fig 2, has been analyzed for more than two decades in different settings. An assortment of this particular philosophy has been commonly utilized in industry to LDD FETs.

ISSN: 2250-0839 © IJNPME 2022

# Reference

- [1] F. van Keulen, et al., "Automated optimization of light dose distribution for moving-mask lithography", Proc. EuroSimE, 2009, pp.1-9.

- [2] T. H. Lee. "A veniwl leao far micmchios." Scientific American. Jan. 2002.

- [3] Y. Hirai et al., "A three-dimensional micro structuring technique exploiting the positive photoresist property", J. Micromech. Microeng., 2010, 065005.

ISSN: 2250-0839 © IJNPME 2022