# Analysis and Design of Universal Shift Register Using Pulsed Latches

<sup>1</sup>Mr. Dharmesh Dhabliya, <sup>2</sup>Dr.S.A.Sivakumar

<sup>1</sup>R&D Department, Yashika Publications Wardha, India <sup>2</sup>Assistant professor-ECE, Info Institute of Engineering, India <sup>2</sup>drsasivakumar@gmail.com

| Article History                                                                                                                                         | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Article Submission<br>27 May 2019<br>Revised Submission<br>12 July 2019<br>Article Accepted<br>19 August 2019<br>Article Published<br>30 September 2019 | Power utilization and die region space are the significant boundaries which are<br>considered for structuring low level power outcomes. This paper put forward the<br>structure of low force general move register and 4-piece counter utilizing pipe<br>rationale. Since flip failures are an innate structure hinder in a few applications,<br>different flip lemon are over viewed and executed in widespread move register and<br>4-piece counter. Flip lemon utilizing pipe rationale is viewed as dependent on the<br>correlation of intensity and region. At last, a low force all inclusive move register<br>and 4-piece counter is planned utilizing pipe rationale. The proposed USR and 4-<br>piece counters are mimicked with various clock rate going from 100 KHz to<br>500MHz. Re-enactment of these flip flounders, the widespread move register and<br>the 4-piece counters are finished utilizing Tanner device at 180nm innovation. The<br>normal force and the PDP of USR are improved by 33% and 27% and further the<br>normal force and the PDP of 4-piece counter are improved by 36.9% and 30.2%<br>when contrasted and existing plan separately. So the put forward plan is reasonable<br>for low level power and elite applications.<br><b>Keywords:</b> Power consumption, universal shift register, pipe logic |  |  |

## I. Introduction

A Shift register act as essential structure impede in VLSI circuit and are commonly used in various applications, for instance, propelled channels, correspondence beneficiaries and picture taking care of IC's. Beginning late, as the size of the picture information keeps reaching out considering the acclaim for top notch data transfer, the word time-span of the shifter register enlargements to progression of monstrous data.. The move register is a consecutive rationale circuit that can be utilized for the capacity or move of information in type of twofold numbers. This consecutive gadget stacks the information present on its data sources and afterward moves or moves it to its yield once every clock cycle, consequently the name move register. A move register essentially comprises of a few single piece D-type information hooks, one for every information bit, either rationale \_0' or \_1' associated together in a sequential course of action with the goal that the yield from one information lock turns into the contribution of the following lock [2].

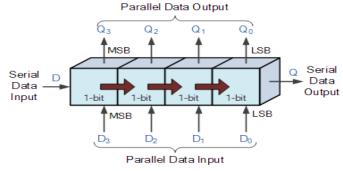

Fig 1: Data movement in shift registers

A key four-piece move register can be constructed using four D flip-flops, as showed up in figure1. The register is first cleared, driving every one of the four respects zero. The data is then applied continuously to the D commitment of the essential flip-flop on the left (FF0). During each clock beat, a tiny smidgen is transmitted from left to right. So as to get the information out of the register, they should be moved out sequentially. The impact of information development from left to directly through a move register can be introduced graphically as appeared in figure 1. The planning outline shows the time connection between the CK heartbeats and changes at the Q yields of the circuit. It tends to be seen that if the sequential information goes from 0 to 1 not long before CK beat 1, the Q yield of flip-flop FF0 will go high at the rising edge of CK beat 1. At the following clock beat rising edge, the rationale 1 will be moved to FF1, etc until it comes to FF3, and the sequential yield [3]. It is the major taking care of part in continuous procedure for intuition.

Flip-bobbles and gets are a principle structure square of bleeding edge gear systems used in PCs, correspondences, and various kinds of structures. Flip-hangs and jolts are utilized as information hoarding portions. A flip-flop stores a solitary piece twofold digit of information; one of its two states tends to a "one" and the differing tends to a "zero". Such information accumulating can be utilized for breaking point of state, and such a circuit is delineated as dynamic technique for thinking. Precisely when utilized in a confined state machine, the yield and next state depend upon its present information, yet in addition on its present status and as such, past information sources. It can also be utilized for tallying of heartbeats and for synchronizing intensely arranged information signs to some reference timing signal [4].

Flip-failures can be either (straightforward or obscure) or timed (coordinated or edge-activated). Despite the fact that the term flip-flop has generally alluded conventionally to both basic and timed circuits, in present day use it is entirely expected to hold the term flip-flop only for examining timed circuits; the basic ones are regularly called hooks. Utilizing this phrasing, a hook is level-delicate, while a flip-flop is edge-touchy. That is, the point at which a hook is empowered it gets straightforward, while a flip failure's yield just changes on a solitary kind (positive going or negative going) of clock edge. This article intends to plan a low force and zone proficient Universal move register and 4-piece counter utilizing altered channel rationale flip lemon. Since flip failures is an innate structure obstruct in both widespread move register and in 4-piece counter.

In this paper different flip flops are being reviewed and actualized in general move register and in 4-piece counter. Further the proposed plan for 4-piece counter is contrasted and existing flip lemon structures, for example, TGMS, MC2MOS flip failure, HLFF, Power PC 603, and SDFF which are executed in 4-piece counter. Flip lemon utilizing pipe rationale is viewed as dependent on the correlation of intensity and region. At long last, a low force general move register and a 4 piece counter is planned utilizing pipe rationale. The proposed USR and 4-piece counter is reproduced with various clock frequencies running from 100 KHz to 500MHz. Reproduction of these proposed structures are finished utilizing Tanner apparatus at 180nm innovation. This paper executes the plan of general move register and 4-piece counter utilizing changed channel rationale flip failure. The normal force utilization and zone of both the structures are evaluated in planning low force applications. So the proposed idea makes the structure possible for low force applications [5].

## **II. Existing techniques**

A great deal of rules for dependable estimation of the certifiable presentation and power features of the flipdisappointment and pro slave lock structures has been presented. The examination approach reveals the wellsprings of execution and power usage bottlenecks in different arrangement styles. Certain tricky limits have been fittingly modified and weighted to reflect the real properties of the idea about structures. In addition, the eventual outcomes of the assessment of operator pro slave snares and flip disappointments depict the upsides of this procedure and the sensibility of different arrangement styles for unrivalled and low-power applications. Half breed lock flip-flop (HLFF) introduced here is perhaps the quickest structure introduced. It additionally has an extremely little PDP. The fundamental disadvantage is that a gathering of half and half structures highlights negative arrangement time and consequently better execution attributes over the gathering of ace slave structures including positive arrangement time and subsequently decreased execution. Another significant downside of the half breed configuration when all is said in done is the optimistic hold time. Because of the single-yield structure, the force utilization scope of the FF is practically identical to stationary circuits. Be that as it may, contingent upon the force appropriation, precharged configuration can scatter more than stationary structures for information designs. Half breed configuration has all the earmarks of being truly appropriate for elite frameworks with practically zero punishment in power when contrasted with old style static structures. Further it has bigger clock stacks alongside bigger power dispersal [6].

A plan of low force moves register utilizing understood and unequivocal sort flip lemon are additionally done. Contingent upon the strategy for beat age, P-FF plans can be named verifiable and unequivocal. In a verifiable sort P-FF, the beat generator is a worked in rationale of the lock plan, and no unequivocal heartbeat signals are created. In an unequivocal sort P-FF, the plans of heartbeat generator and lock are isolated. While trying to lessen power utilization in flip-slumps a low-power flip-flop (FF) plan including an express kind heartbeat activated structure and a changed genuine single stage clock lock dependent on a sign feed-through plan is introduced. The proposed plan effectively takes care of the long releasing way issue in customary express sort beat activated FF (P-FF) structures and accomplishes better speed and force execution. In light of post-format reproduction results utilizing TSMC CMOS 90-nm innovation, the proposed plan beats the traditional P-FF structure. The proposed structure includes the best force delay-item execution in both understood and unequivocal sort flip failures under correlation. Move registers can be planned utilizing such flip failure. Accordingly power utilization is diminished contrasted with customary techniques. Consequently the move registers planned with all these flip-flop structures likewise demonstrate that sign feed through plan is a superior low force structure [7][9].

Scientists introduced new strategies to assess the vitality and postponement of flip-failure and lock plans and shows none of the existing structure carry out well over the wide scope of working systems present in composite frameworks. In this paper, we show noteworthy vitality reserve funds when every TE case is chosen from a heterogeneous library of plans, each tuned to an alternate working system. We accumulate insights on TE action in a pipelined MIPS microchip running SPECint95 benchmarks and show that movement touchy TE choice can decrease all out TE vitality without expanding process duration. We propose the utilization of a choice of flip-failure and lock plans, each tuned for various actuation examples and speed necessities. This paper further shows strategy on MIPS processor information on SPECint95 benchmarks, where complete flip-failure and hook vitality by over 60% is decreased without expanding process duration [10].

## **III. Proposed Methodology**

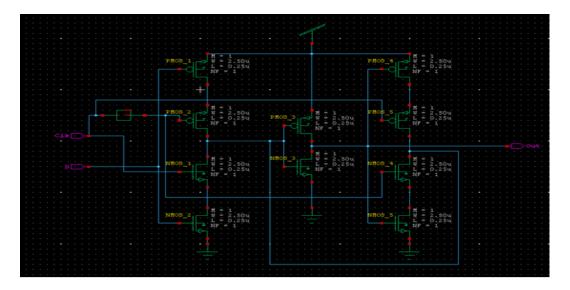

In spite of the fact that the execution of move registers utilizing static correlative beat hook and Transmission Gate Pulsed Latch tackled beat clock signal, the force utilization and the PDP couldn't be decreased. So the proposed strategy utilizes the flip-flops for planning the low force applications. This technique utilizes the PIPE rationale flip-flop for planning low force Universal move register and a 4-piece counter. Flip lemon utilizing pipe rationale is viewed as dependent on the correlation of intensity and zone with a few other flip-flops. So the proposed strategy gives the structure of low force Universal move register and a 4-piece counter utilizing PIPE rationale. The funnel rationale flip lemon utilizes around 10 transistors. Circuit outline of PIPE rationale flip failure is appeared in figure 2.

From the start, the beat clock signal CLK\_pulse invigorates the snare data T1 from Q4. Furthermore, a while later, the beat clock signals CLK\_pulse update the four lock data from Q4 toQ1 continuously. The locks Q2–Q4 get data from the commitment of the move register (IN). The assignments of the other sub move registers are equal to that of the sub move register beside that the fundamental lock gets data from the fleeting storing snare in the past sub move register.

International Journal of New Practices in Management and Engineering Volume 08 Issue 03 (2019)

## Fig 2: Circuit Schematic of pipe logic flip flop

The proposed move register diminishes the amount of delayed beat clock signals basically, yet it constructs the amount of secures perspective on the additional concise storing snares. Regardless of the way that the use of move registers using static correlative beat snare handled the arranging issue using various non-spread conceded beat clock signal and the power is being assessed. This beat lock utilizes around 12 transistors alongside the move registers and this may involve huge zone. So the move register with beat lock utilizing the diverse rationale with the diminished number of transistors is being proposed yet the activity of this proposed move register is like that of the recently structured move register. The proposed move register utilizes the Transmission Gate Pulsed Latch (TGPL).

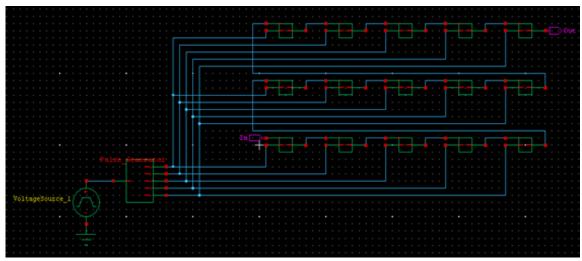

Fig 2: Circuit Schematic of proposed shift register

## **IV. Simulation Results**

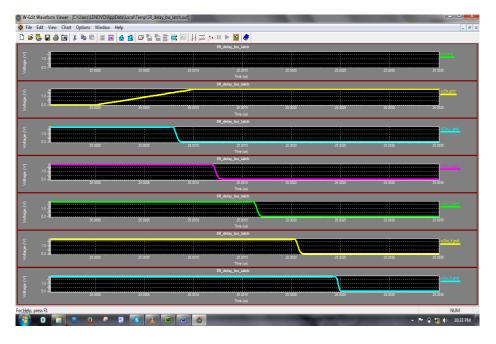

The structure cycle for the improvement of electronic circuits incorporates a significant pre-creation check stage. Due to the cost and time pressures related with the manufacture step, exact check is critical to effective plan. The job of EDA device is to help structure and confirm a circuit's activity by numerically explaining the differential conditions portraying the circuit. These reproduction results permit circuit fashioners to check and adjust plans before submitting them for creation. Twofold edge activating implies that a flip-flop reactions for both positive (0 to 1 change) and negative (1 to 0) edges brings about cutting the recurrence of the clock by one half . In this

ISSN: 2250-0839 © IJNPME 2019 paper the subsequent technique twofold edge activating is proposed to execute clock branch sharing-understood heartbeat (CBS\_ip) conspire flip-failure and make examination investigation with the current twofold edge activating flip-flops.

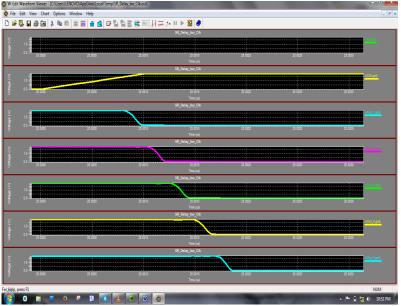

Fig 3: Simulation result of pipe logic flip flops

The flip-flops (FF) in the proposed move register are organized using clock branch-sharing certain beat scheme (CBS\_ip). The diverse existing twofold edge initiated flip-flops are transmission-entryway snare MUX, C2MOS Latch-MUX, Dual-edge transmission-passage beat lock (DE-TGPL). The essential part of the clock branch-sharing arrangement is to diminish the amount of checked transistors in the structure as differentiated and existing twofold edge enacting flip-flops. When diverged from the other top tier twofold edge enacted flip-flop structures, this CBS\_ip arrangement has an improvement in power usage and has less number of planned transistors and most insignificant power, it is sensible for tip top and low power circumstances.

Fig 4: Simulation result of proposed shift register

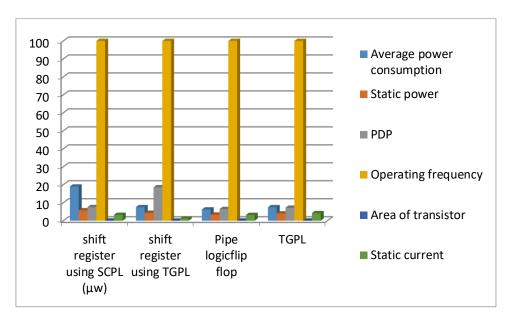

| Parameters                 | shift register<br>using SCPL<br>(µw) | shift register<br>using TGPL | Pipe logic<br>flip flop | TGPL     |

|----------------------------|--------------------------------------|------------------------------|-------------------------|----------|

| Average power              |                                      |                              |                         |          |

| consumption                | 19.02µw                              | 7.53 μw                      | 1.268 µw                | 0.502 μw |

| Static power               | 5.784mw                              | 0.404mw                      | 0.3856mw                | 0.0269mw |

| PDP                        | 7.6nws                               | 18.6nws                      | 0.506nws                | 1.24nws  |

| <b>Operating frequency</b> | 100MHz                               | 100MHz                       | 100MHz                  | 100MHz   |

| Area of transistor         | 0.075µm2                             | 0.031µm2                     | 0.075µm2                | 0.031µm2 |

| Static current             | 3.261µA                              | 1.21µA                       | 0.217µA                 | 0.080µA  |

The move register diminishes zone and power usage by superseding flip-flops with beat snares. The arranging issue between beat locks is settled using different non-spread delayed beat clock hails as opposed to a lone beat clock signal. Barely any the beat clock signals is used by sub shifter enlists and using extra temporary accumulating locks. In this paper, the zone capable move registers using SCPL and TGPL bases are organized and their ability is surveyed. In light of these structures the planning issue of the move registers is unravelled. Reproduction brings about 0.18- $\mu$ m CMOS innovation affirmed that the region of the proposed move register is diminished around half and the force utilization is additionally decreased.

Fig 4: Chart showing comparison of simulation results of proposed shift register

## V. Conclusion

In this paper, a profoundly productive flip failure configuration was proposed with less force utilization for low force applications. A fitting correlation was made between the proposed structure and scarcely any current plans like TGMS, MC2MOS flip failure, HLFF, Power PC 603, and SDFF for 4-piece counter and CDMFF, CPSFF, DETFF, MTCMOS, SCCER for USR. A near examination of PIPE rationale flip lemon at various clock frequencies was performed extending from 100 KHz to 500MHz. The proposed plan is actualized in a 4-piece counter and Universal move register in correlation with Power PC 603 flip failures and DETFF at 100 MHz and 500 MHZ. The outcomes show 30.2% improvement in PDP and 36.9% improvement in decreased normal force utilization for 4-piece counter and 33%. Improvement in decreased normal force utilization and 27% improvement in PDP for Universal move register .All the structures were mimicked utilizing Tanner 13.0 EDA 130nm CMOS

innovation with 1.8 V and contrasted and the proposed plan. The outcomes got from the proposed plan demonstrated that it is well appropriate for low force and elite applications.

#### References

- [1] Markovic D., Nikolic B., Brodersen R.W., Analysis and design of low-energy flip-flops, Proceeding of International Symposium on Low Power Electronics and Design, 2001, 6-7 Aug. 2001, Pages: 52 -55.

- [2] Renganayaki G, Jeyakumar.V, —Design of an Efficient Low power Shift Register using Double Edge Triggered Flip-flop, IEEE J. Solid-State Circuits, vol. Vol. 2, Issue 1, January 2014.

- [3] Yamasaki.H and Shibata.T, —A real-time image-feature-extraction and vector-generation vlsi employing arrayed-shift-register architecture, IEEE J. Solid-State Circuits, vol. 42, no. 9, pp. 2046– 2053, Sep. 2007.

- [4] Kim H.S, Yang J.H, S.-H. Park, S.-T. Ryu, and G.-H. Cho, —A 10-bit column-driver IC with parasiticinsensitive iterative charge-sharing based capacitor-string interpolation for mobile active-matrix LCDs, IEEE J. Solid-State Circuits, vol. 49, no. 3, pp. 766–782, Mar. 2014

- [5] Consoli.E, M. Alioto, G. Palumbo, and J. Rabaey, —Conditional push-pull pulsed latch with 726 fJ energy delay product in 65 nm CMOS, I in IEEE Int. Solid-State Circuits Conf. (ISSCC) Dig. Tech.Papers, Feb. 2012, pp. 482–483.

- [6] Saranya.M, V.Vijayakumar, T.Ravi, V.Kannan, —Design of Low Power Universal Shift Register, IEEE , Solid-State Circuits, Vol. 2 Issue 2, February 2013.

- [7] Reyes.P, P. Reviriego, J. A. Maestro, and O. Ruano, —New protection techniques against SEUs for moving average filters in a radiation environment, IEEE Trans. Nucl. Sci., vol. 54, no. 4, pp. 957–964, Aug.2007.

- [8] Partovi H., Burd R., Salim U., Weber F., DiGregorio L., Draper D., Flowthrough latch and edge-triggered flip-flop hybrid elements, Solid-State Circuits Conference, 1996. Digest of Technical Papers. 43rd ISSCC., 1996 IEEE International, 8-10 Feb. 1996, Pages: 138 -139

- [9] J. Shaikh and H. Rahaman, "High speed and low power preset-able modified TSPC D flip-flop design and performance comparison with TSPC D flip-flop," 2018 International Symposium on Devices, Circuits and Systems (ISDCS), Howrah, 2018, pp. 1-4, doi: 10.1109/ISDCS.2018.8379677.

- [10] M. Tsai, P. Kuo, J. Lin and M. Sheu, "An Ultra-low-power True Single-phase Clocking Flip-flop with Improved Hold time Variation using Logic Structure Reduction Scheme," 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, 2018, pp. 1-4, doi: 10.1109/ISCAS.2018.8350985.