# Leakage Power Minimization Using Gating Technique In FPGA Controlled Device

# Mr. Sagar Kothawade

Department of Electronics Engineering, VOGCE Atgaon India sagarkothawade99@gmail.com

| Article History                                                                                                                                                   | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Article Submission<br>27 September 2013<br>Revised Submission<br>27 October 2013<br>Article Accepted<br>25 November 2013<br>Article Published<br>31 December 2013 | FPGA based controlled devices are widely used in integrated chip sector provided<br>the power consumed by such devices should be low. Leakage power takes vital part<br>in contributing towards the total power consumption. This research work<br>concentrates in proposing a power gating technique based on look up table<br>approach. The novelty of this approach is that common look up tables are employed<br>for asynchronous architectures for each leaf node. Due to this the leakage power and<br>the total area overhead can be minimized. The proposed architecture is simulated<br>through M-Power analysis and simulator tool for leaf nodes and efficiently utilizes<br>H-tree methodology to minimize area. The reduction in number of look up tables<br>leads to 45% to 50% reduction in leakage power of FPGA device.<br><b>Keywords:</b> Leakage power, Fine grain gating, Look up table, Leaf node gating |  |  |  |

## I. Introduction

The VLSI and ULSI technologies are widely used for many applications like computer, digital camera, cellphones and etc. VLSI applications find eminence in the certain areas of research and development. These areas are system specification, design and partitioning, wafer level integration and neural frame architectures [1][2]. Due to this wide application of VLSI components, power consumption of these devices is an important criterion to be considered. Power consumption is broadly classified as static and dynamic power consumption due to the charging and discharging process occurring in the load capacitances. Leakage current is contributed by threshold and junction current which forms the major percentage of leakage current. This leakage current widely increases with increase in the scaling dimension of the transistors [3].

Historically, most CMOS designs are executed with  $V_{dd}$  much more than  $V_{th}$ . If  $V_{dd}=5V$ , then the threshold voltage must be greater than 700mV [4]. The leakage power also comprises of active leakage current and standby leakage current. The leakage power optimization shall also be concentrated on active and sleep mode leakage power. During standby mode, the unwanted power consumption did by circuit blocks that are inactive on temporary basis is to be eradicated by sleep states [5].

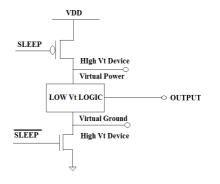

The sleep transistor strategy is commonly used Application Specific Integrated Circuits (ASIC) domain. The dynamic threshold voltage adjustment is also preferred to reduce leakage power [6]. Multi-threshold approaches also find its importance in reduction of leakage power in FPGA. Another dedicated approach is the use of stacked transistors in series instead of individual transistors may also reduce leakage power. Such sleep transistor is shown in figure 1.

Fig.1: Sleep transistor circuit

The sleep transistor reduces the sub-threshold leakage current in peripheral circuits through sleep mode. Various sleep modes are in practice in case of non-volatile FPGA's. The sleep transistor is actually connected between actual ground and circuital ground [7].

#### **II. Existing Methods**

Two existing approaches such as zig zag power gating and individual LUT based logic blocks are discussed in this section.

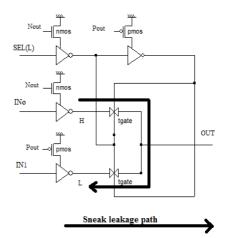

#### A. Zig-Zag Power Gating

CMOS circuits like inverter and logic gates needs straight forward implementation of zig zag power gating. Implementation of such power gating circuits in transmission gate interfaces leads to sneak oriented leakage and area overhead problems [8]. The zig zag power gating method is shown in figure 2.

Fig.2: Sneak leakage problem path

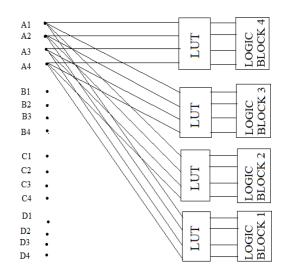

#### B. Individual LUT Based Logic Blocks

According to this method for every logic blocks a look up table is set. The logic block for the given expression is activated only by decision made by the look up table is set. If thousand logic blocks is present means thousand LUT table is needed [9]. It consumes particular amount of power and circuit complexity and area overhead also increased. To reduce the large number of LUT, fine grain based logic blocks introduces common LUT for k number of logic blocks. In this method number of LUT is reduced. So power and circuit complexity also minimized. In our method 65nm CMOS processor is utilized [10].

Fig.3: Block Diagram of Individual LUT base logic blocks

## **III. Proposed Method**

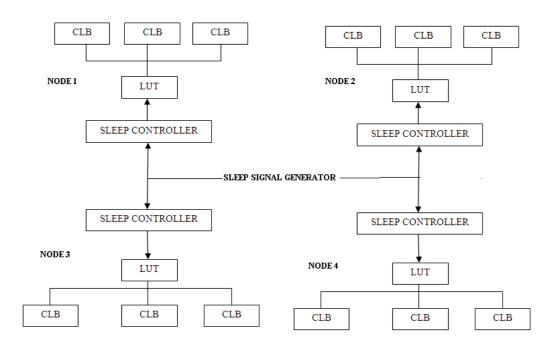

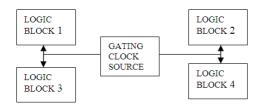

Our proposed method implements a novel LUT based fine grain power gating which will reduce the number of LUT by using a single LUT as common. A single LUT has to manage more number of logic blocks. The number of logic blocks per LUT will depend upon the number of I/P combination. An FPGA k-LUT is comprised of k- input signals which select single output from single input bit. For example 3 I/P signal and 1 enable signal means we can connect 16 logic blocks for that LUT. The proposed block is shown in fig.4.

Fig.4: Block diagram for proposed method

To activate the logic blocks a sleep signal acts as an enable signal. The sleep signal is distributed through H tree. Control signal is distributed to each leaf nodes which should activate the logic blocks. The structure of H-tree is shown in figure 5.

Fig.5: Block Diagram of H Tree

The sleep transistor is used to reduce the leakage power in FPGA circuits. It is an effective way to reduce the leakage of a transistor. It is identified that the sleep transistor itself consume a large leakage power and it is avoided by utilizing a single sleep controller for each leaf node logic blocks. Sleep control signal is selected and distributed through LUT. Look Up Tables (LUT) are the used in FPGAs to select the action of logic blocks. The function of LUT for three inputs is shown in table.1

Table.1.Truth table for 3 input LUT

| В | С                     | $\mathbf{X} = \mathbf{A}\mathbf{B} + \mathbf{B}\mathbf{C}$ |

|---|-----------------------|------------------------------------------------------------|

| 0 | 0                     | 0                                                          |

| 0 | 1                     | 1                                                          |

| 1 | 0                     | 0                                                          |

| 1 | 1                     | 0                                                          |

| 0 | 0                     | 0                                                          |

| 0 | 1                     | 1                                                          |

| 1 | 0                     | 1                                                          |

| 1 | 1                     | 1                                                          |

|   | 0<br>0<br>1<br>1<br>0 | 0 0<br>0 1<br>1 0<br>1 1<br>0 0<br>0 1                     |

#### IV. Simulation Results, Comparison and Optimization

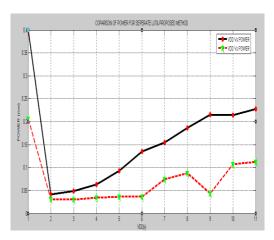

A four node logic block circuit leakage of power was analyzed references and obtains the power consumption for a 5V input using microwind for conventional LUT and LUT based circuits. The table.2 shows the power consumption for their corresponding vdd's for conventional power gating. Similarly table.3 shows the power consumption for fine grain based logic blocks. The figure.6 represents power consumption variations for both the techniques. By simulating our proposed system the power consumption is reduced by 32% to conventional power gating system. Power dissipation for individual LUT/ conventional LUT/ LUT base fine grain method comparison of different methods is shown in figure 6.

Fig.6: Power dissipation for individual LUT/ conventional LUT/ LUT base fine grain method comparison of different methods.

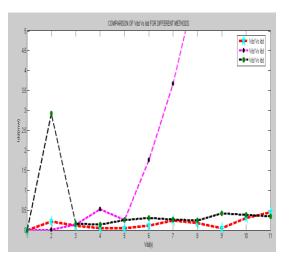

ISSN: 2250-0839 © IJNPME 2013 The figure.6 represents power consumption variations for both the techniques. By simulating our proposed system the power consumption is reduced by 53.9% to separate LUT system. The power comparison of the LUT and conventional power gating are tabulated and the comparison is shown in the graph. In the graph Blue color line indicates the power consumption of non-LUT based logic blocks and red line indicates individual LUT based logic blocks and black line indicates fine grain LUT based logic blocks. The simulation is carried out for 65µm CMOS processor and the results are compared with previous methods. The whole simulation is carried out in M Power simulation and results are shown in table 2. The Idd for their corresponding vdd's for conventional power gating. Similarly table.6 shows the power consumption for fine grain based logic blocks. The figure.10 represents power consumption variations for both the techniques. By simulating our proposed system the power consumption is reduced by 33% to separate LUT system and is shown in figure 7

Fig.7: Idd comparison of individual LUT

| Table.2. power | dissipation | of different | t methods |

|----------------|-------------|--------------|-----------|

|----------------|-------------|--------------|-----------|

| METHODS                                          | POWER CONSUMPTION OF NODES |         |         |

|--------------------------------------------------|----------------------------|---------|---------|

|                                                  | 2 NODE                     | 3 NODE  | 4 NODE  |

| Leaf Nodes For Conventional Power Gating         | 17.31mW                    | 24.4mW  | 34.62mW |

| Leaf Nodes For Individual LUT Based Logic Blocks | 0.16mW                     | 0.27mW  | 0.39mW  |

| Leaf Nodes For Fine Grain Based Logic Blocks     | 0.076mW                    | 0.122mW | 0.167mW |

The Idd comparison of the LUT and conventional power gating are tabulated and the comparison is shown in the graph. In the graph pink color line indicates the Idd consumption of conventional power gating based logic blocks and black line indicates individual LUT based logic blocks and red line indicates fine grain LUT based logic blocks.

## V. Conclusion

This research article examined the relations that exist between configurable logic blocks and LUT reconfiguration of FPGA. The number of LUT reduction in each node leads to reduction in leakage power to considerable amount. This paper also made analysis in area reduction for logical blocks by the usage of minimum controller. In addition to fine grained gating network Idd current also reduced to considerable amount in logic blocks. Our proposed method simulation shows that the total leakage power is reduced to about 40% - 50% with little area overhead.

# References

- [1] Shota Ishihara, Student Member, IEEE, Masanori Hariyama, Member, IEEE, and Michitaka Kameyama, Fellow, IEEE "A Low-Power FPGA Based on Autonomous Fine-Grain Power Gating" IEEE transactions on very large scale integration systems, vol. 19, no. 8, august 2011

- [2] Andy Gean Ye, (2010), "Using the Minimum Set of Input Combinations to Minimize the Area of Local Routing Networks in Logic Clusters Containing Logically Equivalent I/Os in FPGAs", IEEE TRANSACTIONS ON VLSI SYSTEMS, VOL. 18, NO. 1.

- [3] Mingjie Lin and Abbas El Gamal,( 2009), "A Low-Power Field-Programmable Gate Array Routing Fabric", IEEE VLSI SYSTEMS, VOL. 17, NO. 10.

- [4] M. Hariyama, S. Ishihara, and M. Kameyama, (2008), "Evaluation of a field programmable VLSI based on an asynchronous bit- serial architecture," IEICE Trans .Electron, vol. E91-C, no. 9, pp. 1419–1426.

- [5] Y. Ahmed, A. Mohab, and E. Mohamed, (2008), "A comparative study between static and dynamic sleep signal generation techniques leakage tolerant designs," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 16, no. 9, pp. 1114–1126.

- [6] T. Tuan, S. Kao, A. Rahman, S. Das, and S. Trimberger, (2006), "A 90 nm low- power FPGA for battery-powered applications," in Proc.FPGA, pp. 22–24.

- [7] F. Li, Y. Lin, L. He, and J. Cong, "Low- power FPGA using pre-defined dual-Vdd/dual-Vt fabrics," in Proc. 2004 ACM/SIGDA 12th Int. Symp. Field-Programmable Gate Arrays, 2004, pp. 42–50.

- [8] J. H. Anderson, F. N. Najm, and T. Tuan, "Active leakage power optimization for FPGAs," in Proc. ACM Intl. Symp. Field-Programmable Gate Arrays, Februray 2004.

- [9] N. Gupta, "Thermal analysis of energy efficient clock gated arithmetic logic unit on FPGA," 2014 International Conference on Control, Instrumentation, Communication and Computational Technologies (ICCICCT), Kanyakumari, 2014, pp. 990-993.

- [10] S. Chtourou, M. Abid, Z. Marrakchi and H. Mehrez, "Power consumption analysis for mesh based FPGA," 2014 9th IEEE International Conference on Design & Technology of Integrated Systems in Nanoscale Era (DTIS), Santorini, 2014, pp. 1-5.

- [11] Prof. Naveen Jain. (2013). FPGA Implementation of Hardware Architecture for H264/AV Codec Standards. International Journal of New Practices in Management and Engineering, 2(01), 01 - 07. Retrieved from http://ijnpme.org/index.php/IJNPME/article/view/11

- [12] Dr. Bhushan Bandre. (2013). Design and Analysis of Low Power Energy Efficient Braun Multiplier. International Journal of New Practices in Management and Engineering, 2(01), 08 - 16. Retrieved from http://ijnpme.org/index.php/IJNPME/article/view/12

- [13] Mr. Dharmesh Dhabliya. (2012). Intelligent Banal type INS based Wassily chair (INSW). International Journal of New Practices in Management and Engineering, 1(01), 01 - 08. Retrieved from http://ijnpme.org/index.php/IJNPME/article/view/2

- [14] Mr. Dharmesh Dhabliya, Mr. Rahul Sharma. (2012). Efficient Cluster Formation Protocol in WSN. International Journal of New Practices in Management and Engineering, 1(03), 08 - 17. Retrieved from http://ijnpme.org/index.php/IJNPME/article/view/7