# Design and Analysis of Low Power Energy Efficient Braun Multiplier

### Dr. Bhushan Bandre

Department of Computer Science and Engineering bhushan.bandre47@gmail.com

#### Article History

Article Submission

20 October 2012

Revised Submission

2 January 2012

Article Accepted

15 February 2012

Article Published

31st March 2013

#### Abstract

Designing of Braun multipliers using various hybrid full adder circuits are described in this paper. In DSP and communication systems, multipliers are the main power consuming elements. Dynamic power dissipation contributes a lot to power consumption in CMOS logic. Braun multipliers employing Row bypassing techniques are designed to minimise the switching activities which aids in reducing dynamic power consumption. Full adders constitute a most vital part in multipliers. In this paper, Braun multiplier is designed using three different hybrid full adders .Area and power consumption of the resulting circuits are compared and analysed. The Braun multipliers are implemented and simulated using Tanner spice.

Keywords: Conventional Braun multiplier, Full adder, Carry save adder.

#### I. Introduction

Multiplication act as vital task in ALU unit and control the finishing time of almost all DSP algorithms. Instruction cycle of a Digital Signal Processing chip is mainly determined by multiplication time. A digital multiplier circuit multiplies an N bit multiplicand to N bit binary multiplier. A digital multiplier consists of a plurality of AND gates. These AND gates are used to multiply each digit of multiplicand to each digit of the multiplier and outputs of the AND gates represent the partial products that are then arranged corresponding to each digit of the multiplier. The multiplier also contains a plurality of 1's counter to receive all the partial products in parallel except the least significant digit of the multiplier. The most important type of the multiplier is parallel multiplier which is used to carry away elevated speed mathematical actions. Power consumption plays a vital role in the performance of these circuits [1]. So Braun multipliers employing row bypassing technique is used in order to decrease the dynamic power consumption. Full adders in this Braun multiplier are replaced by Radha Krishnan adder, Chang adder, Agarwal adder and their area and power consumption are compared and analyzed.

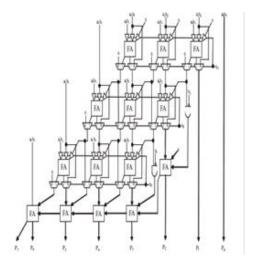

# II. Conventional Braun Multiplier

This multiplier is termed as carry save array multiplier which performs multiplication of two unsigned bits. An nXn Braun multiplier necessitates nX(n-1) adders and  $n^2$  AND gates. Products can be generated parallel using the AND gates. The partial product can be added to the computation of partial product that is formed by the lineup of adders. The carry out is shifted one bit to the left side or right side. Further, it will be summated to the sum that is produced by the  $1^{st}$  adder and the newly spawned partial product. The shifting would happen because of Carry save adder and the ripple carry adder is employed for the final stage output [2].

### Mathematical analysis [4]:

Consider a generic mXn multiplication of two un-signed n-bit numbers Y=Y<sub>m</sub>-1...Y<sub>0</sub> and X=X<sub>n</sub>-1...X<sub>0</sub>.

$$Y = \sum_{i=0}^{m-1} Y_i 2^i$$

$$X = \sum_{i=0}^{n-1} X_i 2^i$$

The product P can be written as follows:

$$P = \sum_{i=0}^{m-1} \sum_{j=0}^{n-1} (Y_i X_j) 2^{i+j}$$

$$A = a_3 \quad a_2 \quad a_1 \quad a_0$$

$$\times \quad B = \quad b_3 \quad b_2 \quad b_1 \quad b_0$$

$$a_3b_0 \quad a_2b_0 \quad a_1b_0 \quad a_0b_0$$

$$a_3b_1 \quad a_2b_1 \quad a_1b_1 \quad a_0b_1$$

$$a_3b_2 \quad a_2b_2 \quad a_1b_2 \quad a_0b_2$$

$$a_3b_3 \quad a_2b_3 \quad a_1b_3 \quad a_0b_3$$

$$P_7 \quad P_6 \quad P_5 \quad P_4 \quad P_3 \quad P_2 \quad P_1 \quad P_0$$

Fig 1: Braun multiplication algorithm

Reduction of switching power consumption is achieved by row by-passing technique which immobilize the operation in selected rows [3]. The components used in braun multiplier with row bypassing are full adders, multiplexers, tri state buffer and AND gates. The multiplexer's select full adder output and by-pass signal. Tristate buffer serve as input gating when by-passing. For example if a bit b2 of figure is zero then the output from the second CSA are fed directly to fourth CSA row and the third CSA row is disabled which in turn reduces the power due to switching of third row. The addition function in the j<sup>th</sup> row is disabled if the bit b<sub>i</sub> in the multiplier is zero.

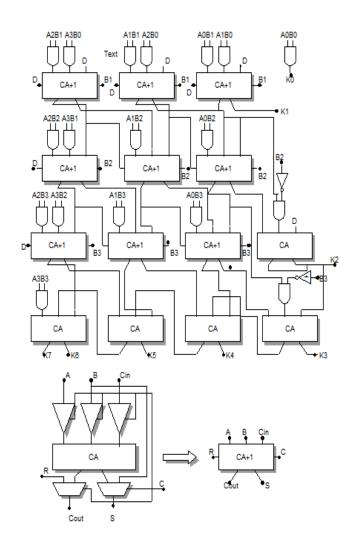

Fig 2: Conventional Braun multiplier

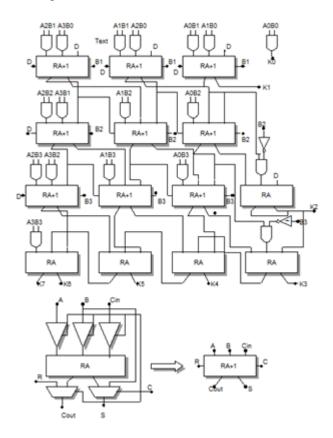

# III. Proposed Braun Multiplier I

Proposed Braun Multiplier I has only six transistors for the XOR-XNOR cell. This leads to operational reliability when the supply voltage is scaled down. The total number of transistor for full adder is twenty two. [5] Using this adder circuit Braun multiplier is implemented.

Fig 3: Proposed Braun multiplier I

Fig 4: Waveform for Proposed Braun multiplier I

# IV. Proposed Braun Multiplier II

Proposed Braun Multiplier II uses 26 transistors and it exploit a modified XOR/XNOR circuit. In the below circuit worst case delay harms because of less logical transitions due to adding up of more transistors. The extra transistors increase the power expenditure of the full adder cell [5]. Using this adder Braun multiplier is implemented.

## V. Proposed Braun Multiplier III

Proposed Braun Multiplier III It uses CPL and this multiplier comprising of various adders is made by NMOS transistors and pull-up PMOS transistors to acquire full swing output voltage. Because of positive feedback and NMOS transistors, the circuit is intrinsically fast. This adder contains a well-balanced construction with esteem to generate sum and carry signals [5]. Using this adder Braun multiplier is implemented.

11

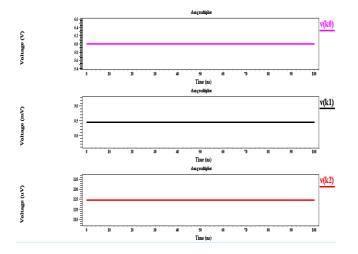

Fig 5: Proposed Braun multiplier II

Fig 6: Waveform for Proposed Braun multiplier II

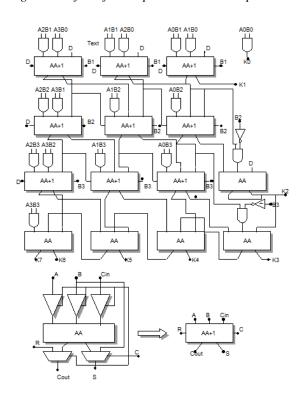

Fig 7: Proposed Braun multiplier III

Fig 8: Waveform for Proposed Braun multiplier III

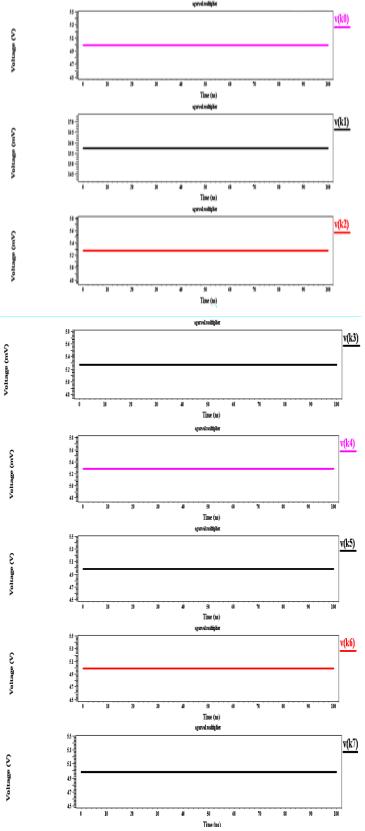

#### VI. Results and Discussions

The Braun multiplier shown in Figure 2 is used with the different adders and the results obtained are listed in table I and table II. Depending on the number of transistors required for designing these multipliers, area is calculated and power consumption for different multipliers are compared in the table II.

Table 1. Area comparison of Multiplier

| S.No | Multiplier                    | No. of transistors |

|------|-------------------------------|--------------------|

| 1.   | Proposed Braun multiplier I   | 740                |

| 2.   | Proposed Braun multiplier II  | 796                |

| 3.   | Proposed Braun multiplier III | 1020               |

Table2I. Power comparison of Multiplier

| S.No | Multiplier                       | Maximum power (watts) | Minimum power (watts) | Average power (watts) |

|------|----------------------------------|-----------------------|-----------------------|-----------------------|

| 1.   | Proposed Braun multiplier I      | 4.172837e-003         | 4.172837e-003         | 2.086419e+004         |

| 2.   | Proposed Braun multiplier II     | 2.860289e-002         | 2.860289e-002         | 1.430145e+005         |

| 3.   | Proposed Braun multiplier<br>III | 1.012971e-004         | 1.012971e-004         | 5.064855e+002         |

## VII. Conclusion

This paper, has proposed a methodology to implement a Braun multiplier using different hybrid full adders .The results of Proposed Braun multiplier-I, Proposed Braun multiplier-II and multiplier-III are compared. Power consumption gets reduced when Braun multipliers are designed with different adders like Agarwal adder, Radhakrishnan adder and Chang adder. But for Agarwal adder based Braun multiplier, area is increased when compared to the other Braun multipliers. Thus in CMOS logic, a limitation can be imposed only on one issue. Here power is the factor that is limited with increase in area and time remaining constant

### References

Candy Goyal and Gazal Preet kaur, "Comparative Analysis of Low Power 4-bit Multipliers Using 120nm CMOS Technology", International Journal of Engineering Research and Applications, Vol. 2, Issue 4, July-August 2012.

15 © IJNPME 2013

ISSN: 2250-0839

- [2] Anitha and Bagyaveereswaran, "Braun's Multiplier Implementation using FPGA with Bypassing Techniques", International Journal of VLSI design & Communication Systems (VLSICS) Vol.2, No.3, September 2011.

- [3] Usha G.Chavan," Optimized multiplier using bypass technique", Department of Electronics Engineering, G.H.R.C.E, Nagpur, The International Journal of Computer Science & Applications, Volume 1, No. 2, April 2012 ISSN 2278-1080.

- [4] Mohammed H. Al Mijalli,"Braun's Multipliers: A Delay Study", Proceedings of the World Congress on Engineering 2012, Vol II, WCE 2012, July 4 6, 2012, London, U.K.

- [5] Rajkumar Sarma and Veerati Raju,"Design and Performance analysis of hybrid adders for high speed arithmetic circuit", Department of VLSI,Lovely Professional University,Punjab, International Journal of VLSI design & Communication Systems (VLSICS), Vol.3, No.3, June 2012.

- [6] V. Kunchigi, L. Kulkarni and S. Kulkarni, "High speed and area efficient vedic multiplier," 2012 International Conference on Devices, Circuits and Systems (ICDCS), Coimbatore, 2012, pp. 360-364.

- [7] Zhijun Huang, Miloš D. Ercegovac, "High-Performance Lefl-to-Right Array Multiplier Design," arith, pp.4, 16th IEEE Symposium on Computer Arithmetic (ARITH-16'03), 2003

- [8] Ramalatha, M Dayalan, K D Dharani, P Priya, and S Deborah, "High speed energy efficient ALU design using Vedic multiplication techniques", ICACTEA, 2009. pp. 600-3, Jul 15-17, 2009

- [9] H Thapliyal, M B Srinivas, and H R Arabnia, "Design and Analysis of a VLSI Based High Performance Low Power Parallel Square Architecture", in Proc. Int. Conf. Algo. Math. Compo Sc., Las Vegas, pp. 72-6, Jun. 2005.