# Vedic Multiplier Implementation for High Speed Factorial Computation

## Prof. Sharayu Waghmare

Department of Computer Engineering, Bapurao Deshmukh College of Engineering Wardha India sharayuwaghmare110@gmail.com

| Article History                                                                                                                                                            | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article Submission<br>12 August 2012<br>Revised Submission<br>7 October 2012<br>Article Accepted<br>5 November 2012<br>Article Published<br>31 <sup>st</sup> December 2012 | Vedic Mathematics arise from the prehistoric classification of Indian mathematics<br>that was recreated by Tirthaji. Ancient mathematical operations are depending on<br>sixteen methods. In this article, a new VLSI architecture to compute factorial of the<br>given number with Vedic based multiplier is proposed. Simulations are performed<br>using Xilinx ISE 14.2. Effective comparative analysis is made with existing<br>multipliers to prove the momentous development in competence and high speed<br>operation. This efficient multiplier is implemented in the proposed factorial<br>architecture which significantly reduces the path delay and provides better<br>optimization.<br><b>Keywords:</b> VLSI Architecture, Multiplication, Vedic Mathematics, Factorial<br>Calculations. |

## I. Introduction

Multipliers acts as heart of Microprocessors, Digital Signal Processors and high end communication oriented processors with sophisticated operational units. Adders plays a vital role in construction of high speed multipliers which are used to compute partial products. The necessity of high speed multipliers is directly proportional to the demand of real time processors for modern day operations. Dealing with reduced delay and power parameters are essential for domestic and industrial applications. Machine based multiplication is combination of addition and shifting operations [1].

Urdhava Tiryakbhyam Sutra is a method through which partial products are calculated in parallel which reduces the computation time there by enhancing its efficiency [4]. Conventional factorial results are compared with our proposed factorial architecture which has the efficient multiplier as one of its module which provides optimization in terms of speed and efficiency. When dealing with combinations and permutations (when dealing with probabilities), the importance of factorial is more [5].

## **II. Vedic Multiplication**

U. Tiryakbhyam Sutra from vedic mathematics is used to perform multiplication in a faster way which means 'vertical as well as crosswise'. The steps concerned in the Urdhava Tiryakbhyam Sutra are as follows:

STEP1: It has n-bit Vedic multiplication unit.STEP2: It has Partial products and carry.STEP3: It has adders and the results of multiplication.

Consider a pair of two bit numbers such as a0a1 and b0b1. Multiplication process is as follows. The process of multiplication is shown in figure 1 and steps is shown in figure 2.

International Journal of New Practices in Management and Engineering Volume 01 Issue 04 (2012)

Fig.1 Multiplication of 252x846 (decimal)

Fig.2 Steps in Multiplication of 252x846 (decimals)

#### III. Proposed Model of UT Multiplier to Calculate Factorial

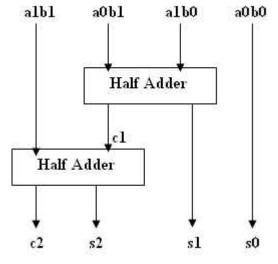

The architecture [2]-[3] shown in fig.1 is similar to conventional multiplier. Let's consider 2 bit numbers such as A = a1a0 and next B = b1b0. The 2X2 VM module is premeditated using 4 AND gates and two half-adders. Architecture is as follows:

Fig.3. Architecture of 2x2 Vedic Multiplier

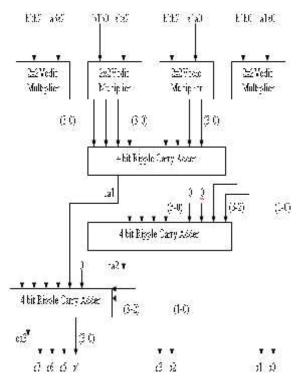

ISSN: 2250-0839 © IJNPME 2012 With the four 2x2 bit VM modules, 4X4 VM is deployed in fig. 4. Let's consider a pair of 4-bit as A and B, say A=a3a2a1a0 & B=b3b2 b1 b0. The resultant product is 8-bit- s7s6s5s4s3s2s1s0 .Architecture of 4X4 VM is shown in figure 4.

Fig.4. Block of 4x4 Vedic Multiplier

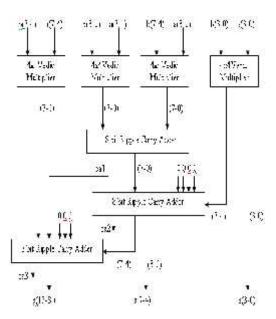

With the four 4x4 bit VM modules, 8X8 VM is deployed in fig. 5. Let's consider a pair of 8-bit as A and B. The resultant product is 16-bit–s15 to s0. Architecture of 8X8 Vedic multiplier is exposed in figure 5.

Fig.5. obstruct of 8x8 Vedic Multiplier

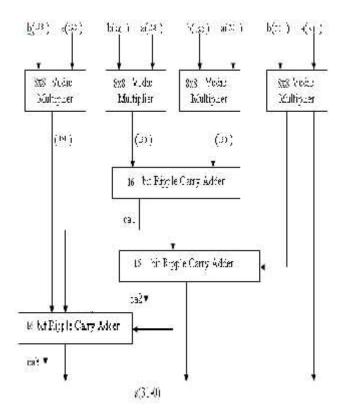

ISSN: 2250-0839 © IJNPME 2012 With the four 8x8 bit VM modules, 16X16 VM is deployed in fig. 6. Let's consider a pair of 16-bit as A & B. The resultant product is 32-bit–s31 to s0 .Architecture of 16X16 VM is shown in figure 6.

Fig.6. structural design of 16x16 Vedic multiplier

## **IV. Proposed Architecture of Factorial Computation**

Factorial is the product of integers from 1 to n inclusive. The formula used to calculate the factorial is as follows:

Factorial of a number

$$= (n)(n-1)(n-2)$$

Example: 4! Can be computed as follows:

$\begin{array}{ll} 4! & = (4)x(4-1)x(4-2)x(4-3) \\ & = 4x3x2x1 \\ 4! & = 24 \end{array}$

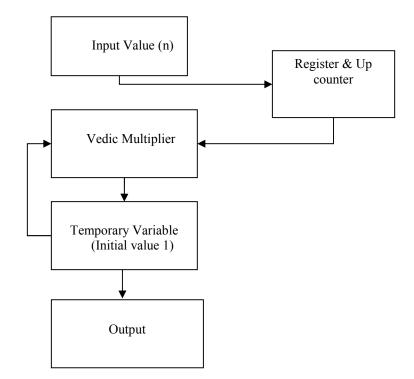

We have used the efficient multiplier as one of the module to calculate the factorial of a number. The VM 16 bit multiplier is used to compute the factorial value. The architecture is explained as follows: First the number whose factorial to be computed is given as input 'n'. The value of 'n' is stored in a memory. Up counter performs counting operation until its value reaches n. The output of up counter and temporary variable is repeatedly multiply up to n times. The architecture is shown in figure 7.

Fig.7. Block Diagram of Vedic Multiplier based Factorial Calculation

Simulations of the proposed design were conducted in the Xilinx ISE 14.2 design environment. The fig 8 & 9 demonstrate the simulation results of 8 bit and 16 bit Vedic multiplier. Figure 10 shows the experimental results of factorial calculation using Vedic Multiplier.

| Name      | Value | 1,999,990 ps 1,959,959 ps |

|-----------|-------|---------------------------|

| 🕨 🕨 a[7   | 99    | 99                        |

| 📕 🕨 📲 b[7 | 126   | 126                       |

| ) 🕨 😽 o[1 | 12474 | 12474                     |

|           |       |                           |

Fig. 8. Results-8x8 Vedic multiplier

| 50    | Name            | Value    | 1,995,998 pc 1,599,995 pc |  |

|-------|-----------------|----------|---------------------------|--|

| 82    | 🕨 🎽 a[15:0]     | 1025     | 1023                      |  |

| 1     | 🕨 🌃 b(1540)     | 12000    | 12000                     |  |

| 0     | ▶ 📲 0,31x]      | 13276000 | 12275000                  |  |

| 1.110 | (2).500 - 00-00 |          |                           |  |

Fig.9. results-16x16 Vedic multiplier

| Name    | Value         | 2,999,994 ns 2,999,995 ns 12,999,998 ns |

|---------|---------------|-----------------------------------------|

| 😤 🔥 🖬   | 1001          | 1201                                    |

| 🦉 Մելու | 1011010010011 | 101100010011000000                      |

| 12      |               |                                         |

Fig. 10. Results-Factorial Calculation

Table 1 depicts the comparative analysis of Vedic multiplier with conventional array multiplier for 8 and 16 bit, the synthesized results shows that VM outperforms in terms of delay compared to conventional multiplier.

| Multipliers                      | Number of<br>LUT's | Delay<br>(ns) |

|----------------------------------|--------------------|---------------|

| Conventional Multiplier<br>8x8   | 114                | 30.059        |

| Conventional Multiplier<br>16x16 | 506                | 59.156        |

| 8x8 Vedic Multiplier             | 115                | 28.629        |

| 16X16 Vedic Multiplier           | 510                | 55.037        |

|                      | A 1 · 1 /        | $\alpha  :  1$ | 1 17 1. 14 1 1.      |

|----------------------|------------------|----------------|----------------------|

| Table I: Performance | Analysis between | Conventional a | and Vedic Multiplier |

#### V. Conclusion

The 2X2 VM module is designed using 4 number logic AND gates and 2 circuit based half adders. With the four number of 2x2 bit Vedic multiplier modules, 4X4 VM is deployed. With the four 8x8 bit Vedic multiplier modules, 16X16 VM is deployed. We have used the efficient multiplier as one of the module to calculate the factorial of a number. The VM 16 bit multiplier is used to compute the factorial value. The synthesized results shows that VM outperforms in delay compared to conventional multiplier. Using Vedic multiplication to calculate factorial is the better way to obtain optimized path delay and efficiency.

#### References

- Pushpalata Verma, K. K. Mehta, "Implementation of an Efficient Multiplier based on Vedic Mathematics Using EDA Tool "International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-1, Issue-5, June 2012.

- [2] Aniruddha Kanhe, Shishir Kumar Das and Ankit Kumar Singh, "Design and Implementation of Low Power Multiplier Using Vedic Multiplication Technique", (IJCSC) International Journal of Computer Science and Communication Vol. 3, No. 1, pp. 131-132, January-June 2012.

- [3] S.S.Kerur, Prakash Narchi, Jayashree C N, Harish M Kittur and Girish V A "Implementation of Vedic Multiplier For Digital Signal Processing" International conference on VLSI communication & instrumentation (ICVCI), 2011.

- [4] Sumita Vaidya and Deepak Dandekar, "Delay-Power Performance comparison of Multipliers in VLSI Circuit Design", International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, pp. 47-56, July 2010.

- [5] Ramalatha, M.Dayalan, K D Dharani, P Priya, and S Deoborah, "High Speed Energy Efficient ALU Design using Vedic Multiplication Techniques", International Conference on Advances in Computational Tools for Engineering Applications (ACTEA) IEEE, pp. 600-603, July 15-17, 2009.

- [6] P. Gulati, H. Yadav and M. K. Taleja, "Implementation of an efficient multiplier using the vedic multiplication algorithm," 2016 International Conference on Computing, Communication and Automation (ICCCA), Noida, 2016, pp. 1440-1443.

- [7] Kanhe Aniruddha, Shishir Kumar Das, Ankit Kumar Singh, "Design and implementation of low power multiplier using vedic multiplication technique", *International Journal of Computer Science and Communication*, vol. 3, no. 1, pp. 131-132, 2012

- [8] Shamim Akhter, VHDL Implementation of Fast NxN Multiplier Based on Vedic Mathematic, IEEE, 2007.