## University of Massachusetts Amherst

## ScholarWorks@UMass Amherst

**Doctoral Dissertations**

Dissertations and Theses

March 2022

## Silicon Germanium BiCMOS Integrated Circuits for Scalable **Cryogenic Sensing Applications**

Mohsen Hosseini University of Massachusetts Amherst

Follow this and additional works at: https://scholarworks.umass.edu/dissertations\_2

Part of the Electrical and Electronics Commons

#### **Recommended Citation**

Hosseini, Mohsen, "Silicon Germanium BiCMOS Integrated Circuits for Scalable Cryogenic Sensing Applications" (2022). Doctoral Dissertations. 2406.

https://doi.org/10.7275/27245161 https://scholarworks.umass.edu/dissertations\_2/2406

This Open Access Dissertation is brought to you for free and open access by the Dissertations and Theses at ScholarWorks@UMass Amherst. It has been accepted for inclusion in Doctoral Dissertations by an authorized administrator of ScholarWorks@UMass Amherst. For more information, please contact scholarworks@library.umass.edu.

# SILICON GERMANIUM BICMOS INTEGRATED CIRCUITS FOR SCALABLE CRYOGENIC SENSING APPLICATIONS

A Dissertation Presented

by

MOHSEN HOSSEINI

Submitted to the Graduate School of the University of Massachusetts Amherst in partial fulfillment of the requirements for the degree of

DOCTOR OF PHILOSOPHY

February2022

Electrical and Computer Engineering

© Copyright by MOHSEN HOSSEINI 2022

All Rights Reserved

# SILICON GERMANIUM BICMOS INTEGRATED CIRCUITS FOR SCALABLE CRYOGENIC SENSING APPLICATIONS

A Dissertation Presented by MOHSEN HOSSEINI

| Approved as to style and content by: |

|--------------------------------------|

|                                      |

| Joseph C. Bardin, Chair              |

|                                      |

| Robert W. Jackson, Member            |

|                                      |

| S. Raman, Member                     |

|                                      |

| Grant W. Wilson, Member              |

Christopher V. Hollot, Department Chair Electrical and Computer Engineering

## ACKNOWLEDGMENTS

First, I greatly appreciate Prof. Joseph Bardin for giving me an opportunity to work as a Ph.D. student under his supervision, and of course, for his fantastic support and advice in each step of my studies.

I would also like to thank my Ph.D. committee members, Prof. S. Raman, Prof. G. Wilson, and Prof. R. Jackson, for their valuable feedback on my work.

I am thankful to all of my colleagues at Quantum RF group of UMASS for their helps in the previous five years.

I would like to thank the TolTEC team for providing valuable feedback in weekly meetings.

I want to thank Holger Rucker from IHP Microelectronics, Alvin Joseph and Nigel Cave from Global Foundries, and Tower Semiconductor for providing wafers for modeling and fabricating the chips.

Finally, I should appreciate National Science Foundation (NSF), Defense Advanced Research Project Agency (DARPA), National Aeronautics and Space Administration (NASA), and Jet Propulsion Laboratory (JPL), California Institute of Technology for partially supporting my work by grants AST-1636621 and N0014-20-1-4004, respectively.

## ABSTRACT

## SILICON GERMANIUM BICMOS INTEGRATED CIRCUITS FOR SCALABLE CRYOGENIC SENSING APPLICATIONS

#### FEBRUARY 2022

### MOHSEN HOSSEINI

B.Sc., SHARIF UNIVERSITY OF TECHNOLOGY

M.Sc., SHARIF UNIVERSITY OF TECHNOLOGY

Ph.D., UNIVERSITY OF MASSACHUSETTS AMHERST

Directed by: Professor Joseph C. Bardin

This dissertation is focused on an investigation of BiCMOS cryogenic low noise amplifiers (LNAs based on Silicon-germanium (SiGe heterojunction bipolar transistors (HBTs for simultaneous low noise and low power design and also taking advantage of CMOS circuitry for adding flexibility to the LNA d esign. Cryogenic LNAs' scalability challenges are discussed and addressed in the dissertation. To achieve that, first, HBTs of three state-of-the-art technologies are characterized and modeled at cryogenic temperature. It is shown that SiGe HBT provides a promising compromise of noise temperature, power consumption, and bandwidth. Moreover, a scalable on-chip approach is proposed and verified for b iasing of SiGe HBTs based LNAs. Finally, the first cryogenic re-configurable LNA is designed, implemented, and measured.

## TABLE OF CONTENTS

|              |      |        |                    | Page                                                            |

|--------------|------|--------|--------------------|-----------------------------------------------------------------|

| A            | CKN  | OWLE   | EDGME              | NTSiv                                                           |

| $\mathbf{A}$ | BSTI | RACT   |                    | v                                                               |

| LI           | ST ( | OF TA  | BLES               | x                                                               |

| LI           | ST ( | OF FIG | GURES.             |                                                                 |

| Cl           | HAP  | TER    |                    |                                                                 |

| 1.           | BA   | CKGR   | OUND 1             | MATERIAL AND MOTIVATION 1                                       |

|              | 1.1  | Need f | for Highly         | Scalable Integrated Cryogenic LNAs                              |

|              |      | 1.1.1  | Terahert           | zz Detection                                                    |

|              |      |        | 1.1.1.1<br>1.1.1.2 | Incoherent Detection       3         Coherent Detection       4 |

|              |      | 1.1.2  | Quantur            | n Computing Scalable Readout                                    |

|              |      |        | 1.1.2.1<br>1.1.2.2 | Spin Qubit Readout                                              |

|              | 1.2  | Need f | for Progra         | ammable Integrated Cryogenic LNAs                               |

| 2.           |      |        |                    | IS OF CRYOGENIC LNAS                                            |

|              |      | _      |                    |                                                                 |

| 3.           |      |        |                    | REVIEW OF SIGE HBTS AND RYOGENIC PERFORMANCE                    |

|              | 3.1  | Device | e Physics          | of SiGe HBTs                                                    |

|    |     | 3.1.1<br>3.1.2<br>3.1.3<br>3.1.4                     | BJT Energy Band Diagram  Band Engineering in SiGe HBT  SiGe HBT Fabrication Process  CMOS Integration with SiGe HBT                                                                                                                                                                                                                                                                                                                          | 20<br>23                               |

|----|-----|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

|    | 3.2 | SiGe I                                               | HBT Equivalent Circuit Model                                                                                                                                                                                                                                                                                                                                                                                                                 | 25                                     |

|    |     | 3.2.1<br>3.2.2                                       | Ebers-Moll Equivalent Model                                                                                                                                                                                                                                                                                                                                                                                                                  |                                        |

|    | 3.3 | Noise                                                | Sources in SiGe HBT                                                                                                                                                                                                                                                                                                                                                                                                                          | 27                                     |

|    |     | 3.3.1<br>3.3.2                                       | Shot Noise                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                        |

|    | 3.4 | Expec                                                | ted Cryogenic Performance of SiGe HBTs                                                                                                                                                                                                                                                                                                                                                                                                       | 29                                     |

|    |     | 3.4.1<br>3.4.2<br>3.4.3                              | Base Current Density                                                                                                                                                                                                                                                                                                                                                                                                                         | 30                                     |

|    | 3.5 | Conclu                                               | asion                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31                                     |

|    |     |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| 4. |     |                                                      | Γ CRYOGENIC CHARACTERIZATION AND SISTOR MODELING                                                                                                                                                                                                                                                                                                                                                                                             | 33                                     |

| 4. |     | ΓRAN                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                        |

| 4. | 7   | ΓRAN                                                 | SISTOR MODELING                                                                                                                                                                                                                                                                                                                                                                                                                              | 33<br>34<br>36                         |

| 4. | 7   | TRAN Tower 4.1.1 4.1.2                               | SISTOR MODELING                                                                                                                                                                                                                                                                                                                                                                                                                              | 33<br>36<br>36<br>37                   |

| 4. | 7   | TRAN Tower 4.1.1 4.1.2                               | SISTOR MODELING  Semiconductor-SBC18H5/SBC18S5  Gummel Measurement of SiGe HBT  RF Measurement and $f_t/f_{\rm max}$ Plots  Cryogenic Model Parameter Extraction  4.1.3.1 $r_e$ and $r_c$ Extraction  4.1.3.2 $C_{\rm CB}$ and $C_{\rm CS}$ extraction                                                                                                                                                                                       | 34<br>36<br>36<br>37<br>38             |

| 4. | 7   | TRAN Tower 4.1.1 4.1.2 4.1.3                         | Semiconductor-SBC18H5/SBC18S5  Gummel Measurement of SiGe HBT  RF Measurement and $f_t/f_{\text{max}}$ Plots  Cryogenic Model Parameter Extraction  4.1.3.1 $r_e$ and $r_c$ Extraction  4.1.3.2 $C_{\text{CB}}$ and $C_{\text{CS}}$ extraction  4.1.3.3 $g_m$ , $r_b$ , $C_{\text{BE}}$ , $r_{be}$ , and $\tau$ extraction                                                                                                                   | 34<br>36<br>36<br>37<br>38<br>41       |

| 4. | 4.1 | TRAN Tower 4.1.1 4.1.2 4.1.3                         | Semiconductor-SBC18H5/SBC18S5  Gummel Measurement of SiGe HBT  RF Measurement and $f_t/f_{\text{max}}$ Plots  Cryogenic Model Parameter Extraction  4.1.3.1 $r_e$ and $r_c$ Extraction  4.1.3.2 $C_{\text{CB}}$ and $C_{\text{CS}}$ extraction  4.1.3.3 $g_m$ , $r_b$ , $C_{\text{BE}}$ , $r_{be}$ , and $\tau$ extraction  Cryogenic Simulation Results of the SiGe HBT                                                                     | 33<br>36<br>36<br>37<br>41<br>42       |

| 4. | 4.1 | TRAN Tower 4.1.1 4.1.2 4.1.3 4.1.4 IHP M 4.2.1 4.2.2 | Semiconductor-SBC18H5/SBC18S5  Gummel Measurement of SiGe HBT RF Measurement and $f_t/f_{\rm max}$ Plots Cryogenic Model Parameter Extraction  4.1.3.1 $r_e$ and $r_c$ Extraction  4.1.3.2 $C_{\rm CB}$ and $C_{\rm CS}$ extraction  4.1.3.3 $g_m, r_b, C_{\rm BE}, r_{be}$ , and $\tau$ extraction  Cryogenic Simulation Results of the SiGe HBT  ficroelectronics-SG13G2  Technology Description Cryogenic Characterization and Comparison | 33<br>36<br>36<br>37<br>41<br>42<br>43 |

| <b>5.</b> | SIG                             | EE HBT CRYOGENIC LNAS FOR MKID READOUT                                                                                                                                                         | 54       |

|-----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

|           | 5.1<br>5.2<br>5.3<br>5.4<br>5.5 | Microwave Kinetic Inductance Detector (MKID)  MKID Readout System  Cryogenic LNA Design Overview and Specifications  LNA Design and Implementation  Servo Bias Board Design and Implementation | 57<br>58 |

|           |                                 | 5.5.1 Servo Bias Board Design                                                                                                                                                                  |          |

|           | 5.6                             | Experimental Results and Comparison to Simulations                                                                                                                                             | 66       |

|           |                                 | 5.6.1 Small-signal Measurement Results                                                                                                                                                         |          |

|           | 5.7                             | LNAs Array Implementation in the MKID Readout System                                                                                                                                           | 71       |

| 6.        |                                 | DEBAND SIGE HBT CRYOGENIC LNAS AS MIXER-BASED SYSTEMS                                                                                                                                          | 73       |

|           | 6.1                             | SiGe HBT LNA Direct Integration with HEB Mixers                                                                                                                                                | 73       |

|           |                                 | 6.1.1LNA Design and Implementation6.1.2Experimental Results6.1.3Comparison and Conclusion                                                                                                      | 77       |

|           | 6.2                             | General Purpose Wideband Cryogenic LNA                                                                                                                                                         | 79       |

|           |                                 | 6.2.1 Cryogenic LNA Design and Implementation                                                                                                                                                  |          |

|           | 6.3                             | Conclusion and Future Work                                                                                                                                                                     | 83       |

| 7.        |                                 | W POWER AND HIGH RESOLUTION CRYOGENIC DAC                                                                                                                                                      | 85       |

|           | 7.1<br>7.2<br>7.3<br>7.4        | Cryogenic LNAs Biasing Approaches  Programmable Base Voltage Biasing  Digital to Analog Converter Design  Biasing Integrated Cryogenic LNA                                                     | 87<br>90 |

|           |                                 | <ul> <li>7.4.1 Biasing Integrated Cryogenic LNA Design and Implementation</li></ul>                                                                                                            |          |

|                | 7.5               | Conclusion                                                                                                                                                            |

|----------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8.             |                   | OGRAMMABLE CRYOGENIC BICMOS LNA DESIGN<br>AND IMPLEMENTATION                                                                                                          |

|                | 8.1<br>8.2<br>8.3 | Introduction97Design Approach99Programmable RLC Resonator Design102                                                                                                   |

|                |                   | 8.3.1Tuning Resistor and Capacitor Banks1038.3.2Varactors at Cryogenic Temperatures1058.3.3Negative Resistor1058.3.4Experimental Results of Programmable Resonator108 |

|                | 8.4               | Amplifier Design, Implementation, and Experimental Setup 109                                                                                                          |

|                |                   | 8.4.1 LNA Design                                                                                                                                                      |

|                | 8.5<br>8.6        | Measurement Results116Conclusion124                                                                                                                                   |

| 9.             |                   | NCLUSION AND SUGGESTIONS FOR FUTURE WORK                                                                                                                              |

|                | 9.1<br>9.2        | Conclusion and Summary                                                                                                                                                |

| $\mathbf{A}$ ] | PPEI              | NDICES                                                                                                                                                                |

| В.             | DE<br>SEF         | EMBEDDING TEST STRUCTURE PARASITIC                                                                                                                                    |

|                | 2                 | SIMULATIONS 132                                                                                                                                                       |

| BI             | BLI               | OGRAPHY 135                                                                                                                                                           |

## LIST OF TABLES

| <b>T</b> able | Page                                                                                                                                                                                                                             |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1           | Model Parameters at 7 K. Units: Current denisty–mA/ $\mu$ m <sup>2</sup> , Area– $\mu$ m <sup>2</sup> , Res.– $\Omega \cdot \mu$ m <sup>2</sup> , Cap.–fF/ $\mu$ m <sup>2</sup> , Transcond.–mS/ $\mu$ m <sup>2</sup> , Delay–ps |

| 4.2           | Summary and comparison of some important cryogenic specifications of HBT in different technologies for LNA design. The ambient temperature is $7  \mathrm{K}$ and frequency of simulated $T_{\min}$ is $4  \mathrm{GHz}$         |

| 5.1           | Model parameters extracted at a physical temperature of 18 K. $W_{\rm E}{=}0.13~\mu{\rm m},~J_{\rm C1,2}{=}0.46,~0.58~mA/\mu{\rm m}^2.$ A standard hybrid- $\pi$ model topology is used [14]                                     |

| 6.1           | Model Parameters at a Physical Temperature of 7 K                                                                                                                                                                                |

| 8.1           | Model Parameters at a Physical Temperature of 16 K. Bias current densities are related to the wideband state of the LNA                                                                                                          |

| 8.2           | Comparison with state-of-the-art cryogenic LNAs                                                                                                                                                                                  |

## LIST OF FIGURES

| Pa                                                                                                                                                                                                                         | ge                                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|

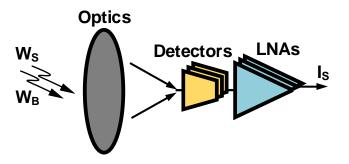

| Schematic of direct detection. $W_S$ is the signal power and $W_B$ is the background radiation power                                                                                                                       | 4                                                                                                    |

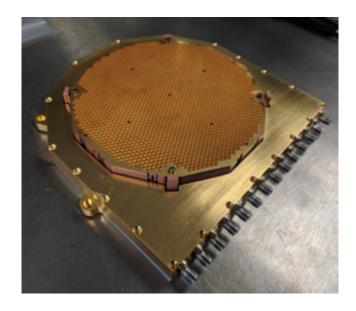

| TolTEC 1.1 mm MKID Array 1800 pixels, 3600 detectors [10]                                                                                                                                                                  | . 5                                                                                                  |

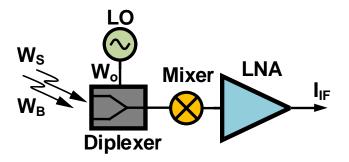

| Schematic of heterodyne detection. $W_S$ is the signal power and $W_B$ is the background radiation power. $W_o$ is LO radiation power                                                                                      | 6                                                                                                    |

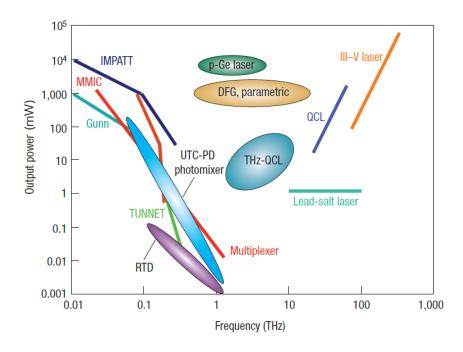

| Terahertz emission power regard to frequency which shows the gap with respect to source technology [88]                                                                                                                    | 7                                                                                                    |

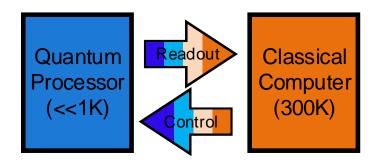

| Fault-tolerant quantum computer with feedback loop of classical computer                                                                                                                                                   | 8                                                                                                    |

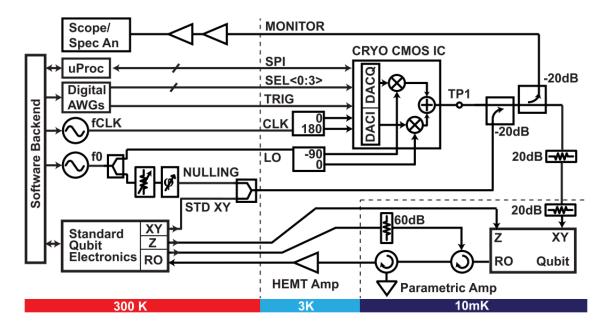

| Integrated quantum control approach described in [12]                                                                                                                                                                      | . 9                                                                                                  |

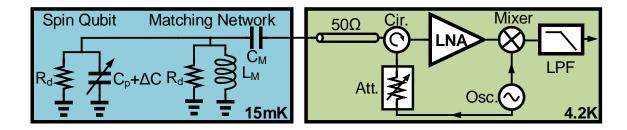

| Simplified model of a spin qubit and readout front end block diagram. Figure is reproduced from [70]                                                                                                                       | 10                                                                                                   |

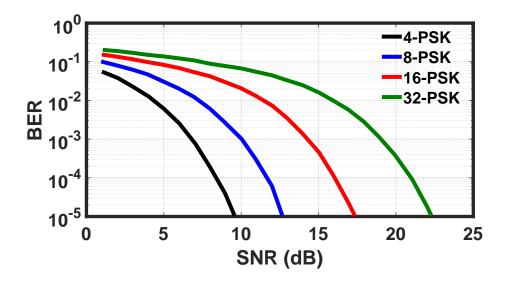

| BER of MPSK via SNR for a given fixed phase error $(\theta = 0)$ . Figure is reproduced from [49]                                                                                                                          | 10                                                                                                   |

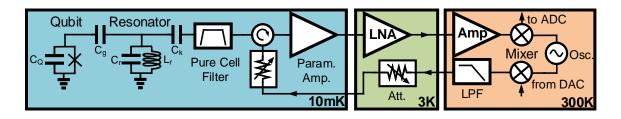

| Simplified model of transmon qubit and readout block diagram.  Figure is reproduced from [13, 54]                                                                                                                          | 10                                                                                                   |

| (a) State-dependent dispersive frequency shift which can be detect as a phase shift in reflection phase. (b) Typical baseband constellation measurement. Blue and red colors correspond to 0 state and 1, respectively[11] | 11                                                                                                   |

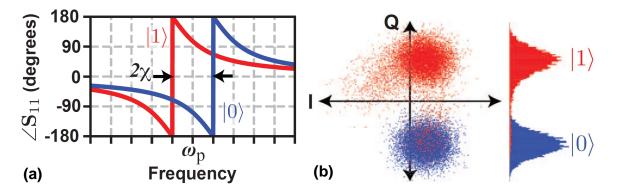

| approach for versatile radio transceiver applications [92]. (a) LNA schematic, (b) Measured S parameters, and (c) Measured                                                                                                 | 13                                                                                                   |

|                                                                                                                                                                                                                            | Schematic of direct detection. $W_S$ is the signal power and $W_B$ is the background radiation power |

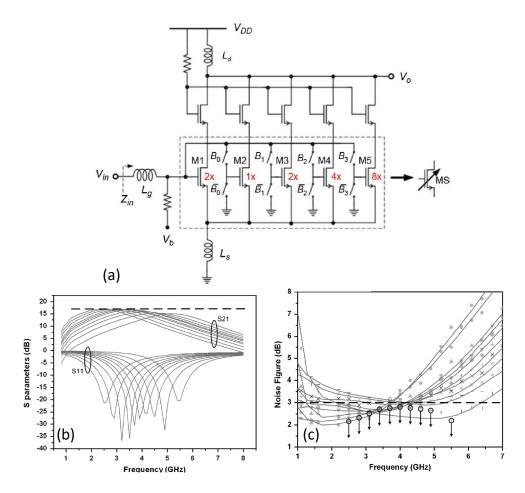

| 1.12 | Tunable frequency response LNA with LC-switch approach for wireless sensor applications [59]. (a) LNA simplified schematic, (b) Measured $S_{11}$ and voltage gain, and (c) Measured noise figure.                                                                                                                                             | 13 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

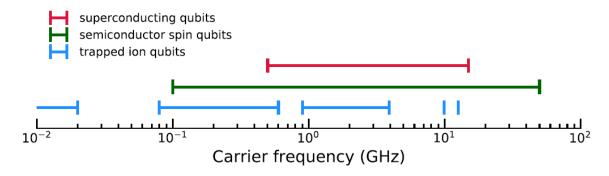

| 1.13 | Different frequency ranges requiered for different type of qubits control and readout. For example, the carrier frequency for trapped ions can be in the a few MHz range. The narrow trapped ion carrier frequency bands at $\sim \! \! 10  \mathrm{GHz}$ and $\sim \! \! 12.6  \mathrm{GHz}$ . The figure is reported in [13]                 | 14 |

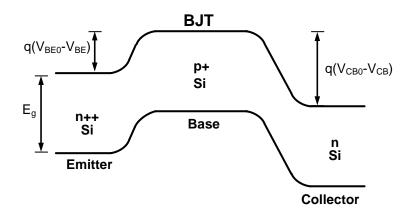

| 3.1  | Energy band diagram of simple BJT device under active forward operation                                                                                                                                                                                                                                                                        | 21 |

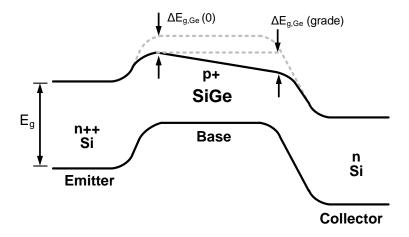

| 3.2  | Energy band diagram of simple SiGe HBT device under active forward operation                                                                                                                                                                                                                                                                   | 22 |

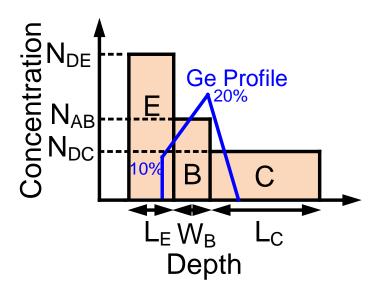

| 3.3  | Schematic of doping and Ge profile for a typical SiGe HBT. Figure reproduced from [85]                                                                                                                                                                                                                                                         | 22 |

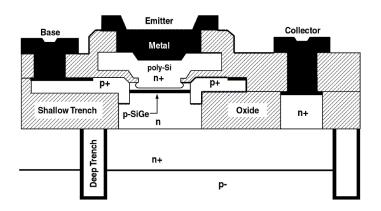

| 3.4  | Cross section of a typical SiGe HBT device [26]                                                                                                                                                                                                                                                                                                | 24 |

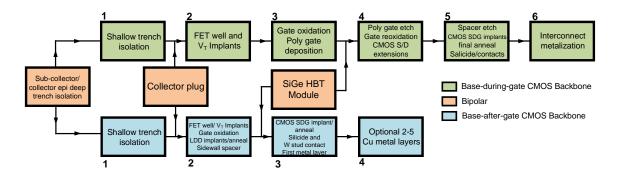

| 3.5  | BiCMOS fabrication process flowchart for BDG and BAG approaches. Figure is reproduced with some changes from [26]                                                                                                                                                                                                                              | 25 |

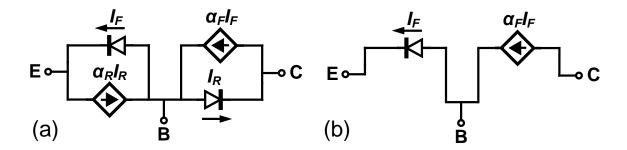

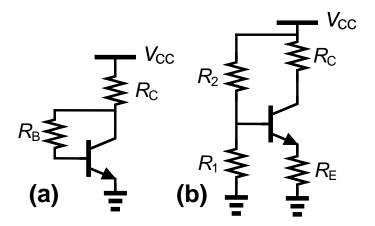

| 3.6  | (a) Simple Ebers-Moll model of NPN device (b) Ebers-Moll model of NPN at active region.                                                                                                                                                                                                                                                        | 26 |

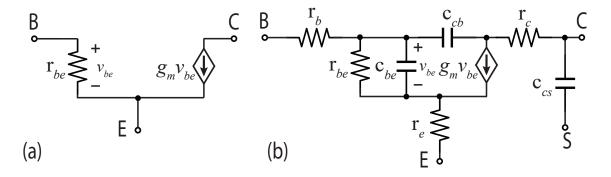

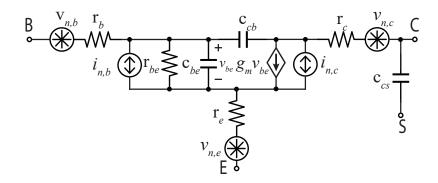

| 3.7  | (a) Simple linearized small-signal model of BJT device (b) High frequency small signal model of SiGe HBT                                                                                                                                                                                                                                       | 26 |

| 3.8  | SiGe HBT small signal model including noise sources                                                                                                                                                                                                                                                                                            | 29 |

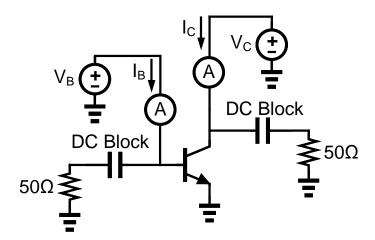

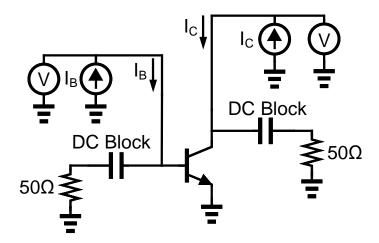

| 4.1  | DC Gummel measurement setup. Collector and base DC currents are measured regards to $V_{\rm BE}$ while $V_{\rm CB}=0$ . Bias tee is used in the measurements.                                                                                                                                                                                  | 34 |

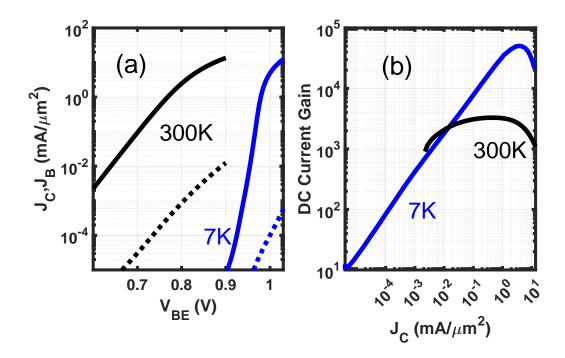

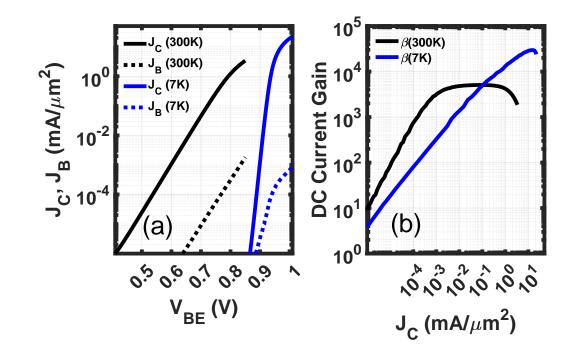

| 4.2  | DC Gummel measurement results of SiGe HBT of SBC18H5 process.  (a) Collector (solid lines) and base (dotted lines) current densities regards to $V_{\rm BE}$ for room (black lines) and cryogenic (blue lines) temperatures. (b) DC current gain ( $\beta_{\rm DC}$ ) of SiGe HBT for room (black line) and cryogenic (blue line) temperatures | 35 |

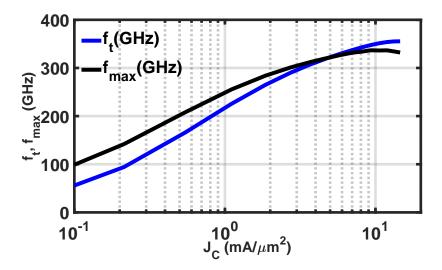

| 4.3  | $f_t$ (blue) and $f_{\text{max}}$ (black) measurement results of SiGe HBT of SBC18H5 process at 7 K ambient temperature regards to collector current density. The measured transistor size is $0.09 \times 20 \times 1 \mu\text{m}^2$ . $V_{\text{CE}} = 0.7 \text{V}$ while $V_{\text{CE}}$ is swept                                                                                                                                                                    | 37 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.4  | Open-collector measurement setup for $r_e$ and $r_c$ parameters extraction. $I_{\rm B}$ is swept in wide range for different values of $I_{\rm B}$                                                                                                                                                                                                                                                                                                                       | 38 |

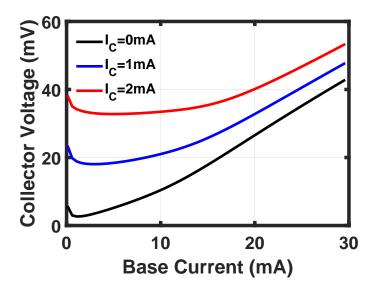

| 4.5  | Open-collector sample cryogenic measurement results. Collector voltage is swept regards to base current for different collector currents                                                                                                                                                                                                                                                                                                                                 | 39 |

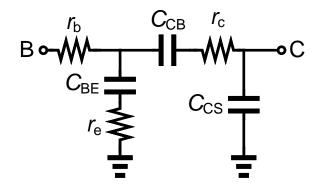

| 4.6  | Small-signal model of SiGe HBT at off-bias state. This model is used to extract $C_{\text{CB}}$ and $C_{\text{CS}}$ parameters                                                                                                                                                                                                                                                                                                                                           | 40 |

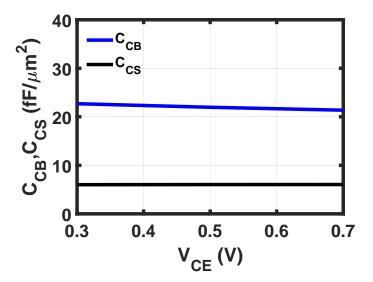

| 4.7  | Extracted cryogenic (7 K) $C_{\rm CB}$ and $C_{\rm CS}$ regards to collector-emitter voltage while $V_{\rm BE}{=}0$ obtained from off-bias measurement. The measured device size is $0.09{\times}20{\times}1\mu{\rm m}^2$                                                                                                                                                                                                                                                | 40 |

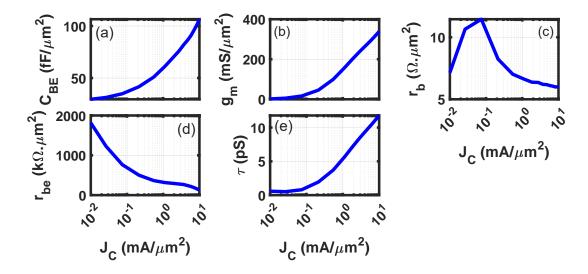

| 4.8  | Cryogenic $(T_a=7\mathrm{K})$ small-signal model parameters extraction from active sweep measurement. (a) $C_{\mathrm{BE}}$ , (b) $g_m$ , (c) $r_b$ , (d) $r_{be}$ , and (e) $\tau$ regards to collector current density while $V_{\mathrm{CE}}=0.7\mathrm{V}$ . The measured device size is $0.09\times20\times1\mu\mathrm{m}^2$ . Extracted $\tau$ is greater than be anticipated for this process $(\tau\approx C_{be}/g_m)$ . It might be due to a measurement error | 41 |

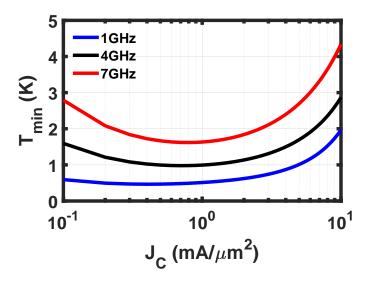

| 4.9  | Simulated cryogenic (16 K) $T_{\rm min}$ of SBC18H5 SiGe HBT regards to current density when $V_{\rm CE}{=}0.7{\rm V}.$                                                                                                                                                                                                                                                                                                                                                  | 43 |

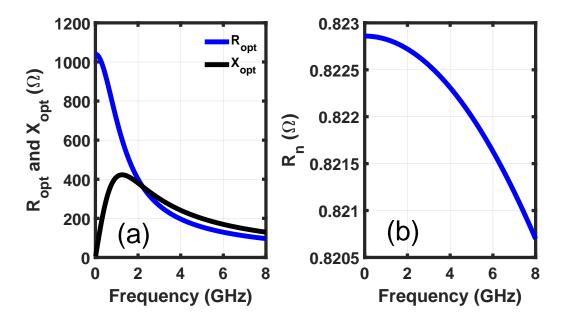

| 4.10 | Simulated cryogenic (16 K) (a) $R_{\rm opt}$ (blue line) and $X_{\rm opt}$ (black line) and (b) $R_n$ of SiGe HBT regards to frequency when $V_{\rm CE}{=}0.7{\rm V}$ and $J_{\rm C}{=}1{\rm mA}/\mu{\rm m}^2$ . Transistor size is $1{\times}20{\times}0.09~\mu{\rm m}^2$                                                                                                                                                                                               | 44 |

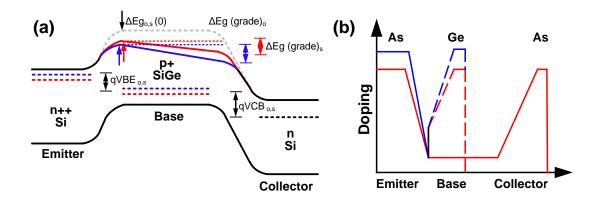

| 4.11 | (a) Energy band diagram (blue: optimized HBT and red: standard HBT) and (b) Doping structure of standard and optimized HBT devices.                                                                                                                                                                                                                                                                                                                                      | 45 |

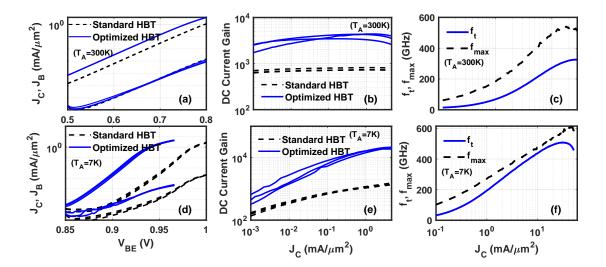

| 4.12 | (a) and (d) Room ( $T_a = 300 \mathrm{K}$ ) and cryogenic ( $T_a = 7 \mathrm{K}$ ) collector and base current densities regards to base-emitter voltage of standard (dashed black lines) and optimized (solid blue lines) of SiGe HBT coming from Gummel measurement. (b) and (e) Room ( $T_a = 300 \mathrm{K}$ ) and cryogenic ( $T_a = 7 \mathrm{K}$ ) DC current gain of standard (dashed black lines) and optimized (solid blue lines) of SiGe HBT coming from Gummel measurement. $f_t$ (solid blue) and $f_{\rm max}$ (dashed black) of (c) standard HBT and (f) optimized HBT at Room ( $T_a = 300 \mathrm{K}$ ) and cryogenic ( $T_a = 7 \mathrm{K}$ ) temperatures regard to collector current density coming from active sweep measurement while $V_{\rm CE} = 0.7 \mathrm{V}$ . Three different samples are measured for each type of transistor | 46 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

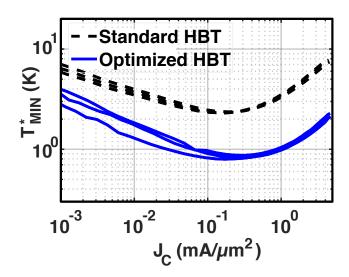

| 4.13 | Room and cryogenic (7 K) minimum noise temperature regards to current density for both standard (dashed black lines) and optimized (solid blue lines) HBTs. Three different samples are measured for each type of transistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 47 |

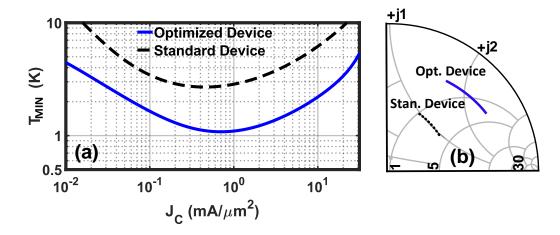

| 4.14 | Modeled noise parameters of the optimized (blue) and standard (dashed black) HBTs at 5 GHz: (a) $T_{\rm min}$ and (b) $\Gamma_{\rm opt}$ (4–8 GHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 48 |

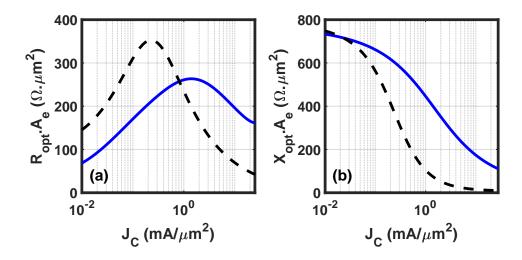

| 4.15 | Modeled noise parameters of the optimized (blue) and standard (dashed black) HBTs at 5 GHz and regards to collector current density: (a) $R_{\rm opt} \times A_{\rm E}$ and (b) $X_{\rm opt} \times A_{\rm E}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 49 |

| 4.16 | Room (300 K, black lines) and cryogenic (7 K, blue lines) Gummel measurement of optimized HBT from SG03 BiCMOS technology. (a) Base (dashed lines) and collector (solid lines) current densities regards to base-emitter voltage and (b) DC current gain ( $\beta$ ) regards to collector current density. The sample HBT size is $0.12\times12\times1~\mu\mathrm{m}^2$ with CBEBC layout structure                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 50 |

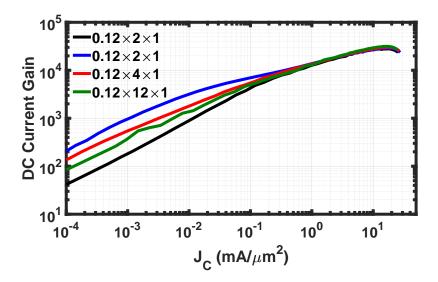

| 4.17 | cryogenic (7 K) DC current gain regards to collector current density for different HBT sizes in different locations of the wafer. The plots are based on Gummel measurement setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 51 |

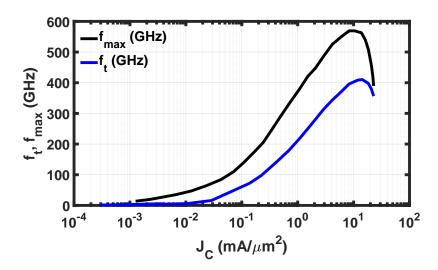

| 4.18 | cryogenic (7 K) measured $f_t$ and $f_{\rm max}$ of the HBT regards to current density. The sample HBT size is $0.12\times12\times1\mu{\rm m}^2$ with CBEBC layout structure. The plot is created based on active-sweep measurement while $V_{\rm CE}=0.7{\rm V}.$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 52 |

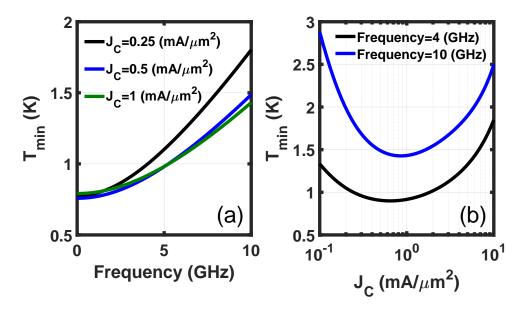

| 4.19 | cryogenic (7 K) $T_{\text{min}}$ simulations based on created standard small signal model regards to (a) frequency and (b) collector current density. The sample HBT size is $0.12 \times 12 \times 1 \mu\text{m}^2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 52 |

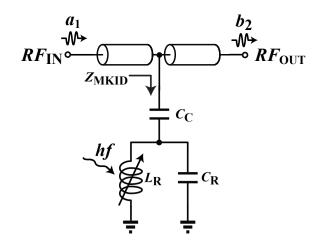

| 5.1  | kinetic inductance $(L_K)$ is modulated by photon flux, resulting in a shift in the series resonant frequency of the coupled MKID, as observed from the transmission line                                                                                                                                                                                                                                  | 55 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.2  | Frequency domain multiplexing of MKIDs                                                                                                                                                                                                                                                                                                                                                                     | 57 |

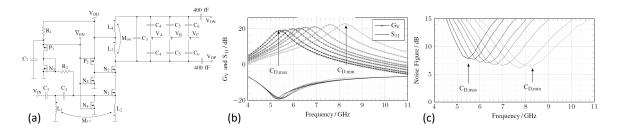

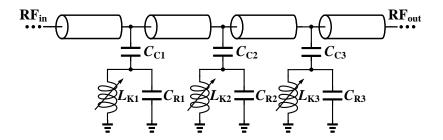

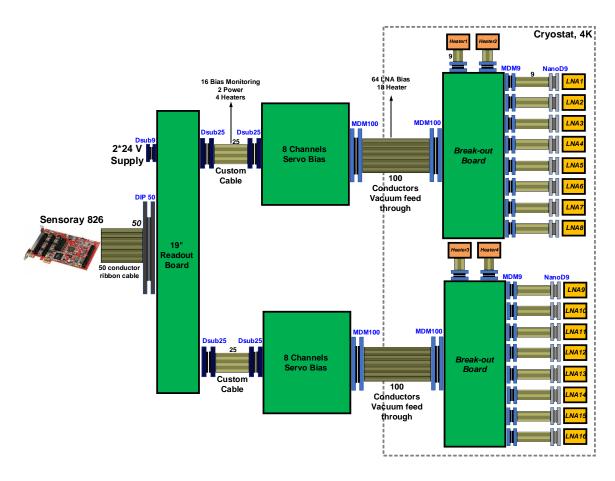

| 5.3  | Simplified system block diagram of the MKID readout                                                                                                                                                                                                                                                                                                                                                        | 58 |

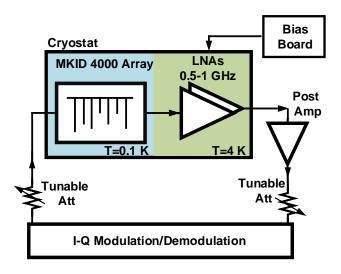

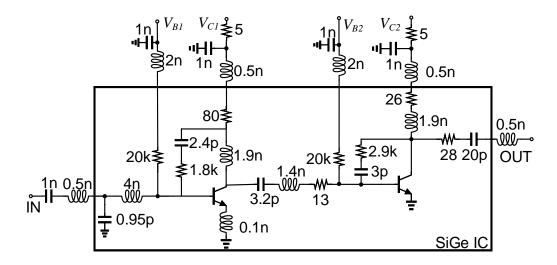

| 5.4  | Schematic design of cryogenic LNA for MKID array readout including off-chip bypassing components and input matching network. Bias points are related for 16 K measurements                                                                                                                                                                                                                                 | 61 |

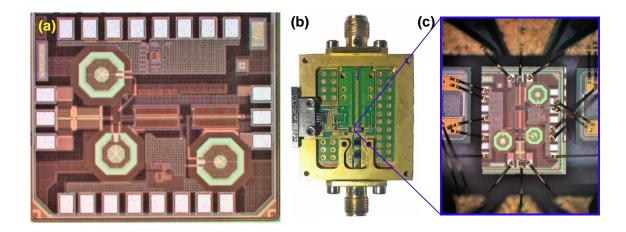

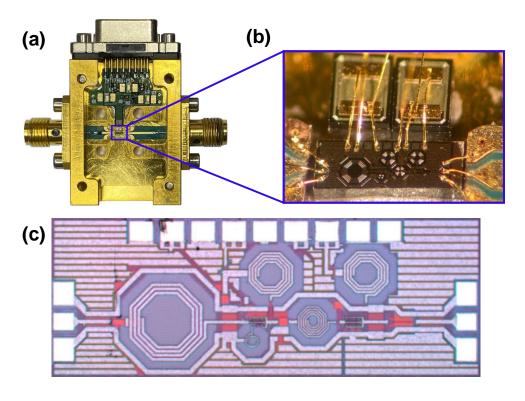

| 5.5  | (a) Chip photograph, (b) Assembled module, and (c) Wire-bonded chip of cryogenic LNA for MKID array                                                                                                                                                                                                                                                                                                        | 62 |

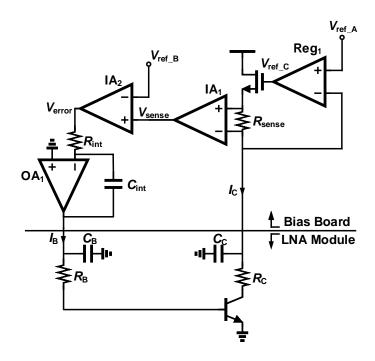

| 5.6  | Design idea of the servo bias of the one stage LNA. Collector current can be precisely controlled by the reference voltage in the servo loop                                                                                                                                                                                                                                                               | 65 |

| 5.7  | Servo bias circuit implementation for biasing one stage of cryogenic LNA. The circuit is copied 16 times to bias up 8 LNAs                                                                                                                                                                                                                                                                                 | 66 |

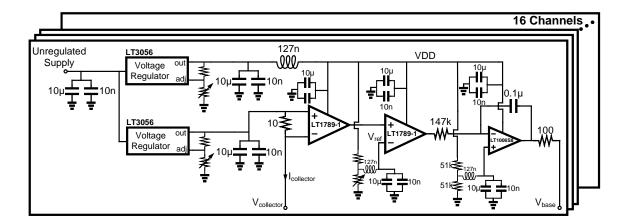

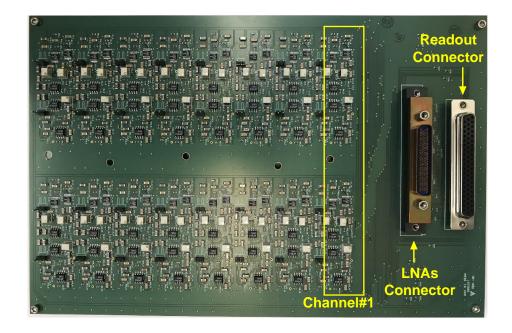

| 5.8  | Eight channels assembled bias board. Standard 4 layers FR4 board is used. A 100-pins Miro-D connector is selected as cryogenic compatible connector. A 25-pins D-sub connector is selected to monitor base and collector voltages and is providing heater signals of the cryostat.                                                                                                                         | 67 |

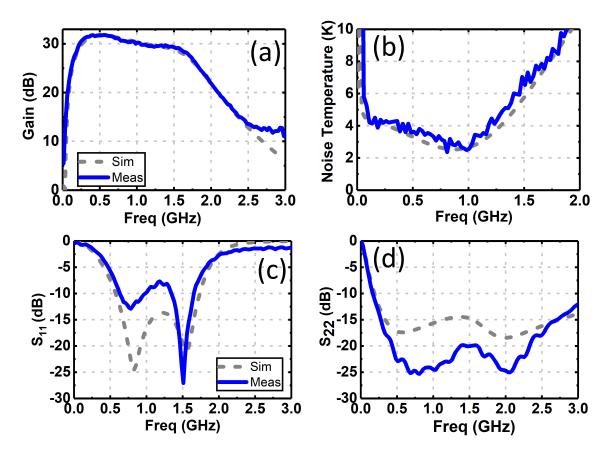

| 5.9  | LNA cryogenic measurement results (solid blue lines) and comparison with simulations (dashed black lines) while the amplifier is consuming 6.6 mW dc power ((a) Gain (b) Noise temperature (c) $S_{11}$ (d) $S_{22}$ ). The amplifier was biased at $V_{C1}$ =0.85 V, $I_{C1}$ =4.8 mA, $V_{C2}$ =0.85 V, and $I_{C2}$ =3 mA. The amplifier and the attenuator temperatures were 16 and 15 K, respectively | 68 |

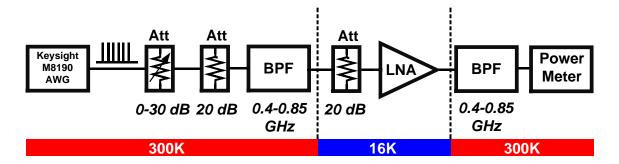

| 5.10 | Test setup used to characterize compression characteristics of the LNA. For CW measurements, the arbitrary waveform generator was replaced by a CW generator                                                                                                                                                                                                                                               | 69 |

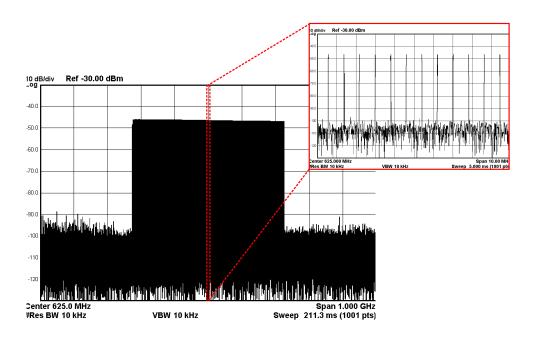

| 5.11 | Spectrum of multi-tone stimulus. The signal consists of 560 evenly spaced tones spanning the frequency range of 0.4–0.85 GHz                                                                                                                                                                                                                                                                               | 70 |

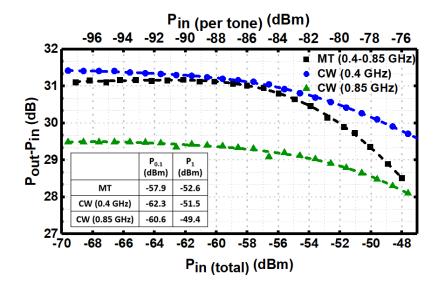

| 5.12 | Measured compression characteristics for CW (Blue=0.4 GHz and green=0.85 GHz) and multi-tone stimuli (Black). The upper x-axis scale corresponds to the input power per-tone for the multi-tone (560 tones) stimulus, which is expected to be -90 dBm in the TolTEC system. | 70         |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.13 | Simplified diagram of the bias board and wiring towards LNAs array and sensory board. Two breakout boards are used to divide each LNA biasing signals                                                                                                                       | 71         |

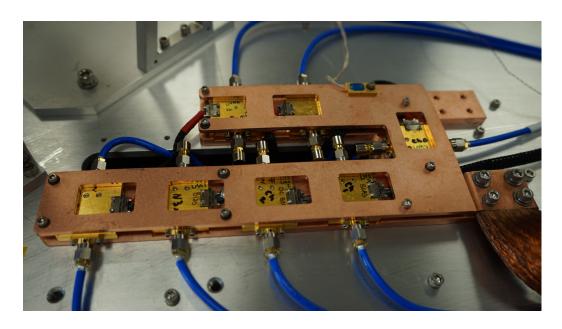

| 5.14 | First LNA array, including 7 LNAs, implemented in the camera                                                                                                                                                                                                                | 72         |

| 5.15 | Readout board for monitoring base and collector voltages of the LNAs                                                                                                                                                                                                        | 72         |

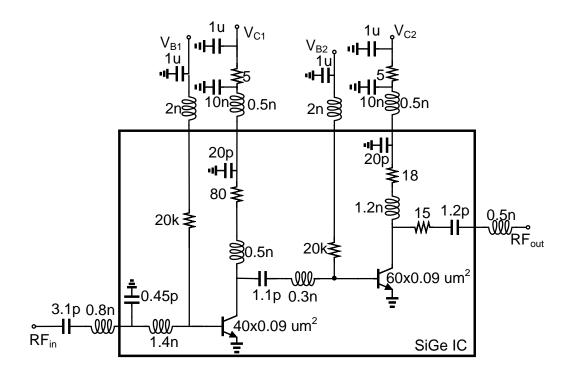

| 6.1  | Schematic design of wideband cryogenic LNA for HEB mixer readout. Transistors total emitter areas for the first and second stages are 5.4 and $7.2\mu\text{m}^2$ , respectively                                                                                             | 75         |

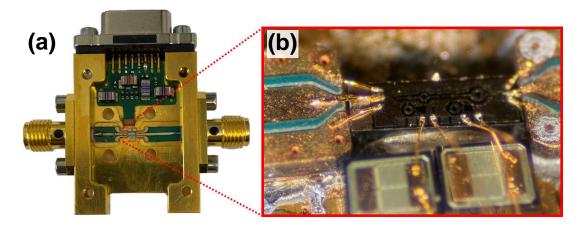

| 6.2  | (a) Assembled module, (b) Wire-bonded chip, and (c) Chip photograph                                                                                                                                                                                                         | 76         |

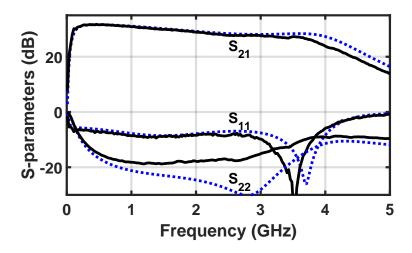

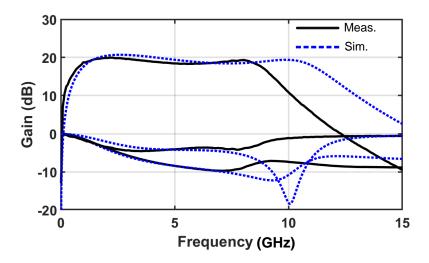

| 6.3  | On-wafer room temperature measurement of chip and comparison with simulations ( $P_{DC}=8\mathrm{mW}$ )                                                                                                                                                                     | 77         |

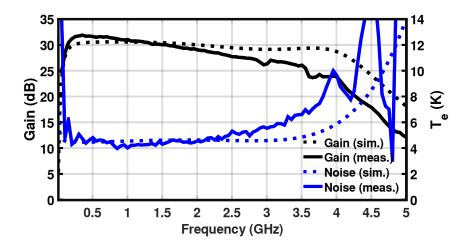

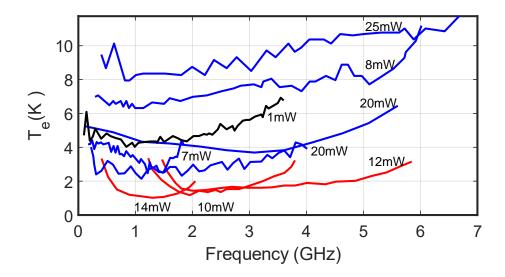

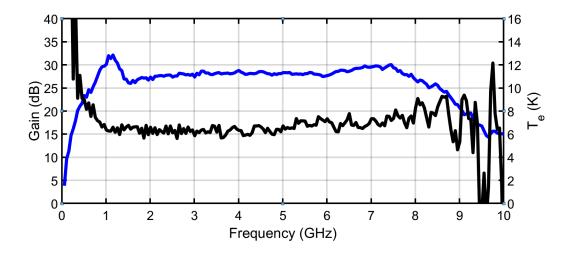

| 6.4  | Measured and simulated gain and noise temperature at a physical temperature of 15 K. These data were taken for a dc power consumption of 0.96 mW ( $I_{\rm C1}$ =2 mA, $I_{\rm C2}$ =0.8 mA, $V_{\rm C1}$ =0.4 V, and $V_{\rm C2}$ =0.2 V).                                 | 78         |

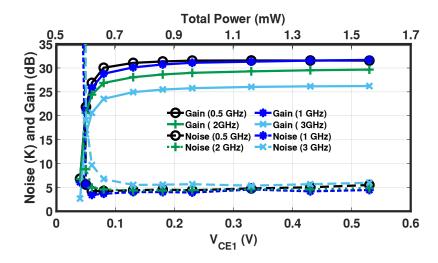

| 6.5  | Cryogenic amplifier performance as a function of first stage power dissipation. As there is $85\Omega$ of series resistance, $V_{\rm C1}$ is $170{\rm mV}$ higher than the collector–emitter voltage                                                                        | <b>7</b> 9 |

| 6.6  | Cryogenic LNAs specifications which potentially can be used for IF LNA of HEB mixer (Black: This work, Red : InP HEMT, and Blue: SiGe HBT) [15, 79, 81, 82, 23, 46]                                                                                                         | 80         |

| 6.7  | Schematic design of wideband cryogenic LNA for SIS mixer readout                                                                                                                                                                                                            | 82         |

| 6.8  | (a) Assembled module, (b) Wire-bonded chip and bypass capacitors                                                                                                                                                                                                            | 82         |

| 6.9  | On-wafer room temperature measurement of chip and comparison with simulations $(P_{DC} = 17 \text{ mW})$                                                                                                                   |    |  |  |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| 6.10 | Measured gain and noise temperature at a physical temperature of 16 K. These data were taken for a dc power consumption of 1.5 mW                                                                                          | 84 |  |  |

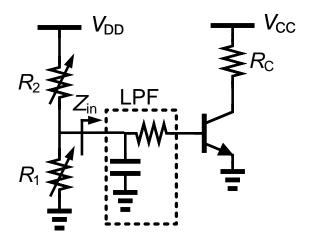

| 7.1  | Self bias approaches of SiGe HBT cryogenic LNAs                                                                                                                                                                            | 87 |  |  |

| 7.2  | Idea of programmable base voltage biasing for SiGe BiCMOS LNA                                                                                                                                                              | 88 |  |  |

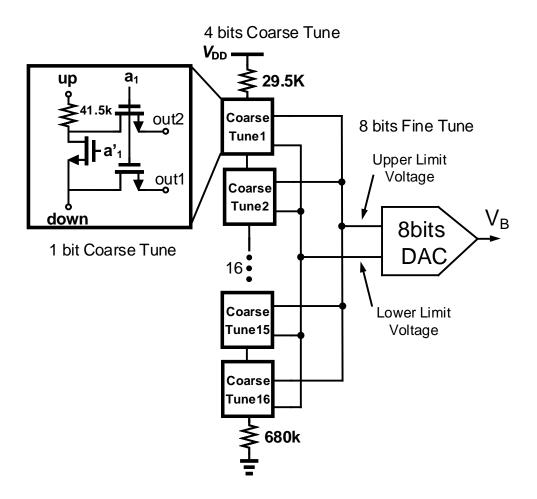

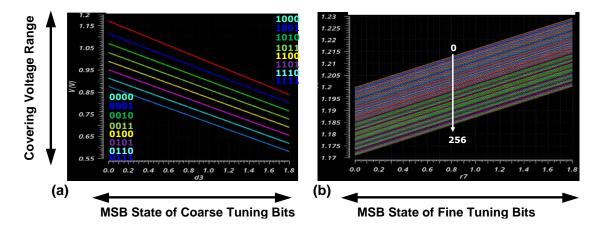

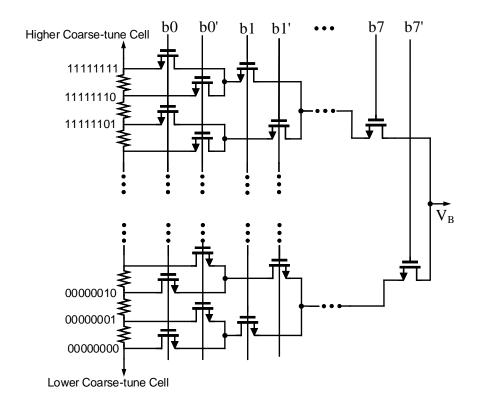

| 7.3  | Circuit implementation of base voltage divider for the LNA. Four/eight bits coarse/fine tuning bits are used for 0.6 V voltage covering range and 0.25 mV voltage resolution                                               | 89 |  |  |

| 7.4  | Cadence simulation results of base voltage tuning range. (a) Output voltage range for 16 states of coarse tuning bits and (b) Output voltage range for 256 states of fine tuning bits while coarse bits state is '1000'.   | 90 |  |  |

| 7.5  | Eight bits low-power digital to analog converter                                                                                                                                                                           | 91 |  |  |

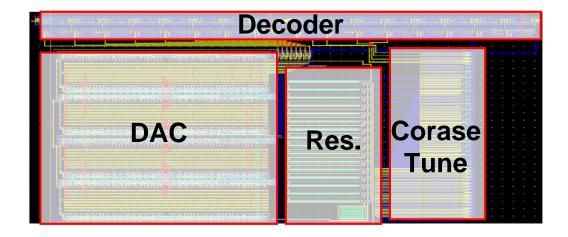

| 7.6  | Programmable base voltage divider layout. The dimensions are $230\times140\mu\mathrm{m}^2$ . The layout includes 8-bits DAC, 4 bits coarse tuning switch-resistors, and a standard decoder                                 | 92 |  |  |

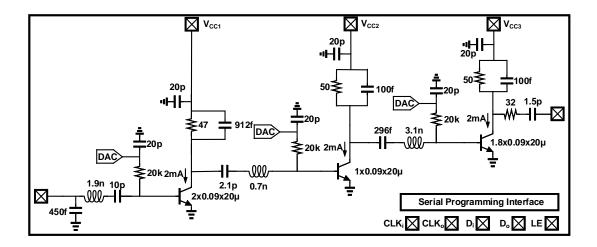

| 7.7  | The schematic design of SiGe BiCMOS LNA to verify the bias integration approach. A three-stage LNA with common emitter topology without inductor degeneration. The chip includes a standard digital programming interface. | 93 |  |  |

| 7.8  | (a) Assembled chip inside a coaxial module. (b) wirebondeded chip photograph and collector bypass capacitors                                                                                                               | 94 |  |  |

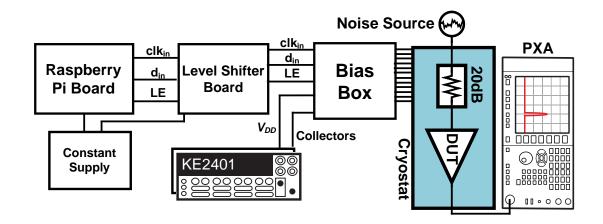

| 7.9  | Cryogenic measurement setup for bias integrated cryogenic LNA                                                                                                                                                              | 95 |  |  |

| 7.10 | Cryogenic measurement results of the bias integrated LNA. Second and third stages DC bias currents are swept to achieve different average gains                                                                            |    |  |  |

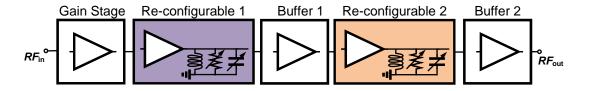

| 8.1  | Block diagram of the proposed reconfigurable LNA1                                                                                                                                                                          | 01 |  |  |

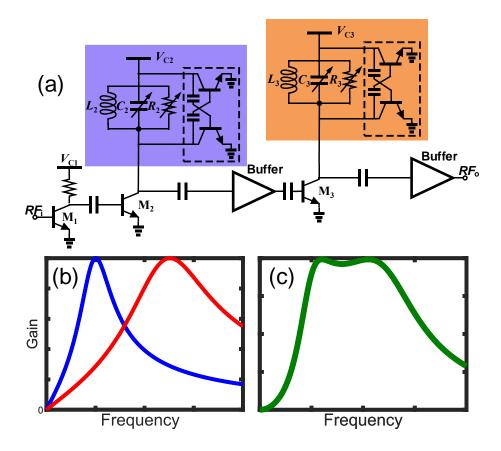

| 8.2  | (a) Simplified schematic of three stages tunable frequency response LNA, (b) Magnitude of the voltage for second and third stages, and (c) Total frequency response of the LNA                                                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

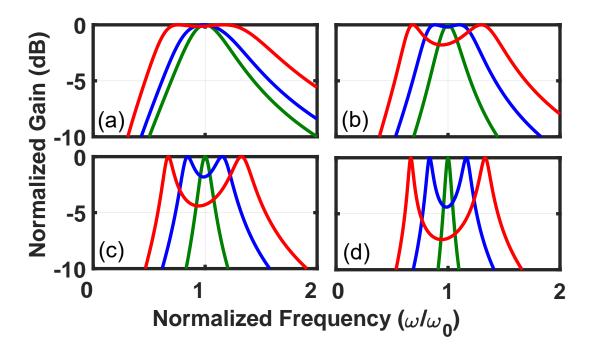

| 8.3  | Normalized voltage gain of the two stages amplifier with tunable RLC load. (a) $Q_1 = Q_2 = 2$ , (b) $Q_1 = Q_2 = 4$ , (c) $Q_1 = Q_2 = 8$ , and (d) $Q_1 = Q_2 = 16$ (Red: $\omega_1 = 0.66\omega_0$ and $\omega_2 = 1.33\omega_0$ , blue: $\omega_1 = 0.83\omega_0$ and $\omega_2 = 1.16\omega_0$ , and green: $\omega_1 = \omega_2 = \omega_0$ ) |

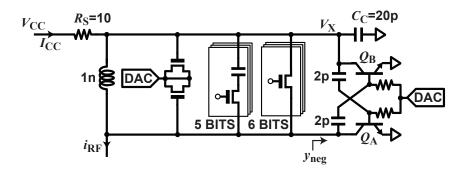

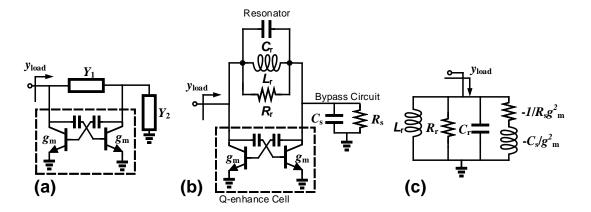

| 8.4  | Tunable LC tank. The MOS varactor and negative conductance biases are provided by on-chip DACs. The capacitor and resistor banks are binary weighted with LSB values of $48\mathrm{fF}$ and $650\Omega$ , respectively                                                                                                                              |

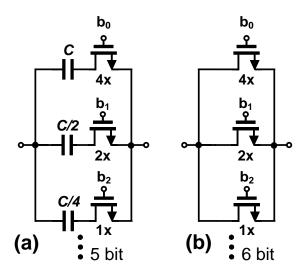

| 8.5  | (a) 5-bits switch-capacitor tuning circuit. (b) 6-bits resistor bank tuning circuit. Minimum transistor gate width for capacitor and resistor banks are 4 and 1 $\mu$ m, respectively. Lowest capacitor value is 48 fF                                                                                                                              |

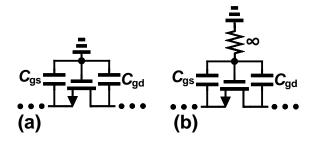

| 8.6  | Adding series resistor in gate to decrease parasitic capacitors of MOS switch. (a) Gate is directly connected to control voltage. (b) Gate is connected to control voltage via a $20\mathrm{k}\Omega$ series resistor 104                                                                                                                           |

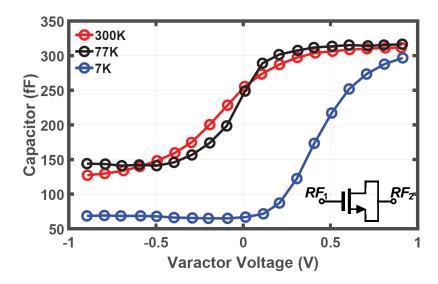

| 8.7  | On-wafer measured total capacitor of MOS varactor test structure regards to control voltage for different temperatures. The DAC is not included for this measurement                                                                                                                                                                                |

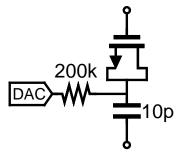

| 8.8  | Circuit implementation of the programmable varactor used in the tunable RLC resonator                                                                                                                                                                                                                                                               |

| 8.9  | (a) Simplified model of RLC tank including negative resistor. (b)  Load impedance calculation of RLC tank including negative resistor and bypass circuit. (c) Equivalent load impedance108                                                                                                                                                          |

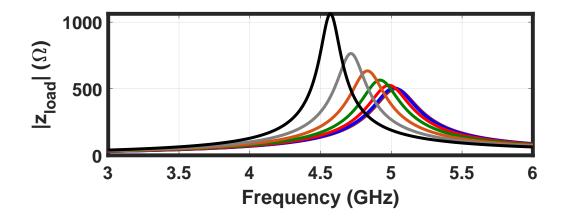

| 8.10 | Effect negative resistor $g_{\rm m}$ on magnitude of RLC resonator.<br>$(R_{\rm r}{=}500\Omega,C_{\rm r}{=}1{\rm pF},L_{\rm r}{=}1{\rm nH},R_{\rm s}{=}10\Omega,C_{\rm s}{=}20{\rm pF},{\rm and}$ $g_{\rm m}{=}0{-}60{\rm mS})$                                                                                                                     |

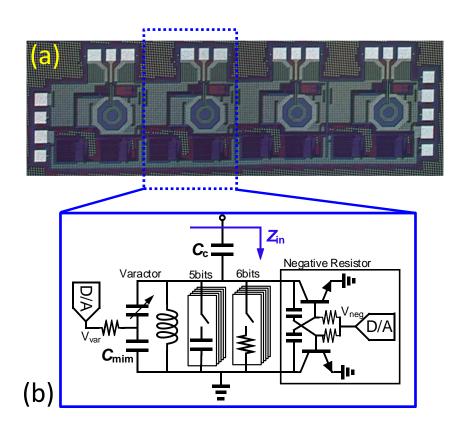

| 8.11 | (a) Programmable RLC resonators test structure. (b) Correspond schematic design                                                                                                                                                                                                                                                                     |

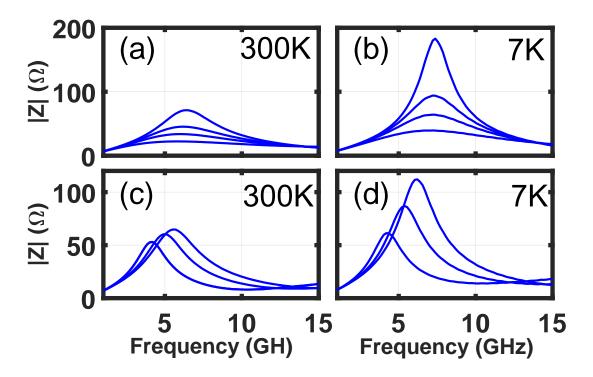

| 8.12 | Sample on-water measurement results of input impedance magnitude of the programmable RLC resonator (the version without coupling capacitor). (a) Different states for the parallel resistor at room temperature. (b) Different states for the parallel resistor at 7 K temperature. (c) Different states for the parallel capacitor at room temperature. (d) Different states for the parallel capacitor at 7 K temperature |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

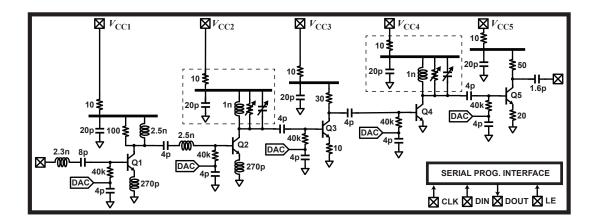

| 8.13 | LNA schematic. The circuitry in the dashed boxes is further described in Fig. 8.11. Transistor dimensions: $Q_1$ : $3 \times 0.09 \mu\text{m} \times 10 \mu\text{m},  Q_2$ : $1 \times 0.09 \mu\text{m} \times 10 \mu\text{m},  Q_3$ : $1 \times 0.09 \mu\text{m} \times 10 \mu\text{m},  Q_4$ : $1 \times 0.09 \mu\text{m} \times 10 \mu\text{m},  Q_5$ : $2 \times 0.09 \mu\text{m} \times 10 \mu\text{m}$                |

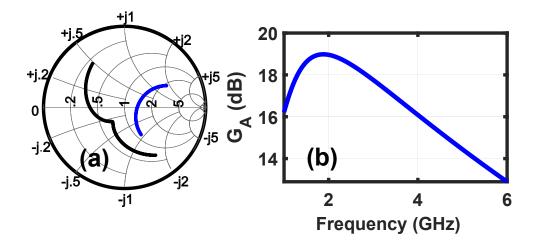

| 8.14 | (a) Cryogenic simulation noise optimum impedance (blue) and conjugate of the input impedance (black) for 3-6 GHz frequency range. (b) LNA First stage cryogenic available power gain of the LNA. Both of these simulations are when LNA is in wideband state                                                                                                                                                                |

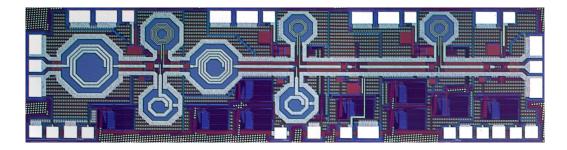

| 8.15 | Chip micrograph. The chip dimensions are $0.75\mathrm{mm} \times 2.8\mathrm{mm} \dots 114$                                                                                                                                                                                                                                                                                                                                  |

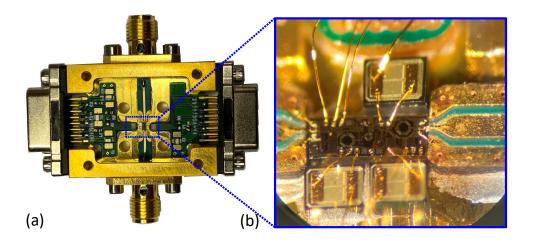

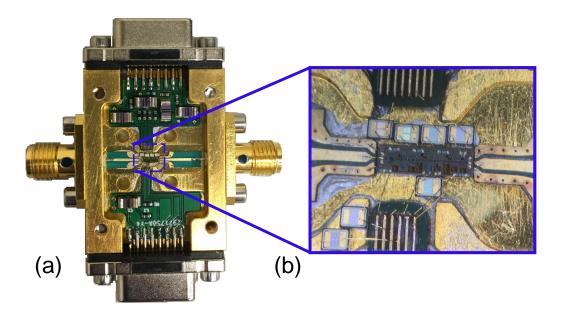

| 8.16 | <ul> <li>(a) The amplifier was packaged within a module for characterization at cryogenic temperatures.</li> <li>(b) Photograph showing the packaged IC. The RF signal enters on the left and leaves on the right.</li> <li>10 nF silicon capacitors are incorporated in close proximity of the IC to optimize the grounding of the collector biases</li></ul>                                                              |

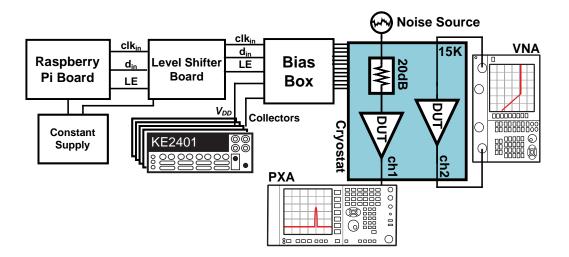

| 8.17 | The cryogenic measurement setup is used for noise characterization and scattering parameters. Five KE2401 are used in the measurement setup because of DC current sensing requirements of the measurement. However, one supply should be enough because 0.3 V is the common voltage for the collectors                                                                                                                      |

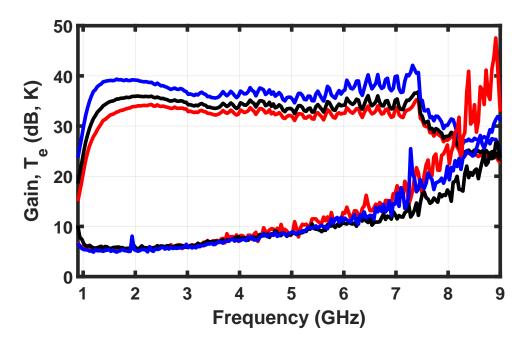

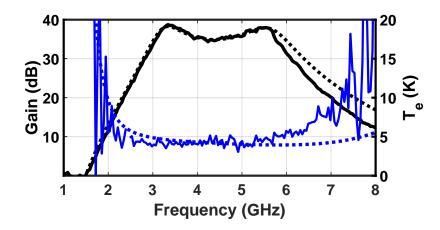

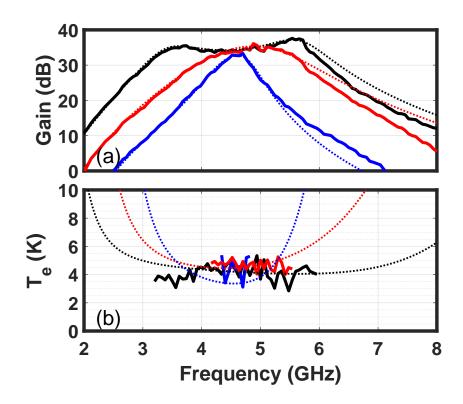

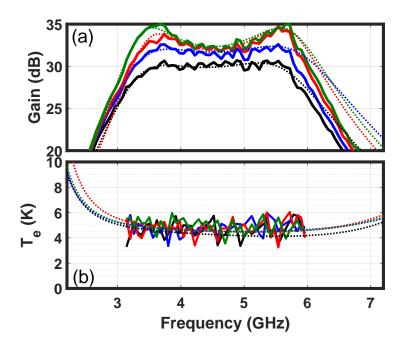

| 8.18 | Measured (solid lines) and simulated (dotted lines) Gain and noise temperature of the LNA at a physical temperature of 16 K when tuned for wideband operation. In this configuration, the LNA drew 1.8 mW from a 0.3 V supply                                                                                                                                                                                               |

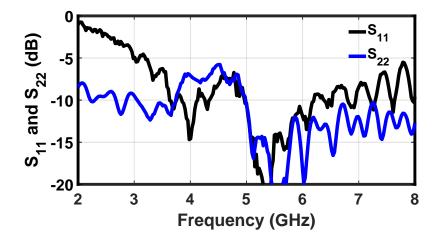

| 8.19 | Cryogenic measurement of input and output matching in wideband                                                                                                                                                                                                                                                                                                                                                              |

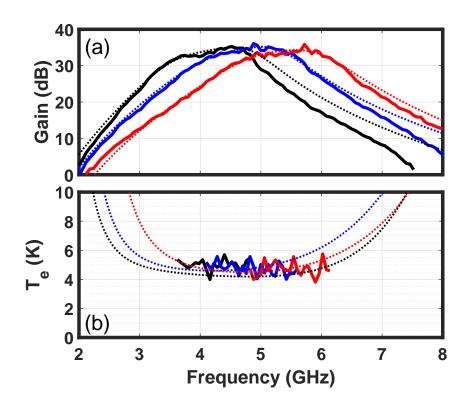

| 8.20 | (a) | Gain and (b) noise simulation (dotted lines) and measurement (solid lines) for the LNA at a physical temperature of 16 K when tuned for different bandwidths. The center frequency for these measurements was set to 4.4 GHz. The power consumed from the 0.3 V supply for the wide-bandwidth, medium-bandwidth, and narrow-bandwidth settings was 1.9, 2.9, and 2.7 mW, respectively                                                                                                                                              |

|------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

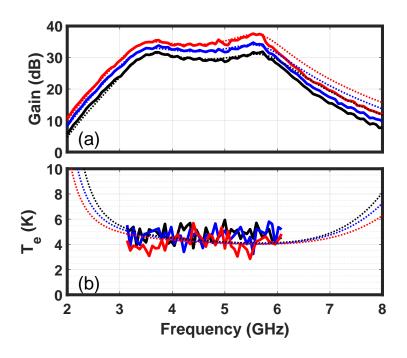

| 8.21 | (a) | and (b) Gain and noise simulation (dotted lines) and measurement (solid lines) of the LNA at a physical temperature of 16 K when configured for different center frequencies. When configured for center frequencies of 4, 4.8, and 5.5 GHz, the chip drew 2.0, 2.2, and 1.7 mW from the 0.3 V supply, respectively                                                                                                                                                                                                                |

| 8.22 | (a) | and (b) Gain and noise measurements of the LNA at a physical temperature of 16 K when configured for different center frequencies with around 250 MHz bandwidth                                                                                                                                                                                                                                                                                                                                                                    |

| 8.23 | (a) | and (b) Gain and noise simulation (dotted lines) and measurement (solid lines) of the LNA at a physical temperature of 16 K when configured for different absolute gain values122                                                                                                                                                                                                                                                                                                                                                  |

| 8.24 | (a) | and (b) Gain and noise measurements of the LNA at a physical temperature of 16 K when configured for different ripples of 0, 0.1, 1, 2, and 3 dB                                                                                                                                                                                                                                                                                                                                                                                   |

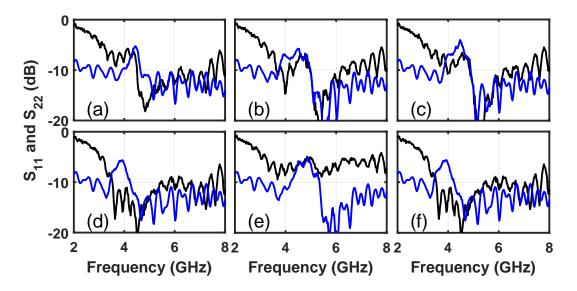

| 8.25 | Me  | easured $S_{11}$ (black) and $S_{22}$ (blue) at a physical temperature of 16 K when tuned for different bandwidths and center frequencies. Top row: The center frequency for these measurements was set to 4.4 GHz. The power consumed from the 0.3 V supply for the (a) narrow-bandwidth, (b) medium-bandwidth, and (c) wide-bandwidth settings was 1.9, 2.9, and 2.7 mW, respectively. Bottom row: center frequencies of (d) 4, (e) 4.8, and (f) 5.5 GHz, the chip drew 2.0, 2.2, and 1.7 mW from the 0.3 V supply, respectively |

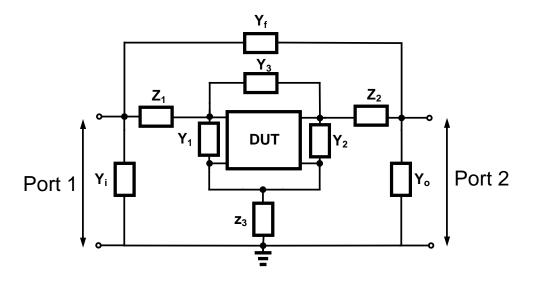

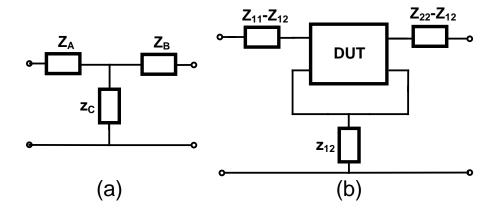

| A.1  | Sar | mple DUT model including parasitic components of test structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

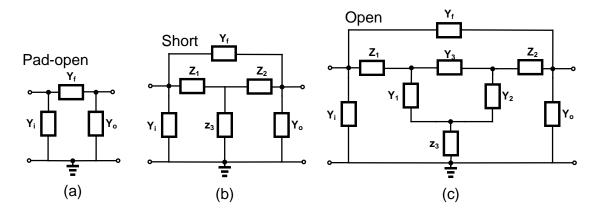

| A.2  | De  | embedding test structures model. (a) Pad-open (b) Short (c) Open                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| B.1  | De  | embedding of measurement setup DC resistance . (a) DC model of short test structure (b) Resistance de embedding based on short test structure                                                                                                                                                                                                                                                                                                                                                                                      |

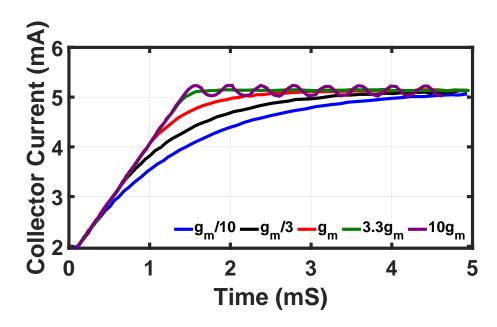

| C.1 | Time-doamin collector current as a pulse response of $V_{\text{ref}_{B}}$ for        |

|-----|--------------------------------------------------------------------------------------|

|     | different values of cryogenic $g_m$ . $R_{\text{sense}}=10 \Omega$ , $g_m=0.4$ , and |

|     | instrumentational amplifiers voltage gains are 10                                    |

## CHAPTER 1

## BACKGROUND MATERIAL AND MOTIVATION

Cryogenic low noise amplifiers are regularly used in a wide range of applications, including radio astronomy [62], quantum computing [11, 13], and fundamental physics research [41]. For many years, InP high-electron-mobility transistors (HEMT) were the only choice for the implementation of these amplifiers [19, 91]. In the last decade, it is shown that SiGe HBT is a promising choice for these applications [93, 14] particularly for low power purposes [63] and lower than 10 GHz frequency range. However, state-of-the-art readout systems in different applications require larger arrays, and consequently, higher scalability and better noise performance for cryogenic LNAs are desired. For example, currently, 54 qubits quantum processor is the state of the art [7], and scaling quantum computers to million qubits is required for practical quantum computers [12], and consequently, it demands implementation of a massive amount of microwave electronics blocks, including scalable, high-performance cryogenic LNAs.

Here in this chapter application of the cryogenic LNAs are described as a motivation for the dissertation. Particularly, it is focused on the applications of the LNAs which are designed in the next chapters of the dissertation.

## 1.1 Need for Highly Scalable Integrated Cryogenic LNAs

#### 1.1.1 Terahertz Detection

The terahertz part of the spectrum (0.1–10 THz) is described as the final unexplored area of the spectrum. Even though human beings have relied on sun radiation (including terahertz band) since a long time ago, the development of terahertz

technologies started in the 1940s, and it was mostly about laboratory applications. Terahertz radiation is resistant to the well-known approaches used for infrared and microwave radiation detection, making it challenging. Despite the fact that the significant use of terahertz spectroscopy is for astronomers and chemists, detection of terahertz is an engineer's challenge [78].

Terahertz remote sensing is challenging because ambient moisture of Earth's atmosphere causes strong absorption at this frequency range. Moreover, unlike visible light and infrared detectors, terahertz detectors have not yet reached fundamental quantum limit characteristics. Therefore, there is still an opportunity for research in this field [84].

Signal to noise ratio of the detected signal is that of the signal current to the shot noise, namely [28]:

$$SNR = \frac{i_{sig}}{i_{n,shot}} = \frac{\Phi_{p,sig}\eta q}{\sqrt{2q\bar{i}\Delta f}} = \frac{\Phi_{p,sig}\eta q}{\sqrt{2q(\Phi_{p,sig}\eta q + \phi_{p,bkg}\eta q)\Delta f}},$$

(1.1)

In which,  $\Phi_{p,sig}$  and  $\Phi_{p,bkg}$  are desired signal and background noise flux and  $\eta$  is quantum efficiency (electrons per photon). Depends on the type of the telescope (ground-based or space-based) the dominant noise contribution can be the shot noise generated by the signal-power envelope or background noise. With a weak signal source detected against a large background which is the most common situation, the dominant shot noise contribution is the shot noise of the background ( $\Phi_{bkg} \gg \Phi_{sig}$ ). The background-limited infrared photo-detector (BLIP) can be calculated from the below equation:

$$SNR_{BLIP} \simeq \frac{\Phi_{p,sig}\eta}{\sqrt{2\Phi_{p,bkg}\eta\Delta f}} = \Phi_{p,sig}\sqrt{\frac{\eta\tau}{\Phi_{p,bkg}}},$$

(1.2)

It shows the  $SNR_{BLIP}$  is inversely proportional to the square root of the background flux; so, reducing the background photon flux increases the SNR. The ultimate performance of the detectors is reached when the readout (including both detector and

LNA) input-referred noise temperature is low (more than a factor of 3–5) compared to the photon noise.

The performance of BLIP detectors can be improved by reducing the background photon flux ( $\Phi_{p,bkg}$ ). This can happen by two approaches. First, a cryogenic or reflective spectral filter for limiting the spectral band. Second, a cooled shield to limit the angular field of view of the detector. The first approach will eliminate background radiation from out-of-spectrum regions. In conclusion, the best detectors yield background-limited directives in a narrow field of view [56].

All radiation detection of terahertz can be divide into two main groups: 1. incoherent Detection and 2. Coherent Detection. Here I briefly describe these two approaches and the pros and cons of each.

#### 1.1.1.1 Incoherent Detection

Incoherent detection is done by direct sensors, which allow just amplitude of the signal, and typically, it has wide instantaneous bandwidth. Incoherent detection provides more effortless scalability than a coherent approach but with lower spectral resolution, and it is also commonly used for ultraviolet, infrared, and visible directions. The schematic of a typical incoherent detection is shown in Fig. 1.1, in which  $W_S$  is the desire signal power and  $W_B$  is background radiation power. Usually, an optic filter is located before detectors to remove background radiation at frequencies other than the desired one. Most sensitive direct detectors are cooled to  $T \approx 0.1$ –0.3 K reaching noise equivalent power (NEP) limited by cosmic background radiation fluctuation.

The threshold power detected by direct detectors is higher than heterodyne because of the LNA's added thermal noise, which is why the noise performance of LNA is critical for this type of detector. On the other hand, the main advantage of direct detection is simplicity and the possibility to design a large array, which requires

**Figure 1.1.** Schematic of direct detection.  $W_S$  is the signal power and  $W_B$  is the background radiation power.

an array of LNAs and consequent power consumption considerations [35]. Power consumption of the LNA is also important for scalable coherent detection method.

Here in this dissertation, I am focusing on a specific type of incoherent detection technology: MKID. In Fig. 1.2 you can see 1800 pixels as an MKIDs array which will be implemented inside, and a millimeter-wavelength camera. Three different arrays are implemented inside the camera to cover 2, 1.4, and 1.1 mm wavelengths. The total number of detectors is 7718, and 13 LNAs are required to read out detectors. The design and implementation of the LNAs for this particular example are described in the dissertation.