## Front-End Electronics of the ALICE dimuon trigger François Jouve, P. Rosnet, L. Royer

### ► To cite this version:

François Jouve, P. Rosnet, L. Royer. Front-End Electronics of the ALICE dimuon trigger. 2004, pp.1-88. <in2p3-00020310>

## HAL Id: in2p3-00020310 http://hal.in2p3.fr/in2p3-00020310

Submitted on 22 Jan 2004  $\,$

**HAL** is a multi-disciplinary open access archive for the deposit and dissemination of scientific research documents, whether they are published or not. The documents may come from teaching and research institutions in France or abroad, or from public or private research centers.

L'archive ouverte pluridisciplinaire **HAL**, est destinée au dépôt et à la diffusion de documents scientifiques de niveau recherche, publiés ou non, émanant des établissements d'enseignement et de recherche français ou étrangers, des laboratoires publics ou privés.

# FRONT-END ELECTRONICS OF THE ALICE DIMUON TRIGGER

#### F. Jouve, Ph. Rosnet, L. Royer,

and the Clermont-Ferrand group,

with the help of C. Fayard, M-L. Mercier, B. Ronfet and E. Sahuc.

Laboratoire de Physique Corpusculaire (LPC) de Clermont-Ferrand IN2P3/CNRS et Université Blaise Pascal 63177 Aubière Cedex - FRANCE

#### Abstract

This document presents the design and performance of the Front-End Electronics (FEE) developed for the ALICE dimuon trigger operating with Resistive Plate Chambers (RPCs) in streamer mode. This electronics, yet ready for production, is based on a dedicated ASIC designed at LPC Clermont-Fd.

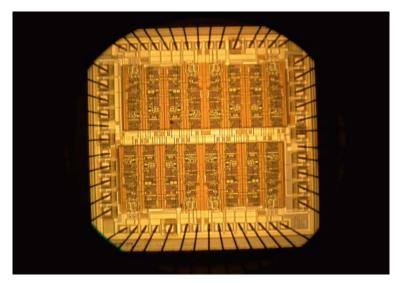

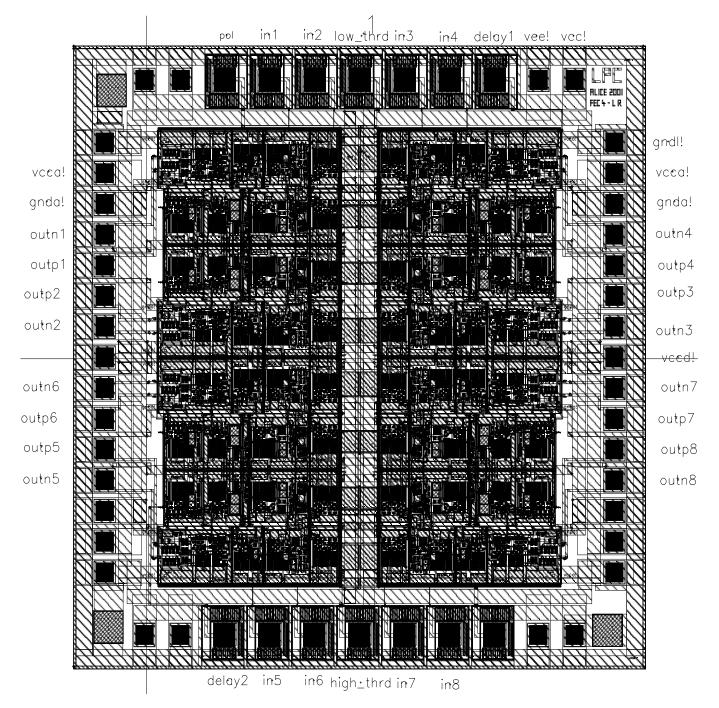

Picture of the front-end ASIC

## Contents

| 1        | Intr | oducti  | on                                          | 1        |

|----------|------|---------|---------------------------------------------|----------|

| <b>2</b> | Ger  | ieral p | resentation and environment                 | 3        |

|          | 2.1  | RPC 1   | pulses                                      | 3        |

|          | 2.2  | Mecha   | nical layout                                | 4        |

|          | 2.3  | Trigge  | r electronics considerations                | 5        |

|          | 2.4  | Requi   | rements for the FEE                         | 5        |

| 3        | From | nt-end  | chip design                                 | 7        |

|          | 3.1  |         | T discrimination technique                  | 7        |

|          | 3.2  |         | ple of one channel                          | 7        |

|          | 3.3  |         | atic of one channel                         | 9        |

|          |      | 3.3.1   | Comparator                                  | 10       |

|          |      | 3.3.2   | Polarity inversion                          | 10       |

|          |      | 3.3.3   | Latching                                    | 10       |

|          |      | 3.3.4   | Low threshold delay and monostable function | 10       |

|          |      | 3.3.5   | Coincidence                                 | 12       |

|          |      | 3.3.6   | Variable delay                              | 12       |

|          |      | 3.3.7   | Shaping                                     | 12       |

|          |      | 3.3.8   | LVDS driver                                 | 13       |

|          | 3.4  | Globa   | l schematic and layout                      | 13       |

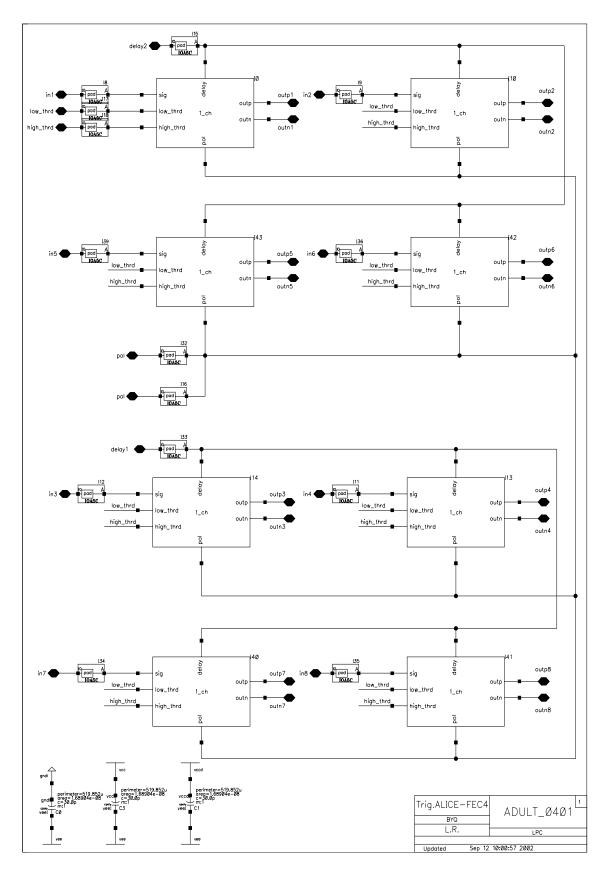

|          |      | 3.4.1   | Global schematic                            | 13       |

|          |      | 3.4.2   | Global layout                               | 14       |

|          | 3.5  | Result  | s of simulations                            | 17       |

|          |      | 3.5.1   | Comparators                                 | 17       |

|          |      | 3.5.2   | ADULT system                                | 18       |

|          |      | 3.5.3   | Statistical simulations                     | 18       |

| 4        | Б    | , I     |                                             | 0.0      |

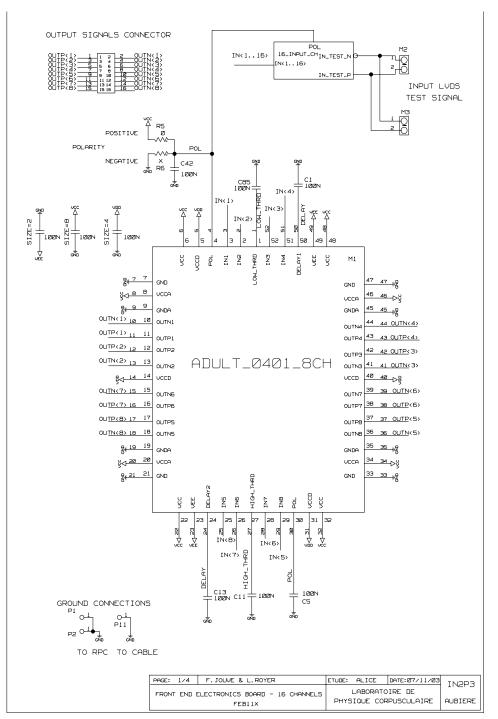

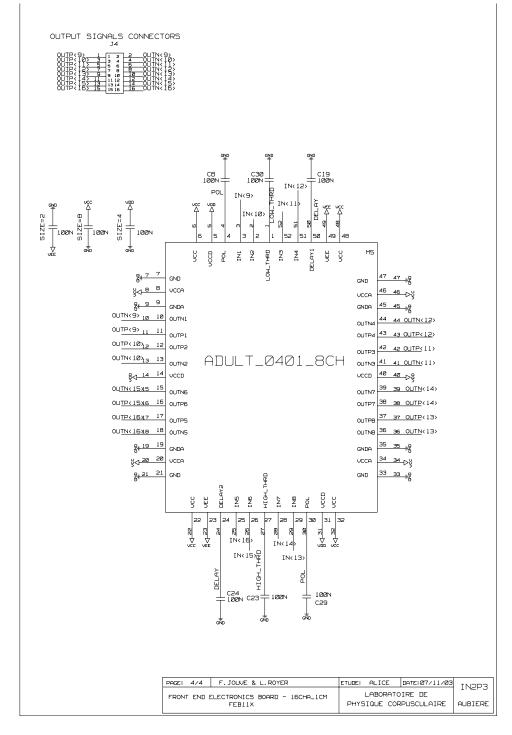

| 4        |      |         | boards design                               | 23       |

|          | 4.1  | -       | ntegration                                  | 23       |

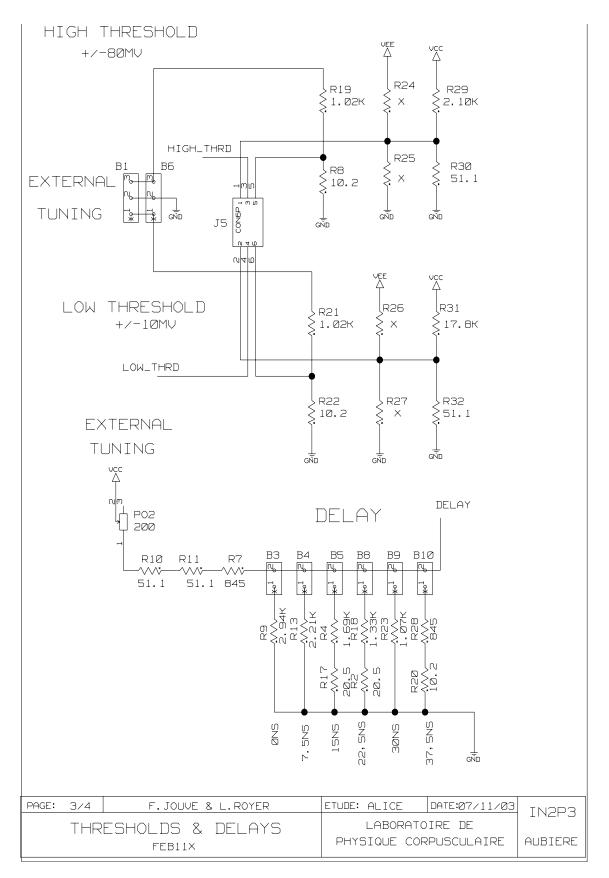

|          |      | 4.1.1   | Thresholds                                  | 23       |

|          |      | 4.1.2   | Delay                                       | 23       |

|          |      | 4.1.3   | Polarity                                    | 24       |

|          | 4.9  | 4.1.4   | Signal and output connectors                | 24       |

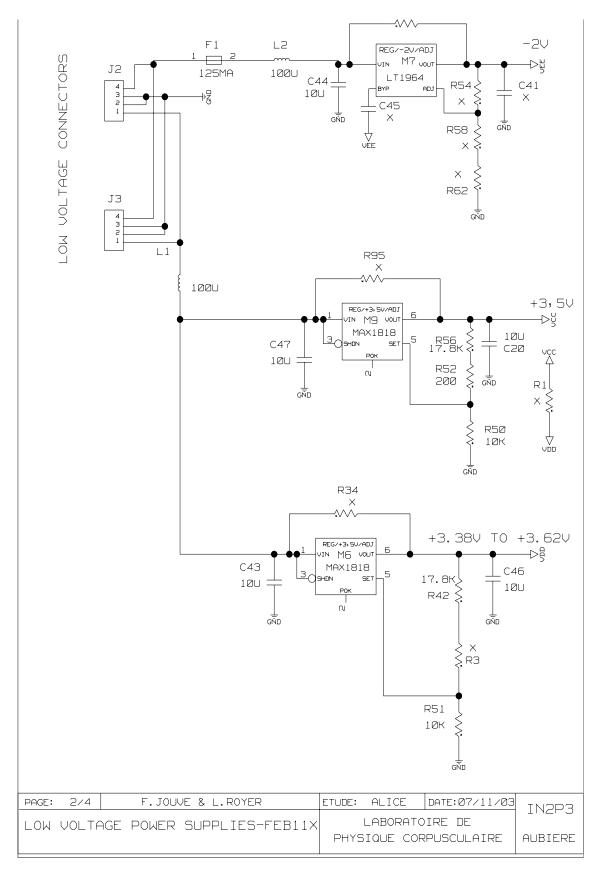

|          | 4.2  |         | oltage power supplies                       | 24<br>25 |

|          |      | 4.2.1   | Low voltage connectors                      | 25       |

|          |      | 4.2.2   | Regulation                                  | 25       |

|          |      | 4.2.3   | Over current protections                    | 25       |

|          | 4.0  | 4.2.4   | Decoupling                                  | 26       |

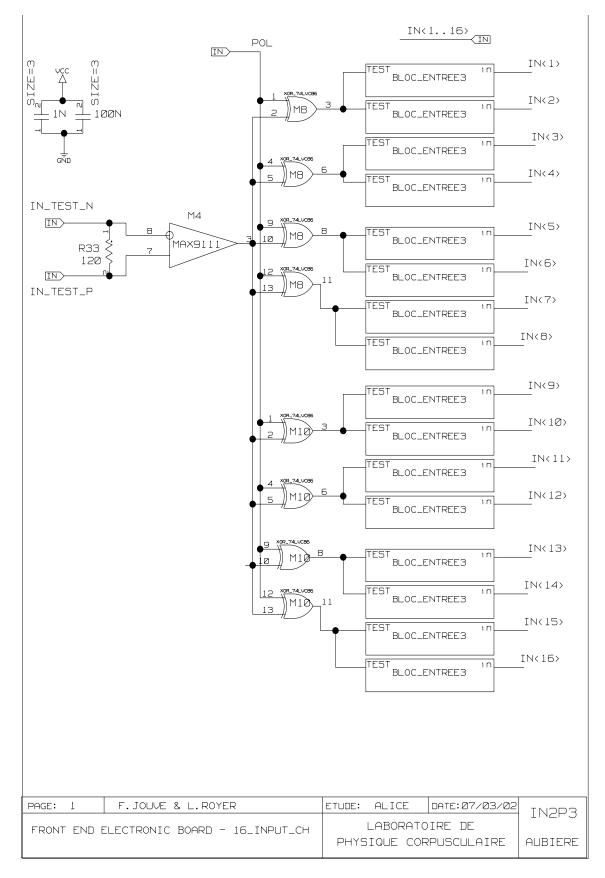

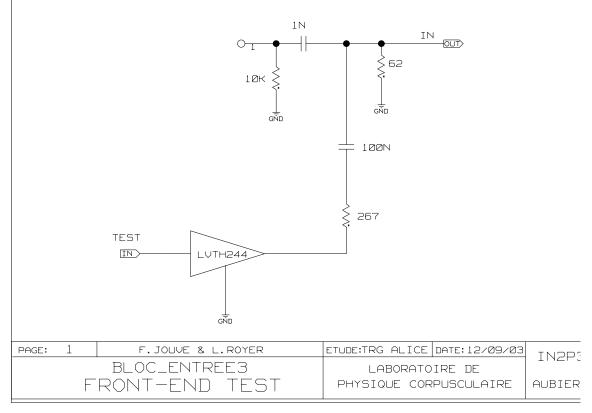

|          | 4.3  |         | End Test (FET) system                       | 26       |

|          | 4.4  | -       | It signal cables                            | 27       |

|          | 4.5  |         | ation boards                                | 28       |

|          | 4.6  | Summ    | ary                                         | 29       |

| <b>5</b>     | Pow                                             | ver supply considerations                                                                                                                      | 33 |  |  |  |  |

|--------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|--|

|              | 5.1                                             | Grounding and shielding overview                                                                                                               | 33 |  |  |  |  |

|              |                                                 | 5.1.1 Constraints                                                                                                                              | 34 |  |  |  |  |

|              |                                                 | 5.1.2 Proposal $\ldots$                                       | 34 |  |  |  |  |

|              | 5.2                                             | Power supply distribution                                                                                                                      | 34 |  |  |  |  |

|              | 5.3                                             | Detector Control System                                                                                                                        | 35 |  |  |  |  |

| 6            | Cha                                             | racterization results                                                                                                                          | 39 |  |  |  |  |

| -            | 6.1                                             | Chip evolution                                                                                                                                 | 39 |  |  |  |  |

|              | 6.2                                             | Test in laboratory                                                                                                                             | 39 |  |  |  |  |

|              |                                                 | 6.2.1 Comparators                                                                                                                              | 39 |  |  |  |  |

|              |                                                 | 6.2.2 ADULT system                                                                                                                             | 40 |  |  |  |  |

|              |                                                 | 6.2.3 One shot system                                                                                                                          | 40 |  |  |  |  |

|              |                                                 | 6.2.4 Variable delay                                                                                                                           | 41 |  |  |  |  |

|              |                                                 | 6.2.5 LVDS output signal                                                                                                                       | 41 |  |  |  |  |

|              |                                                 | 6.2.6 Temperature sensitivity                                                                                                                  | 41 |  |  |  |  |

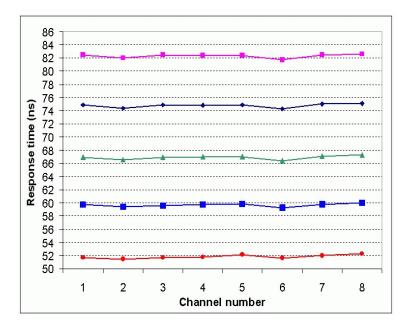

|              |                                                 | 6.2.7 Response time dispersion (between channels and between chips) .                                                                          | 42 |  |  |  |  |

|              |                                                 | 6.2.8 Cross-talk                                                                                                                               | 42 |  |  |  |  |

|              |                                                 | 6.2.9 External thresholds uniformity                                                                                                           | 42 |  |  |  |  |

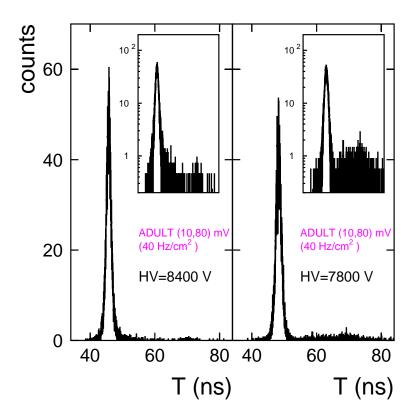

|              | 6.3                                             | Beam tests at CERN                                                                                                                             | 43 |  |  |  |  |

|              | 6.4                                             | Pre-serie production                                                                                                                           | 45 |  |  |  |  |

|              |                                                 | 6.4.1 Tests on bench $\ldots$                                                                                                                  | 45 |  |  |  |  |

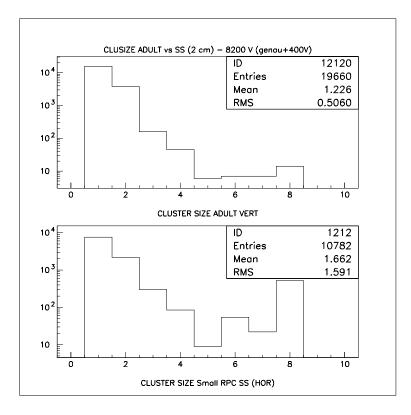

|              |                                                 | 6.4.2 Tests on RPC $\ldots$                                   | 47 |  |  |  |  |

|              | 6.5                                             | Radiation hardness                                                                                                                             | 49 |  |  |  |  |

|              |                                                 | $6.5.1  \text{Neutron test} \dots \dots$ | 49 |  |  |  |  |

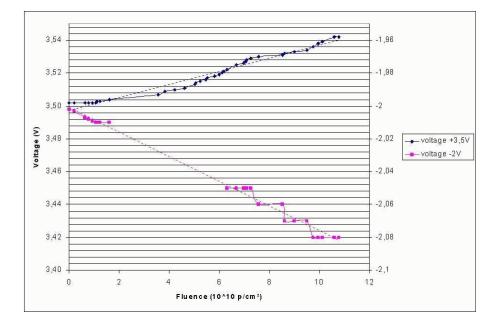

|              |                                                 | $6.5.2  \text{Proton test}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                   | 51 |  |  |  |  |

|              |                                                 | $6.5.3  Photon test  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                                                          | 51 |  |  |  |  |

|              |                                                 | 6.5.4 Conclusion $\ldots$                                     | 51 |  |  |  |  |

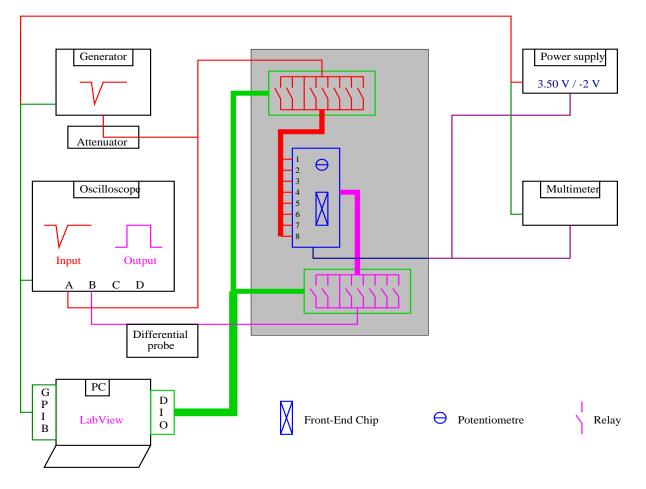

| 7            | Test                                            | t bench and maintenance                                                                                                                        | 53 |  |  |  |  |

|              | 7.1                                             | Test bench design                                                                                                                              | 53 |  |  |  |  |

|              | 7.2                                             | Single point failures and maintenance                                                                                                          | 55 |  |  |  |  |

| 8            | Mile                                            | estones and conclusions                                                                                                                        | 59 |  |  |  |  |

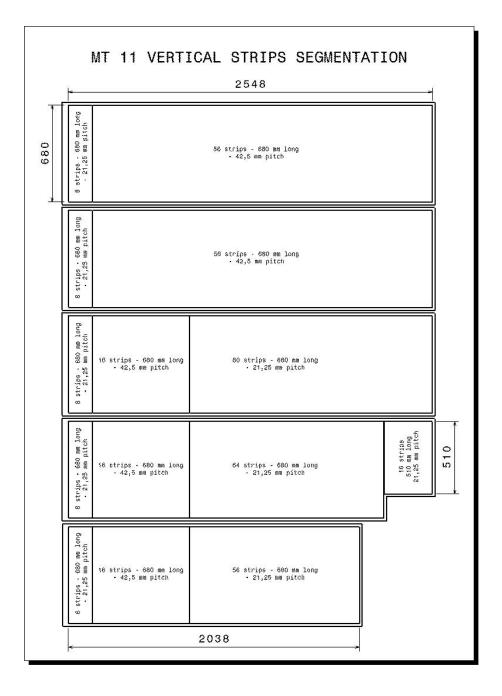

| $\mathbf{A}$ | Stri                                            | ps segmentation                                                                                                                                | 61 |  |  |  |  |

|              |                                                 |                                                                                                                                                |    |  |  |  |  |

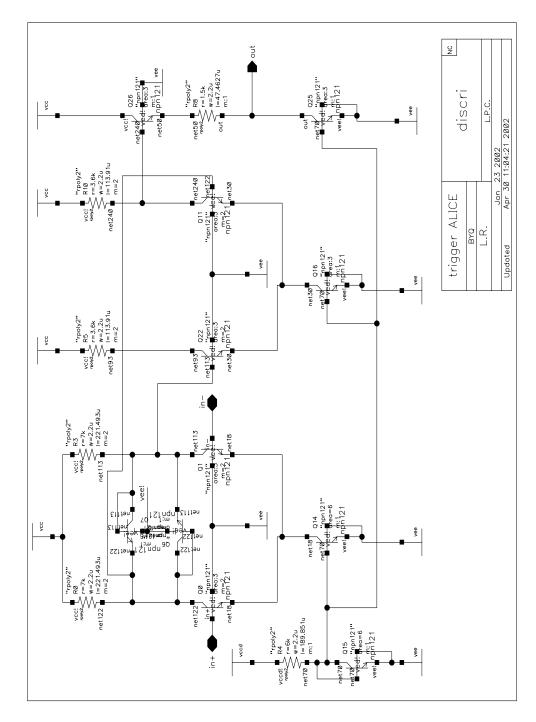

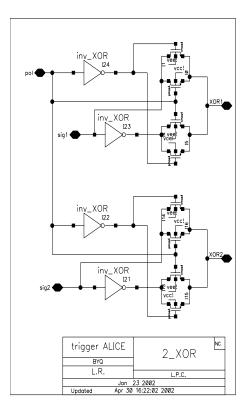

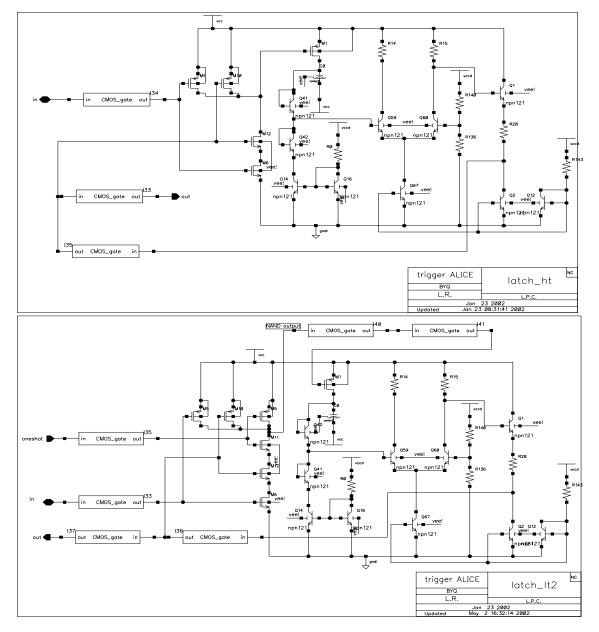

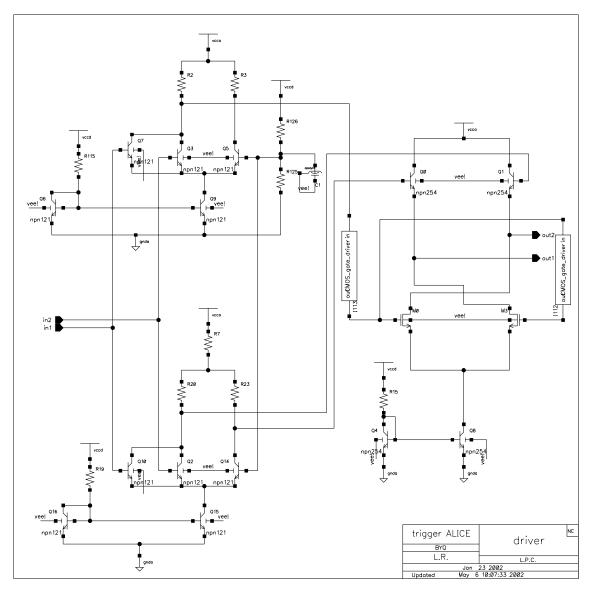

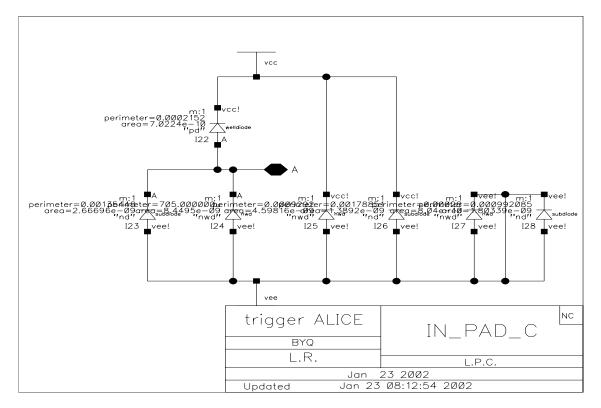

| в            | Froi                                            | nt-end chip electronics schemes                                                                                                                | 63 |  |  |  |  |

| $\mathbf{C}$ | From                                            | nt-end boards electronics schemes for FEB11X                                                                                                   | 74 |  |  |  |  |

| D            | Elec                                            | ctronics components for FEB11X                                                                                                                 | 80 |  |  |  |  |

| $\mathbf{E}$ | E Production Readiness Review recommendations 8 |                                                                                                                                                |    |  |  |  |  |

| Re           | efere                                           | nces                                                                                                                                           | 85 |  |  |  |  |

| GI           | lossa                                           | rv                                                                                                                                             | 87 |  |  |  |  |

|              |                                                 | U C                                                                                                                                            |    |  |  |  |  |

## 1 Introduction

ALICE <sup>1</sup> (A Large Ion Collider Experiment) [1] is the only one detector dedicated to nucleus-nucleus collisions at LHC (the Large Hadron Collider) which is foreseen to start running in year 2007.

The forward part of ALICE consists of a dimuon spectrometer [2] which is aimed to study the charmonium and bottomium decay in the  $\mu^+\mu^-$  channel. Indeed, their yield in heavy ion collision should provide a clear signal for the QGP (Quark-Gluon Plasma) formation which is expected to occur according to lattice QCD (Quantum Chromo-Dynamic) calculations.

x y Absorber x y Tracking chambers Magnet Filter

The general setup of the dimuon arm is displayed in figure 1.

Figure 1: Layout of the forward dimuon spectrometer of the ALICE experiment.

Its angular acceptance is  $2^{\circ} < \theta < 9^{\circ}$  corresponding thus to the pseudo-rapidity range  $2.4 < \eta < 4$ . It consists of a front and small angle absorber, a large dipole magnet, ten high granularity tracking chambers, a muon filter and a trigger system.

The dimuon trigger is included in the level 0 ALICE trigger (L0). It enables to select events containing muons in the forward direction. An online cut on transverse momentum  $(p_{\perp})$  is applied on the charged particles reaching the trigger chambers.

A dedicated trigger electronics based on a geometrical algorithm is developed for this goal.

The trigger system consists of two  $\approx (6 \times 6) \text{ m}^2$  area stations, called MT1 and MT2, located approximatively 16 m and 17 m from the interaction point. Each station is made of two RPC planes (Resistive Plate Chambers[3]) which are readout in X and Y directions with a Front-End Electronics (FEE) amounting to 20992 electronics channels.

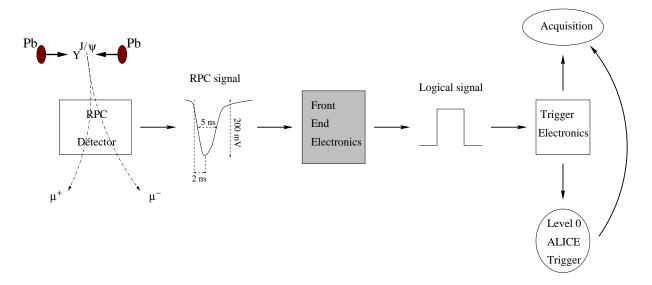

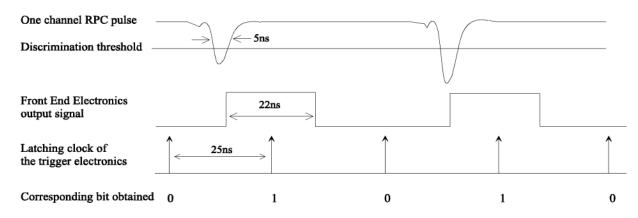

The role of the FEE is to transmit a logical signal to the trigger electronics when a valid analog pulse has been read on the corresponding channel, as illustrated in figure 2.

The goal of the present document, prepared for the Production Readiness Review (PRR) of the FEE, is to give a detailed status report of the FEE in view of its production for the experiment.

<sup>&</sup>lt;sup>1</sup>The main acronym used are reported in a Glossary at the end of the document.

Figure 2: Role of the Front-End Electronics (FEE) of the ALICE dimuon trigger.

This PRR begins with an overview that the FEE must fulfill. The electronics is then described in two steps: the ASIC especially designed for this application and its implementation on boards. Next, general considerations about grounding, power supply and Detector Control System (DCS) are discussed. A summary of all the tests performed both in laboratory and using beams at CERN is given. Finally, the test bench designed to check the characteristics of the whole production is described.

## 2 General presentation and environment

#### 2.1 RPC pulses

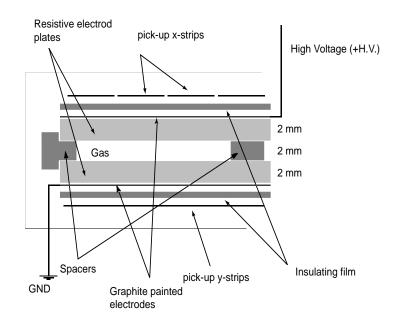

The single 2 mm gas gap RPCs [4] (fig. 3) operate in streamer mode. The choice of the bakelite electrode resistivity (around  $10^9 \Omega.cm$ ) and the gas mixture (49% Ar + 7%  $iC_4H_{10} + 40\% C_2H_2F_4 + 4\% SF_6$ ) have been optimized in beam tests. At present, the fraction of SF<sub>6</sub> has been decreased to 1% to improve the aging of the RPCs.

These characteristics allow to reach a good efficiency (about 98%) up to a rate of  $500 \text{ Hz/cm}^2$ , well above the expected maximum flux of particles in nucleus-nucleus collision at the LHC, which is about  $40 \text{ Hz/cm}^2$  [2]. The best tuning for efficiency is achieved with a high voltage (HV) at 400 V above the "knee", that is typically about 8 kV (with 1% SF<sub>6</sub>), fixing thus the normal operating conditions for these RPCs.

Figure 3: Cross-section of a Resistive Plate Chamber (RPC) used in the ALICE dimuon trigger system.

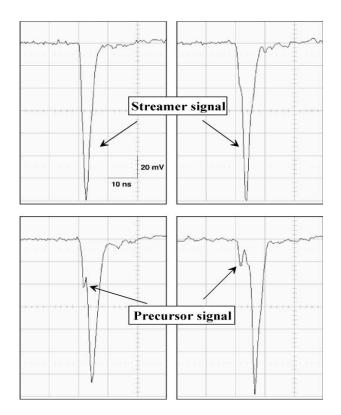

Examples of pulses developed with this type of RPC are displayed in figure 4. It appears that the pulse shape in streamer mode has the following features (see ref. [7] for more details).

- A first peak, called precursor in the following, is fixed in time relatively to the passing time of the particle through the chamber:

- -2 ns rise time (typ <sup>2</sup>),

- $-5 \,\mathrm{ns}$  width (typ),

- -(20-50) mV amplitude (typ).

- A second peak, called streamer in the following, which may be delayed from the precursor by several nano-seconds (delay denoted by  $\Delta t_{p-s}$ ):

<sup>&</sup>lt;sup>2</sup>typ: typical value.

- -2 ns rise time (typ),

- $-5 \,\mathrm{ns}$  width (typ),

- -(100-200) mV amplitude (typ), some pulses may reach several volts.

The mean value of the delay between the precursor peak and the streamer peak depends on the high voltage applied to the RPC. In normal operating conditions of the RPC, the fraction of events with a streamer delayed by more than 15 ns is quite small (about one percent).

Figure 4: Typical pulses picked-up on a single gas gap RPCs operating in streamer mode, with a digital oscilloscope (1 GHz bandwidth) via a short BNC cable (50  $\Omega$  impedance).

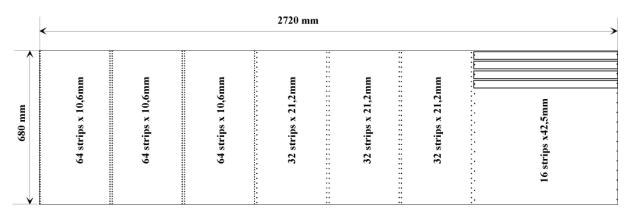

#### 2.2 Mechanical layout

The two trigger stations, called MT1 and MT2, are composed of two chamber planes. Each half chamber plane is made of 9 independent RPC modules, namely 72 modules at total, equipped of X and Y strips on each side as displayed on figures 51 and 52 (see appendices A).

Figures 51 and 52 display also the layout of different types of strips whose characteristics are given in table 1. The number of strips amounts to 20992 for the whole trigger system.

The distance between the two stations is of 1 m, while the distance between the two planes inside a station is 17 cm. Thus there is about 6 cm free space between two chamber planes of the same station.

|                   | Strip 2 | X (horizoi | Strip $Y$ (vertical) |      |       |      |

|-------------------|---------|------------|----------------------|------|-------|------|

| Strip pitch (mm): | MT1     | 10.625     | 21.25                | 42.5 | 21.25 | 42.5 |

|                   | MT2     | 11.3       | 22.6                 | 45.2 | 22.6  | 45.2 |

| Number of stri    | ips     | 3840       | 8448                 | 2688 | 3584  | 2432 |

| Total             |         | 14976      |                      | 60   | )16   |      |

Table 1: Total number of strips as a function of their pitch and their orientation X or Y, the numbers being the same for the two stations MT1 and MT2. The length of the strips varies from 170 to 720 mm.

#### 2.3 Trigger electronics considerations

The trigger electronics is divided into three parts: local (234 boards), regional (16 boards) and global (1 board).

The main function of the local trigger is to do a backup of all signals coming from the RPC strips (sequence called bit-pattern) in a pipeline memory, and to identify single tracks with  $p_{\perp}$  above pre-defined cuts by using a dedicated trigger algorithm.

The regional and next global electronics collect the information from the local boards in order to select dimuon or single muon events. This final decision has to be delivered to the general ALICE L0 trigger < 700 ns after the collision, and the L0 response must be delivered to the ALICE sub-detectors within  $1.2 \,\mu$ s.

Due to the 40 MHz LHC clock (beams collide every 25 ns) the bit-pattern must be received by the local trigger boards within a window of less than 25 ns.

The rack housing the trigger electronics will be placed on the edge above the detector [6], such that the maximum cable length from the RPC to the trigger electronics is 20 m.

Therefore the dedicated Front-End Electronics (FEE) will be placed directly on the trigger detector to pick-up the RPC signals and to deliver a logical signal to the trigger electronics, as described in figure 5.

When taking all the timing constraints into account, the response time of the FEE should be as fast as possible, typically less than 50 ns.

Figure 5: Electronics timing for one channel of the ALICE dimuon trigger.

#### 2.4 Requirements for the FEE

In summary, the requirements for the Front-End Electronics is given in table 2.

| v 1                           | itementos for the Front-End Electromes (FEE).                                                                                   |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Number of channels            | 20992                                                                                                                           |

| Input signal                  | precursor ( $\approx 50 \mathrm{mV}$ ) + streamer ( $\approx 200 \mathrm{mV}$ )                                                 |

| (RPC streamer mode)           | with $\begin{cases} \text{rise time} = 2 \text{ ns} \\ \text{width} = 5 \text{ ns} \end{cases}$                                 |

| $\Delta t_{p-s}$              | (0  to  15)  ns                                                                                                                 |

| Output LVDS signal width      | $20\mathrm{ns} < w_{out} < 25\mathrm{ns}$                                                                                       |

| Maximum response time         |                                                                                                                                 |

| dispersion between channels   | $\pm 2\mathrm{ns}$                                                                                                              |

| Maximum response time         | $50\mathrm{ns}$                                                                                                                 |

| Maximum consumption / channel | $100\mathrm{mW}$                                                                                                                |

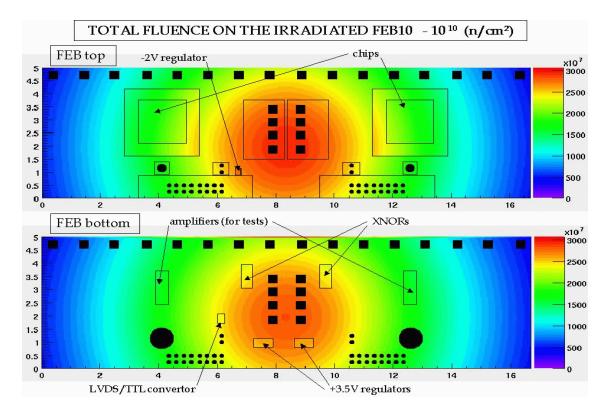

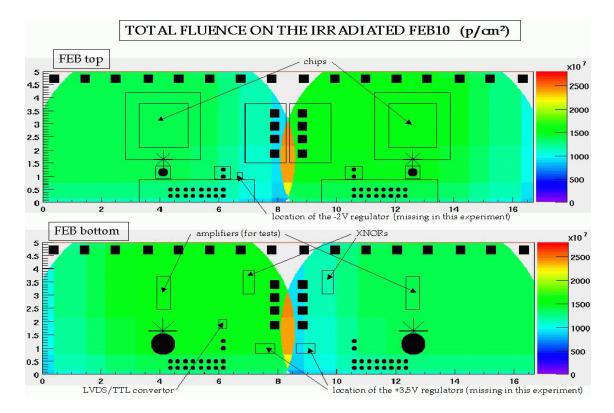

| Radiation hardness            | $ \left. \begin{array}{c} 10^{10}  \mathrm{n/cm}^2 \\ 1  \mathrm{Gy} \end{array} \right\} \mathrm{over} \ 10 \ \mathrm{years} $ |

| Chip spares                   | 30%                                                                                                                             |

| Board spares                  | 10%                                                                                                                             |

| Maximum price / channel       | 5 FCH                                                                                                                           |

| Number of channel / chip      | 8                                                                                                                               |

Table 2: Summary of the requirements for the Front-End Electronics (FEE).

- The FEE must be able to handle very fast signals delivered by RPCs and send an output logical signal to the trigger electronics.

- Because all 20992 FEE signals must be received by the trigger electronics within a window of less than 25 ns, a very careful timing is needed.

- To avoid using a special cooling system for the trigger detector, the power consumption per electronics channel must be lower than 100 mW. Therefore the maximum total power consumption of the front-end electronics will be of 2.1 kW directly dissipated in the cavern.

- The dimuon trigger detector is located over 16 m from the interaction point. Furthermore the absorber, the beam shielding and the filter protect the chambers against radiation damage. The maximum rates expected at the trigger station level, integrated over 10 years of LHC working, are [8]: 10<sup>10</sup> n/cm<sup>2</sup> for the neutron fluence and 1 Gy (100 rad) for the absorbed dose.

- Mainly for cost and consumption reasons, it has been decided to develop this dedicated electronics in micro-electronics technology. Furthermore, the strip segmentation of the detector and trigger electronics imply the grouping of 8 channels per chip (or ASIC).

Basically the required FEE consists of a discriminator stage followed by a shaper. No amplification of the input signal is needed with RPC operating in streamer mode.

## 3 Front-end chip design

#### 3.1 ADULT discrimination technique

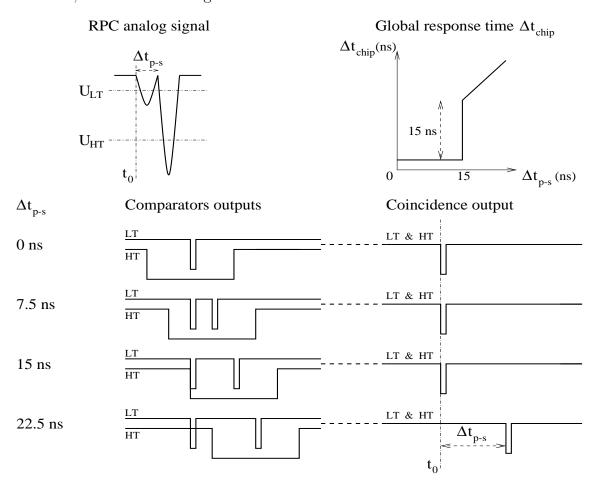

As described in reference [7], a standard single threshold discrimination technique to pickup the streamer signal of the RPC in the operating conditions gives a time resolution of about 3 ns. Furthermore, a double structure appears in the time distribution. This originates in the time fluctuation  $\Delta t_{p-s}$  of the streamer peak for the pulses developed in a RPC (fig. 4).

In order to improve the time resolution, a new discrimination technique has been developed at LPC Clermont-Fd. This technique takes advantage of the precursor time stability with respect to particle crossing through the RPC, by using two discriminators. The first one with a low threshold (typically  $U_{LT} = 10 \text{ mV}$ ) detects the precursor, and the second one with a high threshold (typically  $U_{HT} = 80 \text{ mV}$ ) validates the streamer one. This new discrimination technique is called ADULT (A DUaL Threshold).

The precursor detection (low threshold  $U_{LT}$ ) provides a good time reference. But due to its small amplitude, and to keep all advantages of the streamer mode (large signal/noise ratio and small cluster size), the validation of the RPC pulse is done by the streamer detection (high threshold  $U_{HT}$ ).

#### 3.2 Principle of one channel

This dedicated discrimination technique has been implanted in the Front-End Chip (FEC) developed at LPC Clermont-Fd. The AMS BiCMOS  $0.8 \,\mu\text{m}$  chosen technology is well adapted to the design of fast comparators with low input offset voltage.

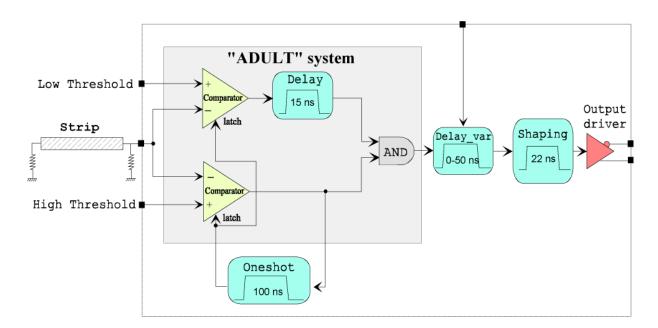

Figure 6: Block diagram principle of one single electronics channel.

The principle of this electronics is presented in figure 6. The main parts are the following:

• The ADULT discriminator stage is made of two fast comparators and a delay followed by an AND gate. The output signal of the low threshold comparator is delayed by about 15 ns, and then a coincidence with the output signal of the high threshold comparator is done. This delay value, optimized during cosmic ray and beam tests [7], is chosen according to the fact that the precursor peak comes earlier than 15 ns relatively to the streamer peak. Thus the coincidence output is in time with the latest of the two input signals, namely the low threshold comparator one, as long as the delay between the precursor and the streamer peaks is shorter than 15 ns, as illustrated in figure 7.

Figure 7: Timing of the output signal with the ADULT technique. The output of the low threshold comparator delayed by 15 ns is noted LT, and the one of the high threshold comparator is labeled HT. The output of the AND gate is noted LT & HT. The curve on top right illustrates the expected global response time  $(\Delta t_{chip})$  versus the streamer peak delay  $(\Delta t_{p-s})$  for a chip delaying by 15 ns the output of the low threshold comparator.

- An "oneshot" system prevents any channel from re-triggering during 100 ns. When the high threshold comparator detects a streamer, its output activates a monostable. The monostable output changes immediately and the new level is held during about 100 ns. The two comparators are disabled during this time.

- A remote control delay, up to 50 ns, and common for a whole chip (namely for the 8 channels of a chip) is tuned by a DC voltage. It allows to adjust the timing of

the output signal, if needed.

• The signal is converted into a 22 ns logical LVDS signal in order to drive a 20 m twisted pair cable. The LVDS standard is well adapted to transmit fast signals with weak consumption.

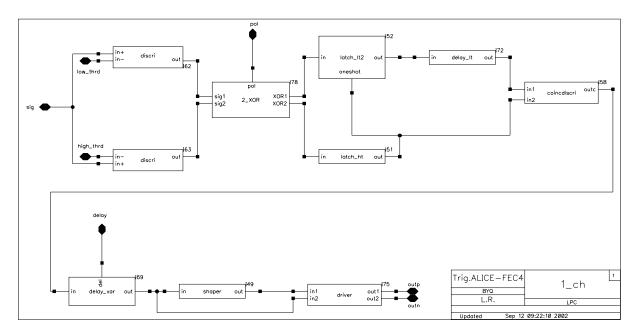

#### 3.3 Schematic of one channel

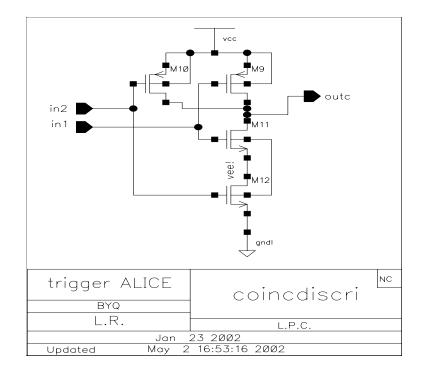

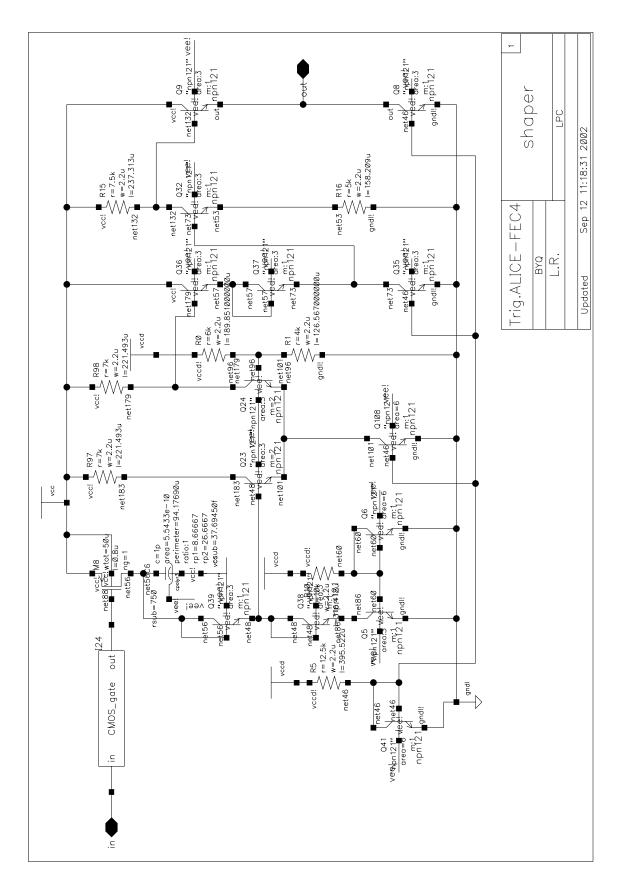

The schematic of one front-end electronics channel is composed of several blocks as displayed in figure 8. The input stage is made of 2 comparators called "discri", the upper one being used to discriminate the precursor pulse (low threshold), and the lower for the streamer pulse (high threshold). Each of them is followed by the "2\_XOR" block which can invert the polarity of the output comparator pulses, depending of the RPC pulse polarity. The polarity is selected by an external pin called "pol". The latching blocks "latch\_lt2" and "latch\_ht" deliver a logic pulse of fixed width independent of the comparator output signal duration. The "latch\_ht" block is also required to freeze the discrimination system during the "oneshot" period of 100 ns. The output of the low threshold latching block "latch\_lt2" is delayed by about 15 ns, as described above, and set into coincidence with the high threshold latched signal. This is done with the "coincdiscri" block to validate the precursor signal by the detection of a streamer pulse. Thus the coincidence output is in time with the latest of its two inputs signals which is the low threshold one, as long as the delay between the precursor and the streamer is shorter than 15 ns (fig. 7). This signal can be delayed in a range of 50 ns by an external DC voltage applied on the "delay" pin. The final 22 ns LVDS signal is obtained through the two last stages called "shaper" and "driver".

Figure 8: Block diagram of one single front-end electronics channel.

The design and performance of each of these blocks has been described in details in previous papers [9] [10].

Main and new (or updated) considerations are reported below.

#### 3.3.1 Comparator

The schematic of the comparator is displayed in figure 53 (appendices B). It is composed of two differential amplifiers followed by an emitter follower transistor Q26. The total gain is greater than 200 up to 100 MHz. The input noise voltage is dominated by thermal noise of the bipolar input transistors Q0 and Q1, but does not exceed  $100 \,\mu V$  RMS for the total frequency bandwidth. Bipolar transistors are preferred to MOS transistors, in order to minimize the input offset.

Two transistors used as diodes are inserted between the two collectors of Q0 and Q1 in order to prevent a slow response time for large RPC pulses due to saturation of the input stage.

#### 3.3.2 Polarity inversion

The two comparators deliver negative (up to down) or positive (down to up) signals according to the polarity of the RPC pulses which is positive for vertical Y strips and negative for horizontal X strips. Thus it is necessary to invert the signal in one of these two situations in order to always input the latching block with the same type of signal. The choice was made to invert for positive RPC pulses. This inversion is carried out with an XOR logic gate, whose the scheme is shown in figure 54 (appendices B). When the "pol" pin is plugged to the upper voltage  $V_{cc}$ , the outputs XOR1 and XOR2 are the inverted signals of respectively "sig1" and "sig2". When "pol" is grounded, the inputs are directly copied to the respective outputs.

#### 3.3.3 Latching

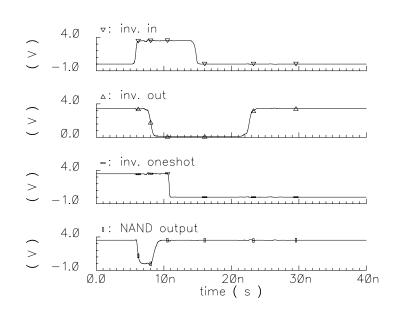

Two latching blocks have been designed. The "latch\_ht" block outputs a 100 ns logic signal when a streamer pulse is detected (high threshold). The "latch\_lt2" block delivers a 15 ns logic signal when the low threshold is crossed. The duration of this pulse is fixed and independent of the input pulse duration. A second input called "oneshot", directly connected to the "latch\_ht" block output, is required to prevent from new latching during 100 ns. The schematics of the two latching blocks are displayed in figure 55 (appendices B). In a first stage, a three (or only two for the "latch\_ht" block) inputs NAND gate is built with PMOS and NMOS transistors: the output state is low only when the three inputs are high. Typical simulated signals of the "latch\_lt2" block are drawn in figure 9. As the input "in" (after the CMOS gate) goes up to 3.5 V when the low threshold is overshot, the output of the NAND gate goes down. Few nanoseconds later, the state of the out pin (after the CMOS gate) goes down, producing thus the coming back of the NAND output to the high state. This pulse controls the PMOS gate of the monostable stage which delivers a 15 ns logic pulse to the next block "delay\_lt" (see the description of the monostable below).

The function of the "latch\_ht" is similar. It delivers a 100 ns logic pulse to the "oneshot" input of the "latch\_lt2" block and to the "coincdiscri" block.

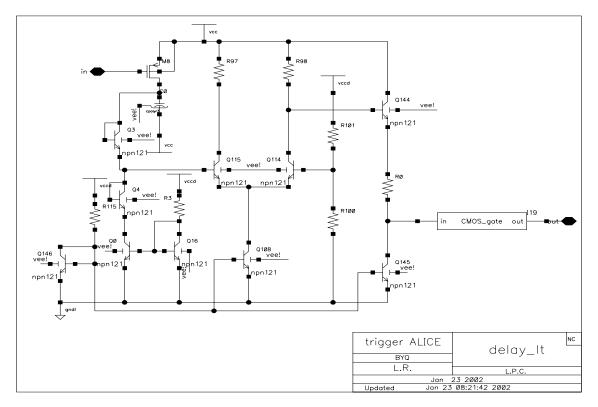

#### 3.3.4 Low threshold delay and monostable function

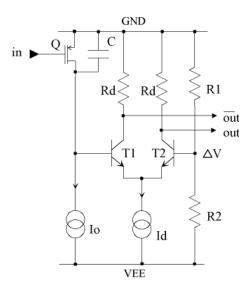

As previously discussed for the ADULT system, it is required to delay the low threshold discriminated signal by a fixed value, in order to guarantee that the reference time will be given by the precursor pulse. This function is carried out by a monostable structure as represented in figure 10. A constant current source  $I_0$  loads a capacitor C when the PMOS transistor Q, operating like a switch, is open. Then the base voltage of T1

Figure 9: Simulated signals for the low threshold latching block "latch\_lt2".

decreases with a constant slope proportional to  $I_0/C$ . This signal is compared to a constant potential  $\Delta V$  by a differential amplifier whose outputs "out" and "out" swing after a time  $t_w = f(C, \Delta V, I_0)$ . This structure is used in the "delay\_lt" block, and also in the "latch\_ht", "latch\_lt2", "delay\_var" and "shaper" blocks, with values of C,  $I_0$  and  $\Delta V$  adjusted to the required delay.

Figure 10: Typical monostable structure.

The schematic of the "delay\_lt" block is given in figure 56 (appendices B). The C = 1 pF capacitor, the  $I_0 = 80 \,\mu\text{A}$  current and the  $\Delta V = +2.10 \text{ V}$  reference voltage have been optimized in order to obtain a delay of about 15 ns between the input and output signals.

[1]

#### 3.3.5 Coincidence

Figure 57 (appendice B) displays the schematic diagram of the "coincdiscri" block, using a classic NAND gate structure. The time of the output pulse as plotted in figure 11 is given by the precursor discrimination, but this signal is only present when a streamer pulse has been discriminated.

Figure 11: Input and output signals of the coincidence obtained by simulation.

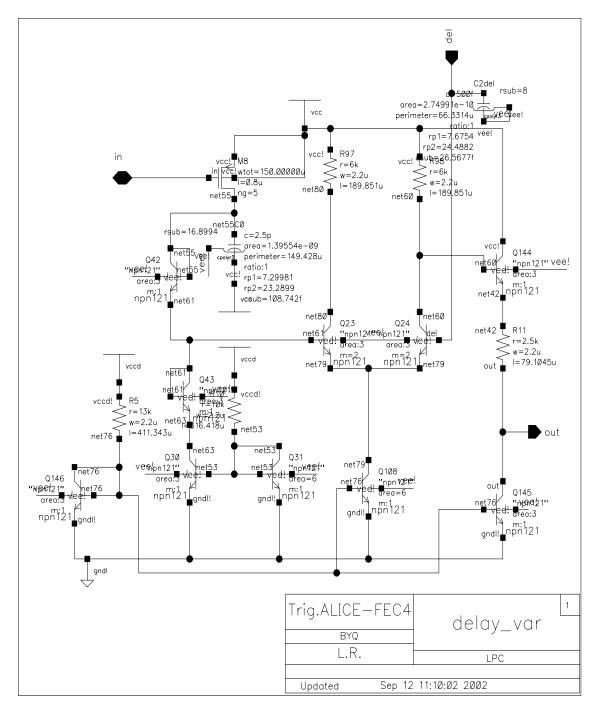

#### 3.3.6 Variable delay

Figure 58 (appendice B) of the "delay\_var" block exhibits a classical monostable structure. The delay is tuned via the external DC voltage applied on the "del" pin to control the  $\Delta V$  threshold. The others monostable parameters are:  $I_0 = 125 \,\mu\text{A}$  and  $C = 5 \,\text{pF}$ .

#### 3.3.7 Shaping

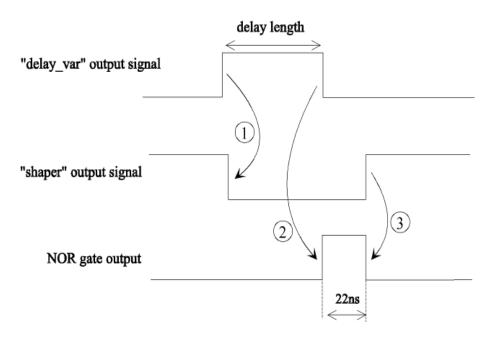

The width of the LVDS output signal is obtained by combining two signals as represented in figure 12. When the output of the "delay\_var" block goes up, the capacitor of the monostable of the "shaper" block (fig. 59 in appendice B) is short-circuited by the PMOS transistor. Then the monostable output goes down quickly (transition 1 in figure 12). When the delay signal comes back to the low state (transition 2), the PMOS transistor of the "shaper" block presents a high impedance and the capacitor is loaded until the voltage reaches the threshold potential (see 3.3.4). Therefore the "shaper" output comes back to the high state (transition 3). This signal and the delay block output are inputted to a NOR gate implanted in the "driver" block. The resulting signal is a pulse with a fixed width according to the monostable parameters of the "shaper" block (C = 2 pF,  $I_0 = 125 \,\mu\text{A}, \,\Delta V = 1.4 \text{ V}$ ) and delayed by the "delay\_var" block according to the external voltage applied to the 'delay' pin.

Figure 12: Principle to obtain the delay and the width of the output LVDS signal.

#### 3.3.8 LVDS driver

The previously introduced NOR gate is simply made of two parallel bipolar transistors of an emitter-coupled pair circuit, noted Q3, Q7 or Q2, Q10 in figure 60 (appendice B) of the "driver" block. It is worth noticing that two emitter-coupled pair circuits are drawn in parallel. The upper one is used to switch the NMOS transistors M0 and M3, and the lower stage to adjust the DC voltage of the two complementary LVDS outputs "out1" and "out2". The common mode voltage imposed by the LVDS standard is about +1.2 V. Thus the common mode voltage on the bases of the bipolar transistors Q0 and Q1 must be set to about +2.0 V. The resistors R7, R20 and R23 produce the required 1.5 V voltage drop, according to the DC current across the corresponding emitter-coupled pair circuit (about  $520 \,\mu$ A).

The output stage is composed of two bipolar transistors, two NMOS transistors and a DC current source (about 3.8 mA) supplied by Q8. When the driver switches, it changes the current direction across the cable termination resistor, thereby creating a valid 'one' or 'zero' logic state to the LVDS receiver. For example, when the output of the NOR gate rises, the NMOS transistor M3 is switched on and M0 is off. The current is out-putted across the "out2" pin, and comes back through "out1" pin.

#### 3.4 Global schematic and layout

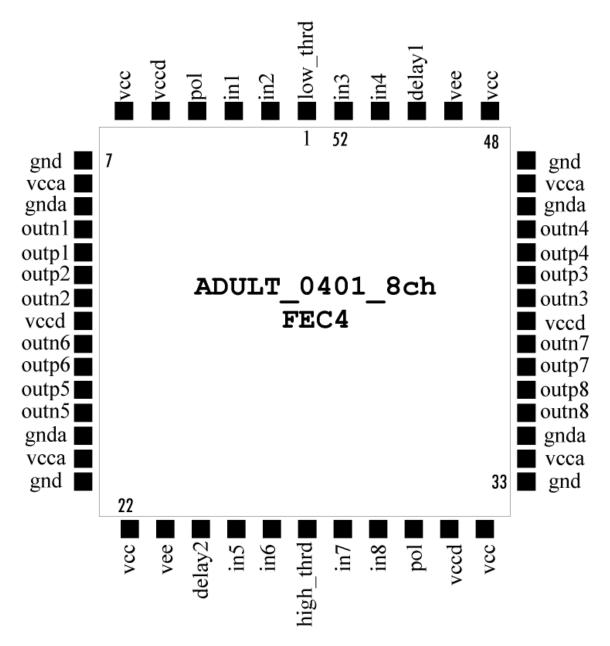

#### 3.4.1 Global schematic

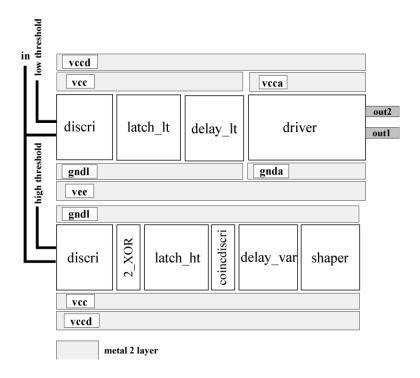

The global schematic of the ASIC is displayed in figure 13, and the pins allocation given in figure 63 (appendices B). Eight previously described one-channel blocks are used. The eight inputs are connected to analog AMS Pcells PADs (see figure 61 in appendices B) to protect them against ESD (ElectroStatic Discharge) and over voltage input pulses. These PADs are also used for the other analog inputs (delay, threshold...).

Four different power supplies are used. The "vcc" +3.5 V power supply, referenced to ground "gndl", supplies all the dynamic stages, except the "driver block". When a +3.5 V DC voltage is required for the current source mirrors or for the threshold values,

a dedicated power supply distribution is used, named "vccd", also referenced to ground "gndl". The -2.0 V negative voltage is supplied by "vee" and used only in the block "discri" in order to discriminate negative RPC pulses. Finally, a distinct power voltage distribution ("vcca" and "gnda") is dedicated to the "driver" block supply, in order to prevent from high current variation on the previous power supplied stages when the outputs switch.

Moreover, three 30 pF decoupling capacitors are directly inserted between the power supply pins "vcc", "vccd", "gndl" and the lowest potential represented by "vee", as displayed in figure 13.

#### 3.4.2 Global layout

The global layout picture is given in appendices B (Fig. 64).

The power distribution of one-channel cell is displayed in figure 14. Horizontal metal2 layers are drawn to distribute the different power supplies to the respective blocks. Two  $10 \,\mu\text{m}$  metal2 layers are used to output the LVDS signals on pins "out1" and "out2". The different widths of the power supplies layers and the values of the respective maximum DC current transported are reported on table 3.

| Layer       | Width $(\mu m)$ | Max. DC current (mA) |

|-------------|-----------------|----------------------|

| vcc         | 30              | 6                    |

| vccd        | 21              | 8                    |

| vee         | 29              | 5                    |

| gndl        | 30              | 6                    |

| vcca        | 48              | 5                    |

| gnda<br>out | 30              | 9                    |

| out         | 10              | 4                    |

Table 3: Maximum DC current for each power supply layers.

Figure 15 displays the global power supply distribution on the 8 one-channel cells. The vertical metal2 layers distribute the different LV power supplies to the horizontal power layers of each one-channel cell. Each of them is connected to several PADS in such a way that the current density across metal is limited. The VCCA and GNDA layers are drawn near the output stages of each channel in order to prevent from voltage drops due to long power paths. In the same way, the VCC and GND metal2 layers are drawn in the center of the chips, close to the input stages, and the VEE and VCCD layers form a ring all around the chip. Table 4 gives the width, the maximum DC current, and the numbers of PADs for each vertical power supply layer.

| Layers | Width $(\mu m)$ | Max. DC current (mA) | Numbers of PADs |

|--------|-----------------|----------------------|-----------------|

| ~      | , ,             |                      | 1               |

| vcc    | 50              | 25                   | 4               |

| vccd   | 70              | 33                   | 4               |

| vee    | 55              | 19                   | 2               |

| gndl   | 50              | 26                   | 4               |

| vcca   | 60              | 10                   | 4               |

| gnda   | 60              | 17                   | 4               |

Table 4: Maximum DC current for each vertical power supply layers.

Figure 13: Global electronics scheme of the chip.

Figure 14: Power distribution on one-channel cell.

Figure 15: Global power distribution on the chip.

To conclude, it can be noticed that the  $1.5 \text{ mA}/\mu\text{m}$  maximum current density (metal2) advised by AMS is greatly respected in the layout.

#### 3.5 Results of simulations

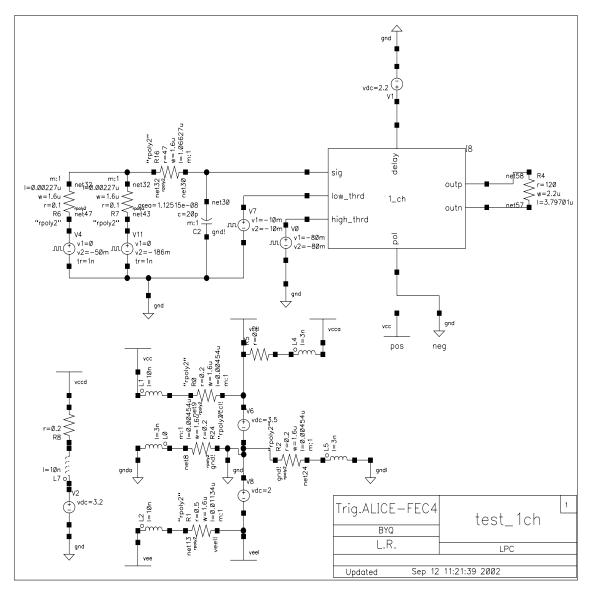

Numerous simulations have been carried out to validate the design, but only the main results are reported here. They were obtained with the model of the "analog\_extrated view" of one channel included in the schematic displayed in appendices B (fig. 62). RPC like pulses are generated as inputs to the FEE channel, and the corresponding LVDS output signals are computed.

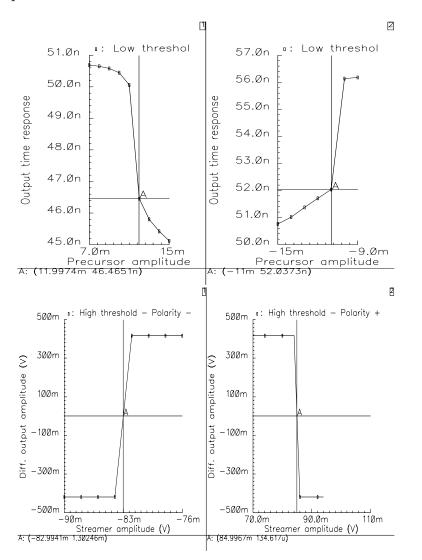

#### 3.5.1 Comparators

The sensitivity of the low and high threshold comparators has been simulated, with positive and negative polarities, and the result is plotted in figure 16. The value of the low and high thresholds are fixed respectively to  $\pm 10 \text{ mV}$  and  $\pm 80 \text{ mV}$ , but the precursor or streamer amplitudes are variable.

Figure 16: Sensitivity of the comparators for each polarity: upper plot for low threshold  $(\pm 10 \text{ mV})$  and lower plot for high threshold  $(\pm 80 \text{ mV})$ .

- The sensitivity of the low threshold comparator is defined as the minimum amplitude of the precursor signal above the threshold which is required to change abruptly the response time of LVDS output signal. Then, the reference time is given by the precursor signal instead of the streamer pulse. The sensitivity obtained is about 1 mV for the low threshold comparator for each polarity.

- The sensitivity of the high threshold comparator is defined as the minimum amplitude of the streamer signal above the threshold which is required to swing the differential amplitude of the LVDS output signal. The simulated sensitivity is 5 mV for positive and 3 mV for negative polarity, which is acceptable according to the experimental requirements.

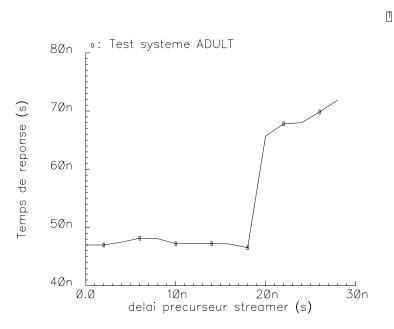

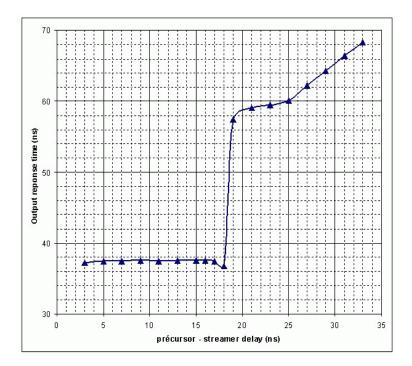

#### 3.5.2 ADULT system

The test consists in increasing progressively the delay between the precursor and the streamer signals while measuring the response time of the FEE channel. The corresponding curve is plotted in figure 17. It is worth noticing that the response time is almost steady for a delay up to 18 ns, with a maximum time variation of  $\pm 1$  ns. For a delay longer than 18 ns, the time reference is not any more given by the precursor signal but by the streamer one (fig. 7). Then, a jump of about 20 ns appears in the response time. According to this plot, the operation requirements of the ADULT system are fulfilled.

Figure 17: Response time (arbitrary absolute value) of a front-end channel as a function of the delay between the precursor and the streamer peaks.

#### 3.5.3 Statistical simulations

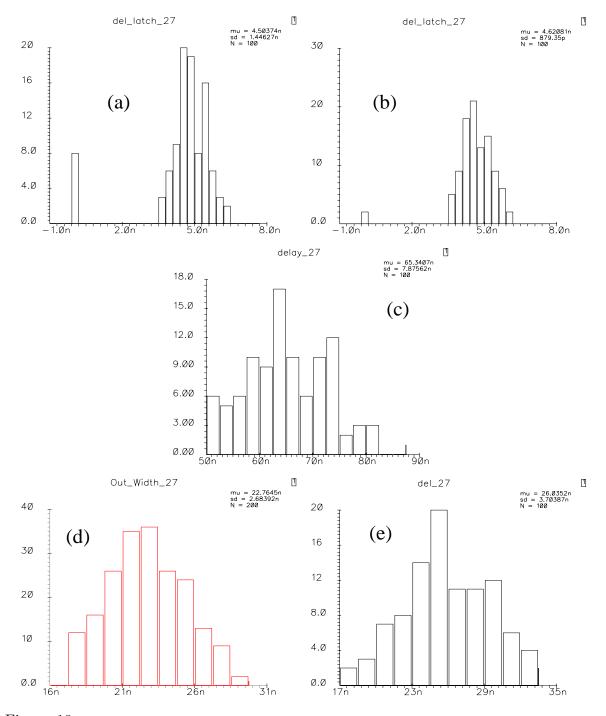

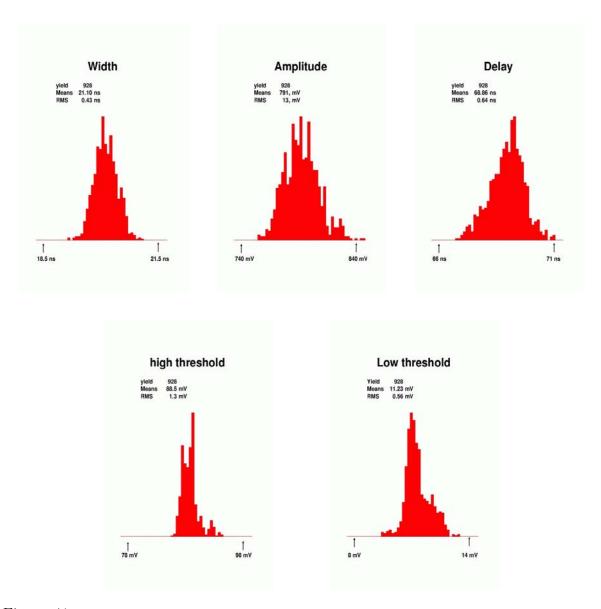

In order to evaluate the consequences of process parameters variations in AMS BiCMOS  $0.8 \,\mu\text{m}$  technology on the chip performances, Monte-Carlo simulations have been processed using the Affirma Analog Statistical Analysis tool of Cadence and the models of AMS. Several parameters have been controlled, like those presented in figure 18.

Figure 18: Statistical simulations to estimate several parameters value from one foundry Run to another: (a) and (b) discriminators sensitivity, (c) variable delay range, (d) output signal width, (e) global response time.

• Discriminators sensitivity (a) and (b)

The sensitivity decrease of the low threshold discriminator is not significant (about 2 mV instead of 1 mV). The sensitivity loss is higher for the high threshold discriminator. The number of missing discrimination is 8% (a) with an input signal amplitude 10 mV over the threshold, and drops to only 2% (b) with an amplitude of 15 mV above the threshold. This sensitivity loss can be corrected by increasing the high voltage power supply of the RPCs. Moreover, the delay applied to the low threshold discrimination signal varies from 9 ns to 17 ns (instead of 15 ns typ.), which are still acceptable values from the physical viewpoint.

• Variable delay range (c)

The minimum variable delay range is 50 ns which matches the required value, so no external adjustment of this parameter is needed.

• Global response time of one channel (e)

The response time dispersion among the chips must be lower than  $\pm 1$  ns. As all the ASICs will be produced during the same run, we can assume that the response time variation will be limited. However, this parameter will be adjusted on test bench in order to compensate for any mismatching between chips, using a potentiometer on the front-end board described below.

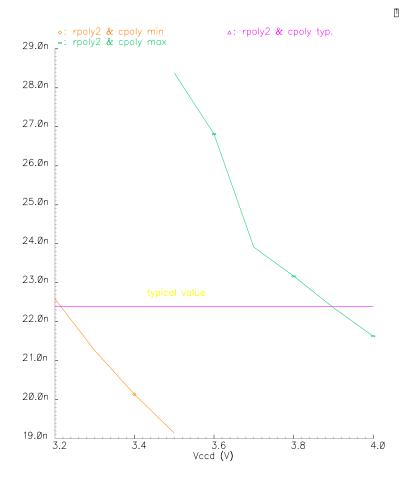

• Output signal width (d)

Last but not least, the output signal width variation with process, from 16 ns to 30 ns, is not acceptable as compared to the required value between 20 ns and 25 ns. As described before, the LVDS signal width is controlled by the components values  $(C, I_0, \Delta V)$  of a monostable stage. The variation of the slope of the capacitor loading curve, due to capacitor and resistor values fluctuations, may be corrected by the adjustment of the DC current  $I_0$ , through the "Vccd" power supply voltage. Increasing or decreasing "Vccd", compared to the typical value of +3.5 V, the output signal width is respectively decreased or increased. This correction is also beneficial for all the others DC current sources implemented in the chip, because they are in the same time taken back to their typical values. The benefits of "Vccd" adjustment have been evaluated by the simulation of the two worst cases, it means with the minimum and the maximum 'rpoly2' and 'cpoly' parameters values. The results are plotted on figure 19. The typical LVDS signal width is represented by the horizontal line between 22 ns and 23 ns. With the minimum values of 'rpoly2' and 'cooly' (lower plot), the typical value of the signal width is recovered with a "Vccd" value of about +3.2 V. For the maximum values of 'rpoly2' and 'cpoly' (upper plot), the typical curve is crossed with "Vccd" equal to 3.9 V. It is also important to notice that, during simulations, when the "Vccd" power supply is increased, the negative "Vee" power supply is decreased in the same ratio in order to not exceed the breakdown voltage of 5.5 V advised by AMS.

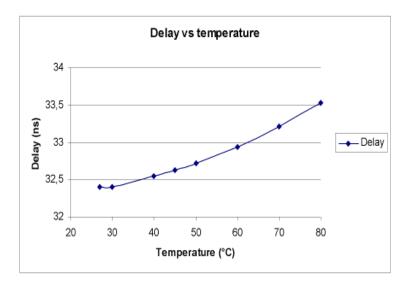

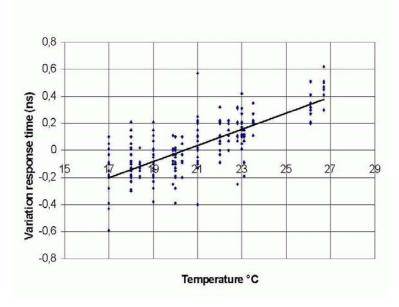

Finally it has been checked that the temperature fluctuations have no major effect on the chip response time. This has been simulated over a large range of temperature, from  $27^{\circ}$ C to  $80^{\circ}$ C. The results as plotted in figure 20 show a good stability with respect to temperature fluctuations, with a sensitivity coefficient of about:

$$\left(\frac{\partial \Delta t_{chip}}{\partial \theta}\right) \approx 37 \, \mathrm{ps/^{\circ}C} \, .$$

Figure 19: Output width variation as a function of "Vccd" for the extreme value of 'rpoly2' and 'cpoly'.

Figure 20: Response time of the output LVDS signal as a function of temperature.

## 4 Front-end boards design

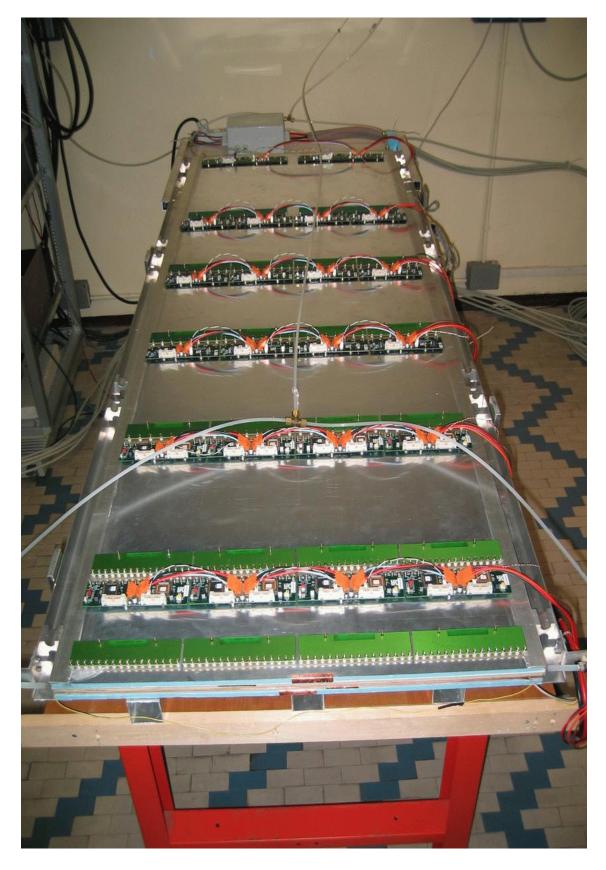

The length of the RPC detectors is about 2.7 m. The granularity in the deviation planes (X horizontal strips) implies to pick-up the signals on the surface of the RPCs (fig. 21), while this is usually done at their edges. Thus, the front-end boards (FEB) are directly plugged on dedicated connectors placed at the end of the strips.

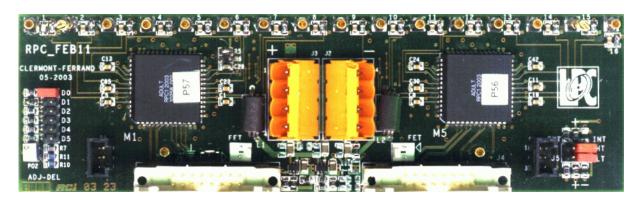

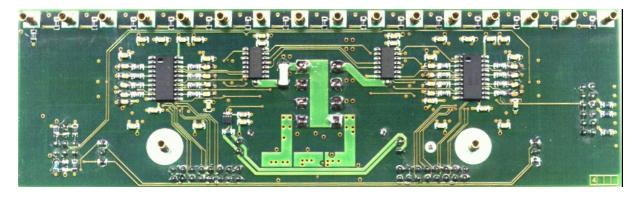

Each FEB is equipped with one or two ASICs and with all the components which are required to configure, supply and test the FECs.

Figure 21: Scheme displaying the points where the signals of X strips (horizontal) are picked-up on an entire RPC, with the three types of strip pitch.

### 4.1 Chip integration

The electronics schematic viewes of the front-end board are shown in appendice C for the most complicated: a FEB11X (fig. 65 to 70). Front-end ASIC are directly soldered on the PCB because of the bad ageing of the socket to chip contacts.

#### 4.1.1 Thresholds

The two threshold values ( $\pm 10 \text{ mV}$  and  $\pm 80 \text{ mV}$ ) are fixed on board and simply built with resistive dividers referenced to the +3.5 V supply for positive thresholds, and to the -2 V supply for the negative ones. The polarity is chosen at the manufacturing stage, and consists in soldering the required resistors on the board. As trigger dimuon collaboration asked to foresee an external tuning of the thresholds with a external voltage reference, two dedicated connectors are implanted on the board for threshold adjustments, through a resistive  $\frac{1}{100}$  ratio divider. Two jumpers on boar allow to choose the fixe thresholds (10/80 mV) or the external ones.

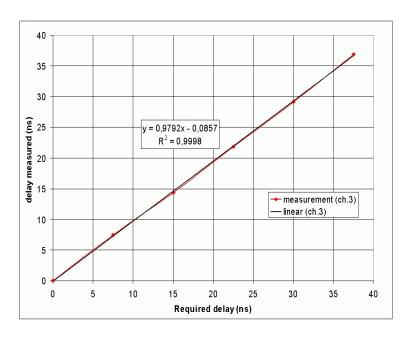

#### 4.1.2 Delay

The LVDS output signals can be delayed by five 7.5 ns steps in order to compensate different cable lengths. The required delay is configured with jumpers, according to the cable length attached to the front-end board. The values of the resistive dividers corresponding to the five delay steps are given in table 5. In addition, a potentiometer is tuned up during test on bench to put in time all the boards (in a window of 4 ns).

As the two trigger stations are 1 meter apart, the signals delivered by the MT1 station front-end electronics must be delayed by about 3 ns relatively to those of the MT2 station to compensate for the time of flight difference. Therefore different resistive dividers are used for stations MT1 and MT2.

|       |            |           | MT1        |             |             |           | MT2        |             |             |

|-------|------------|-----------|------------|-------------|-------------|-----------|------------|-------------|-------------|

| Delay | $R_1$      | $V_{dth}$ | $R_{2th}$  | $R_{2real}$ | $V_{dreal}$ | $V_{dth}$ | $R_{2th}$  | $R_{2real}$ | $V_{dreal}$ |

| (ns)  | $(\Omega)$ | (V)       | $(\Omega)$ | $(\Omega)$  | (V)         | (V)       | $(\Omega)$ | $(\Omega)$  | (V)         |

| 0     | 1000       | 2.61      | 2933       | 2940        | 2.61        | 2.53      | 2608       | 2610        | 2.53        |

| 7.5   | 1000       | 2.41      | 2211       | 2210        | 2.41        | 2.33      | 1991       | 2000        | 2.33        |

| 15    | 1000       | 2.21      | 1713       | 1690        | 2.20        | 2.13      | 1555       | 1540        | 2.12        |

| 22.5  | 1000       | 2.01      | 1349       | 1330        | 2.00        | 1.93      | 1229       | 1210        | 1.92        |

| 30    | 1000       | 1.81      | 1071       | 1070        | 1.81        | 1.73      | 977        | 976         | 1.73        |

| 37.5  | 1000       | 1.61      | 852        | 845         | 1.60        | 1.53      | 777        | 768         | 1.53        |

Table 5: Different delay values for the boards of the two stations MT1 and MT2.  $R_{2th}$  and  $V_{dth}$  are the calculated values, while  $R_{2real}$  and  $V_{dreal}$  the real values.

#### 4.1.3 Polarity

The polarity, depending on which of the X or Y strips the FEB are connected, is configured by a strapping  $0\,\Omega$  resistor soldered to ground or to the  $+3.5\,\mathrm{V}$  power supply, respectively for the negative and positive polarity.

#### 4.1.4 Signal and output connectors

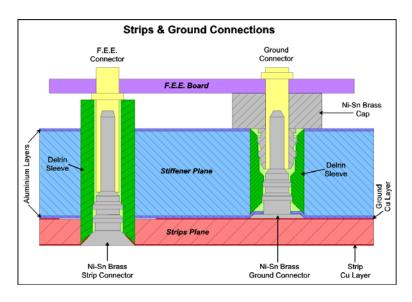

The connection of the front-end board on the RPC strips is done by dedicated female Burndy pin (in brass) plugged into specific strip connectors (fig. 22). Each input is connected to a  $50 \Omega$  strip adaptation resistor and to a 100 nF decoupling capacitor.

The mechanical resistance and resistivity reliability of these connectors, both on strips (for the male part) and on PCB (for the female part), has been tested by a succession of connections and disconnections (about 100). No damage has been observed. Furthermore, several connectors have been tested after suffering for nine months in a corrosive environment (humidity and temperature variations). No increase of the contact resistance has been observed. In addition, during all the tests performed with RPC prototypes (at the LPC Clermont-Fd and at CERN) no connection problem occured.

To improve the ground connection (see section 6 illustrating the effect on cross-talk), a connection to the ground of the strip plane is obtained in the same operation with dedicated connectors (fig. 22), when the FEB is plugged in the strip connectors.

An output connector (16 pins HE10 type) is used on the FEB, with the corresponding female part on the cable (see section 4.4), for each 8 output differential signals of one chip.

#### 4.2 Low voltage power supplies

As described before, the FEC needs three different power supplies:  $V_{ee} = -2$  V for the analog input stage,  $V_{ccd}$  adjustable between 3.2 V and 4 V for the DC current sources, and  $V_{cc} = +3.5$  V for the others parts of the chip. Low voltage digital circuits implanted on the FEB are supplied with  $V_{cc}$ .

Figure 22: Connection between a FEB and a strip plane, with a strip connector (left) and a ground connector (right).

#### 4.2.1 Low voltage connectors

The low voltages which are used to supply the chips are brought along a specific power distribution system (see section 5.2) in such a way that several boards are connected in chain. Then two low voltage connectors are necessary on each FEB in order to transmit the power supply from a board to the following. Furthermore, the choosen connector are obliques, as displayed in figure 28, to avoid large cable loop between two boards.

#### 4.2.2 Regulation

The two positive voltages required to supply the chip are obtained through two MAX1818 regulators from Maxim company. The voltage  $V_{cc}$  is fixed to +3.5 V, while  $V_{ccd}$  will be adjusted depending of the performances of some numerous FEC samples picked up in the amount of manufactered chips. The voltage is determinated by a resistive divider made of  $R_1$  and  $R_2$ , which obey to the following equation:

$$R_1 = R_2 \left[ \frac{3.5}{1.25} - 1 \right] \,,$$

where  $R_2 = 10 \,\mathrm{k\Omega}$  and  $R_1 = 18 \,\mathrm{k\Omega}$  (the last value is obtained using two serial resistors of  $17.8 \,\mathrm{k\Omega}$  and  $200 \,\mathrm{\Omega}$ ) to obtain a voltage of  $3.50 \,\mathrm{V}$ .

#### 4.2.3 Over current protections

The current of the negative -2 V power supply is limited with the use of one Very Fast-Acting fuse. The ampere rating is 125 mA for a nominal supply current of about 80 mA (16 channels boards). Concerning the positive +3.5 V power supply, the use of fuse is prohibited due to the voltage drop induced by the serial resistance. However, the DC/DC regulators Max1818 include an thermal overload protection and an output current limit. Combined with the current limit provided by the Wiener power supplies through the DCS, these protections are suitable with the safety CERN policy.

#### 4.2.4 Decoupling

The input positive and negative are each filtered with one serial ferrite inductor and one  $10 \,\mu\text{F}$  ceramic capacitor connected to the ground. The DC/DC regulators outputs are also filtered as recommanded in the datasheets (see Fig. 66).

## 4.3 Front-End Test (FET) system

A global test of the front end and trigger electronics is required before and during physics runs. It will allow to check:

- the good running of every front-end electronics channel,

- the quality of the transmission of the LVDS signals on every twisted pairs cable,

- the good running of the trigger electronics with any algorithm implemented.

The principle of the system chosen is to generated a RPC like pulse to each front end electronics input, at the same time, when a procedure of test is requested. In other words, the whole 21000 FEE channels must be lighted in the same 25 ns window. Considering the different time jitter sources (between twisted pairs, chips, ...), the jitter time of the test system must be then limited to 5 ns. The frequency of this test will not exceed 1 kHz.

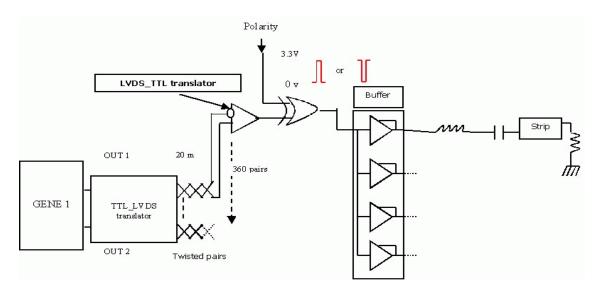

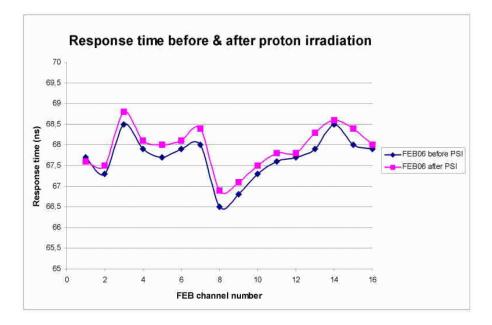

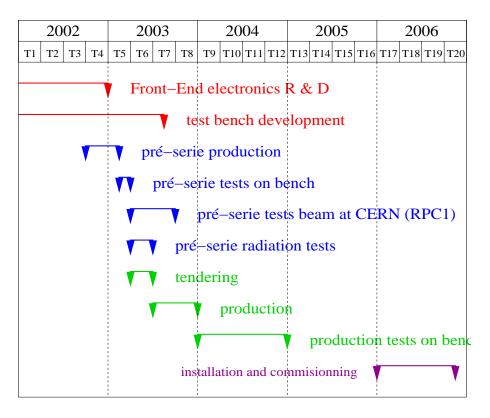

The test system is composed of several devices, as represented in figure 23.

Figure 23: Whole FET principle for one channel.

- A pulse generator delivers a trigger signal to the Local Trigger Unit (LTU) to inform the DAQ that a test is in progress. At the same time, it generates a logical pulse to TTL-to-LVDS translator modules.

- The TTL-to-LVDS translator modules distribute the logical pulse to every frontend board plugged on the 72 RPCs, through dedicated twisted pairs cables.

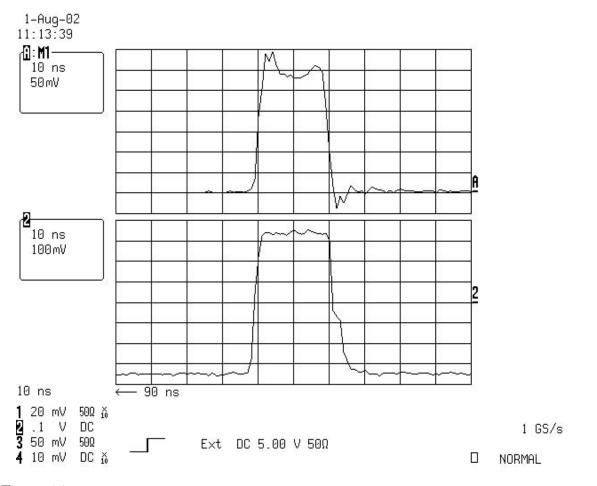

On each FEB, the LVDS pulse is translated into a TTL pulse, through a LVDS-to-TTL translator. This signal is inverted or not with a XOR gate, according to the required pulse polarity (X or Y plan), and inputted to an octal low voltage buffer. Each buffered output is then sent to every front-end ASIC input through a 300 Ω resistor to reduce the pulse amplitude, and through a 1 nF capacitor to filter the DC voltage. The positive pulse obtained is plotted in figure 24.

Figure 24: Result of the FET system: pulse test generated at the FEC input (upper plot) and LVDS pulse test received on the FEB (lower plot).

The time jitter measured between the 8 channels of the same FEB20 is lower than 1.5 ns. Moreover, the distribution of the LVDS signals on every FEB will be optimized in order to limit the global time jitter to 5 ns as required.

#### 4.4 Output signal cables

The output signal cables must transmit a fast LVDS pulse from the front-end electronics to the trigger electronics. The different cable lengths required with the corresponding quantity are given in the table 6 (amounting to about 24 km).

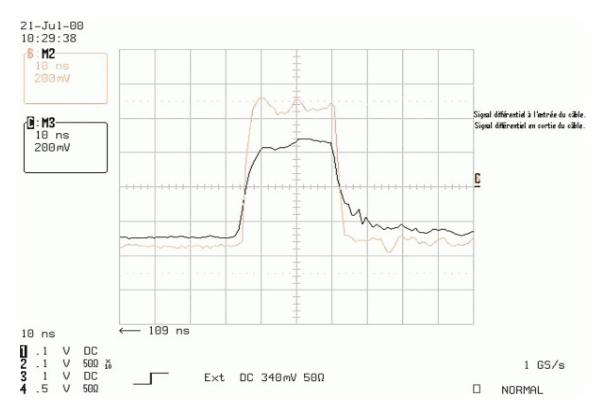

A twisted pairs cable with global shielding has been chosen, in order to minimize transmission losses and sensitivity to electromagnetic interferences. A 21 round twisted pairs cable, available at CERN store, has been tested. Figure 25 displays a LVDS signal measured at the beginning and at the end of a 20 meters long cable. The loss of differential amplitude is about 25% with no alteration of the pulse edges. When

| Table 6: Cable lengths and quantities.  |     |     |     |     |     |  |

|-----------------------------------------|-----|-----|-----|-----|-----|--|

| Length (m) $20$ $18.5$ $17$ $15.5$ $14$ |     |     |     |     |     |  |

| Number                                  | 120 | 324 | 358 | 360 | 270 |  |

this output signal is put into a LVDS receiver, the logic signal is recovered without information loss.

The technical specifications of the required cable are based on the tested cable. A pre-production of 200 m cable has been done to validate the manufacturing. Tests show that the cables are in accordance with the specifications:  $\Delta t_{max} < 3$  ns between pair on 20 m long cable.

Figure 25: Output LVDS signal at the beginning (channel B) and at the end (channel C) of the 20 m differential cable.

#### 4.5Adaptation boards

The RPCs strip must be adapted on both ends in order to avoid signal reflections.

The characteristic impedance  $Z_c$  has been measured for each of the three types of strip widths corresponding to station MT1. The results displayed in table 7 (first line) represent the mean value of ten measurements, and the associated error calculated as their root mean square (rms).

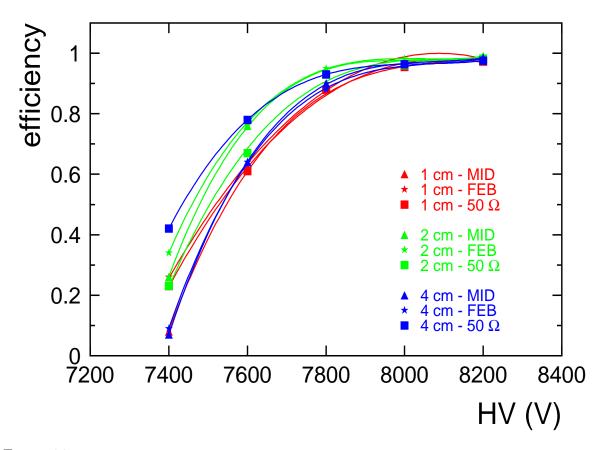

Amplitude measurements have been carried out with the same RPC (in cosmic rays) using successively the three types of strip width, with  $50 \Omega$  at each end. The results are reported in table 7 (second line). Moreover, figure 26 displays the efficiency of the RPC (at CERN-GIF) as a function of its high voltage for the three type of strips. In all the cases, the efficiency plateau is reached for a high voltage of about 8 kV.

According to these measurements, it has been decided to take the same impedance termination  $Z_0 = 50 \Omega$  for the three types of strip width.

Table 7: Characteristic impedance  $Z_c$  of the strips (station MT1), and mean value of the signal amplitude picked-up on the strips equipped with 50  $\Omega$  impedances at both ends.

| Strip width      | 1 cm             | $2 \mathrm{cm}$  | $4 \mathrm{cm}$  |

|------------------|------------------|------------------|------------------|

| $Z_c$            | $(49\pm2)\Omega$ | $(40\pm3)\Omega$ | $(28\pm3)\Omega$ |

| Signal amplitude | $400\mathrm{mV}$ | $450\mathrm{mV}$ | $450\mathrm{mV}$ |

### Efficiency curves for strips of various widths

Figure 26: Efficiency curves as a function of the RPC high voltage for strips of various widths (50 cm long) for particles crossing the strip: on the middle (MID), near the front-end board (FEB) and near the adaptation board (50  $\Omega$ ).

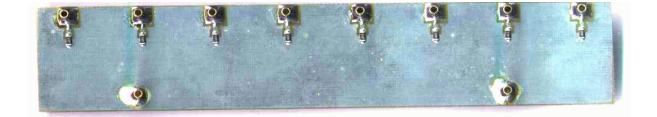

An equivalent resistor is inserted on each input of the FEB. Moreover, dedicated adaptation boards are plugged on the other end of the strips, which also contain  $50 \Omega$  resistors connected to ground. The layout and the plug system of these boards are identical to the FEB ones (see Fig. 27).

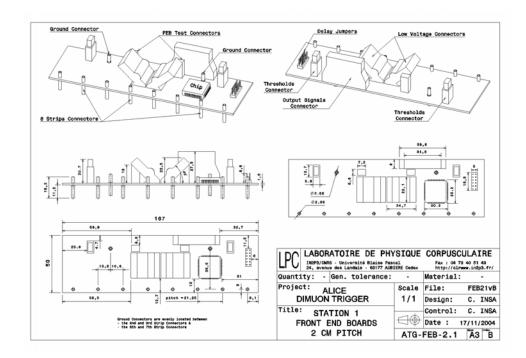

#### 4.6 Summary

To make the connection and disconnection of the FEB easier as well as their manufacturing, it has been decided to limit the length of the boards according to 8 strips of

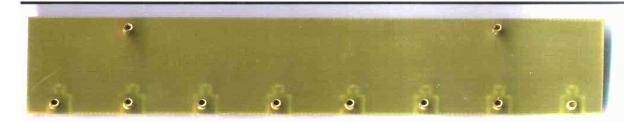

Figure 27: Adaptation board (50  $\Omega$  resistor) with 8 strip connectors (2 cm pitch) and 2 ground connectors: top view (upper picture) and bottom view (lower picture).

$45.2\,\mathrm{mm}$  width, namely to about  $36\,\mathrm{cm}.$  So the final solution consists of three types of FEB:

- FEB10 with 2 chips for a strip pitch of about 1 cm (16 channels),

- FEB20 with 1 chip for a strip pitch of about 2 cm (8 channels),

- FEB40 with 1 chip for a strip pitch of about 4 cm (8 channels).

A summary of the front-end boards features is given in table 8, while figures 28 and 29 illustrate a FEB with all its connectors. Due to services (power supply and output cable "goulottes" roads estimated on a mock-up), the connectors are not placed on the edge of the boards in order to make the cable connections or disconnections easier.

Finally, the whole list of electronics components for the front-end board types FEB11X is given in appendice D, and the number of different FEBs is listed in table 9.

| Board type                        | FEB10     | FEB20     | FEB40     |

|-----------------------------------|-----------|-----------|-----------|

| Number of chips                   | 2         | 1         | 1         |

| Number of strip connectors        | 16        | 8         | 8         |

| Number of ground connectors       | 2         | 2         | 4         |

| Number of output connectors       | 2         | 1         | 1         |

| Number of low voltages connectors | 2         | 2         | 2         |

| Number of test system connectors  | 2         | 2         | 2         |

| Length (mm) for $MT1 / MT2$       | 167 / 175 | 167 / 167 | 304 / 326 |

| Width (mm) for MT1 / MT2          | 50 / 50   | 50 / 50   | 50 / 50   |

Table 8: Mechanical data for the three types of front-end boards: FEB10 (1 cm pitch), FEB20 (2 cm pitch) and FEB40 (4 cm pitch).

Table 9: Number of front-end boards FEBijk for the different types required (without spares), with i giving the pitch (1 cm, 2 cm or 4 cm), j the station number (1 for MT1 and 2 for MT2), and k the strips direction (X for the horizontal strips and Y for the vertical strips). The designations FEB10, FEB20 and FEB40 gather together all the FEBs of a given pitch (for instance FEB20 = FEB21X + FEB21Y + FEB22X + FEB22Y).

| FEB10  |        |        |        |  |  |  |  |  |

|--------|--------|--------|--------|--|--|--|--|--|

|        | 240    |        |        |  |  |  |  |  |

| FE     | B11    | FE]    | B12    |  |  |  |  |  |

| 12     | 20     | 12     | 20     |  |  |  |  |  |

| FEB11X | FEB11Y | FEB12X | FEB12Y |  |  |  |  |  |

| 120    | 0      | 120    | 0      |  |  |  |  |  |

|        | FE]    | B20    |        |  |  |  |  |  |

|        | 15     | 04     |        |  |  |  |  |  |

| FE     | B21    | FEB22  |        |  |  |  |  |  |

| 75     | 52     | 752    |        |  |  |  |  |  |

| FEB21X | FEB21Y | FEB22X | FEB22Y |  |  |  |  |  |

| 528    | 224    | 528    | 224    |  |  |  |  |  |

|        | FE]    | B40    |        |  |  |  |  |  |

|        | 64     | 40     |        |  |  |  |  |  |

| FE     | B41    | FEB42  |        |  |  |  |  |  |

| 32     | 20     | 320    |        |  |  |  |  |  |

| FEB41X | FEB41Y | FEB42X | FEB42Y |  |  |  |  |  |

| 168    | 152    | 168    | 152    |  |  |  |  |  |

Figure 28: Connectors used on a FEB20 or FEB40. For a FEB10 (with 2 chips), 16 strip connectors and 2 output connectors are used.

# Upper side view of a FEB11

# Underside view of a FEB11

Figure 29: Pre-serie version of FEB11.

# 5 Power supply considerations

# 5.1 Grounding and shielding overview

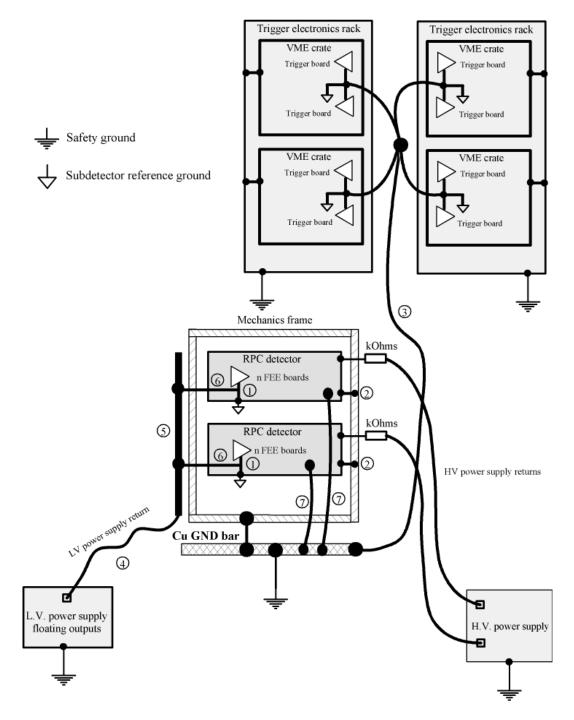

An overview of the global grounding and shielding proposal of the Dimuon trigger setup is shown on figure 30. It is mainly based on general considerations of the ALICE grounding plan [11].

Figure 30: Global FEE grounding scheme.

#### 5.1.1 Constraints

The reference ground of each front-end board is connected to the metallic body of the RPC on which the board is plugged (connection 1 on Fig. 30). The RPCs are held up by a steel frame which is in contact with the RPC body. So, the whole frame of the trigger chambers setup is connected indirectly to the FEE reference ground (connection 2 in Fig. 30). Moreover, as the FEE transmits LVDS signals to the Trigger electronics, the shifting of their respective reference ground must not exceed  $\pm 1 \text{ V}$ . It is why the FEE and Trigger electronics reference grounds must be connected (connection 3 in Fig. 30).

#### 5.1.2 Proposal

1. Low Voltage Power Supply (LVPS)

The LVPS of the FEE has floating outputs. Each LVPS return (connection 4 in Fig. 30) is connected to a vertical copper bus-bar distribution, where the ground reference of each FEB is connected (connection 6 in Fig. 30).

2. High Voltage Power Supply (HVPS)

Each HVPS with floating outputs supplies one RPC. The HVPS return is isolated from the sub-detector reference ground by a resistor, typically of order  $1 k\Omega$ . For personnel safety reason, the whole mechanical frame of the trigger setup must be connected to earth. However it is recommended to separated the signal ground to the safety ground. The description of the setup has shown that, by construction, these 2 potentials are connected together. We propose to build an equipotential central point with copper bars located below each half trigger plan. This single point connection is a center of a star network (connections 7 in Fig. 30), which provides the reference and safety potential and avoids shield currents flowing into the system.

3. LVDS signal cables

The 1500 cables which transmit data from each FEB to the trigger boards are shielded. In order to prevent ground loops, the cable shield is connected to the sub-detector reference ground on the FEB and via a capacitor to the local ground on the trigger boards.

## 5.2 Power supply distribution

The aim of such a device is to supply the front-end boards, by taking into account different consumptions according to the voltage:

- $10 \,\mathrm{mW/channel}$  for the  $-2 \,\mathrm{V}$ ,

- $90 \,\mathrm{mW/channel}$  for the  $+3.5 \,\mathrm{V}$ .

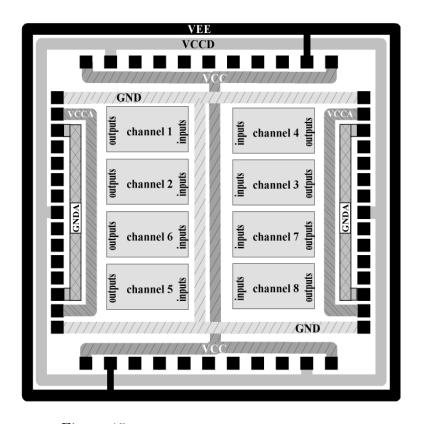

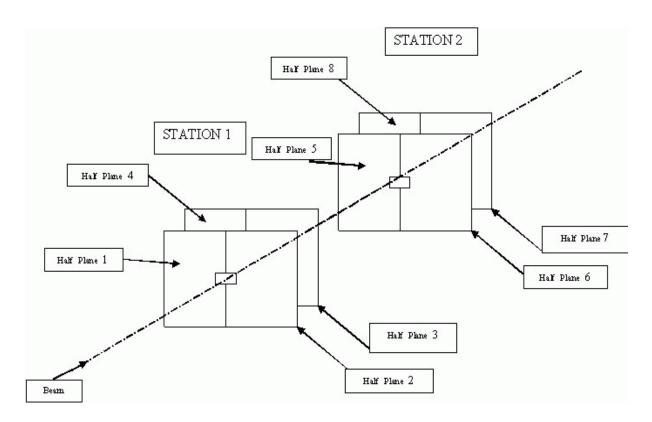

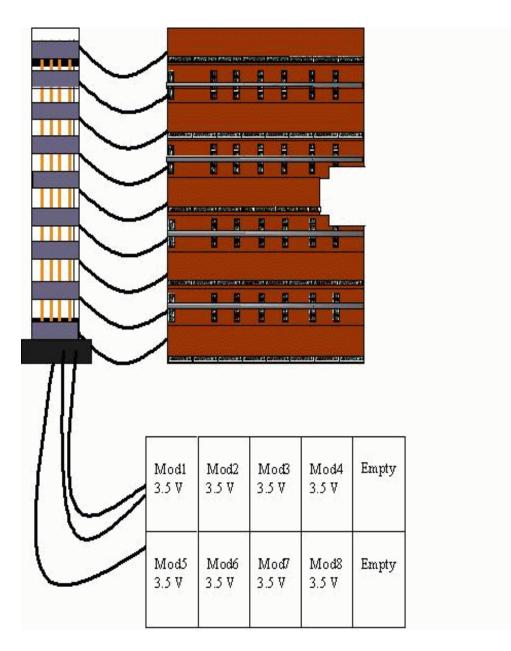

The trigger detector is divided into 8 half planes, as displayed in figure 31. Each part has the same number of front-end channels and can be supplied in the same way.

Two low voltage power units, corresponding to +3.5 V and to -2 V, will supply all the FEB plugged in each half plane. The 16 power supply units which are required for the whole detector are manufactured by the Wiener company. They are modular floating power supplies and are designed to provide external load channels with high power consumption over long distances.

Figure 31: Segmentation of the low voltages for the whole dimuon trigger detector.

The power supply modules are housed into two 6U crates. Each crate admits 10 modules, but only 8 are required in our case (4 positive and 4 negative). The first crate will supply the four left half planes and the second one the four right half planes. The cable length between the power supplies and the detector will be 20 meters approximately. The voltage drops along these cables are compensated by a remote-sense regulator.

As displayed in figure 32, four vertical copper rods transport the low voltage currents from the cable ends to the edge of the 9 RPCs of one single half plane. The voltages are then distributed along each RPC using a distribution cable device. There will be as many such cables as RPC.

The results show that voltage regulators are required for the positive voltage. Concerning the negative voltages, regulators are not essential. Nevertheless, in order to avoid losses due to the connections along the distribution, a particular care must be taken during the manufacture of these connections (tinning and use of resin). Under these conditions, simulations show that the differences of the power supply voltages on each FEB are less than  $\pm 100 \,\mathrm{mV}$ .

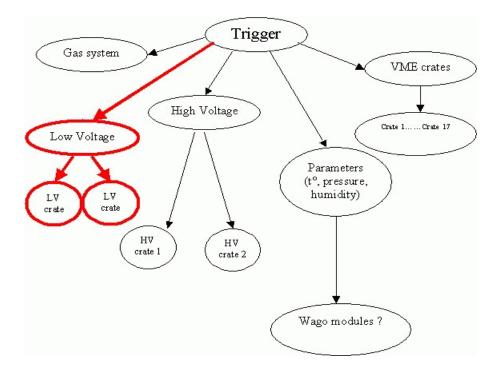

#### 5.3 Detector Control System

As previously explained, the low voltage power supply system will be made of sixteen modules (eight for the positive voltages and eight for the negative ones). These modules will be arranged by eight into two crates: four positive and four negative modules in each of them.

Figure 33 displays the structure of the DCS (Detector Control System), in which the low voltages system is inserted.

It is expected to control about thirty parameters concerning each low voltage channel [12] (both for positive and negative voltage):

Figure 32: Global view of the low voltages distribution system.

Figure 33: Structure of the dimuon trigger DCS.

| QuickTest_: BT\wier<br>File Panel ? | ner.pnl                   |                                           |                 |                      |  |

|-------------------------------------|---------------------------|-------------------------------------------|-----------------|----------------------|--|

| Surve                               | ey                        | Wiener PL500<br>First crate               |                 | 4:17:23 PM 4/23/2003 |  |

|                                     | Chan4<br>Positive voltage | Crate ON/OFF                              | Chan'i<br>Negat | i<br>ive voltage     |  |

| Vreq                                | 3.77 ₹                    |                                           | Vreq            | 3.11 V               |  |

| 📃 🖉 vMon                            | 3.77 ¥                    | ON/OFF                                    | vition          | 3.11 V               |  |

| <u>i</u> Mon                        | 84.80 A                   | ON                                        | iMon            | 84.77 A              |  |

| Ilim                                | 90 A                      |                                           | Ilim            | 85 A                 |  |

| Iover/max                           | 90 A                      |                                           | Iover/max       | 85 A                 |  |

| Vmax                                | 4.00 ₩                    | Change setting                            | Vmax            | 3.90 V               |  |

| Vmin                                | 2.50 ¥                    | Change setting:                           | 5 Vmin          | 3.10 V               |  |

|                                     |                           | GOTO ALARM<br>Crate Temperature<br>25 ° C |                 |                      |  |

|                                     |                           |                                           |                 | Close                |  |

Figure 34: Structure of the dimuon trigger DCS.

- Parameters of low voltage modules (8)

- status setting and reading (on / off),

- input voltage setting,

- output current limit setting,

- output ramp up setting,

- output ramp down setting,

- output voltage reading,

- input current limit reading,

- input ramp up reading,

- input ramp down reading;

- Parameters of low voltage crates (2)

- status setting and reading (on / off),

- input voltage reading,

- input current reading,

- input temperature reading,

- output speed fan setting,

- input speed fan reading.

With this scheme, there will be no control of the low voltage directly on the front-end boards. The working of each FEB can be checked only with the help of the FET system.

According to the CERN standard, the DCS of the Low Voltage powe supply is built up within the PVSS software. The actual working version, uses the CERN custom SLiC OPC server, which is to be replaced by the genuine Wiener OPC server as soon as the later will be available. The main drawback of the present solution is its limitation to the Wiener PL500 LV device while the Wiener OPC server should allow to manage Wiener crates.

The graphical user interface is made of a main panel which summarizes the LV status for each half plane of the trigger. Clicking into the representation of a half plane gives access successively to two panels, dedicated respectively to the survey and the setting of its LV power supply. The survey panel (see Fig. 34) displays the status of each channel with the corresponding date and time, and a button to set ON/OFF the crate. A green/red light shows the ON/OFF status. The settings are shown for information, and the monitored current and voltage are displayed, together with a green/red light. For each of them, a button allows to display the trending curve. Alarms are displayed by the way of pop-up windows to acknowledge. A button gives access to the alarm log file. The second important panel is accessed via a dedicated button. It allows to change the settings. Note that access control facilities will be attached to this button.

# 6 Characterization results

### 6.1 Chip evolution

The electronics presented in this document has been developed over four years. In other words, the final version of the ASIC described in section 3 and its associated boards is the fruit of several improvements. Table 10 summarizes the evolution of the main characteristics of this chip.

| Table 10: Different versions of the ASIC developed at LPC Clermont-Fd. |             |             |             |               |  |  |

|------------------------------------------------------------------------|-------------|-------------|-------------|---------------|--|--|

| Chip version                                                           | FEC1        | FEC2        | FEC3        | FEC4          |  |  |