# A Novel Design and Implementation of New Double Feynman and Six-correction logic (DFSCL) gates in Quantum-dot Cellular Automata (QCA)

# Dr. Sajjad Waheed Sharmin Aktar Ali Newaz Bahar

Department of Information and Communication Technology, Mawlana Bhashani Science and Technology University, Santosh, Tangail-1902, Bangladesh

doi: 10.19044/esj.2017.v13n15p265 URL:http://dx.doi.org/10.19044/esj.2017.v13n15p265

### Abstract

Abstract In recent years, quantum cellular automata (QCA) have been used widely to digital circuits and systems. QCA technology is a promising alternative to CMOS technology. It is attractive due to its fast speed, small area and low power consumption. The QCA offers a novel electronics paradigm for information processing and communication. It has the potential for attractive features such as faster speed, higher scale integration, higher switching frequency, smaller size and low power consumption than transistor based technology. In this paper, Double Feynman and Six-correction logic gate (DFSCL) is proposed based on QCA logic gates: MV gate and Inverter gate. The proposed circuit is a promising future in constructing of nano-scale low power consumption information processing system and can stimulate higher digital applications in OCA. higher digital applications in QCA.

Keywords: Quantum Cellular Automata; QCA Logic Gates; DFSCL gate, dfscl gate in QCA

# Introduction

Quantum technology has gradually applied in various fields (Yi Liu 2008, Hao Li, Shiyong Li: 2011). Quantum-dot cellular automata is projected as a promising nanotechnology for future *ICs* (Lent et al. 1993; Lent and Tougaw, 1997; Bahar et al. 2013a; Sarker et al. 2014). A *QCA* is an array of structures known as quantum-dots. Computing with *QCA* is achieved by the tunneling of individual electrons among the quantum-dots inside a cell and the classical coulomb interaction among them (Abdullah-Al-Shafi et al.2017; Bahar et at.2017). A *QCA* cell consists of two electrons positioned at opposite corners owing to columbic repulsion (Islam et at. 2014; Bahar et al. 2014; Sarker et at. 2017), so the polarization states of P=-1 and P=+1 can be represented by two stable configuration of a pair of electrons, the corresponding the logic values of "0" and "1" also be represented in Fig.1 The electrostatic repulsion between electrons leads to the synchronization of neighboring cells. Thus, one cell's polarization is determined by the effect of its neighboring cell's polarization (Al Shafi et al. 2015; Bahar et al. 2015a; Abdullah-Al-Shafi, & Bahar 2016; BAHAR, et al. 2015b)

Therefore, the array of *QCA* cells will be able to propagate information as a wire (Abdullah-Al-Shafi et al. 2015; Bahar, & Waheed 2016; ). The *QCA* cells can form the primitive logic gates shown in Fig. 2 (inverter gate), Fig. 3 (majority gate). A majority gate with the logic function of MV(A,B,C) = AB+AC+BC is composed of five cells. By setting one of the inputs of this gate permanently to 0 or 1, *AND* and *OR* functions will be formed in *QCA*. Some other combinational logic designs with plus-shaped quantum-dot cellular automata using minority gate as the fundamental building block have been presented in (Islam et al.2016; Bahar et al. 2017).

An array of cells that are aligned can construct a QCA wire which is shown in Figure 4. The polarization of each cell in a QCA wire is directly affected by the polarization of its neighboring cells on account of electrostatic force(Bahar et al. 2017; Abdullah-Al-Shafi et al. 2017). Accordingly, QCA wires can be used to propagate information from one end to another(Abdullah-Al-Shafi & Bahar 2016; Islam et al. 2015).

Fig. 4 A QCA Wire

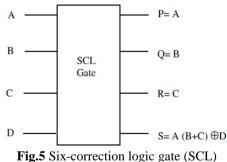

# **Reversible Logic Gate** Six-Correction Logic Gate

Six-Correction Logic Gate is a 4 x 4 gate with two garbage outputs (Rahman et al.2015; Rahman, M. S., Waheed, S., Bahar, A. N.:2015), the input vector is I (A, B, C, D) and the output vector is O (P, Q, R, S) and output is defined by P = A, Q = B, R = C, S=A (B+C)  $\bigoplus D$  the relation between input and output shown in figure 5. There is a one-to-one mapping between inputs and outputs of SCL gate and it can be used to add 6 to the sum in order to correct it to get the correct BCD sum (Bhagyalakshmi and Venkatesha : 2010).

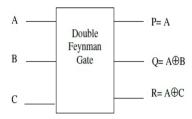

#### **Double Feynman gate (F2G)**

Figure 6 shows a 3 x 3 Double Feynman gate (Bahar et al. 2013b; Parhami:2006). The input vector is I (A, B, C) and the output vector is O (P, Q, R) and output is defined by P = A,  $Q = A \oplus B$ ,  $R = A \oplus C$ .

Fig.6 Double Feynman gate

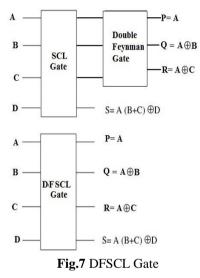

# Proposed dfscl gate

DFSCL gate

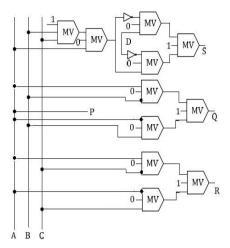

Figure 7 shows a DFSCL Gate. The input vector is I (A, B, C, D) and the output vector is O (P, Q, R, S).P =A, Q =A $\oplus$ B, R =A  $\oplus$  C and S= A(B+C)  $\oplus$ D.

Figure 8 shows the QCA representation of Six-Correction Logic Gate (DFSCL)

Fig.8 QCA block diagram of DFSCL gate

based of majority voter (MV) gate. Here eleven majority gates are used to design Six-correction logic gate (DFSCL).

#### **Simulation Result and Discussion**

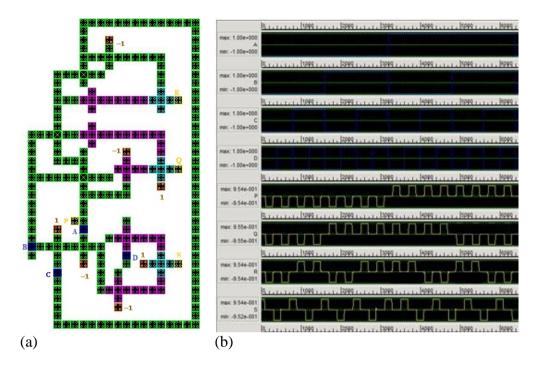

The circuit is functionally simulated using the QCADesigner (Budiman & Dysart, Jullien, T. J., R. A., Walus, 2004). The simulated circuit layout is shown in Figure 9, here the input signals are: A, B, C and D and the output signals are: P=A, Q=A $\oplus$ B, R=A  $\oplus$  C and S=A (B+C)  $\oplus$ D and this module goes through four clock zones, it means that the delay is a full clock cycle. Therefore, at the output P, Q, R and S are available one clock cycles after A, B, C and D has been applied. Moreover, it requires One Hundred Sixty (160) cells and total area of 0.22 µm<sup>2</sup>.

Fig.9 (a) QCA circuit layout of DFSCL logic gate and (b) simulated waveforms proposed circuit

We can find the output value of S is low level when the input digits (A = 0, B = 0, C = 0, D = 0) and S is up level when the input digits (A = 0, B)=0, C= 0, D =1). We look into the other two output values of A, B and C also translating the input data successfully. The simulated waveforms of DFSCL gate is shown in figure 10. Here, the S output is delayed by 1 clock cycle. Finally, in Table 1, designing parameters are compared.

| Table 1. Comparison of proposed DFSCL logic circuit designs |                 |                            |                     |

|-------------------------------------------------------------|-----------------|----------------------------|---------------------|

| Design                                                      | Number of Cells | Area (in µm <sup>2</sup> ) | Delay (clock cycle) |

| DFSCL logic circuit                                         | 160             | $0.22 \times 1.00 = 0.22$  | 1.00                |

#### Conlusion

This paper present New Double Feynman and Six-correction logic (DFSCL) gate based on QCA does logic gates. The proposed DFSCL gate has been simulated and verified using QCADesigner. The result is compared in terms of complexity (cell count), covered area and time delay. The simulation result shows that the proposed design achieves a sound improvement. This design will be very helpful for designing ultra low power digital circuits.

# **References:**

- 1. Abdullah-Al-Shafi, M., Aneek, R. H., Bahar, A. N. (2017). Universal Reversible Gate in Quantum-Dot Cellular Automata (QCA): A Multilayer Design Paradigm. International Journal of Grid and Distributed Computing, 10 (1), 43-50.

- 2. Abdullah-Al-Shafi, M., & Bahar, A. N. (2016). Optimized design and performance analysis of novel comparator and full adder in nanoscale. Cogent Engineering, **3**(1), 1237864.

- 3. Abdullah-Al-Shafi, M., Shifatul, M., & Bahar, A.N. (2015). A Review on reversible logic gates and its QCA implementation. *International Journal of Computer Applications*, **128(2)**, 27-34. 4. Abdullah-Al-Shafi, M., & Bahar, A. N. (2016, May). QCA: An

- effective approach to implement logic circuit in nanoscale. In Informatics, Electronics and Vision (ICIEV), 2016 5<sup>th</sup> International Conference on (pp. 620-624). IEEE.

- Abdullah-Al-Shafi, M., Bahar, A. N., Ahmad, P. Z., Ahmad, F., Bhuiyan, M. M. R., & Ahmed, K. (2017). Power analysis dataset for QCA based multiplexer circuits. *Data in Brief*, 11, 593-596.

6. Al Shafi, A., Bahar, A. N., & Islam, M. S. (2015). A quantitative

- approach of reversible logic gates in QCA. Journal of Communications Technology, Electronics and Computer Science, 3, 22-26.

- 7. Bahar, A. N., Habib, M. A., & Biswas, N. K. (2013a). A novel presentation of toffoli gate in quantum-dot cellular automata (QCA). *International Journal of Computer Applications*, **82**(10).

- Bahar, A. N., Roy, K., Asaduzzaman, M., Bhuiyan, M. M. R. (2017). Design and Implementation of 1-bit Comparator in Quantum-dot Cellular Automata (QCA). *Cumhuriyet Science Journal*, **38** (1), 146-152.

- 9. Bahar, A. N., Uddin, M. S., Abdullah-Al-Shafi, M., Bhuiyan, M. M. R., & Ahmed, K. (2017). Designing efficient QCA even parity generator circuits with power dissipation analysis. Alexandria Engineering Journal.

- 10. Bahar, A. N., & Waheed, S. (2016). Design and implementation of an efficient single layer five input majority voter gate in quantum-dot cellular automata. *SpringerPlus*, 5(1), 636.

11. Bahar, A. N., Waheed, S., Uddin, M. A., & Habib, M. A. (2013b). Double Feynman gate (F2G) in quantum-dot cellular automata (QCA). *International Journal of Computer Science Engineering* (MCGE) 2(6) 251-255. (IJCSE), 2(6), 351-355.

- 12. Bahar, A. N., Waheed, S., & Habib, M. A. (2014, April). A novel presentation of reversible logic gate in Quantum-dot Cellular

Automata (QCA). In Electrical Engineering and Information & Communication Technology (ICEEICT), 2014 International Conference on (pp. 1-6). IEEE.

- 13. Bahar, A. N., Waheed, S., & Hossain, N. (2015a). A new approach of presenting reversible logic gate in nanoscale. *SpringerPlus*, **4**(1), 153.

- 14. BAHAR, A. N., WAHEED, S., & HABİB, M. A. (2015b). An Efficient Layout Design of Fredkin Gate in Quantum-dot Cellular Automata (QCA). Düzce Üniversitesi Bilim ve Teknoloji Dergisi, **3**(1).

- 15. Bahar, A. N., Waheed, S., Hossain, N., Asaduzzaman, M. (2017). A novel 3-input XOR function implementation in quantum-dot cellular automata with energy dissipation analysis. *Alexandria Engineering* Journal.

- 16. Bhagyalakshmi, H. R., and Venkatesha, M. K. (2010). Optimized reversible BCD adder using new reversible logic gates. arXiv preprint arXiv:1002.3994.

- 17. Budiman & G. A., K., Dysart, Jullien, T. J., R. A., Walus, (2004). QCADesigner: A rapid design and simulation tool for quantum-dot cellular automata. Nanotechnology, IEEE Transactions on 3(1): 26-31.

- 18. Hao Li, Shiyong Li (2011). A Quantum Immune Evolutionary Hao Li, Shiyong Li (2011). A Quantum Immune Evolutionary Algorithm and Its Application. Journal of Computational Information Systems. 7, pp. 2972 – 2979.

Islam, M. S., Abdullah-Al-Shafi, M., & Bahar, A. N. (2016). A New Approach of Presenting Universal Reversible Gate in Nanoscale. International Journal of Computer Applications, 134 (7), 1–4.

Islam, S. S., Farzana, S., & Bahar, A. N. (2014). Area efficient layout design of Multiply Complements Logic (MCL) gate using QCA Technology. Global Journal of Research In Engineering, 14(4).

Islam, M. S. Shafi, M. A.-A., & Bahar, A. N. (2015).

- 21. Islam, M. S., Shafi, M. A.-A., & Bahar, A. N. (2015). Implementation of Binary to Gray Code Converters in Quantum Dot Cellular Automata. Journal on Today's Ideas Tomorrow's Technologies, 3(2), 145–160

- 22. Kim, K., Wu, K., and Karri, R., (2007). The robust QCA adder designs using composable QCA building blocks. *Computer-Aided Design of Integrated Circuits and Systems, IEEE Transactions on* **26**(1): 176-183.

- 23. Lent, C. S., & Tougaw, P. D. (1993). Lines of interacting quantumdot cells: A binary wire. Journal of applied Physics, 74(10), 6227-6233.

- 24. Lent, C. S., Tougaw, P. D., Porod, W., & Bernstein, G. H. (1993). Quantum cellular automata. *Nanotechnology*, **4**(1), 49.

- 25. Lent, C. S., & Tougaw, P. D. (1997). A device architecture for computing with quantum dots. *Proceedings of the IEEE*, **85**(4), 541–557.

- 26. Parhami, B. (2006, October). Fault-tolerant reversible circuits. In Signals, Systems and Computers, 2006. ACSSC'06. Fortieth Asilomar Conference on (pp. 1726-1729). IEEE.

- 27. Rahman, M. A., & Bahar, A. N. (2015). Six-Correction Logic (SCL) Gates in Quantum-dot Cellular Automata (QCA). *International Journal of Science and Engineering*, 9(1), 9-12.

28. Rahman, M. S., Waheed, S., & Bahar, A. N. (2015, November).

- 28. Rahman, M. S., Waheed, S., & Bahar, A. N. (2015, November). Optimized design of full-subtractor using new SRG reversible logic gates and VHDL simulation. *In Electrical & Electronic Engineering* (*ICEEE*), 2015 International Conference on (pp. 69-72). *IEEE*.

- 29. Roy, S., & Saha, B. (2006, September). Minority gate oriented logic design with quantum-dot cellular automata. In *International Conference on Cellular Automata* (pp. 646-656). Springer Berlin Heidelberg.

- 30. Sarker, A., Bahar, A. N., Biswas, P. K., & Morshed, M. (2014). A novel presentation of peres gate (PG) in quantum-dot cellular automata (QCA). *European Scientific Journal*, 10 (21), 101–106.

- Sarker, A., Miah, M. B. A., & Bahar, A. N. (2017). Design of 1-bit Comparator using 2 Dot 1 Electron Quantum-Dot Cellular Automata.*International Journal of Advanced Computer Science and Applications*, 8(3), 481-485.

- Applications, 8(3), 481-485.

32. Liu, Y. (2008). Modified Quantum Genetic Algorithm Apply for Flow Shop Scheduling Problem. *Journal of Computational Information Systems*, 4, 183-188.