ALEXANDRE DAVID BRANDÃO Front-ends para LiDAR baseados em ADC e TDC

ADC and TDC-based front-ends for LiDAR

ALEXANDRE DAVID BRANDÃO

## Front-ends para LiDAR baseados em ADC e TDC

ADC and TDC-based front-ends for LiDAR

"There is always a way if one does not avoid hard work."

— Demosthenes

## ALEXANDRE DAVID BRANDÃO

## Front-ends para LiDAR baseados em ADC e TDC

## ADC and TDC-based front-ends for LiDAR

Dissertação apresentada à Universidade de Aveiro para cumprimento dos requisitos necessários à obtenção do grau de Mestre em Engenharia Eletrónica e Telecomunicações, realizada sob a orientação científica do Doutor Arnaldo Silva Rodrigues de Oliveira, Professor Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Universidade de Aveiro, e do Doutor Miguel Vidal Drummond, Investigador Auxiliar do Instituto de Telecomunicações .

| o júri / the jury            |                                                                                                                                                                        |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| presidente / president       | Prof. Doutor Manuel Alberto Reis de Oliveira Violas<br>professor Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Universi-<br>dade de Aveiro |

| vogais / examiners committee | Prof. José Carlos dos Santos Alves<br>professor Associado da Faculdade de Engenharia da Universidade do Porto                                                          |

|                              | Prof. Arnaldo Silva Rodrigues de Oliveira<br>professor Auxiliar do Departamento de Eletrónica, Telecomunicações e Informática da Univerdade                            |

de Aveiro

## agradecimentos / acknowledgements

Um grande obrigado,

Aos meus pais, por apoiarem-me e sempre ter confiado em mim, Aos meus avós, por apoiarem-me e sempre ter confiado em mim, Ao meus irmãos, por serem os meus melhores amigos e um especial agradecimento ao meu irmão por tudo e principalmente a sua disponibilidade para ajudar, Ao Reis, Celso, Nuno, Bernardo, Josué, Pedro, Torres, Beatriz, Rios e ao Vala, por tantos anos de amizade e experiências.

Um especial agradecimento aos meus orientadores Miguel Drummond e Arnaldo Silva pela confiança, autonomia para explorar o problema, capacidade de motivar e capacidade de ensinar.

Agradeço ao Daniel Bastos pela paciência e apoio prestado durante todo o desenvolvimento do projeto.

Agradeço ao Eng.º Pedro Barbosa da Bosch por toda a ajuda prestada, e por ter gentilmente cedido uma primeira arquitetura de um TDC com base numa TDL sobre a qual a parte de TDCs desta tese foi elaborada.

Agradeço ao projeto SOFTLI, financiado pela Bosch Car Multi-media no âmbito do projeto Sensible Car (POCI010247FEDER037902). Este trabalho é financiado em parte pelo Fundo Europeu de Desenvolvimento Regional (FEDER), através do Programa Operacional Competitividade e Internacionalização, Programa Operacional Regional de Lisboa, Programa Operacional Regional do Algarve, na sua componente FEDER, e pela Fundação para a Ciência e Tecnologia, Projeto RETIOT, POCI-0145-FEDER-016432.

Agradeço ao Instituto de Telecomunicações por ter prestado os seus equipamentos.

Por último, agradeço à Universidade de Aveiro, por me acolher, fazer-me crescer e ajudar-me ao longos destes árduos 5 anos.

**Palavras Chave**

Conversores tempo para digital, Conversores analógicos para digitais, LiDAR, veículos autônomos

Resumo

Os veículos autónomos são uma tecnologia promissora para salvar mais de um milhão de vidas por ano, colhidas por acidentes rodoviários. Contudo, colocar veículos autónomos seguros no mercado requer inúmeros desenvolvimentos, a começar por sensores de visão. O LiDAR é um sensor de visão fundamental para veículos autónomos, pois permite uma visão 3D de alta resolução. Contudo, o LiDAR automotivo não é uma tecnologia madura, e portanto requer também desenvolvimento em vários aspectos.

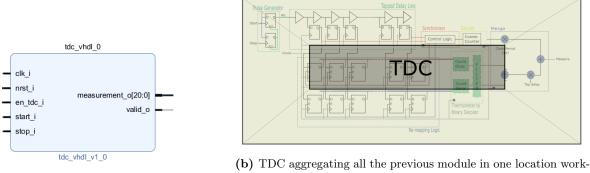

Esta dissertação visa contribuir para a maturidade do LiDAR, com foco em arquiteturas de amostragem para front-ends de LiDAR. Foram desenvolvidas duas arquiteturas. A primeira assenta numa ADC pipelined, por sua vez implementada numa placa de teste AD-FMCDAQ2-EBZ. A ADC opera em sincronismo com o pulso emitido, e permite capturar amostras a 1 Gsample/s. A segunda arquitetura assenta num TDC implementado diretamente numa FPGA. O TDC baseia-se numa topologia tapped delay line com 45 linhas de atraso, e num descodificador à base de multiplexers, permitindo uma resolução temporal de 50 ps.

Resultados preliminares mostram que ambas as implementações operam corretamente, e são adequadas para amostrar pulsos curtos tipicamente associados a LiDAR. Em termos comparativos, a arquitectura com base numa ADC tem um consumo de potência considerável e requer uma quantidade significativa de recursos da FPGA. Contudo, esta permite amostrar a forma de onda de LiDAR sem nenhuma perda de informação, permitindo assim alcance e precisão máximos. A arquitectura com base num TDC é exatamente o oposto: tem um baixo consumo de potência e requer poucos recursos da FPGA. Contudo, permite capturar apenas uma amostra por pulso.

Time-to-Digital Converters, Analog-to-Digital Converters, LiDAR, e autonomous vehicles.

Autonomous vehicles are a promising technology to save over a million lives each year that are lost in road accidents. However, bringing safe autonomous vehicles to market requires massive development, starting with vision sensors. LiDAR is a fundamental vision sensor for autonomous vehicles, as it enables high resolution 3D vision. However, automotive LiDAR is not yet a mature technology, and, also requires massive development in many aspects.

This thesis aims to contribute to the maturity of LiDAR, focusing on sampling architectures for LiDAR front-ends. Two architectures were developed. The first is based on a pipelined ADC, available from an AD-FMCDAQ2-EBZ board. The ADC is synchronized with the emitted pulse and able to sample at 1 Gsample/s. The second architecture is based on a TDC that is directly implemented in an FPGA. It relies on a tapped delay line topology comprising 45 delay elements and on a mux-based decoder, resulting in a resolution of 50 ps.

Preliminary test results show that both implementations operate correctly, and are both suitable for sampling short pulses typically used by LiDARs. When comparing both architectures, we conclude that an ADC consumes a significant amount of power, and uses many FPGA resources. However, it samples the LiDAR waveform without any loss of information, therefore enabling maximum range and precision. The TDC is just the opposite: it consumes little power, and uses less FPGA resources. However, it only captures one sample per pulse.

Keywords

Abstract

## Contents

| C        | onten  | ts                                      | i  |

|----------|--------|-----------------------------------------|----|

| Li       | st of  | Figures                                 | v  |

| Li       | st of  | Tables                                  | ix |

| G        | lossar | y                                       | xi |

| 1        | Intr   | oduction                                | 1  |

|          | 1.1    | Scope                                   | 2  |

|          | 1.2    | Motivation                              | 4  |

|          | 1.3    | Objectives                              | 5  |

|          | 1.4    | Document Stucture                       | 5  |

|          | 1.5    | Contributions                           | 6  |

| <b>2</b> | Fun    | damental ADC and TDC concepts           | 7  |

|          | 2.1    | Introduction                            | 7  |

|          | 2.2    | ADC Architectures                       | 7  |

|          |        | 2.2.1 SAR                               | 8  |

|          |        | 2.2.2 Delta-Sigma A/D                   | 10 |

|          |        | 2.2.3 Dual-Slope A/D $\ldots$           | 11 |

|          |        | 2.2.4 Flash A/D                         | 12 |

|          |        | 2.2.5 Pipelined A/D                     | 13 |

|          |        | 2.2.6 Summary                           | 14 |

|          | 2.3    | TDC Architectures                       | 15 |

|          |        | 2.3.1 Time-to-Amplitude Converter (TAC) | 15 |

|          |        | 2.3.2 Pulse Shrinking                   | 16 |

|          |        | 2.3.3 Tapped Delay Line                 | 17 |

|          |        | 2.3.4 Vernier Delay Line                | 19 |

|          |        | 2.3.5 Phased Clocks                     | 20 |

|   |      | 2.3.6   | Gated Ring Oscillator                              | 21 |

|---|------|---------|----------------------------------------------------|----|

|   |      | 2.3.7   | Summary                                            | 22 |

|   | 2.4  | Encodi  | ng Logic for Thermometer Code                      | 23 |

|   |      | 2.4.1   | ROM based Thermometer-to-Binary converter          | 24 |

|   |      | 2.4.2   | Wallace Tree based Thermometer-to-Binary converter | 26 |

|   |      | 2.4.3   | Fat-Tree based Thermometer-to-Binary converter     | 28 |

|   |      | 2.4.4   | Multiplexer Based Thermometer-to-Binary Converter  | 29 |

|   |      | 2.4.5   | Summary                                            | 32 |

| 3 | ADO  | C-based | l front-end                                        | 33 |

|   | 3.1  | Introdu | action                                             | 33 |

|   | 3.2  | Initial | setup                                              | 34 |

|   | 3.3  | AD-FN   | ICDAQ2-EBZ Evaluation Board overview               | 34 |

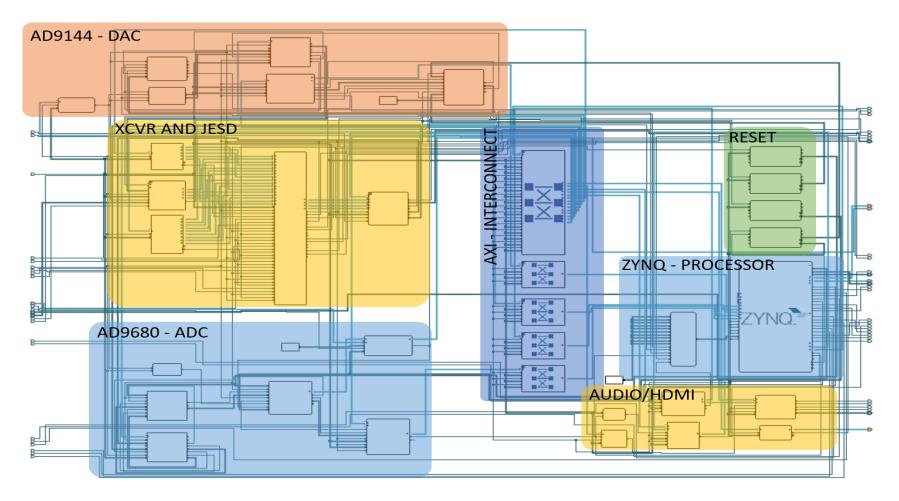

|   |      | 3.3.1   | Analog Devices Reference Design overview           | 34 |

|   |      | 3.3.2   | AD-FMCDAQ2-EBZ Clocking                            | 36 |

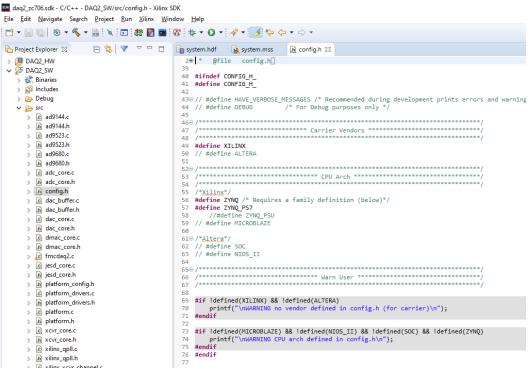

|   |      | 3.3.3   | Bare Metal AD-FMCDAQ2-EBZ Software                 | 37 |

|   | 3.4  | DAC/A   | ADC Front End implementation                       | 37 |

|   |      | 3.4.1   | Operating the DAC                                  | 38 |

|   |      | 3.4.2   | Operating the ADC                                  | 42 |

|   |      | 3.4.3   | Python user interface                              | 46 |

|   | 3.5  | Experi  | mental validation                                  | 47 |

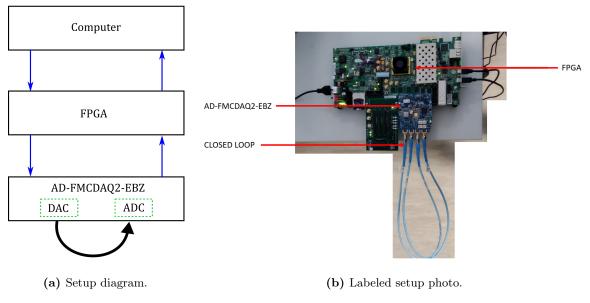

|   |      | 3.5.1   | Setup                                              | 47 |

|   |      | 3.5.2   | Results                                            | 47 |

| 4 | TDO  | C-based | front-end                                          | 49 |

|   | 4.1  | System  | overview                                           | 49 |

|   | 4.2  | Pulse g | generator                                          | 52 |

|   | 4.3  | Tapped  | l delay line                                       | 53 |

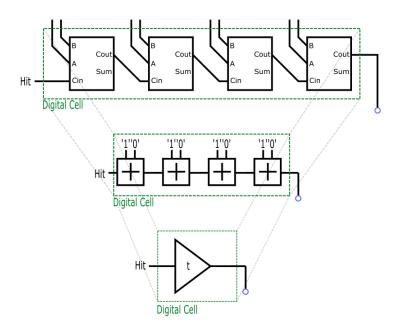

|   |      | 4.3.1   | Digital cell                                       | 53 |

|   |      | 4.3.2   | Tapped delay line topology                         | 54 |

|   | 4.4  | Synchr  | onizer                                             | 56 |

|   | 4.5  | Re-map  | pping logic                                        | 58 |

|   | 4.6  | Counte  | я <b>г</b>                                         | 59 |

|   | 4.7  | Counte  | er error                                           | 59 |

|   | 4.8  | Therm   | ometer-to-Binary decoder                           | 61 |

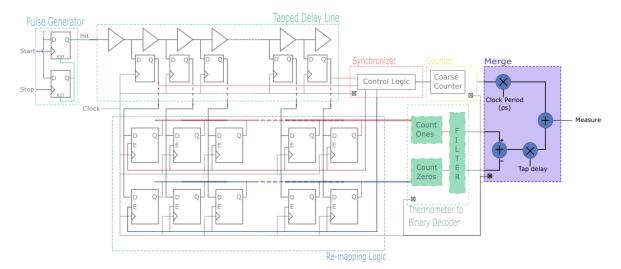

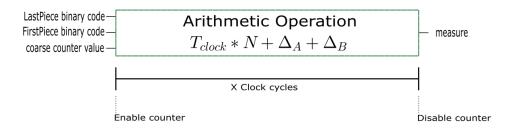

|   | 4.9  | Merge   |                                                    | 62 |

|   | 4.10 | Summa   | ary                                                | 65 |

| 5 | Imp  | lement  | ation of a TDC                                     | 67 |

| 5 | Implementation | of a | TDC |

|---|----------------|------|-----|

| U | implementation | or a | IDU |

|                           | 5.1            | Introduction |                                  |     |

|---------------------------|----------------|--------------|----------------------------------|-----|

|                           | 5.2            | Impler       | nentation and simulation results | 67  |

|                           |                | 5.2.1        | Vivado Design Suite              | 67  |

|                           |                | 5.2.2        | Module Implementation in VHDL    | 68  |

| 6                         | $\mathbf{Exp}$ | erimen       | tal validation of a TDC          | 93  |

|                           | 6.1            | Introd       | uction                           | 93  |

|                           | 6.2            | Digital      | l cell delay estimation          | 93  |

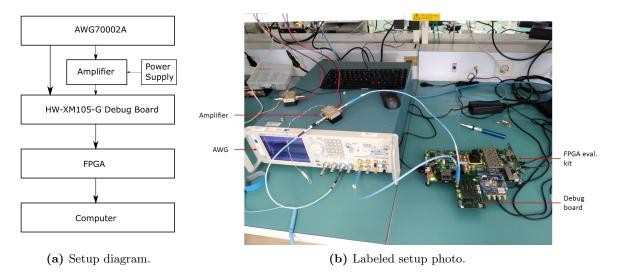

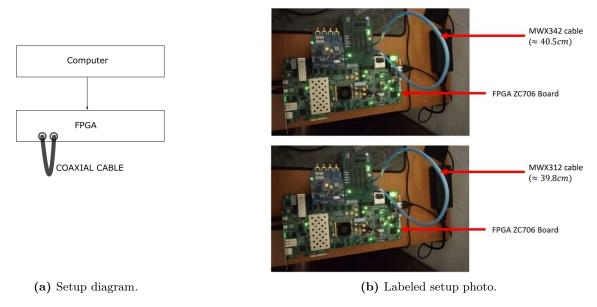

|                           |                | 6.2.1        | Experimental Setup               | 93  |

|                           |                | 6.2.2        | Results                          | 94  |

|                           | 6.3            | Estim        | ation Linearity                  | 94  |

|                           |                | 6.3.1        | Experimental Setup               | 94  |

|                           |                | 6.3.2        | Results                          | 97  |

|                           | 6.4            | Estima       | ation repeatability              | 98  |

|                           |                | 6.4.1        | Experimental setup               | 98  |

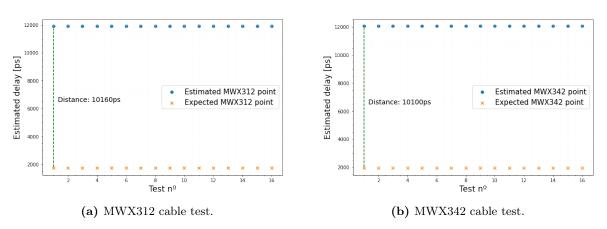

|                           |                | 6.4.2        | Results                          | 99  |

|                           | 6.5            | Resour       | rce usage                        | 99  |

|                           | 6.6            | Summ         | ary                              | 100 |

| 7                         | Con            | clusion      | I                                | 101 |

|                           | 7.1            | Future       | work                             | 102 |

| Bibliography 103          |                |              | 103                              |     |

| $\mathbf{A}_{\mathbf{j}}$ | ppen           | dix A        |                                  | 109 |

| $\mathbf{A}_{\mathbf{j}}$ | ppen           | dix B        |                                  | 119 |

# List of Figures

| 1.1  | The 6 levels of a vehicles autonomy ranging from fully manual to the vehicles full autonomy | 2  |

|------|---------------------------------------------------------------------------------------------|----|

| 1.2  | Some key sensors of an autonomous vehicle                                                   | 2  |

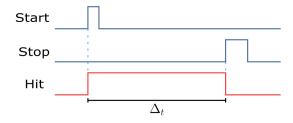

| 1.4  | Illustration of a ToF measuring system.                                                     | 4  |

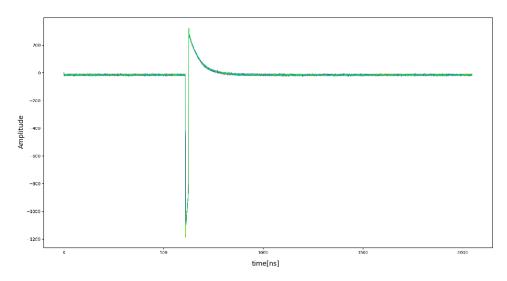

| 1.5  | Left side: ADC-based sampling. Right side: A direct ToF estimation obtained from a TDC.     | 5  |

| 2.1  | Conventional ADC architectures comparison                                                   | 8  |

| 2.2  | SAR Block Diagram.                                                                          | 8  |

| 2.3  | Operation of a 4-bit ADC based on SAR                                                       | 9  |

| 2.4  | Delta-Sigma Block Diagram.                                                                  | 10 |

| 2.5  | Modulator block diagram from Delta-Sigma architecture seen in the frequency domain          | 10 |

| 2.6  | Dual-Slope ADC graphical analysis                                                           | 11 |

| 2.7  | Flash ADC Diagram.                                                                          | 12 |

| 2.8  | Pipelined ADC diagram.                                                                      | 13 |

| 2.9  | Pipelined ADC operation for a 9-bit ADC                                                     | 13 |

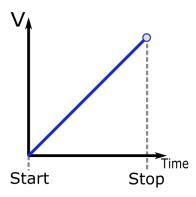

| 2.10 | Single-Slope Analog-To-Time-Interpolation converter.                                        | 15 |

| 2.11 | Single-Slope Analog-To-Time-Interpolation converter graphical illustration.                 | 16 |

| 2.12 | TDC common architectural block diagram for Pulse Shrinking                                  | 16 |

| 2.13 | Pulse Shrinking TDC internal architecture.                                                  | 17 |

| 2.14 | Tapped Delay Line.                                                                          | 17 |

| 2.15 | Tapped Delay Line temperature effect of average delay per digital cell                      | 18 |

| 2.16 | Coarse counter presence for increasing the dynamic range of the TDL                         | 18 |

| 2.17 | Vernier Delay Line concept                                                                  | 19 |

| 2.18 | Phased Clocks architecture.                                                                 | 20 |

| 2.19 | GRO architecture.                                                                           | 21 |

| 2.20 | Bubble effect                                                                               | 23 |

| 2.21 | ROM based encoder circuitry and scheme.                                                     | 24 |

| 2.22 | ROM based encoder example.                                                                  | 25 |

| 2.23 | ROM based encoder example analysis                                                          | 25 |

| 2.24 | Full digital ROM based encoder.                                                             | 26 |

| 2.25 | 3 Bit Wallace Tree Encoder.                                                                   | 27 |

|------|-----------------------------------------------------------------------------------------------|----|

| 2.26 | 4-bit Wallace Tree encoder example                                                            | 27 |

| 2.27 | Fat Tree encoder.                                                                             | 28 |

| 2.28 | Fat Tree logic analysis.                                                                      | 28 |

| 2.29 | Standard mux based encoder                                                                    | 29 |

| 2.30 | Mux based encoder algorithm.                                                                  | 30 |

| 2.31 | Mux Based encoder example                                                                     | 31 |

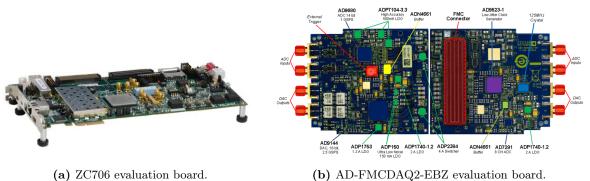

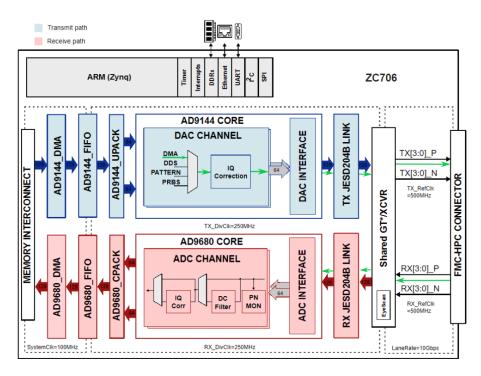

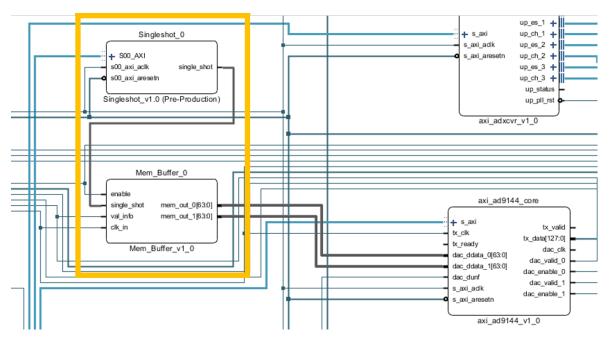

| 3.2  | Analog Devices setup for a Xilinx block diagram for the ZC706                                 | 35 |

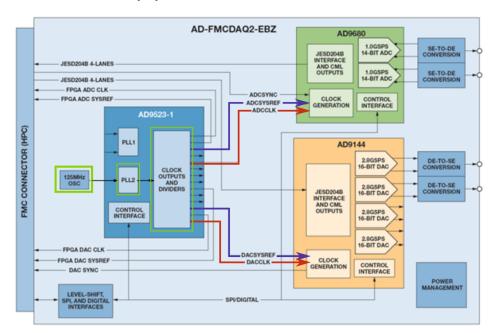

| 3.3  | AD-FMCDAQ2-EBZ Block Diagram                                                                  | 36 |

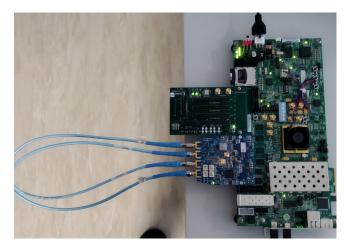

| 3.4  | Closed loop AD-FMCDAQ2-EBZ.                                                                   | 37 |

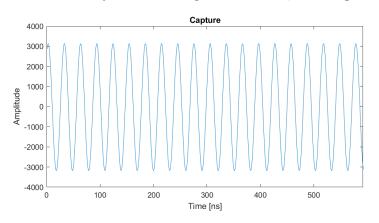

| 3.5  | Sine wave being repeatedly outputted cyclically by the DAC                                    | 37 |

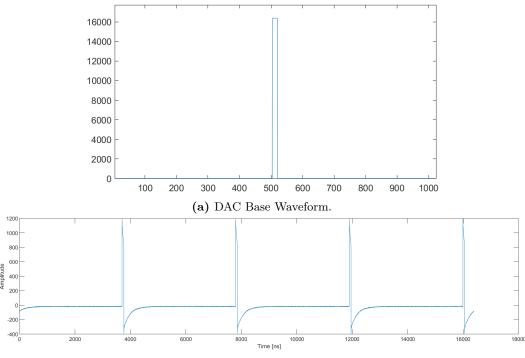

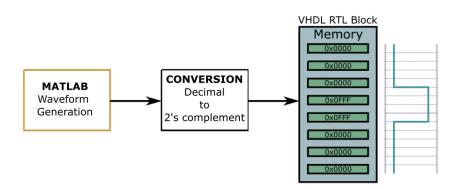

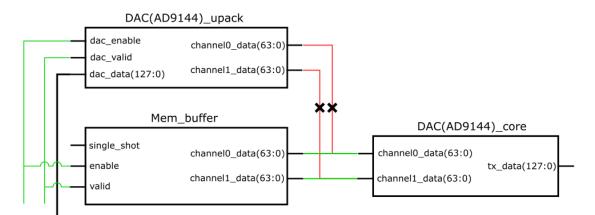

| 3.7  | From waveform generation to RTL memory block.                                                 | 39 |

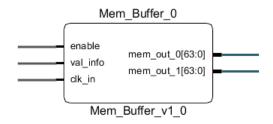

| 3.8  | First Version of the Memory Buffer operating in cyclic mode                                   | 39 |

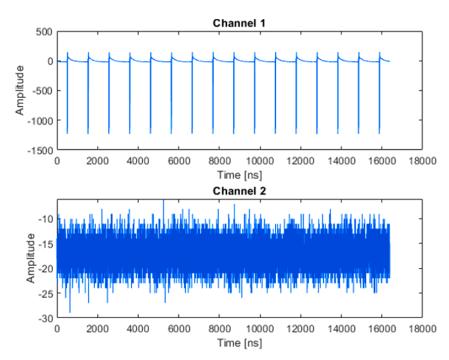

| 3.9  | Short pulses produced by the DAC. The bottom plot is the noise of the effect of disconnecting |    |

|      | the channel 2                                                                                 | 39 |

| 3.10 | Simplified diagram of the DAC upack block substitution for the new RTL mem_buffer block.      | 40 |

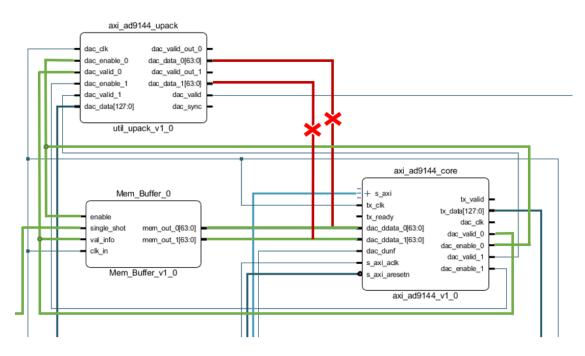

| 3.11 | Adding the new updated Register-Transfer Level (RTL) block to the Vivado Reference            |    |

|      | Design operating in single-shot                                                               | 40 |

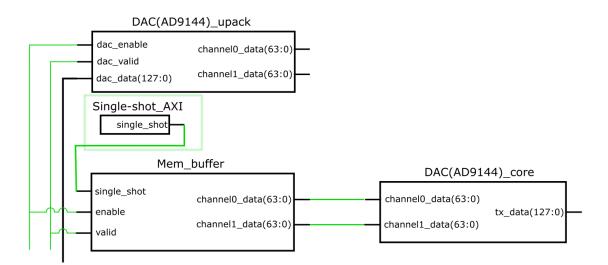

| 3.12 | Block diagram of the insertion of single-shot axi block.                                      | 41 |

| 3.13 | Connecting the new RTL block with the single shot RTL block.                                  | 41 |

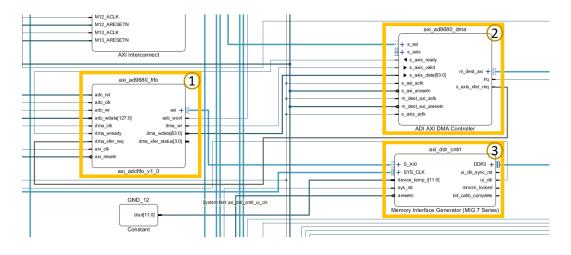

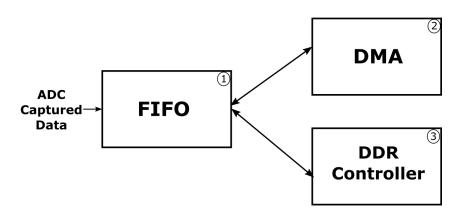

| 3.14 | Identified the block involved with the ADC for capturing and storing                          | 42 |

| 3.15 | Simplified block diagram of the block design for capturing and storing data.                  | 42 |

| 3.16 | Sample distribution.                                                                          | 42 |

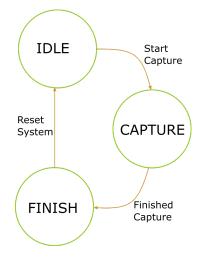

| 3.17 | Finite state machine diagram for the ADC                                                      | 43 |

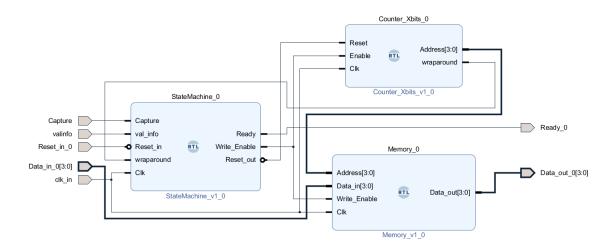

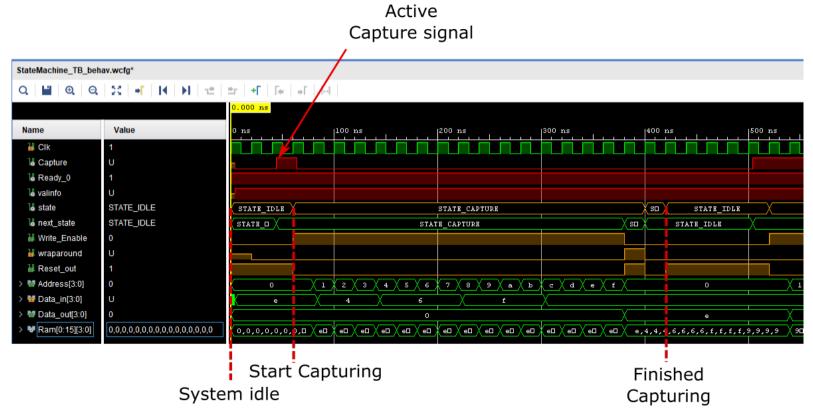

| 3.18 | Memory controller                                                                             | 44 |

| 3.19 | Testbench - memory controller in a simulated environment                                      | 45 |

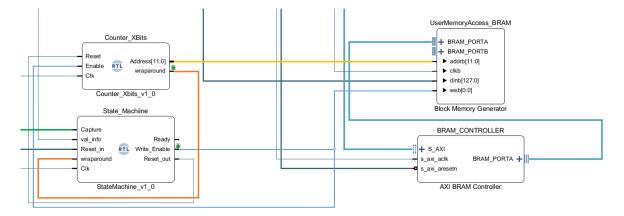

| 3.20 | Memory controller connected to the BRAM                                                       | 46 |

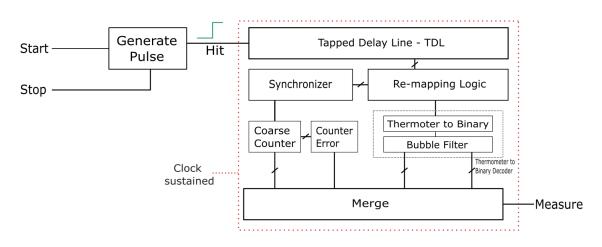

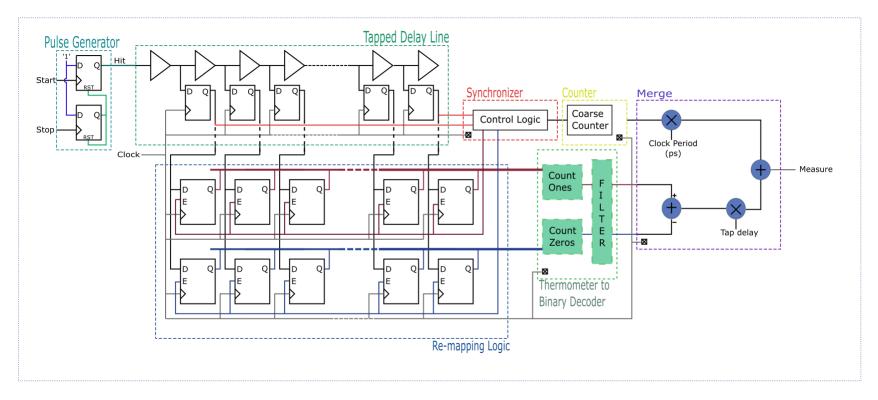

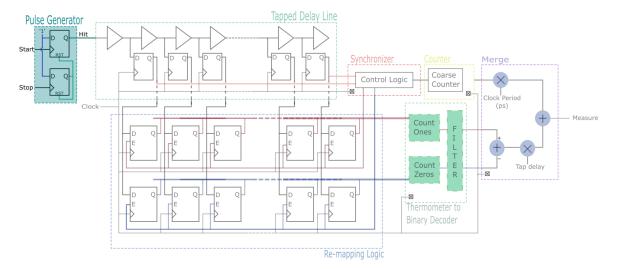

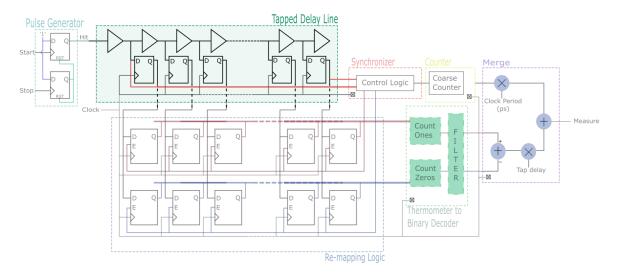

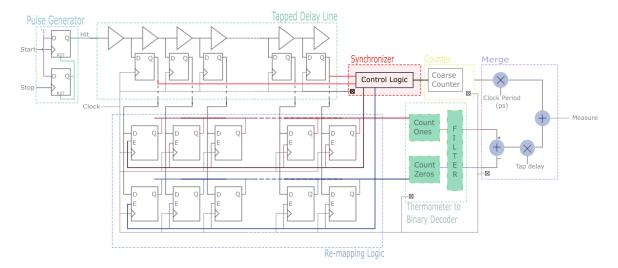

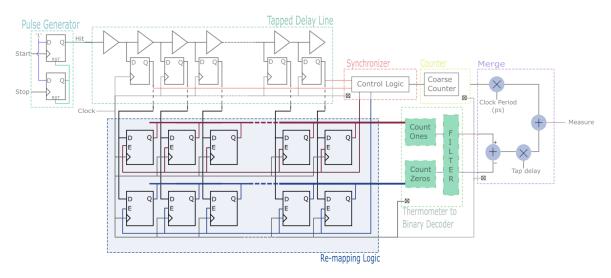

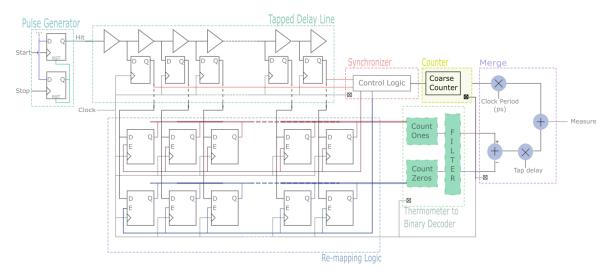

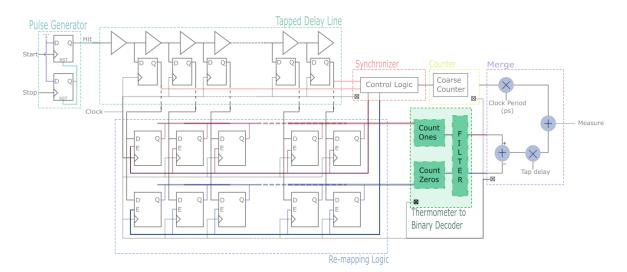

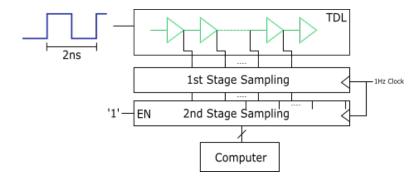

| 4.1  | System architecture overview.                                                                 | 49 |

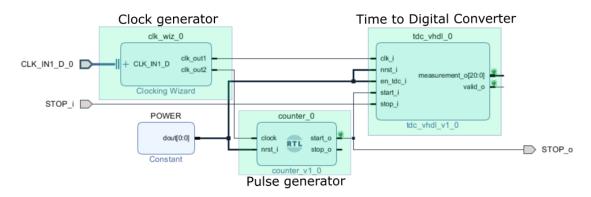

| 4.2  | Simplified RTL block diagram of the system architecture                                       | 51 |

| 4.3  | Pulse Generator block.                                                                        | 52 |

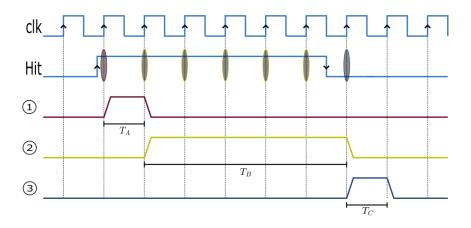

| 4.4  | Pulse Generator timing diagram                                                                | 52 |

| 4.5  | TDL block                                                                                     | 53 |

| 4.6  | Timing resolution expansion.                                                                  | 53 |

| 4.7  | Digital cell                                                                                  | 54 |

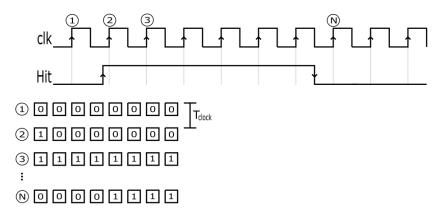

| 4.8  | Ideal representation of the system sampling the hit signal through the delay line             | 55 |

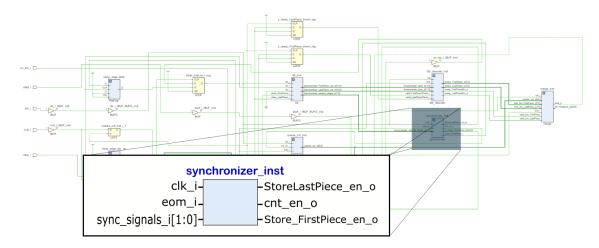

| 4.9  | Synchronizer block.                                                                           | 56 |

| 4.10 | Synchronizer datapath.                                                            | 56 |

|------|-----------------------------------------------------------------------------------|----|

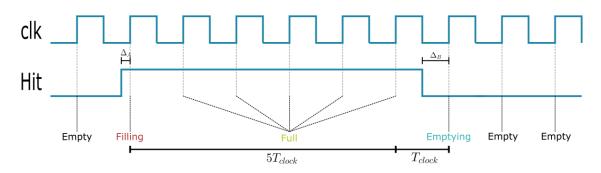

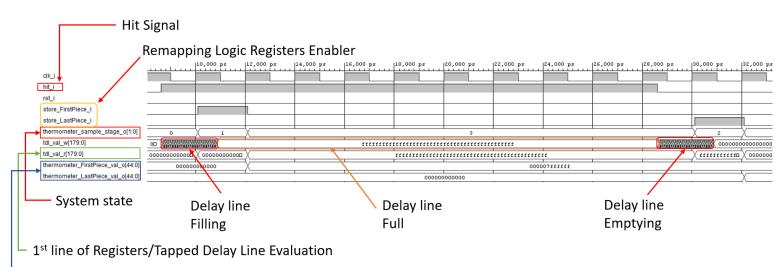

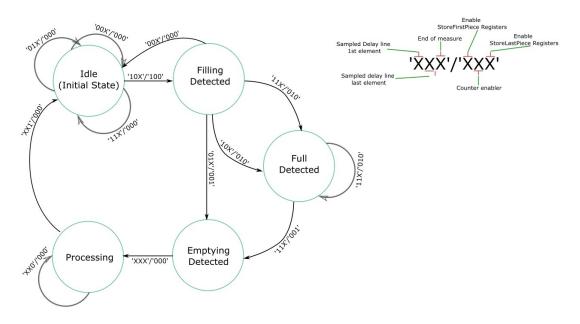

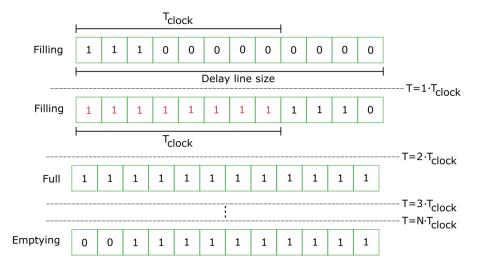

| 4.11 | Tapped delay line states.                                                         | 57 |

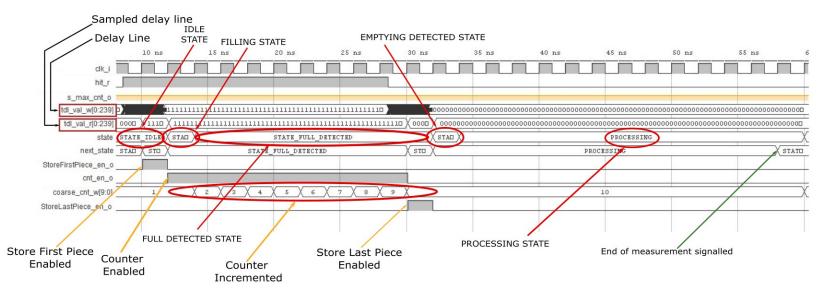

| 4.12 | Synchronizer timing diagram                                                       | 57 |

| 4.13 | Remapping Logic block                                                             | 58 |

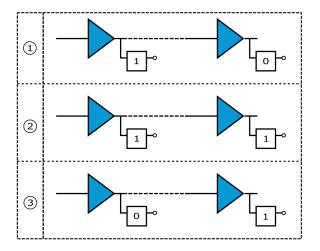

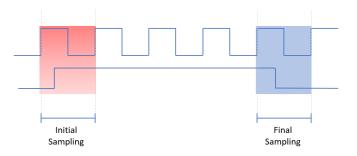

| 4.14 | First and last sampling stages of the hit signal                                  | 58 |

| 4.15 | Counter block.                                                                    | 59 |

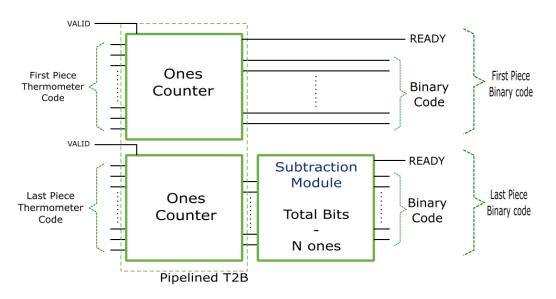

| 4.17 | Thermometer to Binary Decoder block.                                              | 61 |

| 4.18 | 14-bit pipelined mux based encoder with a counter in the final stages             | 61 |

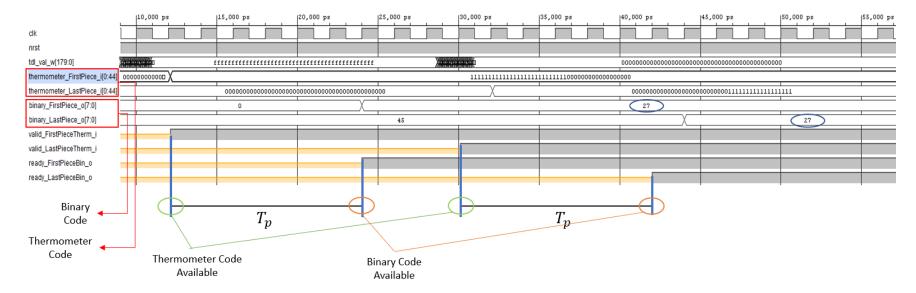

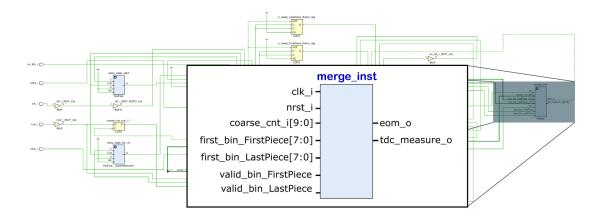

| 4.19 | Merge block                                                                       | 62 |

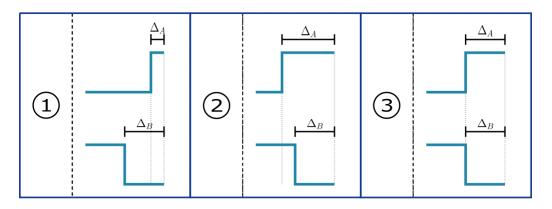

| 4.20 | Observation of System States                                                      | 63 |

| 4.21 | Possible Case Scenarios of the First and Last Piece of the TDL                    | 63 |

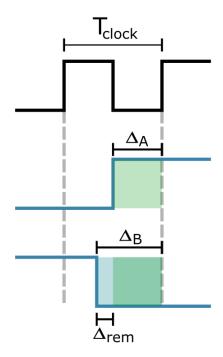

| 4.22 | Fine Measurement Analysis                                                         | 64 |

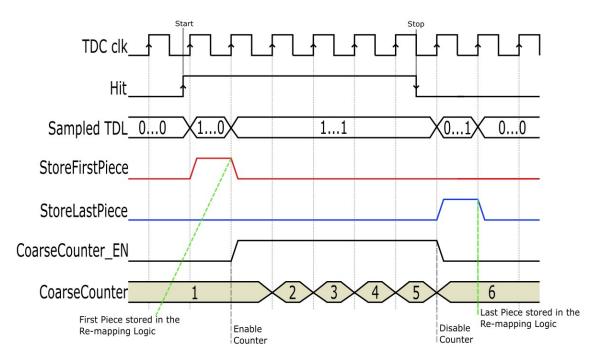

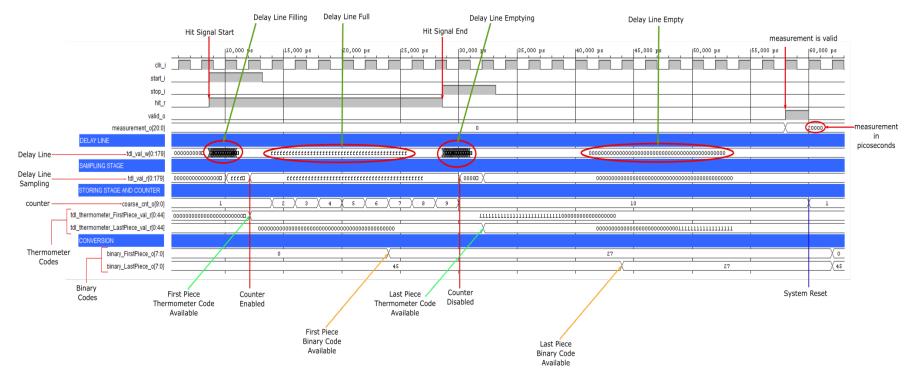

| 4.23 | System architecture timing diagram                                                | 65 |

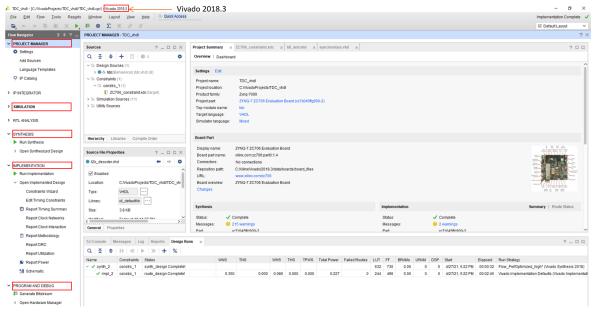

| 5.2  | Vivado 2018.3 Interface with focus on "Flow Navigator"                            | 68 |

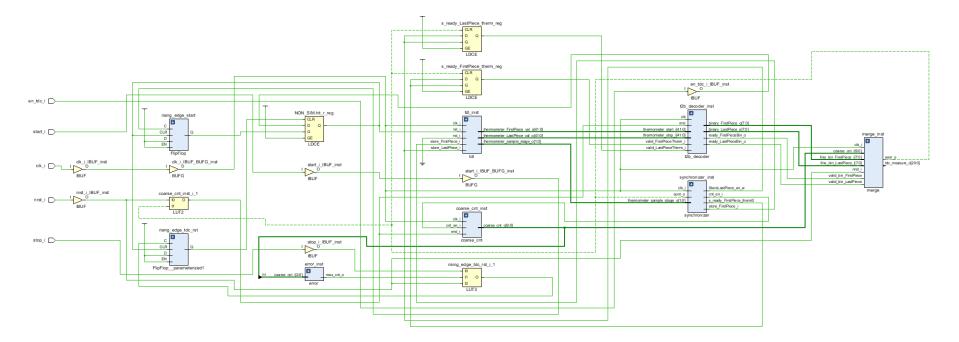

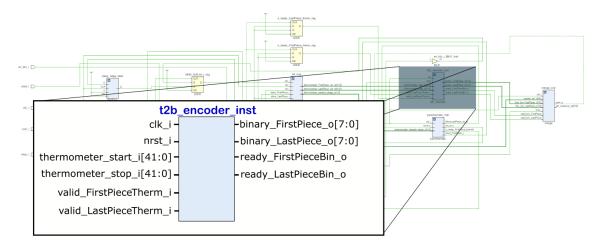

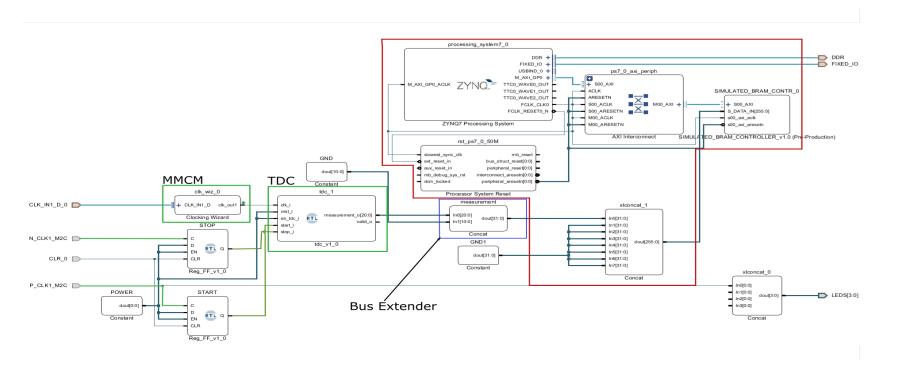

| 5.3  | System implementation overview.                                                   | 69 |

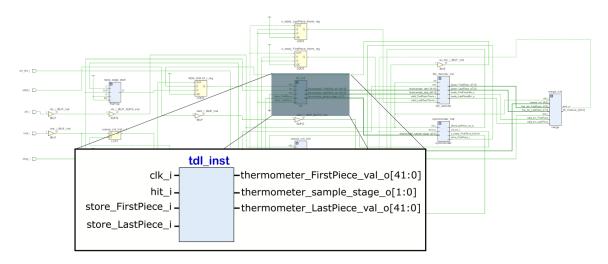

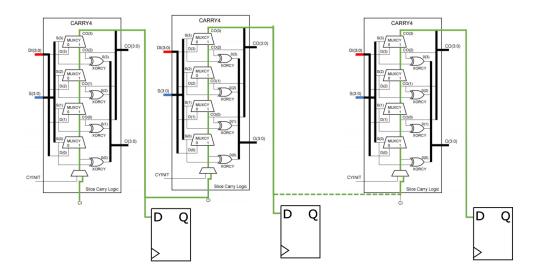

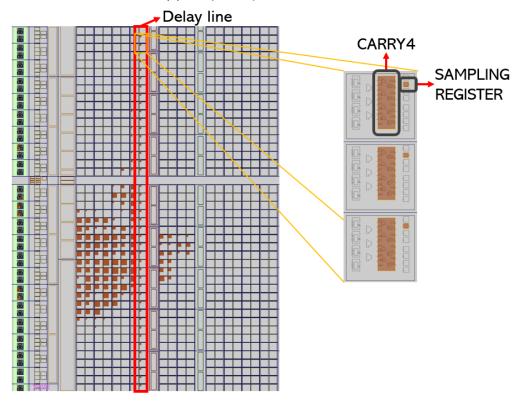

| 5.4  | TDL instantiation module.                                                         | 70 |

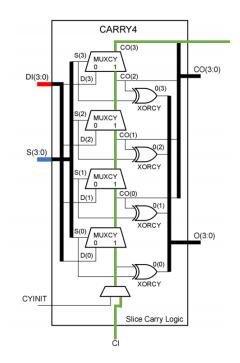

| 5.5  | CARRY4 Primitive from Zynq 7000 libraries                                         | 71 |

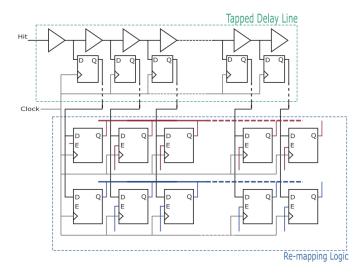

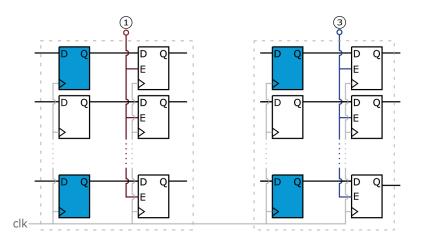

| 5.7  | TDL and Re-mapping Logic combined.                                                | 74 |

| 5.8  | Re-mapping Logic register datapath structure.                                     | 75 |

| 5.9  | TDL instantiation simulation results.                                             | 77 |

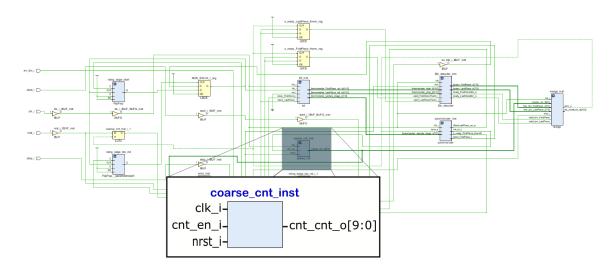

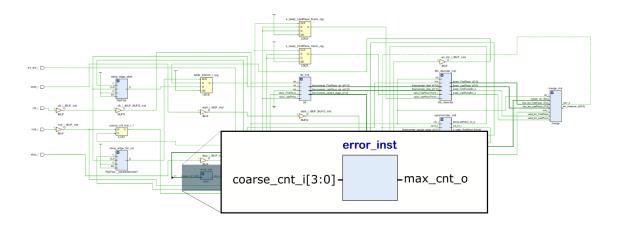

| 5.10 | Counter module.                                                                   | 78 |

| 5.11 | Counter simulation results.                                                       | 79 |

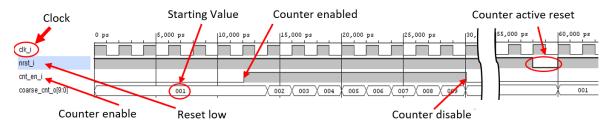

| 5.12 | Counter error module                                                              | 80 |

| 5.13 | Synchronizer module.                                                              | 81 |

| 5.14 | Synchronizer - Finite state machine                                               | 81 |

| 5.15 | Delay line temporal analysis of anomaly detected.                                 | 82 |

| 5.16 | Synchronizer simulations and FSM behavior.                                        | 83 |

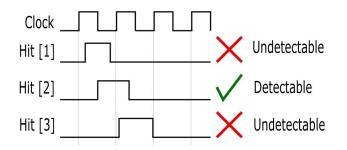

| 5.17 | System limitation representing case scenarios where the system may fail to detect | 84 |

| 5.18 | Thermometer to Binary module                                                      | 84 |

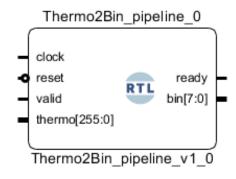

| 5.19 | Pipelined Thermometer to Bin encoder blackbox.                                    | 85 |

| 5.20 | T2B block diagram.                                                                | 85 |

| 5.21 | T2B simulation results.                                                           | 87 |

| 5.22 | Merge module                                                                      | 88 |

| 5.23 | Included counter for timing correction.                                           | 88 |

| 5.24 | TDC simplified RTL view and interface.                                            | 89 |

| 5.25 | Hit signal illustration.                                                          | 89 |

| 5.26 | TDC simulation results.                                                           | 90 |

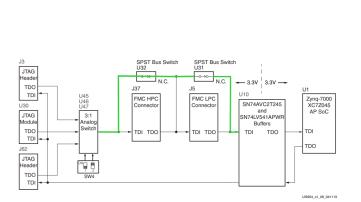

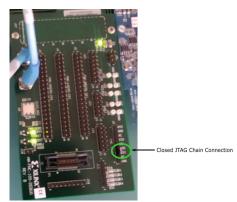

| 5.27 | Closing the ZC706 FMC LPC JTAG Chain.                                             | 91  |

|------|-----------------------------------------------------------------------------------|-----|

| 6.1  | Setup for the number of digital cells estimation necessary to fit one clock cycle | 93  |

| 6.2  | Visual results of the thermometer code sampled twice                              | 94  |

| 6.4  | Vivado - TDC Testing block diagram setup.                                         | 96  |

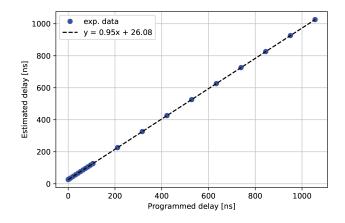

| 6.5  | Estimated delay as a function of the programmed delay                             | 97  |

| 6.7  | Vivado design setup for variance test.                                            | 98  |

| 1    | Vivado DAQ2 reference design.                                                     | 120 |

## List of Tables

| 2.1 | ADC state of the art architectures performance comparison. | 14 |

|-----|------------------------------------------------------------|----|

| 2.2 | TDC state of the art architectures summary                 | 22 |

| 2.3 | Thermometer encoding                                       | 23 |

| 3.1 | Memory controller actions.                                 | 44 |

| 3.2 | User interface operations                                  | 46 |

| 3.3 | ADC - FPGA resource usage on the ZC706.                    | 48 |

| 4.1 | Carry Lookahead Adder truth table                          | 54 |

| 6.1 | Base TDC FPGA resource usage on the ZC706.                 | 99 |

# Glossary

| AAF            | Anti-Aliasing Filtering       | $\mathbf{LSB}$  |

|----------------|-------------------------------|-----------------|

| ADC            | Analog-to-Digital Converter   | $\mathbf{LUT}$  |

| AXI            | Advanced eXtensible Interface | MCMM            |

| $\mathbf{ARM}$ | Advanced RISC Machine         | $\mathbf{MSB}$  |

| AWG            | Arbitrary Waveform Generator  | os              |

| $\mathbf{AV}$  | Autonomous Vehicle            | $\mathbf{PLL}$  |

| BRAM           | Block Random Access Memory    | $\mathbf{PL}$   |

| RCA            | Ripple Carry Adder            | PRBS            |

| CLB            | Configurable Logic Block      | PVT             |

| $\mathbf{CSV}$ | Comma Separated Value         | RF              |

| DAC            | Digital-to-Analog Converter   | ROM             |

| $\mathbf{DAQ}$ | Data Acquisition (System)     | BTL             |

| DDR            | Double Data Rate              | SAR             |

| $\mathbf{DLL}$ | Delay Locked Loop             | 01110           |

| DMA            | Direct Memory Access          | SONAR           |

| DOT            | Department of Transportation  | SDK             |

| DDS            | Direct Digital Synthesis      | $\mathbf{SPI}$  |

| ENOB           | Effective Number of Bits      | $\mathbf{SoC}$  |

| ETH            | Ethernet                      | $\mathbf{SPST}$ |

| $\mathbf{FSM}$ | Finite State Machine          | TDI             |

| FPGA           | Field Programmable Gate Array | TDO             |

| FIFO           | First In First Out            | $\mathbf{TDL}$  |

| FMC            | FPGA Mezzanine Card           | TDC             |

| GRO            | Gated Ring Oscillator         | ToF             |

| HDL            | Hardware Descriptive Language | TCL             |

| HPC            | High Pin Count                | UART            |

| ILA            | Integrated Logic Analyzer     |                 |

| IP             | Intellectual Property         | VLSI            |

| I2C            | Inter-Integrated Circuit      | $\mathbf{VDL}$  |

| JTAG           | Joint Test Action Group       | VCO             |

| LPC            | Low Pin Count                 | VHDL            |

| LiDAR          | Light Detection And Ranging   | ,               |

|                | - 0                           |                 |

| $\mathbf{LSB}$       | Least Significant Bit                            |

|----------------------|--------------------------------------------------|

| $\mathbf{LUT}$       | Look-Up Table                                    |

| MCMM                 | Mixed Mode Clock Manager                         |

| $\mathbf{MSB}$       | Most Significant Bit                             |

| os                   | Operating System                                 |

| $\mathbf{PLL}$       | Phase Locked Loop                                |

| $\mathbf{PL}$        | Programmable Logic                               |

| PRBS                 | Pseudorandom Binary Sequence                     |

| $\mathbf{PVT}$       | Process-Voltage-Temperature                      |

| $\mathbf{RF}$        | Radio Frequency                                  |

| ROM                  | Read Only Memory                                 |

| $\mathbf{RTL}$       | Register-Transfer Level                          |

| $\mathbf{SAR}$       | ${\it Successive-Approximation-Register}$        |

| SONAR                | Sound Navigation and Ranging                     |

| SDK                  | Software Development Kit                         |

| SPI                  | Serial Peripheral Interface                      |

| $\mathbf{SoC}$       | System on Chip                                   |

| SPST                 | Single Pole Single Throw                         |

| TDI                  | Test Data in                                     |

| TDO                  | Test Data out                                    |

| $\operatorname{TDL}$ | Tapped Delay Line                                |

| TDC                  | Time-to-Digital Converter                        |

| ToF                  | Time of Flight                                   |

| TCL                  | Tool Command Language                            |

| UART                 | Universal Asynchronous Receiver<br>Transmitter   |

| VLSI                 | Very Large-Scale Integration                     |

| $\mathbf{VDL}$       | Vernier Delay Line                               |

| VCO                  | Voltage Controlled Oscillator                    |

| VHDL                 | Very High Speed Hardware Description<br>Language |

## CHAPTER

1

## Introduction

Each year approximately 1.35 million people die as a result of traffic accidents. According to the US Department of Transportation's National Highway Traffic Safety Administration, 94% of the severe traffic accidents happen because of human errors [1]. The Department of Transportation (DOT) believes that fully Autonomous Vehicles (AVs) have the potential to significantly reduce traffic fatalities by up to 90 percent, as it removes human error [2]. This means that a AVs may be able to save more than 1 million lives every year.

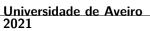

Although, the prospect of fully AV seems very near, it still seems paradoxically impossibly futuristic as safe AVs are extremely complex to implement. This can be easily observed by looking to the roadmap towards complete autonomy, shown in figure 1.1.

Figure 1.1: The 6 levels of a vehicles autonomy ranging from fully manual to the vehicles full autonomy reproduced from [3], [4].

#### 1.1 Scope

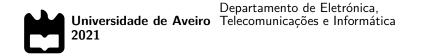

Levelling up the autonomy of a vehicle requires safe decision-making algorithms, which in turn require detailed information about the vehicle surroundings. This is why vision sensors are a fundamental part of an AV. Some key vision sensors are observed in figure 1.2.

Figure 1.2: Some key sensors of an autonomous vehicle reproduced from [4].

Just like human senses, sensors must be strategically positioned in an AV to continuously feed information on the car's surroundings [5]. However, there is a limit to where sensors can be placed and there is no sensor that can fit all the requirements. Consequently, multiple sensors are required to complement each-other and whose combination is highly effective in creating a safe and automated driving experience.

Figure 1.3 presents an overview of the various and most common sensors required for autonomous driving such as cameras, Sound Navigation and Ranging (SONAR), Light Detection And Ranging (LiDAR) and RADAR.

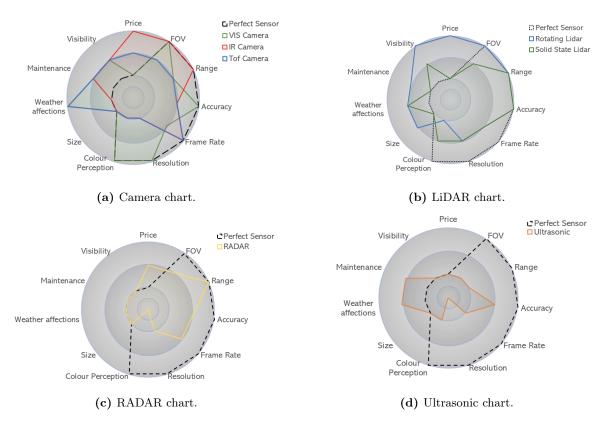

Figure 1.3: Key sensors radar charts adapted from [6].

Cameras are the main sensor for 2D vision. However, cameras lack precision in providing 3D vision, a vital feature for safe driving. LiDAR has the unique capability of providing a detailed and accurate point cloud of the surroundings of the vehicle. The LiDAR sensors are now implemented in autonomous vehicles to be the eyes of the car, providing them 360 degrees view helping them change lanes, keeping a safe distance from other vehicles and pedestrian and spotting roadblocks and other obstructions [7]. However, contrary to all the others sensors, LiDAR still has a long way to go as the technology is still improving and has not yet matured. LiDAR is also far away from meeting the reasonable costs [8].

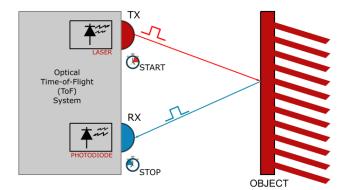

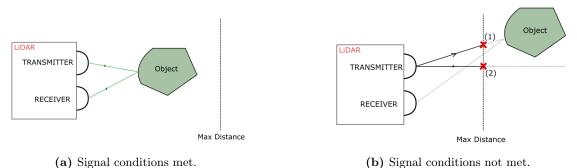

Figure 1.4: Illustration of a ToF measuring system adapted from [9].

The basic operation principe of a LiDAR, which is estimating the Time of Flight (ToF), is depicted in figure 1.4. The distance is given by (1.1).

$$d = \frac{ToF}{2c} = \frac{Stop - Start}{2c},\tag{1.1}$$

where, d is the distance between the LiDAR and the object, c is the speed of light, *Start* is the time at which the LiDAR emits the pulse and *Stop* is the time at which the LiDAR receives the pulse.

According to (1.1), it is very important that the LiDAR is temporally precise as 1 cm takes only about 50 ps. As such, it is fundamental that the received signal is adequately sampled and digitally processed.

#### 1.2 MOTIVATION

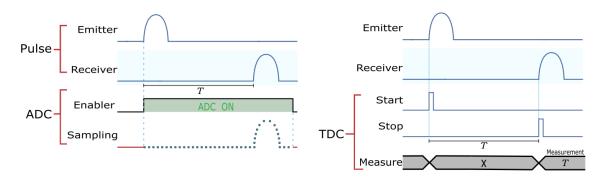

The main motivation of this work is to devise suitable sampling architectures for LiDAR. Two architectures are studied, one based on an Analog-to-Digital Converter (ADC), and another based on a Time-to-Digital Converter (TDC).

On each side of the figure 1.5 is an example of an ADC and TDC based sampling methods. An ADC-based architecture is useful for a full-waveform LiDAR [10], and thus for achieving best possible range and precision. In contrast, a TDC-based architecture is not suitable for full-waveform nor optimal performance; however, it can be directly implemented in an Field Programmable Gate Array (FPGA) as an all-digital design.

Figure 1.5: Left side: ADC-based sampling. Right side: A direct ToF estimation obtained from a TDC.

#### 1.3 Objectives

The main objective of this dissertation is to study, implement and compare two different sampling methods suitable for LiDAR. This results in the following objetives.

- 1. Find out which types of ADCs are appropriate for a LiDAR.

- 2. Configure an ADC with a suitable architecture for operating according to the needs of a LiDAR.

- 3. Investigate whether a TDC can be implemented directly in an FPGA.

- 4. If point 3. is observed to be true, implement a TDC directly in an FPGA.

- 5. Compare both implementations (ADC vs. TDC) based on the obtained results.

#### 1.4 DOCUMENT STUCTURE

This document is divided in 7 chapters, including this introductory chapter:

**Chapter 1** - *Introduction*: contextualization of the topic and scope of this document, the motivation for this research and what it attempts to clarify. Briefly describes how the document is organized and the contributions associated with this research.

**Chapter 2** - *Fundamental ADC and TDC concepts*: Study and research on various state of the art implementations for ADC and TDC with the purpose of identifying the sampling architectures that best suit the application at hand.

**Chapter 3** - *ADC* - *based front-end*: This chapter explains the steps taken to implement a sampling method based on ADC suitable for LiDAR in a workflow manner. It presents the experimental results from the work developed.

**Chapter 4** - *TDC* - *based front-end*: This chapters describes at a conceptual level the design of the TDC architecture to implement a suitable sampling method for LiDAR.

**Chapter 5** - *Implementation of a TDC*: This chapters describes the implementation design of the TDC architecture, and presents corresponding simulation.

**Chapter 6** - *Experimental validation of a TDC*: This chapters presents corresponding experimental results of the implementation design of the TDC architecture.

**Chapter 7** - *Conclusion*: a summary of the results and outcomes presented and discussed across the document, along with some topics for future work.

#### 1.5 Contributions

The software and hardware developed for this dissertation can be accessed on the author's personal GitHub page, on https://github.com/alexandre-brandao/SOFTLI. Several Very High Speed Hardware Description Language (VHDL) modules were developed to meet the requirements of the dissertation, namely, ADC and TDC implementation in a LiDAR context.

- Set the ADC/DAC as fully synchronous and operating as single-shot.

- Added a python interface to operate the ADC/DAC for ADC implementation in a LiDAR context.

- Implementation and development of an all-digital TDC based on a tapped delay line and a mux-based encoder.

- Development of an all-digital TDC with features that, to the best of the author's knowledge, have not been found in the literature.<sup>1</sup>

- Co-author of an invention report within the scope of project SOFTLI, titled "Interferenceresilient LiDAR waveform and estimation method thereof". Such an invention relies on TDCs.

<sup>&</sup>lt;sup>1</sup>Please refer to section 4.10 for more detail.

# CHAPTER 2

# Fundamental ADC and TDC concepts

#### 2.1 INTRODUCTION

In this chapter, ADC and TDC architectures suitable for ToF measurement are examined and discussed. The chapter starts with the study of various conventional ADC architectures to find the best architecture that suits this dissertations needs based on power, speed and accuracy. Next is a study of the various TDCs architectures to investigate the possible implementation of a TDC in an FPGA. As a last study, search for a suitable thermometer encoder which is typically coupled with a TDC.

#### 2.2 ADC Architectures

When looking for an ADC, there are three important features that should be considered:

- 1. Sampling rate.

- 2. Power consumption.

- 3. Resolution (Effective Number of Bits (ENOB)).

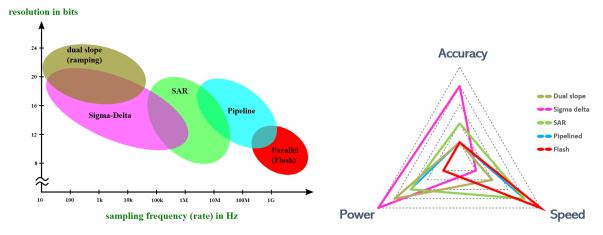

Defining such features is important as it rules out some ADC architectures, leaving others to be chosen. The reason for such a rationale is that, unfortunately, there is no "one size fits all" architecture. Figure 2.1 illustrates the tradeoffs of the conventional architectures.

(a) Conventional ADC architectures comparison diagram in (b) Some of the conventional ADC architectures terms of resolution vs speed.

trade-offs on a radar chart.

Figure 2.1: Conventional ADC architectures comparison adapted and reproduced from [11], [12].

The following subsections discuss different ADC architectures with its respective pros and cons, namely:

- 1. SAR.

- 2. Delta-Sigma A/D.

- 3. Dual-Slope A/D.

- 4. Flash A/D.

- 5. Pipelined A/D.

#### 2.2.1SAR

Successive-Approximation-Register (SAR) architecture has been used for decades. SAR ADCs are very common, stable and reliable and are also known as the "Bread and Butter" of the the Data Acquisition (System) (DAQ) world.

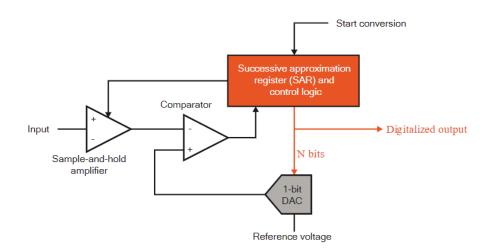

Figure 2.2: SAR Block Diagram reproduced from [13].

The Input signal is initially held on the sample-and-hold circuit that outputs a signal that will remain constant at the input  $V^-$  of the comparator until the circuit decides if it has successfully created a word. The output of the Digital-to-Analog Converter (DAC) is connected at the input  $V^+$  of the comparator which creates an analog reference voltage based on the N bit digital word generated from the control logic. The N bit digital word is based on a binary search algorithm which tries to successfully divide the reference voltage until the output of the DAC matches the sampled input voltage which is being held by the sample-and-hold circuit.

The algorithm works by starting with the N-bit register, the digitalized output. This output is first set the Most Significant Bit (MSB) to 1 and the remaining bits to 0, that is, 100...00. This forces the DAC output half of the reference voltage, where the DAC output voltage is provided to the comparator, where it will output a high or low signal and consequently be evaluated by the control logic. At this point the MSB of the digitalized remains with the logic attribute assigned by the comparator. The SAR control logic then moves to the next bit down, forces that bit high, and does another comparison. This process continues for *n* successive times, with *n* being the bit resolution of the ADC itself, until the closest value to the actual signal is found [13], [14] as shown in the figure. 2.3.

Figure 2.3: Operation of a 4-bit ADC based on SAR.

*Pros and cons.* This architecture is capable of handling a wide variety of signals with excellent fidelity whilst offering a good balance between speed and resolution [13] and can possess high sampling rate. The disadvantage of this architecture is that these ADCs do not possess any inherent Anti-Aliasing Filtering (AAF) to get rid of higher-frequency noise and signals, unless it is manually added.

*Applications.* Applications for SAR ADCs include DAQ systems, from low-end multiplexed ADC systems to higher speed ADC systems, industrial control and measurement and CMOS imaging [13].

#### 2.2.2 Delta-Sigma A/D

Delta-Sigma architectures are known for their high bit resolution systems as they are able to strongly reduce quantization error.

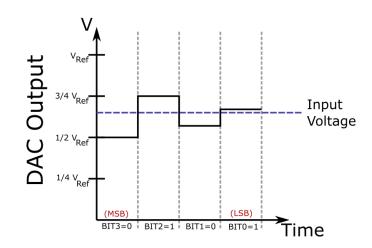

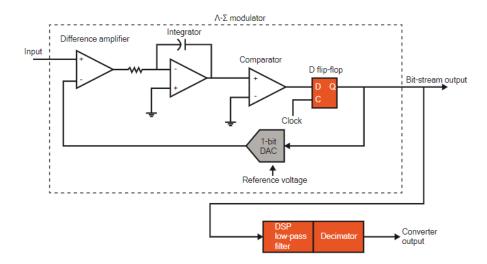

Figure 2.4: Delta-Sigma Block Diagram adapted from [13].

This architecture uses oversampling to sample far higher than the base sample rate. The Delta-Sigma ADC consists of a modulator, a filter, and a decimator described next, these ADCs are mostly digital.

$\Delta - \Sigma$  modulator. This module is used for noise shaping of the oversampled input signal consisting of a difference amplifier, an integrator, a comparator and a 1 bit DAC, which essentially also acts as a comparator. In the figure 2.5 is the another form the modulator representation.

Figure 2.5: Modulator block diagram from Delta-Sigma architecture seen in the frequency domain reproduced from [15].

The integrator in this architecture acts as a low-pass filter to the input signal. Quantization noise is added to the signal output of this filter due to the 1-bit conversion process. The output of the modulator can be represented using (2.1) [15].

$$S_o(f) = \frac{S_i(f) + qf}{f+1} = \frac{S_i(f)}{f+1} + \frac{qf}{f+1},$$

(2.1)

where q is the quantization noise.

The first term of the equation (2.1) is considered the signal term and the second term can be considered the noise term. As the frequency approaches zero, it can be seen that the noise term approaches zero and the output of modulator approaches  $S_i$ . As the frequency is increased, the noise term approaches q and the signal term approaches zero. Thus, the integrator acts as a high-pass filter for the quantization noise [15].

DSP Low-pass filter. The effect of the low pass filter eliminates the second term of the eq. 2.1. Resulting in a clean output signal given by (2.2).

$$S_o(f) = \frac{S_i(f)}{f+1}.$$

(2.2)

*Decimator.* Decimation is the process of discarding the unnecessary samples and is used as a mechanism to reduce the data rate to a usable value whilst maintaining the information.

*Pros and Cons.* This approach creates a very high-resolution data stream and has the advantage of allowing multistage AAF, making it virtually impossible to digitize false signals [13]. However, this architecture pays in speed.

*Applications.* Data acquisition, especially noise and vibration, industrial balancing, torsional and rotational vibration, power quality monitoring, precision industrial measurements, audio and voiceband, communications [13].

#### 2.2.3 Dual-Slope A/D

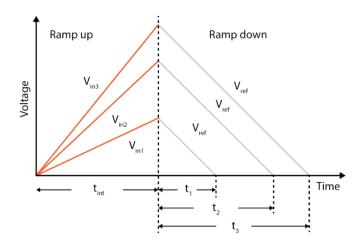

Dual Slope ADC are accurate and possess medium to high speed in relation to other architectures.

Figure 2.6: Dual-Slope ADC graphical analysis reproduced from [13].

This principle is simple, the input voltage is allowed to "run up" for a controlled period of time [13]. Once the signal has been set up for a set duration, a known voltage starts running down at a fixed speed when the polarity is changed. When the known voltage hits the value 0, the systems compares the time stamps and calculates the input voltage based on the time stamps relation.

*Pros and Cons.* This architecture is simple, very precise and accurate, but as the graph indirectly shows, the setup lacks the speed.

Applications. Handheld and benchtop multimeters[13].

# 2.2.4 Flash A/D

Flash ADCs are very well known ADCs. This is due to to their conversion speed and is also very simple to understand. Their conversion speed is the fastest out of the architectures and operate with negligible latency.

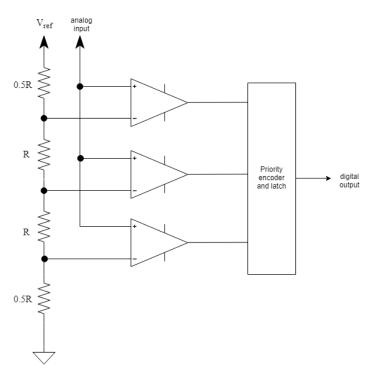

Figure 2.7: Flash ADC diagram reproduced from [16].

The flash ADC resolution is limited by the number of resistors, this means that if we want an N bit flash ADC, there is a need for  $2^N$  resistors and  $2^N - 1$  comparators.

*Pros and Cons.* This circuit is ideal for the need of high sampling rates, however there's a big price to pay with power vs resolution.

*Applications.* Fastest digital oscilloscopes, microwave measurements, fiber optics, RADAR detection, and wideband radio [13].

#### 2.2.5 Pipelined A/D

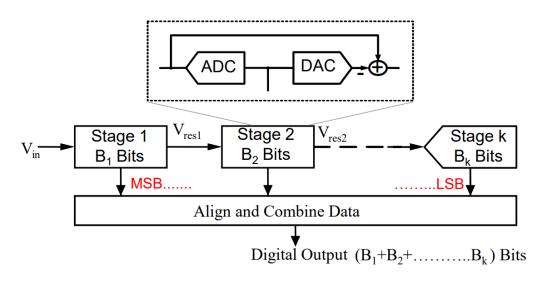

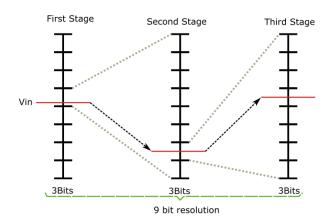

The Pipelined ADC stands on the middle ground in terms of speed. It is faster than the SAR and delta-sigma architectures but slower than flash ADC.

Figure 2.8: Pipelined ADC diagram reproduced from [17].

This architecture cascades low resolution stages to obtain high overall resolution, can also be seen as the pipelined version of the flash ADC. The flash ADC latches all of its comparators to one reference voltage, however, in a pipelined ADC, the analog signal is not latched by all comparators at the same time, thus spreading out the energy required to convert the analog to a digital value as seen in the figure 2.8. Each stage performs coarse A/D conversion and computes its quantization error. In this type of ADC, the conversion takes two steps. During the first step, the most significant bits of the digital output are determined by the first stage flash ADC. Then a DAC converts this digital result back to an analog signal to be subtracted from the input signal. This residue is amplified by the inter-stage gain amplifier and then sent to the second stage flash ADC. The second stage flash determines the least significant bits of the digital output, as shown in the figure 2.9.

Figure 2.9: Pipelined operation for a 9 bit ADC [18].

*Pros and Cons.* This architecture allows high resolution without using huge amounts of energy. On the other hand, this architecture is slower than the Flash ADC.

*Applications.* Digital oscilloscopes, RADAR, software radios, spectrum analyzers, HD video, ultrasonic imaging, digital receivers, cable modems, and Ethernet [13].

# 2.2.6 Summary

| ADC Type  | Slope     | Sigma-Delta        | SAR             | Pipelined  | Flash          |

|-----------|-----------|--------------------|-----------------|------------|----------------|

| Accuracy  | 6-20 bits | 16-32 bits         | 6-16 bits       | 8-16 bits  | $<\!\!12$ bits |

| Speed     | Slowest   | Slow               | Moderate        | High       | Highest        |

| Bandwidth | Slowest   | Slow               | Moderate        | High       | Highest        |

| Latency   | Moderate  | Highest            | Low             | High       | Lowest         |

| Power     | Low       | Moderate           | Low             | Low        | High           |

| Area      | Small     | Small              | Small           | Small      | High           |

| Pros      | Accurate, | High stability and | Good            | Very fast  | Fastest        |

|           | inexpen-  | dynamic perfor-    | speed/resolutio | n          |                |

|           | sive      | mance, inherent    | ratio           |            |                |

|           |           | anti-aliasing      |                 |            |                |

|           |           | protection         |                 |            |                |

| Cons      | Low speed | Hysteresis on un-  | No inherent     | Limited    | Low bit        |

|           |           | natural signals    | anti-aliasing   | resolution | resolution     |

|           |           |                    | protection      |            |                |

The table 2.1 summarizes the features of the presented architectures.

Table 2.1: ADC state of the art architectures performance comparison [13], [19]-[21].

Having analyzed the different ADC architectures, it is now time to choose a suitable architecture for a LiDAR receiver. The waveform to be sampled is a short pulse with a pulse width between 10 ns and 100 ns, with a repetition rate lower than 10 kHz. A suitable ADC for sampling such a pulse with high fidelity should have:

- 1. A high sampling frequency between 200 Msamples/s to 1 Gsample/s.

- 2. Power consumption lower than 1 W.

- 3. An ENOB of at least 8.

Table 2.1, aids in choosing the ADC based on the features above. Such a high sampling frequency, excludes Slope, Sigma-Delta and SAR architectures. Out of the two fastest architectures, there is a need for low power consumption. As such, the chosen architecture is the pipelined architecture which has the best match in terms of the accuracy, power and speed.

Based on the chosen architecture, we chose to purchase an ADC based on pipelined architecture of the AD9680 ADC, which in turn was found integrated in the AD-FMCDAQ2-EBZ kit. The AD-FMCDAQ2-EBZ Board from Analog Devices provides an ADC that has an on-chip buffer and sample-and-hold circuit designed for low power, small size, and ease of use, which is very practical. The ADC also has an ENOB of 10.4bits when operating at 10 MHz which is greater than the required 8 bits and is able to sample wide bandwidth analog

signals of up to 2 Gsamples/s which the required was a maximum of 1 GHz. To add to that it uses a low jitter clock generator which can run up to 3 Gsamples/s and a reference design compatible with our FPGA, a ZC706 evaluation board.

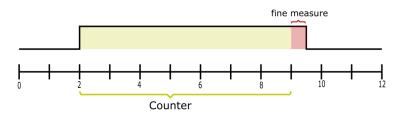

#### 2.3 TDC Architectures

TDCs precisely measure the time intervals between two events, popularly known as start and stop, and have applications in a large number of time measurement systems and subsequently have a variety of industrial and research applications. They are widely used in digital storage oscilloscopes, logic analyzers and high-energy particle physics experiments [22]. The simplest form of a TDC is a digital counter. However, to achieve a high resolution TDC, one needs to use a very high frequency counter and this is not energy efficient. The resolution of counterbased TDCs can be improved significantly by resolving the counter residual error with a high resolution fine TDC based on gate delay [23].

This section provides an overview of some important existing architectures of TDCs, focusing on its principle of operation and emphasizing suitability for FPGA implementation. The following architectures with its respective pros and cons are discussed:

- 1. Time-to-Amplitude Converter.

- 2. Pulse Shrinking.

- 3. Tapped Delay Line.

- 4. Vernier Delay Line.

- 5. Phased Clocks.

- 6. Gated Ring Oscillator.

#### 2.3.1 Time-to-Amplitude Converter (TAC)

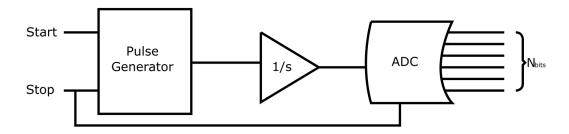

The first approach at measuring ToF was quantizing a signal into a digital word. This can be seen in the figure 2.10.

Figure 2.10: Single-Slope Analog-To-Time-Interpolation converter reproduced from [24].

As with many TDCs, it has a start and stop command, in this case, triggering the commands, start and stop, respectively, define the width of the pulse of the Pulse Generator, in this architecture the start command triggers a pulse to stay at a logical 1, or a constant and positive voltage that is then introduced into a integrator.

Figure 2.11: Single-Slope Analog-To-Time-Interpolation converter graphical illustration.

The integrator behaviour can be seen in the figure 2.11. Once the **stop** signal is triggered, the value at the output of the integrator, is an analog signal, which is introduced into an ADC and is then converted into a word which can be mapped into a value in time[24]. The number of bits at the output of the ADC will dictate the maximum value of time that can be measured.

$$DR = 2^N \cdot T_{LSB} \tag{2.3}$$

Where DR is the Dynamic Range of the ADC converter and  $T_{LSB}$  is the time it takes the Least-Significant-Bit to transition from a logical 0 to 1.

#### 2.3.1.1 Pros and Cons

This architecture is easy to understand and very intuitive, however, the reason why it is so rarely used nowadays is because the final system resolution is defined by the ADC resolution and the conventional usage of the ADC. All blocks should have a linear response and the integrator itself is very dependent on its implementation. Finally, the presence of the ADC makes this architecture unsuitable for the FPGA implementation.

#### 2.3.2 Pulse Shrinking

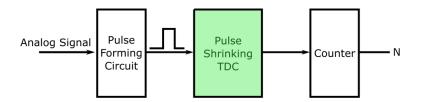

Figure 2.12: TDC common architectural block diagram for Pulse Shrinking adapted from [25].

Figure 2.13: Pulse Shrinking TDC reference architecture adapted from [25].

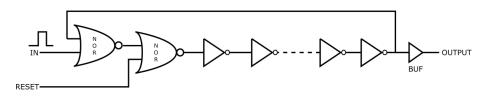

Pulse shrinking architectures are very straightforward, as the name implies, it consist in, given an input signal, repeatedly shrink the input pulse until it ceases to exist.

To shrink the pulse, the input signal must propagate through a delay line which is set by a consecutive number of inverters, ideally with the same width and an even number of NOT gates as seen in figure 2.13. If all inverters maintain the same size, the pulse would maintain its duration and because it has a closed loop, these architectures exhibit a ring oscillator behavior where the number of NOT gates determine the oscillation frequency. For this circular behavior, the signal is fed back into a NOR Gate as seen in figure 2.13. Knowing that for each loop that occurs, the pulse is shrunk by a set amount and that the counter is incremented in each loop, set by **OUTPUT** signal, figure 2.13, to the counter block [25]. The relation between the value of the counter, in other words, the number of loops that occur times the shrinking factor tell us the length of the input pulse.

#### 2.3.2.1 Pros and Cons

This architecture offers great resolutions and low power consumption. The disadvantage of this architecture is that as it is not possible to create custom cells and hard control the shrinking time in an FPGA. Nevertheless, the pulse shrinking delay line can be implemented in FPGA subjected to limitations [25], [26].

# 2.3.3 Tapped Delay Line

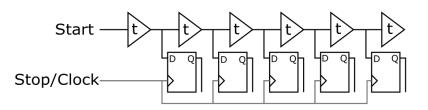

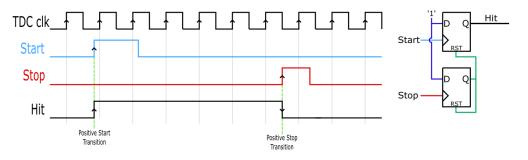

Figure 2.14: Tapped Delay Line.

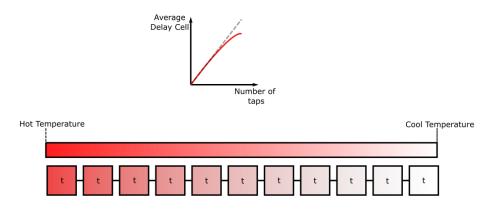

Tapped Delay Line (TDL) architectures are very popular due to their simplicity in implementation, the idea behind the TDLs is to use the intrinsic propagation delay of a basic element, also known as a digital cell to be able to make fine measurements [27], [28]. As shown in figure 2.14, we can see that when a **start** signal is set, it starts to propagate through the delay line, the idea is to delay the signal through these taps. In which each tap delays a signal by the delay introduced from its implementation. The **stop** or the **clock** signal is set so that at each rising edge of the clock or when the **stop** signal is triggered to store a "photo" of the state of the delay line, making it possible to infer at which position the signal stopped. It is important to known that this architecture is easily affected by Process-Voltage-Temperature (PVT) conditions, this means that the bigger the delay line, the less linear it is. This can be seen in the figure 2.15.

Figure 2.15: Tapped Delay Line temperature effect of average delay per digital cell.

The idea behind figure 2.15 is that if every delay cell suffered the same variation, that would mean that the average delay cell would increase or decrease linearly, however, because temperature in many cases does not affect the delay line in a uniform manner, the TDL tends to deteriorate in linearity, thus leading to a transfer curve that differs from the desired linear behaviour. To minimize effects which are propagated through the delay chain, it is desirable to have a delay chain as short as possible.

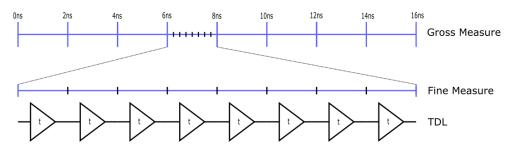

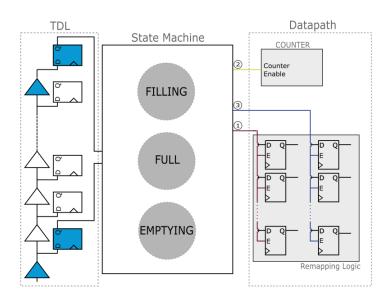

Like the other mentioned architectures, all of them have a problem with dynamic range and in this particular case, there is a limit to how many digital cells can be present in a limited area, and second, due to PVT conditions, it is not recommend to have a large number of digital cells. The TDL is typically seen coupled with a counter, known as a coarse counter which deals with big jumps in time and the TDL deals with the fine measurements. This type of schemes can be seen in the figure 2.16.

Figure 2.16: Coarse counter presence for increasing the dynamic range of the TDL.

#### 2.3.3.1 Pros and Cons

The advantage of this architecture is that it is possible to develop a fully digital TDC at the cost of the FPGA resources in which digital cell chains are always accompanied by their following register chains in a modern FPGA fabric, which is convenient for the software compiler to automatically generate the TDL. The algorithm is relatively simple and it has low power consumption [29]. However, it is prone to glitches, easily affected by bubbles<sup>1</sup> and has metastability problems as the latching input might transition exactly when being captured, violating setup/hold constraints [30]. Another disadvantage of this architecture is the fact that it is limited by the technology itself and the most significant limitation of these architectures is the difficulty to predict the placement and routing delays as well as the time delay of the logic gates itself. The consequence of this inevitable hardware restriction is a non-stable resolution of the designed TDC [31].

# 2.3.4 Vernier Delay Line

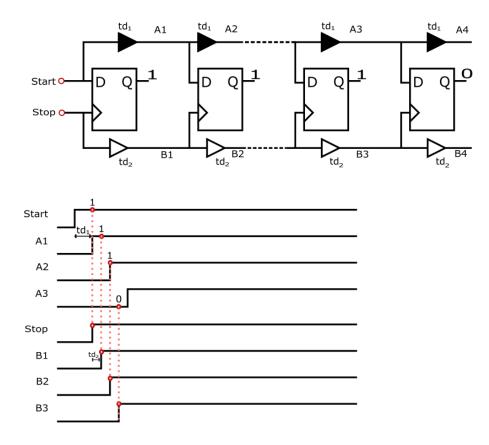

This architecture was proposed to remove the limitation of the cell delay being limited by technology in the TDL.

Figure 2.17: Vernier Delay Line concept reproduced from [24].

It's basic setup and principle of operation can be seen in the figure 2.17. The proposed architecture consist of 2 parallel delay lines, in which each delay element that belongs to the start line must be close to and higher than the delay of the elements of the stop line. This means that when the start sets off and starts propagating through its delay line and after some time, the **stop** signal is triggered. When the stop signal is triggered, it must be able to catch up to **start** signal, in other words, the **stop** signal must propagate faster than the start signal.

<sup>&</sup>lt;sup>1</sup>For more information about bubbles, please see section 2.3.

The measurement is done based of the difference between the **start** and **stop** signal, this means that there is direct relationship between how far into the delay line it took the **stop** signal to catch up to the start signal.

# 2.3.4.1 Pros and Cons

High resolution can be achieved and the delay mismatch is low due to same delay elements used as delay cells. Regarding FPGA implementations, the Vernier Delay Line (VDL) architecture is usually implemented using a dual ring oscillator schemes, paired with a phased detector [32]. However, implementation on FPGAs is complex due to creating the delay elements in an FPGA making it much more complex than the TDL.

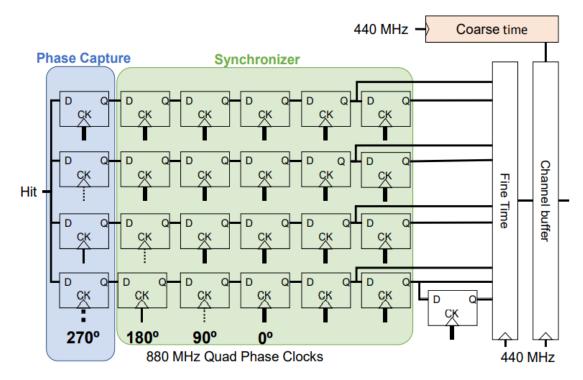

# 2.3.5 Phased Clocks

If the resolution demands are not very high, then the phased clocked architecture is typically used to reduce resource usage. The architecture can be seen in the figure 2.18.

Figure 2.18: Phased Clocks architecture reproduced from [33].

The basic structure of a phased clock architecture is that uses multiple phases as bins to sample the hit signal which can be generated via pulse generator as shown in figure 2.10 with a start and stop command. The input signal is divided in four parts and detected by the D-type flip-flops based on four different clock phases. The locations of the four D-type flip-flops are constrained to control the difference between the divided signal paths. The vertical double lines, thick lines, double dashed lines, and dashed thick line correspond to the clock phases 0, 90, 180, and 270, respectively. The outputs from the four D-type flip-flops are aligned step by step by the chains of additional D-type flip-flops [34]. The fine time counter extracts a three-bit time count from the pattern of the outputs from the chains. The fine time count is combined with the data from a coarse time counter to output a reasonable measurement. Unlike the TDL, the delay is not generated by the intrinsic cell propagation time but instead is given by the phase difference between the clocks used. The higher the number of clock phases, the higher will the resolution be [33].

# 2.3.5.1 Pros and Cons

This architecture poses lots of problems with high frequencies and routing skew. On the other hand, an advantage of this architecture is its simplicity. Another advantage of this architecture is that for FPGAs this is a great implementation as there are multiple ways of generating phased clocks such as using Phase Locked Loop (PLL), Delay Locked Loop (DLL) or even delay lines for phase shifting. This architecture is also PVT insensitive in comparison to other architectures [35].

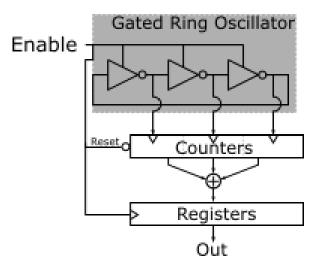

# 2.3.6 Gated Ring Oscillator

Figure 2.19: GRO architecture reproduced from [36].

This architecture operates only when the **Enable** signal is high level and stops when this signal is at low level. The outputs of the Gated Ring Oscillator (GRO) are used as the clocks which drives the counter [37]. One important note, the GRO topology is different from a traditional ring oscillator, such as the Pulse Shrinking architecture by its property to freeze between two consecutive time measurements. If instead of freezing, the system is reset between measurements, there is no possibility to use the previous state to improve the resolution by analyzing the quantization error.

#### 2.3.6.1 Pros and Cons

The benefit from the gating technique, especially with successive measurements, is the increased effective time resolution which cannot be achieved for a simple measurement [38]. However, the main issue is to initialize and maintain a well-defined oscillation through gating operation, since the ring freezes and starts from the previous state without reset [39]. Implementation in an FPGA would be very complex.

# 2.3.7 Summary

| Туре                    | Advantages                                                                                                                                                                                                                                                                                            | Disadvantages                                                                                                                                                                                                                                      | FPGA<br>Implementation |

|-------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| TDL                     | Clock is not required. High<br>resolution can be achieved<br>and has a simple design.<br>Low resource usage. Simple<br>to calibrate.                                                                                                                                                                  | Needs very high frequencies<br>for lower number of delay<br>cells for better performance.<br>Needs calibration.                                                                                                                                    | Simple                 |

| VDL                     | Delay mismatch is low due<br>to same delay elements used<br>as delay cells. High Resolu-<br>tion can be achieved. Clock<br>is not necessarily required.<br>These lines have higher com-<br>plexity but are able to offer<br>performance levels close to<br>the ones achieved by tapped<br>delay lines | Component variant delay<br>due to many buffers in one<br>delay line. Higher complex-<br>ity when compared to the<br>TDL. Requires a minimum<br>of 2 TDLs on FPGA. Hard<br>to calibrate.                                                            | Challenging            |

| GRO                     | Simple and delivers high resolution.                                                                                                                                                                                                                                                                  | High area usage. When<br>propagating a pulse along a<br>chain of buffers configured as<br>a ring, due to mismatch on<br>the cells' rise and fall times,<br>a pulse shrinking/stretching<br>effect can occur leading to<br>the cease of the signal. | Complex                |

| Pulse<br>Shrink-<br>ing | Offers a decent resolution<br>although higher resolutions<br>can be achieved                                                                                                                                                                                                                          | The shrinking factor can-<br>not be fully controlled in<br>an FPGA. Resolution still<br>falls flat against the TDL<br>when implemented in FPGA<br>and the extra complexity in-<br>volved to compete with the<br>TDL is not justified.              | Complex                |

| TAC                     | Simplicity.                                                                                                                                                                                                                                                                                           | Requires the presence of an ADC. Weak linearity.                                                                                                                                                                                                   | No                     |

| Phased<br>clocks        | Best linearity and very low<br>hardware resource utiliza-<br>tion. Good for low resolu-<br>tion applications and PVT<br>insensitivity. No calibration.                                                                                                                                                | Sensitive to routing skew<br>and very unstable at high<br>frequencies.                                                                                                                                                                             | Simple                 |

Table 2.2: TDC State of the Art architectures summary [24], [40].

Table 2.2 summarizes each one of the architectures advantages and disadvantages. The TDL-based TDC is the simplest to understand and possibly the least complex to implement

in an FPGA, turning it into an attractive option. Another reason to consider the TDL is the significant number of publications directly related to the TDL, allowing for a more mature architecture.

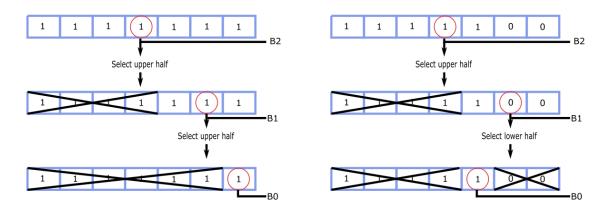

# 2.4 Encoding Logic for Thermometer Code

TDC architectures typically offer their measurement as a word known as a thermometer code which must be converted into a binary code. These thermometer codes were mainly seen in flash type ADC where the output was digital and seen as a sequence of 1s and 0s. This sequence known as a thermometer code, is an entropy coding of a sequence of 1s followed by a 0 or vice-versa which depending on the state of the chain can indicate position of the pulse.

| Decimal | Thermometer | Binary Code | Binary Code |

|---------|-------------|-------------|-------------|

| Number  | Code        | for ones    | for zeros   |

| 0       | 0000000     | 000         | 111         |

| 1       | 0000001     | 001         | 110         |

| 2       | 0000011     | 010         | 101         |

| 3       | 0000111     | 011         | 100         |

| 4       | 0001111     | 100         | 011         |

| 5       | 0011111     | 101         | 010         |

| 6       | 0111111     | 110         | 001         |

| 7       | 1111111     | 111         | 000         |

Table. 2.3 is representation of the conversion of the thermometer codes to binary codes to figure out the number of ones that are present.

Table 2.3:

Thermometer encoding.

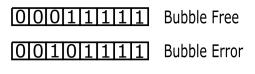

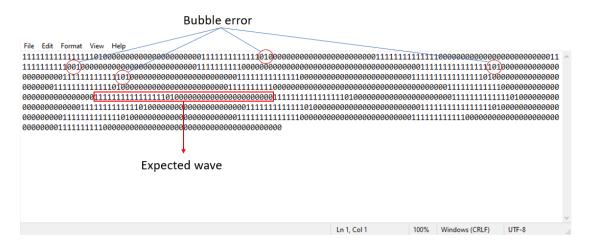

An appropriate definition for bubble errors is when there is one or more invalid bits in a thermometer code then it is termed as bubble error and the thermometer codes depending on the FPGA design suffer from bubble errors. For example the binary word 111110000 may turn into a 110010000. We can see this effect in the figure 2.20.

Figure 2.20: Bubble effect.

The main cause are due to uneven propagation delays in the design or uncertainty introduced in the sampling moment due to meta-stability. Now, choosing the proper design for the encoder is crucial to minimize the resulting error with the minimum delay possible, this means the encoder must be "bubble proof" so the encoder should output a reasonable number. As such, the following thermometer encoders are presented along with its pros and cons:

- 1. ROM based thermometer encoder.

- 2. Wallace Tree based encoder.

- 3. Fat Tree based encoder.

- 4. Multiplexer based encoder.

#### 2.4.1 ROM based Thermometer-to-Binary converter

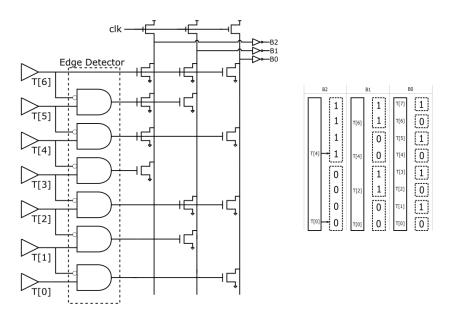

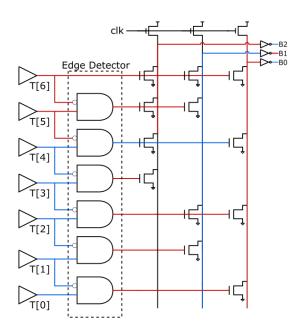

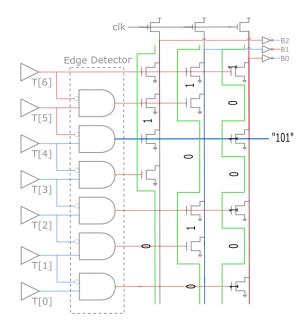

The Read Only Memory (ROM) based technique is one of the first techniques implemented in thermometer encoding, also very popular to this day and was initially adopted for flash ADC classified as Binary-ROM encoder using a parallel layout [41], [42]. The circuitry and scheme layout of this encoder can be seen in the figure 2.21 is used to count the number of ones in a binary representation.

Figure 2.21: ROM based encoder circuitry and scheme adapted from [41].

The layout of figure 2.21 at first looks relatively complex but the reality of the situation is that it is not. To start, the schematics show us a 7 bit thermometer code input and a 3 bit binary code output. Between the input and the output there is an Edge Detector, or what the original authors call the 1 of N block or One-Hot-Encoder[41]. Essentially, the edge detectors detects transitions of a logical 1 to logical **0** of the thermometer code, in which it is always necessary to assume that the code is clean and so there are no bubble errors. The edge detector is composed of multiple AND gates with 1 input non-inverted and the other input inverted. Next is the layout of the transistors, visible on the right side of figure 2.21. Finally, the output has inverters at it is output and their purpose is just to invert whatever value is at the input of the inverter.

Next, the example in the figure 2.22.

Figure 2.22: ROM based encoder example.

The blue lines in the figure 2.22 represent the logical value 1 and the red lines represent the logical value 0, the color of the lines also represent the state of the lines. So, with an input of 1111100, the expected output should be the binary word 101. Looking closely at the figure, B2 and B0 are blue and B1 is red which represent the binary word 101, so as expected, the circuit works and counted correctly the number of 1s. Basically, it stores combination of input variables and for each combination it will generate the output.

Next, looking at the same circuit one last time in the figure 2.23.

Figure 2.23: ROM based encoder example analysis.

We can see that the scheme on the right side of the figure 2.21 and the figure 2.23,

makes the pattern of the transistors very visible, highlighted in green and the blue line from the edge detector passes through the green lines when it is logical values are 1, 0, 1, respectively. However, the output is inverted, so it doesn't make sense for it to be actually, 1, 0, 1, respectively, in reality, looking again at the same figure, these values are acting on the transistor gate inverting the expected logical value, so it is possible to infer that it is actually the inverted values of the expected output and that's why the output is inverted.

This method is able to correct at least one bubble error.

To note that it is possible to implement a fully digital Binary-ROM based encoder as mentioned by [41] and seen in the figure 2.24.

Figure 2.24: Full digital ROM based encoder reproduced from [41].

#### 2.4.1.1 Pros and Cons

The advantage of this circuit is its simplicity. However, relation to the other architectures it is slow, power consumption is high in general and grows with increased thermometer codes and increased data speed might turn this technique into a victim of bubble error making it unsuitable for very high frequency applications, to add to this more circuitry is required to fix these bubble errors.

For an FPGA, that positions its logic cells in very specific locations, make it hard for these kind of techniques to be accepted as the probability of uneven propagation delay occurring is much worse than implementation via Very Large-Scale Integration (VLSI). In other words, for high speed operations, this technique will only degrade in performance and implementation on the FPGA is hardly feasible.

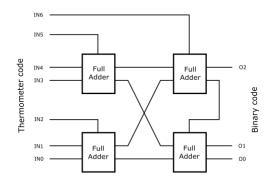

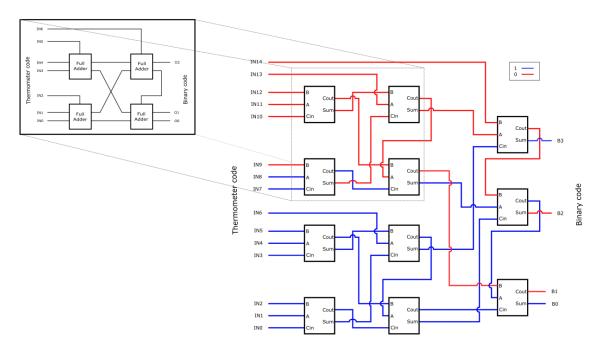

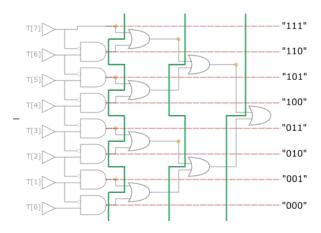

#### 2.4.2 Wallace Tree based Thermometer-to-Binary converter

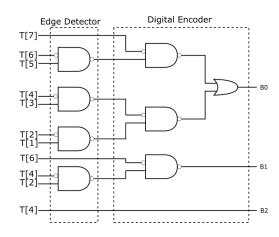

The Wallace Tree encoder is, like the ROM based Encoder, a technique to calculate the number of ones, but instead uses Full Adders as illustrated in the figure 2.25

Figure 2.25: 3 Bit Wallace Tree Encoder.

In the figure 2.26 we can see that its basic cells, the Full Adders are arranged in a specific way to count the number of logical 1s at their input for its final binary output. In this particular example, the blue lines represent the logical value 1 and the red lines represent the logical value 0. For an input 11111111000000 the output is 1001 which represents the decimal value of 9.

Figure 2.26: 4 Bit Wallace Tree encoder example adapted from [43].

The operations of the encoder can be easily pipelined, allowing the thermometer codes to be converted into fine timestamps without introducing dead time. Using this encoder severely reduces the probability of having missed TDC codes since it does not aim at locating the transition point in the thermometer code [42], [44].

# 2.4.2.1 Pros and Cons

The advantage of this circuit is its flexibility and the fact that its topology can be selected according to speed and power. The disadvantage is the fact that relative to the other architectures it has a huge area, high power consumption, it is relatively complex to implement on an FPGA with scalability and has a long critical path [45].

#### 2.4.3 Fat-Tree based Thermometer-to-Binary converter

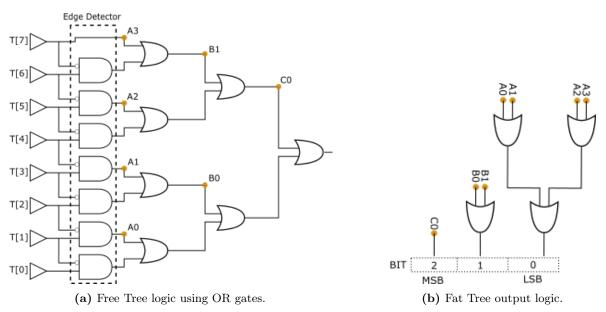

The fat tree shown in figure 2.27 is relatively simple technique where OR Gates are main component. This simplicity allows for direct conversion from the input to the output calculating the number of ones.

Figure 2.27: Fat Tree encoder adapted from [46].

It's behavior is very similar to ROM based encoder where instead of using a representation via transistors, this architecture uses some combinatorial logic to produce an output.

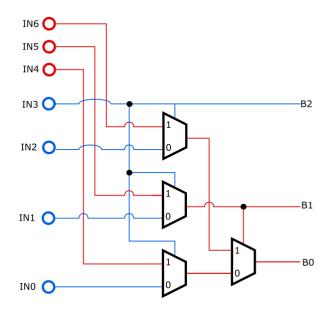

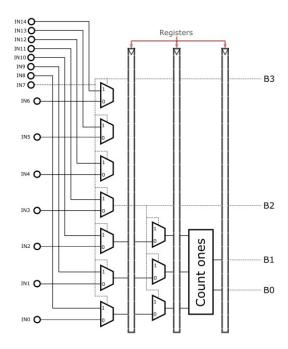

Figure 2.28: Fat Tree logic analysis.