# This electronic thesis or dissertation has been downloaded from Explore Bristol Research, http://research-information.bristol.ac.uk

Author:

Tancock, Scott

The Efficient Design of Time-to-Digital Converters

Access to the thesis is subject to the Creative Commons Attribution - NonCommercial-No Derivatives 4.0 International Public License. A copy of this may be found at https://creativecommons.org/licenses/by-nc-nd/4.0/legalcode This license sets out your rights and the restrictions that apply to your access to the thesis so it is important you read this before proceeding.

Some pages of this thesis may have been removed for copyright restrictions prior to having it been deposited in Explore Bristol Research. However, if you have discovered material within the thesis that you consider to be unlawful e.g. breaches of copyright (either yours or that of a third party) or any other law, including but not limited to those relating to patent, trademark, confidentiality, data protection, obscenity, defamation, libel, then please contact collections-metadata@bristol.ac.uk and include the following information in your message:

- · Bibliographic details for the item, including a URL

- An outline nature of the complaint

Your claim will be investigated and, where appropriate, the item in question will be removed from public view as soon as possible.

# The Efficient Design of Time-to-Digital Converters

$\mathbf{B}\mathbf{y}$

SCOTT TANCOCK

Department of Electrical and Electronic Engineering UNIVERSITY OF BRISTOL

A dissertation submitted to the University of Bristol in accordance with the requirements of the degree of DOCTOR OF PHILOSOPHY in the Faculty of Engineering.

DECEMBER 2021

Word count: 50786

#### ABSTRACT

ime-to-Digital Converters (TDCs) perform the conversion (sampling and quantisation) of time periods into digital (binary) numbers and are vital for Time-of-Flight (ToF) systems such as RADAR, LiDAR, SONAR and Ultrasonics. They are also vital in frequency-locking applications such as All-Digital Phase-Locked Loops (ADPLLs) and Delay-Locked Loops (DLLs), quantum applications such as Quantum Key Distribution (QKD), Single-Photon LiDAR / Single-Photon Time-of-Flight (SPToF) and coincidence counting.

The literature on TDCs is fragmented, with research clustering around specific applications and little cross-pollination of ideas between them. Therefore, I reviewed all these areas for novel TDC architectures and found several new designs including algorithmic, successive approximation and wave union TDCs. Most designs were based on Application Specific Integrated Circuits (ASICs) due to the hardware flexibility, with the rest on Field Programmable Gate Arrays (FPGAs), all of which have been verified.

One of the most promising hardware architectures for TDCs are FPGAs as they are of a lower cost than ASICs. I have presented the first TDC implementation on the FPGA's DSP blocks and resolved the extreme non-linearity in the DSP blocks with multisampling techniques to produce an effective delay line with performance comparable to carry chains (13.60 ps single-shot precision). DSP delay lines avoid the use of general-purpose fabric, allowing larger quantities of channels or more applications to be integrated on to a single device.

The long bubbles caused by applying the wave union multisampling technique were unable to be corrected by existing bubble correctors. Therefore, a new hardware bubble corrector, which operates at line rate with zero dead time (130 MHz, 144 bits/cycle on my TDCs), was designed and tested.

#### ACKNOWLEDGEMENTS

could not have completed this PhD project without the help of many individuals and organisations, and so I would like to thank them for their support. If any of these people were missing, this project would not have succeeded as it did.

Firstly, to the Engineering and Physical Sciences Research Council (EPSRC) and the University of Bristol for providing the funding, resources, and stipend to complete this project. It's hard to perform good research without suitable equipment, spaces, and daily necessities, so this project could not have been completed without them.

Second, to my supervisor, Professor Naim Dahnoun. He has been instrumental in pushing this PhD forward, improving the quality of my written work and communication, discussing problem points and issues with my designs, and helping me focus on the bigger picture. Without him, this PhD would never have reached completion and my papers would likely not have been accepted for publication.

Third, to my co-supervisor, Professor John Rarity. He has been very helpful in providing equipment, funds, opportunities to network with other researchers and perspective on my topic and its applications. It is because of him that my research has been able to create an impact on other engineering and scientific fields rather than being purely confined to the realms of the theoretical.

Fourth, to my interim assessor Dr Krishna Coimbatore Balram for his guidance on progressing through the PhD. His input during our yearly reviews was indispensable for keeping the PhD focused and on-track, having a plan for progression and submission and understanding the PhD assessment process.

Fifth, to Dr. Jose Nunez-Yanez for his assistance related to FPGA implementation, routing, and toolchains. The architectures of FPGAs and tools to configure them can often be outright cryptic, and his deep knowledge on the matter really helped me move on with my research rather than scratching my head at the tools.

Sixth, to Dr. Dinesh Pamunuwa for his assistance related to ASIC design and manufacture. A large quantity of TDC literature is inherently intertwined with ASIC design and manufacture, a lot of which would have been very difficult to understand if not for Dinesh's expertise on VLSI design. He was a great resource for understanding the more complex designs and physical effects encountered in TDC papers.

Seventh, to my co-researcher Ekin Arabul for the time spent discussing TDC designs and implementation aspects. TDC papers, word limited as they are, often do not explore the tiny details and common errors in implementation, so having another researcher whom I could discuss these matters with was invaluable. I hope he was able to benefit as much from my presence as I did from his.

Eighth, to Rich Walker and the staff in the engineering workshop who helped me bring

physical aspects of my designs to reality, including PCBs, protective covers, and cabling. These matters can seem minor in the heat of the moment but can often be the difference between a reliable experimental setup and one that only works when the planets are aligned.

Ninth, to the professional services and technical services staff in the University who helped with administrative and organisational tasks such as booking flights and conferences, organising desk allocations and equipment procurement. Again, these can seem like minor matters individually, but without them no research could be done.

Tenth, to the various researchers I met, talked with, and listened to at conferences, as well as the reviewers of the papers I have submitted for publication. Your input and perspective inspired me to question my own work more deeply, to be more rigorous in my assertions, and to examine the problem from angles I would never have considered. I could not have become a competent researcher without the guidance of the many people I interacted with in the publication process and while presenting at conferences.

Finally, I would like to thank the developers of the various open-source tools I use daily to turn my ideas into reality. From large projects such as the Linux Operating System, Git, LATEX, Golang and the GNU Project, to small ones such as Sublime Text, Inkscape and Krita, these tools are provided for free by developers with spare time and generosity without any remuneration, so I would like to thank them for making these excellent tools available to the community.

In addition to those who helped me in a professional capacity, I would like to thank those who helped me in a personal capacity.

I would like to thank my parents for their emotional support, providing accommodation and general tolerance of my unconventional work schedule. Despite the stresses of the PhD and the many things in their own lives, they have taken the time to help me in more ways than I could ever imagine.

Also, I would like to thank my brothers for their emotional support and assistance with proofreading and critical opinions. They have been incredibly helpful in ensuring that the text I've written and diagrams I've drawn are of a suitable quality, easy to understand and error-free.

Finally, my friends inside and outside the University, including Jamie Marsden, Alex Stanoev, Elliott Worsey, Roget Kou, Charles Khoury, Abdu Elturki, Alex Gregory and Ed Nutting. As well as their emotional support and willingness to let me bounce ideas off them, they have helped me to take a step back from my work and unwind when I've needed to, helping me avoid burnout for the better part of five years.

Without these people, this project would not have been possible, and so they have my heartfelt gratitude for everything they have done for me over the past four and a half years. I hope that one day I can return the favour.

### **AUTHOR'S DECLARATION**

declare that the work in this dissertation was carried out in accordance with the requirements of the University's Regulations and Code of Practice for Research Degree Programmes and that it has not been submitted for any other academic award. Except where indicated by specific reference in the text, the work is the candidate's own work. Work done in collaboration with, or with the assistance of, others, is indicated as such. Any views expressed in the dissertation are those of the author.

| SIGNED: | $DATE \cdot$ |

|---------|--------------|

| 9191120 | 2111 2       |

|    |       |           | ]                                                      | Page |

|----|-------|-----------|--------------------------------------------------------|------|

| Li | st of | Tables    |                                                        | xiii |

| Li | st of | Figures   |                                                        | xv   |

| 1  | Intr  | oduction  | n                                                      | 1    |

|    | 1.1   | Researc   | h Motive                                               | . 1  |

|    | 1.2   | Aims an   | nd Goals                                               | . 2  |

|    | 1.3   | List of C | Contributions                                          | . 3  |

|    |       | 1.3.1     | Comparison between the Literature and My Contributions | . 7  |

|    | 1.4   | Structur  | re of this Thesis                                      | . 9  |

|    | 1.5   | Applicat  | tions                                                  | . 9  |

|    |       | 1.5.1     | Coincidence Counting                                   | . 11 |

|    |       | 1.5.2     | Spectrometry                                           | . 11 |

|    |       | 1.5.3 I   | Rangefinding                                           | . 12 |

|    |       | 1.5.4 I   | Frequency Locking                                      | . 14 |

|    |       | 1.5.5 I   | Health and Monitoring                                  | . 15 |

|    |       | 1.5.6     | Commercial Availability                                | . 17 |

|    | 1.6   | Perform   | ance and Cost                                          | . 18 |

|    |       | 1.6.1 I   | Least Significant Bit (LSB)                            | . 18 |

|    |       | 1.6.2 I   | Range                                                  | . 18 |

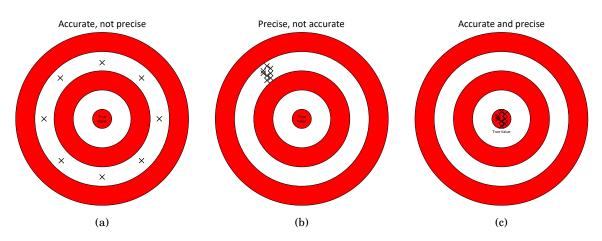

|    |       | 1.6.3 A   | Accuracy                                               | . 20 |

|    |       | 161 I     | Progision                                              | 25   |

|   |     | 1.6.5   | Resolution                    | 26 |

|---|-----|---------|-------------------------------|----|

|   |     | 1.6.6   | Linearity                     | 28 |

|   |     | 1.6.7   | Quantity of Channels          | 30 |

|   |     | 1.6.8   | Repetition Rate               | 30 |

|   |     | 1.6.9   | Power                         | 31 |

|   |     | 1.6.10  | Area                          | 33 |

|   |     | 1.6.11  | Time-to-Market and Technology | 33 |

| 2 | Har | dware   |                               | 39 |

|   | 2.1 | Abstrac | t                             | 39 |

|   | 2.2 | Hardwa  | are Types                     | 45 |

|   |     | 2.2.1   | CPUs                          | 45 |

|   |     | 2.2.2   | GPUs                          | 45 |

|   |     | 2.2.3   | DSPs                          | 46 |

|   |     | 2.2.4   | MCUs                          | 48 |

|   |     | 2.2.5   | Analog Systems                | 49 |

|   |     | 2.2.6   | Discrete Logic                | 50 |

|   |     | 2.2.7   | FPGAs                         | 51 |

|   |     | 2.2.8   | ASICs                         | 52 |

|   | 2.3 | FPGAs   | in Detail                     | 53 |

|   |     | 2.3.1   | FPGA Overview                 | 53 |

|   |     | 2.3.2   | FPGA Building Blocks          | 54 |

|   |     | 2.3.3   | FPGA Architecture             | 60 |

|   | 2.4 | Conclus | sion                          | 67 |

| 3 | Rev | iew     |                               | 69 |

|   | 3.1 | Abstrac | t                             | 69 |

|   | 3.2 | Introdu | ction                         | 69 |

|   | 3.3 | TDC Ar  | chitectures                   | 71 |

|   |     | 3.3.1   | Counter TDC                   | 71 |

|   |     | 3.3.2 Delay Line TDC                      |

|---|-----|-------------------------------------------|

|   |     | 3.3.3 Vernier Delay Line                  |

|   |     | 3.3.4 Pulse-shrinking TDC                 |

|   |     | 3.3.5 Local Passive Interpolation         |

|   |     | 3.3.6 Stochastic TDC                      |

|   |     | 3.3.7 Successive Approximation TDC        |

|   |     | 3.3.8 Algorithmic TDC                     |

|   |     | 3.3.9 Gated Ring Oscillator               |

|   |     | 3.3.10 Stochastic Phase-Interpolation TDC |

|   |     | 3.3.11 Wave Union Launchers               |

|   |     | 3.3.12 TAC-ADC                            |

|   |     | 3.3.13 SERDES TDC                         |

|   |     | 3.3.14 Time Amplification                 |

|   | 3.4 | Performance                               |

|   | 3.5 | Architecture Comparison                   |

|   | 3.6 | Conclusions and Recommendations           |

|   |     |                                           |

| 4 | DSP | Blocks as Delay Generators 11             |

|   | 4.1 | Abstract                                  |

|   | 4.2 | Introduction                              |

|   |     | 1.2.1 Initial Investigation               |

|   |     | 1.2.2 Solving the Non-Linearity           |

|   |     | 1.2.3 Temperature Characterisation        |

|   |     | 1.2.4 Delay Lines                         |

|   | 4.3 | nitial Investigation                      |

|   |     | 4.3.1 DSP48A1 Architecture                |

|   |     | 4.3.2 System Design                       |

|   |     | 4.3.3 Test Methodology                    |

|   |     | 4.3.4 Results                             |

|   |                 | 4.3.5                                                                                    | Code Density Testing                                                                                                                                                               | 129                                           |

|---|-----------------|------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|   |                 | 4.3.6                                                                                    | Discussion                                                                                                                                                                         | 136                                           |

|   |                 | 4.3.7                                                                                    | Conclusion                                                                                                                                                                         | 138                                           |

|   | 4.4             | Solvin                                                                                   | g the non-linearity                                                                                                                                                                | 139                                           |

|   |                 | 4.4.1                                                                                    | System Design                                                                                                                                                                      | 139                                           |

|   |                 | 4.4.2                                                                                    | Methodology                                                                                                                                                                        | 146                                           |

|   |                 | 4.4.3                                                                                    | Results                                                                                                                                                                            | 147                                           |

|   |                 | 4.4.4                                                                                    | Discussion                                                                                                                                                                         | 153                                           |

|   |                 | 4.4.5                                                                                    | Conclusion                                                                                                                                                                         | 157                                           |

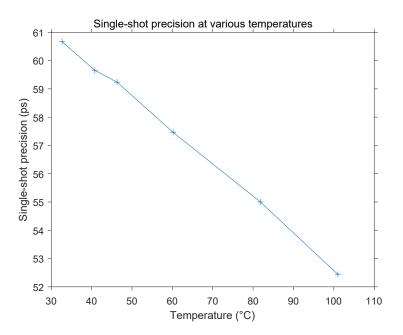

|   | 4.5             | Tempe                                                                                    | erature Characterisation                                                                                                                                                           | 157                                           |

|   |                 | 4.5.1                                                                                    | System Design and Methodology                                                                                                                                                      | 157                                           |

|   |                 | 4.5.2                                                                                    | Results                                                                                                                                                                            | 159                                           |

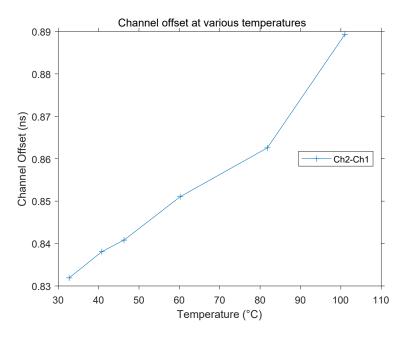

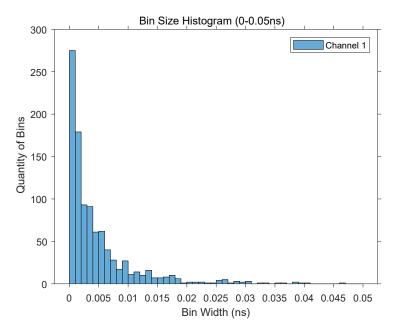

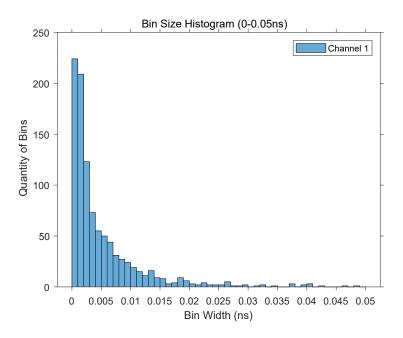

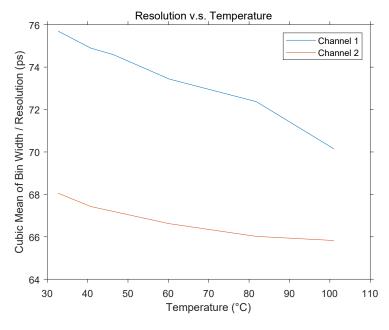

|   |                 | 4.5.3                                                                                    | Discussion                                                                                                                                                                         | 166                                           |

|   |                 | 4.5.4                                                                                    | Conclusion                                                                                                                                                                         | 167                                           |

|   |                 |                                                                                          |                                                                                                                                                                                    |                                               |

|   | 4.6             | Conclu                                                                                   | asion                                                                                                                                                                              | 168                                           |

| 5 |                 | Conclu <b>tisamp</b>                                                                     |                                                                                                                                                                                    | 168<br><b>169</b>                             |

| 5 |                 | tisamp                                                                                   |                                                                                                                                                                                    | 169                                           |

| 5 | Mul             | <b>tisamp</b><br>Introd                                                                  | oling                                                                                                                                                                              | <b>169</b><br>169                             |

| 5 | <b>Mul</b> 5.1  | <b>tisamp</b><br>Introd<br>DSP b                                                         | oling uction                                                                                                                                                                       | 1 <b>69</b><br>169<br>170                     |

| 5 | Mul 5.1 5.2 5.3 | tisamp<br>Introd<br>DSP b<br>Wave                                                        | oling uction                                                                                                                                                                       | 169<br>169<br>170<br>171                      |

| 5 | Mul 5.1 5.2 5.3 | tisamp<br>Introd<br>DSP b<br>Wave                                                        | oling uction locks Union Methods                                                                                                                                                   | 169<br>169<br>170<br>171                      |

| 5 | Mul 5.1 5.2 5.3 | Introd  DSP b  Wave 1  Combi                                                             | uction                                                                                                                                                                             | 169<br>169<br>170<br>171<br>174<br>176        |

| 5 | Mul 5.1 5.2 5.3 | Introd<br>DSP b<br>Wave 1<br>Combi                                                       | uction uction locks Union Methods nation of the Wave Union Method and DSPs Inverting Configuration                                                                                 | 169<br>169<br>170<br>171<br>174<br>176        |

| 5 | Mul 5.1 5.2 5.3 | Introd DSP b Wave 1 Combi 5.4.1                                                          | uction  locks  Union Methods  nation of the Wave Union Method and DSPs  Inverting Configuration  Non-inverting Configuration                                                       | 169<br>169<br>170<br>171<br>174<br>176<br>178 |

| 5 | Mul 5.1 5.2 5.3 | Introd DSP b Wave 1 Combi 5.4.1 5.4.2 5.4.3                                              | uction locks Union Methods nation of the Wave Union Method and DSPs Inverting Configuration Non-inverting Configuration Propagating Configuration                                  | 169<br>170<br>171<br>174<br>176<br>178<br>179 |

| 5 | Mul 5.1 5.2 5.3 | Introd<br>DSP b<br>Wave 1<br>Combi<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4                   | uction locks Union Methods nation of the Wave Union Method and DSPs Inverting Configuration Non-inverting Configuration Propagating Configuration Configuration variables          | 169 170 171 174 176 178 179 180               |

| 5 | Mul 5.1 5.2 5.3 | Introd<br>DSP b<br>Wave 1<br>Combi<br>5.4.1<br>5.4.2<br>5.4.3<br>5.4.4<br>5.4.5<br>5.4.6 | uction locks Union Methods nation of the Wave Union Method and DSPs Inverting Configuration Non-inverting Configuration Propagating Configuration Configuration variables Decoding | 169 170 171 174 176 178 179 180 182           |

|          | 5.7 | Conclusion                       | 193 |  |  |  |  |

|----------|-----|----------------------------------|-----|--|--|--|--|

| 6        | Bub | bble Correction 19               |     |  |  |  |  |

|          | 6.1 | Abstract                         | 195 |  |  |  |  |

|          | 6.2 | Introduction                     | 195 |  |  |  |  |

|          | 6.3 | Algorithm                        | 198 |  |  |  |  |

|          | 6.4 | Proof of Correctness (Algorithm) | 202 |  |  |  |  |

|          |     | 6.4.1 Bit Rearrangement          | 203 |  |  |  |  |

|          |     | 6.4.2 Iteration                  | 206 |  |  |  |  |

|          | 6.5 | Implementation                   | 208 |  |  |  |  |

|          | 6.6 | In-Situ Results                  | 211 |  |  |  |  |

|          | 6.7 | Limitations and Extensibility    | 212 |  |  |  |  |

|          | 6.8 | Conclusion                       | 213 |  |  |  |  |

| <b>A</b> | N/1 | ti-Chain Vernier TDCs            | 215 |  |  |  |  |

| A        |     |                                  |     |  |  |  |  |

|          |     | Abstract                         |     |  |  |  |  |

|          | A.2 | Introduction                     |     |  |  |  |  |

|          | A.3 | System Design                    |     |  |  |  |  |

|          |     | A.3.1 Overview                   |     |  |  |  |  |

|          |     | A.3.2 PDK                        | 217 |  |  |  |  |

|          |     | A.3.3 Discriminators             | 217 |  |  |  |  |

|          |     | A.3.4 Vernier Elements           | 218 |  |  |  |  |

|          |     | A.3.5 Initial Time Offset        | 219 |  |  |  |  |

|          | A.4 | Test Methodology                 | 222 |  |  |  |  |

|          |     | A.4.1 Testbench                  | 222 |  |  |  |  |

|          |     | A.4.2 Model Parameters           | 222 |  |  |  |  |

|          |     | A.4.3 Typical Mean and Sweeps    | 222 |  |  |  |  |

|          |     | A.4.4 Monte-Carlo Analysis       | 222 |  |  |  |  |

|          | A.5 | Results                          | 223 |  |  |  |  |

|          |     | A 5.1 Typical Mean and Sweeps    | 223 |  |  |  |  |

|              |      | A.5.2 Monte-Carlo               | 224                                           |

|--------------|------|---------------------------------|-----------------------------------------------|

|              | A.6  | Conclusion                      | 225                                           |

| В            | Oth  | er Publications                 | 227                                           |

|              | B.1  | Multi-Channel TDCs              | 227                                           |

|              | B.2  | Machine Vision                  | 227                                           |

|              | B.3  | E-Learning                      | 227                                           |

| $\mathbf{C}$ | Inst | antiation of DSP blocks         | 229                                           |

| •            |      |                                 |                                               |

|              | C.1  | DSP48A1 Blocks in VHDL          | 229                                           |

|              | 0.1  | DSP48A1 Blocks in VHDL          |                                               |

|              | C.2  |                                 | 234                                           |

|              | C.2  | DSP48E1 Blocks in SystemVerilog | 234<br>247                                    |

|              | C.2  | DSP48E1 Blocks in SystemVerilog | <ul><li>234</li><li>247</li><li>247</li></ul> |

# LIST OF TABLES

| TABLE |                                                                     |       |

|-------|---------------------------------------------------------------------|-------|

| 1     | List of contributions.                                              | . 3   |

| 1.2   | Comparison of DSP and carry chain delay lines                       | . 8   |

| 1.3   | Application performance requirements                                | . 10  |

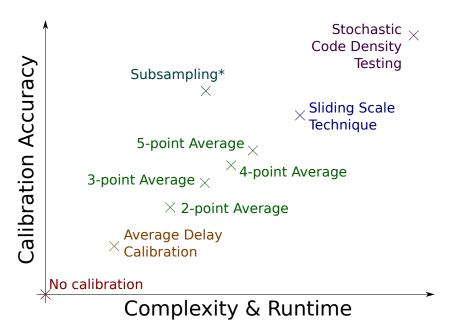

| 1.4   | Comparison of calibration techniques                                | . 24  |

| 1     | Table summarising the pros and cons of different hardware platforms | . 41  |

| 3.1   | Summary of TDC Architectures.                                       | . 71  |

| 3.2   | Performance of the wave union TDCs in [1].                          | . 100 |

| 3.3   | Comparison of TDCs in the current literature                        | . 108 |

| 4.1   | Comparison of DSP and carry chain delay lines                       | . 112 |

| 4.2   | Parameters of CARRY4 and DSP48A1                                    | . 136 |

| 4.3   | Characterisation results at various temperatures                    | . 164 |

| 5.1   | Performance of various TDC implementations. N/A: Not Available      | . 192 |

| 6.1   | Sample corrections                                                  | . 212 |

# LIST OF FIGURES

| Figu | URE Pa                                                                                                   | ge |

|------|----------------------------------------------------------------------------------------------------------|----|

| 1.1  | Context of DSP Delay Lines                                                                               | 7  |

| 1.2  | Context of Wave Union on DSP Delay Lines                                                                 | 8  |

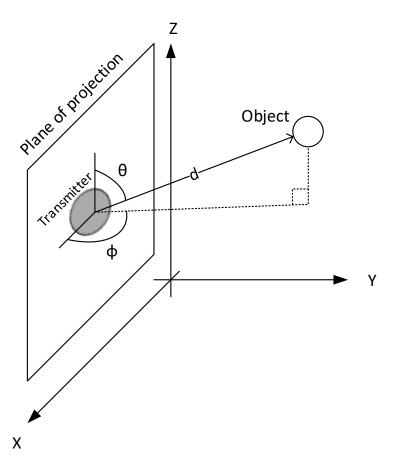

| 1.3  | Visualisation of a Time-of-Flight (ToF) system, showing the cartesian as well as                         |    |

|      | spherical coordinate systems.                                                                            | 13 |

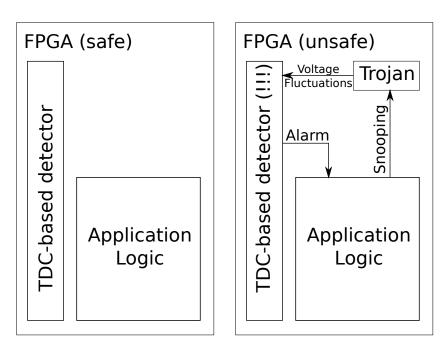

| 1.4  | Application of TDCs to hardware security by Ma et. al. [2]. When a trojan is added to                    |    |

|      | the FPGA device, the TDC-based detector observed changes in voltage and tempera-                         |    |

|      | ture and sounded the alarm                                                                               | 17 |

| 1.5  | Accuracy and Precision                                                                                   | 21 |

| 1.6  | Calibration Effort                                                                                       | 22 |

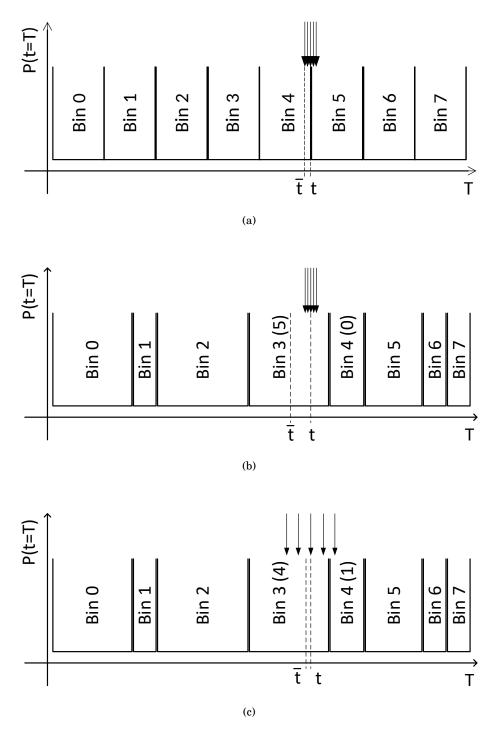

| 1.7  | (a) A TDC with perfectly distributed bins. (b) A TDC with a poor DNL. The DNL will                       |    |

|      | be at its maximum between bins two and three (both above-average size, bin $\equiv$ LSB).                |    |

|      | (c) A demonstration of how averaging and sufficient measurement uncertainty can                          |    |

|      | improve accuracy. The estimated value $\overline{t}$ is closer to the true value $t$ as the distribution |    |

|      | between bins three and four allows us to infer the value of $t$ to a resolution higher                   |    |

|      | than the bin size                                                                                        | 35 |

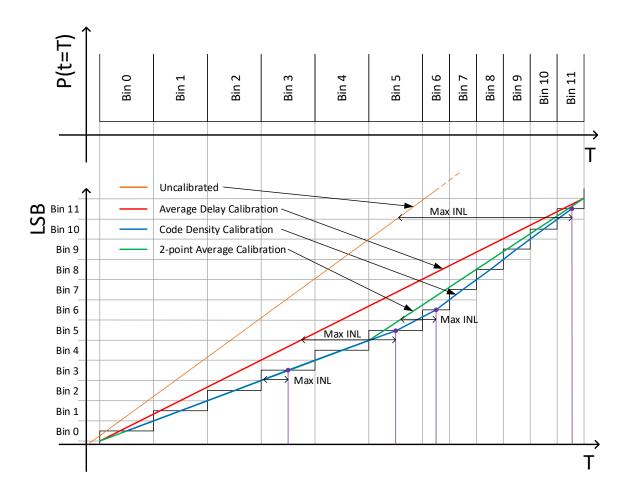

| 1.8  | An example TDC with poor native INL, along with various methods to correct the INL.                      |    |

|      | The maximum INL for each method is shown                                                                 | 36 |

| 1.9  | Power Comparison of DL-TDC usage.                                                                        | 37 |

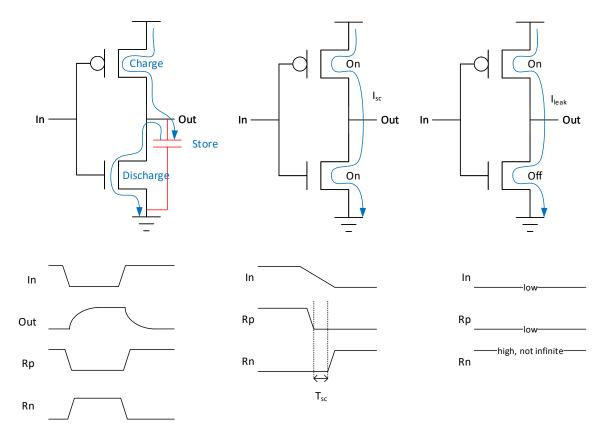

| 1.10 | Demonstration of power consumption with a CMOS inverter (common delay element)                           |    |

|      | as a sample circuit. Left: dynamic power; middle: short-circuit power; right: static power.              | 38 |

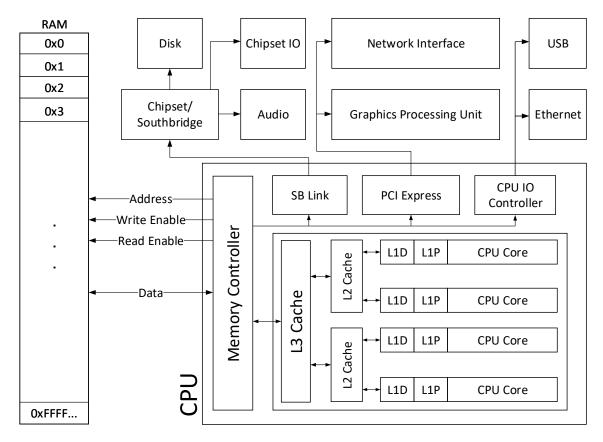

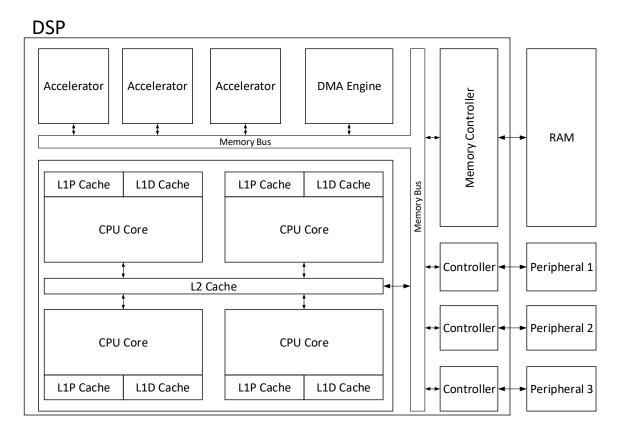

| 2.1  | Common example of a CPU in a system. RAM = Random-Access Memory. L1P = Level                 |    |

|------|----------------------------------------------------------------------------------------------|----|

|      | 1 Program Cache. L1D = Level 1 Data Cache. SB = South Bridge. IO = Input/Output.             |    |

|      | PCI = Peripheral Component Interconnect. USB = Universal Serial Bus                          | 46 |

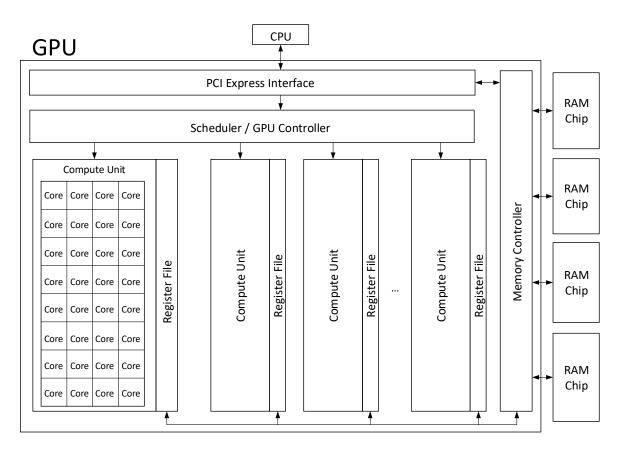

| 2.2  | Internal layout of a GPU                                                                     | 47 |

| 2.3  | Example internal layout of a DSP.                                                            | 49 |

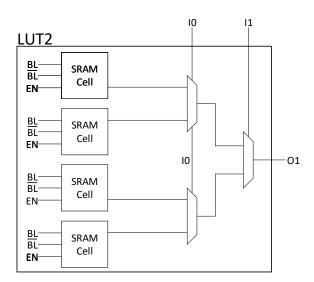

| 2.4  | Implementation of a two-input LUT using multiplexers and SRAM cells. The SRAM                |    |

|      | cells store the truth table, and the multiplexers select the correct element from the        |    |

|      | truth table                                                                                  | 55 |

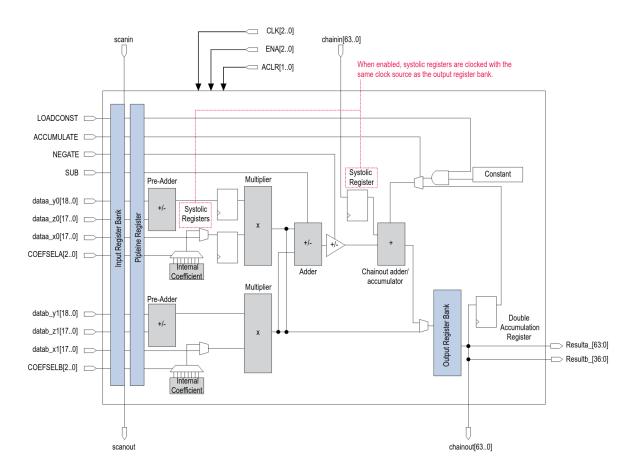

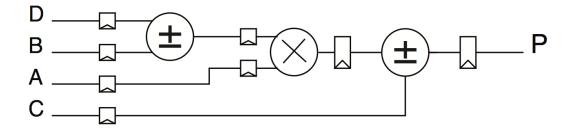

| 2.5  | Architecture of Intel's variable-precision DSP blocks [3]                                    | 58 |

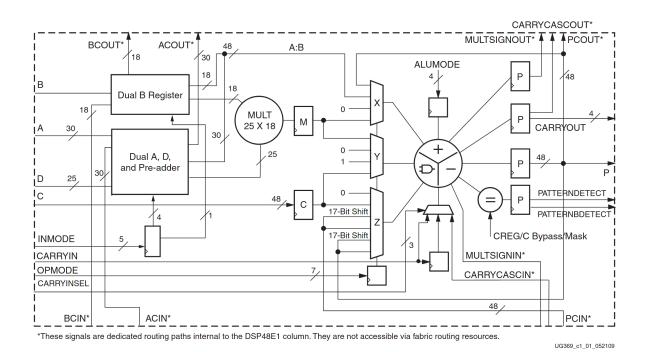

| 2.6  | Simplified architecture of Xilinx's DSP48E1 blocks [4]                                       | 58 |

| 2.7  | Detailed architecture of Xilinx's DSP48E1 blocks [4]                                         | 59 |

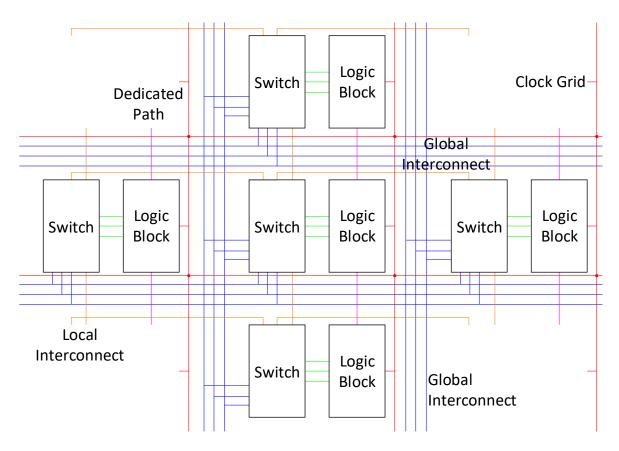

| 2.8  | Routing structure of an FPGA, showing local switch (green), local interconnect (or-          |    |

|      | ange), global interconnect (blue), clock grid (red) and dedicated path (purple) connections. | 61 |

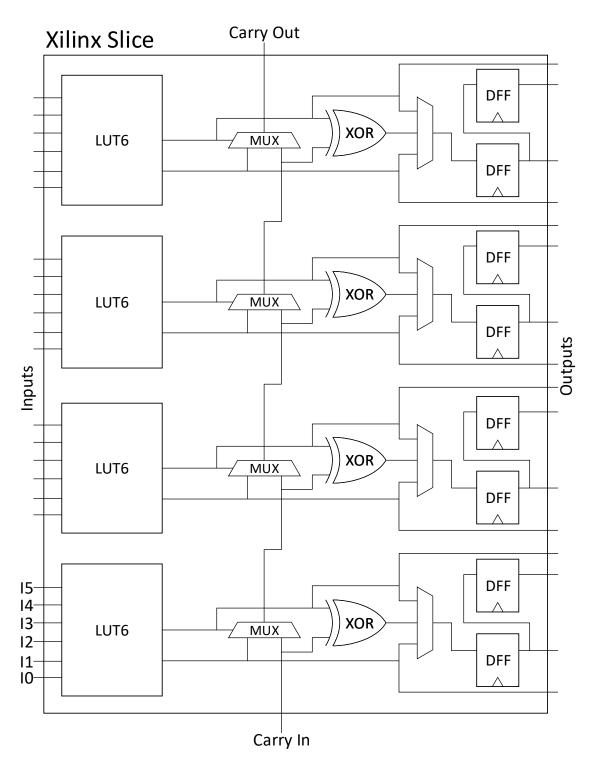

| 2.9  | Architecture of a Xilinx 'slice' (two slices per CLB/logic block).                           | 65 |

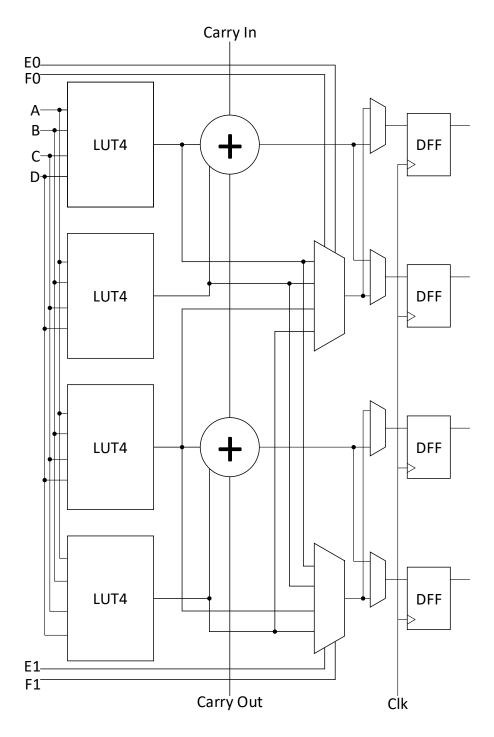

| 2.10 | Architecture of an Intel 'ALM' (10 ALMs per LAB/logic block). Input port names               |    |

|      | truncated (A = dataa, B = datab, E0 = datae0 etc.)                                           | 66 |

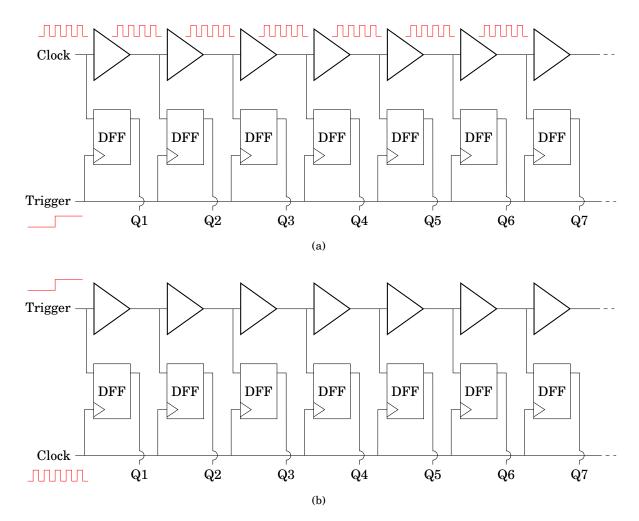

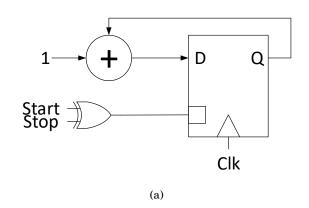

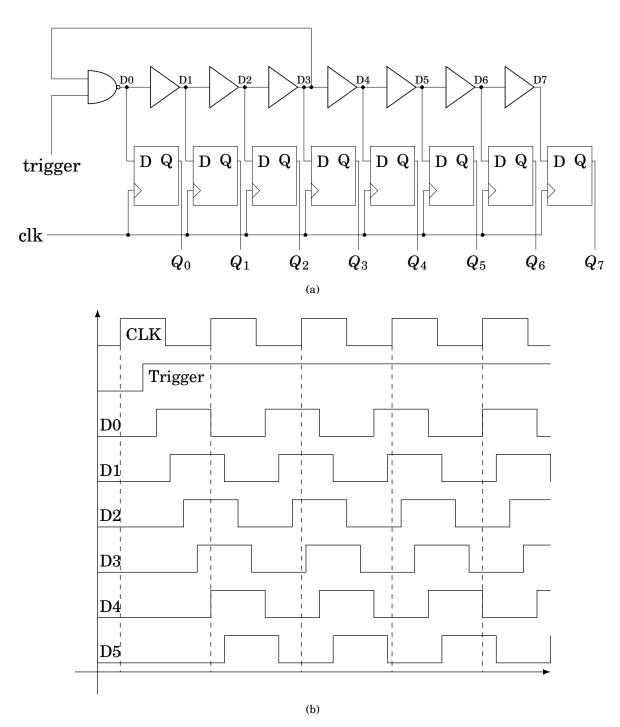

| 3.1  | (a) A counter TDC; (b) A multi-phase clock                                                   | 73 |

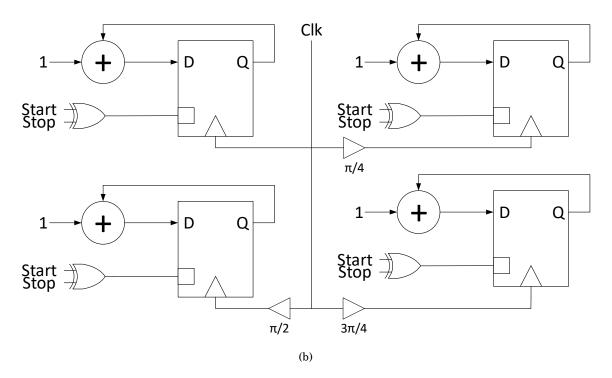

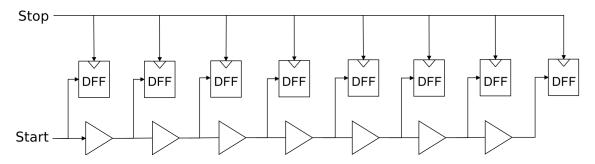

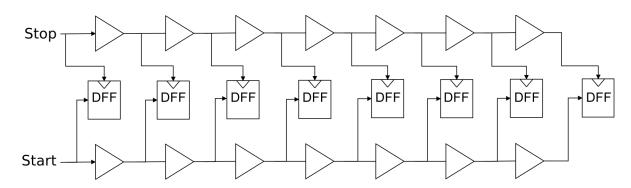

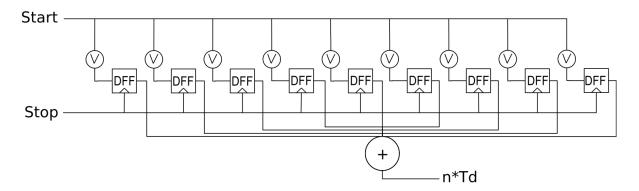

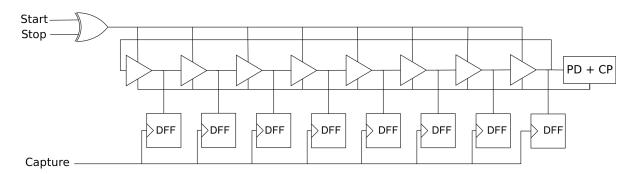

| 3.2  | A delay line. DFF = D-type Flip-Flop.                                                        | 76 |

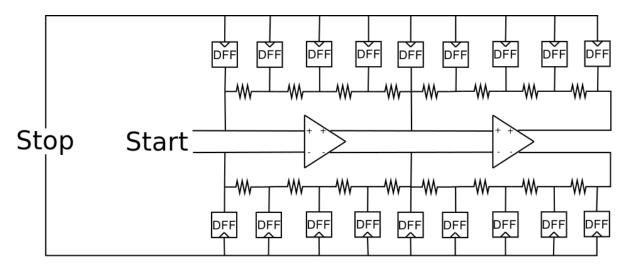

| 3.3  | A Vernier delay line                                                                         | 78 |

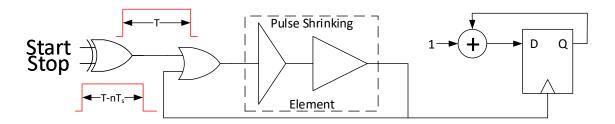

| 3.4  | A pulse shrinking TDC                                                                        | 81 |

| 3.5  | An LPI TDC                                                                                   | 83 |

| 3.6  | A stochastic TDC                                                                             | 85 |

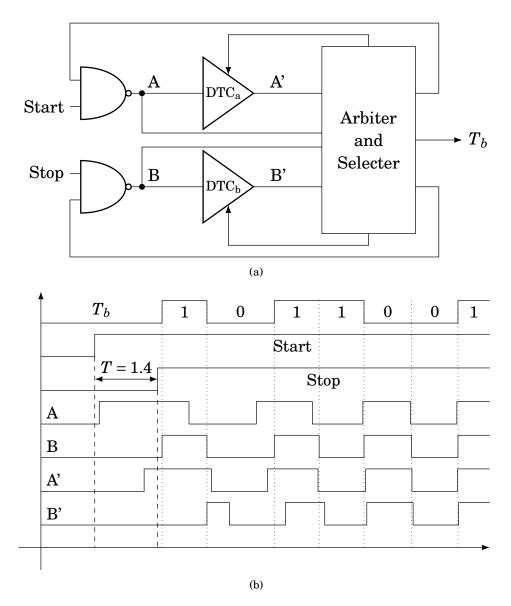

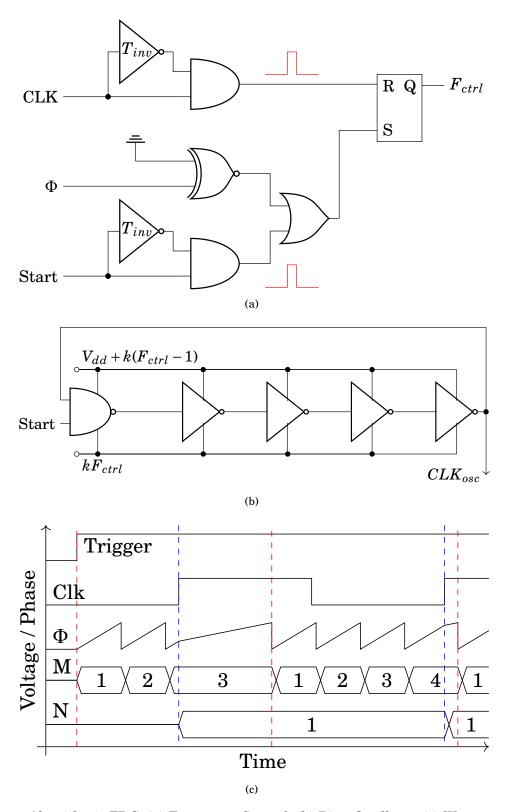

| 3.7  | (a) Block diagram and (b) waveform of a CSA TDC                                              | 90 |

| 3.8  | Algorithmic TDC. (a) Frequency Control. (b) Ring Oscillator. (c) Wave trace for a            |    |

|      | sample conversion based on [5] (residue = $38\%$ of a clock period). Outputs (M, N, M, N,    |    |

|      | ) are 3, 1, 4, 1,                                                                            | 91 |

| 3.9  | A gated ring oscillator.                                                                     | 94 |

| 3.10 | output is dependent on $\frac{T}{T_{c/b}}$                                                      | 96  |

|------|-------------------------------------------------------------------------------------------------|-----|

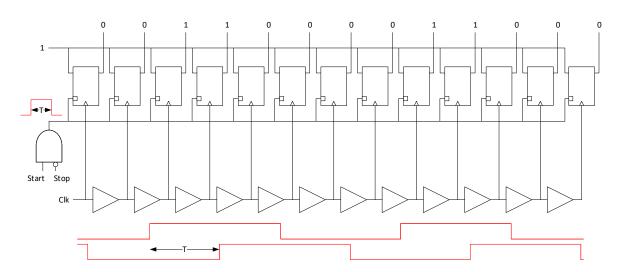

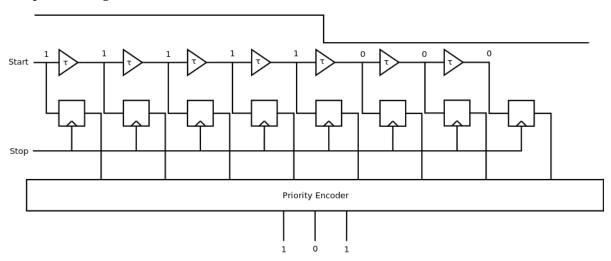

| 9 11 | Initial section of a wave union launcher using multiplexers (the delay line continues           |     |

| 0.11 |                                                                                                 | 07  |

| 0.10 | further)                                                                                        | 91  |

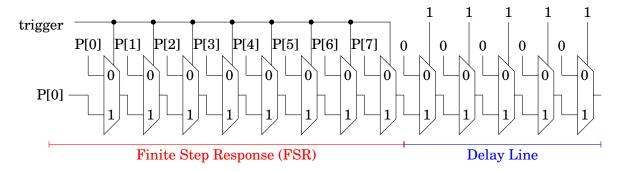

| 3.12 | Example of a type B (ISR) wave union launcher. (a) Gate-level implementation; the               |     |

|      | NAND gate and first three buffers act as the startable oscillator. (b) Waveform of a            |     |

|      | type B wave union launcher where $F_{CLK} > F_{OSC}$                                            | 99  |

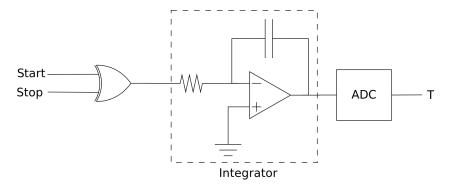

| 3.13 | A TAC-ADC combination acting as a TDC. The integrator could be replaced with any                |     |

|      | other design.                                                                                   | 102 |

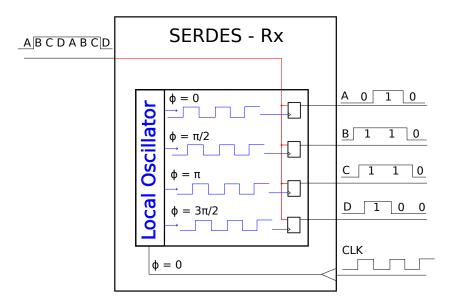

| 3.14 | A SERDES TDC with 4 x interpolation. $\Phi$ is the phase of the clock signal from 0 to $2\pi$ . | 104 |

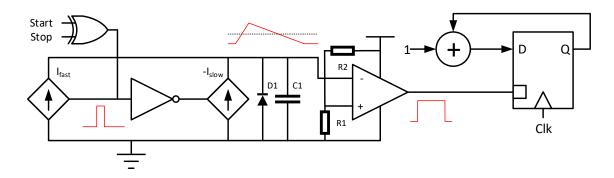

| 3.15 | A dual-slope time amplifier.                                                                    | 105 |

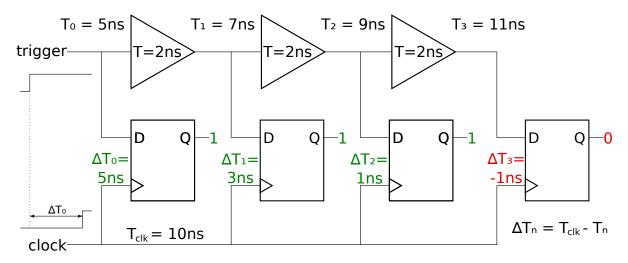

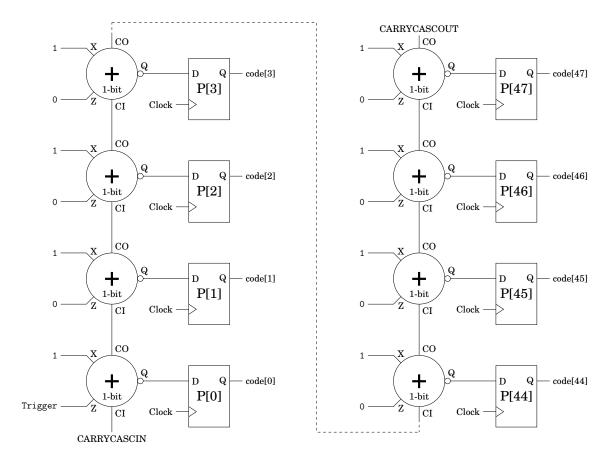

| 4.1  | General operation of a delay line                                                               | 116 |

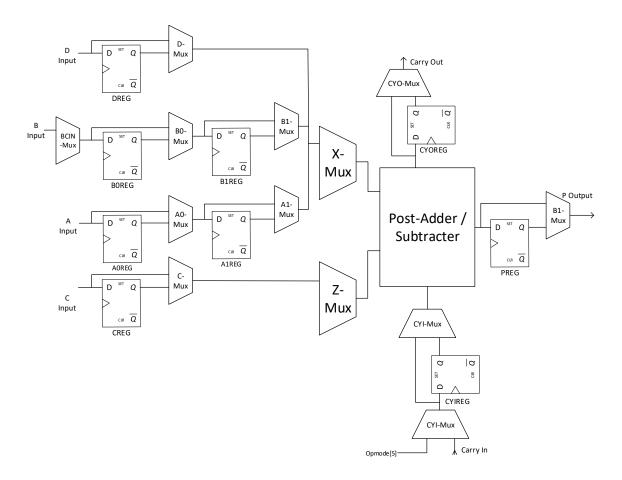

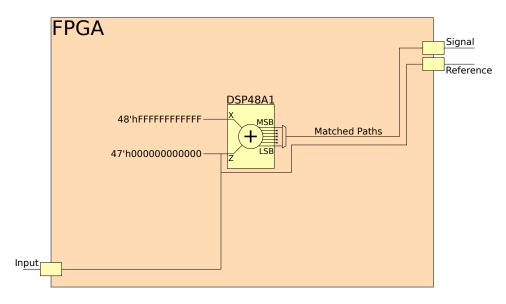

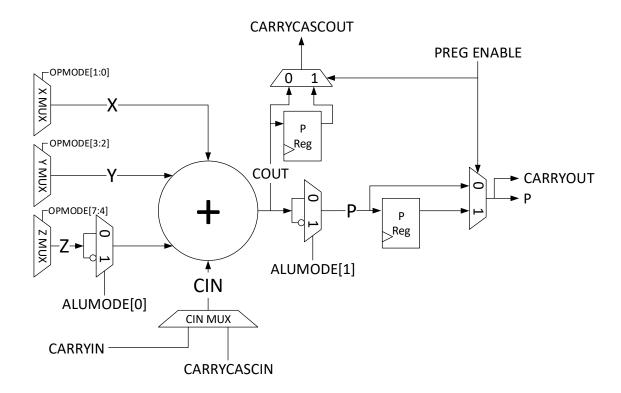

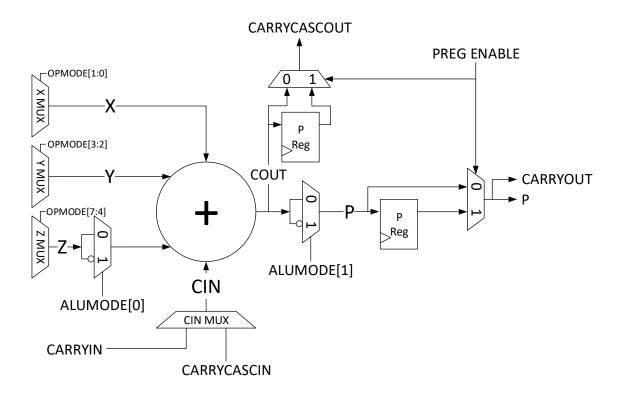

| 4.2  | A simplified block diagram of the DSP48A1 [6]                                                   | 117 |

| 4.3  | The internal architecture of the DSP48A1 block (utilised components only), based on [6].        | 118 |

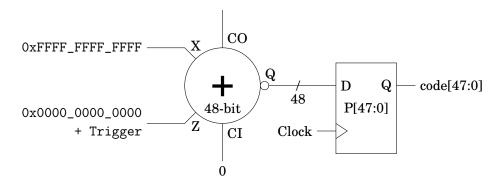

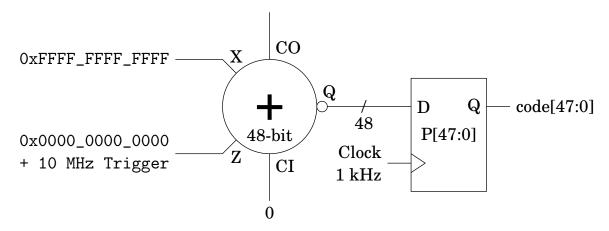

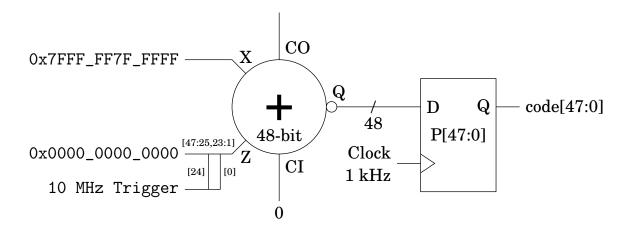

| 4.4  | Configuration of a single DSP block                                                             | 118 |

| 4.5  | Internal operation of a DSP block                                                               | 119 |

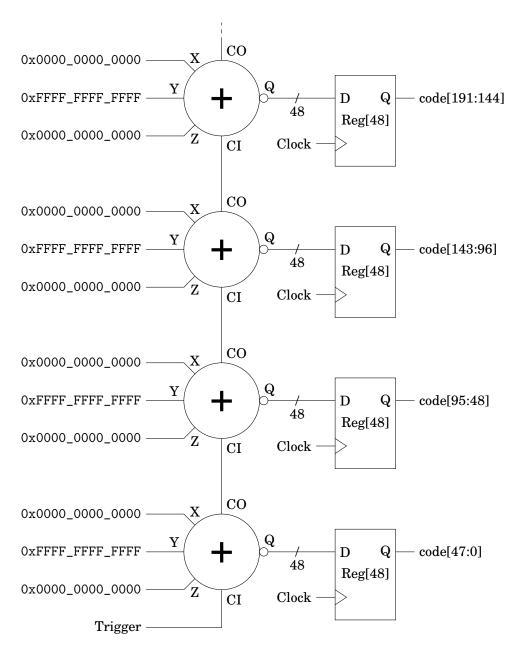

| 4.6  | Configuration of multiple DSP blocks                                                            | 120 |

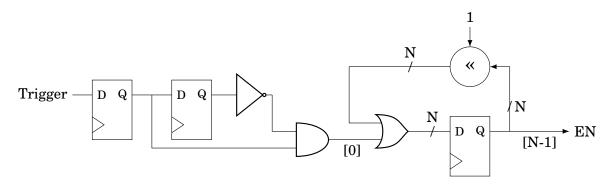

| 4.7  | Trigger logic                                                                                   | 122 |

| 4.8  | DSP48A1 readout logic                                                                           | 123 |

| 4.9  | Generic model of a delay line.                                                                  | 124 |

| 4.10 | Method for average delay testing                                                                | 125 |

| 4.11 | Cyclic code density test                                                                        | 127 |

| 4.12 | Subdivided code density test                                                                    | 128 |

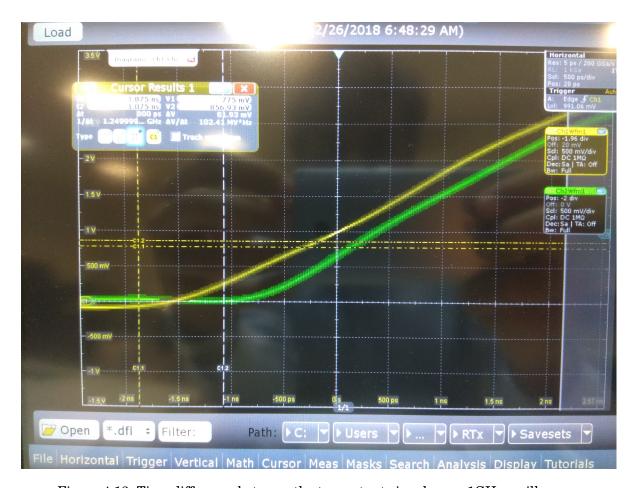

| 4.13 | Time difference between the two output signals on a 1GHz oscilloscope.                          | 129 |

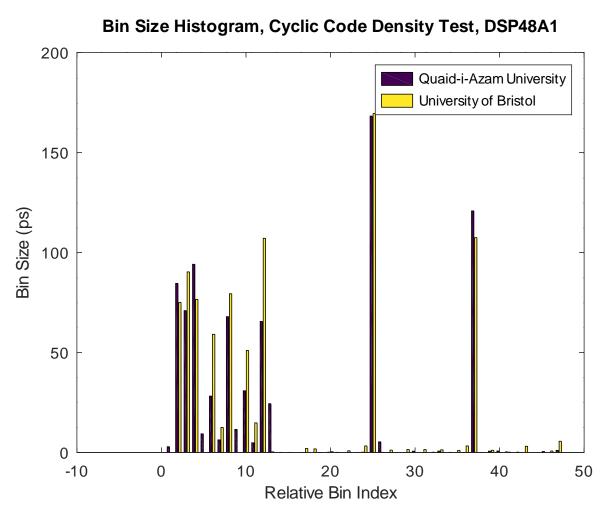

| 4.14 | A histogram of a 384k-hit cyclic code density test, converted to bin sizes. Results from        |     |

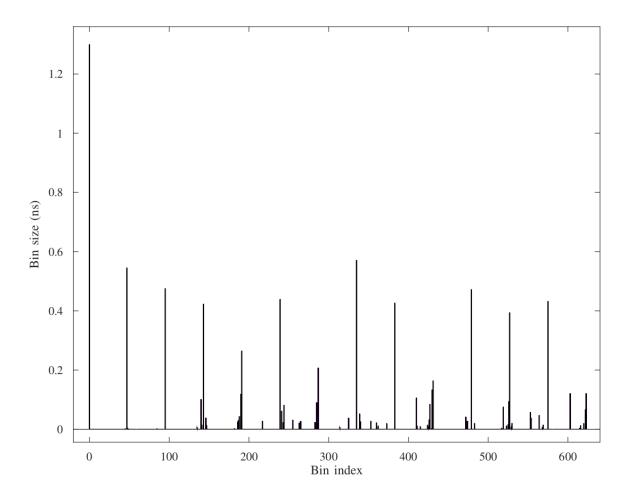

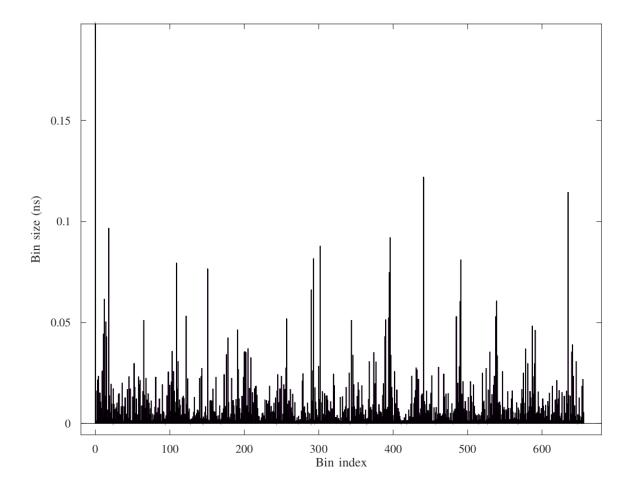

|      | the University of Bristol and Quaid-i-Azam University are shown in parallel                     | 130 |

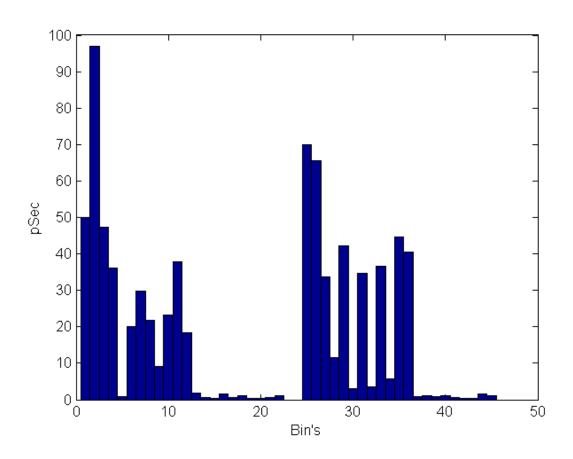

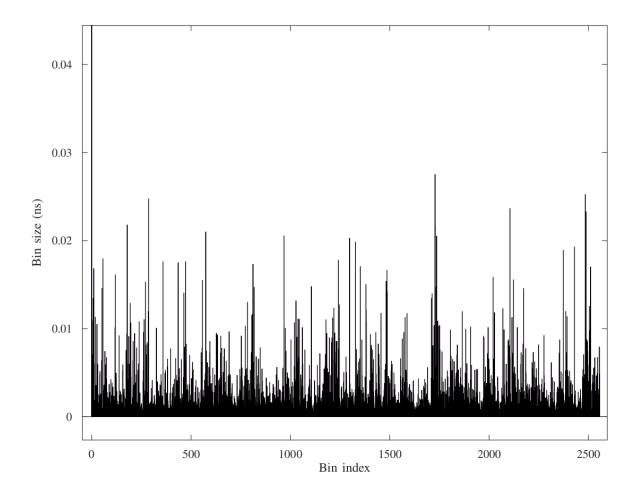

| 4.15 | A histogram of the 384k-hit linear code density test, converted to bin sizes                    | 131 |

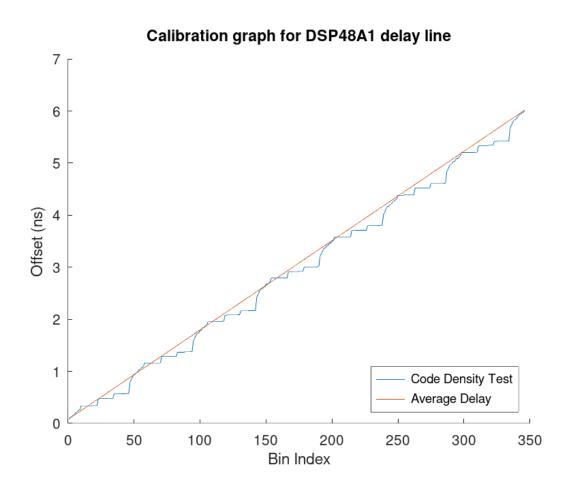

| 4.16 | The calibration chart obtained from a histogram of a 384k-hit linear code density test.         | 132 |

#### LIST OF FIGURES

| 4.17 | The histogram of the subdivided test                                                                             | 133 |

|------|------------------------------------------------------------------------------------------------------------------|-----|

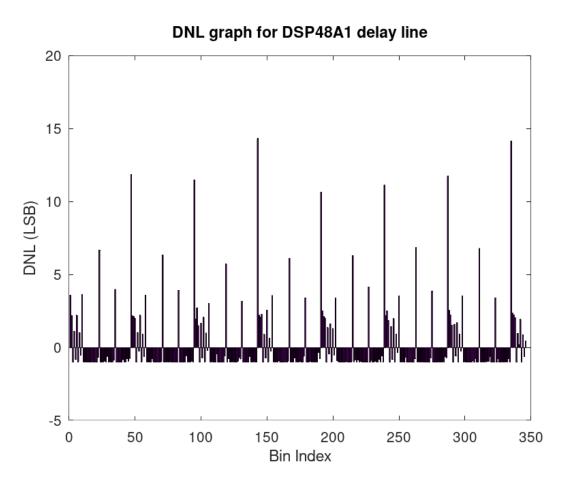

| 4.18 | DNL graph for a DSP48A1 delay line                                                                               | 134 |

| 4.19 | INL graph for a DSP48A1 delay line                                                                               | 135 |

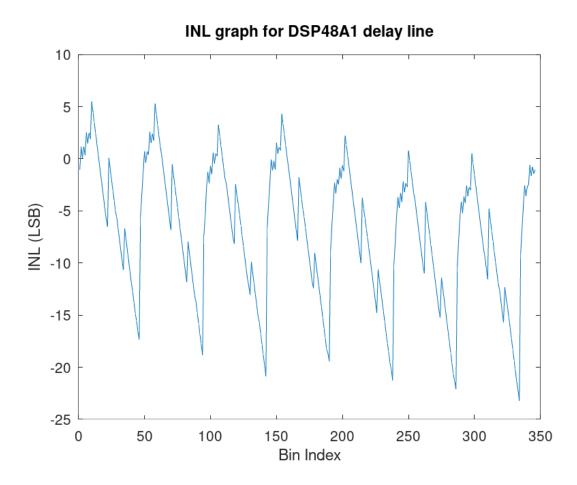

| 4.20 | 96-bin pattern                                                                                                   | 138 |

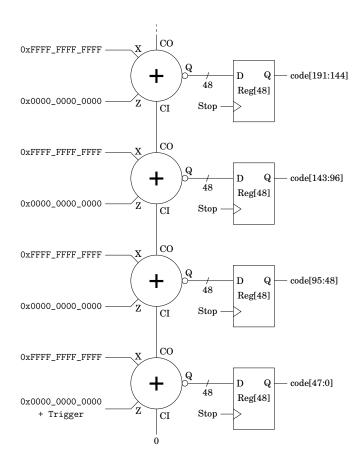

| 4.21 | Overview of the parallel system                                                                                  | 139 |

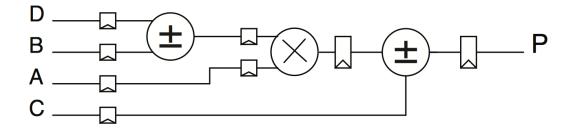

| 4.22 | DSP add/sub operation, showing the purpose of the ALUMODE[1:0] and OPMODE[7:0]                                   |     |

|      | inputs, based on [4]                                                                                             | 141 |

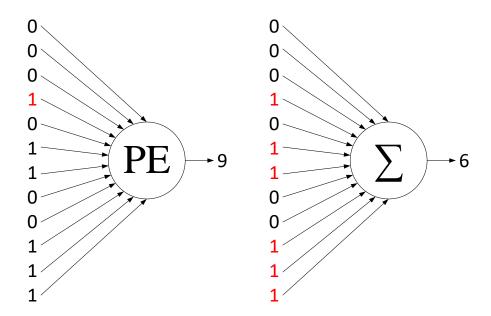

| 4.23 | Configuration of multiple DSP blocks                                                                             | 143 |

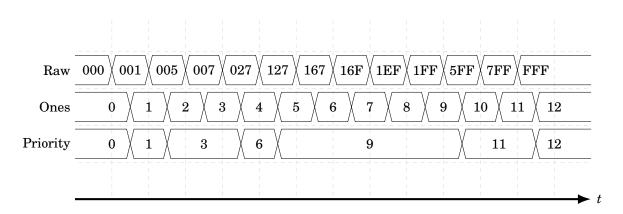

| 4.24 | Priority Encoder vs Ones-Encoder                                                                                 | 144 |

| 4.25 | Waveform of a ones-encoder and priority encoder                                                                  | 144 |

| 4.26 | Monotonic increase of the combination of delay lines $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$              | 145 |

| 4.27 | Overlap of DSP chains                                                                                            | 146 |

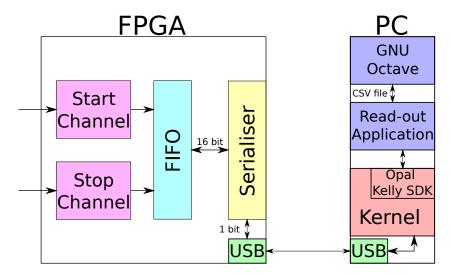

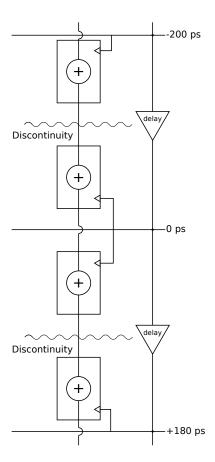

| 4.28 | Block diagram of test setup.                                                                                     | 147 |

| 4.29 | Block diagram of test setup.                                                                                     | 148 |

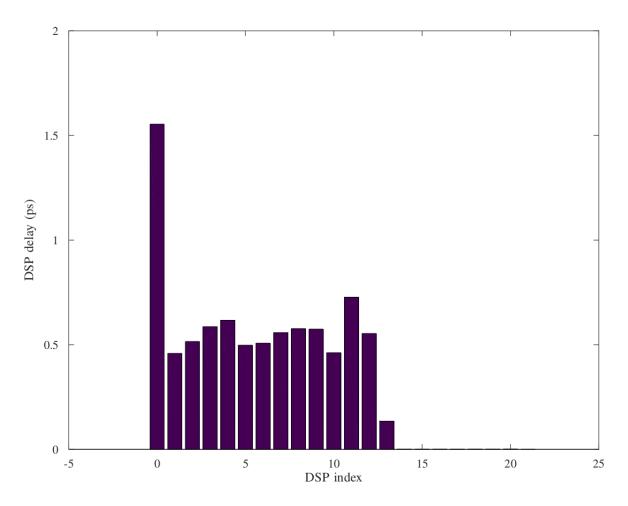

| 4.30 | Delays of the DSP blocks                                                                                         | 149 |

| 4.31 | Average delay within a DSP block                                                                                 | 150 |

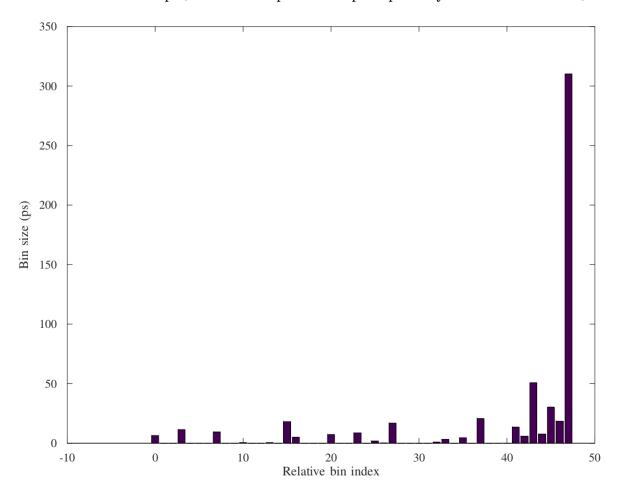

| 4.32 | Linear code density test                                                                                         | 151 |

| 4.33 | Linear code density test with ones-encoder. Bin 0 is 447ps                                                       | 152 |

| 4.34 | Code density test with four offset delay lines. Bins 0 and 1 are 710ps and 106ps                                 |     |

|      | respectively                                                                                                     | 153 |

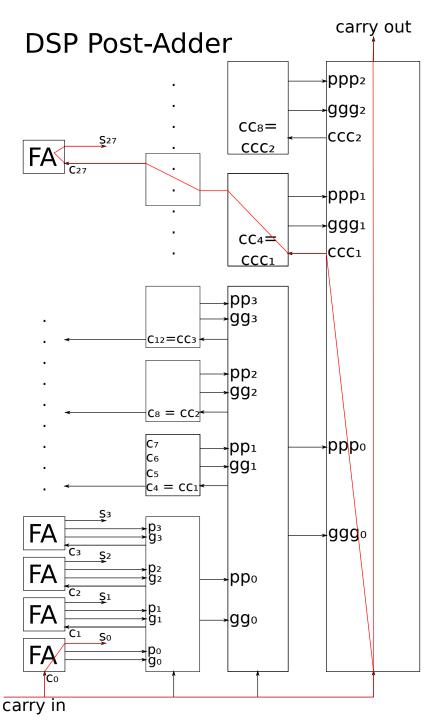

| 4.35 | Internal logic of a DSP48E1 post-adder, demonstrating the out-of-order timings. FA:                              |     |

|      | full adder; $s_i$ : sum output $i$ ; $c_i$ : carry signal $i$ ; $g_i$ carry-generate signal $i$ ; $p_i$ : carry- |     |

|      | propagate signal $i$                                                                                             | 155 |

| 4.36 | Block diagram of test setup.                                                                                     | 158 |

| 4.37 | SSP plotted v.s. temperature.                                                                                    | 160 |

| 4.38 | Channel offset plotted v.s. temperature                                                                          | 160 |

| 4.39 | Bin width histogram for channel 1, 32.7° C                                                                       | 161 |

| 4.40 | Bin width histogram for channel 1, 101° C                                                                        | 162 |

| 4.41 | Variation in resolution (cubic mean bin width) with temperature.                                                 | 162 |

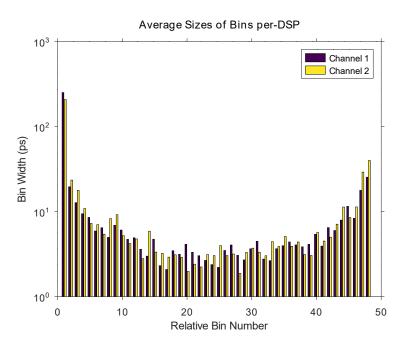

| 4.42 | Per-DSP bin size, 32.7° C                                                                   | 163 |

|------|---------------------------------------------------------------------------------------------|-----|

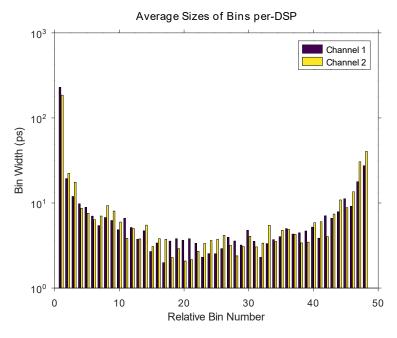

| 4.43 | Per-DSP bin size, 101° C                                                                    | 163 |

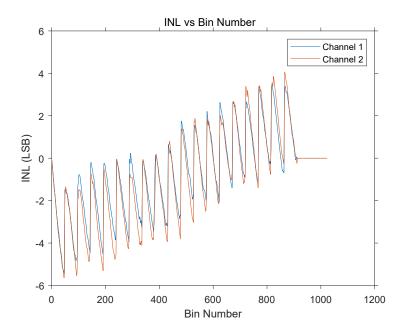

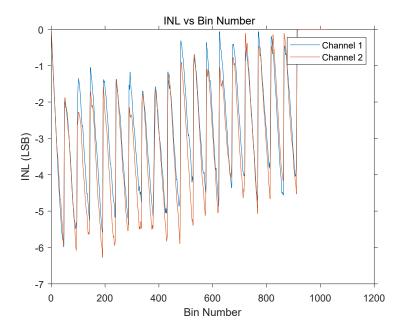

| 4.44 | INL graph at 32.7° C                                                                        | 165 |

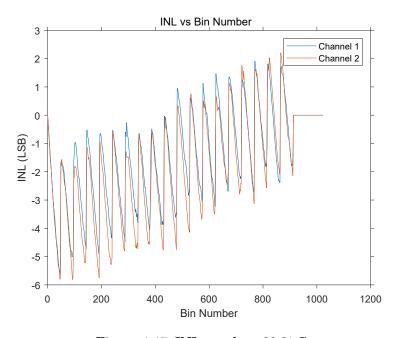

| 4.45 | INL graph at 60.2° C                                                                        | 165 |

| 4.46 | INL graph at 101° C                                                                         | 166 |

| 5.1  | Idea to explore                                                                             | 170 |

| 5.2  | $DSP\ add/sub\ operation, showing\ the\ purpose\ of\ the\ ALUMODE [1:0]\ and\ OPMODE [7:0]$ |     |

|      | inputs, based on [4]                                                                        | 171 |

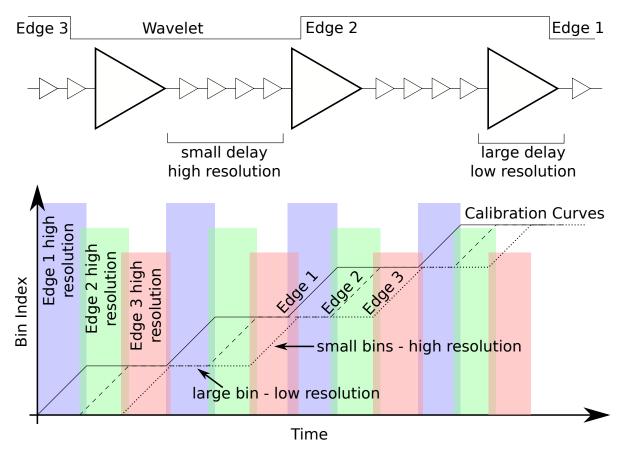

| 5.3  | Operating principle of a wave-union TDC. At any point in time, at least one edge is in      |     |

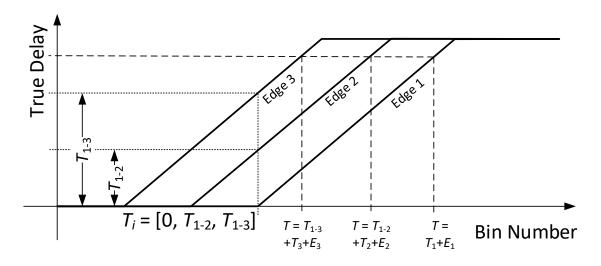

|      | a high-resolution region. Solid line: edge 1; dotted line: edge 2; dashed line: edge 3 1    | 173 |

| 5.4  | Diagram showing relative wave union operation. $T_i$ = time estimate $i$ . $E_i$ = error in |     |

|      | estimate $i$                                                                                | 173 |

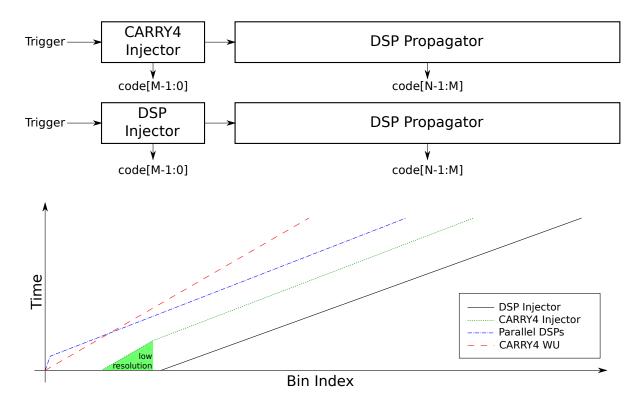

| 5.5  | Comparison between injectors                                                                | 175 |

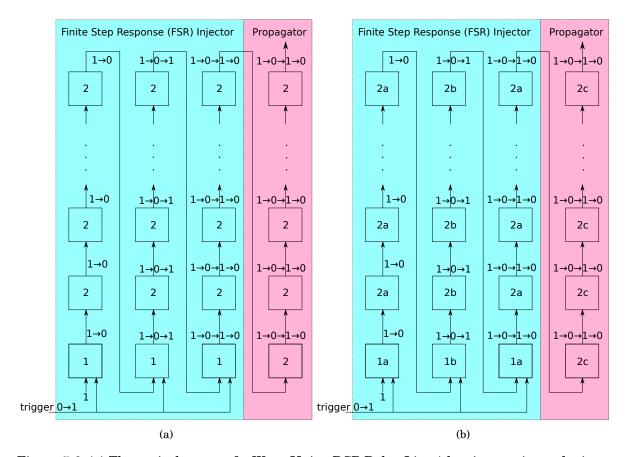

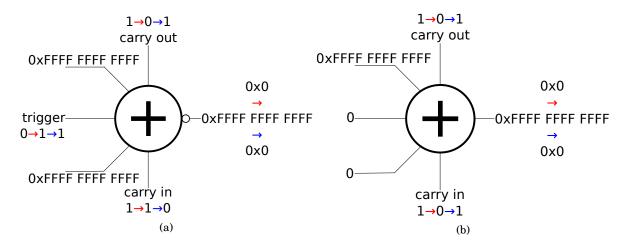

| 5.6  | (a) Theoretical set-up of a Wave-Union DSP Delay Line (showing carries and trigger          |     |

|      | only). Each block marked '1' in the FSR adds another edge to the pulse train. (b) Real      |     |

|      | (on device) set up of the Wave-Union DSP Delay Line (due to differences in architecture).   | 177 |

| 5.7  | (a) Inverting configuration (blocks marked '1'). (b) Non-inverting configuration (blocks    |     |

|      | marked '2')                                                                                 | 177 |

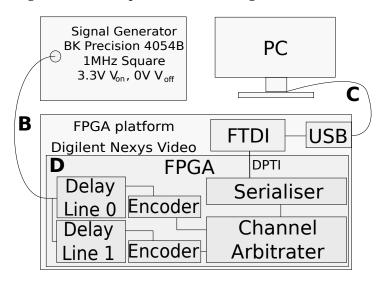

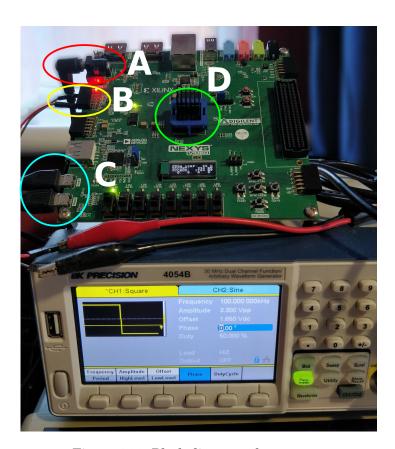

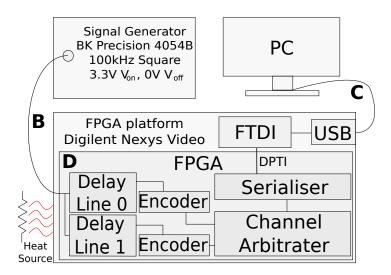

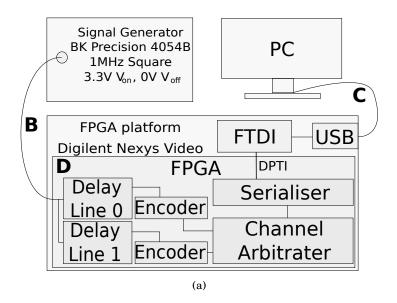

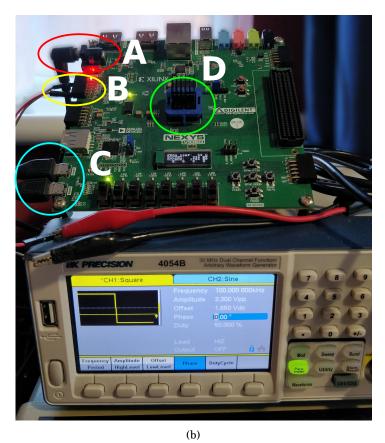

| 5.8  | Test setup (a) diagram and (b) picutre. Red circle (A): power in. Yellow circle (B):        |     |

|      | trigger in. Blue circle (C): data out. Green circle (D): FPGA + heatsink                    | 184 |

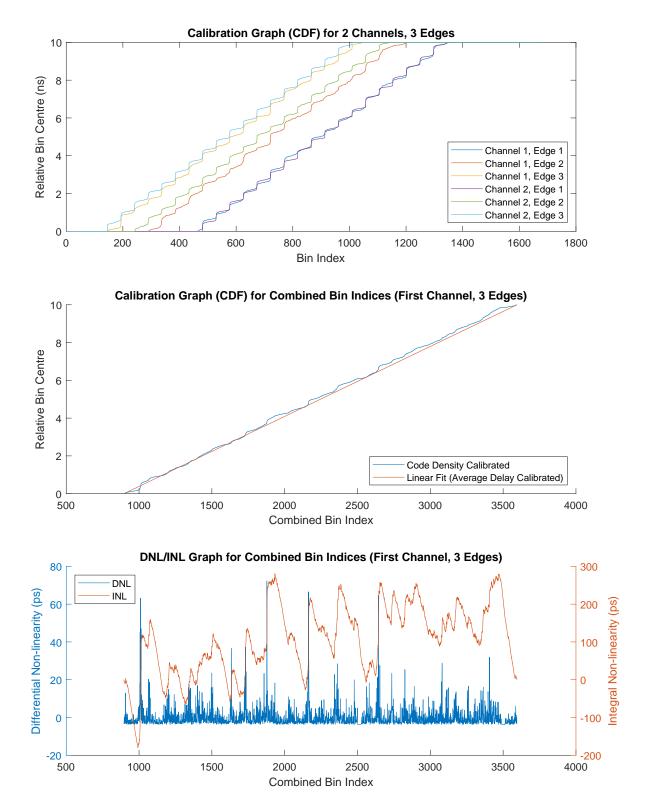

| 5.9  | Calibration and DNL/INL graph for the wave union method                                     | 186 |

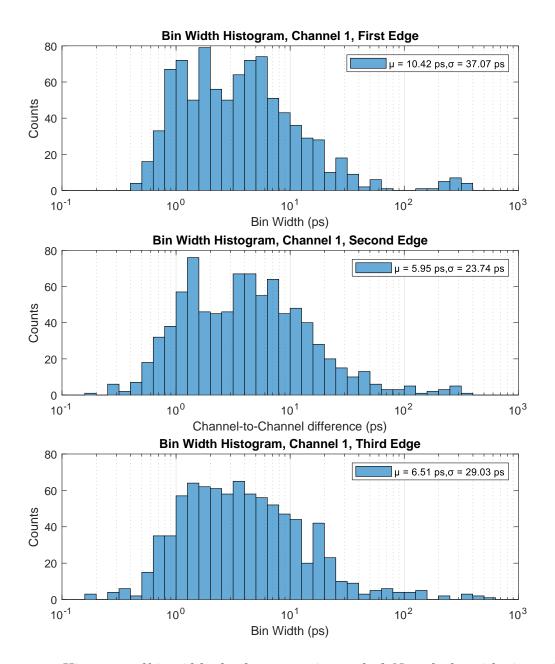

| 5.10 | Histogram of bin widths for the wave union method. Note the logarithmic x axis 1            | 187 |

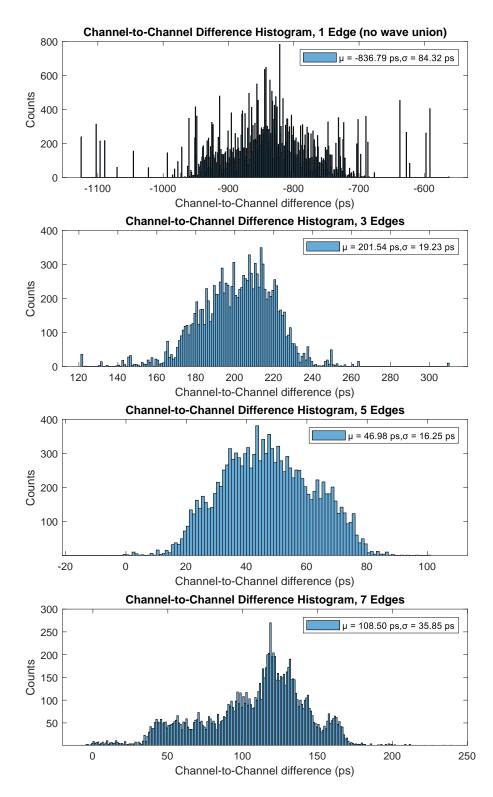

| 5.11 | Histogram of channel differences (precision) for one edge, three edges, five edges and      |     |

|      | seven edges. There are three DSPs of delay per edge                                         | 188 |

| 5.12 | SSP vs Temperature characterisation                                                         | 191 |

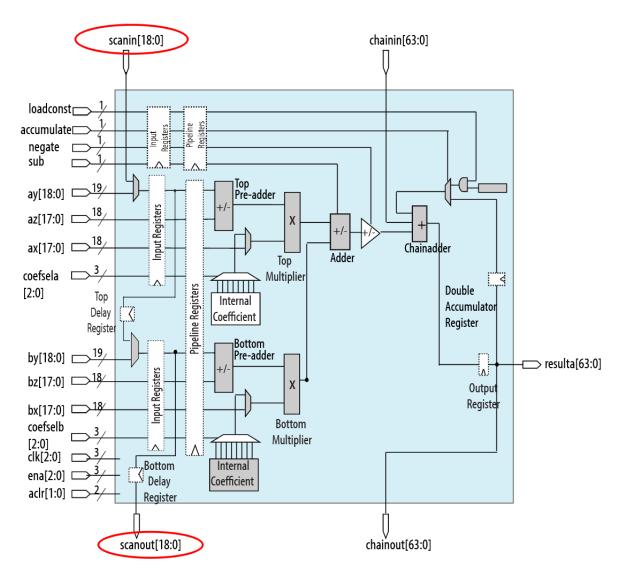

| 5.13 | Intel DSP Block internals [3]. The 'scanin' and 'scanout' ports are highlighted. Regis-     |     |

|      | ters with dashed borders are systolic (optional).                                           | 193 |

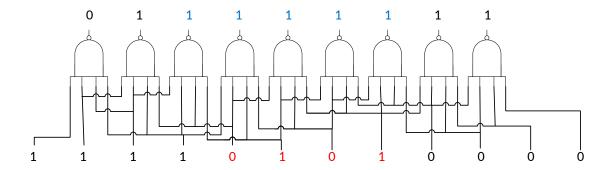

| 6.1  | N-bit NAND bubble corrector                                                                 | 197 |

#### LIST OF FIGURES

| 6.2         | Multiplexer bubble corrector                                                              | 197  |

|-------------|-------------------------------------------------------------------------------------------|------|

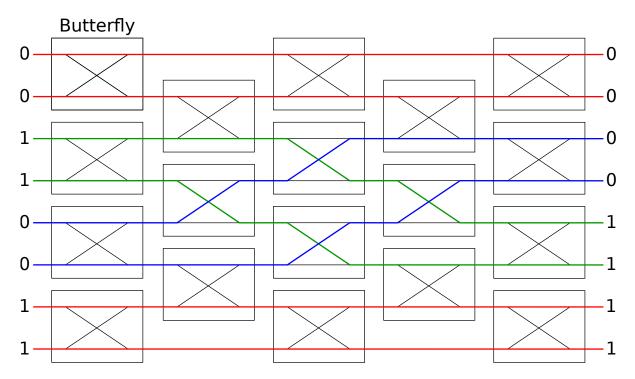

| 6.3         | Butterfly bubble corrector                                                                | 198  |

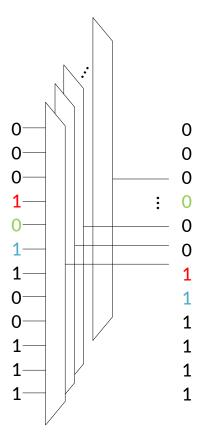

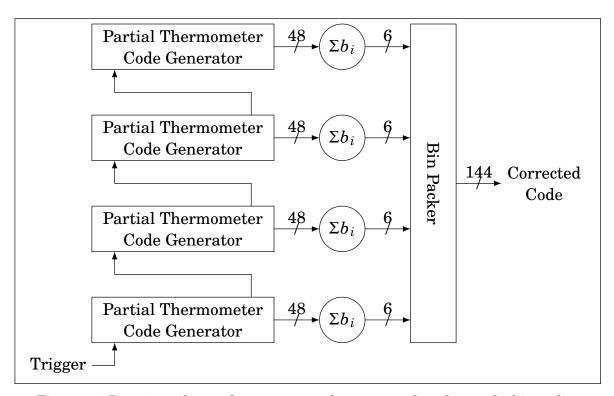

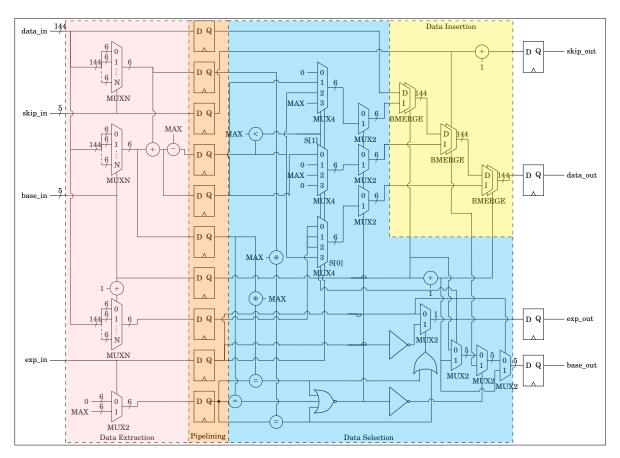

| 6.4         | Data input from code generator to the ones-encoders then to the bin packer                | 199  |

| 6.5         | Block diagram of the bin packer top level                                                 | 200  |

| 6.6         | Kernel pushing ones forward                                                               | 201  |

| 6.7         | Kernel pulling ones backward                                                              | 201  |

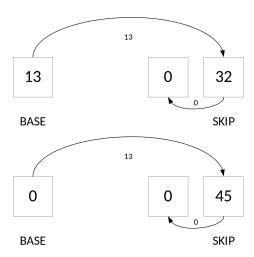

| 6.8         | Change in expected value                                                                  | 202  |

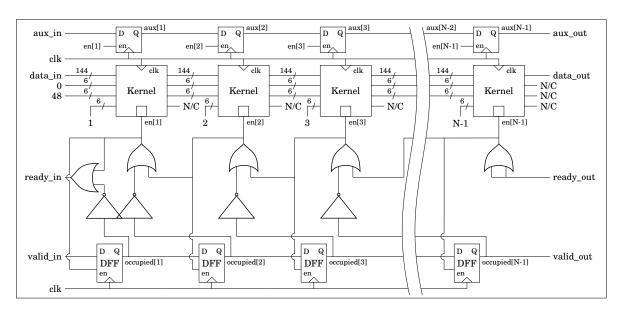

| 6.9         | Advancement of pointers                                                                   | 203  |

| 6.10        | (a) Function of a BMERGE block. (b) Pin arrangement on one of the Kernel blocks           | 209  |

| 6.11        | Schematic for the kernel, with extra pipeline registers                                   | 210  |

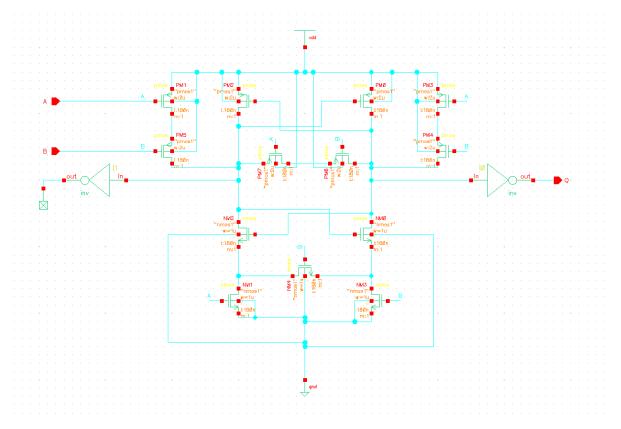

| A.1         | Sense amplifier used as a discriminator in the TDC core. Cell name 'sense'. The 'inv'     |      |

|             | cell is a simple CMOS inverter.                                                           | 219  |

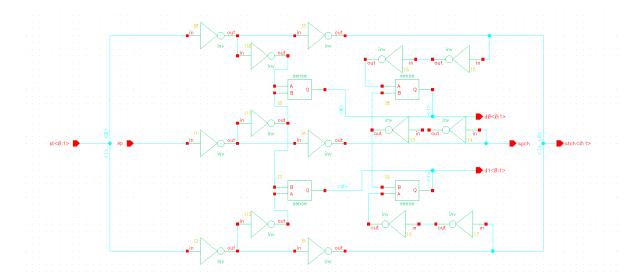

| A.2         | Vernier element used in the TDC core. Implements two taps of the Vernier delay line.      |      |

|             | The top and bottom chains are 'start' chains, while the middle chain is the 'stop' chain. | .220 |

| <b>A</b> .3 | Testbench used to confirm correct operation of the TDC                                    | 220  |

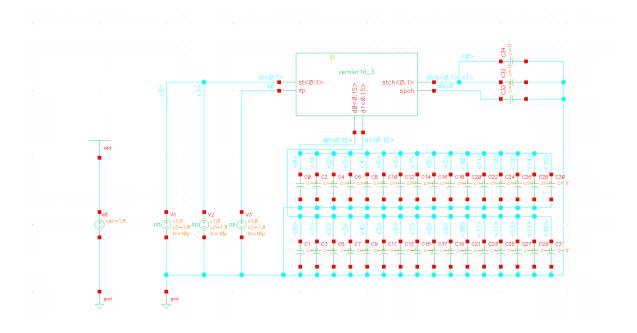

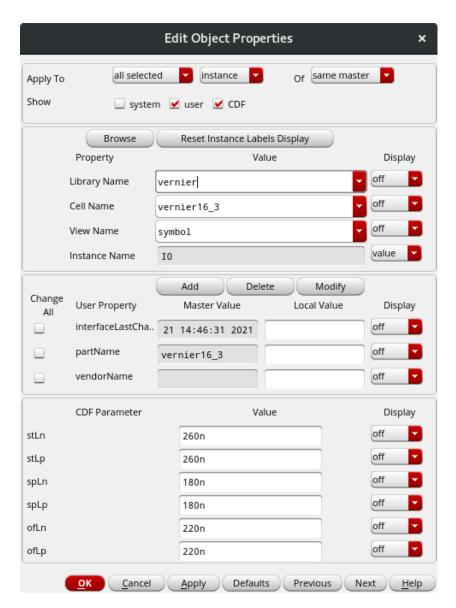

| A.4         | Parameters of the 16 element two-chain Vernier delay line. st = start chains, sp = stop   |      |

|             | chain, of = offset transistors on second start chain, Ln = Length of NMOS transistors,    |      |

|             | Lp = Length of PMOS trnasistors                                                           | 221  |

| A.5         | Vernier delay line for 16 taps                                                            | 221  |

| A.6         | Expressions used to determine the tap delays. delXY = Delay tap X of chain Y. Notice      |      |

|             | how two start channel taps (/I0/stshX<0> and /I0/stshX<1>) map to the same stop           |      |

|             | channel tap (/I0/spshX)                                                                   | 223  |

| A.7         | Delays of the Vernier taps under typical mean scenarios. delXY = Delay tap X of chain Y   | .224 |

| Δ &         | Delays of the Vernier tans under a Monte Carlo simulation                                 | 225  |

CHAPTER

Introduction

#### 1.1 Research Motive

ime-to-Digital Converters (TDCs) are relatively obscure compared to their analog counterparts, Analog-to-Digital Converters (ADCs), due to the relative lack of time-domain systems to which they can be applied. However, this has changed in recent years. Light Detection And Ranging (LiDAR) systems have seen a surge in popularity due to the advent of autonomous ("self-driving") cars, improvements in pulsed lasers and Single-Photon Avalanche Diodes (SPADs) have allowed Quantum Key Distribution (QKD) to become a reality, Phase-Locked Loops (PLLs) are being replaced by All-Digital PLLs (ADPLLs) and many designers are looking to Time-Mode Signal Processing (TMSP) to solve problems that are not tractable with analog systems due to their poor area scaling. As these applications see more widespread adoption, so too will TDCs, and thus TDC designs need to be available to satisfy the performance and cost requirements of these applications.

The current literature on TDCs can best be described as fragmented. Communities have developed around specific applications such as Time-of-Flight (ToF), frequency-locking (such as ADPLLs) and quantum, with very little interaction between these communities. Some researchers are approaching TDCs from a more theoretical perspective, and interacting with many of these

communities, but the penetration of ideas is not very high. Therefore, one of the main goals of this PhD project is to aggregate designs from across the literature and communities, compare and summarise the available architectures, and provide recommendations according to performance requirements.

TDCs are often costly components due to the specific hardware requirements for implementing them. As we will see in later sections, the hardware that can be used for TDC operation is quite limited. If the hardware is expensive, then the cost of integrating a TDC into a system will also be high. Therefore, the other main goal of this PhD project is to develop new TDC architectures which can be used to target unique cost-performance-complexity trade-offs and enable TDCs to be applied to new areas.

#### 1.2 Aims and Goals

The key aims and goals of this PhD project are:

- To identify applications to which TDCs can be applied.

- To identify and define metrics by which TDCs can be compared.

- To review TDC architectures present in the literature, compare them in terms of defined metrics, and make recommendations for the identified applications.

- To develop new TDC architectures with alternative characteristics to those currently available in the literature.

- To identify methods to combine TDC architectures available in the literature to achieve improved characteristics.

# 1.3 List of Contributions

Table 1.1: List of contributions.

|                                        | List of contributions. |                                |

|----------------------------------------|------------------------|--------------------------------|

| Publication                            | My Contribution        | Advancement of the             |

|                                        |                        | State-of-the-Art               |

| S. Tancock and N. Dahnoun, "Digital    | Details on CPU,        | Summarises all the different   |

| Signal Processing Systems: Choosing a  | GPU, FPGA and          | architectures for custom       |

| Processor," in 2020 International      | microcontroller        | algorithms and makes           |

| Conference Engineering and             | architectures.         | suggestions based on           |

| Telecommunication (En&T), Nov 2020,    |                        | performance, cost and power.   |

| Plenary Talk.                          |                        |                                |

| S. Tancock, E. Arabul, and N. Dahnoun, | Review of all          | Brought current review         |

| "A Review of New Time-to-Digital       | current literature,    | literature up to date with the |

| Conversion Techniques," IEEE           | selection of           | inclusion of Successive        |

| Transactions on Instrumentation and    | techniques to          | Approximation, Algorithmic,    |

| Measurement, vol. 68, no. 10, pp.      | include,               | Wave Union, SERDES and         |

| 3406–3417, 2019.                       | comparison and         | DSP Delay Line TDCs. Also      |

|                                        | summarisation of       | summarises available           |

|                                        | techniques.            | calibration and linearisation  |

|                                        |                        | techniques.                    |

| S. Tancock, J. Rarity, and N. Dahnoun, | Discovery, selection,  | Summarises the 14 new TDC      |

| "Developments in Time-to-Digital       | comparison,            | architecture papers, 4 new     |

| Converters during 2020," in 5th        | summarisation and      | TDC application papers, and    |

| International Nordic-Mediterranean     | evaluation of          | 4 review and analysis papers   |

| Workshop on Time-to-Digital            | papers to be           | published in 2020.             |

| Converters and Applications            | included.              |                                |

| NoMe-TDC 2021, 2021.                   |                        |                                |

Continued on next page

Table 1.1: List of contributions. (Continued)

| S. Tancock, E. Arabul, N. Dahnoun,      | Investigation of the | Provided an initial          |

|-----------------------------------------|----------------------|------------------------------|

| and S. Mehmood, "Can DSP48A1            | internal delay       | investigation into the       |

| adders be used for high-resolution      | structure of the     | feasibility of DSP blocks as |

| delay generation?" in 2018 7th          | DSP48A1 blocks,      | delay generators.            |

| Mediterranean Conference on             | collating and        |                              |

| Embedded Computing (MECO), IEEE.        | digesting results.   |                              |

| Institute of Electrical and Electronics |                      |                              |

| Engineers (IEEE), Aug 2018, pp. 1–6.    |                      |                              |

| S. Tancock and N. Dahnoun, "A 5.25      | Creation of the      | Produced a functional TDC    |

| ps-resolution TDC on FPGA using DSP     | TDC core and         | using the FPGA's DSP blocks  |

| blocks," in Proceedings of the Digital  | read-out logic,      | instead of general purpose   |

| Image & Signal Processing'19            | collating and        | logic, reducing logic        |

| conference, October 2019.               | digesting data,      | utilisation and providing a  |

|                                         | speculation on the   | high-resolution TDC.         |

|                                         | internal structure   |                              |

|                                         | of the DSP block.    |                              |

Continued on next page

Table 1.1: List of contributions. (Continued)

| S. Tancock, J. Rarity, and N. Dahnoun, | TDC design,        | Significantly improved the    |

|----------------------------------------|--------------------|-------------------------------|

| "Temperature Characterisation of the   | experimental       | characterisation of the DSP   |

| DSP Delay Line," in 5th International  | set-up and         | blocks as delay generators,   |

| Nordic-Mediterranean Workshop on       | temperature        | providing metrics which were  |

| Time-to-Digital Converters and         | characterisation.  | missing from previous papers  |

| Applications NoMe-TDC 2021, 2021.      |                    | as well as temperature        |

|                                        |                    | sensitivity characterisation. |

|                                        |                    | Lent further evidence to our  |

|                                        |                    | speculations on the internal  |

|                                        |                    | structure of the DSP48E1      |

|                                        |                    | post-adder.                   |

| S. Tancock, J. Rarity, and N. Dahnoun, | TDC design and     | Significantly reduced the     |

| "The Wave-Union Method on DSP          | data collation and | DSP Delay Line's area         |

| Blocks: Improving FPGA-based TDC       | digestion          | requirements using the Wave   |

| resolutions by 3x with a 1.5x area     |                    | Union technique with an       |

| increase," IEEE Transactions on        |                    | FSR injector.                 |

| Instrumentation and Measurement        |                    |                               |

| (Accepted), 2021.                      |                    |                               |

Continued on next page

Table 1.1: List of contributions. (Continued)

| S. Tancock, J. Rarity, and N. Dahnoun,                                                                                                                                                                     | Algorithm and                                                               | Created a new bubble                                                                                                                                                                                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "A Long-Range Hardware Bubble                                                                                                                                                                              | hardware design,                                                            | corrector in hardware that                                                                                                                                                                                                         |

| Corrector Technique for                                                                                                                                                                                    | proof of                                                                    | operates with zero dead time                                                                                                                                                                                                       |

| Short-Pulse-Width and                                                                                                                                                                                      | correctnesss.                                                               | and is capable of correcting                                                                                                                                                                                                       |

| Multiple-Registration Encoders," in 5th                                                                                                                                                                    |                                                                             | multiple large bubbles which                                                                                                                                                                                                       |

| International Nordic-Mediterranean                                                                                                                                                                         |                                                                             | are infeasible with                                                                                                                                                                                                                |

| Workshop on Time-to-Digital                                                                                                                                                                                |                                                                             | traditional bubble correction                                                                                                                                                                                                      |

| Converters and Applications                                                                                                                                                                                |                                                                             | techniques.                                                                                                                                                                                                                        |

| NoMe-TDC 2021, 2021.                                                                                                                                                                                       |                                                                             |                                                                                                                                                                                                                                    |

| S. Tancock, J. Rarity, and N. Dahnoun,                                                                                                                                                                     | TDC design and                                                              | Proof of concept showing that                                                                                                                                                                                                      |

| "Improving TDC Resolution with the                                                                                                                                                                         | simulation.                                                                 | multi-chain techniques may                                                                                                                                                                                                         |

| Multi-Chain Vernier Method," IEEE                                                                                                                                                                          |                                                                             | be possible on Vernier Delay                                                                                                                                                                                                       |

| Access (submitted), 2021.                                                                                                                                                                                  |                                                                             | Lines.                                                                                                                                                                                                                             |

|                                                                                                                                                                                                            |                                                                             |                                                                                                                                                                                                                                    |

| E. Arabul, S. Paesani, S. Tancock, J.                                                                                                                                                                      | Delay line                                                                  | Demonstrated a 320 Mcps,                                                                                                                                                                                                           |

| · ·                                                                                                                                                                                                        | Delay line optimisations,                                                   |                                                                                                                                                                                                                                    |

| E. Arabul, S. Paesani, S. Tancock, J.                                                                                                                                                                      |                                                                             | Demonstrated a 320 Mcps,                                                                                                                                                                                                           |

| E. Arabul, S. Paesani, S. Tancock, J.<br>Rarity, and N. Dahnoun, "A Precise                                                                                                                                | optimisations,                                                              | Demonstrated a 320 Mcps,<br>8.9 ps RMS, 8-channel                                                                                                                                                                                  |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based                                                                                                        | optimisations, dual-clock                                                   | Demonstrated a 320 Mcps,<br>8.9 ps RMS, 8-channel<br>coincidence counter which is                                                                                                                                                  |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based Multi-Channel Coincidence Counting                                                                     | optimisations, dual-clock multisampling,                                    | Demonstrated a 320 Mcps, 8.9 ps RMS, 8-channel coincidence counter which is much higher performance                                                                                                                                |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based Multi-Channel Coincidence Counting System for Quantum Photonics                                        | optimisations, dual-clock multisampling, triggering logic                   | Demonstrated a 320 Mcps, 8.9 ps RMS, 8-channel coincidence counter which is much higher performance than competing 8-channel                                                                                                       |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based Multi-Channel Coincidence Counting System for Quantum Photonics Applications," IEEE Photonics Journal, | optimisations, dual-clock multisampling, triggering logic design and design | Demonstrated a 320 Mcps, 8.9 ps RMS, 8-channel coincidence counter which is much higher performance than competing 8-channel designs and operates beyond                                                                           |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based Multi-Channel Coincidence Counting System for Quantum Photonics Applications," IEEE Photonics Journal, | optimisations, dual-clock multisampling, triggering logic design and design | Demonstrated a 320 Mcps, 8.9 ps RMS, 8-channel coincidence counter which is much higher performance than competing 8-channel designs and operates beyond the saturation rate and                                                   |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based Multi-Channel Coincidence Counting System for Quantum Photonics Applications," IEEE Photonics Journal, | optimisations, dual-clock multisampling, triggering logic design and design | Demonstrated a 320 Mcps, 8.9 ps RMS, 8-channel coincidence counter which is much higher performance than competing 8-channel designs and operates beyond the saturation rate and significantly below the timing                    |

| E. Arabul, S. Paesani, S. Tancock, J. Rarity, and N. Dahnoun, "A Precise High Count-Rate FPGA Based Multi-Channel Coincidence Counting System for Quantum Photonics Applications," IEEE Photonics Journal, | optimisations, dual-clock multisampling, triggering logic design and design | Demonstrated a 320 Mcps, 8.9 ps RMS, 8-channel coincidence counter which is much higher performance than competing 8-channel designs and operates beyond the saturation rate and significantly below the timing noise floor of the |

#### 1.3.1 Comparison between the Literature and My Contributions

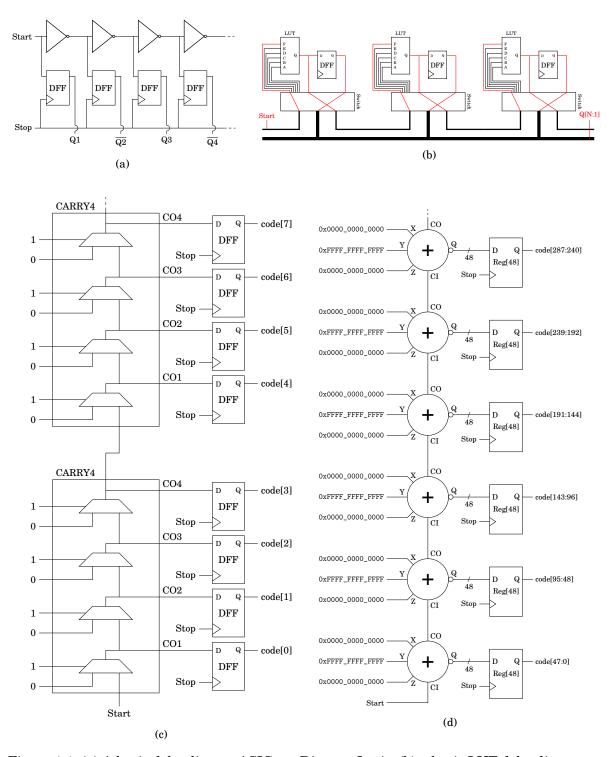

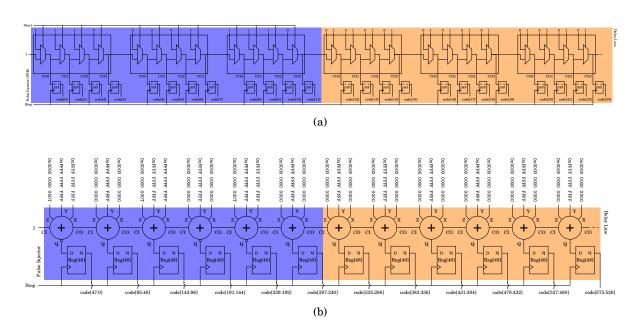

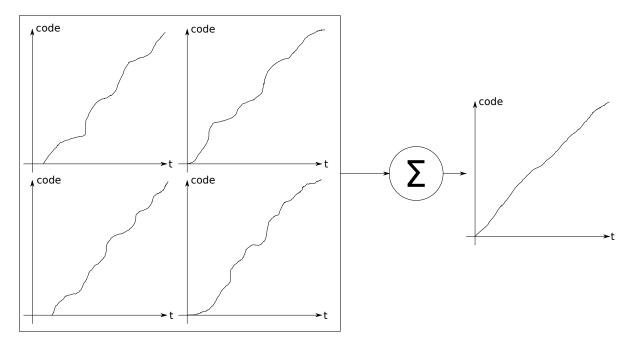

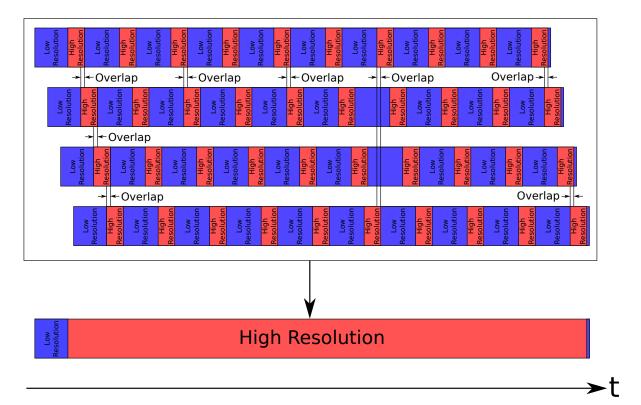

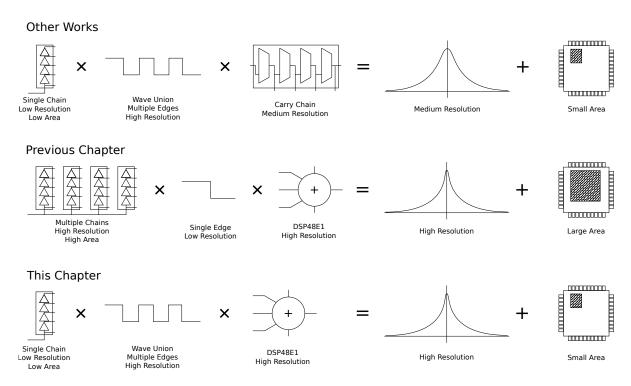

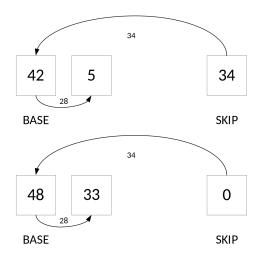

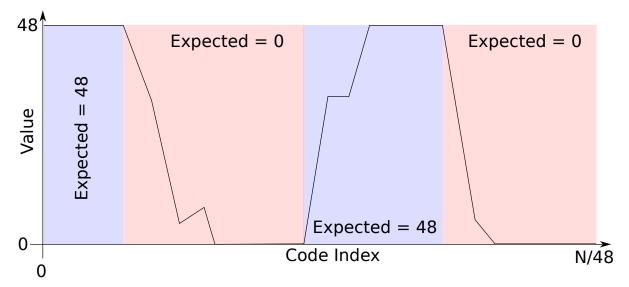

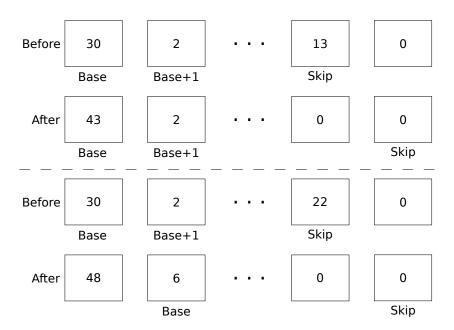

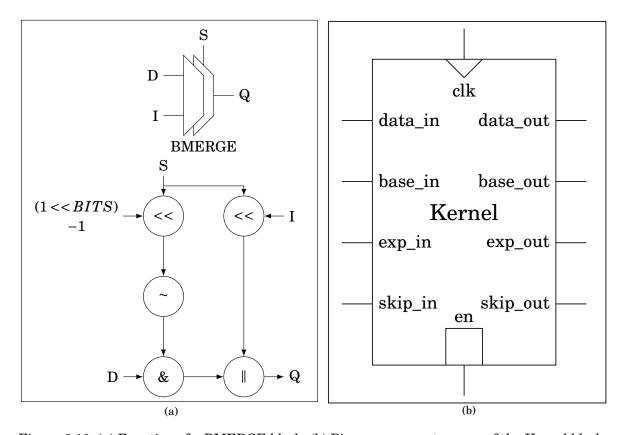

Figure 1.1: (a) A basic delay line on ASICs or Discrete Logic; (b) a basic LUT delay line on an FPGA; (c) state-of-the-art: a carry chain based delay line; (d) my contribution: a DSP block based delay line.

Figure 1.2: (a) Current state-of-the-art: the wave union method on carry chains; (b) my contribution: the wave union method on DSP blocks (T = Start).

Table 1.2: Comparison of DSP and carry chain delay lines.

| Technique            | Device            | Resource                        | Resolution (average) | Utilisation<br>(10 ns clock) |  |

|----------------------|-------------------|---------------------------------|----------------------|------------------------------|--|

| Delay Line           | Spartan-6<br>FPGA | 6-input look-up<br>table (LUT6) | 20 ps                | 128 CLBs                     |  |

| Delay Line           | Artix-7 FPGA      | 6-input look-up<br>table (LUT6) | 15 ps                | 170 CLBs                     |  |

| DSP Delay Line       | Spartan-6<br>FPGA | DSP Block<br>(DSP48A1)          | 16.7 ps              | 13 DSPs                      |  |

| DSP Delay Line       | Artix-7 FPGA      | DSP Block<br>(DSP48E1)          | 9.8 ps               | 22 DSPs                      |  |

| 4x DSP Delay<br>Line | Artix-7 FPGA      | DSP Block<br>(DSP48E1)          | 5.25 ps              | 74 DSPs                      |  |

| 8x DSP Delay<br>Line | Artix-7 FPGA      | DSP Block<br>(DSP48E1)          | 3.70 ps              | 146 DSPs                     |  |

#### 1.4 Structure of this Thesis

In the following sections, the applications of TDCs and metrics by which we evaluate them will be explained. Chapter 2 is the next chapter and describes the different hardware available for a possible implementation of a TDC. It will describe the benefits and drawbacks of various technologies before diving into more detail on Field Programmable Gate Arrays, which have been the main focus of this PhD project. After that, Chapter 3 will present a detailed review of TDC architectures in the available literature, showing the performance-cost trade-offs that are already available to designers. Related to this chapter are the first two major contributions of this PhD project, a review paper published in IEEE Transactions on Instrumentation and Measurement [8] and another published in the Nordic Mediterranean Time-to-Digital Converter Workshop (NoMeTDC) [9]. Then, Chapter 4 will describe the third major contribution of this PhD project, a new TDC architecture implemented on an FPGA's DSP blocks [10-13]. After that, Chapter 6 will describe the bubble correction logic designed for use in high-performance TDCs on DSP blocks [14]. This logic solves a major issue with the DSP block TDCs, namely the long bubbles that occur in the thermometer codes. Next, Chapter A will describe the final major contribution of this PhD project: the Multi-Chain Vernier TDC architecture [15]. Finally, Appendix B will detail other contributions I have made to the wider field of Electronic Engineering.

### 1.5 Applications

Time-to-digital converters (TDCs) play a vital role in almost all computational systems in existence. From their appearance in Phase-Locked Loops (PLLs), where they measure the difference between the loop and the reference clock to avoid clock drift, to Time of Flight (ToF) applications where the time between an emission and reception is measured to discover information about an object from which the signal was reflected or the environment through which the signal passed. In addition, there are also quantum versions of these applications, where the signal is a single quantum, and the PLL or time-of-flight measurement must perform well despite some quanta being lost in-flight. They also make an appearance in medical imaging, as some systems such as Positron Emission Tomography (PET) and Fluorescence Lifetime Imaging (FLIM) use the ToF or

absorption time of tissues or substances to form an internal image of a complex structure such as a human body.

Table 1.3: Comparison of performance requirements for TDC applications.

| Application                                         | SSP      | Dead<br>Time | DNL<br>(LSB) | INL<br>(LSB) | Range               | Channels | Power               |

|-----------------------------------------------------|----------|--------------|--------------|--------------|---------------------|----------|---------------------|

| LiDAR (automotive, single-point, forward-facing)    | < 100 ps | < 10 ns      | < 1          | < 10         | > 1 us <sup>1</sup> | 1        | < 10 W              |

| LiDAR (automotive, single-point, all-around)        | < 100 ps | < 1 ns       | <1           | < 10         | > 500 ns            | 1        | < 50 W              |

| LiDAR (automotive, multi-point, all-around)         | < 100 ps | < 10 ns      | <1           | < 10         | > 500 ns            | ≥ 8      | < 50 W              |

| Coincidence Counting (Positron Emission Tomography) | < 10 ps  | < 10 ns      | < 5          | < 20         | > 10 ns             | ≥ 2      | _ 2                 |